# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA CURSO DE ENGENHARIA DE COMPUTAÇÃO

# FELIPE ROCHA DA ROSA

# Fast and Accurate Evaluation of Embedded Applications for Many-core Systems

Bachelor Thesis presented in partial fulfillment of the requirements for the degree of Computer Engineer.

Advisor: Prof. Dr. Ricardo Reis Co-advisor: Prof. Dr. Luciano Ost

# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos Alexandre Netto Vice-Reitor: Prof. Rui Vicente Oppermann

Pró-Reitor de Graduação: Prof. Sérgio Roberto Kieling

Diretor do Instituto de Informática: Prof. Luís da Cunha Lamb

Coordenador do Curso de Engenharia de Computação: Prof. Marcelo Götz Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

"Scientists investigate that which already is; Engineers create that which has never been." Albert Einstein

"Scientists dream about doing great things.

Engineers do them."

James A. Michener

#### **RESUMO**

# Avaliação rápida e precisa de aplicações embarcadas para sistemas de muitos núcleos

Sistemas embarcados multiprocessados (*Many-cores*) são apontados com a solução mais viável para abordar as emergentes restrições de design em custo, potência e performance [Borkar and Chien 2011]. Todavia, conceber estes sistema impõe novos desafios para engenheiros de software, compreendendo entre outros: (i) definição de protocolos de comunicação entre processos, (ii) analisar e portar sistemas operacionais, (iii) possiblidade de melhor explorar modelos de programação para tratar de questões para processamento paralelo. [Marongiu and Benini 2012], (*iv*) desenvovilmento de *drivers* [Gray and Audsley 2012], (v) traduzir aplicações entre sistemas multiprocessados.

Esta crescente complexidade de software faz com que a verificação funcional tornese mais difícil, como resultado, engenheiros de software estão dedicando-se para escalar a performance. Tornado a simulação critica durante o desenvolvimento de software, principalmente nas fases inicias, durante a exploração do espaço de design.

Plataforma virtuais *Event-driven* e *quasi-cycle accurate* como GEM5 tem como objetivo o desenvolvimento micro arquitetural uma vez que modelos detalhados são fornecidos (e.g. protocolo de coerência de cache) [Binkert et al. 2011 p. 5]. Este tipo de simuladores não é escalável a um grande número de processadores, especialmente quando se trata de usabilidade, facilidade de criação de modelos e tempo de simulação.

O contexto resultante leva a adoção de plataformas virtuais que são capazes de simular sistemas embarcadas executando código de aplicações reais a velocidade de centenas de milhões de instruções por segundo [Sanchez and Kozyrakis 2013]. Nestes cenários o *Open Virtual Plataforms (OVP)* [Imperas 2014] está emergindo com um poderoso framework de simulação provendo dezenas de arquiteturas (e.g. ARM, MIPS, MicroBraze, etc.) e vários periféricos (e.g. memória cache). No entanto, o simulador OVP semelhantemente a outros simuladores JIT-based não provem modelos precisos mas, em modelos com precisão em nível de instruções, o qual provem estimativas incorretas de software (e.g. estimativas de energia e tempo de execução).

Este trabalho objetiva começar a tratar os desafios impostos na construção de simuladores *JIT-Based* adequados para estimativas de software, aprimorando a capacidade de engenheiros de software melhor explorar o espaço de design em estágio inicial de desenvolvimento de sistemas. Nesta tese, será apresentado um modelo chamado *Watchdog* visando fornecer estimativas de energia e tempo de execução em uma metodologia integrável em qualquer simulador baseado em *JIT*

A metodologia proposta foca em um modelo baseado em eventos, baseada nas instruções individualmente executadas, simplificando a construção entorno do simulador. Adicionalmente, a abordagem proposta nesta tese é puramente *run-time*, isto significa que toda a computação necessária para implementar o modelo é realizada concomitante com a simulação, evitando enorme quantidade de uso de memória necessária para abordagens baseadas em *trace-driven* ao mesmo tempo que mantém a escalabilidade para sistemas *many-core*.

A fim de demonstrar a validade do modelo proposto, várias conjuntos de aplicações populares foram selecionados, dentre elas MiBench [Guthaus et al. 2001], Mälardalen WCET [Jan Gustafsson 2010], SPLASH-2 [Woo et al. 1995].

Os resultados mostram que a precisão do nosso modelo de tempo de execução varia de 0,6% a 11,5%, com 4,35% em de erro média. O modelo de energia atinge 0,01% a 8,6% de precisão dependendo do perfil de referência com um erro médio de 4,33%. Além disso, o modelo foi submetido a cenários de 1000 processadores mantendo um desempenho estável de 1,8 MIPS.

**Palavras-chave**: Sistemas multiprocessados. Estimativas de Energia. Estimativa de tempo de execução. Sistemas Embarcados.

#### **ABSTRACT**

Many-core embedded systems are pointed to be the most viable solution to addressing emerging design constraints on cost, power and performance scalability [Borkar and Chien 2011]. Nevertheless, conceive and design many-core systems impose new challenges to software engineers, comprising among other: (*i*) inter- processor communication protocol stacks definition, (*ii*) operating system (OS) porting and analysis, (*iii*) exploration of better programming model facilities to address parallel programming [Marongiu and Benini 2012], (*iv*) drivers development [Gray and Audsley 2012], (*v*) application software portability for heterogeneous multiprocessing hardware.

This increasing software complexity makes the software functional verification more difficult, as result, software engineers are struggling to scale up the system performance. Simulation becomes critical to software development, principally in early stage during space design exploration where many design decisions must be taken.

This work address the challenge of making JIT-Based simulator as OVP suitable for software performance estimation, providing to software engineers better means to explore the design space at early stage of system development. This Bachelor Thesis proposes two instruction-driven performance models, which can be used for early software performance evaluation, which were integrated into a JIT-based simulator. The proposed approach is a purely run-time based, i.e. the entire computation necessary to implement the model is concomitant with the simulation, avoiding huge amount of memory usage.

The proposed models were validated by using several benchmarks suits MiBench [Guthaus et al. 2001], Mälardalen WCET [Jan Gustafsson 2010], SPLASH-2 [Woo et al. 1995]. Results show that the accuracy of our timing model varies from 0.6% to 11.5% with 4.35% in average. In turn, the energy model provides an accuracy of 0.01% to 8.6% depending on the benchmark profile with a mean error of 4.33%. Additionally, the model was submitted to 1000 CPU's scenarios maintaining a stable performance of 1.8 MIPS.

**Keywords**: Many-Core Systems. Energy Estimation. Timing Estimation Embedded Systems.

# LIST OF FIGURES

| FIGURE 1.1 - SOFTWARE AND ARCHITECTURAL DESIGN COSTS FOR EMBEDDED SYSTEMS AT ADVANCED PROCESS         |          |

|-------------------------------------------------------------------------------------------------------|----------|

| TECHNOLOGIES. FIGURE EXTRACTED FROM IBS 2013 [IBS 2013]                                               | 12       |

| FIGURE 3.1 - OVP VIRTUAL PLATFORM SIMULATION INTERFACES. FIGURE EXTRACTED FROM [DAVIDMANN AND GRAH    | AM       |

| 2014]                                                                                                 | 19       |

| FIGURE 3.2- SCALABILITY OF TIME SLICE.                                                                | 20       |

| FIGURE 3.3 - BLOCK DIAGRAM AND MAIN FLOW OF THE RUN-TIME BASED APPROACH.                              | 22       |

| FIGURE 3.4 - CALLBACK EXAMPLE CODE                                                                    | 24       |

| FIGURE 4.1 - PROPOSED INSTRUCTION-DRIVEN EVALUATION FLOW                                              | 26       |

| FIGURE 4.2 - BLOCK DIAGRAM OF THE ENERGY APPROACH                                                     | 28       |

| FIGURE 5.1 - BLOCK DIAGRAM OF DEVELOPED WATCHDOG MODULE THREAD EXTENSION                              | 31       |

| FIGURE 6.1 - ADOPTED REFERENCE BOARD PLATFORM. PROPOSED ILLUSTRATION INTEGRATES FIGURES CAPTURED FROM | √I THEIR |

| OWNER'S WEBSITES.                                                                                     | 32       |

| FIGURE 6.2 - SAMPLE CODE NECESSARY TO ACCESS THE DWT REGISTERS.                                       | 33       |

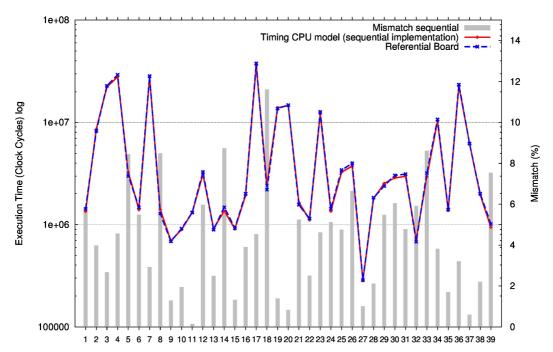

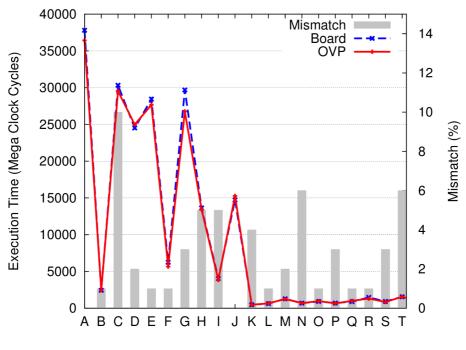

| FIGURE 6.3 - EXECUTION TIME COMPARISON BETWEEN REAL BOARD AND PROPOSED TIMING MODEL                   | 35       |

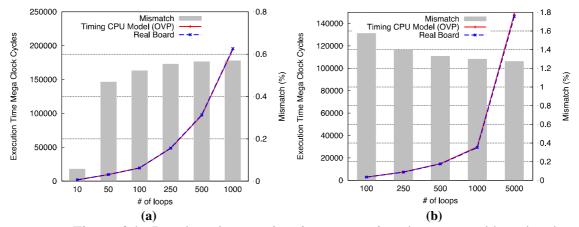

| FIGURE 6.4 - BENCHMARK EXECUTION TIME COMPARISON BETWEEN REAL BOARD AND TIMING CPU MODEL (OVP), VA    | ARYING   |

| THE NUMBER OF LOOPS. LEFT A FFT (A) AND IN RIGHT A HARMONIC (B) APPLICATION                           | 36       |

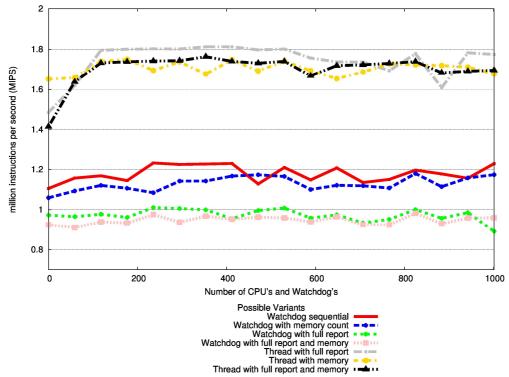

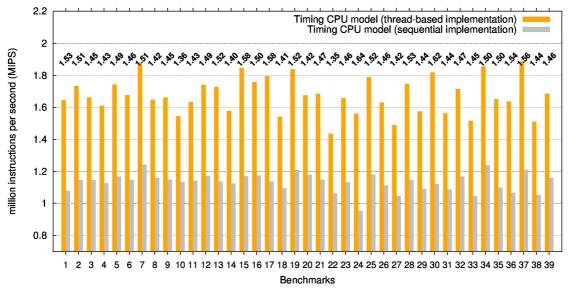

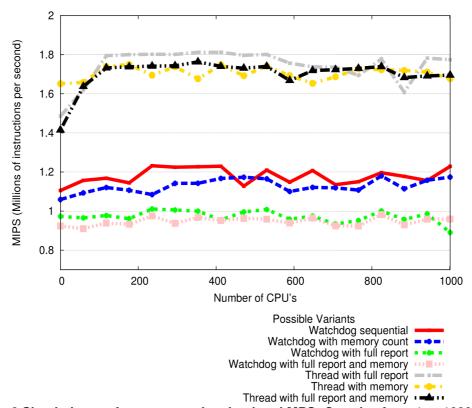

| FIGURE 6.5 - SIMULATION PERFORMANCE AS THE SIMULATED MPSOC SCALES FROM 1 TO 1000 CPUS                 | 37       |

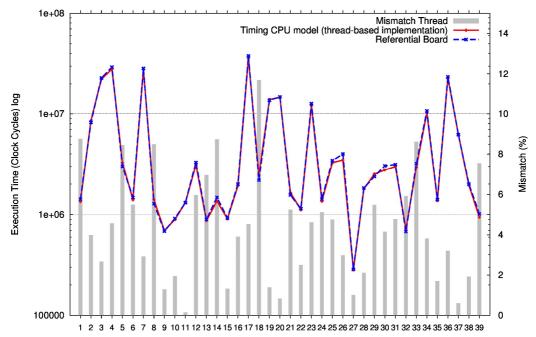

| FIGURE 6.6 - EXECUTION TIME COMPARISON BETWEEN REAL BOARD AND PROPOSED THREAD EXTENSION               | 37       |

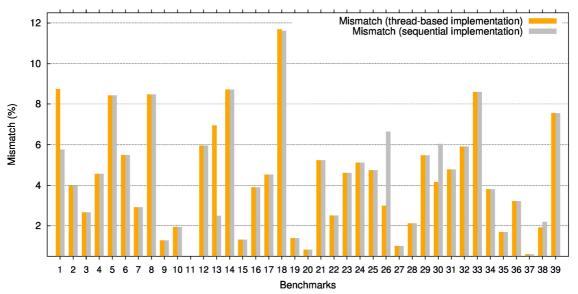

| FIGURE 6.7 - COMPARISON BETWEEN THE TIMING MODEL MISMATCH AND THE THREAD EXTENSION MISMATCH           | 38       |

| Figure 6.8 - Speedup comparison between timing model in sequential and thread extension versions      | 39       |

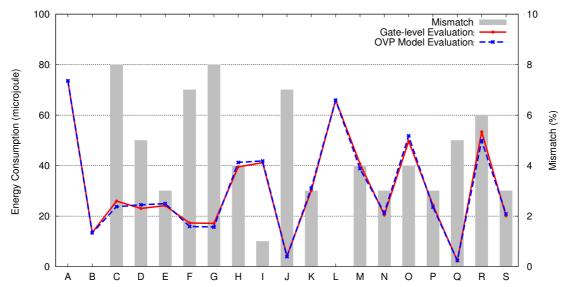

| FIGURE 6.9 - APPLICATION BENCHMARK ENERGY CONSUMPTION: GATE-LEVEL SIMULATION VERSUS PROPOSED INSTRUC  | TION-    |

| DRIVEN ENERGY MODEL IN OVP                                                                            | 41       |

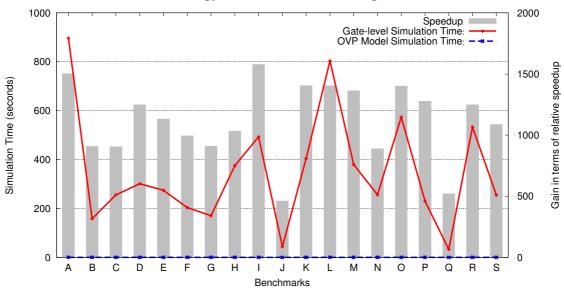

| FIGURE 6.10 - GAIN IN TERMS OF SPEEDUP: GATE-LEVEL SIMULATION VERSUS PROPOSED OVP ENERGY MODEL        | 41       |

| FIGURE 6.11 – PLATFORM WITH FOUR CLUSTERS USED IN THE EVALUATION                                      | 42       |

| FIGURE 6.12 – ENERGY COST OF THE THREE MAPPING HEURISTICS.                                            | 42       |

# LIST OF TABLES

| TABLE 2.1 - RELATED WORKS ON FULL-SYSTEM SIMULATION           | 14 |

|---------------------------------------------------------------|----|

| Table 2.2 - State-of-Art in instruction-driven energy models. | 17 |

| Table 4.1 - Energy groups profiled.                           | 27 |

| Table 6.1 - List of used benchmarks to cycle estimation.      | 34 |

| Table 6.2 - List of used benchmarks in energy estimation      | 40 |

#### LIST OF ABBREVIANTIONS AND ACRONYMS

API Application programming interface

BHM Behavioral Models

CPU Central processing unit

DBT Dynamic Binary Translation

GCC GNU Compiler Collection

GDB GNU Debugger

HPC High-performance computing

IBS International business strategy

ICM Innovative CPU Manager

ILP Instruction-level Parallelism

ISA Instruction Set Architecture

ISS Instruction set simulator

ITRS International Technology Roadmap for Semiconductors

JIT Just In Time

KIPS Thousand Instructions per Second

MIPS Million Instructions per Second

MPSoC Multiprocessor System-on-Chip

NoC Network on a chip

NOP No Operation

OS Operating System

OVP Open Virtual Platforms

OVPsim Open Virtual Platforms Simulator

PE Processing element

RTL Register-transfer level

TRM Technical Reference Model

UFRGS Universidade Federal do Rio Grande do Sul

WCET Worst-case execution time

# CONTENT

| RESU           | JMO                                                                      | 4  |

|----------------|--------------------------------------------------------------------------|----|

| <b>ABS</b> 1   | FRACT                                                                    | 6  |

|                | OF FIGURES                                                               |    |

|                | OF TABLES                                                                |    |

|                | OF ABBREVIANTIONS AND ACRONYMS                                           |    |

|                |                                                                          |    |

|                | ITRODUCTION                                                              |    |

| 1.1            | Outline of this thesis                                                   |    |

| 2 R            | ELATED WORK                                                              |    |

| 2.1            | Related work in Timing CPU models in JIT-based Simulators                |    |

| 2.2            | Timing CPU model in JIT-based Simulators - Closing Remarks               | 16 |

| 2.3            | Related work in Instruction-driven Energy Models in JIT-based Simulators | 16 |

| 2.4            | Instruction-driven Energy Models - Closing Remarks                       |    |

| 3 IN           | ISTRUCTION DRIVEN TIMING CPU MODEL                                       |    |

| 3.1            | Open Virtual platforms (OVP)                                             |    |

| 3.1.1          | Simulation Capability                                                    |    |

| 3.2            | Instruction-driven Timing CPU Model                                      |    |

| 3.3            | Timing Calibration Process                                               |    |

| 3.4            | Run-time based Approach                                                  |    |

| 3.4.1          | Disassembly and Parser (i)                                               |    |

| 3.4.2          | Hash table (ii)                                                          | 23 |

| 3.4.3          | Timing information computation (iii)                                     |    |

| 3.4.4          | Callback                                                                 |    |

| 3.5            | Simulation behavior                                                      |    |

|                | ISTRUCTION-DRIVEN ENERGY MODEL                                           |    |

| 4.1            | Characterization                                                         |    |

| 4.1.1          | Benchmark conception                                                     |    |

| 4.1.2          | Activity measurement                                                     |    |

| 4.1.3          | Power acquisition                                                        |    |

| 4.1.4          | Energy per group                                                         |    |

| 4.2            | Application Estimation                                                   |    |

| 4.3            | Simulation Behavior                                                      |    |

|                | HREAD EXTENSION                                                          |    |

| 5.1            | Modules modification                                                     |    |

| 5.2            | Buffer Management                                                        |    |

| 5.3            | Thread Management                                                        |    |

| 5.4            | Simulation behavior                                                      |    |

|                | XPERIMENTAL SETUP AND RESULTS                                            |    |

| 6.1            | Timing CPU model results                                                 |    |

| 6.1.1          | Timing CPU model - Experimental Setup                                    |    |

| 6.1.2          | Accuracy results and comparisons                                         |    |

| 6.1.3          | Scalability                                                              |    |

| 6.1.4          | Thread extension accuracy                                                |    |

| 6.1.5          | Thread extension speedup                                                 | 38 |

| 6.2            | ENERGY EXPERIMENTAL SETUP AND RESULTS                                    |    |

| 6.2.1<br>6.2.2 | Test Planning                                                            |    |

| 6.2.3          | Accuracy results and comparisons                                         |    |

| 6.2.4          | Relative speedup gain                                                    |    |

|                | Application to Large Scale Systems                                       |    |

|                | ONCLUSION                                                                |    |

| KEFE           | ERENCES                                                                  | 45 |

| <b>APPF</b>    | ENDIX A- TRABALHO DE CONCLUSÃO L                                         | 49 |

#### 1 INTRODUCTION

Many-core embedded systems are pointed to be the most viable solution to addressing emerging design constraints on cost, power and performance scalability [Borkar and Chien 2011]. Such embedded systems increase performance by scaling the number of cores, which vary in terms of structure, performance and energy-efficiency, to execute system application tasks. However, employing a large number of cores will be restricted by the so-called *power wall* [Bose 2013; Esmaeilzadeh et al. 2011; Zhang et al. 2013].

Under this scenario, a significant number of cores must remain inactive or in low-consumption state at some point in time, in order to preserve the system activity within the available energy budget. Further, important challenges inherent to the design of such systems are:

- *reliability*: the transistors reach the physical limits of operation, thus becomes increasingly difficult for the hardware components to achieve reliable operation [Papanikolaou et al. 2008];

- *energy efficiency*: in battery-driven devices, it is becoming more critical than high-speed operation, and dark silicon era is imposing more power-oriented constraints to the design of such systems [Miura et al. 2013];

- *programmability*: ease of programming is a feature of paramount importance in large-scale systems composed of different processors, resulting in different platform libraries (e.g. APIs), compilers, instruction set architecture (ISAs) [Marongiu and Benini 2012];

- *simulation*: To achieve efficient exploration of emerging many-core systems, the use of flexible and scalable simulators becomes mandatory. Such simulators should combine efficient modeling, debugging and simulation capabilities for verifying the both software and hardware development,

In addition to such challenges, software development becomes one of the major challenges in many-core system design. Software development comprises, among other: (i) inter- processor communication protocol stacks definition, (ii) operating system (OS) porting and analysis, (iii) exploration of better programming model facilities to address parallel programming [Marongiu and Benini 2012], (iv) drivers development [Gray and Audsley 2012], (v) application software portability for heterogeneous multiprocessing hardware.

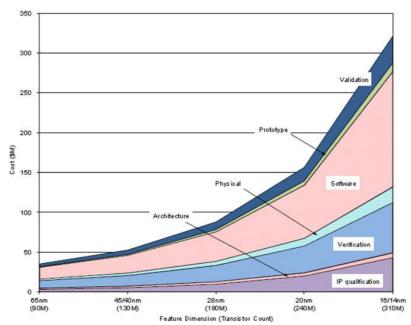

Such challenges make the software functional verification more difficult, resulting into increased development cost [Borkar 2007; Ceng et al. 2009]. IBS [IBS 2013] projects that software development consumes at least 50% of the system's design cost, and that percentage is rising, as illustrated in Figure 1.1. Developing and evaluating complex software stacks (OS, drivers, etc.), require fast and effective means for assessment of the performance-oriented and energy-efficiency practices. For instance, to assess the energy impact of software stacks, several software and hardware parameters must be tuned and evaluated properly, considering a large design space. With 200-core chips available in the market [MPPA 2014], the use of analytical models and prototyping boards is inadequate, especially for many-core architectures.

Figure 1.1 - Software and architectural design costs for embedded systems at advanced process technologies. Figure extracted from IBS 2013 [IBS 2013].

Analytical models undergo substantial development effort to identify behaviors that can be estimated by employing equations without compromising the model purpose. In turn, while specialized board designs produce accurate results, they require a substantial development effort to setup/port the software stacks. Further, physical boards can be expensive, with limited resources (e.g. number of CPUs, memory), as well as poor debuggability due the lack of internal observability and controllability of its components.

The resulting context leads to the adopting of virtual platform frameworks that are capable of simulating embedded systems running real application code at the speed of hundreds of MIPS [Imperas 2014]. While accelerating the software development, such simulators usually offer a set of CPU models and memory system models, allowing the analyses of executing different application/OSs onto multiprocessor architectures without modifications, which gives flexibility to explore more features at earlier design phase. Examples of such simulators are Simics [Magnusson et al. 2002], PTLsim [Yourst 2007], SimpleScalar [Austin et al. 2002], GEM5 [Binkert et al. 2011] and OVPSim [Imperas 2014]. Such simulators differ in terms of accuracy, simulation speed, as well as modeling and debugging support (e.g. GDB).

For example, event-driven and quasi-cycle accurate virtual platform frameworks like GEM5 target microarchitecture exploration since specific modeling details are provided (e.g. instruction pipeline details, cache coherence protocols, etc.). Such simulators are not scalable to a large number of CPUs, specifically when it comes to usability, ease-of-modeling and simulation time (around 200 KIPS [Sanchez and Kozyrakis 2013]). In contrast, simulators such as the Open Virtual Platforms (OVP) OVPsim that rely on just-in-time (JIT) dynamic binary translation can achieve simulation speeds of up to 100 MIPS. However, such simulation speed comes at the expense of accuracy; OVPsim provides instruction accuracy only, which results in inaccurate software performance estimation (e.g. application execution time).

The foregoing context provides the *motivation* for this Bachelor Thesis, which aims at making JIT-based simulators suitable for software performance and energy evaluation. The original *contribution* of this thesis is enhancing OVPSim capability by including energy and timing models, making it suitable for software performance and

energy analysis. With the underlying *contribution*, this Thesis advocates that software engineers can validate the functional behavior of the entire software stack executing it onto a given CPU architecture, using the original OVPSim. Then, software engineers may use the proposed OVPSim extension in a still reasonable simulation speed to investigate if target software stack can be executed according to the performance and energy requirements.

The contributions of the paper are summarized as follows:

- the implementation and integration of a quasi-cycle accurate timing model into OVPSim simulator;

- the extensive timing model evaluation by using several benchmarks, while comparing it to a real hardware platform;

- the development of a fast and accurate instruction-driven energy model;

- integration of proposed energy model into a NoC-based MPSoC platform;

# 1.1 Outline of this thesis

This work is organized in 7 chapters. Chapter 2 describes the state-of-the-art in timing and energy estimation models, taking into account approaches that are developed into JIT-based simulators. Additionally, a survey considering the most popular virtual platforms is also presented. Chapter 3 introduces the proposed run-time instruction-driven timing CPU model. After, Chapter 4 presents the development of a fast and accurate energy model. Chapter 5 contains a thread extension for the model in order to improve the simulation speed. In 6 the experimental setups and related results to timing and energy models were presented. Finishing with conclusion in the chapter 7.

#### 2 RELATED WORK

Due the different simulation speed/accuracy tradeoffs, it's difficult to cover all modeling (e.g. flexibility, debuggability) and simulation (e.g. accuracy, scalability) requirements into one single simulator. This Chapter starts by providing an extension of the survey proposed in [Butko et al. 2012], considering the most popular virtual platforms. Such virtual platform simulators, also called *full-system simulators*, are compared according to different criteria: (i) accuracy, (ii) flexibility in terms of supported processor architectures, (iii) licensing, and (iv) support activity. Table 2.1 summarizes the reviewed work according to the four criteria mentioned.

| Reference               | Simulator    | Accuracy                  | Supported processor architectures                            | License             | Active<br>support |

|-------------------------|--------------|---------------------------|--------------------------------------------------------------|---------------------|-------------------|

| [Magnusson et al. 2002] | Simics       | Functionally-<br>accurate | Alpha, ARM, MIPS,<br>PowerPC, SPARC, and<br>x86              | Private             | Yes               |

| [Yourst 2007]           | PTLsim       | Cycle-accurate            | X86                                                          | Open                | Yes               |

| [Austin et al. 2002]    | SimpleScalar | Cycle-accurate            | Alpha, ARM, PowerPC, and x86                                 | Open                | No                |

| [Binkert et al. 2011]   | GEM5         | Cycle-accurate            | Alpha, ARM, MIPS,<br>PowerPC, SPARC, and<br>x86              | Open                | Yes               |

| [Bellard 2005]          | QEMU         | Instruction-<br>accurate  | ARM, MicroBraze ,MIPS,<br>PowerPC, SPARC, x86,<br>and others | Open                | yes               |

| [Imperas 2014]          | OVPsim       | Instruction-<br>accurate  | Alpha, ARC, ARM, MIPS,<br>PowerPC, MicroBraze, and<br>others | Open and<br>Private | Yes               |

Table 2.1 - Related works on full-system simulation.

The Simulation Software Engineer (Simics) is simulator that enables unmodified target software (e.g. operating system, applications) to run onto a platform model similar to a real physical implementation. A wide range of processor architectures (e.g. ARM, MIPS, PowerPC), as well as operating systems (e.g. Linux, VxWorks, Solaris, FreeBSD, QNX, RTEMS), can be adopted to model the desired systems. This simulator includes SystemC interoperability, debuggers, software and hardware analysis views, as well. Simics has one main disadvantage, it is not claimed to be open source, and thus, commercial license is required by Wind River Systems.

In turn, PTLsim also supports simulation of different processor architectures [Yourst 2007]. PTLsim is a cycle accurate microprocessor simulator, thus the complete cache hierarchy, memory subsystem and supporting hardware devices are offered. PTLsim presents two main drawbacks; only x86 architectures are supported and the tool suite is not actively maintained anymore.

SimpleScalar [Austin et al. 2002] is an open source infrastructure for simulation and architectural modeling. As previous simulator, software engineers can use SimpleScalar to develop applications and execute them onto a range of processor architectures, which varies from simple unpipelined processors to detailed microarchitectures with multiple-level memory hierarchies. However, SimpleScalar is not actively maintained anymore (last update was in March 2011), and other faster solutions, like GEM5 are available.

GEM5 is a modular discrete event simulator, which is open-source and supports

a rich set of ISAs [Binkert et al. 2011 p. 5]. Moreover, this simulator has an active development and support team. As mentioned before, GEM5 target microarchitecture exploration, which incurs in huge simulation overheads due the number of modeled aspects. Further, the amount of memory required by these approaches is too high, making their use infeasible when exploring a large design space exploration.

QEMU [Bellard 2005] is an open source and a functional simulator that relies on dynamic binary translation. QEMU can be used to simulate several CPUs (e.g. x86, PowerPC, ARM, and Sparc). Nevertheless, QEMU is designed to single-processor platforms and virtualization purposes. Thus the lack of documentation on the APIs or standardized methodology for creating many-core platform models limits its use.

Excluding PTLSim that only supports x86, reviewed simulators are composed of several processor architectures. Quasi clock accurate simulators such as SimpleScalar and GEM5 entail high-simulation time, thereby limiting its applicability to the exploration of large many-core systems. Further, while Simics has a private license. Further, SimpleScalar does not provide support or development anymore.

OVPsim supports the larger number of processor architectures (ISAs) among reviewed simulators. OVP supports dozens of architectures (e.g. MIPS, ARM, x86, PowerPC) ramifying in several model variants (e.g. arm cortex-A5, cortex-A9, cortex-M4F, etc.), as well peripherals (e.g. DMAs, TIMERs), and integration with System-C modules. Besides, of supplied models, the user is able to create customized models easily integrated with the platform, justifying our choice.

As mentioned before, the lack of accuracy inherent to JIT-based simulators is motivating research in alternatives performance / accuracy tradeoffs. The next Section presents approaches that are instrumenting JIT-based simulators with timing models. In this context, instructions, basic architecture block models and their inter-operations (e.g. read and write) are calibrated according to a reference platform. Thus, software performance evaluation can be estimated by, for instance, summing up the annotated timing numbers along execution of given application.

# 2.1 Related work in Timing CPU models in JIT-based Simulators

Chiang et al. [Chiang et al. 2011] utilize the integration of QEMU and SystemC in order to allow faster clock-accurate evaluation when compared to RTL-based. Attaching a SystemC co-processor in the simulator framework, using the information extracted from the DBT interface. This approach reduces the simulation speed of QEMU, capable to reached approximate 38 MIPS, to approximate near 0.46 MIPS using the full simulation with SystemC. A pipeline model was included into QEMU in [Thach et al. 2012], where the authors proposed a two-phase approach an offline and an online phase to estimate the application performance. In the offline phase, a cycle pre-estimation of the application execution time is performed. Using the computed information at dynamic adaption phase when CPU status and execution time of critical instructions are also taken in account, improving the approach accuracy presenting a mismatch around 10%.

A similar approach is presented in [Stattelmann et al. 2012], where worst-case execution time (WCET) analysis and QEMU are combined for a LEON3 processor. In this work, the offline phase is composed by four steps, which produce a timing database that is used during the QEMU simulation. The proposed work in [Bohm et al. 2010] modified an ARC instruction set simulator based on JIT DBT to improve the simulation accuracy. A complex pipeline and execution state models were constructed direct in the DBT framework, taking advantage from the direct access of JIT Translation block.

# 2.2 Timing CPU model in JIT-based Simulators - Closing Remarks

Making an overview of the reviewed researches, it is noticeable that QEMU is largely employed due its free GNU licensing. It is possible to verify that almost all related approaches are based on a reconstruct pipeline model that update its internal state according to executed instructions during the simulation. There are different abstraction levels of implementations and consequently, the necessary amount of data information considered before and during the simulation. Complex models may implement several abstract queues, internal pipeline state, etc.

The drawback of the approach proposed in [Stattelmann et al. 2012], is the prior application profiling phase, which restricts its use when exploring large scenarios composed of diverse applications. Another disadvantage of this work is that any software modification (e.g. changing the OS scheduling algorithm) implies in rerunning offline phases.

Different from the reviewed work, the proposed approach (described in section 3.4) relies on OVP and run-time basis, eliminating huge trace files, as well as pre- or post-processing software/application profiling. Despite the low-memory usage, the proposed approach can be easily configured to observe as many CPUs as desired. Another contribution of the proposed timing CPU model, when compared to the reviewed works, is the easy portability to other CPU architectures.

# 2.3 Related work in Instruction-driven Energy Models in JIT-based Simulators

In the case of prototyping boards, the power information is captured from a precision resistor positioned between the power supply and the power input pin [Bazzaz et al. 2013; Konstantakos et al. 2008; Lee et al. 2001; Nikolaidis et al. 2003]. The use of physical information can aggregate precision to the high-level models (error varying from 2.5% to 7% as presented in the third column of Table I). However, to measure the power of each instruction, additional and expensive hardware (e.g. high-performance oscilloscopes) are required. Another drawback of this approach is the difficulty of accessing/isolating individual modules inside the processor due to internal structure and connections (e.g. Flash, Rom, SPI, AD, and DC).

In simulated-based techniques, the required information is extracted from low-level simulators (e.g. SPICE, gate-level), in which a hardware description is used to execute input benchmark applications and to profile the power of each instruction. For example, in [Abril Garcia et al. 2002] an instruction set simulator (ISS) is enriched with an energy model based on the mean switching activity of the processor, which is modeled by two states, *active* and *NOP*. A similar approach is presented in [Sultan and Masud 2009], which considers the average switching activity of an LEON3 processor simulated at RTL level. In this work, the power is computed according to the number of transitions generated in response to a certain instruction that is fetched from BootROM of LEON3.

Authors in [Castillo et al. 2007] propose obtaining energy values directly from the analysis of the source-code without requiring simulation or even compilation. A further higher-level approach is proposed in [Callou et al. 2011], in which the source-code is converted in a Colored Petri net model, which is used to estimate the energy cost of a given application.

Table 2.2 - State-of-Art in instruction-driven energy models.

| Reference                     | Reference<br>model                                         | Claimed<br>Accuracy                                                      | Benchmark suite                                                                | Description                                                                                                                                                                                                                                                                  |

|-------------------------------|------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [Lee et al. 2001]             | ARM7TDMI                                                   | Average 2,5% and worst case 6,33%                                        | 36 randomly-<br>generated<br>instructions                                      | Model based in a linear regression analysis.                                                                                                                                                                                                                                 |

| [Abril Garcia et al. 2002]    | Gate-level<br>estimation using<br>an ARM920                | Not available                                                            | MPEG-4 video<br>decoder                                                        | Inclusion of a power model calibrated in gate-level activity in a System-level Cycle-Accurate simulator                                                                                                                                                                      |

| [Kalla et al.<br>2003]        | Synthesizable<br>RTL of a<br>SPARC                         | Energy less than<br>5% and per-<br>cycle power<br>inside 15% of<br>error | Bubble Sort, Heap<br>Sort, Insertion Sort,<br>Key 3 and 3D image<br>processing | Model based in Active and Stall consumption for each module of the architecture, refined with inter-instruction effect. Additionally provides the maximum and the minimum of power.                                                                                          |

| [Nikolaidis et al. 2003]      | ARM7TDMI                                                   | 5%                                                                       | A few instructions                                                             | Abstract model for pipeline with static, inter-instruction, and pipeline power.                                                                                                                                                                                              |

| [Konstantakos<br>et al. 2008] | Motorola<br>HC908GP32                                      | Not available                                                            | Not available                                                                  | The instructions are divided into groups by the cycle's length.                                                                                                                                                                                                              |

| [Lee et al. 2006]             | Gate-level<br>estimation for<br>M32R-II and<br>SH3-DSP     | Average 3% and worst case 16%                                            | JPEG and MPEG2<br>encoders, compress,<br>FFT and DCT                           | Training benchmarks are used in conjunction with a gate-level simulator and linear optimization to generate several parameters to describe frames of instructions. Afterward this parameters are utilize together with ISS.                                                  |

| [Castillo et al. 2007]        | Arm ISS, arm-<br>elf-gdb, for a<br>ARM9TDMI<br>and ARM TRM | Less than 11%                                                            | Bubble Sort, FIR,<br>Array, Fibonacci<br>and Quicksort                         | An online analysis of the source-code without requiring simulation or even compilation. Based in the mean energy per instruction calculated from values provide by ARM Manual. Detailed study about the operators in C e.g. + = >> and their costs in meter of instructions. |

| [Sultan and<br>Masud 2009]    | Synthesizable<br>RTL of a<br>LEON3                         | Not available                                                            | Not available                                                                  | Propose of an instruction level power model profiling each instruction in different stages of a pipelined processor. The aim is to measure the activity generate in the processor and taking in count the capacitance to calculate the power.                                |

| [Callou et al. 2011]          | NXP LPC2106<br>with an<br>ARM7TDMI-S                       | 7% in average                                                            | 5 applications                                                                 | Stochastic approach based on Coloured<br>Petri nets and source code analysis                                                                                                                                                                                                 |

| [Bazzaz et al. 2013]          | AT91                                                       | Less than 6%                                                             | 8 MiBench<br>benchmark                                                         | ISS Model calibrated from real measures.<br>Complete model with static, inter-<br>instruction, and pipeline power.                                                                                                                                                           |

| Proposed<br>approach<br>2014  | Gate-level<br>estimation                                   | Between 0,06% and 8%                                                     | 19 benchmarks from<br>WCET and in-house<br>applications                        | Instruction-driven model calibrated from<br>the switching activity of the processor<br>internal components. Run-time model<br>developed on the basis of OVP API that<br>monitors the instructions executed by a<br>given CPU.                                                |

# 2.4 Instruction-driven Energy Models - Closing Remarks

Reviewed approaches focus on creating instruction-driven models, which compute energy/power values by observing the sequence of executed instructions. One difference between such approaches is the calibration process. For instance, in [Bazzaz et al. 2013] authors evaluate instructions individually to feed the instruction-driven model, while in [Lee et al. 2001] fixed length instruction groups are used. Authors argue that different transition scenarios may significantly affect the energy estimation. For that reason, some works such as [Bazzaz et al. 2013; Kalla et al. 2003; Nikolaidis et al. 2003] also calculate the inter-instruction energy, i.e. the energy required to switch from one to another.

Another distinction lies in the energy evaluation process. For instance, the approach proposed in [Castillo et al. 2007], differs from the other works in the sense that it translates the source code in an intermediary code representation, which is used to estimate the application energy consumption. This approach does not require simulation that may decrease the energy evaluation effort. However, to predict the behavior of loop and branches only by code inspection is not a trivial task that may pose other design/evaluation challenges.

Our contribution distinguishes from previous works by enhancing the OVPSim (JIT-based simulator) with energy evaluation capability allowing faster and accurate exploration of energy-efficiency software development. Contrary to the most of reviewed approaches, our approaches cover both timing and energy evaluations. Another advantage of our approach is that once calibrated whatever OS/application can be ported, modified, and its timing and energy-efficiency can be evaluated without any code modification or re-calibration phase. To accomplish these features, a common foundation for monitoring at run-time the instructions executed by each CPU, while presenting the system functionality was developed. This foundation is described in the next Chapter.

#### 3 INSTRUCTION DRIVEN TIMING CPU MODEL

This Chapter describes the proposed timing CPU model in OVP. The following Section presents the basic concepts and features related to OVP.

# 3.1 Open Virtual platforms (OVP)

Open Virtual platforms is a simulation framework marketed Imperas [Imperas 2014]. OVP is composed of three main components: (*i*) APIs that enable modeling in C/C++ hardware components, (*ii*) library with a large number of CPU architectures, peripheral, memory, and sub-system models, and (*iii*) the OVPsim simulator.

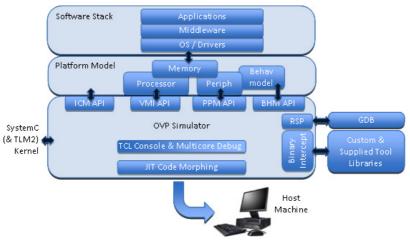

As illustrated in Figure 3.1, OVPsim employs a Just-In-Time Code Morphing binary translation simulator engine that dynamically translates target instructions to the host machine instructions. In this context, OVPSim is capable to handle virtual memory simulation with minimal performance penalty. OVPsim also supports non-intrusive semihosting using dynamically loaded libraries that are completely separate to processor models. As defined in [Davidmann and Graham 2014], there is no need to compile application code using special flags to support semihosting: given an appropriate semihost library, OVPsim can run unmodified binary. OVPsim semihosting works by allowing semihosting libraries to take special actions either when particular functions are executed in the simulated application (e.g. write) or when particular instructions are executed (e.g. break instructions).

Figure 3.1 - OVP Virtual Platform Simulation Interfaces. Figure extracted from [Davidmann and Graham 2014].

OVPsim has been developed for the maximum simulation throughput and includes several optimizations enabling simulation of platforms utilizing many homogeneous and heterogeneous processors with many complex memory hierarchies. Also includes several models of MMUs, caches, and TLBs.OVP framework features four API: Innovative CPU Manager (ICM), Virtual Machine Interface (VMI), Behavioral Hardware Modeling (BHM), and Peripheral Programming Mode (PPM). Each of which has a specific purpose, for instance the ICM is intended to create and to simulate the target platform, including any number of processor, busses, memories and peripherals models. Busses, memories and processors can be interconnected in arbitrary topologies and arbitrary multiprocessor shared memory configurations. Further, ICM functions also encapsulate OVPsim models in SystemC or TLM 2.0 simulations. OVP models also include processors and peripherals wrappers for use with SystemC TLM2.0. The ICM is responsible for merging all four APIs in a single environment

providing interoperability between then. OVPSim platform is composed of one C file containing few lines of code compiled with Imperas libraries to create an executable file.

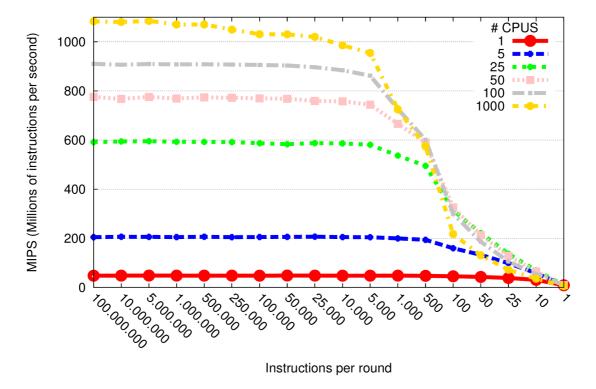

# 3.1.1 Simulation Capability

In order to support multi-core simulations, OVPsim implements a Round-Robin scheduling algorithm similar to a typical used in OS schedulers. Thus, each processor entity (PE) has a time slice variable, typically 0.001 seconds. Note that it is possible to define a common time slice for all processors of a given scenario. Such variable is converted into a number of instructions that should be executed by each processor in the defined time slice. The number of simulated instructions is obtained multiplying the time slice by the processor nominal MIPS, which is defined 100 per default. OVPSim works in sequential way (i.e. simulating a unique processor at time, even if the simulator is hosted in a multi-core host machine). Nevertheless, this algorithm inserts an issue related to the synchronization between simultaneous events related to different processors. For instance, if a processor sends a message to another in the middle of their time slices, the receiver only will be aware of the message at the begin of his time slice. In simulation scenarios tightly based in intercommunications between processor (e.g. NoC-based MPSoC), the precision of results may be affected.

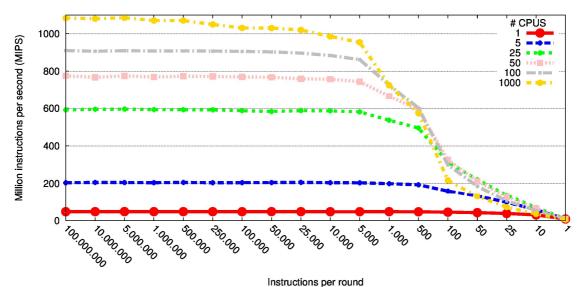

A possible solution could be resizing the time slice, decreasing the number of instruction executed each time by the each processor. In order to observe this behavior a series of experiments was conducted, using the same application (FFT), varying the time slice from 1 to 0.000001 and the instructions per window from 1.000.000 to 1. Figure 3.2 shows the degradation in terms of simulation speed vs. time slice. It can be observed that the simulation slows down dramatically when less than 5 thousand instructions per round are executed. Notwithstanding, the modification impacts in the performance obtain by the simulator due the cost in the context switch between the processors.

Figure 3.2- Scalability of Time Slice.

# 3.2 Instruction-driven Timing CPU Model

This Section describes the development and the integration of the proposed timing CPU model into OVPSim. As mentioned before, our timing CPU model relies on monitoring at run-time the instructions executed by a target CPU. The proposed approach requires an instruction set profile as mean to determine cycle count (timing information), which can be captured from datasheet, physical boards, low-level simulation, etc. In order to diminish development complexity, we propose to combine instructions in groups according timing costs similarity. Separating ISA in classes and groups according different timing behaviors and other representing constant one-cycle instructions. While simulating, unless the model identifies an instruction as belonging to one of defined groups, it is considered as one-cycle instruction. In order to demonstrate the timing calibration process, let's consider the Cortex-M4F ISA as study case.

#### 3.3 Timing Calibration Process

Timing Behavior of ARMv7-M Thumb instruction set implantation in Cortex-M4F can be grouped according their similarities, for instance, almost all logical and arithmetic instructions are single cycle. Notwithstanding, division has a dependable cycle count imposed by the early termination accelerator based on the number of leading ones and zeroes in the input operands. In this case, one division can take from 2 to 12 cycles.

While not taken branch instruction execution requires a single cycle, taken breaches lead to 3 cycles as result of pipeline flushing. Semaphore cycle count is usually two, and for *push* and *pop* the exact cycle count relies on the number of registers in the register list, increasing in one cycle per register. Additionally, instructions that use PC as destination register have three cycle's penalty.

In the case of load and store, the timing analysis is the most complex one. Load and store are normally two cycle's instructions, as result of neighboring load and store. Single instructions may pipeline their address and data phases affecting cycle's count, leading to one cycle's instructions. The instructions are pipelined when the next instruction is an *LDR* or *STR*, and the destination of the first is not used to compute the address for the next instruction, then one cycle is removed from the cost of the next instruction (e.g. *LDR R0,[R1,R5]; LDR R1,[R2]; LDR R2,[R3,#4]* - normally four cycles total instead six). Further, other environmental factors that could modify the cycle count can be found in the TRM [ARM 2013]. This document has important timing information, which are fundamental to the proposed timing model. Nevertheless, the document not exposes detailed information concerning timing behavior. In order to verify the collected timing information, several experiments were conducted using the platform [STM32F4 2014], considering the interleaving between instructions, as load and stores.

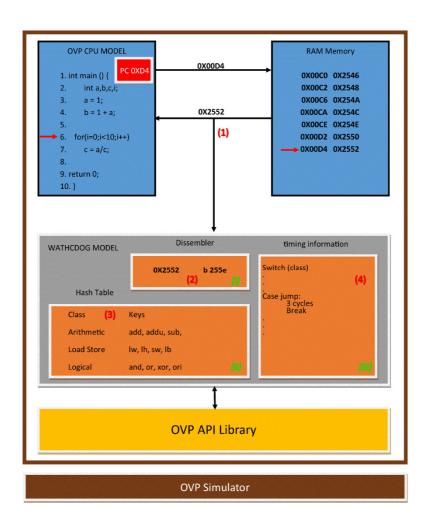

# 3.4 Run-time based Approach

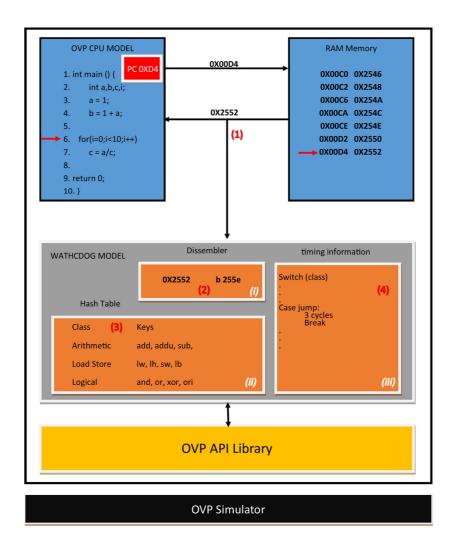

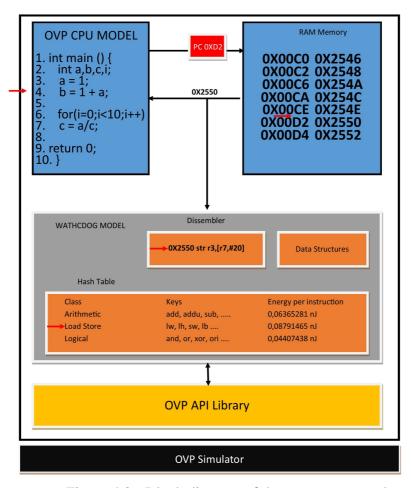

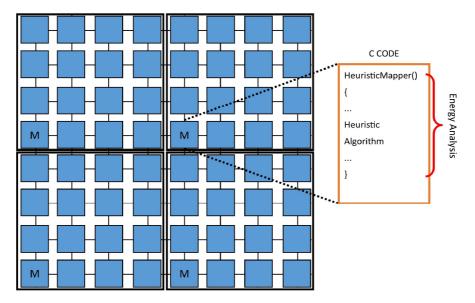

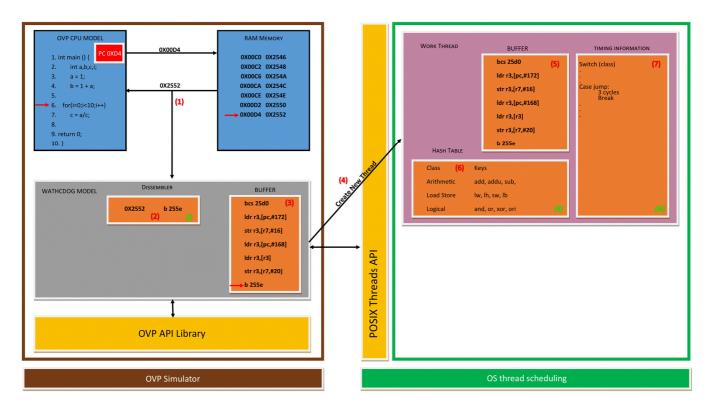

The monitoring process was developed on the basis of OVP APIs and integrated in a component called Watchdog, comprising three main modules: (*i*) disassembly and parser, (*ii*) a hash table containing pre-characterized groups of instruction, and (*iii*) timing information computation, in the Figure 3.3 and descripted in sections 3.4.1, 3.4.2, and 3.4.3.

Figure 3.3 - Block diagram and the main flow of the run-time based approach.

#### 3.4.1 Disassembly and Parser (i)

In this module, an instruction binary code is disassembled into a string and afterwards subdivided in other substrings. The purpose is to isolate the instruction mnemonic from the instruction registers arguments to feed both hash table (ii) and timing computation module (iii). As a means to disassemble binary code instructions, our implementation employs a function provide in the ICM API called icmDisassemble. This function call disassembles an arbitrary memory position for an arbitrary CPU instance at any moment of the simulation. The function arguments are the CPU model object and the target memory address. This function returns a string containing the address, the mnemonic, and the arguments of the disassembled instruction (e.g. 0X2550 STR r3, [r7, #20]).

In *icmDisassemble* function is important to note issues related to concurrent access, consequently this calls are necessary exclusive, cause by internal buffers when storing partial results. The model describes in this chapter is sequential, i.e. the instructions are guaranteed to be exclusively resulting in mutual exclusion for all access. Nevertheless, with the purpose of increase simulation speed was developed a POSIX Thread version. As a consequence, concurrent access is possible, necessitating assure mutual exclusion, subsequently, is necessary to parse the string, separating in different sub-strings in order to correctly update internal structures and supply the next module.

# **3.4.2** Hash table (*ii*)

With the purpose of efficiently store the timing information, it was employed a hash table, instructions mnemonic are the key for the data, which relates the instruction group and the key. Thus, in a single access, using the mnemonic as key is possible retrieve the information for the timing computation. The hash table is created and initialized at simulation begin, inserting all mnemonic in the hash.

In the early model version was not used a hash table, instead a linked list due the implementation simplicity. Occasionally, was noticeable this storage access as performance bottleneck during simulation. As result of our methodology, every executed instruction is processed sequentially after the fetch event; consequently an access is performed after each fetch. Therefore, the search in linked list is not scalable and do not have a fixed time cost, leading to performance loss. In order to overcome this situation, a hash table replaces the linked list as storage solution in newer version.

# 3.4.3 Timing information computation (iii)

This module is responsible for processing information provide by previous modules together with processor state information. Structured as switch, using returned value from the hash table as a selector variable. A null pointer signifies a single-cycle instruction, accordingly to our methodology when assume one cycle per default. Estimate cycle's count requires several chained tasks, separate in two groups: Those performed to every group and those restricted to individual group. For instance, all instructions possessing registers list requires several verifications: Instructions modifying the program counter need to be identified, as well inline shifters.

Each profile class requires a specific treatment after been identified. For instance, at any time a load occurs it is necessary verify if the precedent instruction was a store or load, the same for stores. To implement this verification, a buffer of one instruction is maintained during the simulation and verify when is necessary. In instructs as *pop* or *push* requires count the number of registers contained in the register list of the instruction, each one adds one cycle to cycle count. To correct estimate division cycles is necessary acquire the two operands, verifying the number of leading zeros in the operands. According to the number of zeros, the cycle count is estimated.

#### 3.4.4 Callback

The monitoring process bases in a special function supply by the ICM API called Callback. Triggering when a predefined particular event occurs, and subsequently the simulator call a handler function provided by the designer. Trigger configuration events, as memory access or as bus access, take place at compilation-time. Additionally allowing restrict this event a memory range instead entire address space. Restricting address range impacts in the simulation speed as a result of the algorithm employed by the simulator.

Callaback instantiation requires two steps, shows in Figure 3.4. First, an ICM function (i.e. icmAddFetchCallback) (a) located in the platform creator inserts callback trigger. This specific function adds a fetch event trigger. Handler function construct as ICM specific wrapper (b) perform any task desire. Is important note that simulation stops during callback treatment and handler execution.

Figure 3.4 - Callback example code.

#### 3.5 Simulation behavior

As propriety of OVPsim all processor, busses, and memory are created at runtime using linked libraries. The same process is applied to our Watchdog module and its internal components. Also is possible define different constraint to the model, as an CPU instance that will be monitored. Figure 3.3 shows a block diagram of the watchdog associated with the platform. Numbers from 1 to 4 are used to describe the model behavior.

After the platform simulation begins, whenever an instruction is fetched from the memory (1) is triggered a callback, thus starting the Watchdog. Inside the first module, the binary code of the instruction is acquired using the program counter (PC) register. Thus, the binary code is disassembled, divided into sub-strings, and identifies the instruction that must be executed (2). The identified instruction is employed as a hash table key to discovering which class (e.g. arithmetic, load, store) such instruction belongs (3). Thus, computing the necessary number of cycles to perform this instruction, considering the predefined timing information. Once, computed the cycle count, each instruction is executed in the CPU (4). At simulation end is possible retrieve the cycle estimation separated by CPUs, additionally, the statistics concerning the number of executed instruction per mnemonic.

Our methodology can be extended and applied to other simulator frameworks. Nevertheless, to achieve better simulation performance, the development demonstrated in section 3.4 takes full advantage of OVP functions and methods. Additionally, as result of the OVP APIs extensive use diminishes developing time and cost, improving productivity.

The proposed methodology lies in a single-event model, based on the individually executed instruction, simplifying construction around the simulator. Capturing as an event, identifying the instruction, processing properly, and storing the computation. The proposed approach in this thesis is a purely run-time based, i.e., full computation is executed concomitantly with the simulation, avoiding a huge amount of memory usages needed by trace-driven based approaches and maintaining scalability, as well as pre- or post-processing software/application profiling.

#### 4 INSTRUCTION-DRIVEN ENERGY MODEL

Proven the flexibility of previous timing model, in this chapter, is introduced an instruction-level energy estimation model. It is important to highlight that the proposed profiling method is simple and transparent, applicable in any other processor cores with no considerable rework.

The Proposed energy model maintains a methodology presented in chapter 3 to timing estimation. Focusing in a single-event model, based in the individually executed instruction, simplifying construction around the simulator. Capturing as an event, identifying the instruction, processing properly, and storing the computation.

However, in the first case, almost information about cycle duration was available in the documentation, for this energy approach, the manufacturer does not offer the information about energy consumption. In order to overcome this problem is necessary acquire information through a calibration phase. As a result, dividing the process flow in two: a Characterization phase and the simulation phase.

#### 4.1 Characterization

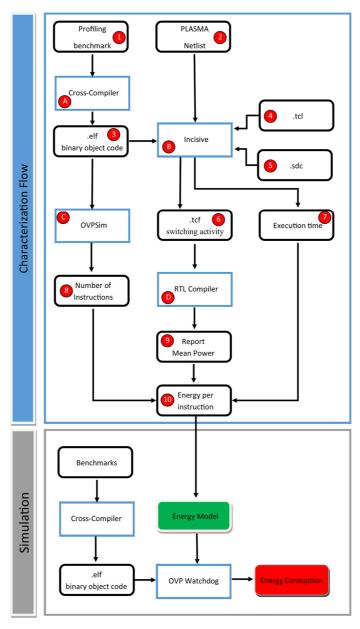

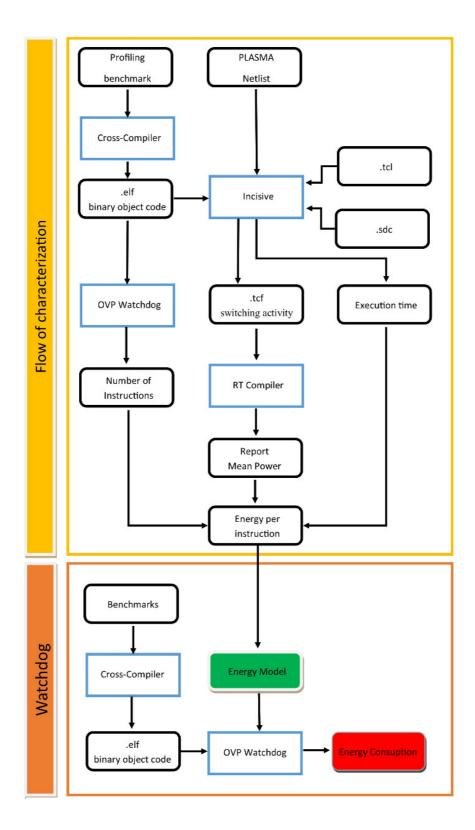

The first and most important phase is the characterization, which profiles the energy spent by each instruction belong with the target ISA. The proposed characterization flow is validated taking as reference the Plasma processor [Plasma 2014], a 32-bit RISC processor based in the MIPS architecture with a 3-stage pipeline. The characterization flow is executed once per ISA architecture, and it comprises four main steps: (i) benchmark development; (ii) activity measurement; (iii) power acquisition; (iv) energy computation. In Figure 4.1, the numbers from 1 to 10 are used to describe intermediary files, while the letters from A to D represent the adopted tools.

# 4.1.1 Benchmark conception

The first step of the characterization flow encompasses developing the benchmarks that will be used to profile the energy consumption for each instruction (1 in Figure 4.1). To reduce the computation cost of our model, we classified the instructions in seven groups due their behavior in the processor data-path: (i) arithmetic, (ii) logical, (iii) move, (iv) branches, (v) load/store, (vi) nops, and (vii) shifts. One practical example is the close relationship between instructions such as *add* and *addiu* or between *lw* and *sw*. Note that the mnemonic *move* is considered in this work as arithmetic instruction through a pseudo-instruction implementation (performed by a *lui* and *ori*).

To profile the energy consumption of each instruction group (1 in Figure 4.1), an application was carefully developed, in a way, that at least 90% of the executed instructions would belong with the target group, including the possible variations of the same instruction (e.g. *add*, *addi*, *addiu*, etc.). Previous experiments using higher percentages (e.g. 95%), showed a negligible difference. Note that multiplication and division instructions are modeled as 12 arithmetic instructions each, since our Plasma version takes 12 cycles to execute them. Further, an application benchmark was created to characterize the pipeline stall as a *nop* instruction.

Each application is executed in the OVPSim simulator (C in Figure 4.1) to verify its correctness and to extract the exact number of executed instructions (8 in Figure 4.1). Each application executes, in average, 35 thousand instructions, which requires less than one 1 second of simulation. The Plasma is synthesized with Cadence RTL Compiler tool (2 in Figure 4.1) targeting a 65nm low-power library from ST Microelectronics. Then, each application is simulated using Cadence Incisive simulation tool (B), taken as inputs: the Plasma netlist (2), the application object code (3), a tcl script (4), and the sdc file containing the timing constraints (5). The simulating is

executed until the end of the application.

Figure 4.1 - Proposed instruction-driven evaluation flow

# 4.1.2 Activity measurement

Each application is simulated using Cadence Incisive simulation tool (B in Figure 4.1), taken as inputs: the Plasma netlist (2 in Figure 4.1), the application object code (3), a *tcl* script (4), and the *sdc* file containing the timing constraints (5). The simulating is executed until the end of the application. As a result, a *tcf* file (6) is generated. This file contains statistic information about the switching activity of each cell and wire in the netlist. In addition, the exact execution time of each application is collected (7).

# 4.1.3 Power acquisition

Finally, the power evaluation is executed. Cadence RTL Compiler (D Figure 4.1) also performs this task; the tool reads the netlist (2 Figure 4.1) and computes de average power consumed by each cell based in their switching activity information in the tcf (6) file. Subsequently, the tool produces a report containing the average power consumption (9) for the application.

# 4.1.4 Energy per group

The final step computes the average energy spent by each characterized group (10 in Figure 4.1). Associating the average power (9) and execution time (7) collected in the previous step with the number of instructions (8), the energy consumed per instruction group is obtained using Equation 4.1. This flow is repeated for each instruction class.

Equation 4.1 - Formula to calculate the energy spend by each group.

Average energy =

$$\frac{\text{execution time}(\mu s) \times \text{power}(mw)}{\text{executed instructions}}(nJ)$$

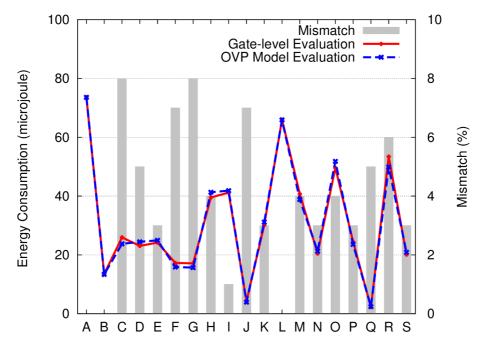

Table 4.1. Summarizes the energy results for each instruction group. Results in the column "number of instructions" are obtained through the OVPSim simulation. Results in the columns "power" and "execution time" are obtained through the gate level simulation. The total energy consumption ("energy" column) is obtained by multiplying the number of instructions by the total execution time. Then, with the number of executed instructions and the total energy consumed, it is possible to compute the energy consumed by each instruction ("Energy per Inst." column).

| Groups     | Power (mW) | Exec Time (us) | Energy (nJ) | # of inst | Energy per Inst (nJ) |

|------------|------------|----------------|-------------|-----------|----------------------|

| Arithmetic | 6,456      | 342,755        | 2212,826    | 34764     | 0,0636528098         |

| Jump       | 6,046      | 102,600        | 620,320     | 10224     | 0,0606728873         |

| Load-Store | 4,094      | 1042,800       | 4269,223    | 48561     | 0,0879146476         |

| Logical    | 4,469      | 349,735        | 1562,966    | 35462     | 0,0440743815         |

| Move       | 3,129      | 480,725        | 1504,189    | 39363     | 0,0382132593         |

| NOP        | 2,141      | 257,155        | 550,569     | 26130     | 0,0210703733         |

| Shift      | 3,824      | 298,735        | 1142,363    | 30362     | 0,0376247494         |

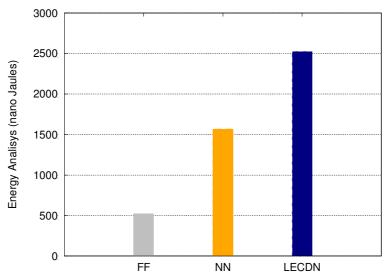

Table 4.1 - Energy groups profiled.

#### **4.2** Application Estimation

After the characterization phase is finished, the next phase comprises building the energy model in the instruction-set simulator. Developing the monitoring process by modifying the previous cycle estimation model presented in the section 3.4, extending and enriching with energy models. Figure 4.2 shows the three main Watchdog modules: (i) disassembler, (ii) a hash table with pre-characterized groups of instructions, and (iii) internal data structures. In energy model, the hash-table contains the belonging class (e.g. arithmetic, load, store) to each instruction mnemonic (e.g. add, or, lw, etc.).

#### 4.3 Simulation Behavior

During the simulation, whenever an instruction is fetched from the memory (1) is triggered a callback, thus activating the Watchdog. Inside the first module, the binary code of the instructions is acquired using the program counter (PC) register, thus the binary code is disassembled, divided into sub-strings, and identifies the instruction that must be executed (2). The identified instruction is employed as a hash table key to discovery which class (e.g. arithmetic, load, logical) such instruction belongs (3). Thus, computing the necessary energy to perform this instruction, considering the predefined energy information. Once, storage the information, each instruction is executed in the CPU (4). At simulation ends is possible retrieve the cycle estimation separated by CPUs, additionally, the statics concerning the number of executed instruction per mnemonic or grouped by class.

Figure 4.2 - Block diagram of the energy approach.

#### 5 THREAD EXTENSION

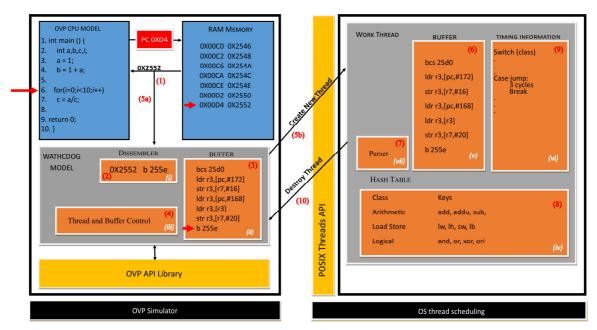

In order to improve the simulation speed of proposed timing and energy models, a thread-based implementation (i.e. POSIX Thread library) is proposed. We select POSIX Thread due its portability to multiple host machines in different operation systems (i.e. Windows and Linux), its availability in standard compilers as GCC, and its low footprint. The model describes in chapter 3 will be further referred as *sequential* version while be named *thread-based*.

Proposed extension maintains a methodology presented in the previous chapter, based in individually executed instruction, every fetched instruction is disassembled, parsed, identified, and processed. The sequential version accomplishes all tasks in the interval between two fetches producing speed degradation. In this context, every task inserted in the model causes significant computation, preventing the addition of more complex features. However, is impossible to parallelize the entire model to achieve better workload distribution. This extension proposes divide cycle estimation in two phases: a concomitant and parallel. The first occurs in the fetch event treatment (i.e. the callback), and the other is asynchrony using the OVPsim natural flow as referential. Figure 5.1 shows the thread-based version block diagram. The propose extension aim transfer as much as possible workload to parallel phase, introducing a buffer between concomitant and parallel phases in order to accumulate information before processing. Note, this buffer differs of other works exist a post-processing moment, in this proposed model the buffer consumption is concurrent with the simulation. Described in section 5.2.

The concomitant phase is responsible to intercept instructions, binary code disassemble, buffer management, and thread creation. Instruction trace is mandatory belong to this phase, is impossible create a satisfactory trace using functions asynchronous to OVP CPU model in the adopted framework. Consequentially is necessary store the trace in a temporary buffer, adding buffer management cost to this phase. Binary code disassemble theoretically is compulsory in the concomitant phase, nevertheless, while development was discovered a problems related to icmDisassemble function presented in section 3.4.1. Thus, was necessary maintain disassembly and consequently the buffer was redesign to contain a string (32 bytes) instead 32 bits operation code increasing memory consumption. However, the proposed approach has a smart buffer management in order to reduce memory footprint during execution.

# 5.1 Modules modification

Insertion of explicit parallelism certainly increases model complexity, as so, creating other and modifying previous modules presented in sections 3.4.1, 3.4.2, and 3.4.3. Figure 5.1 shows the module in roman algorisms (from i to vi). Disassembly and Parser module are organized in two modulus, (i) and (vii) respectively. Comprising sequential phase, disassembly module (i) utilize icmDisassemble function, generating a string. Buffer module (ii) is responsible to storage the generate strings to posterior processing. Buffer implementation follows a queue data type, i.e. making bottom insertions and top removals. Module (iii) manages both buffer and thread. Buffers creation is on demand (i.e. they are dynamic created when certain conditions are satisfied and detailed in the next section). In thread side, the buffer (v) module sources the string in the same order they are stored. Timing computation (vi) is almost identical with the sequential version. Differing only by the division cycle counting due unavailability of operands, required to calculate early termination algorithm. Hash table (iv) was not modified. Parser module (vii) process the string arising from the buffer, supplying sub-string to module (iv) and (vi).

# **5.2** Buffer Management

The proposed extension requires a buffer as provisory trace storage as means to separate timing estimation in two phases. In order to preserve scalability, focusing many-core systems, is impossible maintain a static buffer as previous discussed. We propose take benefit of compartmentalized OVPsim nature (see section 3.1), using time-slice switching as size referential and as trigger event. A buffer receives instructions arriving from one processor until the OVP scheduler switch its model, per default at each 100K instructions. At this moment, an event creates a thread and passes buffer pointer as an argument. Therefore, through one model is simulated other threads can profit from host processor parallelism.

The time-slice event is triggered even when the platform simulates only one CPU. Nevertheless, this event is configurable, enabling insert an index trigger, besides time-slice transitions is possible provoke thread creation during the time-slice of a processor. For instance, if the CPU is configured with a 10K instructions index in a 100K time-slice, will be generated 10-work threads during each simulate time-slice for this CPU with the processing beginning immediately after thread creation. As a result, workload is separate in more threads although several tests not demonstrate a measurable gain.

Buffer allocation occurs when a processor try store an instruction and discover a null pointer in the buffer handler, and the size is by default a time-slice (100K). Additionally, buffers are independent of others, i.e. a processor in a determined instant may have several buffers been consumed, however, just one buffer is receiving data at any moment. Notwithstanding the number of simultaneous buffers is unpredictable due thread scheduling, experimental data show not more than four buffer existing simultaneously. As a result of host parallelism, for example, in a quad-core host OVPSim use only one leaving the other three to work threads. This behavior is due the duration of timing estimation of a chunk of instructions, been faster than simulate these instructions in OVPsim with the concomitant phase attached due the necessity of simulation interrupt at every fetch.

# **5.3** Thread Management

This extension also requires thread management, and in order to benefit better from host parallelism threads are independent of simulation main flow, i.e. there will be not a join calls after. The use of detached threads improves performance, while decreases the memory usage, since resources are immediately released as soon as a thread execution is completed.

When simulations come to end is not guarantee to all worker threads already finished, as result is necessary synchronize all threads. The synchronization is performed through a barrier like mechanism insert at simulation main flow end. As previous mentioned, threads are detached; consequently, thread join function is not an option and is not truly imperative since is necessary wait all threads finishes, not a specific one.

We use a global thread count variable, responsible by control the active threads number. Whenever a thread is created, the counter is incremented. Just after a work thread updates internal data, counter is decremented. The barrier is developed as a loop statement until thread counters reach zero, to avoid busy waiting and release resources a sleep call is realized inside the loop.

#### 5.4 Simulation behavior

This extension also requires thread management, and in order to benefit better from host parallelism threads are independent of simulation main flow, i.e. there will be not a join calls after. The use of detached threads improves performance, while decreases the memory usage, since resources are immediately released as soon as a thread execution is completed.

When simulations come to end is not guarantee to all worker threads already finished, as result is necessary synchronize all threads. The synchronization is performed through a barrier like mechanism insert at simulation main flow end. As previous mentioned, threads are detached; consequently, thread join function is not an option and is not truly imperative since is necessary wait all threads finishes, not a specific one.

We use a global thread count variable, responsible by control the active threads number. Whenever a thread is created, the counter is incremented. Just after a work thread updates internal data, counter is decremented. The barrier is developed as a loop statement until thread counters reach zero, to avoid busy waiting and release resources a sleep call is realized inside the loop.

Figure 5.1 - Block diagram of developed watchdog module thread extension.

#### 6 EXPERIMENTAL SETUP AND RESULTS

#### 6.1 Timing CPU model results

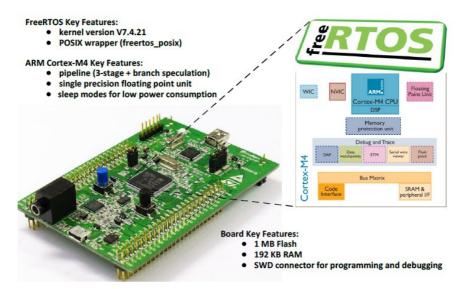

In order to demonstrate the effectiveness of our approach, a 32-bit ARM Cortex-M4F processor, which is based on the ARMv7M architecture, was used as a case study. In the study case are used benchmarks from different domains, demonstrating the benefits towards the software evaluation facilities inherent to the proposed approach.

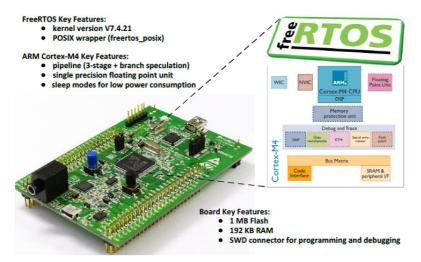

For our experiments, the STM32F4-Discovery board was used as reference platform, as illustrated in Figure 6.1. The reference STM32F4 Discovery board is built around a 32-bit ARM Cortex-M4F core running a FreeRTOS kernel version V.7.4.21 at 168 MHz. Among other features, ARM Cortex-M4F supports single precision floating-point unit (FPU) and power saving modes, which can be used for the development of energy-efficient embedded systems. Both Cortex-M4F and FreeRTOS are highly used in high-performance embedded system design, justifying the choice.

Figure 6.1 - Adopted reference board platform. Proposed illustration integrates figures captured from their owner's websites.

As means to verify model accuracy is fundamental expose the watchdog to real scenarios, diversifying possible instructions patterns encountered during simulation. Benchmark execution is composed by three phases. First, port chosen benchmarks to our framework, real board and OVP. Committed to ensuring both platform runs most similar code as possible, although is not feasible execute exactly the same binary duo platform related initialization. However, this discrepancy is less than 500 instructions. Assuring a compilation using same cross-compile, libraries, compilation flags is possible create almost identical binaries.