# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

### KARLSRUHER INSTITUTE FÜR TECHNOLOGIE FAKULTÄT FÜR ELEKTROTECHNIK UND INFORMATIONSTECHNIK

#### JOSÉ RODRIGO FURLANETTO DE AZAMBUJA

#### Designing and Evaluating Hybrid Techniques to Detect Transient Faults in Processors Embedded in FPGAs

A thesis submitted to evaluation in partial fulfillment of the requirements for the Degree of Doctor of Computer Science

A thesis submitted to evaluation in partial fulfillment of the requirements for the Degree of  $Doctor\ of\ Engineering$

Prof. Dr. FernandaGusmão de Lima Kastensmidt Advisor Prof. Dr.-Ing. Dr. h. c. Jürgen Becker

Advisor

#### CIP – CATALOGAÇÃO NA PUBLICAÇÃO

Azambuja, José Rodrigo Furlanetto de

Designing and Evaluating Hybrid Techniques to Detect Transient Faults in Processors Embedded in FPGAs / José Rodrigo Furlanetto de Azambuja – Porto Alegre: Programa de Pós-Graduação em Computação, 2013.109 p.:il.

Thesis (doctorate) – Universidade Federal do Rio Grande do Sul and Karlsruher Institute für Technologie. Programa de Pós-Graduação em Computação and Fakultät für Elektrotechnik und Informationtechnik. Porto Alegre, BR – RS, 2013. Supervisors: Fernanda Gusmão de Lima Kastensmidt and Jürgen Becker.

1. Fault tolerance. 2. Radiation effects. 3. Processors. I. Kastensmidt, Fernanda G. L. and Becker, J.. II. Designing and Evaluating Hybrid Techniques to Detect Transient Faults in Processors Embedded in FPGAs.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos Alexandre Netto

Vice-Reitor: Prof. Rui Vicente Oppermann

Pró-Reitor de Pós-Graduação: Prof. Vladimir Pinheiro do Nascimento

Diretor do Instituto de Informática: Prof. Luís da Cunha Lamb

Coordenador do PPGC: Prof. Luigi Carro

Bibliotecário-Chefe do Instituto de Informática: Alexsander Borges Ribeiro

#### **ACKNOWLEDGEMENTS**

I would like to start by thanking my parents, Tais and Gui, and my brother, Cado, who have always been there for me, being "there" a few meters, or a few thousand kilometers away. Thank you for all the support you provided me, allowing me to devote myself entirely to the studies. I also thank my grandparents, uncles and cousins for the countless moments, which would not fit in these few lines.

I take the opportunity also to thank Georg, who despite not having any kind of kinship with me was like a second father during the time I spent in Germany.

I would also like to thank my colleagues from UFRGS, Anelise, Carol, Eduardo, Fernando, Jimmy, Jorge, Lucas, Samuel, William and Mauricio, for the countless hours discussing a variety of subjects, the chimarrões, and the terrible football championships (and let there be Radecs!), and from KIT, Christoph, Falco, Mahtab and Oliver, for the indoor sports, FPGA boards resuscitation and hat making.

To all my friends who took me out of the lab during the weekends - and also to the ones who kept me in it during the week - and my apologies for not being able to quote you all. To FDC, for all the poorly planned adventures, and to the band, for not letting rock die - and still allowing me to play in it.

To the great friends who I rediscovered and to the great friendships I made during my stay in Germany, who made my day much better and my job much easier, Ari, Bruna, Cilene, Cláudio, Elian, Fada, Irigas, Paola, Pedrão, Gabriel, Oliver, Sharon and Zatt, and to those who I barely saw in person, but have always been fighting evil with me in the fields of justice, Christoph, Dirk, Fabio and Julian.

To my entrepreneurs friends who came to believe in a small project and today are richer than Eike Batista: Inácio and Werner.

Especially to Fernanda, for putting up with me during 7 years. Thank you for the confidence and freedom of research on the most varied subjects. I also thank Professor Jürgen Becker for the many research opportunities inside - and outside - of KIT, as well as for providing me with a great work environment. To Professors Álvaro, Lisboa, Luigi, Michael, Paolo, Reis and Weber, for all their help during my PhD.

To Elisiane, Leivo and to the coordination of PPGC, Instituto de Informática, ITIV, UFRGS, and KIT and to the financial support provided by CNPq, CAPES and HIRST.

Finally, I would like to thank the supernatural forces - in which I do not believe, but I know they exist - that make us go forward and until the end.

To all of you, my sincere Thanks.

# TABLE OF CONTENTS

| LIST OF A                                                  | ABREVIATIONS AND ACRONYMS                                                                                                                                               | 7              |

|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| LIST OF F                                                  | GURES                                                                                                                                                                   | 10             |

| LIST OF 1                                                  | ABLES                                                                                                                                                                   | 11             |

| ABSTRAC                                                    | CT                                                                                                                                                                      | 12             |

| RESUMO                                                     |                                                                                                                                                                         | 13             |

| ZUSAMM                                                     | ENFASSUNG                                                                                                                                                               | 14             |

| 1 INTRO                                                    | DUCTION                                                                                                                                                                 | 15             |

| 1.1 Motiv                                                  | ration and Problem Definition                                                                                                                                           | 15             |

| 1.2 Over                                                   | view                                                                                                                                                                    | 17             |

| 2 BACK                                                     | GROUND                                                                                                                                                                  | 19             |

| 2.1.1<br>2.1.1.1<br>2.1.1.2                                | Concepts of Dependable and Secure Computing  Defect, Upset and Fault Definitions  Single Event Effect (SEE):  Total Ionizing Dose (TID):  Error and Failure Definitions | 19<br>20<br>20 |

| 2.1.2                                                      | 21.01 41.01 41.01 5 5 11.11.120.10                                                                                                                                      | 21             |

|                                                            | Architecture                                                                                                                                                            |                |

| 2.2 MIPS  2.3 SEE i  2.3.1  2.3.2  2.4 Fault  2.4.1        | n MIPS Processors                                                                                                                                                       | 2324252627     |

| 2.2 MIPS  2.3 SEE i  2.3.1  2.3.2  2.4 Fault  2.4.1  2.4.2 | n MIPS Processors                                                                                                                                                       | 2324252627     |

| 3    | 3.1            | Software-Based Techniques                              | 31 |

|------|----------------|--------------------------------------------------------|----|

| 3    | 3.2            | Hardware-Based Techniques                              | 33 |

| 3    | 3.3            | Hybrid Techniques                                      | 35 |

| 3    | 3.4            | Summary                                                | 37 |

|      |                |                                                        |    |

| DD ( |                | ROPOSED TECHNIQUES TO DETECT TRANSIENT FAULTS IN       |    |

| FNC  | JUL            | 330K3                                                  | 39 |

| 4    | .1             | Hardening Post Compiling Tool (HPCT)                   | 39 |

| 4    | 1.2            | Improved Variables Technique (VAR)                     | 41 |

|      | 4.2.           | .1 Implementation Details                              | 41 |

| 4    | 1.3            | Improved Inverted Branches Technique (BRA)             | 43 |

|      | 4.3.           | .1 Implementation Details                              | 43 |

| 4    | .4             | PODER Technique                                        | 45 |

|      | 4.4.           | .1 Software-based Side                                 | 46 |

|      |                | 4.4.1.1 Jumps to the Beginning of a Basic Block        |    |

|      |                | 4.4.1.2 Jumps to the Same Basic Block                  |    |

|      | 4.4.           |                                                        |    |

|      | 4.4.           |                                                        |    |

|      |                | 4.4.3.1 PODER's Software Transformation Implementation |    |

|      | 4              | 4.4.3.2 Hardware Module Implementation                 | 54 |

| 4    | 1.5            | On-line Control Flow Checker Module (OCFCM)            |    |

|      | 4.5.           |                                                        |    |

|      | 4.5.           |                                                        |    |

|      | 4.5.           | 3 Implementation                                       | 58 |

| 4    | <b>l.6</b>     | Hybrid Error-detection Technique using Assertions      | 60 |

|      | 4.6.           | · ·                                                    |    |

|      | 4.6.           | 2 Software-based Side                                  | 62 |

|      | 4              | 4.6.2.1 Description Details                            | 62 |

|      | 4              | 4.6.2.2 Signature checking algorithms                  | 63 |

|      | 4.6.           |                                                        |    |

|      | 4.6.           | r                                                      |    |

|      |                | 4.6.4.1 HETA Software Transformation                   |    |

|      | 4              | 4.6.4.2 Hardware Module Implementation                 | 68 |

| 5    | <del>.</del> e | IMULATION FAULT INJECTION EXPERIMENTAL RESULTS         | 70 |

| į.   | ) 3            |                                                        |    |

| 5    | 5.1            | PODER                                                  | 71 |

| 5    | 5.2            | OCFCM                                                  | 73 |

| 5    | 5.3            | HETA                                                   | 74 |

|      |                |                                                        |    |

| 6    |                | ONFIGURATION BITSTREAM FAULT INJECTION EXPERIMENT      |    |

| RES  | SULT           | TS                                                     | 75 |

| 6    | 5.1            | PODER                                                  | 76 |

| 6    | 32             | OCECM                                                  | 78 |

| 6.3 H | IETA                         | 79 |

|-------|------------------------------|----|

| 7 RA  | DIATION EXPERIMENTAL RESULTS | 81 |

| 7.1 M | IIPS in Flash-based FPGAs    | 81 |

| 7.1.1 |                              |    |

| 7.1.2 | Neutron Experiment           | 85 |

| 7.2 N | IIPS in SRAM-based FPGAs     | 86 |

| 7.2.1 | TID Experiment               | 86 |

| 7.2.2 | Neutron Experiment           | 86 |

| 8 CO  | NCLUSIONS AND FUTURE WORK    | 91 |

| REFER | RENCES                       | 93 |

| APEN  | DIX - PROPOSTA DE DOUTORADO  | 99 |

#### LIST OF ABREVIATIONS AND ACRONYMS

ACCE Automatic Correction of Control Flow Errors

ACCED Automatic Correction of Control Flow Errors with Duplication

ALU Arithmetic and Logic Unit

ASIC Application Specific Integrated Circuits

AUT Area Under Test

BB Basic Block

BID Block Identifier

BRA Inverted Branches Technique

BRAM Block Random Access Memory

CAEN Chemically Assembled Electronic Nanotechnology

CCA Control Flow Checking using Assertions

Control Flow Identifier

CEDA Control-flow Error Detection through Assertions

CFCSS Control Flow Checking by Software Signatures

CLB Configurable Logic Block

COTS Commercial Off The Shelf

CUT Circuit Under Test

**CFID**

CWSP Code Word State Preserving

DUT Design Under Test

DWC Duplication With Comparison

ECC Error Correcting Codes

ECCA Enhanced Control Flow Checking using Assertions

EDAC Error Detection And Correction

ED<sup>4</sup>I Error Detection by Data Diversity and Duplicated Instructions

EHP Electron-Hole-Pairs

ENSERG Ecole Nationale Supérieure d'Electronique et de Radioélectricité de

Grenoble

EoE End of Execution

FIT Failure In Time

FF Flip-Flop

FP Frame Pointer

FPGA Field Programmable Gate Array

GUI Graphic User Interface

GP Global Pointer

GPP General Purpose Processor

GPU Graphic Processing Unit

GSR Global Signature Register

HDL Hardware Description Language

HETA Hybrid Error-detection Technique using Assertions

HPCT Hardening Post Compiling Translator

IC Integrated Circuit

Icc Power Supply Current

ICAP Internal Configuration Access Port

I-IP Infrastructure Intellectual Property

IP Intellectual Property

ISA Instruction Set Architecture

ITAR International Traffic in Arms Regulation

JALR Jump And Link to Register

JR Jump to Register

JRE Java Runtime Environment

KIT Karlsruhe Institute of Technology

LANSCE Los Alamos Nuclear Science Center

LANL Los Alamos National Laboratory

LUT Look-Up Table

MeV Mega-electron Volts (106 electron Volts)

MIPS<sub>1</sub> Microprocessor without Interlocked Pipeline Stages

MIPS<sub>2</sub> Mega (10<sub>6</sub>) Instructions Per Second

NES Node Exit Signature

NGL Next Generation Lithography

NIS Node Ingress Signature

NoC Network-on-Chip

NOP No Operation

NRE Non-recurring engineering

NT Node Type

OCFCM Online Control Flow Checker Module

PC Program Counter

PLL Phase-Locked Loop

RA Return Address

RadHard Radiation Hardened

RAM Random Access Memory

RISC Reduction Instruction Set Computer

RTL Register Transfer Level

SEE Single Event Effect

SEL Single Event Latch-up

SET Single Event Transient

SEU Single Event Upset

SIC Structural Integrity Checking

SIHFT Software Implemented Hardware Fault Tolerance

SoC System-on-Chip

SP Stack Pointer

SRAM Static Random Access Memory

TCL Tool Command Language

TID Total Ionizing Dose

TMR Triple Modular Redundancy

UFRGS Universidade Federal do Rio Grande do Sul

USML United States Munitions List

VAR Variables Technique

VHDL Very-high-speed integrated circuits Hardware Description Language

XOR Exclusive OR

XTMR Xilinx Triple Modular Redundancy

## LIST OF FIGURES

| Figure 2.1: SEU and SET effects on a circuit.                                                   |       |

|-------------------------------------------------------------------------------------------------|-------|

| Figure 2.2: Upset, fault, error and failure chain-effect for SET and SEU                        | 21    |

| Figure 2.3: Logical masking.                                                                    |       |

| Figure 2.4: Electrical masking                                                                  |       |

| Figure 2.5: Latch window masking.                                                               |       |

| Figure 2.6: Pipeline architecture of the miniMIPS.                                              | 23    |

| Figure 2.7: miniMIPS sensitive areas under SEE.                                                 |       |

| Figure 3.1: COTS x RadHard processor throughput (KEYS, 2008)                                    |       |

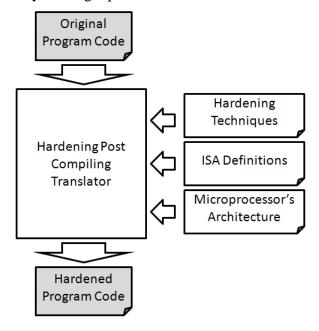

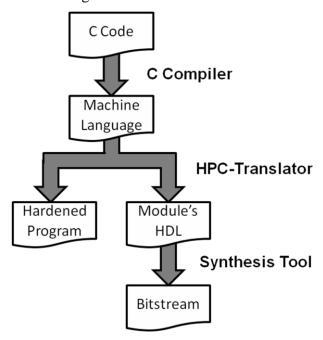

| Figure 4.1: HPCT's workflow                                                                     | 40    |

| Figure 4.2: Variables technique's transformation.                                               |       |

| Figure 4.3: Inverted Branches technique's transformation.                                       |       |

| Figure 4.4: Examples of Incorrect jumps to the same BB (1) and to the beginning of a BB (2)     | 46    |

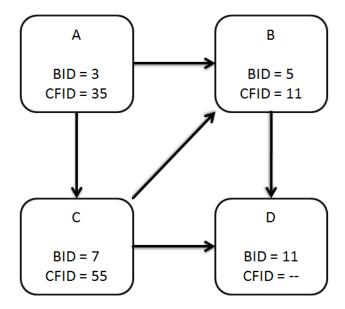

| Figure 4.5: PODER technique's BB graph                                                          | 48    |

| Figure 4.6: Incorrect jumps to unused memory addresses (3) and control flow loops (4)           | 49    |

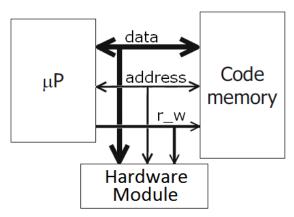

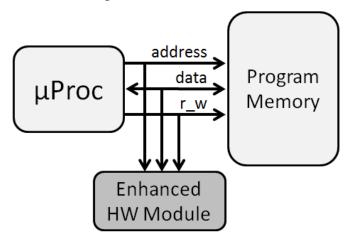

| Figure 4.7: PODER technique's system architecture.                                              | 50    |

| Figure 4.8: PODER technique transformation for queue management                                 | 51    |

| Figure 4.9: PODER technique transformation for XOR value                                        | 52    |

| Figure 4.10: PODER technique transformation after optimization                                  |       |

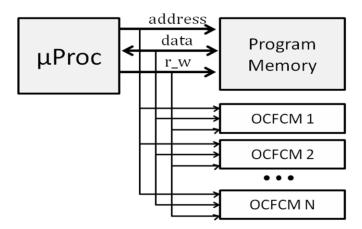

| Figure 4.11: OCFCM's system architecture                                                        | 56    |

| Figure 4.12: Automatic hardware generation flow.                                                | 58    |

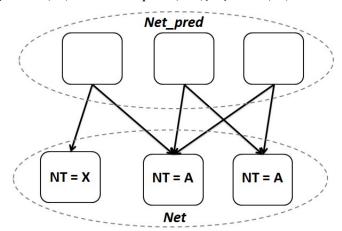

| Figure 4.13: Program graph with both NT types.                                                  |       |

| Figure 4.14: Algorithm for the signature's lower half                                           | 64    |

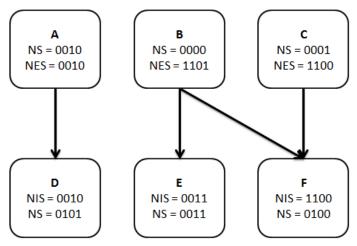

| Figure 4.15: NIS, NS and NES signatures                                                         |       |

| Figure 4.16: HETA's system architecture.                                                        |       |

| Figure 4.17: HETA transformation.                                                               | 67    |

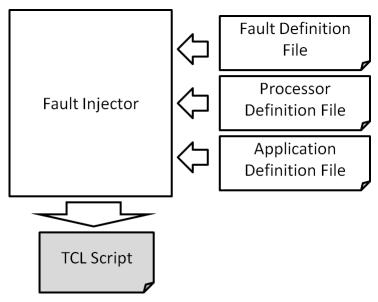

| Figure 5.1: Fault injector's role                                                               | 70    |

| Figure 5.2: Fault injection example of a SET in signal add_reg1 bit 3                           | 71    |

| Figure 6.1: Configuration bitstream fault injector system overview (NAZAR, 2012a)               | 76    |

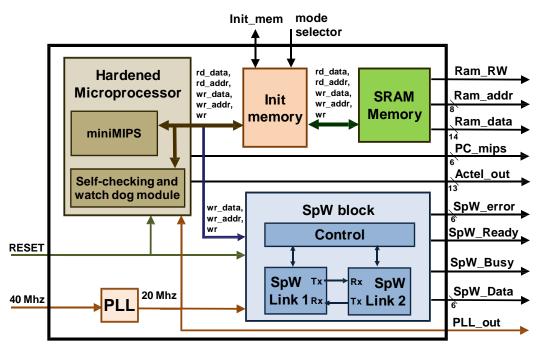

| Figure 7.1: Architecture of the embedded system.                                                | 82    |

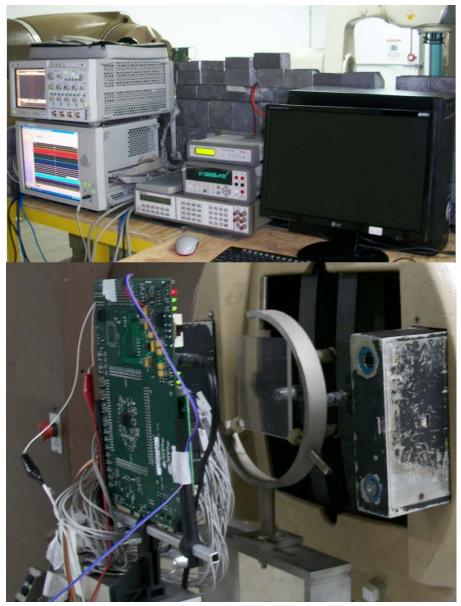

| Figure 7.2: Experimental setup.                                                                 | 83    |

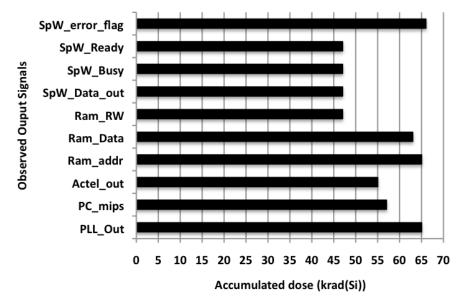

| Figure 7.3: Accumulated dose for each signal output.                                            | 84    |

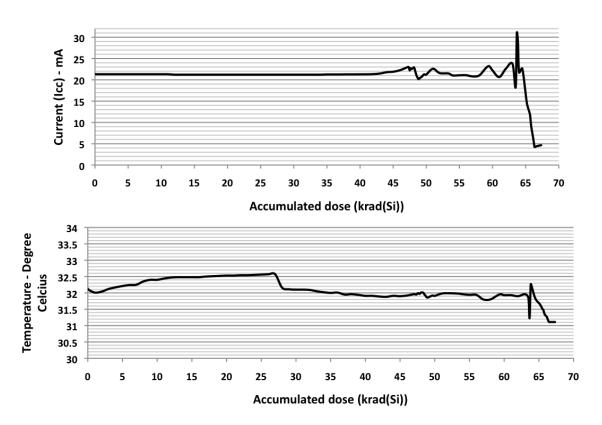

| Figure 7.4: Measured current and temperature                                                    | 85    |

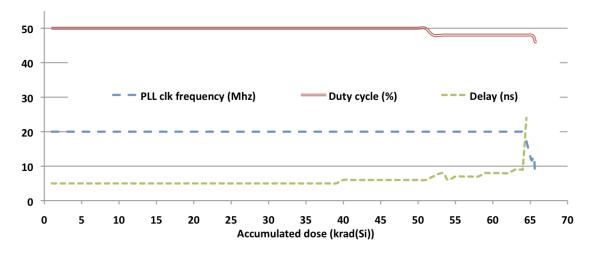

| Figure 7.5: PLL clock output measurements: frequency, duty cycle and delay compared to the ext  | ernal |

| 40 MHz clock                                                                                    |       |

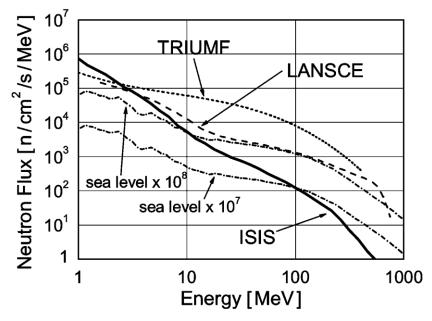

| Figure 7.6: ISIS spectrum compared to those of the LANSCE and TRIUMF facilities and to the tell |       |

| one at sea level multiplied by $10^7$ and $10^8$                                                | 86    |

| Figure 7.7: DUT's architecture with the test control unit                                       | 87    |

| Figure 7.8: FPGA's module placement                                                             | 88    |

# LIST OF TABLES

| Table 2.1: MIPS' instruction format                                                                    | 24  |

|--------------------------------------------------------------------------------------------------------|-----|

| Table 3.1: Fault tolerance techniques summary                                                          |     |

| Table 4.1: Characteristics for the variables technique program transformation                          |     |

| Table 4.2: Characteristics for the Inverted Branches technique program transformation                  | 44  |

| Table 4.3: Characteristics for the PODER program transformation to the matrix multiplication           |     |

| Table 4.4: Characteristics for the PODER program transformation to the bubble sort                     | 53  |

| Table 4.5: Area and performance of miniMIPS and the hardware module used by PODER technique            |     |

| synthesized in 0.18µ CMOS process technology                                                           | 54  |

| Table 4.6: OCFCM technique area results for a set of applications and the percentage of the area       |     |

| compared to the miniMIPS microprocessor synthesized into FPGA                                          | 59  |

| Table 4.7: Partial reconfiguration time for SRAM-based FPGA (Virtex 4 xc4vlx80-12ff1148)               |     |

| Table 4.8: Characteristics for the HETA program transformation to the matrix multiplication            |     |

| Table 4.9: Characteristics for the HETA program transformation to the bubble sort                      | 68  |

| Table 4.10: Original and modified architecture characteristics for HETA technique synthesized in 0.1   | 8μ  |

| CMOS process technology                                                                                | 69  |

| Table 5.1: Percentage of number of error from fault injection results for PODER fault tolerant technic | que |

| in miniMIPS running the matrix multiplication                                                          | 72  |

| Table 5.2: Percentage of number of error from fault injection results for PODER fault tolerant technic | que |

| in miniMIPS running the bubble sort                                                                    |     |

| Table 5.3: Number of faults injected by simulation fault injection in miniMIPS protected by OCFCM a    | and |

| the percentage of detected errorsthe percentage of detected errors                                     | 74  |

| Table 5.4: Number of faults injected by simulation fault injection in miniMIPS protected by HETA and   | d   |

| the percentage of detected errors                                                                      |     |

| Table 6.1: Classification of the total 48,323 faults in the miniMIPS protected by PODER technique wi   | th  |

| VAR and BRA                                                                                            |     |

| Table 6.2: Diagnosis of detected faults and errors for PODER with VAR and BRA                          | 78  |

| Table 6.3: Classification of the total 54,024 faults in the miniMIPS protected by OCFCM technique w    | ith |

| VAR and BRA                                                                                            |     |

| Table 6.4: Diagnosis of detected faults and errors for OCFCM with VAR and BRA                          | 79  |

| Table 6.5: Classification of the total 75,619 faults in the miniMIPS protected by HETA technique with  | l   |

| VAR and BRA                                                                                            |     |

| Table 6.6: Diagnosis of detected faults and errors for HETA with VAR and BRA                           |     |

| Table 7.1: Classification of the total 958 faults in FPGA design tested under neutrons                 | 89  |

| Table 7.2: Fault injection by partial reconfiguration in SRAM-based FPGA                               | 89  |

#### Designing and Evaluating Hybrid Techniques to Detect Transient Faults in Processors Embedded in FPGAs

#### **ABSTRACT**

Recent technology advances have provided faster and smaller devices for manufacturing circuits that while more efficient have become more sensitive to the effects of radiation. Smaller transistor dimensions, higher density integration, lower voltage supplies and higher operating frequencies are some of the characteristics that make energized particles an issue when dealing with integrated circuits in harsh environments. These types of particles have a major influence in processors working in such environments, affecting both the program's execution flow by causing incorrect jumps in the program, and the data stored in memory elements, such as data and program memories, and registers. In order to protect processor systems, fault tolerance techniques have been proposed in literature using hardware-based and software-based approaches, which decrease the system's performance, increase its area, and are not able to fully protect the system against such effects. In this context, we proposed a combination of hardware- and software-based techniques to create hybrid techniques aimed at detecting all the faults affecting the system, at low performance degradation and memory overhead. Five techniques are presented and described in detail, from which two are known software-based only techniques and three are new hybrid techniques, to detect all kinds of transient effects caused by radiation in processors. The techniques are evaluated according to execution time, program and data memories, and area overhead and operating frequency degradation. To verify the effectiveness and the feasibility of the proposed techniques, fault injection campaigns are performed by injecting faults by simulation and performing irradiation experiments in different locations with neutrons and a Cobalt-60 sources. Results have shown that the proposed techniques improve the state-of-the-art by providing high fault detection rates at low penalties on performance degradation and memory overhead.

**Keywords:** fault tolerance, radiation effects, processors.

#### Desenvolvendo e Avaliando Técnicas Híbridas para Detectar Falhas Transientes em Processadores Embarcados em FPGAs

#### **RESUMO**

Os recentes avanços tecnológicos proporcionaram dispositivos menores e mais rápidos para a fabricação de circuitos que, apesar de mais eficientes, se tornaram mais sensíveis aos efeitos de radiação. Menores dimensões de transistores, mais densidade de integração, tensões de alimentação mais baixas e frequências de operação mais altas são algumas das características que tornaram partículas energizadas um problema, quando lidando com sistemas integrados em ambientes severos. Estes tipos de partículas tem uma grande influencia em processadores funcionando em tais ambientes, afetando tanto o fluxo de execução do programa ao causar desvios incorretos, bem como os dados armazenados em elementos de memória, como memórias de dados e programas e registradores. A fim de proteger sistemas processados, técnicas de tolerância a falhas foram propostas na literatura usando propostas baseadas em hardware, software, que diminuem o desempenho do sistema, aumentam a sua área e não são capazes de proteger totalmente o sistema destes efeitos. Neste contexto, propomos a combinação de técnicas baseadas em hardware e software para criar técnicas híbridas orientadas a detectar todas as falhas que afetam o sistema, com baixa degradação de desempenho e aumento de memória. Cinco técnicas são apresentadas e descritas em detalhes, das quais duas são conhecidas técnicas baseadas puramente em software e três são técnicas híbridas novas, para detectar todos os tipos de efeitos transientes causados pela radiação em processadores. As técnicas são avaliadas de acordo com o aumento no tempo de execução, no uso das memórias de dados e programa e de área, e degradação da frequência de operação. Para verificar a eficiência e aplicabilidade das técnicas propostas, campanhas de injeção de falhas são realizadas ao se simular a injeção de falhas e realizar experimentos de irradiação em diferentes localidades com nêutron e fontes de Cobalto-60. Os resultados mostraram que as técnicas propostas aprimoraram o estado da arte ao fornecer altas taxas de detecção de falhas com baixas penalidades em degradação de desempenho e aumento de memória.

Palavras-Chave: tolerância a falhas, efeitos de radiação, processadores.

#### Entwurf und Auswertung von Hybrid-Techniken zur Erkennung von transienten Fehlern in FPGA eingebetteten Prozessoren

#### ZUSAMMENFASSUNG

Der aktuelle Stand der Technologie bringt schnellere und kleinere Bausteine für die Herstellung von integrierten Schaltungen mit sich, die während sie effizienter sind auch anfälliger für Strahlung werden. Kleinere Abmessungen der Transistoren, höhere Integrationsdichte, geringere Versorgungsspannungen und höhere Betriebsfrequenzen sind einige der Charakteristika, die energiegeladene Partikel zu einer Herausforderung machen, wenn man integrierte Schaltungen in rauen Umgebungen einsetzt. Diese Art der Partikel hat einen sehr großen Einfluss auf Prozessoren, die in einer solchen Umgebung eingesetzt werden. Sowohl die Ausführung des Programms, welche durch fehlerhafte Sprünge in der Programmsequenz beeinflusst wird, als auch Daten, die in speichernden Elementen wie Programmspeicher, Datenspeicher oder in Registern abgelegt sind, werden verfälscht. Um solche Prozessorsysteme abzusichern, wird in der Literatur Fehlertoleranz empfohlen, welche die Systemperformanz verringert, einen größeren Flächenverbrauch mit sich bringt und das System dennoch nicht komplett schützen kann. Diese Fehlertoleranz kann sowohl durch software- als auch durch hardwarebasierte Ansätze umgesetzt werden. In diesem Zusammenhang schlagen wir eine Kombination aus Hardware- und Software- Lösung vor, welche die Systemperformanz nur sehr wenig beeinflusst und den zusätzlichen Speicheraufwand minimiert. Diese Hybrid-Technologie zielt darauf ab, alle Fehler in einem System zu finden. Fünf solcher Techniken werden beschrieben und erklärt, zwei der vorgestellten Techniken sind bekannte Software-Lösungen, die anderen drei sind neue Hybrid-Lösungen, um alle transienten Effekte von Strahlung in Prozessoren erkennen zu können. Diese unterschiedlichen Ansätze werden anhand ihrer Ausführungszeit, Programm-, Datenspeicher, Flächenvergrößerung und Taktfrequenz analysiert und ausgewertet. Um die Effizienz und die Machbarkeit des vorgeschlagenen Ansatzes verifizieren zu können, werden Fehlerinjektionstests sowohl durch Simulation als auch durch Bestrahlungsexperimente in unterschiedlichen Positionen mit einer Cobalt-60 Quelle durchgeführt. Die Ergebnisse des vorgeschlagenen Ansatzes verbessern den Stand der Technik durch die Bereitstellung einer höheren Fehlererkennungsrate bei sehr geringer negativer Beeinflussung der Performanz und des Speicherverbrauchs.

**Stichworte:** Fehlertoleranz, Strahlungseffekte, Prozessoren.

#### 1 INTRODUCTION

Since the 1950's, when computers were made with vacuum tubes and the personal computer was nothing more than a dream, fault tolerance has been an important topic of interest. In the early ages of computers, their usage was very specific, aimed at activities such as military applications, precise calculations and space missions. An error in these applications working in such harsh environments, and sometimes even in remote places like as the space, could completely jeopardize the mission, since the repair and, in some cases, the available time to repair the system was impractical. From then until nowadays many things have changed. The technology no longer relies on vacuum tubes, but on transistors, computers became ubiquitous and a personal computer can be found in any cell phone. One the other hand, a few things remained the same, such as the old topic on how to give a system the ability to cope with a fault and continue its correct operation, or in other words, fault tolerance.

The technology did not only advance in the past, but it is constant progress. Today we can observe new trends, such as the continued reduction in transistor sizes, new fabrication processes and materials, low-power systems to fit small ubiquitous microprocessors and medical applications and, as always, the need for more processing power through higher frequencies of operation and more processing cores per die. At the same time that these advances push technology forward, they increase the system's susceptibility to noises that are present in the environment. One well-known effect is the radiation effect present in space applications but also at avionic and at ground-level. Due to the reduced transistor size and low voltages, the fault effect in integrated circuits is increasing in magnitude; consequently, fault tolerant techniques will become mandatory in all devices in the close future.

This document exposes the reasons behind the concerns surrounding a system's fault tolerance. Some of the most important fault tolerant techniques presented in the literature are analyzed and three hybrid techniques to detect faults in processors are proposed as the thesis work. In order to prove the effectiveness of the proposed techniques, fault injection campaigns were performed, including configuration bitstream fault injection, and neutron and Cobalt-60 beams irradiation experiments.

#### 1.1 Motivation and Problem Definition

The recent advances in the semiconductor industry have led in the development of more complex components and systems' architectures by allowing fabrication processes to place a higher number of transistors per area of the silicon die. The CMOS technology has developed according to Moore's law (MOORE, 1965), where the number of transistors on Integrated Circuits (IC) doubles every two years. Nowadays, with factories fabricating transistors with 32nm, we are reaching the physical limits of a couple atoms to form the transistor's gate (KIM, 2003), (HOMPSON, 2005). Still, new

technologies arise, such as Next Generation Lithography (NGL) and Chemically Assembled Electronic Nanotechnology (CAEN), promising to reduce feature sizes to 20nm and less.

However, the same technology that made possible all this progress has also reduced the transistor reliability by reducing threshold voltages, node capacitances and tightening the noise margins (BAUMANN, 2001). These have made transistors more susceptible to faults caused by radiation interference, which can be energized particles presented on space or secondary particles such as alpha particles, generated by interaction of neutron and materials at ground level. As a consequence, mission-critical applications, such as space applications or avionics, demand fault tolerant techniques capable of recovering the system from a fault with minimum implementation and performance overhead.

Processors working in harsh environments can be upset by such energized particles. They affect processors by modifying values stored in memory elements (such as registers and data memory), by leading the processor to incorrectly execute an application by jumping or re-executing some instructions, or even by entering in a loop and never finishing the application. Such faults can also modify some computed data values, generating errors in the data results. Therefore, the use of fault tolerance techniques is mandatory to detect and/or correct these types of faults. Since processors run software on top of their hardware, fault tolerance techniques used to harden them can be based on software, hardware or hybrid solutions.

Fault tolerance techniques based on software rely on adding extra instructions to the original program code to detect or correct faults (BOLCHINI, 2005). They may be able to detect faults that affect the data and the control flow. Software-based techniques provide high flexibility, low development time and cost, since there is no need to modify the hardware. In addition, new generations of microprocessors that do not have Radiation Hardened (RadHard) versions can be used. As a result, aerospace applications can use commercial off the shelf (COTS) microprocessors with RadHard software. However, some results from random fault injection have shown the impossibility of achieving complete fault coverage when using only software-based techniques, due to control flow errors (AZAMBUJA, 2011b). This limitation is due to the inability of the software in protecting against all possible control flow effects errors that can occur in the microprocessor. One example would be a fault in the Program Counter (PC), where only a single No OPeration (NOP) instruction can execute. In this case, it does not matter how many instructions or data are added to the original code, because none of them will be executed by the processor and no fault will be detected.

As a consequence of the redundant instructions inserted in the original program code, software-based techniques have as drawbacks overheads in both data and program memory, and degradation in performance, due to an increased computation time required to execute the program. The program memory increases due to additional instructions inserted in the original program code, while the data memory may increase due to variable replication, which can be, for example, the replication of all stored data in the memory. Performance degradation comes from the execution of redundant instructions.

Hardware-based techniques usually change the original processor architecture by adding redundant logic, such as module replication with majority voters, information redundancy, such as Error Correcting Codes (ECC), or time redundancy, such as the one presented by Anghel (2000). Hardware-based techniques can also be based on

hardware monitoring devices that are inserted to the system's architecture, such as a verification hardware module, and therefore change the system's architecture, but not the processor's architecture and in this case are non-intrusive. They exploit special purpose hardware modules, called watchdog processors, to monitor memory accesses.

As a consequence of the extra logic or information redundancy, hardware-based techniques increase the processor's area up to more than three times the original size, which leads to more power consumption and production costs. Time redundancy usually does not have a big impact in area, but decreases considerably the performance, since they affect the execution time and, in some cases, the operation clock frequency. Non-intrusive hardware modules, such as watchdogs, may have a smaller impact in area and operating clock frequency, but they require access to processor's connections, such as access to the data and code memory connections. Watchdogs do not detect faults that are latent inside the microprocessor, as faults in the register bank, because they do not have access to the processor's internal buses (in order to be non-intrusive).

#### 1.2 Overview

In order to provide reliable systems that can cope with radiation effects, we believe that the solution lies in combining software-based and hardware-based techniques. The main objective of this work is finding the best trade-off between software-based and hardware-based techniques to increase existing fault detection rates up to 100%, while maintaining low overheads in performance, in the means of operating clock frequency and application execution time, and area, in the sense of both program and data memory overhead, and extra hardware modules.

The first step to achieve our goal was to analyze the radiation effects on integrated circuits. In a second step, we performed an analysis on the influence of such effects in processors, such as the effects of a fault at a given part of the processor and its influence on the results of a running program. To do so, we checked the affected area in processor in the sense of which areas are more sensitive to which types of effects, and also the effect of a particle in the processor, in the sense of control or data flow effects. Then, we searched the literature for existing fault tolerant techniques using hardware-based techniques, software-based techniques and hybrid ones. As a result, none of the available techniques in the literature could fully protect a processor against transient effects without huge drawbacks, such as performance degradation and area overhead.

We started by implementing two known software-based techniques, called Variables and Inverted Branches (AZAMBUJA, 2010b). From there, we proposed three hybrid techniques, based both on software and hardware replication characteristics. The implemented techniques are generic and could be implemented to any application, but in order to focus this work in the techniques, instead of the application, we chose a few case-study applications and implemented the techniques for each of them. Results showed low performance degradation and memory overhead, when compared to techniques in presented in the literature.

In order to check the effectiveness and feasibility of the proposed techniques, we performed three fault injection campaigns. The first one consisted of simulating faults through a commercial simulator, where we injected hundreds of thousands of faults in the chosen case-study applications. For the second injection campaign, we used a Field Programmable Gate Array (FPGA) based on Static Random Access Memory (SRAM) configuration bitstream and exhaustively injected millions of faults in the configuration memory bitstream. For the third fault injection campaign, we used cyclotrons around

the world to hit the integrated circuit hardened by our techniques with neutron and cobalt-60 beam sources. For the last campaign, we used SRAM-based and flash-based FPGAs to implement the Design Under Test (DUT) and test them for radiation effects.

Preliminary results have shown interesting results, when compared to related works in the literature. The performance degradation combined with area and memory overhead improved the state-of-the-art. These results have been backed by intense fault injection campaigns, performed both by simulation and irradiation experiments in the sense that the proposed techniques can indeed be applied to protecting processors in harsh environments.

Chapter 2 presents the terminology and general concepts used in this work. Chapter 3 describes existing fault tolerant techniques for processors presented in the literature. Chapter 4 describes the fault tolerant techniques implemented in this work to detect transient faults in processors, from which two are known software-based and three are new hybrid techniques. Chapter 5 presents experimental fault injection campaigns for the implemented fault tolerant techniques. Chapter 6 presents the configuration bitstream fault injection campaign and results. Chapter 7 presents radiation experiments on some of the proposed techniques. Chapter 8 describes future work and concludes the thesis.

#### 2 BACKGROUND

In this chapter, we introduce the main technical terms used in the text, describe the microprocessor architecture used as a case study and discuss background information required for better enlightenment of the topics in this thesis.

#### 2.1 Basic Concepts of Dependable and Secure Computing

This section presents the basic set of definitions that will be used throughout this work. The definitions encompass from defects and upsets that occur in individual logic gates to fault, error and failure.

#### 2.1.1 Defect, Upset and Fault Definitions

Defect or upset is defined as unintended differences between the implemented system and its intended function. It can be commonly a manufacture defect, for example, or transient upsets that happen during some perturbation of the environment.

Fault is then defined as a logic level abstraction of a physical defect or upset. It is used to describe the change in the logic function of a device caused by the defect or upset. Fault can be described as a deviation from the expected behavior of logic. Faults can be transient, intermittent or permanent. Transient faults occur and then disappear. They are transient effects that may occur during the lifetime of the component and it exists for a short period of time. Intermittent faults are characterized by a fault occurring, then vanishing, and then reoccurring and so on. An example of intermittent faults is signal interferences such as cross-section between connection lines. Permanent faults continue to exist in the system until the faulty component is repaired or replaced. They are usually due to manufacturing problems. Some defects or upsets may be masked by the electrical properties of the device and no fault may be observed. Usually when there is a fault in the circuit, there will be an error. However, some faults may be masked by some logic, electric or application and no error will be observed. Error is considered a wrong output signal produced by a defective system.

With nanometer dimension technologies, transistors have become more susceptible to faults caused by radiation interference due to reduced threshold voltages, reduced node capacitances and tightened noise margins (BAUMANN, 2001). Such faults can be caused by energized particles present in space or secondary particles such as alpha particles, generated by the interaction of neutron and materials at ground level (INTERNATIONAL, 2005). Integrated circuits operating in a space environment are sensitive to these particles and can be affected mainly by transient ionization and long term ionizing damage.

In the following, we will discuss the main effects from radiation interference that cause upsets in integrated circuits.

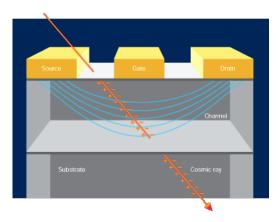

#### 2.1.1.1 Single Event Effect (SEE):

Transient ionization may occur when a single radiation ionizing particle strikes the silicon, creating a transient voltage pulse, or a Single Event Effect (SEE). This effect can be destructive or non-destructive. An example of destructive effect is Single Event Latchup (SEL) that results in a high operating current, above device specifications, that must be corrected by a power reset. Non-destructive effects, also known as soft errors, are transient effects provoked by the interaction of a single energized particle in the PN junction of an off-state transistor (DODD, 2004). When the transient pulse occurs in a memory element, such as a register, it is classified as Single Event Upset (SEU). When the particle hits a combinational element, inducing a pulse in the combinational logic, the upset is classified as Single Event Transient (SET).

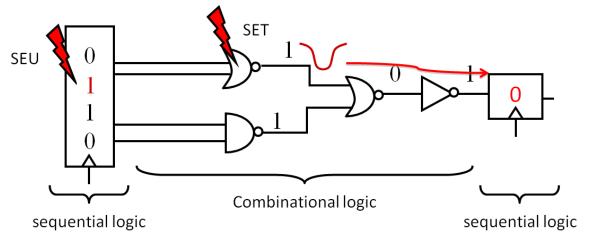

Figure 2.1 shows examples of SEU and SET effects in a circuit. On the left, one can see the SEU effect. A particle, represented by the bolt, hits the sequential logic (which could be seen as a register), changing the store value from "0010" to "0110". This effect directly affects the rest of the circuit, changing the value stored in the sequential logic on the right from "1" to "0". In the middle, one can see a particle hitting the NOR gate and causing a voltage pulse in the combinational logic. When propagated, the pulse hits the sequential latch window on the sequential logic to the right, which registers the incorrect value "0", instead of a "1". Such effects may be masked by the circuit, as discussed in the following subsections.

Figure 2.1: SEU and SET effects on a circuit.

Soft errors can be detected and corrected by the system's logic, meaning that it does not require a hard reset to recover from an error. Sections 7.1.2 and 7.2.2 present neutron irradiation experiments simulating the effect of SEE in Flash-base and SRAM-based FPGAs, while Chapters 5 and 6 present fault injection simulation experiments simulating SEEs at RTL level and in the configuration memory bitstream, respectively. In this thesis, SEUs and SETs will be used to describe transient faults that the techniques presented here can cope with.

#### 2.1.1.2 Total Ionizing Dose (TID):

The long term ionizing damage is also known as Total Ionizing Dose (TID). It is caused by the interaction of energized particles with atoms of the silicon. Photon-induced damage is initiated when Electron-Hole-Pairs (EHP) are generated along the track of secondary electrons emitted via photon-material interactions. EHPs are created from a fraction of the kinetic energy of the incident particles. Some of them are

annihilated due to recombination, but a few remain in the silicon. The remaining EHPs may fall into deep traps in the oxide bulk or near the Si/SiO<sub>2</sub> interface, forming trapped positive charges (BARNABY, 2006), (OLDHAM, 2003). By doing so, TID can affect the system by shifting the threshold voltage, generating leakage current and timing skews and even leading to functional failures. Sections 6.1.2 and 6.2.2 present neutron irradiation experiments using Flash- and SRAM-based FPGAs, respectively, while Section 6.1.1 discusses the effects of TID in SRAM-based FPGAs.

In this thesis, we will refer fault as the single event transient (SET) pulse that may occur in the combinational logic and as the single event upset (SEU) that is the bit-flip that may occur in the memory element.

#### 2.1.2 Error and Failure Definitions

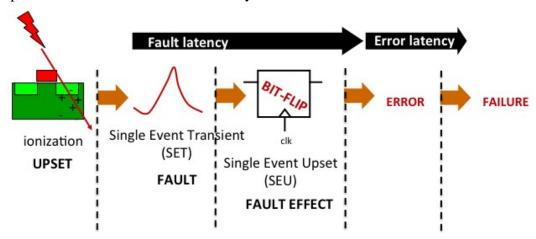

The design of fault tolerant systems consists in preventing a fault to cause an error and consequently a failure in the implemented system. Therefore, there is a cause-effect relationship from the particle hit (fault) to the erroneous result (system failure), as demonstrated in Figure 2.2. In this work, we will use the definition presented in Avizienis (2004).

In order to define error and failure, we first have to define a system. A system is an entity that interacts with other entities, such as other systems, hardware, software, and the physical world. A system follows a functional specification, composed of several different functions. The behavior of a system is what it does to implement its functions and is described by a sequence of states. Finally, the service delivered by a given system is its behavior, as it is perceived by its users.

Failure is the abbreviation of service failure and is defined as a system malfunction, or in other words, when the delivered service deviates from the correct one. The delivered service is considered correct when it is according to the system specification. When the service specification includes a set of several functions, the failure of one or more of the services implementing the functions may lead the system to a degraded mode that still offers a subset of needed services. We define this case as a partial failure.

Error is defined as the deviation in one of the system's sequence of states. Such deviation may compromise a system service, thus leading to a service failure. It is important to note that an error not always leads to a failure.

Figure 2.2: Upset, fault, error and failure chain-effect for SET and SEU.

By defining fault, error and failure, one can notice that a failure can always be seen by the user, since it leads to a system malfunction. Faults can be latent in the circuit until manifested as an error. There are detection techniques that can detect faults and there are techniques that can detect errors.

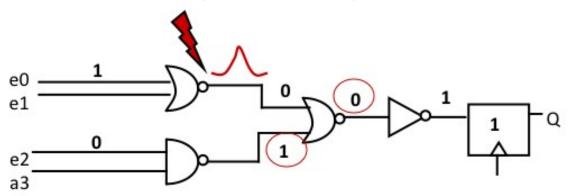

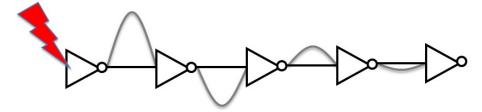

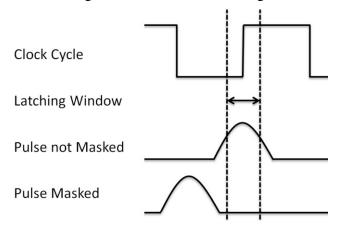

Faults can also be masked by three different ways in the circuit: logical masking, electrical masking and latch window masking. Figures 2.3, 2.4 and 2.5 show each of them, respectively. The logical masking is when the logic of the gate being hit by a fault masks its effect. Figure 2.3 shows a NOR gate being hit by a particle and forcing its output to "1". As one can see the fault cannot propagate through the circuit as the other NOR gate has one of the inputs at value '1', which is dominant forcing the output of that gate to '0'. Electrical masking happens when the propagation of the pulse is weakened by the logic, such as the one shown in Figure 2.4. A NOT gate is hit by a particle, generation a high voltage pulse in its output. When propagating through the other three NOT gates, the pulse is weakened until electrically masked. Latch window masking happens when the pulse does not hit the latching window of a sequential logic. Figure 2.5 shows a clock cycle with its latching window. When the voltage pulse lasts for the whole latching window, the errors are stored in the logic. When the pulse does not last until the latch window (as shown in the bottom), the fault is masked.

Figure 2.3: Logical masking.

Figure 2.4: Electrical masking.

Figure 2.5: Latch window masking.

#### 2.2 MIPS Architecture

The case study microprocessor used in this work is the Microprocessor without Interlocked Pipeline Stages (MIPS). It has a standard processor architecture based on the Reduced Instruction Set Computing (RISC) instruction set. The basic idea behind RISC is that using simple instructions, which enable easier pipelining and larger caches, the performance can be largely boosted. The MIPS architecture can be seen since 1985 in commercial applications, from workstations to Windows CE devices, routers, gateways and PlayStation gaming devices.

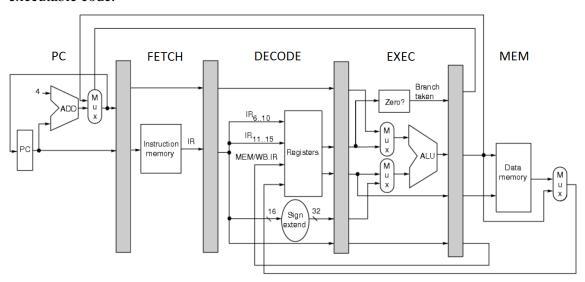

Among the different MIPS architecture processors, there is the miniMIPS (HANGOUT, 2013), which will be used in the work as case-study microprocessor. The miniMIPS is an open source processor that has a reduced instruction set from the original MIPS architecture, with 52 instructions. It is described in the hardware description language, Very-high-speed integrated circuits Hardware Description Language (VHDL). Consequently, it can be logically simulated and it can be synthesized into programmable circuits as FPGAs. The miniMIPS can be implemented using the Harvard memory model, where the program and data memory are separated in two different memories, or the Von Neumann, where program and data memory share the same memory. It has five stages pipeline: Instruction Address Calculation, Instruction Fetch, Instruction Decode, Execution and Memory Access. A model of the miniMIPS pipeline is shown in Figure 2.6.

The miniMIPS microprocessor has thirty-two 32-bit registers in the register bank. It also has a PC with a simplistic logic, since it has fixed size instructions and static branch prediction. Besides the PC, the microprocessor has other special purpose registers, such as the Stack Pointer (SP), Global Pointer (GP), Frame Pointer (FP), Return Register (RA) and Zero (always has the value 0), which can all be found in the register bank. The miniMIPS uses a gcc cross-compiler to translate C code into executable code.

Figure 2.6: Pipeline architecture of the miniMIPS.

The instruction set used by miniMIPS has a fixed size of 32 bits, from which only two have access to the memory: the load instruction and the write instruction. Instructions have a 6-bit opcode and are divided in three classes: type-R, which specify three registers (*rs*, *rt* and *rd*), plus a shift value (*shamt*), and a function field (*funct*), type-I, which specify two registers (*rs* and *rt*) and a 16-bit immediate value, and type-J,

which do not specify any register, only a 26-bit address. Figure 2.7 shows these classes in detail.

| Type | -31- format (bits) |              |        |                | -0-       |           |

|------|--------------------|--------------|--------|----------------|-----------|-----------|

| R    | opcode (6)         | rs (5)       | rt (5) | rd (5)         | shamt (5) | funct (6) |

| I    | opcode (6)         | rs (5)       | rt (5) | immediate (16) |           |           |

| J    | opcode (6)         | address (26) |        |                |           |           |

Table 2.1: MIPS' instruction format

The miniMIPS microprocessor has been chosen as a case-study to this work due to the following reasons. The first one is that it is largely used in the literature (also because it has been in development since 1985). It also has a simple, but efficient, architecture with RISC architecture and a 5-stage pipeline, which follows modern microprocessor models, such as Intel's and ARM's. The miniMIPS version has a very stable version, since 2009, and has been simulated and implemented in various platforms, from FPGAs (both Flash- and SRAM-based) to ASICs. The miniMIPS version used in this work was initially developed by the Ecole Nationale Supérieure d'Electronique et de Radioélectricité de Grenoble (ENSERG), made open source in Hangout (2013), and slightly improved at UFRGS (modules such as the branch prediction, as well as memory controllers).

In this thesis, we use a VHDL model of the mini-MIPS that can be logical simulated and synthesized to ASIC and to programmable platforms as FPGAs.

#### 2.3 SEE in MIPS Processors

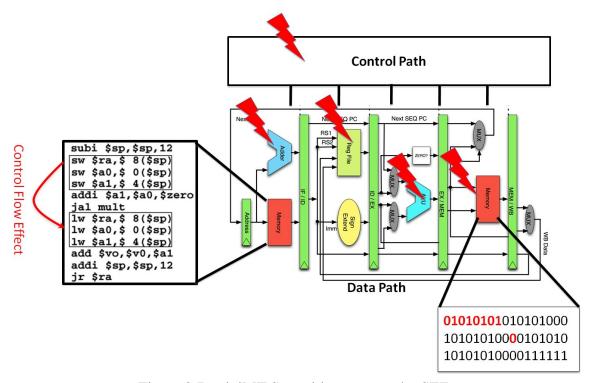

A processor is nothing more than a group of sequential and combinational circuits combined in one component. This combination of different circuits induces processors to be sensitive to different radiation in different areas with different effects. A processor could be roughly divided in five logical groups according to the area (program memory, data memory, register bank, control path, and data path) and in two logical groups when relating to the effect of a fault (data flow and control flow). In the following subsections, we will address how SEEs affect each part of a processor and theirs effects.

#### 2.3.1 SEEs Divided by Sensitive Areas of a Processor

Memories are sequential circuits and therefore very sensitive to SEUs. Due to their regular physical structure, they are optimized to fit in smaller die areas than normal circuits and normally with higher operation frequencies. That means that the radiation effects, such as multiple-bit upset due to a single particle, are intensified in memory components. There are two main types of available memory: flash and SRAM memory. The first one is less sensitive to radiation effects, because it requires a high voltage to be written (change their current state), typically higher than 5V. Its main drawbacks are that it has a finite number of program-erase cycles, meaning that a memory position can only be written around 100,000 times before deteriorating its integrity, and because of the fact that normally the write circuit needs to pump up the voltage in order to reach

the high voltage for writing, and this circuit is sensitive to radiation effects. The SRAM memory is more sensitive to radiation effects, since it operates in normal voltages, but has better performance and power consumption. Besides, it doesn't have the finite number of program-erase cycles.

The memory organization of a processor can be with program and data memory combined in the same memory element (Von Neumann), or separated (Harvard). When separated, the program memory is usually stored in a flash memory and the data memory in an SRAM memory. By doing so, it is possible to reduce the number of upsets in the program memory, while the data memory can be protected by fault tolerant techniques. When sharing the same memory, program and data memories are typically implemented on SRAM memory. Because of the fact that fault tolerance techniques are too expensive to protect the program memory, low-level approaches, such as Error Detection And Correction (EDAC) must be implemented on the memory.

The register bank is mostly a sequential circuit, just like the program and data memory. Because of that, it is very sensitive to SEUs. The register bank can be implemented over an SRAM memory or by using flip-flops. In the first case, the same principles from the data program are applied. In the second case, hardware replication can be used, or even software-based technique to replicate the information stored in the registers. The miniMIPS has thirty-two 32-bit registers, resulting in a total of 1024 bits, which is a big number, when considering radiation effects.

The data path represents the computing circuit of the processor. It is defined as the circuit leading from a stored value (in the memory or in the register bank), through the Arithmetic and Logic Unit (ALU), and back to a store element. It is composed of both combinational and sequential logic, since the data path not only processes data, but also crosses the register barriers from the pipeline stages. Because of that, it is sensitive to SEUs (in the pipeline registers) and SETs (in the computing logic, such as the ALU). The effect of a fault in the data path usually leads to an erroneous result in the end of the computation, but hardly leads to an infinite loop, or a control flow error.

The control path is defined as the decision logic of a processor. It is responsible for calculating the next instruction to be fetched and setting the internal flags, such as to command the ALU to sum or subtract and a branch to be taken or not. The control path is mostly combinational, but since it has to cross the pipeline stages, also has sequential logic. The main difference between the control path and the data path is that an error in the control path leads to control flow errors, such as a branch being taken, when it should not have. Such control flow errors may lead to an erroneous result in the end of the computation.

Figure 2.8 shows a detailed view of the architecture of the miniMIPS with the sensitive areas.

#### 2.3.2 SEEs Divided by Effect on a Processor

Faults can be classified as having data or control flow effect in a processor. Data flow effect is defined as an error in a variable during the computation. It means that the program was correctly executed, but with an erroneous result. An example would be the instruction "Registers  $A = Register\ B + Register\ C$ ", where the value stored in A would be "Register B + (Register C + 1)", due to an SEU that happened in Register C. It means that the processor correctly performed the sum in the ALU, but register C had an incorrect value. Control flow effect is defined as an error in the program execution. It means that the variables were correct, but the computation was incorrect. An example

would be the same instruction, "Registers A = Register B + Register C", where the value store in A would be "Register B - Register C", due to an SET in the ALU that subtracted the registers, instead of summing them.

In order to differentiate a control flow from a data flow error, we check the PC evolution and compare it with a golden module. In case of a mismatch, the fault is classified as a control flow effect. If not, it is classified as a data flow effect. In some cases, a fault with a data flow effect may cause a control flow effect. An example could be an error in a register used to decide whether a branch should be taken or not. In such cases, we consider it as a control flow effect.

The relation between the location of a fault and its effect is not direct. A fault in the register bank not necessarily will have a data flow effect on a processor. Likewise, a fault in the control path will have a control flow effect.

Figure 2.8 shows the difference between a control flow and a data flow effect in a processor. On the left, one can see a control flow effect, where a jump in the program execution causes an error. On the bottom right, one can see the data memory with errors due to a data flow effect fault.

Figure 2.7: miniMIPS sensitive areas under SEE.

#### 2.4 Fault Injection and Testing

Although the effect of faults is increasing at ground level, the rate is not yet sufficient to test fault tolerant techniques. In order to do so, fault emulation and testing is necessary. In this Section, we will go over a few options to do so, such a software fault injection by simulation, fault injection in the FPGA's memory configuration bitstream and irradiation experiments.

#### **2.4.1** Fault Injection by Simulation

Fault injection by simulation can be done by injecting faults at logical or electrical level in commercial simulators, such as ModelSim, from Mentor, or open source simulators, such as Spice. The main idea behind fault injection by simulation is to add interferences to the circuit. The good side about it is that it offers a huge control over the fault injection because it can be clock cycle accurate and therefore big amounts of data as a result. The drawback is that the description of the circuit is needed. If at electrical level, SPICE level description is used. If at logical level, Register Transfer Level (RTL) hardware description level can be used or logical level description. By simulating at RTL hardware description, one can get all values from all the signals implementing the circuit (and memory values) during simulation. Also, it is possible to stop the simulation, access any value inside the circuit, and resume the simulation. The main drawback is that fault injection by simulation requires huge computational power. The injection of 100,000 faults, depending on the abstraction level, may take a few days to finish.

One example was presented in Azambuja (2010b), where a fault injector by logical simulation was introduced. It was implemented in Java and could generate a script to be run in ModelSim. The software had as inputs the list of signals describing the DUT, a definition file containing the description of the faults to be injected and a definition file containing the description of the application, with information such as runtime, correct output values and the memory used by it.

#### 2.4.2 FPGA Memory Configuration Bitstream Fault Injection

In this type of fault injection, the FPGA board is used to replace the simulator. The circuit is implemented using the FPGA, which can emulate the circuit behavior at RTL level. By doing so, instead of using the simulator, a much faster hardware circuit is used. The mechanisms to inject faults and controlling the process are more complex and harder to be implemented, but the speed improvement makes it possible to inject faults in much higher rates than by injecting faults by simulation.

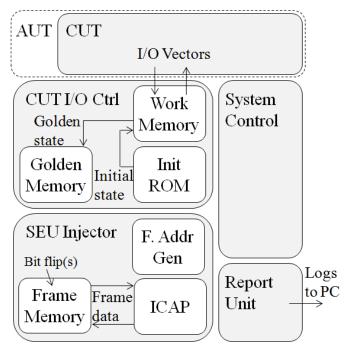

There are mainly two techniques to perform fault injection in FPGA emulation. Using FPGA reconfiguration mechanisms, a fault is injected by loading a new bitstream into the FPGA, which corresponds to the original bitstream with one or more bits flipped (faulty circuit). Partial reconfiguration can be used to reduce the size of the bitstream. In this case, faults are injected in all configuration bits of the FPGA emulating upsets in the bits that control the routing, the user flip-flops and the bits that program the combinational circuits, the well-known lookup tables (LUT). Examples of FPGA fault injectors in the bitstream are FT-Unshades (NAPOLES, 2007) and the one introduced by Nazar (2012b).

Alternatively, circuit instrumentation can be used for fault injection. Circuit instrumentation consists in inserting some hardware modules, also called instruments. They can provide external controllability and observability to inject a fault and observe its effects. Circuit instrumentation is an automatic process that is basically performed by substituting cells of the DUT by their equivalent instrumented cells. Then, the instrumented circuit is prototyped in the FPGA. An example is AMUSE (ENTRENA, 2010).

#### 2.4.3 Irradiation Experiments

The last and closest to real space radiation are irradiation experiments. It is possible, at ground level, to use energized particles to emulate the particles present in space. In order to do so, particles are accelerated and thrown at the circuit under test. Such equipment is called Cyclotron and can be found in different places in the world, using different types of energized particles. They can accelerate heavy ions, protons and neutrons.

Such experiments require a facility that can accelerate particles at high energies, such as 10MeV, with a constant flux of particles. Equipment to measure the flux, time of exposure and energy of particles is also required. Due to the complexity of the experiment, costs for renting the facilities and the danger involved, irradiation experiments can be very expensive. Because of that, irradiation campaigns take a long preparation time, in order to guarantee that the tested circuit will work, as well as the measurements. On the other hand, irradiation experiments are the closest we can get to simulate the space environment at ground level.

Examples of cyclotrons are the heady ions source in Leuven, Belgium, the proton source in Karlsruhe, Germany, and neutron sources in Didcot, United Kingdom, and Los Alamos, USA. For TID testing, a cyclotron can be found in Sao Jose dos Campos, Brazil, with a Cobalt-60 as radioactive source.

# 3 FAULT TOLERANCE TECHNIQUES FOR PROCESSORS

Fault tolerance techniques aiming to detect transient effects can be mainly divided in three broad categories: (1) software-based techniques, (2) hardware-based techniques and (3) hybrid techniques. Fault tolerance techniques can be applied at different levels of implementation, starting from the software level down to the architecture description level, the logical and transistor level, until the layout level. In this thesis, we will focus on techniques applied at software level and hybrid techniques.

Fault tolerance techniques based on software rely on adding extra instructions to the original program code to detect and/or correct faults (GOLOUBEVA, 2003), (OH, 2002b). They may be able to detect faults that affect the data and/or the control flow. Software-based techniques provide high flexibility, low development time and cost, since there is no need to modify the hardware. In addition, new generations of microprocessors that do not have RadHard versions can be used. As a result, aerospace applications can use Commercial Off-The-Shelf (COTS) processors with RadHard software. However, results from random fault injection campaigns have shown the impossibility of software-based techniques alone in achieving complete fault coverage for SEU (BOLCHINI, 2005), (AZAMBUJA, 2011a). This limitation is due to the inability of the software to protect all the possible control flow effects that can occur in the microprocessor.

As a consequence of the redundant instructions inserted in the original program code, software-based techniques have as drawbacks high overheads in program memory footprint and a significant increase in the execution time. The program memory increases due to the additional instructions inserted into the original code, while the data memory increases due to variable replication (in some cases, variables store in the data memory are duplicated). Performance degradation comes from the execution of redundant instructions (GOLOUBEVA, 2003), (OH, 2002).

Hardware-based techniques change the original architecture of the system or its components by adding extra hardware modules. Such techniques must be implemented during the design of the system to be hardened. Therefore, they are not suited for hardening COTS processors or closed Intellectual Property (IP) components. Their main market is Application Specific Integrated Circuits (ASICs) and FPGA based systems. Hardware-based techniques can be intrusive, when they modify the architecture of a processor, or non-intrusive, when they do not modify the processor's architecture, but the system's architecture, through communication buses or by adding extra hardware modules that do not require changes inside the components from the system. The most common non-intrusive technique is called watchdog processor (MAHMOOD, 1988), where a small hardware module uses the access between processor and memory to

check the processor's transitions and then monitor its behavior. Intrusive techniques are mainly related to replicating hardware and adding logical and arithmetic checkers.

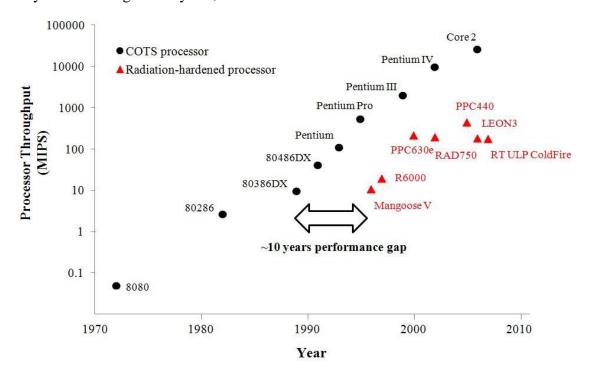

As a consequence, hardware-based techniques can be very expensive duo to changes in the design project, or Non-Recurring Engineering (NRE) costs, development time, verification time, and testing. Also, besides the price in extra die area to fit the redundant hardware modules, it is very common that RadHard processors have lower performances than non-hardened components because they also are fabricated in older technologies compared to the state-of-the-art COTS processors due to the cost of developing new RadHard processors at any new technology release. Figure 3.1 shows a graphic comparing RadHard with COTS processors according to the processor throughput, or Mega (106) Instructions Per Second (MIPS). As one can see, the graphic shows an approximate 10 year gap. It is true that MIPS is not a fair comparison between processors with different architectures (which is the case of the figure), but is still valid to show that there is a gap in performance between COTS and RadHard processors. It may not be as large as 10 years, but it exists.

Figure 3.1: COTS x RadHard processor throughput (KEYS, 2008).

Hardware based techniques can be based on duplication with comparison, EDAC codes to protect registers and some other logical parity techniques to protect the logic. But all of them have some limitation on fault detection coverage. Without duplicating the whole processor, hardware-based techniques cannot achieve full fault detection against SEE, since part of the processor will always be unhardened. Non-intrusive modules, such as watchdogs, also cannot achieve full fault tolerance, since they do not have access to internal information from the microprocessor, like register values, for example. On the other hand, watchdogs and intrusive hardware-based techniques are the only fault tolerant techniques that can detect an infinite loop in an instruction, such as a persistent error, since software-based techniques require that the system is executing its instructions in order to detect an error.

Hybrid techniques combine software-based techniques with hardware-based techniques. The design space for hybrid techniques is quite large, since it multiplies all hardware-based possibilities per the software-based options.

The result from the use of hybrid technique is a high effectiveness, since they can provide high levels of dependability while minimizing the introduced overhead. They also offer low development time (from the software-based techniques) and small performance degradation (from the hardware-based techniques). As drawbacks, they require the application source code (in order to transform it), which is not always available, and require changes, at least, in the system's architecture.

In the following subsections, the main techniques in each category are commented and their strengths and weaknesses concerning this scenario are discussed.

#### 3.1 Software-Based Techniques

Software-based techniques, or Software Implemented Hardware Fault Tolerance (SIHFT) techniques, use the concepts of operation, time and information redundancy to detect the occurrence of faults during program execution. In the past years techniques have been proposed so that can be automatically applied to the source code of a program, reducing significantly the development time and costs (RHOD, 2008). By doing so, the hardening is applied during software construction. The main drawbacks are the performance degradation, due to the extra instructions that will be executed by the processor, slowing the overall application runtime, and the overhead in program memory due to the extra instructions. As far as the fault tolerance is the only concern, the overhead in memory is not an issue, since EDAC techniques can be used to protect the memory. On the other hand, when power is also a concern, memory may become a constraint, since memories are responsible for most of the power dissipation and area within a chip.

Software-based techniques can be divided into two groups, according to their aim at detecting faults: (1) data flow checking techniques, which aim to detect faults affecting the data flow and (2) control flow checking techniques, which aim at detecting faults affecting the program's execution control flow. The first group comprises faults in the data structures of the processor, such as variables, registers and the data memory. Such faults may lead the processor to calculate an incorrect result, but they do not change the program flow. The second group is related to faults that affect the normal execution of a program. Such errors can be a deviation from the normal program flow, which can cause an infinite loop in a subroutine, for example, or even in an instruction. Software-based techniques usually aim to detect only one of these two groups of faults.

Among the most important solutions to detect data flow errors, there are a few techniques that exploit information and operation redundancies, such as Error Detection by Data Diversity and Duplicated Instructions (ED<sup>4</sup>I) (OH, 2002a), the transformation technique proposed in Cheynet (2000) and Variables 1 (VAR1), Variables 2 (VAR2) and Variables 3 (VAR3) techniques proposed in Azambuja (2011b).

ED<sup>4</sup>I consists in modifying the original version of the program by multiplying (or dividing) all variables by a constant value. The replicated version is then executed along with the unmodified program. After executing both versions, their results are compared for consistency (considering the constant value added to the replicated version). An error is detected if a mismatch is found. By running two versions of the code, instead of

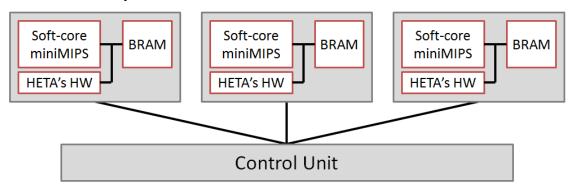

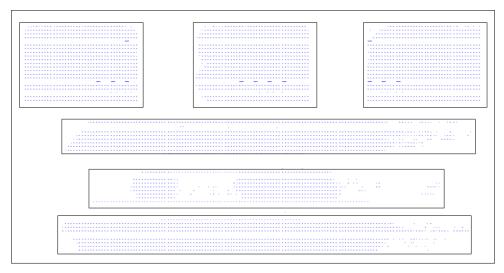

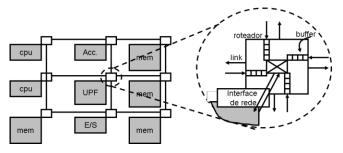

one, and comparing the results, this technique introduces overheads in memory and execution time.