# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

#### FRANCIS BIRCK MOREIRA

# Profiling and Reducing Micro-Architecture Bottlenecks at the Hardware Level

Thesis presented in partial fulfillment of the requirements for the degree of Master of Computer Science

Prof. Dr. Philippe Olivier Alexandre Navaux Advisor

#### CIP - CATALOGING-IN-PUBLICATION

Moreira, Francis Birck

Profiling and Reducing Micro-Architecture Bottlenecks at the Hardware Level / Francis Birck Moreira. – Porto Alegre: PPGC da UFRGS, 2014.

75 f.: il.

Thesis (Master) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação, Porto Alegre, BR–RS, 2014. Advisor: Philippe Olivier Alexandre Navaux.

1. System Architecture. 2. Program Profiling. 3. Hardware Design. I. Navaux, Philippe Olivier Alexandre. II. Título.

#### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof<sup>a</sup>. Carlos Alexandre Neto

Pró-Reitor de Coordenação Acadêmica: Prof. Pedro Cezar Dutra Fonseca Pró-Reitora Adjunta de Pós-Graduação: Prof. Vladimir Pinheiro do Nascimento

Diretor do Instituto de Informática: Prof. Luís da Cunha Lamb

Coordenador do PPGC: Prof. Luigi Carro

Bibliotecário-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

# **ACKNOWLEDGMENTS**

Well, I should as well make this the longest chapter of this dissertation. First, I would like to thank my parents for, well, everything. There is simply too much in this "everything" to be detailed, so let us keep ourselves at that. Second, I must thank Laércio Lima Pilla for enduring my introverted, awkward presence while living together for three and a half years, and for still being by far a better friend than I should hope to have. Thanks to him, I was able to make friends and become somewhat more human again. I'll also use this space to thank Francieli Zanon Boito, his girlfriend, for all the guaca mole, and for becoming a friend with who I am usually able to identify with myself. In this same line, I must thank my cousin Herberth Birck Fröhlich, for living with me for four years and a half, and always being able to make me laugh in the simplest of ways. Thanks to his influence, I became someone who could even, at times, be considered fun and extrovert.

I am grateful to Philippe Olivier Alexandre Navaux, for the opportunity in the first place to engage in research. And when speaking of research, a special acknowledgment must go to Marco Antonio Zanata Alves for his endless help. Ever since I started researching, Marco has mentored me, taught me, laughed with me, corrected me, argued with me, corrected me again, and so on, until I eventually came up with something decent. This work would simply not exist were it not for Marco pushing me into MsC and always being there for me.

There are many more who I should thank, such as everyone in my laboratory, as everyone always helped: Vicente Cruz, Matthias Diener, Eduardo Cruz, Eduardo Roloff and others. I should also thank all the people who eventually became friends with me, and, somehow, changed me and my ways of thinking. Eight years ago I would not find it possible, but this number of friends became large enough that I should not list them here. Thank you all.

#### BLAP: Um Caracterizador de Blocos Básicos de Arquitetura

#### **RESUMO**

A maior parte dos mecanismos em processadores superescalares atuais usam granularidade de instrução para criar ou caracterizar especulações, tais como predição de desvios ou prefetchers. No entanto, muitas das características das instruções podem ser obtidas ao analisar uma granularidade mais grossa, o bloco básico de código, aumentando a quantidade de código coberta em um espaço similar de armazenamento. Adicionalmente, códigos podem ser analisados mais precisamente e prover uma variedade maior de informação ao observar diferentes tipos de instruções e suas relações. Devido a estas vantagens, a análise no nível de blocos pode fornecer mais oportunidades para mecanismos que necessitam desta informação. Por exemplo, é possível integrar informações de desvios mal previstos e acessos a memória para gerar informações mais precisas de quais acessos a memória oferecem melhor desempenho ao serem priorizados.

Nesta tese propomos o Block-Level Architecture Profiler (BLAP) (Block Level Architecture Profiler), um mecanismo em hardware que caracteriza gargalos no nível microarquitetural, tal como loads delinquentes, desvios de difícil previsão e contenção nas unidades funcionais. O BLAP trabalha no nível de bloco básico, apenas detectando e fornecendo informações que podem ser usada para otimizar tais gargalos. Um mecanismo para a remoção de prefetches e uma política de controlador de memória DRAM foram criados para usar a informação criada pelo BLAP e demonstrar seu potencial. Juntos, estes mecanismos são capazes de melhorar o desempenho do sistema em até 17.39% (3.9% em média). Nosso método mostrou também ganhos médios de 13.14% quando avaliado com uma pressão na memória mais alta devido a prefetchers mais agressivos.

Palavras-chave: Arquitetura de Sistemas, Perfil de Programas, Design de Hardware.

## **ABSTRACT**

Most mechanisms in current superscalar processors use instruction granularity information for speculation, such as branch predictors or prefetchers. However, many of these characteristics can be obtained at the basic block level, increasing the amount of code that can be covered while requiring less space to store the data. Moreover, the code can be profiled more accurately and provide a higher variety of information by analyzing different instruction types inside a block. Because of these advantages, block-level analysis can offer more opportunities for mechanisms that use this information. For example, it is possible to integrate information about branch prediction and memory accesses to provide precise information for speculative mechanisms, increasing accuracy and performance.

We propose a BLAP, an online mechanism that profiles bottlenecks at the micro-architectural level, such as delinquent memory loads, hard-to-predict branches and contention for functional units. BLAP works at the basic block level, providing information that can be used to reduce the impact of these bottlenecks. A prefetch dropping mechanism and a memory controller policy were developed to use the profiled information provided by BLAP. Together, these mechanisms are able to improve performance by up to 17.39% (3.90% on average). Our technique showed average gains of 13.14% when evaluated under high memory pressure due to highly aggressive prefetch.

**Keywords:** System Architecture, Program Profiling, Hardware Design.

# **LIST OF FIGURES**

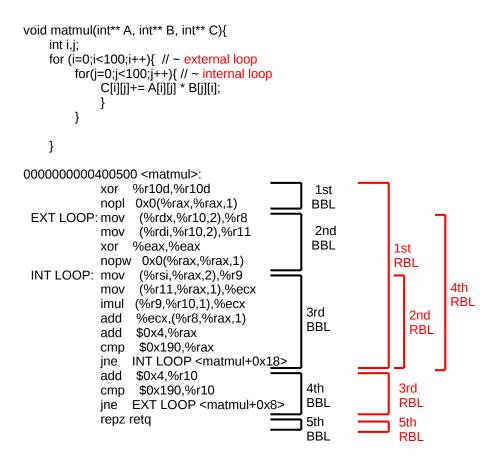

| 2.1 | Example of code presenting the classical definition of basic blocks (BBL) and our relaxed definition (RBL)                                                                                            | 24 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

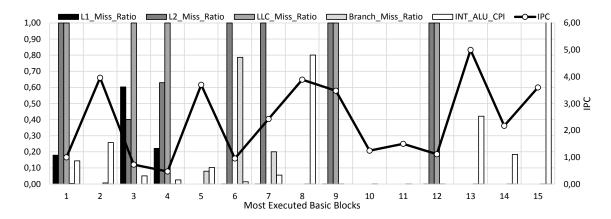

| 2.2 | Statistics for the most relevant blocks of the <i>libquantum</i> benchmark, and their relationship with performance measured in IPC                                                                   | 25 |

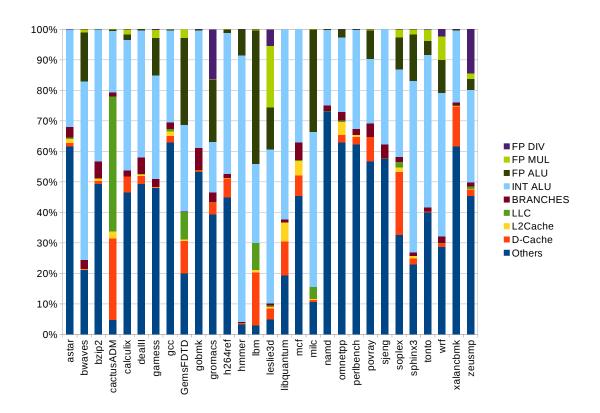

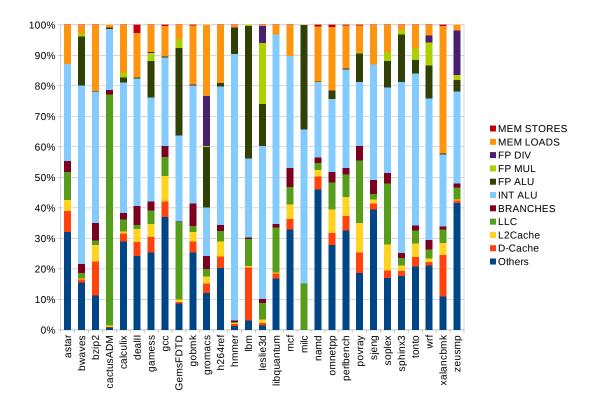

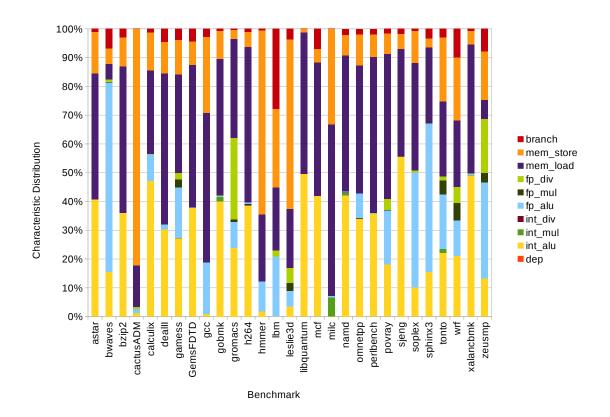

| 4.1 | Basic block characteristic distribution. Every block receives only one characteristic, the most relevant one according to the hardware counters                                                       | 36 |

| 4.2 | Basic block characteristic distribution. Every block receives only one characteristic, the most relevant one according to the hardware counters. Now statistics are properly attributed to each block | 37 |

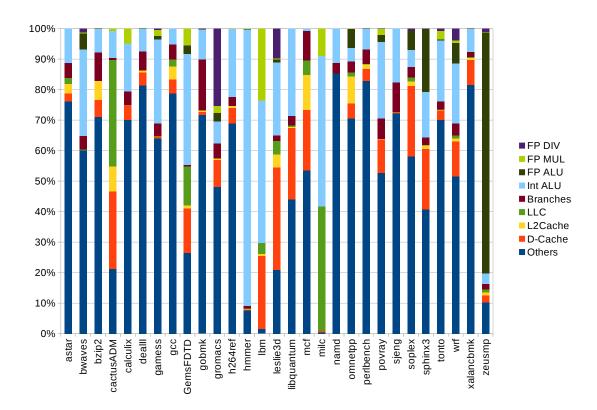

| 4.3 | Basic block characteristic distribution. Every block receives one characteristic, the most relevant one according to the sum of register true dependencies delays per type                            | 39 |

| 4.4 | Basic block characteristic distribution. Every block receives only one characteristic, the most relevant one according to commit stage delays                                                         | 40 |

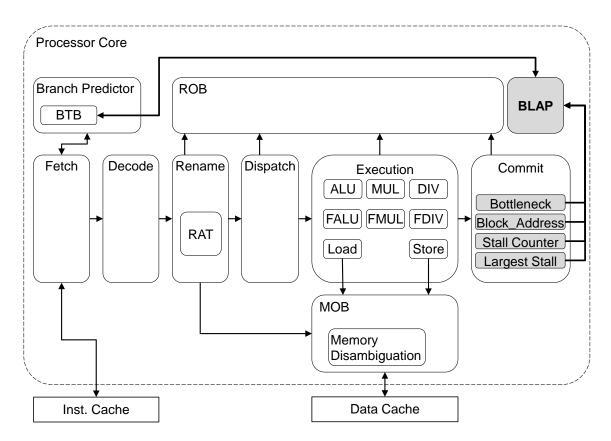

| 5.1 | Overview of the operation of BLAP in a superscalar processor. Parts in gray represent BLAP's modifications or additions to the processor.                                                             | 43 |

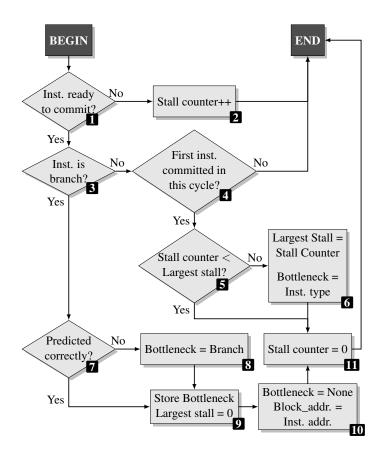

| 5.2 | Flow chart of additional commit stage events                                                                                                                                                          | 45 |

| 5.3 | Modeled performance improvements correctly predicting 25%, 50%, 75% and 100% of branch instructions in blocks characterized as "Brch".                                                                | 50 |

| 5.4 | Modeled performance improvements solving 25%, 50%, 75% and 100% of the load instructions of blocks characterized as "memory                                                                           |    |

| 5.5 | load"                                                                                                                                                                                                 | 50 |

|     | 100% of the load instructions of blocks characterized as "memory load", when the mechanism <i>only</i> characterizes loads                                                                            | 51 |

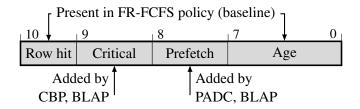

| 6.1 | Request selection logic for different memory controller mechanisms.                                                                                                                                   | 56 |

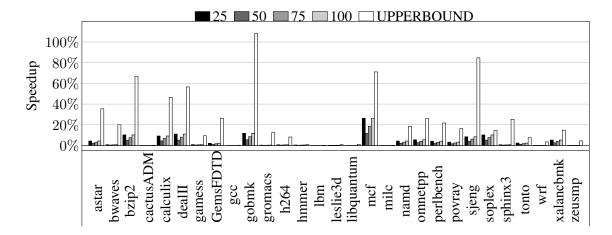

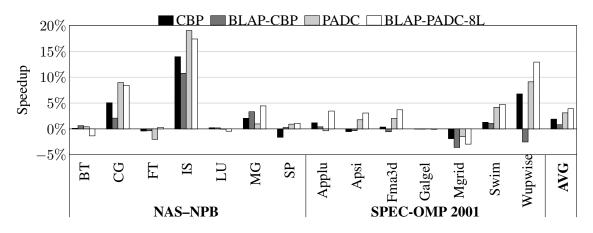

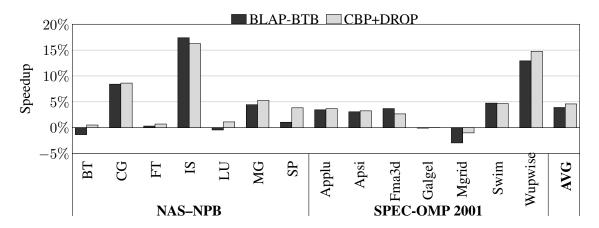

| 7.1 | Performance results for NAS-NPB and SPEC-OMP2001, relative to FR-FCFS baseline                                                                                                                        | 57 |

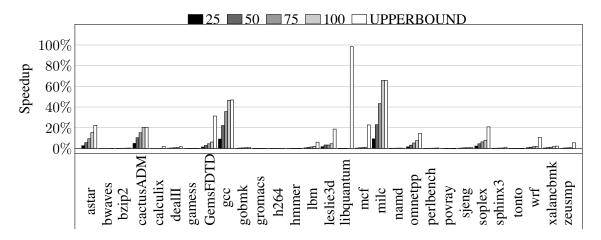

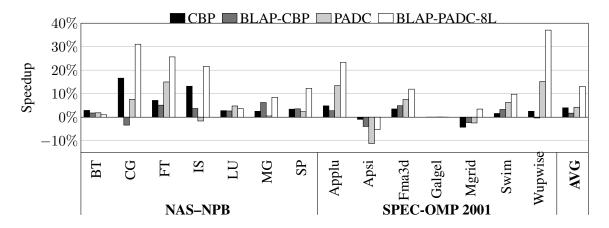

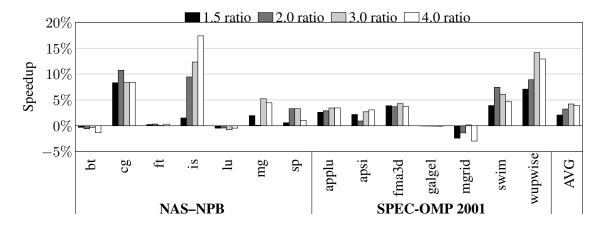

| 7.2 | Performance results for NAS-NPB and SPEC-OMP2001 with increased aggressivity prefetcher, relative to FR-FCFS baseline                                                                                 | 58 |

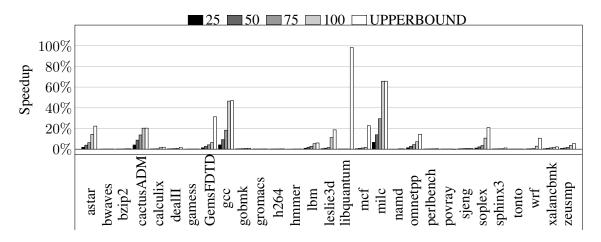

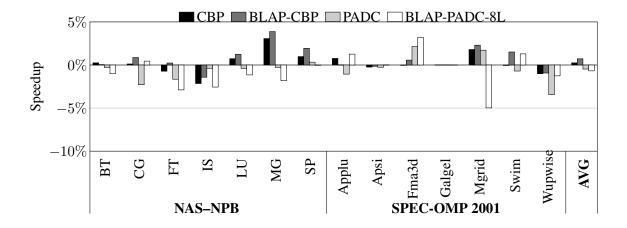

| 7.3 | Performance results for NAS-NPB and SPEC-OMP2001 with conservative aggressivity prefetcher, relative to FR-FCFS baseline                                                                              | 59 |

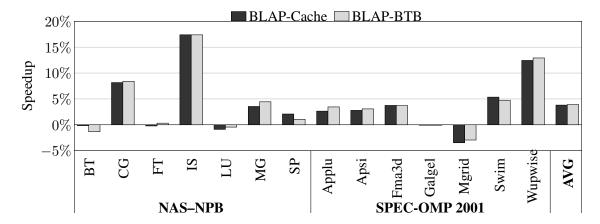

| 7.4 | Performance results comparison between using the branch target buffer and a large cache, relative to FR-FCFS baseline.                                                                                | 60 |

| 7.5 | Performance results comparison using the same memory controller,     |    |

|-----|----------------------------------------------------------------------|----|

|     | but different informations, from BLAP and CBP respectively, relative |    |

|     | to FR-FCFS baseline                                                  | 60 |

| 7.6 | Mechanism performance, normalized to baseline configurations with    |    |

|     | different memory latencies                                           | 61 |

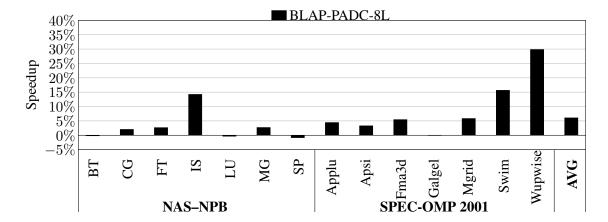

| 7.7 | Mechanism performance with BLAP-PADC-8L using Branch Target          |    |

|     | Buffer (BTB), normalized to baseline configurations with 16 cores    | 62 |

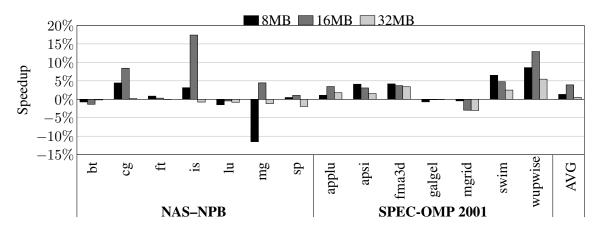

| 7.8 | Mechanism performance, normalized to baseline configurations with    |    |

|     | different memory latencies                                           | 62 |

# **LIST OF TABLES**

| 2.1 | Pearson moment-product correlation coefficients of absolute statistics per block and performance in IPC for sequential benchmarks | 27 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Pearson moment-product correlation coefficients of absolute statistics per block and performance in IPC for parallel benchmarks   |    |

| 5.1 | Hardware Costs of BLAP                                                                                                            | 49 |

| 6.1 | Baseline simulated architectural parameters                                                                                       | 54 |

# LIST OF ABBREVIATIONS AND ACRONYMS

BBL Basic Block

BBV Basic Block Vector

BHT Branch History Table

BLAP Block Level Architectural Profiler

BTB Branch Target Buffer

CBP Criticality Binary Prediction

CPU Core Processing Unit

FR-FCFSFirst Row - First Come First Serve

GPU Graphic Processing Unit

ILP Instruction-Level Parallelism

IPC Instructions per Cycle

ISA Instruction Set Architecture

LLC Last Level Cache

LRU Least Recently Used

MOB Memory Reorder Buffer

MSHR Miss Status Handle Register

OBP Online Behavior Predictor

PADC Prefetch-Aware DRAM Controller

RBL Relaxed Block

ROB Reorder Buffer

TLP Thread-Level Parallelism

x86 Intel's ISA x86

# **CONTENTS**

| 1 II<br>1.1<br>1.2<br>1.3           | NTRODUCTION                                                                                                                                                                           | 19<br>19<br>20<br>21                         |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 2 B<br>2.1<br>2.2<br>2.3            | Basic Block and Relaxed Blocks                                                                                                                                                        | 23<br>23<br>24<br>25                         |

| 3 A<br>3.1<br>3.2<br>3.3<br>3.4     | ANALYSIS OF THE STATE-OF-THE-ART  Code Behavior Detection and Use                                                                                                                     | 29<br>30<br>31<br>31<br>33                   |

| 4 B<br>4.1<br>4.2<br>4.3<br>4.4     | Introduction                                                                                                                                                                          | 35<br>35<br>35<br>37<br>38                   |

| 5 B 5.1 5.2 5.3 5.4 5.4.1 5.4.2 5.5 | BLOCK LEVEL ARCHITECTURAL PROFILER  Behavior Detection  Behavior Storage  Behavior Labeling  Critical Path Implications  Profile Stability  Hardware Costs  Evaluating BLAP Precision | 43<br>43<br>46<br>46<br>47<br>47<br>48<br>48 |

| 6 E<br>6.1<br>6.2                   | SVALUATION METHODOLOGY                                                                                                                                                                |                                              |

| 7 E<br>7.1<br>7.2<br>7.2.1          | Mechanism Exploration                                                                                                                                                                 | 57<br>57<br>60<br>61                         |

| 7.2.2             | Cores Number                                 | 61             |

|-------------------|----------------------------------------------|----------------|

| 7.2.3             | Cache Size                                   | 61             |

| 8 C<br>8.1<br>8.2 | CONCLUSIONS AND FUTURE WORK                  | 63<br>63<br>64 |

| REFE              | ERENCES                                      | 65             |

| 9 A<br>9.1<br>9.2 | APPENDIX - PORTUGUESE SUMMARY                | 69<br>69<br>70 |

| 9.3               | BLAP: Proposta de Detecção de Blocos Básicos | 72             |

| 9.3.1             | Detecção                                     | 72             |

| 9.3.2             | Armazenamento                                | 73             |

| 9.3.3             | Rotulamento                                  | 73             |

| 9.3.4             | Implicações no caminho Crítico               | 73             |

| 9.3.5             | Custos de Hardware                           | 73             |

| 9.4               | Resultados                                   | 74             |

| 9.5               | Conclusões                                   | 75             |

## 1 INTRODUCTION

Currently, industry has reached the limits of Instruction Level Parallelism (ILP) for the available computing system models, which feature superscalar out-of-order execution. Extensive research has enabled compilers to optimize a program's fundamental building blocks (also known as basic blocks) for specific architectures, mostly through profiling with specific data inputs. However, a dissonance is still present in the code optimization, as compilers cannot leverage the hardware state information of different architectures, which leads to the concepts present in this thesis.

#### 1.1 Introduction

Characterization of basic blocks is an important, recurring technique, used for automatic optimization of several types. Software tools such as Vtune (REINDERS, 2005) allow manual analysis to detect performance improvement opportunities, such as rewriting code to avoid high cache miss rates for specific basic blocks, known as hotspots. The basic block granularity is especially useful (COCKE, 1970) as basic blocks represent portions of code that always end with conditional or unconditional branch instructions. A program's execution path is therefore defined by basic block execution sequences, enabling a program phase characterization and dynamic optimization. A recent example is the work of Kambadur et al. (KAMBADUR; TANG; KIM, 2012), which uses basic blocks to characterize the thread-level parallelism of an application in its different phases.

General-purpose processor designs (YUFFE et al., 2011) only collect information at the instruction level. Although several research papers used basic block analysis, most did so using a software approach, even for hardware adaptations (PANAIT; SASTURKAR; WONG, 2004; RATANAWORABHAN; BURTSCHER, 2008). One of the few techniques that actually performed basic block analysis at the hardware level was the rePlay framework (PATEL; LUMETTA, 2001). It analyzes the code to perform dynamic code optimization which is stored in a trace cache for future use, although no bottleneck profiling is performed. Another example is (CLARK et al., 2007), which uses post-commit analysis to make dynamic translation from scalar instructions to SIMD instructions (given offline step to convert SIMD to scalar instructions), although using a single function (detecting branch-and-link instructions) as scope to detect scalar instructions for translation.

Block profiling is usually done in software due to the high complexity of detailed profiling and analysis required. Nevertheless, profiling in hardware is interesting as it can leverage current hardware state information to efficiently generate relevant information of a program's execution, requiring no pre-analysis or source code modification. Recent trends in hardware development also point to the relation of instructions within blocks for performance improvements (AFRAM; ZENG; GHOSE, 2013; FAROOQ; KHUBAIB;

JOHN, 2013). The main limitation of basic block analysis is on what kind of analysis and characterization can be performed in hardware. It must be relevant enough to ensure performance improvements, and simple enough for effective trade-off.

With the mainstream acceptance of prefetchers (ZHUANG; LEE, 2007) and the recent inclusion of the memory controller into the processor chip (RIXNER et al., 2000), there is space for research using basic block information to provide information to such mechanisms. Sherwood et al. (2001) shows that there is a strong correlation between the characteristics found in the most relevant blocks of each application and the overall application characteristic. Based on this correlation, a basic block classification has the potential to provide relevant information regarding the application's performance. As basic block granularity automatically adapts to program phase changes, there is no need for additional control and time to adapt to changing phases. Additionally, the granularity allows for higher coverage with less hardware, opposite to designing with instruction granularity, such as in Ghose et al. (2013). Finally, any ideas that have been successfully implemented using simple basic block classification in software could be enabled to be implemented in hardware.

#### 1.2 Contributions

In this thesis, we propose BLAP. BLAP characterizes basic blocks according to the most relevant delays occurring per block, thus allowing improvement of future executions of these blocks. BLAP has several advantages over other mechanisms. It adapts to program phase changes, as it dynamically keeps track of basic blocks. It requires less storage than mechanisms which use instruction granularity, as we aggregate the behavior per block. We are able to use the BTB to efficiently store this information, as it retains the initial address of each block targeted by a branch. BLAP is capable of detecting different types of performance-related issues within a block, thus being able to provide information to a wide range of mechanisms.

In order to show the potential of BLAP, we explore the use of its profiling information to design an improved memory controller. Compared with the instruction-granularity information used by Ghose et al. (2013) and Lee et al. (2008), our mechanism achieves better performance with a scalable hardware overhead. Moreover, BLAP's basic implementation can be extended to provide detailed information regarding a wide range of bottlenecks at low hardware costs. To the best of our knowledge, no previous research has profiled basic blocks in hardware. Moreover, we present an integration between BLAP and other mechanisms, in order to show the usefulness of the profiled information. The main contributions of this thesis are the following:

**Characterization Mechanism:** We propose BLAP, an efficient detection mechanism capable of characterizing applications at the basic block level during their execution. The mechanism's highlights are the ability to store information using a BTB extension, therefore adding minimal overhead. It detects a varied amount of characteristics, and provides information to all instructions fetched in each core.

**Mechanisms Integration:** We integrated BLAP with mechanisms that improve memory performance by adapting them to use the profile information and by creating a new mechanism that relies on BLAP.

**New Memory controller:** In order to adapt existing concepts in a format that could use BLAP's information, we have created a new, aggressive prefetch-dropping memory controller.

## 1.3 Organization

The main objective of this work is to propose and study a hardware mechanism capable of detecting the blocks that build a program and characterizing their behavior. Such characterization can make it possible to improve the processor performance through its use by other mechanisms, such as prefetchers or priority policies. In Chapter 3, we cite the related work done in the area of basic block classification, and recent works that are used for concept implementation and performance comparison. In Chapter 4, we overview several methods to characterize blocks accordingly to their characteristics. In Chapter 5, the mechanism is detailed, in order to estimate the area overhead and feasibility of implementation. In Chapter 6, we describe the simulation environment and methodology, presenting preliminary results showing BLAP's potential. Chapter 7 details related work on memory access, how they can be adapted to use BLAP, and compares all the implementations. Chapter 8 finishes the thesis with our conclusions and suggestions for future work.

## 2 BACKGROUND

In this section, we explore the relationship between blocks and performance. We actually use a relaxed definition of a basic block (ANSALONI et al., 2013; COCKE, 1970; HUANG; LILJA, 2000) for our mechanism.

#### 2.1 Basic Block and Relaxed Blocks

A basic block is a stretch of code with a single point of entry and a single point of exit. Thus, every basic block ends either with a branch instruction, or before an instruction targeted by a branch. This enables mechanisms based on basic blocks to automatically adapt to the program phase, as a program's phase is characterized by the blocks being used (RATANAWORABHAN; BURTSCHER, 2008). However, our low overhead hardware implementation allows multiple entry points, as it is not possible to efficiently detect the beginning of a block which was not targeted by a branch without changing the instruction set functionality. In Figure 2.1, we can see an example of what might happen during a code execution.

In Figure 2.1, we can see a simple matrix multiplication with fixed dimensions, both in C code as well as in AT&T assembly, for visualization of how a basic block is seen by the hardware. The assembly is composed of 5 real basic blocks: initialization (1st BBL), external loop - internal loop initialization (2nd BBL), internal loop (3rd BBL), external loop - increment and check (4th BBL) and return (5th BBL). These are divided in the real basic block, as for example, the first instruction of 2nd BBL is the target of the *jne* 400508 < matmul + 0x8 > instruction in address 400540, and being a new point of entry, must denote the end of 1st BBL and the beginning of a new BBL, 2nd BBL.

In the rightmost brackets in red, we can see how a hardware mechanism can detect a relaxed definition of basic blocks, noted by *RBL*. As the hardware does not know about new entry points ahead of time, it will detect the relaxed blocks in the following order. First, it will aggregate BBLs 1st, 2nd, and 3rd in the 1st RBL. Once instruction *jne 400518* <*matmul+0x18>* at address 400533 jumps back to the beginning of the 3rd BBL, we will detect the 2nd RBL, which is the internal loop. This allows a relaxed definition to still obtain frequently repeated loop code. Once the instruction fails to jump and execution reaches the end of the first external loop, we will detect the 3rd RBL, similar to the 4th BBL. However, we will now create a 4th RBL that aggregates the 2nd BBL and 3rd BBL, as we cannot see the entry point between them. Finally, once the external loop is over, the 5th BBL is equal to the 5th RBL, ending the function.

Although there is an overlap between the characteristics detected for each code portion, as the information is to be stored into the BTB, we have precise information for each block following a branch. In the example, the 1st RBL is only going to execute once,

Figure 2.1: Example of code presenting the classical definition of basic blocks (BBL) and our relaxed definition (RBL)

while the 4th RBL is going to execute 100 times, and the 2nd RBL, the code that is truly repetitive, will execute 10000 times.

A design issue to be considered when extending the BTB is that it only records information for blocks that begin after a taken branch. Given that the behavior to be exploited is usually repetitive, this is normally not a problem, as as the repetition of blocks begins after taken branches. Since we cannot recognize branch targets unless their respective branch occurred, we are breaking the definition of basic block, as we will likely record blocks with overlapping information. These blocks will aggregate behavior from all the instructions of the few, smaller real basic blocks inside them, and thus will not be characterized separately. However, the smaller basic blocks will be correctly characterized once they are targeted by a branch, thus obtaining their correct starting address. As in most cases smaller blocks represent conditions inside loops, they will be executed enough times to be characterized. If they do not, then they are likely not relevant.

#### 2.2 Basic Block Characteristics and Performance

To motivate the behavior that can be observed per block and their correlation with performance, in Figure 2.2 we can see the behavior detection of the benchmark *libquantum* of the SPEC-CPU 2006 workload obtained through simulation. In the Figure 2.2, there are five bars showing the statistics of each block. These statistics all refer to the instructions inside the block (e.g. the branch misprediction happened for the branch within the block). The blocks are ordered in terms of number of executions, from most executed (1)

Figure 2.2: Statistics for the most relevant blocks of the *libquantum* benchmark, and their relationship with performance measured in IPC

to least executed (15).

The characteristics of the block clearly affect the performance on the majority of the blocks. As examples of blocks without characteristics, there are blocks 10 and 11. Likely, these blocks have different performances due to different code dependencies. In blocks 2, 8, 13, 14, and 15, contention in the ALU integer unit is present. Although contention should represent a problem for performance, we can notice that the blocks with this contention present higher performance than the average. This happens due to integer operations being simple and fast, and as the modeled architecture has 3 integer units, if there is contention, then it means that at least 3 instructions are being finished each cycle.

Blocks 3 and 4 show the worst performance. They also show bars representing a high data rate miss in all cache levels. In block 6, a similar effect occurs with branch mispredictions. If the architecture presented a better prefetcher, reducing the data miss rate, we could obtain improved performance for blocks 1, 3, 4 and 12. Alternatively, a prefetcher could use information regarding the poor performance of these blocks in order to prioritize them. This is the main motivation for our work, which is to improve or enable other mechanisms through observation of the block behavior.

To further motivate the behavior that can be observed per block and their correlation with performance, we used statistical correlation.

#### 2.3 Correlation between Characteristics and Performance

To demonstrate the behavior that can be observed for our relaxed block definition and its correlation with performance, we statistically correlated execution events (such as branch mispredictions) with performance, using the Pearson Moment-Product Correlation Coefficient. This is a generalization of the linear regression model, used to observe how closely two different sets of data correlate. The resulting coefficient lies between -1 and 1. The higher the absolute value the stronger is the correlation between the parameters. If the coefficient is negative, the parameters are inversely correlated (i.e. the value of the parameters influence each other, but when one increases, the other decreases). If it is positive, they are correlated, both values increase or decrease together. The closer to 0, the smaller is the correlation between parameters.

The details of the configuration and benchmarks used can be found in Section 6. To calculate the correlation, we generated a profile of the execution. This profile contained the most important processor events relevant for execution performance (WALL, 1993)

for each block: L1 data cache misses, L2 cache misses, Last-Level Cache (LLC) misses, branch mispredictions, number of floating point arithmetic-logic instructions, and number of floating point division instructions. Whenever a basic block finished executing, we recorded the number of instructions the block contained and how many cycles it took to execute, in order to measure its performance. We then recorded how many of the events happened during the execution of that block. For fourteen parallel application from the NAS-NPB and SPEC-OMP2001 benchmark suites, each correlation coefficient was calculated considering blocks from all the threads together.

The correlation results are shown in 2.1 and Tables 2.2. The Tables show sequential benchmarks (SPEC-CPU2006) and parallel benchmarks (NAS-NPB and SPEC-OMP2001), respectively. The highest correlation coefficients for each benchmark are marked in bold. Looking at the cache misses correlation coefficients, we can observe a diminishing correlation as we go from smaller and faster to slower and larger caches. Although a miss in the LLC means a main memory access, which is likely to stall the processor, the number of accesses the LLC receives is small, because most accesses are serviced by higher level caches. Therefore, although a single LLC miss has a considerable impact on the final performance, it happens much less frequently than L1 and L2 misses, such that it does not correlate highly with the performance differences between blocks. We have noticed that, due to the large number of varied block executions, all correlation values are low. Were we to first partition the blocks into specific block types and run correlations individually, we would find much higher values. However, this analysis still serves the purpose of showing, for the entire program, which is the most relevant bottleneck of the program. A low correlation value will simply mean that the problem does not present many gains for the entire benchmark execution, but if we solved the specific problem of each block, we would certainly improve the overall execution.

Although a branch misprediction in a pipeline with 15 stages results in flush latency and a large number of stalled cycles, for parallel benchmarks, the other instruction types correlations seem to significantly diminish the branch instruction correlation. We found this low correlation coefficient happens due to a low branch misprediction rate, smaller than 1% in most of the parallel benchmarks. In the sequential benchmarks, we can observe higher branch misprediction correlation coefficient values for several benchmarks, denoting that the small memory pressure of a single thread alleviates the issues with memory for many benchmarks allowing branch misprediction to have a larger impact on program performance.

Floating points instructions per block correlate well on a few benchmarks. For parallel benchmarks, we can observe that for Apsi and Mgrid, floating point ALU instruction count is the statistic that correlates the most with degraded performance. In sequential benchmarks, the same happens for astar and hmmer.

Following this analysis, we seek to improve the memory access bottleneck. Therefore, in the next Chapter, we overview the related work that led us into our research and the state of the art regarding use of block profiling and memory controller improvements.

Table 2.1: Pearson moment-product correlation coefficients of absolute statistics per block and performance in IPC for sequential benchmarks.

| Benchmark  | L1D Misses | L2<br>Misses | LLC<br>Misses | Branch<br>Mispred. | FP ALU<br>Inst. | FP DIV<br>Inst. |

|------------|------------|--------------|---------------|--------------------|-----------------|-----------------|

| astar      | -0.185     | -0.186       | -0.066        | -0.209             | -0.003          | 0.000           |

| bwaves     | -0.026     | -0.006       | -0.002        | -0.015             | -0.168          | -0.088          |

| bzip2      | -0.073     | -0.117       | -0.011        | -0.308             | 0.000           | 0.000           |

| cactusADM  | -0.349     | -0.452       | -0.230        | 0.038              | -0.036          | 0.063           |

| calculix   | -0.092     | -0.051       | -0.016        | -0.253             | 0.096           | -0.010          |

| dealII     | -0.090     | -0.073       | -0.014        | -0.158             | 0.036           | 0.000           |

| gamess     | -0.052     | -0.015       | -0.004        | -0.076             | -0.062          | -0.025          |

| gcc        | -0.371     | -0.341       | -0.157        | -0.011             | -0.225          | -0.135          |

| GemsFDTD   | -0.187     | -0.216       | -0.089        | -0.185             | 0.118           | 0.000           |

| gobmk      | -0.009     | -0.015       | -0.011        | -0.343             | -0.006          | -0.003          |

| gromacs    | -0.223     | -0.068       | -0.008        | -0.201             | 0.001           | -0.333          |

| h264       | -0.065     | -0.063       | -0.013        | -0.129             | 0.006           | -0.002          |

| hmmer      | -0.077     | -0.058       | -0.006        | -0.048             | -0.359          | 0.002           |

| lbm        | -0.200     | -0.651       | -0.148        | -0.031             | -0.219          | -0.087          |

| leslie3d   | -0.413     | -0.356       | -0.143        | -0.049             | -0.174          | -0.325          |

| libquantum | -0.517     | -0.374       | -0.078        | -0.143             | 0.000           | 0.000           |

| mcf        | -0.374     | -0.309       | -0.064        | -0.305             | 0.000           | 0.000           |

| milc       | -0.312     | -0.299       | -0.245        | -0.004             | 0.028           | 0.000           |

| namd       | -0.007     | -0.019       | -0.002        | -0.068             | -0.033          | -0.016          |

| omnetpp    | -0.224     | -0.236       | -0.051        | -0.151             | -0.132          | -0.002          |

| perlbench  | -0.140     | -0.095       | -0.010        | -0.108             | 0.002           | -0.001          |

| povray     | -0.102     | -0.022       | -0.003        | -0.128             | -0.029          | -0.113          |

| sjeng      | -0.056     | -0.051       | -0.018        | -0.235             | 0.000           | 0.000           |

| soplex     | -0.242     | -0.204       | -0.072        | -0.170             | -0.066          | -0.152          |

| sphinx3    | -0.270     | -0.177       | -0.028        | -0.023             | 0.097           | -0.035          |

| tonto      | -0.041     | -0.035       | -0.003        | -0.086             | -0.085          | -0.041          |

| wrf        | -0.161     | -0.128       | -0.056        | -0.031             | -0.141          | -0.114          |

| xalancbmk  | -0.254     | -0.087       | -0.033        | -0.113             | -0.025          | -0.005          |

| zeusmp     | -0.116     | -0.110       | -0.034        | -0.090             | -0.112          | -0.164          |

Table 2.2: Pearson moment-product correlation coefficients of absolute statistics per block and performance in IPC for parallel benchmarks.

| В             | enchmark | L1D<br>Misses | L2<br>Misses | LLC<br>Misses | Branch<br>Mis-<br>pred. | FP ALU<br>Inst. | FP DIV<br>Inst. |

|---------------|----------|---------------|--------------|---------------|-------------------------|-----------------|-----------------|

| NAS-NPB       | BT       | -0.28         | -0.34        | -0.39         | -0.01                   | -0.14           | -0.15           |

|               | CG       | -0.63         | -0.44        | -0.48         | 0.00                    | 0.13            | 0.13            |

|               | FT       | -0.51         | -0.31        | -0.25         | -0.05                   | 0.04            | 0.05            |

|               | IS       | -0.18         | -0.16        | -0.16         | -0.01                   | -0.00           | 0.00            |

|               | LU       | 0.04          | 0.02         | -0.14         | 0.01                    | 0.11            | 0.10            |

|               | MG       | -0.34         | -0.28        | -0.28         | -0.02                   | 0.06            | -0.23           |

|               | SP       | -0.40         | -0.36        | -0.31         | -0.05                   | -0.27           | -0.34           |

| SPEC-OMP 2001 | Applu    | -0.45         | -0.45        | -0.39         | -0.01                   | 0.26            | 0.00            |

|               | Apsi     | -0.13         | -0.14        | -0.14         | 0.01                    | -0.27           | -0.26           |

|               | Fma3d    | -0.27         | -0.33        | -0.33         | -0.03                   | -0.00           | 0.12            |

|               | Galgel   | -0.18         | -0.21        | -0.08         | -0.01                   | 0.21            | 0.25            |

|               | Mgrid    | -0.30         | -0.29        | -0.28         | -0.01                   | -0.49           | -0.45           |

|               | Swim     | -0.69         | -0.60        | -0.59         | -0.01                   | -0.40           | -0.32           |

|               | Wupwise  | -0.58         | -0.50        | -0.47         | -0.00                   | 0.01            | -0.06           |

## 3 ANALYSIS OF THE STATE-OF-THE-ART

The common goal of basic block profiling is to enhance code execution by obtaining knowledge about its behavior in its different phases. Most approaches are done in software, through use of instrumentation tools to obtain profile information during the program's execution (LUK et al., 2005). Such method has an overhead due to additional instructions, and the very pollution generated by this overhead in registers and caches reduces the reliability of performance measurements done by such approach. Nevertheless, this approach can still correctly approximate the behavior of program phases. Its main problem is the need to execute a program multiple times with the same input, which makes any improvement achieved for single executions negligible.

State-of-the-art compilers can also use input sets to simulate a program execution and obtain profiling information, thus optimizing the code after some executions (LATTNER; ADVE, 2004). This approach can obtain performance improvements given a training input that is generic enough, i.e. which fully explores the code's execution paths. However, the bias over the necessarily exploring all execution paths may degrade performance for several input loads which only stress specific program execution paths. Alas, the need for recompilation among different architectures and systems always counts as a major factor in industry decisions to adopt a new technology.

Finally, the option of detecting basic blocks in hardware has intuitively been considered difficult to use. Most of the works which seek behavior characterization and reuse in hardware use coarser granularity for the sets of instructions analyzed in order to achieve performance gains. Such coarse granularity misses on opportunities for performance gain due to loss of specific blocks behavior information that is averaged among several blocks (PADMANABHA et al., 2013). This argument can also be used against basic blocks: it is a coarse granularity when compared to instructions. Nevertheless, individual instruction types are quite different, and cannot be compared with each other for any other purpose than hardware design analysis. Moreover, basic blocks have been proven to be a better granularity mostly due to code layout pattern detection (COCKE, 1970). As basic blocks identify the code units of repetition due to their direct relation with branches, they are intuitively good for the behavior analysis of different execution path phases.

The remainder of this section describes the works which serve as base to understand the potential usage of the mechanism, and then exemplifies hardware design mechanisms that can be improved with it.

#### 3.1 Code Behavior Detection and Use

Sherwood et al. (2001) is the precursor to SimPoints (HAMERLY et al., 2005) and other works, such as Pinpoints (PATIL et al., 2004). The authors characterize the behavior of entire programs based on the analysis of basic block execution distribution. The concept of a *Basic Block Vector* (BBV) is first introduced to characterize a program. A basic block vector contains execution counts for all basic blocks, normalized by the total number of basic block executions. Therefore, the vector gives the execution frequency of each basic block proportionally to the entire program slice observed. The authors are then able to compare the behavior of executions of different sizes, for different inputs. In order to do so, a BBV comparison method is created by treating each BBV as a fingerprint of the observed program slice. To compare them, a BBV is subtracted from another, and all absolute values are summed, generating a value between zero and two. Zero means the BBVs are identical, as there was no difference between their fingerprints, while two means the BBVs do not execute any block in common.

With this comparison, the authors show a variety of features of their technique. They are able to identify the different phases of a program, such as the initialization phase of a program, due to the considerable difference between the BBV obtained for the first 100 million instructions and the BBV of the entire program. With the BBV of the entire program, they are also able to identify or create BBVs that have identical fingerprints, but a much smaller number of instructions. They show that the behavior of selected program slices with similar BBV are practically the same, with statistics pertaining to cache misses, branch mispredictions and overall type of instructions executed differing at most by 3%. This was further improved in SimPoints, which can use the Pin instrumentation tool (LUK et al., 2005) to build simulation points based on this technique. The importance of these techniques for our work is that our methodology uses Pinpoints to simulate programs in a reasonable time. Sherwood's work also shows that by improving only the performance of the repetitive blocks that define the entire program behavior, we can achieve overall improved performance.

The rePLay framework (PATEL; LUMETTA, 2001) has a similar concept to our work. In this work, the authors use an extended definition of a block called a frame. A frame aggregates several basic blocks, as it ignores unconditional branches, and promotes easily predictable branches into assertions (PATEL; EVERS; PATT, 1998). They also provide a scheme to replay a frame in case an assertion fires, which signals a misprediction of an easily predictable branch which was promoted. In this way, they achieve a coarse granularity, enabling dynamic code optimizations during execution, and alongside the rollback mechanism, the opportunity for aggressive speculative techniques, such as value prediction and value reuse (PILLA et al., 2004). Although the framework is described, it is not explored in the paper. Frames intuitively have few opportunities for value reuse and value prediction, as they are coarse enough to capture several executions of loops, and seem to represent distinct phases of data progression in programs. The authors only show manual optimizations of single frame examples, and do not show any mechanism that can make automatic run time optimizations using the frames collected. In our work, we characterize application behavior on a finer granularity, so we can better inform other mechanisms.

The recent work of Kambadur et al (2012) also uses a simple profiling method called Parallel Basic Block Vectors. It can be seen as an extension of Sherwood's work, as now each entry in the BBV contains n positions, each representing the degree of parallelism at which the basic block is executed. When a basic block is executed, the number of parallel

threads is observed and used as index to increment the appropriate part of the entry. This allows the authors to identify how frequently every basic block execute at each parallelism level, clearly identifying sequential and parallel code blocks. They also identify the most critical regions of code in terms of performance. Several scenarios are illustrated to show how this analysis can be applied, such as serial and parallel application partitioning, or analysis of program features by degree of parallelism and parallelism hotspots.

#### 3.2 Basic Block and Phases Use Cases

In Panait et al (2004), the authors statically classify load instructions based on several heuristics. These include operations used for calculation of target address, registers used in address calculation and execution frequency. The work defines the *delinquency* of each load, pinpointing the instructions that are responsible for most of the data cache misses during execution. With static analysis, the authors are able to select only 10% of the total load instructions as responsible for more than 90% of the level 1 data cache misses. Using basic block analysis alongside the compiler, they reduce this number to 1.3% of all load instructions, responsible for 82% of all level 1 data cache misses. In this way, the efficiency of basic block analysis is shown by identifying blocks with loads that do not fit prefetch patterns or have overall low temporal or spatial locality.

Ratanaworabhan et al (2008) presents a new concept to detect program phase transition. Their phase transition is defined by critical basic block transitions. A critical basic block transition occurs when a rarely executed basic block is executed, signaling the change of behavior in a branch instruction. This usually signals a change of program phase, and thus different behavior. By observing critical basic block transitions, the work aggregates code into ten million instruction phases, and offers insight into different methods to detect critical block transitions, reusing the concept of BBV from Sherwood et al. to find the rarely executed basic blocks. It then uses phase information to adapt cache sizes to each phase. This shows the effectiveness of dynamic cache sizes when compared to optimal static size selection, as it reduces average cache size by 15%.

The work of Padmanabha et al (2013) proposes a predictive trace-based switching controller, which predicts an upcoming phase change in a program and preemptively migrates execution to an appropriate core in order to reduce energy consumption. In reality, the work uses a single heterogeneous core composed of a single frontend and 2 back ends. Each back end is based on the different organizations found in ARM's big.LITTLE architecture (PETER GREENHALGH, 2011), and what the authors describe as execution migration is actually selecting which back end will be used. Therefore, the only overhead is the communication of the register file's contents for correct context execution. With such a low overhead, migrations can be done often. Thereby the authors explore fine switching granularities, where they observe that these finer granularities offer more opportunities for energy savings. At the granularity of 300 instruction, the average time spent on the Little back end constitutes 28% of the execution, while targeting maximum performance degradation of 5%. This leads to an increased energy savings of 15% in comparison to running only on Big, representing claims of 60% improvement over existing techniques.

# 3.3 Hardware Design Opportunities

The main targets of current processor design research are branch prediction and memory access, as these issues are responsible for the greatest bottlenecks in modern super-

scalar designs. Although many other design points are becoming increasingly important, such as energy consumption, and others have been explored to some extent, such as value reuse (PILLA et al., 2004), branch prediction and memory access remain constant problems across decades. Therefore, it is of our interest to obtain information on the state-of-the-art mechanisms used to treat or alleviate these issues. We focus on memory access as it has the highest correlation with performance.

One of the methods available to improve memory access is prefetching. Prefetching is a technique that improves memory access by predicting future accesses and making requests ahead of time, generating better memory throughput and increased instructions per cycle due to lower average memory wait time. However, not all memory patterns are easily detectable, making the technique sometimes useless. Moreover, the technique can degrade performance by incorrectly predicting a pattern and generating useless prefetches. This results in cache pollution and unnecessarily increased memory pressure. To alleviate these aspects, Srinath et al (2007) create a mechanism to control prefetching aggressiveness. Every cache line is increased by 2 bits to characterize which lines were prefetched from main memory and which lines were touched. At the eviction of a line, if a line was prefetched and not touched, it falls under the case of pollution. With heuristics and mechanisms to insert prefetches on the last positions of a LRU policy (JALEEL et al., 2010), the authors propose tests using an adaptive stream prefetcher (HUR; LIN, 2006), which uses feedback from the cache lines to change the prefetcher aggressiveness configuration. Let it be noted that the technique can be used for any kind of prefetcher based on configurable parameters. In these results, performance of benchmarks from the SPEC-CPU 2000 benchmark suite increases by 6.5% on average when compared to the best performing static prefetcher configuration, while consuming 18.7% less memory bandwidth. Compared to a prefetcher using the same bandwidth, feedback directed prefetching provides 13.6% improved performance.

The work is superseded by Lee et al. (2008), who implements the same methodology to obtain prefetcher pollution data, but to avoid the slow pace of aggressiveness change, instead drops prefetches when detecting high pollution levels. This technique, known as Prefetch-Aware DRAM Controller (PADC), is able to obtain better improvements with a specific memory controller policy, with smaller hardware overhead. We used Lee's paper concepts to create a new memory controller using BLAP's information, and so we offer greater detail on their implementation in Chapter 6.

These works, along with Zhuang et al. (2007), ensure that no prefetcher ever degrades performance by reducing aggressiveness, even disabling all prefetch requests if necessary. These papers are crucial for prefetchers, as the increased memory pressure coming from multiple cores has been a main point of consideration regarding whether prefetchers should or should not be used. Generally, their performance improvement outweighs their performance degradation, even for large numbers of cores. These works use an interval to detect prefetching pattern, a fixed period of 8192 level 2 cache useful block evictions which is detected by the access bit of the lines. This is a valid approach to detect a program's memory phase change, but it does not detect a program's execution phase change.

In Ghose et al. (2013), the authors work on a memory controller policy capable of prioritizing critical loads. To identify critical loads, they develop a mechanism that stores information over the stalled cycles each load instruction generated in the commit stage. This characterizes how long each load takes, and with this several policies are possible. They explore binary policy, giving priority to loads which are currently stalling the commit stage and using a prediction table to give priority to loads that have stalled it before.

Moreover, they explore the usage of the cycles that a load stalls by creating four more policies. As we used this work for comparison, more details are given in Chapter 6.

The work's idea is solid, but the methodology shows some flaws. Prioritizing loads ahead of time ends up giving priority to loads that are already in the cache, or are easily predicted by prefetcher. Moreover, the aliasing of load PC addresses in the tagless table can lead to prioritization of irrelevant loads.

The authors used a processor frequency predicted to be present in the future, with a 4.27 Ghz frequency, while modeling a current DDR3 main memory at 1066 Mhz frequency. Therefore the memory pressure becomes much higher and the relevance of reordering loads in the memory controller also higher than it should be. We consider this to be a valid assumption, as the access times of memory accesses are likely to increase in the future. We use this idea in our work, as it can be implemented in coarse granularity by giving priority to all loads in a block. Additionally, we keep track of block behavior and ensure that a block has stable behavior before changing priorities. We also make a deeper study around the benefits of such approach in the presence of prefetchers.

## 3.4 Summary of the State of Art

Overall, most of the existing works in hardware to improve performance or energy consumption use coarse granularity phases. They do this given several constraints of their own implementations, such as migration overhead or detection overhead.

However, most works do not take into account that the branch target buffer structure contains information regarding all branch targets. These are the instructions that begin basic blocks. Detecting basic block execution is possible given relaxation of the definitions, and as seen in the related work, it should provide good granularity to detect program behavior.

Following the work of (PATEL; LUMETTA, 2001), we take a new direction by using the behavior detected to adapt existing hardware mechanisms, namely (GHOSE; LEE; MARTÍNEZ, 2013) and (LEE et al., 2008). In the next Chapter, we present all detection mechanisms that led from related work to the final mechanism, presented in Chapter 5.

## 4 BLOCK CHARACTERIZATION

Basic block profiling is a frequently used technique in compiler and post-compilation steps. It aims to characterize basic blocks in some aspect (LATTNER; ADVE, 2004). In this Chapter, we explore methods to perform block profiling at the hardware level.

#### 4.1 Introduction

Our proposed method to perform block profiling in hardware builds an evolving profile of a program's code. Thereby, it is possible to improve frequently used blocks by characterizing them and improving their performance in future executions. In the following sections, the profiles generated by the mechanism in this work record the types of instructions that are responsible for the largest delays in each block. However, the basic concept of the mechanism can be extended to implement a variety of techniques based on block profiling. In this section, we base ourselves on the related work to discuss common techniques to characterize code behavior, and how we can adapt these techniques to the basic block case. This section shows a progression towards accuracy and simplicity, in order to achieve a useful technique which could be implemented in hardware. This section only cares about behavior detection. Behavior storage and its information use are explored in later sections.

#### 4.2 Hardware Counter Classification

Currently, Intel processors come with hardware counters available to enable performance profiling and analysis, used by tools such as Vtune (REINDERS, 2005). These counters keep track of several events during processor execution, such as cache misses, operations per type, to the point of detailing even bus transactions. Such statistics intuitively correlate to performance, and they can be used to provide insight on what issues might result in suboptimal performance of a code snippet.

However, to do so at the basic block level raises a few issues. The first issue is identifying and delimiting blocks. As our relaxed block definition uses branches and jumps as blocks' last instructions, we can identify branch and jump commits to mark block endings. We then store the hardware counter values and reset them, so they start collecting information for the next block. If we assign a weight to each counter in order to properly characterize each instruction given its performance overhead, we get the block distribution seen in Figure 4.1. The figure shows the execution of a simulation that prints, at every block end, which weighted characteristic had the highest value for that block. We assigned the following weights for hardware counters: 8 for instruction cache misses, 8

for data cache misses, 32 for level 2 cache misses, 200 for last level cache misses and 120 for branch mispredictions. All functional unit stalls were already counted as cycles, and thus had weight 1. In all of our tests we eliminated statistics that did not show to have a relevant number of occurrences or delays, such as integer multiplication, integer division, and instruction cache misses. Their occurrences accounted for less than 1% of all blocks. "Others" denote none of the registered characteristics were found in the block, so any stalls result from register real dependencies or were simply not detected.

Figure 4.1: Basic block characteristic distribution. Every block receives only one characteristic, the most relevant one according to the hardware counters

These results show us the second issue. As we are using superscalar architectures, the branch commit contains all the information of what was processed since the previous branch commit; the in-order commit stage ensures that. However, since new instructions do not wait for a branch commit to happen, they can enter execution after branch "A", change some of the statistics (such as data cache accesses), and be stored as information of the block that finishes at the branch "A", i.e. the *previous* block information. Therefore, we now have information that does not belong to this block, resulting in its pollution. This also means the next block will be lacking this information, and it may also grab information from the block ahead of it. We denote this phenomenon as *information skew*.

This would not be a problem if all statistics collected to characterize a block were obtained within two branch instruction commits. As the skew happens for every block, we would have a fixed skew for every block, and a fixed characteristic skew. However, statistics such as level 1 data cache miss and last level cache miss take different times to be recorded. This generates variable pollution for each block, which is the main challenge in implementing a real mechanism.

To avoid this, in our simulation we created a table to store statistics per in-flight branch. Whenever a new statistic must be recorded, we search the reorder buffer for the first conditional branch instruction that would come after it, and increment the statistics for that branch entry. Then, when the branch commits, we get the statistics from this table, ensuring no information skew occurs. Due to the large size and difficulty of hardware implementation, we believe that creating such a table in hardware and checking for ordering would offer a mediocre tradeoff. Nevertheless, the characteristics of this distribution are shown in Figure 4.2.

Figure 4.2: Basic block characteristic distribution. Every block receives only one characteristic, the most relevant one according to the hardware counters. Now statistics are properly attributed to each block.

Although there were several changes in the characteristics attributed to each block, the main problem with both classifications is that many blocks do not receive any characterization. In order to achieve characterization for more blocks, we must use information of greater detail, which led us to seek the latencies generated by register dependencies.

# 4.3 Register Dependence Latency Classification

The basic, initial number of delayed cycles caused by a single instruction A is the one measured by how many cycles another instruction B, which is dependent of instruction A's result, was delayed. To implement this mechanism we observe the latencies generated by each register dependence (we do not take into account structural hazards, i.e. two unrelated instructions which need the same functional unit). A table is kept with an entry for each characteristic. When an instruction is blocked due to register dependencies, we

count how many cycles the instruction takes to receive the register value which it needs. The instruction A, which was using the register, is accused of generating the delay, and thus the characteristic of such instruction type's entry is incremented by that number of cycles.

Although the accused instruction A might have suffered with delays from other instruction C, instruction C would also be accused for such delays, as it was stalling A first. This warrants we find the culprits for the largest stalls in the critical path of the application. We can observe the resulting basic block distribution in Figure 4.3. As we do not know the level of cache that was able to provide the correct line for loads and writes (considering caches with write-allocate policy), we measure the number of cycles delayed and classify them into the three levels. If the delay is smaller than the minimum number of cycles necessary to access to the level 1 cache, we classify the delays as memory loads and memory stores, representing latencies on the load-store queue.

An odd observation is that memory stores are taking up a portion of the benchmarks, such as in the *dealII* benchmark. In Sandy Bridge's pipeline, once a write has been sent to memory, there is no need to wait for registers, as they do not store values at any register. After some research, we found out that Pin considers the *CALL* instruction as store, as the instruction writes values to the stack and increases its size. However, it also generates register dependence for the PC and stack pointer registers, therefore generating dependence for other instructions. Even with the prediction of the PC value in the branch target buffer, instructions which require the stack pointer, such as the instructions that must obtain the parameters of the function in the stack, would theoretically still be stalled. To remediate this, Intel uses a "Stack Engine" in the front-end, which keeps a copy of the stack pointer updated to free dependencies for every *CALL*, *RET*, *POP*, *PUSH*, and other instructions which implicitly use the stack pointer.

This mechanism was modeled in simulation, but deemed too complex for hardware implementation, as in hardware there is no efficient way to trace back which instruction generated the delay. Even if we built such a mechanism, to assign instruction types to registers in order to check for dependence delays, this would likely generate larger delays per stages in the middle of the back end, which is not desirable.

Alas, the number of blocks characterized as *ALU integer* is large likely due to minimal stalls characterizing the block, covering the area that was presented as *others* or *none* in the previous distributions. Nevertheless, integer operations do not cause any real harm to performance, as the unit's latency is minimal. Even though register dependencies delay instructions, the overall throughput can still be high, as long as the hindrances do not stall the commit stage, which takes us to the next idea.

## 4.4 Stall Commit Classification

Rather than checking for indirect and intermediary effects on performance, a simpler way is to observe the delays generated by the instructions at the final point: the commit stage. If an instruction delays the commit stage, it means that it will affect throughput, as the commit stage is in-order, and being blocked by one instruction means blocking all instructions that could be committed in the same cycle. This is a rather simple way to observe delays, as we do not see the indirect delays that register dependencies generate. If instruction B was greatly delayed by instruction A, instruction B will stall the commit stage and we will accuse its delay. However, our intuition is that instruction A will likely stall the commit stage before instruction B does, and for a longer time. The resulting

Figure 4.3: Basic block characteristic distribution. Every block receives one characteristic, the most relevant one according to the sum of register true dependencies delays per type

block characteristic distribution can be seen in Figure 4.4.

As seen in this Chapter, obtaining detailed hardware counter statistics per block during execution is a complex matter. As we aim to aggregate behavior and uniquely identify blocks, within a reduced storage size, using statistics gives us three challenges. First, a statistic must show a direct impact on performance. While cache misses are intuitively correct in expressing delinquent loads (PANAIT; SASTURKAR; WONG, 2004), current architectures are usually tolerant to L1D misses due to high ILP, which provides enough computation to overlap the cache access latency. That is, in most cases, L1D misses stall the processor for a small number of cycles.

Second, different hardware events cannot be directly compared. When a level 1 data cache miss occurs, we know that it will take at least the level 1 data cache access time plus level 2 cache access time for a request to be serviced, but we do not know the state of the Miss-Status Handling Registers (MSHR) of each cache, or even if the cache line will be serviced in level 2. Even such a large latency could be hidden in the presence of a branch misprediction. If we want to find which was the most relevant bottleneck in a block, we cannot compare such a value directly to the delay generated by a floating point division unit, as we do not know whether there is any instruction that actually depends on the unit result, or even if it is actually going to stall the commit stage.

Third, hardware counters cannot be used directly to profile the block. As blocks of instruction are committed, we do not know which statistics belong to which block. As an example, if instructions from a block have executed, are ready to commit, and we

Figure 4.4: Basic block characteristic distribution. Every block receives only one characteristic, the most relevant one according to commit stage delays

obtained all their statistics, once the last instruction from the block commits, we should reset the counters to gather statistics for the next block. However, instructions from the next block making accesses to the data cache or committing floating point instructions might be altering these statistics, preventing us to accurately evaluate a block.

To overcome these challenges, we opted to exploit the commit stage. Instructions only cause bottlenecks or delay the pipeline if eventually this leads to the commit stage being blocked. So, in order to compare instruction delays, we only look at how many cycles each instruction stalled the commit stage. This technique will obtain information that directly impacts performance (first issue), since we are looking at the commit stage stalls. We can directly compare the number of commit stage stalled cycles between instructions, since they are measured in terms of cycles (second issue). Finally, as we do not use hardware counters, the statistics are not skewed (third issue).

Overall, this is the better choice because it is simple to implement in hardware. As the operation code of the instructions can be obtained from their reorder buffer entries when they are being retired, no critical path increase is generated, as a simple wire extension can give us those signals. All the needed hardware for detection can be counted in a few registers to detect how many cycles each instruction stalls the commit stage. When using register dependencies or isolated hardware counters, we need intermediary storage to isolate the information per block, which is expensive with large reorder buffers and high ILP, making these techniques unfeasible. Furthermore, this technique only measures meaningful stalled cycles, as the throughput of the processor is usually observed by the number of instructions retired in the commit stage every cycle.

In summary, a potential hardware mechanism that identifies the bottlenecks using the commit stage stalls has new relevant applications and requirements. It must be able to meaningfully characterize blocks, requiring small logic overhead. This is possible by recording the stall of the instructions at the head of the Reorder Buffer (ROB), and detecting branch instructions to observe block boundaries. It is also required to effectively store this profile. Therefore, the information for each block should be kept to a minimum. Additionally, the size of the information has an impact as we need to communicate the profile to different mechanisms. Finally, the mechanism should be able to provide multiple characterizations, so multiple mechanisms can use the profile. In accordance with the correlation results and the characteristic distribution, we chose to record the following characteristics: *None* to denote that the block presents no problems, *Brch* to denote branches hard to predict, *Mem* to denote commit stalls due to loads and *FP* to denote commit stalls due to any floating point unit. We have chosen to use the *Brch* characteristic due to more tests which show the relevance of the characteristic influence in block executions.

## 5 BLOCK LEVEL ARCHITECTURAL PROFILER

In this Chapter, we show the detailed implementation of BLAP(Block Level Architectural Profiler) in hardware. BLAP consists of three parts: Behavior Detection, Behavior Labeling and Behavior Storage. After explaining each, we discuss potential critical path implications and how they can be avoided. We then list the hardware overhead costs these three stages and describe additions to further improve the profile information.

## **5.1** Behavior Detection

Modern superscalar processors use an in-order commit stage, so they can avoid memory access speculation (CRISTAL et al., 2004). This enables reading the decoded in-order stream of instructions of a program by looking at the retired instructions each cycle. With the instructions decoded, we can observe which instructions are conditional branches,

Figure 5.1: Overview of the operation of BLAP in a superscalar processor. Parts in gray represent BLAP's modifications or additions to the processor.

thus allowing us to detect ends of basic blocks. Whenever the branch target buffer is accessed by a branch, we can observe the beginning of a new basic block as branch targets are stored in the BTB.

To better illustrate the hardware needed for our mechanism, in Figure 5.1 we can see a common abstraction of a modern superscalar design with our mechanism additions in gray. The fetch, decode, rename and commit stages are all in-order. For every branch instruction, the fetch stage consults the branch predictor to speculate on the correct path to follow. This forces the fetch stage to be in-order, as the instruction path is conditioned by the branches present in the instruction flow.

The following substages which compose the decode and rename stages all perform simple, single-cycle operations on the instructions. The rename stage is in-order, as it needs to be aware of instruction order to keep track of real dependencies and eliminate false dependencies. The rename stage also passes instructions to the reorder buffer, while it keeps track of the register dependencies between these instructions. Thereby, the reorder buffer keeps all ordered instruction information, so the out-of-order stages can execute correctly.

The next stage, dispatch, begins out-of-order execution. It will dispatch any instruction to an available functional unit of the instruction type. Given different program behaviors, this means that a busy functional unit will delay its instruction type, while another instruction can be scheduled to another functional unit type in that cycle, thus resulting in the reorder of the instructions. Moreover, different functional units take different times to execute, which also affects the execution order.

The commit stage is responsible for retiring instructions from the reorder buffer in order. This stage is executed in order to ensure *precise exceptions*, which means that whenever an instruction generates an exception, every instruction previous to it must have finished, and nothing after it can have finished execution. In this way the software state is not changed by incorrect execution of instructions that could be affected by the instruction that generated an exception.

Further, an in-order commit stage also simplifies the rollback mechanism necessary for branch mispredictions when using speculative execution. As an example, let's consider that a branch prediction speculative path contains an instruction II that changes a register value. With an in-order commit stage, whenever a branch's prediction is detected as a misprediction, the necessary steps to continue the correct execution are to flush the reorder buffer positions that come after the branch, flush all in-order stages of the front end (fetch, decode and rename), and then start fetching instructions from the correct datapath. In this way, the II instruction will be flushed, and since it never committed its results, register values would not be changed. If this instruction was allowed to commit its results before the branch, a misprediction would imply that the branch would need to keep every register state, so it would know which registers were changed by the speculated instruction and would be able to recover their values.

In Figure 5.2, we show a flowchart of the additional events needed to implement our detection mechanism in the commit stage of a superscalar processor. BLAP implementation requires an in-order commit stage, which is widely used in current commercial processors. The Figure accounts events that must happen for all instructions, but a real implementation will only look for the reorder buffer head instruction and the first branch instruction it finds, as can be seen in the sequence of conditionals 3 and 4.

In the commit stage, we must check whether the oldest instruction, at the reorder buffer head, is ready to commit **1**. Whenever an instruction stalls the commit, a *Stall*

Figure 5.2: Flow chart of additional commit stage events.