### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

### ATILA BOHLKE VASCONCELOS

# Modelo de Performance para Código com Desvios de Execução em Hardware Gráfico

Dissertação apresentada como requisito parcial para a obtenção do grau de Mestre em Ciência da Computação

Prof. Dr. João Luiz Dihl Comba Orientador

Prof. Dr. Rui Manuel Ribeiro de Bastos Co-orientador

### CIP - CATALOGAÇÃO NA PUBLICAÇÃO

Vasconcelos, Atila Bohlke

Modelo de Performance para Código com Desvios de Execução em Hardware Gráfico / Atila Bohlke Vasconcelos – Porto Alegre: Programa de Pós-Graduação em Computação, 2006. 63 f.:il.

Dissertação (mestrado) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação. Porto Alegre, BR – RS, 2006. Orientador: João Luiz Dihl Comba; Coorientador: Rui Manuel Ribeiro de Bastos.

1.Modelo de Performance. 2.Processamento Gráfico. 3.Hardware Gráfico. I. Comba, João Luiz Dihl. II. Bastos, Rui Emanuel Ribeiro de. III. Título.

#### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. José Carlos Ferraz Hennemann Vice-Reitor: Prof. Pedro Cezar Dutra Fonseca

Pró-Reitora de Pós-Graduação: Profa. Valquiria Linck Bassani

Diretor do Instituto de Informática: Prof. Philippe Olivier Alexandre Navaux

Coordenador do PPGC: Prof. Flávio Rech Wagner

Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

# Sumário

| LISTA DE FIGURAS                                        | 4  |

|---------------------------------------------------------|----|

| LISTA DE TABELAS                                        | 5  |

| RESUMO                                                  | 6  |

| 1 INTRODUÇÃO                                            |    |

| 2 HARDWARE GRÁFICO                                      | 12 |

| 2.1 Arquitetura da GPU                                  | 12 |

| 2.2 Processador de Fragmentos                           |    |

| 3 MEDIÇÃO DE PERFORMANCE                                |    |

| 3.1 Métrica de Performance                              |    |

| 3.1.1 Estágios do processamento gráfico                 | 22 |

| 3.2 Estratégia Adotada para Medição de Performance      |    |

| 3.3 Precisão das Medidas                                |    |

| 3.4 Características de Performance                      | 28 |

| 4 MODELO DE PERFORMANCE                                 | 31 |

| 4.1 Características do Modelo                           | 33 |

| 4.2 Proposição do Modelo                                |    |

| 4.2.1 Modelo Básico.                                    | 35 |

| 4.2.2 Desvios de fluxo                                  | 37 |

| 4.2.3 Tamanho de triângulos                             | 38 |

| 4.2.4 Blocos de coerência                               | 39 |

| 4.2.5 Acesso a texturas.                                | 39 |

| 4.3 Simulador de Performance                            | 40 |

| 4.4 Características e Limitações                        | 41 |

| 5 VALIDAÇÃO E VERIFICAÇÃO DO MODELO                     | 43 |

| 5.1 Validação do Simulador com Experimentos Sintéticos  | 43 |

| 5.1.1 Simulador Básico                                  | 46 |

| 5.1.2 Tamanho de Triângulos                             | 49 |

| 5.1.3 Blocos de Coerência                               | 50 |

| 5.1.4 Acesso a Texturas Independentes                   | 53 |

| 5.1.5 Acesso a Texturas Dependentes                     |    |

| 5.1.6 Discussão sobre os experimentos de validação      | 59 |

| 5.2 Verificação do Simulador com Uma Aplicação Complexa |    |

| 5.2.1 Sistema Massa-Mola: Problema                      |    |

| 5.2.2 Sistema Massa-Mola: Simulador                     |    |

| 5.3 Resultados da Validação e da Verificação            |    |

| 6 CONCLUSÕES                                            | 66 |

| REFERÊNCIAS                                             | 69 |

# **LISTA DE FIGURAS**

| Figura 2.1:    | Diagrama de blocos da arquitetura simplificada de um PC (extraído de GPU       |            |

|----------------|--------------------------------------------------------------------------------|------------|

|                | ~~ = /                                                                         | 11         |

| -              | Diagrama de blocos simplificado da GPU (extraído de GPU Gems 2)1               |            |

| _              | O processador de vértices (extraído de GPU Gems 2)                             |            |

| Figura 2.4:    | Processador de Fragmentos (extraído de GPU Gems 2)                             | 13         |

| Figura 3.1:    | Estágios do Processamento Gráfico                                              | 9          |

| Figura 3.2:    | A linha tracejada marca a fronteira entre a CPU e a GPU nos estágios do        |            |

|                | r                                                                              | 19         |

| Figura 3.3:    | Exemplo de comandos de desenho disponibilizados pela API DirectX2              | 20         |

| Figura 3.4:    | O Buffer de Comandos acumula comandos para enviar em lotes; a cada             |            |

|                | envio de instruções para o driver ocorre uma transição de estado               | 20         |

| Figura 3.5:    | Exemplo de código da aplicação instrumentado para utilização do contador       |            |

|                | de alta performance                                                            | 21         |

| Figura 3.6:    | Exemplo de código da aplicação instrumentado e com comandos para o             |            |

|                | esvaziamento do buffer de comandos da API                                      | 23         |

| Figura 3.7:    | Performance como função do tamanho de triângulos                               | 24         |

| Figura 3.8:    | Variação da performance com o número de fragmentos processados2                | 25         |

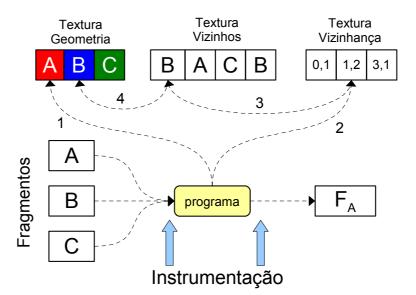

| _              | Estrutura do modelo Proposto; O modelo é composto de estágios (lógicos)        |            |

| C              | que vão aproximando sucessivamente a estimativa de performance                 |            |

| Figura 4.2:    | Exemplo do arquivo de configuração do primeiro estágio do simulador3           |            |

| _              | Estágios implementados pelo simulador                                          |            |

| _              | Exemplo de código de processador de fragmentos                                 |            |

| _              | Variação da Performance como função do número de fragmentos                    |            |

| 1 18010 0 10 1 | , , , , , , , , , , , , , , , , , , ,                                          | 10         |

| Figura 5 4:    | Exemplo de programa de fragmentos com 6 ciclos no hardware da ATI4             |            |

|                |                                                                                | 11         |

| _              | Variação do tamanho de triângulos para preencher uma tela inteira              |            |

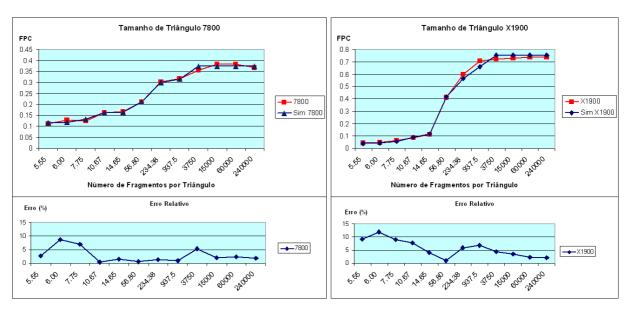

|                | Variação de performance com o tamanho do triângulo. Valores medidos,           | -          |

| 1 1guru 5.7.   |                                                                                | 13         |

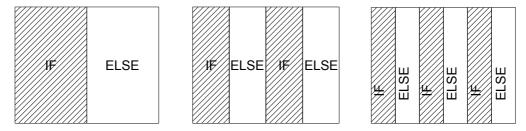

| Figura 5 8.    | Exemplo de código com desvio condicional que divide os fragmentos em 2         | _          |

| 1 igura 5.6.   | grupos (coordenada x de textura maior ou igual que 0,5 e coordenada de         |            |

|                |                                                                                | 14         |

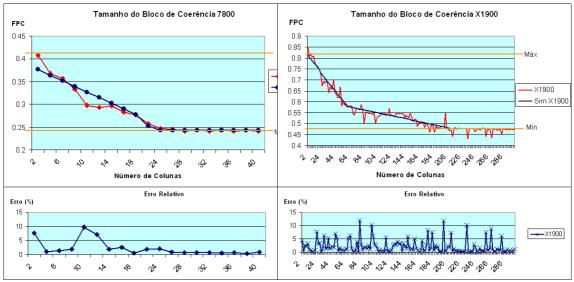

| Figura 5 0:    | Variação da largura da coluna, que determina o tamanho do bloco de             | Γ-         |

| rigura 3.9.    | ,                                                                              | 14         |

| Figure 5 10    | ,                                                                              | +4         |

| rigula 3.10    | ): Variação da performance com o tamanho da coerência da tomada de             | _          |

|                | desvios. A performance diminui (o tempo aumenta) conforme o tamanho de         | U          |

|                | bloco de coerência diminui. Abaixo de 60 fragmentos por coluna a               | 1 =        |

| E: 5.11        | performance é constante                                                        |            |

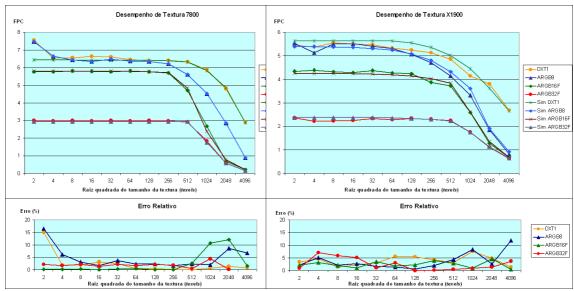

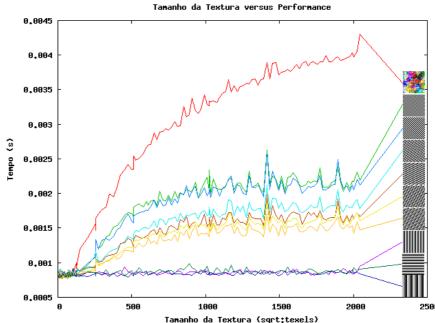

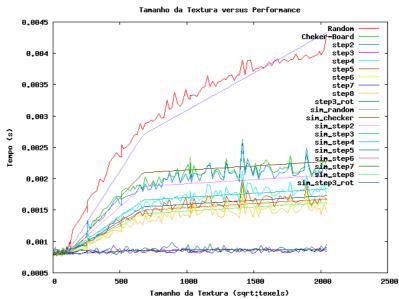

|                | Performance como função do tamanho da textura                                  |            |

| Figura 5.12    | 2: Padrões de acesso utilizados (da esquerda para direita): aleatório, xadrez, | . <b>_</b> |

|                | step2, step3, step4, step5, step6, step7, step8, step3_rot4                    | <b>1</b> 7 |

| Figura 5.13    | 3: Performance versus tamanho da textura dependente. À direita estão as        |            |

|                | texturas independentes, que regem o padrão de leitura da memória               |            |

| -              | 4: Performance Medida e Performance Estimada pelo Simulador4                   | 19         |

| Figura 5.15    | 5: Programa de Fragmentos utilizado para verificação do simulador com a        |            |

|                | aplicação do sistema massa-mola sendo executado na GPU                         | 53         |

| Figura 5.16    | 6: Pseudo código executado pela aplicação massa-mola; as instruções            |            |

|                | aritméticas não estão representadas5                                           | 54         |

# **LISTA DE TABELAS**

| Tabela 2.1: Custo das instruções de desvio na GPU G70. Cada instrução de con | trole de |

|------------------------------------------------------------------------------|----------|

| fluxo adicionada a um programa de fragmentos incorre numa sobre              | carga de |

| dois ciclos ao programa (extraído de GPU Gems 2)                             | 17       |

| Tabela 3.1: Comparação das técnicas de análise de performance                | 19       |

| Tabela 5.1: Performance medida e simulada para o modelo massa-mola           | 55       |

### Resumo

O advento das unidades de processamento gráfico (GPUs) programáveis forneceram um novo modelo computacional que pode ser utilizado em diversas aplicações. Baseadas em arquitetura de fluxo paralelo, a atual geração de GPUs oferece processadores de vértices e de fragmentos programáveis que podem aumentar drasticamente a performance comparada com soluções implementadas exclusivamente em CPUs. Entretanto obter performance ótima no modelo computacional da GPU, que é complexo e altamente paralelo, com ferramentas de depuração limitadas é uma tarefa difícil e importante. Neste trabalho nós descrevemos uma abordagem simples para avaliar diversas soluções baseadas em GPU para uma dada solução. Ela consiste de um modelo de estimativa de performance que procura reproduzir, dentro de faixas toleráveis de erro, a medida de performance para a unidade de processamento de fragmentos. Nós avaliamos a nossa proposta utilizando as últimas gerações de placas gráficas da NVidia e da ATI usando um conjunto de medidas sintéticas bem como um estudo de caso de uma aplicação em tempo-real.

## Performance Model for Code with Execution Branches in Graphics Hardware

### **ABSTRACT**

The advent of Graphics Processing Units (GPUs) with programmable shaders brought a new computational model that can be used in several applications. Based on a parallel streaming architecture, current GPU generations offer a vertex and fragment shader that can drastically improve performance if compared to CPU-only solutions. However, obtaining optimal performance in the highly parallel and complex GPU model with limited debugging tools is a challenging and important task. In this work we describe a simple approach to evaluate several GPU alternatives to a given solution. It consists of a performance estimation model that aims to reproduce within acceptable errors the measured performance of the fragment shader. We evaluate our proposal using last generation cards from NVIDIA and ATI using synthetic benchmarks as well as a real-time graphics application case-study.

**Keywords**: performance model, graphics processing, graphics hardware

## 1 Introdução

O sub-sistema de processamento gráfico nos computadores pessoais (PCs) modernos tem evoluído em velocidade mais acelerada do que a evolução das CPUs (Unidades Centrais de Processamento). O sub-sistema gráfico é composto por uma placa de expansão (placa de vídeo) que conecta com o sistema através de barramentos PCI, AGP ou PCI-Express. A placa gráfica contém um micro-processador chamado usualmente de GPU (Unidade de Processamento Gráfico) ou VPU (Unidade de Processamento Visual). Devido à natureza intrinsecamente paralela deste tipo de hardware, as GPUs já ultrapassam as CPUs em capacidade de processamento e é esperado que esta vantagem continue aumentando no futuro. Existem aplicações que demandam grande capacidade de processamento, tal qual a GPU pode oferecer.

Algumas classes de aplicações têm mostrado excelente potencial para implementação em GPUs. Isto se deve ao fato dos processadores gráficos terem se mostrado excelentes "stream processors" (processadores de fluxo), capazes de processar qualquer informação e não apenas dados gráficos. As GPUs estão cada vez mais perto de tornarem-se pequenos "super co-processadores". Exemplos de aplicações incluem desde a solução de problemas básicos de álgebra linear (GOODNIGHT, 2003), até problemas complexos como a simulação de fluidos (GRIMM, 2004) e Ray Tracing (PURCEL, 2005). Estimar a performance das GPUs é essencial para implementação eficiente destas aplicações.

É importante notar que não se pretende aqui realizar apenas medidas de "benchmark". Um benchmark roda diversos programas e gera um relatório de como o hardware responde a execução destes programas. Diversos trabalhos apresentam medidas de performance para soluções em particular; Fathalian (2004) e Hall (2003) reportam os resultados que foram obtidos para multiplicações de matrizes utilizando o processamento na GPU. Trancoso (2005) compara medidas de desempenho realizadas numa CPU e numa GPU. Mas em nenhum dos casos anteriores existe a tentativa de previsão de performance. O que se pretende com este trabalho é simular qual será a performance de uma dada solução para uma determinada configuração.

Estratégias comumente utilizadas para produzir tais estimativas correspondem a um modelo matemático ou construção de um simulador. Para ambas abordagens é necessário conhecimento das características de performance da GPU a ser avaliada. O processo de construção do modelo ou simulador é usualmente feito de forma incremental, começando de uma representação simples e adicionando detalhes sob demanda. Por exemplo, o caso mais simples na GPU é estimar a performance de código executado sem desvios e saltos, sem nenhum acesso a texturas. Quando o código a ser avaliado contém desvios, condicionais ou incondicionais, o modelo necessário para correta previsão da performance se torna mais complexo e necessita de informações

adicionais se comparado com códigos sem desvios. Estes dados adicionais podem estar relacionados com a coerência dos dados sendo processados ou com a freqüência com que os desvios são tomados. Cada tipo de desvio altera o desempenho da arquitetura de maneira diferente e conhecendo como o desempenho da arquitetura varia em cada caso, pode-se construir um modelo para estimar a performance dessa arquitetura sob diferentes cargas de trabalho.

Este trabalho tem por objetivo estimar a performance do hardware gráfico e propor um modelo que seja capaz de auxiliar nesta estimativa. A análise pode ajudar a entender o ganho que determinadas classes de aplicações teriam se fossem efetuadas modificações na maneira em que são implementadas ou mapeadas para a arquitetura da GPU. O modelo deve fornecer informações que permitam avaliar qual a melhor estratégia para se utilizar código com desvios condicionais ou incondicionais. Este modelo deve levar em consideração diversos recursos que o hardware coloca à disposição do programador e como eles podem ser associados para resultar na performance que é obtida. Uma vez proposto o modelo, um simulador pode ser construído para que seja possível verificar a validade do modelo aplicando diversas cargas a cada um dos recursos escolhidos para implementação.

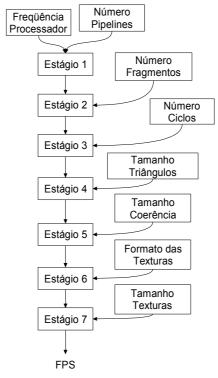

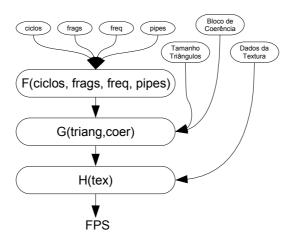

O modelo proposto visa aproximar a performance do processador de fragmentos – um dos componentes internos – de uma GPU. Este modelo é composto de estágios que podem ser agrupados para obtenção do resultado final de estimativa de performance. A composição em estágios tem por finalidade diminuir a complexidade de cada estágio. O modelo apresentado é um modelo de desaceleração, onde uma estimativa de performance máxima é obtida inicialmente e após refinamentos a estimativa é reduzida de acordo com a carga a que cada recurso do hardware está submetido. Os estágios são aplicados seqüencialmente e cada estágio entrega como resultado uma estimativa de performance parcial até o último estágio ser utilizado. Os estágios do modelo podem tomar como dados de entrada parâmetros relativos ao hardware e/ou relativos aos dados sendo processados.

Um simulador composto por estágios foi implementado tendo como base o modelo proposto. O primeiro estágio gera como saída uma estimativa de performance máxima e toma como parâmetros de entrada dados relativos ao hardware e à carga à qual ele está submetido:

- número de pipelines

- frequência de operação do processador

- número de ciclos dos programas sendo executados

- quantidade de fragmentos sendo processados

O segundo estágio do simulador é responsável por desaceleração devido a perda de performance que está associada com a coerência dos dados sendo processados. Para isto, o estágio toma como parâmetros de entrada:

- estimativa de performance do estágio anterior

- tamanho dos triângulos desenhados

- tamanho do bloco de coerência das tomadas de desvio

O terceiro estágio do simulador é responsável pela introdução de desaceleração devido aos acessos de memória, representados no hardware pelo acessos de leitura a texturas. Este estágio toma como parâmetros de entrada:

- estimativa de performance do estágio anterior

- tamanho das texturas acessadas

- formato (ou bytes por texel) das texturas

A validação dos dados previstos pelos estágios do simulador foi realizada comparando resultados de performance com a execução de aplicações simples em situações sintéticas, onde apenas um parâmetro foi variado de cada vez. Em seguida, o simulador foi verificado com a execução de uma aplicação complexa: um simulador massa-mola, implementado em GPU. Foi estabelecido que o erro relativo médio máximo admitido não ultrapassaria 10% em cada estágio do simulador durante as medidas sintéticas. Para o simulador com três estágios seqüenciais que apresentamos, compondo o erro relativo de cada estágio espera-se que o erro final do simulador não ultrapasse 33%, isto é:

$$\underbrace{[(\underbrace{X*1,1})*1,1]*1,1=1,33*X}_{estágio 1}$$

$$\underbrace{\underbrace{estágio 1}_{estágio 3}}$$

dos quais 1,0\*X é o sinal e 0,33\*X é o erro.

As estimativas do simulador comparadas com medidas obtidas com experimentos sintéticos executados na GPU indicam um erro relativo dentro do estabelecido como aceitável. Para simulações que não levam em conta acessos a memória da placa de vídeo, o simulador consegue reportar estimativas com erros menores que 2%. No caso do experimento do simulador massa-mola, utilizado para verificar o simulador, o erro relativo não ultrapassou 10%.

Esse texto está organizado em 6 capítulos que podem ser divididos em dois grupos. A parte inicial procura colocar o leitor no contexto da utilização do hardware gráfico. A segunda parte aborda o tema central do trabalho que é a proposição de um modelo de performance e avaliação de um simulador baseado no modelo proposto.

No capítulo 2 o leitor é introduzido ao hardware gráfico e seu funcionamento, como é utilizado para geração de imagens e como pode ser programado. São apresentadas APIs de programação que fazem a interface entre a aplicação que roda na CPU e os programas que são executados de fato pelos processadores do hardware gráfico. No capítulo 3 é apresentada a técnica utilizada para coleta de dados de desempenho. O capítulo 4 propõe o nosso modelo de performance do hardware gráfico parametrizado por recursos que escolhemos como significativos na descrição da arquitetura do hardware gráfico. O modelo recebe como entrada os parâmetros escolhidos e combina-os para entregar uma estimativa de performance dentro do limite de erro relativo estabelecido. No capítulo 5, o simulador que implementa o modelo de performance proposto é avaliado e verificado; são mostradas medidas de performance usando situações simples e complexas. O capítulo 6 encerra o trabalho, avaliando a eficácia do modelo e do simulador com relação a dados reais e propõe trabalhos futuros.

### 2 Hardware Gráfico

Este capítulo apresenta uma descrição do hardware gráfico. Inicia com uma visão abrangente do hardware usado como base neste trabalho e parte da discussão baseia-se no capítulo sobre a arquitetura da GeForce 6800 discutido em "GPU Gems 2" (KILGARIFF, 2005). Descreve a associação entre CPU e GPU e mostra os diversos estágios do pipeline gráfico e a arquitetura das modernas GPUs. Explica a programação dos processadores da GPU e faz uma breve menção sobre as linguagens e APIs empregadas para tal.

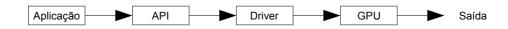

O processamento gráfico é decomposto em diversas atividades que podem ser representadas por estágios funcionais num pipeline (semelhante a uma linha de montagem): processamento da aplicação, processamento de geometria, rasterização e renderização. Cada um destes estágios funcionais é implementado por um ou mais estágios correspondentes no hardware gráfico (BOUATOUCH, 2002). A aplicação (responsável pelo envio de comandos a serem executados pelos demais estágios do pipeline gráfico) roda no processador central da estação de trabalho (CPU). Os demais estágios são implementados por uma unidade de processamento especializada chamada GPU.

A GPU é composta de estágios responsáveis pelo processamento de vértices, estágios que realizam rasterização das primitivas (pontos, linhas e planos) formadas pela geometria dos vértices e estágios que processam os fragmentos rasterizados. Estes estágios podem ser programados (MARK, 2001) através de comandos enviados pela aplicação para realizar determinada operação sobre os dados que estão passando por estes estágios. Estes comandos são gerados pela aplicação que executa na CPU do sistema; portanto existe uma comunicação entre a CPU e a GPU, para o envio dos comandos e dos dados a serem processados.

# 2.1 Arquitetura da GPU

O processamento gráfico é composto de diversos procedimentos que devem ser realizados sobre dados para a geração de uma imagem. Estes procedimentos são realizados de maneira seqüencial, de modo similar a uma linha de montagem. No início desta linha de montagem está a CPU que envia ao sub-sistema gráfico os dados e os comandos que vão compor a imagem. Na extremidade final da linha de montagem está o display gráfico (monitor) do sistema. Esta linha de montagem é representada pela placa de vídeo do computador (o sub-sistema gráfico). A placa de vídeo é composta por um conjunto de processadores que coletivamente são chamados de GPU (Graphics Processor Unit) e bancos de memória onde dados temporários são armazenados.

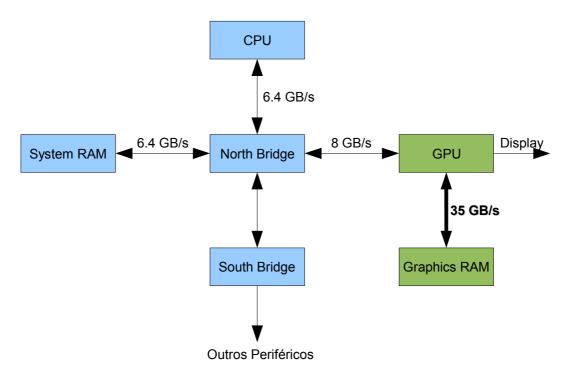

A placa de vídeo, sendo um sub-sistema do computador, interage com o resto do hardware por uma interface padronizada, como os barramentos PCI, AGP ou PCI-Express. É por esta interface que comandos e dados a serem processados pela GPU ou armazenados na memória da placa de vídeo trafegam. Devido à grande quantidade de dados e comandos a serem repassados para a GPU, é importante que esta interface não seja um gargalo para o sistema. Por isto, têm sido desenvolvidos barramentos cada vez mais rápidos, culminando atualmente com o PCI-Express que provê uma largura de banda de 8 GB/s entre a CPU e a GPU – figura 2.1.

Figura 2.1: Diagrama de blocos da arquitetura simplificada de um PC (extraído de GPU Gems 2)

A GPU é organizada numa linha de montagem (pipeline), similar à linha de montagem do processamento gráfico. A GPU contém processadores que se encarregam do processamento da geometria da cena a ser composta, unidades de rasterização, que transformam a geometria da cena numa imagem plana em duas dimensões composta por pequenos fragmentos de imagens, processadores que operam sobre os fragmentos e um sistema que apresenta o resultado no display gráfico.

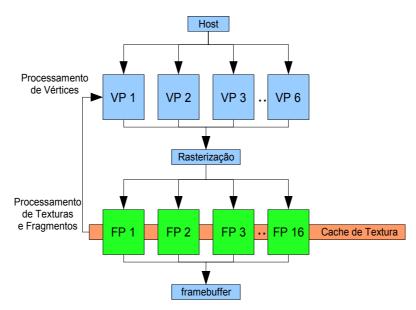

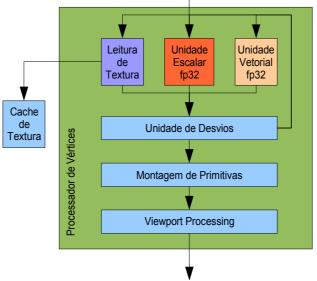

No início desta linha de montagem – figura 2.2 – estão os processadores de vértices, que são os primeiros a receber os comandos e dados provenientes da CPU. A figura 2.3 apresenta a arquitetura dos processadores de vértices. Os dados recebidos por estes processadores são vértices que contêm propriedades, tais como posição espacial, cor, etc. Os comandos recebidos pelos processadores de vértices contêm instruções de como agrupar os vértices recebidos, de forma a gerar o que é chamado de primitiva. Uma primitiva é uma figura geométrica espacial simples, em geral linhas e triângulos. Primitivas são combinadas para formar figuras mais complexas a serem exibidas na imagem final. A decomposição dos objetos da imagem em primitivas tem a finalidade de facilitar os processamento em cada estágio do pipeline gráfico, de forma que as

operações enviadas pela aplicação (a partir da CPU) sempre sejam realizadas da maneira mais rápida possível.

As primitivas montadas e manipuladas pelos processadores de vértices são enviadas para as unidades de rasterização. Um rasterizador tem a função de analisar a primitiva que recebe, verificar as propriedades dos vértices que a compõe e então interpolar valores entre estes vértices. O rasterizador obtém isto, tomando o espaço entre cada vértice e subdividindo-o em pequenos pedaços, os fragmentos. Idealmente cada fragmento deveria ser interpretado como um ponto no espaço, mas é tratado como uma pequena área associada ao ponto. Para cada fragmento, certos valores indicados pelos vértices são interpolados, tais como a cor e a posição espacial entre os extremos dados pelos vértices da primitiva.

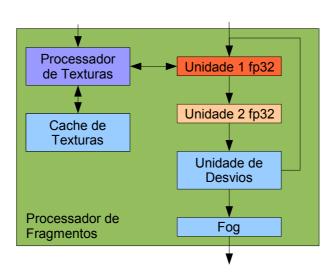

Figura 2.2: Diagrama de blocos simplificado da GPU (extraído de GPU Gems 2)

A última parte desta linha de montagem da GPU, antes da imagem final ser apresentada, trata do processamento que deve ser aplicado sobre os fragmentos provenientes do rasterizador. Esta parte é composta por um número de processadores que é maior do que o número de processadores de vértices, pois o número de fragmentos gerados por cada primitiva em geral supera em muitas ordens de grandeza o número total de primitivas que compõem uma imagem. Estes processadores são chamados de processadores de fragmentos. A figura 2.4 mostra a arquitetura dos processadores de fragmentos. Um processador de fragmentos tem a função de aplicar sobre cada fragmento recebido um conjunto de instruções que lhe foi enviado pela aplicação (ou seja um programa a ser executado para cada fragmento. Os fragmentos são independentes uns dos outros, o que permite os processadores de fragmentos trabalharem de forma coordenada e maximizar o número de fragmentos processados em paralelo. Conforme os fragmentos vão terminando seu processamento, os resultados vão sendo depositados numa área da memória da placa de vídeo chamada de framebuffer. Os dados contidos nessa memória são chamados de pixels. Cada pixel no framebuffer corresponde a um elemento de imagem que compõe o display (monitor) conectado à placa de vídeo.

Figura 2.3: O processador de vértices (extraído de GPU Gems 2)

## 2.2 Processador de Fragmentos

O foco deste trabalho foi centrado no processador de fragmentos, uma parte da linha de montagem do processamento gráfico. Nesta seção vamos aprofundar o conhecimento sobre o processador de fragmentos e algumas de suas estruturas internas para termos um clara definição do que estará sendo tratado nos capítulos a seguir. Começamos por uma breve descrição da evolução dos processadores de fragmentos para então analisar como o processador de fragmentos é implementado nas gerações mais recentes das placas de vídeo.

Figura 2.4: Processador de Fragmentos (extraído de GPU Gems 2)

O processador de fragmentos é um dos vários estágios do processamento gráfico. Este processador é composto por pipelines internos. Dados entram por uma extremidade do processador e, após serem manipulados, saem pela outra extremidade do processador. O processador de fragmentos pode ser entendido como sendo composto por um ou mais pipelines, com diversos estágios que realizam diferentes tarefas.

Inicialmente estes estágios internos do processador de fragmentos eram simples e realizavam tarefas simples, não havendo a necessidade de programação. Eventualmente alguma configuração para alterar certos estados dos estágios dos pipelines do processador de fragmentos. Os primeiros processadores de fragmentos eram apenas uma unidade de aplicação de textura aos fragmentos que passavam por eles. A aplicação de uma textura consiste na leitura de um mapa de cores, a textura, e a correta aplicação da cor a um dado fragmento de acordo com a sua posição. Nessa situação, apenas a textura a ser aplicada necessitava ser configurada, uma vez que a tarefa a ser realizada era sempre a mesma: ler a cor de uma posição na textura e transferir esta cor para o fragmento.

Com a evolução do hardware, tarefas mais complexas começaram a ser disponibilizadas nos processadores de fragmentos. A aplicação simultânea de mais de uma textura, por exemplo, exigiu a leitura de dois valores de cor para cada fragmento, a combinação destes valores e a escrita do valor resultante para o fragmento. Isto criou a necessidade de mais informações além da simples menção das texturas a serem utilizadas, pois cada textura pode ter um peso diferente na composição da cor resultante. Mais dados são necessários como entrada e mais estágios no pipeline precisam ser utilizados. Com o tempo, operações aritméticas também começaram a se tornar desejáveis. Estas novas operações exigiram novos estágios no pipeline do processador de fragmentos. Com mais tarefas a serem realizadas, a simples configuração de cada estágio começou a se mostrar uma limitação para a completa utilização do pipeline de fragmentos.

Os estágios de um pipeline de um processador de fragmentos atualmente compreendem desde unidades de leitura de texturas até unidades de tomadas de desvios condicionais, passando por unidades aritméticas. O conjunto destas unidades pode ser programado para realizar uma determinada tarefa. Para cada fragmento ter um programa totalmente aplicado sobre si, podem ser necessárias diversas passadas pelas unidades do pipeline de fragmentos, onde em cada passada as unidades do pipeline estarão configuradas de maneira diferente, correspondendo às instruções do programa. Um programa longo exige diversas passadas pelo pipeline, enquanto um programa curto pode exigir poucas passadas. Este número de passadas necessárias está intimamente ligado ao programa que está em execução e à forma como os diversos estágios do pipeline estão organizados. Dependendo da organização do pipeline, as instruções que compõem um programa podem ser agrupadas e executadas de maneiras diferentes. Em geral a organização do pipeline muda para cada modelo de GPU.

Os pipelines do processador de fragmentos da NVidia obedecem a estruturas similares: duas unidades de operações aritméticas e uma unidade de tomada de desvios (BAUMANN, 2006). A primeira unidade aritmética pode realizar operações de leitura de textura no lugar de uma operação matemática. Um fragmento pode, portanto, ter executada uma instrução de textura, uma instrução aritmética e uma instrução de desvio ou duas instruções aritméticas e uma instrução de desvio. Se mais acessos a texturas ou mais instruções aritméticas são necessárias do que disponível em unidades no pipeline,

então um fragmento pode tem que entrar novamente no pipeline, desta vez com as novas instruções configuradas em cada estágio.

A ATI utiliza uma abordagem diferente para os pipelines do processador de fragmentos (TRIOLET, 2006). O processador de fragmentos das GPUs da ATI têm pipelines especializados na leitura de texturas e outros pipelines especializados em operações aritméticas e desvios de fluxo de execução. Os pipelines de leitura de textura realizam apenas esta tarefa e após um fragmento ter passado por ele, deve ser encaminhado a um pipeline de processamento aritmético para realizar a as operações matemáticas que eventualmente necessite. Os pipelines de processamento aritmético têm duas unidades que realizam operações matemáticas e uma unidade de desvios. Destas duas unidades aritméticas, a primeira é especializada em operações de soma, não estando apta a realizar outro tipo de operação. A segunda unidade aritmética pode realizar tanto instruções de soma quanto as demais instruções disponibilizadas pelo hardware.

A configuração dos estágios do pipeline é feita via um agrupamento de instruções que é enviado para o pipeline e vai reconfigurando os estágios següêncialmente. Este agrupamento de instruções é chamado de VLIW (PATTERSON, 1996), do inglês Very Long Instruction Word (Palavra de Instrução Muito Longa). A VLIW é um agrupamento de instruções que são endereçadas aos estágios aos quais elas devem configurar. A responsabilidade da montagem mais adequada desta VLIW é do compilador, que tem conhecimento detalhado sobre o hardware para o qual ele está gerando o código. Os modelos do hardware para os quais VLIWs são construídas, são diferentes entre si. Por mais sutil que sejam estas diferenças, elas devem ser levadas em conta pelo compilador que está gerando as VLIWs. Por isso um programa otimizado para um determinado hardware jamais irá executar com a mesma performance em outro (se eventualmente puder executar). Isso implica recompilar um determinado programa para cada hardware no qual ele vai ser executado. Esta recompilação pode ocorrer antecipadamente ou na hora de execução. Existem aplicações que podem examinar o programa a ser executado antecipadamente e prever quantas VLIWs serão formadas de acordo com as características do pipeline em questão.

Para cada VLIW formada é necessária uma passada (ciclo) do fragmento a ser processado pelo pipeline. Em situações especiais, quando são usadas instruções complexas pode ser necessária mais de uma passada (ou mais de uma VLIW) para a completa execução de uma única instrução. Instruções de desvio são um exemplo de instruções que podem necessitar de mais de uma passada pelo pipeline — tabela . Na primeira passada, por exemplo, podem ser decididos quais fragmentos vão tomar o desvio; na segunda passada, pode ser decidido o salto necessário para a tomada do desvio. A correspondência entre o número de ciclos necessários para a execução de uma instrução sobre o fragmento não precisa ser constante entre os modelos diferentes de hardware, pois cada modelo tem suas particularidades.

Tabela 2.1: Custo das instruções de desvio na GPU G70. Cada instrução de controle de fluxo adicionada a um programa de fragmentos incorre numa sobrecarga de dois ciclos ao programa (extraído de GPU Gems 2).

| Instrução     | Custo (ciclos) |

|---------------|----------------|

| if/endif      | 4              |

| if/else/endif | 6              |

| call          | 2              |

| ret           | 2              |

| loop/endloop  | 4              |

A maneira como uma VLIW é montada pode dar pistas sobre as particularidades internas dos pipelines, uma vez que cada instrução deve corresponder ao estágio a que ela se destina. Uma destas particularidades diz respeito à maneira paralela como os dados são tratados dentro dos estágios do pipeline. Os dados sobre os quais o processador de fragmentos trabalha são fragmentos. Fragmentos possuem 4 elementos de cor: os canais Vermelho ("Red"), Verde ("Green"), Azul ("Blue") e Alfa, indicam a combinação de cores básicas que deve ser utilizada para obter a cor resultante e mais o percentual de transparência do fragmento. Estes quatro elementos podem ser tratados como elementos de um vetor de quatro posições, uma vez que todos os fragmentos possuem estes mesmos elementos. Fragmentos possuem também coordenadas, em geral bi-dimensionais, que indicam sua posição relativa na textura que deve ser aplicada, sendo por isso facilmente tratadas como vetores. Uma vez que os fragmentos podem ser descritos por vetores é de se esperar que os estágios do pipeline de fragmentos sejam especializados no tratamento de vetores – como de fato o são.

A taxionomia de Flynn (FLYNN, 1966) é usada para classificar como operam os processadores da GPU. Flynn classifica processadores em 3 tipos: processadores SIMD, MIMD e SISD. Processadores SISD executam uma única instrução sobre um único dado. Processadores SIMD se caracterizam por executar uma mesma instrução sobre um grupo de dados ao mesmo tempo. Processadores MIMD (Multiple Intructions Multiple Data) se caracterizam por executar diferentes instruções sobre diferentes dados. As unidades de execução de um pipeline de fragmentos podem trabalhar de uma maneira SIMD sobre os vetores que descrevem os fragmentos. Isto é, diversos pipelines podem estar aplicando a mesma instrução a diversos fragmentos.

# 3 Medição de Performance

A análise de performance de sistemas computacionais pode ser entendida como uma combinação de medidas e interpretações sobre diversas características do sistema, como performance, velocidade de comunicação, tamanho dos dados, etc. (JAIN, 1991). Devido à complexidade de alguns sistemas, em muitos casos a análise concentra-se em apenas um subconjunto do sistema inteiro. Por exemplo, pode-se estar interessado apenas na performance do subsistema gráfico de um computador. Entretanto os componentes de um sistema computacional podem interagir de uma maneira muito complexa e muitas vezes de maneira imprevisível. Para a análise ser efetiva, é necessário desenvolver técnicas que perturbem o mínimo possível o sistema a ser analisado.

Os objetivos da análise de um sistema computacional dependem da situação específica, dos interesses e da habilidade do analista (LILJA, 2000). Entretanto é possível identificar alguns objetivos típicos:

- Comparação de alternativas: identificar a mais eficaz entre várias configurações.

- Determinação do impacto de uma funcionalidade: medir o impacto na performance quando uma funcionalidade é adicionada ou removida.

- Ajuste fino de sistemas: qual conjunto de configurações resulta na melhor performance.

- Identificação de performance relativa: identificar a performance relativa a dados obtidos de um histórico.

- Detecção de problemas de performance: descobrir por que um sistema não está desenvolvendo a performance esperada.

- Expectativas de performance: indicar o que pode ser esperado de um dado sistema.

Um objetivo comum a todos estes listados acima é caracterizar como a performance do sistema (ou sub-sistema) muda quando certos parâmetros são variados. Quando deparado com problemas de análise de performance, existem três técnicas fundamentais que podem ser empregadas:

- Medida em um sistema existente

- Simulação do sistema

### Modelagem analítica

As medidas realizadas em um sistema existente levam aos melhores resultados da análise de performance. Dado que existam as ferramentas necessárias para a realização das medidas, nenhuma simplificação sobre o sistema precisa ser feita. Isto também torna os resultados mais confiáveis. Realizar medidas em sistemas reais não é muito flexível, uma vez que estas medidas proporcionam informação apenas sobre o sistema medido. Por exemplo, em muitos sistemas não é possível variar a velocidade do subsistema de memória.

A simulação é um instrumento para modelar as características importantes de um sistema. Projetada de forma a ser facilmente modificada, permite estudar o impacto de modificações em vários componentes do sistema simulado. O custo da simulação depende da complexidade do sistema sendo modelado e do grau de detalhamento que está sendo incorporado ao simulador. A primeira limitação na construção de um simulador é a impossibilidade de se modelar todos os detalhes microscópicos do sistema sendo estudado. Simplificações devem ser assumidas para que seja viável a construção do simulador, ciente de que estas devem afetar a precisão e a credibilidade da análise realizada.

A modelagem analítica é uma descrição matemática do sistema. Comparado com as técnicas de medição e de simulação, a modelagem analítica é muito mais complexa de se realizar. É comum optar por representações analíticas mais simples, como aproximações lineares, mas isso faz com que a modelagem seja menos precisa. Um modelo analítico simples permite uma compreensão rápida do sistema, concentrando as medidas em um dado mais específico. Ele ainda ajuda a confirmar os resultados provenientes de um simulador ou de medidas realizadas.

Os critérios para a escolha de uma técnica de análise de performance estão resumidos na tabela 3.1.

| Característica | Medida | Simulação | Modelo<br>Analítico |

|----------------|--------|-----------|---------------------|

| Flexibilidade  | Baixa  | Alta      | Alta                |

| Custo          | Alto   | Médio     | Baixo               |

| Credibilidade  | Alta   | Média     | Baixa               |

| Precisão       | Alta   | Média     | Baixa               |

Tabela 3.1: Comparação das técnicas de análise de performance

Este trabalho tem como meta a proposição de um modelo para previsão de performance da GPU. Para isto será construído um simulador com base no modelo e seus resultados comparados com medidas realizadas em equipamentos de referência. Deve-se, portanto, conhecer e saber aplicar técnicas e ferramentas que permitam que medidas sejam realizadas e em seguida comparadas com previsões que o simulador possa fornecer.

Neste capítulo são apresentadas algumas ferramentas que podem ser utilizadas para medição de performance do hardware gráfico. A escolha do método utilizado para a medição da performance em um hardware de referência também é apresentada, bem como a métrica utilizada para medição de performance e quais parâmetros foram escolhidos para avaliação.

#### 3.1 Métrica de Performance

Antes de ser entendido qualquer aspecto da performance de um sistema computacional, deve-se determinar quais aspectos são importantes e úteis para a medida (LILJA, 2000). As características básicas que tipicamente se mede em um sistema computacional são:

- contagem de quantas vezes um evento ocorre

- a duração de algum intervalo de tempo

- característica de um parâmetro de entrada

Por exemplo, pode-se estar interessado em quantas vezes um processador inicia uma requisição de entrada e saída, ou quanto tempo cada uma dessas requisições demora. Para este tipo de dado, utiliza-se diretamente o valor medido. Este valor é chamado de métrica de performance. Se o valor interessado é o tempo, contagem ou tamanho de um valor medido, pode-se utilizar o valor diretamente como a métrica de performance. Seguidamente utiliza-se a contagem normalizada de eventos, por exemplo, a uma base comum de tempo para prover uma métrica de velocidade, tal como operações executadas por segundo. Este tipo de métrica é chamado de métrica de taxa. Em geral a métrica de taxa é calculada dividindo a contagem do número de eventos que ocorrem em um dado intervalo de tempo pelo intervalo de tempo em que eles ocorrem. Uma vez que uma métrica de taxa é normalizada para uma base de tempo comum, é razoável utilizar métricas de taxa para comparações.

Uma métrica escolhida para medição de performance de hardware gráfico é o número de quadros que podem ser gerados em um segundo. Um quadro é todo trabalho necessário para exibir uma imagem na tela. Esta métrica recebe o nome de Quadros Por Segundo (abreviada na sua forma em inglês, FPS – Frames Per Second).

Muitas vezes pode-se medir um valor com grandezas inversamente proporcionais. É o caso do FPS. Ao contrário de contar quantos quadros são completados em um segundo, pode-se medir o tempo necessário para o desenho de um quadro. Sabendo o tempo que um quadro leva para ser desenhado, é uma questão de inverter a razão para saber quantos quadros podem ser desenhados em um segundo:

$$FPS = \frac{1}{tempo \ de \ 1 \ quadro}$$

(3.1)

Embora FPS seja uma métrica simples de entender, pode levar a resultados não intuitivos, se for utilizada para comparar performance de processadores executando com diferentes freqüências. Para evitar este problema, normalizam-se as medidas pela freqüência dos processadores e obtém-se FPC (do inglês Frames Per Clock):

$$FPC = \frac{FPS}{freqüência\ do\ processador}$$

(3.2)

Para medir corretamente o tempo necessário para o desenho de um quadro, deve-se ter em mente que durante a sua composição, um quadro passa por diversos estágios até que esteja finalizado. No caso do hardware gráfico, alguns destes estágios podem estar executando em processadores distintos. A seguir tem-se uma breve discussão sobre os estágios que estão envolvidos na composição de um quadro. Esta discussão é necessária para que se torne claro como as medidas de tempo estarão sendo implementadas, em qual estágio os dados estão sendo coletados e como essa coleta é realizada.

### 3.1.1 Estágios do processamento gráfico

O processamento gráfico é realizado em diversos estágios (BOUATOUCH, 2002). A geração de uma imagem é feita através de comandos que processam formas geométricas primitivas. Em geral o triângulo é utilizado como primitiva básica e agrupado para compor primitivas geométricas mais complexas. Comandos de desenho informam ao hardware gráfico características destes triângulos, tais como posição dos vértices, cores, etc. Estes comandos de desenho são gerados e enviados para o hardware gráfico por uma aplicação. O processamento destes comandos passa por diversos estágios de processamento – figura 3.1 – alguns rodando na CPU do sistema, outros rodando na GPU. Para a obtenção de medidas de performance, deve-se realizar a amostragem em lugares adequados destes estágios – figura 3.4. Cada um destes estágios pode interferir com o trabalho dos demais, na medida em que podem realizar otimizações, podem estar sobrecarregados (um gargalo no sistema) ou podem simplesmente não existir em um dado sistema. Processar uma primitiva pode levar um determinado tempo, enquanto que processar 2 ou 3 primitivas pode levar um tempo apenas ligeiramente maior – e não 2 ou 3 vezes maior– devido a um agrupamento de instruções.

Figura 3.1: Estágios do Processamento Gráfico

O estágio inicial do processamento reside na aplicação, que utiliza comandos de desenho disponibilizados pela API – figura 3.3. A aplicação controla a cena, lida com interações com o usuário e determina como o desenho será efetuado. Todo o trabalho é especificado por uma seqüência de comandos de desenho que é enviada para a API. Essa seqüência de comandos de desenho é independente do hardware utilizado.

A API converte essa seqüência de comandos em um formato independente do hardware, mas pode introduzir algumas otimizações (sem conhecimento sobre o hardware que será utilizado), realizando agrupamentos, ou troca de ordem de instruções. Depois de reagrupadas e reordenadas as chamadas de função da API, as instruções de desenho são repassadas para o driver, que é diferente para cada hardware. A API

utilizada neste trabalho é a DirectX (DIRECTX) desenvolvida pela Microsoft e acompanha os sistemas operacionais Windows.

O driver do sistema operacional conhece o hardware (GPU) disponível e faz otimizações adicionais, desta vez mais agressivas que as anteriores, para tirar o máximo proveito da GPU. O driver pode, por exemplo, otimizar a utilização de registradores que um programa referencia. Também deve se considerar que o driver retorna o controle da execução para a API imediatamente após ter enviado as instruções de desenho para a GPU, sem esperar pela finalização do processo de desenho, para evitar que a CPU fique ociosa enquanto a GPU trabalha. Isto dificulta a medida do tempo gasto pela GPU na execução das instruções.

Figura 3.2: A linha tracejada marca a fronteira entre a CPU e a GPU nos estágios do processamento gráfico.

A GPU processa cada primitiva com todas as informações que a constituem, como vértices e texturas. As GPUs modernas podem ser programadas de duas formas: programas de vértices, que atuam sobre dados relativos a vértices e programas de fragmentos, que atuam sobre os dados relativos a fragmentos. Quando a GPU finaliza seu trabalho, um quadro está completamente desenhado. Cada chamada de uma função gráfica da API, realizada pela aplicação, necessariamente passará por todos os estágios da figura 3.1.

A relação entre os diversos estágios é complexa, pois alguns estágios são executados por processadores diferentes – figura 3.2. O fato de mais de um processador estar envolvido introduz um acoplamento entre estes processadores. A medida de relógio de clock não é a mesma para os processadores e existe largura de banda finita para a conexão entre os processadores.

```

BeginScene();

...

SetTexture(...);

DrawPrimitive(D3DPT_TRIANGLELIST, 0 ,1);

...

EndScene();

Present();

```

Figura 3.3: Exemplo de comandos de desenho disponibilizados pela API DirectX.

O pipeline de processamento DirectX possui um "buffer" que armazena os comandos antes de serem enviados para o driver. Esse buffer é responsável por armazenar instruções de desenho até que a aplicação pare de enviar instruções ou até que o buffer esteja cheio. Quando um desses dois eventos ocorre, temos uma transição de estado – figura 3.4. Uma transição de estado acontece quando o controle da CPU passa da API para o driver e a CPU passa a operar com privilégios que pertencem apenas ao Sistema Operacional. Quando o driver finaliza as tarefas, uma nova transição ocorre; saindo do modo privilegiado indo para o modo de usuário. O buffer de

comandos da API não tem tamanho rígido, podendo mudar durante o tempo ou de uma versão para a seguinte da API. Existem outros eventos que podem levar a uma transição de estado, tais como a chamada da função IDirect3DQuery9::GetData com argumento D3DGETDATA FLUSH, que será utilizada mais adiante.

Figura 3.4: O Buffer de Comandos acumula comandos para enviar em lotes; a cada envio de instruções para o driver ocorre uma transição de estado.

O pacote de desenvolvimento para DirectX disponibiliza um conjunto de ferramentas para medição de performance de aplicativos que utilizam essa API. Alguns fabricantes de hardware gráfico também disponibilizam algumas ferramentas para medição de performance nos seus conjuntos de desenvolvimento. Algumas dessas ferramentas interagem diretamente com o driver da GPU, disponibilizando para a aplicação acesso a alguns contadores implementados em posições estratégicas do hardware, como é o caso do NVPerfHUD (REGE, 2004).

Algumas dessas aplicações não são adequadas para utilização no presente trabalho. O PIX, ferramenta de avaliação de performance (DIRECTX, 2004) distribuída junto com o conjunto de desenvolvimento do DirectX, não permite salvar os dados coletados em um arquivo com formato que não seja o seu próprio, que é proprietário. O NVPerfHUD da Nvidia não salva os dados coletados para arquivos, apenas apresenta-os na tela, sobrepostos à aplicação. Outro método para a medição de performance foi escolhido devido a limitação dessas aplicações. A estratégia escolhida foi a instrumentação do código da aplicação, como será discutido na próxima seção.

# 3.2 Estratégia Adotada para Medição de Performance

O processamento gráfico é realizado em vários estágios e nem todos estes estágios rodam no mesmo processador – figura 3.2. É importante saber de qual parte do pipeline se está realmente medindo a performance. A aplicação, em geral, não tem acesso ao driver e apenas informa o código que será executado na GPU. Como a GPU não disponibiliza mecanismos de medição de performance é necessário a utilização de mecanismos de medida disponibilizados pelo sistema operacional e pela API – ambos rodando na CPU. A estratégia adotada é a instrumentação do código da aplicação que executa na CPU para, com auxilio de funções implementadas pela API, medir o tempo que a GPU leva para executar seu trabalho. Será usado um contador de alta performance disponibilizado pelo sistema operacional.

Alguns sistemas incluem um contador de performance de alta resolução que provê tempos decorridos com grande precisão. Este contador é acionado pelo relógio interno da própria CPU e a cada número definido de ciclos de relógio tem o seu valor incrementado. Se esse contador existe no sistema, a função QueryPerformanceFrequency disponibilizada pelo sistema operacional MS Windows XP pode ser utilizada para expressar a freqüência deste contador em contagens por segundo. O valor dessa contagem é dependente do processador; para cada freqüência de operação da CPU um valor diferente é utilizado. Existe outra função que retorna a leitura atual deste contador de alta performance e que é utilizada para inferir intervalos de tempo.

As medidas realizadas neste trabalho foram feitas através de instrumentação do código da aplicação — figura 3.5 — utilizando o contador de alta precisão do Sistema Operacional. A função QueryPerformanceCounter (LARGE\_INTEGER \*1pPerformanceCount) lê o valor do contador de alta performance e o armazena na variável 1pPerformanceCount. A estratégia para medir o tempo gasto para execução de uma parte do código é registrar o valor do contador antes e depois de executar a seção de código. Assumindo, por exemplo, que QueryPerformanceFrequency indica que a freqüência do contador de alta performance é 50.000 contagens por segundo. Se uma aplicação chama QueryPerformanceFrequency imediatamente antes e imediatamente depois de uma seção de código, os valores retornados por QueryPerformanceCounter podem ser 1500 e 3500, respectivamente. Estes valores indicariam um tempo transcorrido de 0,04 segundos (2000 contagens) enquanto o código é executado. Este cálculo pode ser expresso como:

Tempo =

$$\frac{contagem\ final\ -\ contagem\ inicial}{contagens\ por\ segundo} = \frac{3500-1500}{50000} = 0.04\ s$$

(3.3)

A instrumentação apresentada acima não leva em consideração as transições de estado que podem ocorrer entre o envio de um comando da API e o seguinte (entre SetTexture e DrawPrimitive, na figura 3.5, por exemplo). Para contornar este problema, é utilizado um mecanismo que garante que o buffer de comando esteja vazio

```

BeginScene();

...

QueryPerformanceCounter(&start);

SetTexture(...);

DrawPrimitive(D3DPT_TRIANGLELIST, 0 ,1);

QueryPerformanceCounter(&stop);

...

EndScene();

Present();

```

Figura 3.5: Exemplo de código da aplicação instrumentado para utilização do contador de alta performance.

quando a contagem de tempo é iniciada. Existem dois comandos que auxiliam na tarefa de saber quando não existem mais comandos de desenho a serem despachados para o pipeline gráfico. Uma chamada de função Idirect3DQuery9::Issue com o argumento D3DISSUE\_END coloca um marcador na fila de comandos de primitivas. Este marcador

indica para o driver que todos os comandos que o precedem devem ser despachados e executados pela GPU. Este comando faz com que novos comandos de desenho sejam enviados para a GPU somente depois dela ter finalizado os comandos que o precediam. Finalmente uma chamada ao comando Idirect3DQuery9::GetData com o argumento D3DGETDATA\_FLUSH somente retorna verdadeiro quando todas as instruções do buffer de comando foram enviadas para o driver e para a GPU. O procedimento para medir o tempo gasto pela instruções de desenho da API é descrito a seguir:

- Adicionar um marcador na fila de comandos que serão enviados para a GPU. Isto é feito chamando Idirect3DQuery9::Issue com o argumento D3DISSUE\_END. Este marcador indica ao driver para controlar quando todos os comandos que o precedem terminaram de executar e a GPU está ociosa figura 3.6.

- Esperar o buffer de comandos ficar vazio invocando Idirect3DQuery9::GetData com o argumento D3DGETDATA\_FLUSH. Este comando garante que as instruções remanescentes no buffer de comandos sejam definitivamente enviadas para o driver e finalmente para a GPU. Este comando não retorna verdadeiro enquanto ainda houver algum comando no buffer que precise ser enviado para o driver e para GPU. Com um laço, fica-se verificando constantemente se o comando de esvaziamento do buffer já retornou. O processamento somente prossegue quando o programa sai deste laço.

- Anotar o valor inicial do contador de alta performance mediante uma chamada a QueryPerformanceCounter.

- Enviar o(s) comando(s) que dispara(m) o desenho do quadro

- Adicionar um novo marcador na fila de comandos enviados para a GPU.

- Esvaziar o buffer de comandos novamente, de maneira similar a utilizada anteriormente e espera-se até que a GPU tenha finalizado seu processamento.

- Anotar o valor do contador de alta performance novamente.

- Obter a diferença entre o valor inicial e o valor final do contador de alta performance.

A diferença entre as duas medidas do contador, dividido pelo número de contagens que ele executa a cada segundo, indica o tempo necessário para a execução dos comandos contidos entre as duas leituras do contador. Se foram enviados comandos necessários para desenhar apenas um quadro, então este é o tempo requerido para o processamento de apenas um quadro pela GPU. O inverso desse número é a quantidade instantânea de quadros por segundo (FPS) que a GPU está desenhando. Essa medida é dita instantânea, porque indica o número de quadros que estão sendo desenhados em um determinado instante de tempo. Esse número pode variar com o tempo, fruto da carga a qual a GPU pode estar sendo submetida.

O número de quadros desenhados pode ser muito alto sob certas condições, ultrapassando até mesmo mais de quatro mil quadros desenhados em um único segundo. Nessas condições, outras flutuações de carga que ocorrem naturalmente no hardware –

como outros processos requisitando a atenção da CPU e da GPU, ou algum periférico enviando uma interrupção – podem alterar muito a performance instantânea medida. Para evitar as flutuações de mais alta frequência, optou-se por realizar apenas uma medida por segundo, em vez de anotar o tempo gasto por cada um dos quadros. Os valores medidos são então enviados para um arquivo texto puro no disco rígido do computador, o que também justifica esta política de amostragem, evitando gargalos em outros subsistemas do computador utilizado. O valor final é então obtido como a média aritmética de uma série de valores armazenados.

Figura 3.6: Exemplo de código da aplicação instrumentado e com comandos para o esvaziamento do buffer de comandos da API.

A instrumentação direta do código a ser executado na GPU não é possível pois não existem funções de medida de performance semelhantes a estas disponíveis no hardware gráfico. Apenas o driver do hardware tem capacidade de verificar quando a GPU terminou o seu processamento e está ociosa.

É importante observar que o driver pode forçar com que o subsistema gráfico opere sincronizado com o dispositivo de display, o que efetivamente diminui a performance de toda a aplicação. Quando este modo de operação está habilitado, dizemos que o sincronismo de vídeo está ligado. Para as medidas realizadas neste trabalho o sincronismo de vídeo esteve sempre desligado, permitindo que a GPU trabalhe independentemente da velocidade de exibição do display gráfico.

#### 3.3 Precisão das Medidas

Na análise de performance de sistemas computacionais é importante ter em conta quando um intervalo de tempo é significativo para as medidas realizadas. Neste trabalho a CPU está sendo utilizada para medir tempos relativos a trabalhos realizados na GPU. Deve-se levar em consideração se a CPU está apta a medir com confiança os intervalos de tempos de trabalho típicos da GPU. Por exemplo, em uma CPU que opera em freqüências entre 2 e 3 Ghz, o contador de alta performance faz cerca de 3 milhões de contagens por segundo. A precisão do contador de alta performance é da ordem de centenas de micro-segundos, ou  $10^{-4}$  segundos.

Um processador de fragmentos típico trabalha em freqüências superiores a 350 Mhz. Se a GPU está equipada com 16 pipelines, por exemplo, este processador consegue operar sobre cerca de  $5,6\cdot10^9$  fragmentos a cada segundo (cada pipeline executa um ciclo do programa de fragmentos em um fragmento a cada ciclo de relógio). Um quadro que ocupe toda a tela do computador numa resolução de 1024x768 pixels, tem menos de um milhão de fragmentos. Isso resulta num pico de processamento que supera os 5 mil quadros por segundo.

$$FPS = \frac{frags/s}{frags/quadro} = \frac{5.6 \times 10^9}{1024 \times 768} \simeq 5000 FPS$$

(3.4)

Segundo a equação 3.1, se são desenhados cerca de 5 mil quadros por segundo, isso significa que cada quadro gasta cerca de  $2 \cdot 10^{-4}$  segundos para ser desenhado. Se o número de eventos do contador de alta performance transcorridos durante o tempo de desenho de um quadro é muito baixo, mesmo pequenas oscilações nas medidas de tempo podem desviar muito os resultados obtidos. Sendo o número de eventos grande frente a resolução do contador, é garantido que pode ser obtida uma boa precisão nos números quando medindo o tempo gasto para o desenho de cada quadro. Amostrando estes valores em intervalos regulares — uma vez por segundo nas medidas atuais — também garante a independência das oscilações de carga de mais alta frequência. Utilizar a média de diversas amostras, auxilia ainda mais na remoção de oscilações (ou ruído).

#### 3.4 Características de Performance

Alguns parâmetros do sistema devem ser variados para que seja possível caracterizar como a performance de um sistema se comporta com a sua variação. Agora que se sabe como realizar as amostragens para as medidas de performance, deve-se decidir quais serão estes parâmetros a variar. Os primeiros parâmetros escolhidos para descrever o comportamento da performance do hardware a ser estudado foram os que descrevem a performance máxima que um processador de fragmentos pode atingir:

- A frequência de operação do processador de fragmentos. Como cada pipeline pode aplicar um ciclo do programa em um fragmento a cada ciclo do relógio, este número dá a performance máxima obtida por pipeline.

- O número de pipelines presente em cada processador de fragmentos. Indica quantos fragmentos podem ser processados simultaneamente pelo processador de fragmentos.

- O número de ciclos necessários para a execução completa do programa de fragmentos. Este parâmetro é um indicativo da carga de trabalho que deverá ser realizado sobre cada dado a ser processado.

- O número de dados a serem processados. O foco deste estudo são os fragmentos (dados) que compõem um quadro.

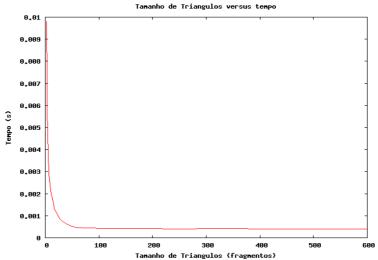

Figura 3.7: Performance como função do tamanho de triângulos

Além dos parâmetros que definem a performance máxima de um processador de fragmentos é interessante analisar parâmetros que podem ser responsáveis por redução de performance do processador de fragmentos. Os parâmetros escolhidos para serem abordados neste trabalho são:

- O tamanho dos triângulos desenhados em cada quadro

- O tamanho do bloco de coerência na execução de desvios de código dos fragmentos sendo processados

- O tamanho das texturas sendo acessadas

- O tipo de texturas isto é, bytes por texel

Alguns destes recursos têm seus valores fixos no modelo de hardware utilizado. O número de pipelines, por exemplo, não pode ser alterado, para medições em uma mesma placa gráfica. Mesmo parâmetros que não podem ser variados devem ser levados em conta porque descrevem características fundamentais do hardware. Tomando novamente como exemplo o número de pipelines de fragmentos, este indica um grau de paralelismo do hardware sendo analisado.

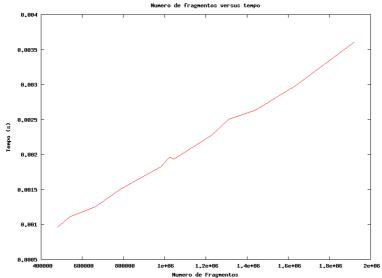

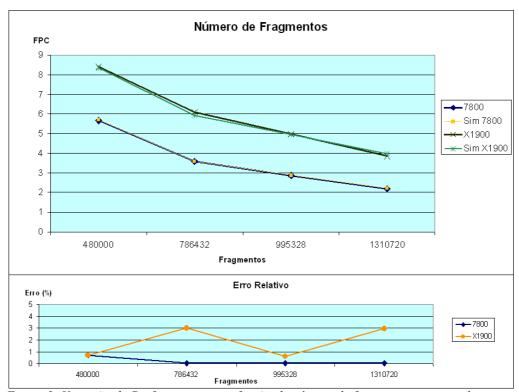

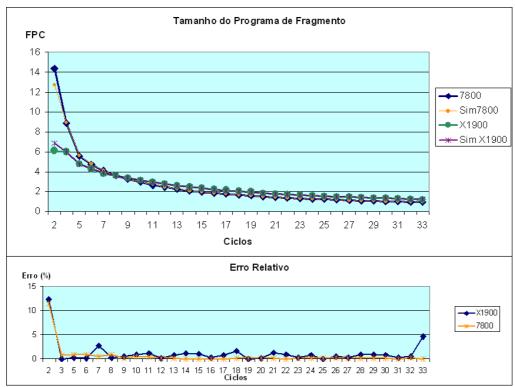

Dentre os recursos que podem ser variados, medidas preliminares indicam que a variação de alguns destes parâmetros têm impacto maior sobre a performance do que outros, como por exemplo o tamanho dos triângulos – figura 3.7. Outros recursos apresentam comportamento bastante linear, como por exemplo a variação do número de fragmentos – figura 3.8.

Figura 3.8: Variação da performance com o número de fragmentos processados

Estes recursos foram escolhidos por se julgar os mais representativos de possíveis vínculos entre os diversos componentes do processador de fragmentos. Estes recursos também são os mais utilizados pela maioria das avaliações de performance publicadas e também são os recursos que o programador tem acesso e maior grau de controle em aplicações.

### 4 Modelo de Performance

Um modelo pode ser visto como uma construção teórica que representa um processo (JACOBY, 1980). Modelos são utilizados primariamente para descoberta de novos fatos, prover argumentos lógicos para explicações, avaliação de hipóteses teóricas e construção de procedimentos experimentais para teste dessas hipóteses. As deduções de um modelo são ditas idealizadas porque o modelo faz suposições que podem não ser verdadeiras em algum nível de detalhamento, mas permitem a produção de resultados que são precisos dentro de um limite de erro. Em alguns casos modelos podem ser utilizados para implementar simulações computacionais que ilustram o comportamento do sistema.

Um modelo matemático descreve um sistema por um conjunto de variáveis e um conjunto de equações que estabelecem relações (vínculos) entre as variáveis (DYM, 1980). As variáveis descrevem propriedades do sistema, como por exemplo contadores, medição de tempo, ocorrência de eventos, etc. O modelo de fato é o conjunto de funções que descreve a relação entre as diferentes variáveis. Pode-se destacar 5 grupos básicos de variáveis usadas na prática:

- decisão ou independentes: representam as propriedades que serão manipuladas para avaliação do comportamento do modelo.

- **estado**: são variáveis que selecionam um dentre diversos estados possíveis para uma dada propriedade do sistema.

- **constantes**: representam propriedades fixas do sistema modelado, que não são alteradas pelo modelo.

- variáveis aleatórias: utilizadas em modelos que admitem propriedades não determinísticas.

- **saída**: representam o resultado das operações de vínculo entre as demais variáveis, e representam a saída do modelo.

Os modelos matemáticos possuem diferentes propriedades que permitem classificá-los de diversas formas:

• **linear** vs. **não-linear**: O modelo é dito linear se as funções e vínculos são representados inteiramente por equações lineares. Se uma ou mais das funções ou vínculos é representado por uma equação não linear o modelo é dito não linear.

- **determinístico** vs. **probabilístico**: Um modelo é dito determinístico quando a probabilidade de ocorrência de qualquer evento que ele esteja modelando é sempre 1 (ou 100%). Em um modelo probabilístico (ou estocástico), a probabilidade da ocorrência de um ou mais eventos modelados pode não ser 100%.

- estático vs. dinâmico: Um modelo estático não tem dentre as suas variáveis (exceto as de saída) o elemento tempo. Um modelo dinâmico considera o tempo como uma de suas variáveis utilizadas.

Problemas de modelagem matemática seguidamente são classificados como "caixa-preta" ou "caixa-transparente", de acordo com quanta informação do sistema está disponível a priori (BRATLEY, 1987). Um modelo "caixa-preta" representa um sistema do qual não se tem praticamente nenhuma informação a priori. Um modelo "caixa-transparente" é um sistema no qual toda informação necessária está à disposição. Praticamente todos os sistemas estão em algum ponto entre os dois extremos, portanto este conceito serve como um guia intuitivo. Usualmente é preferível utilizar tanta informação quanto possível para tornar o modelo mais preciso. Modelos "caixatransparente" são considerados mais precisos, porque se informações corretas forem utilizadas o modelo irá se comportar mais próximo da realidade. Informação a priori, seguidamente, vem na forma de conhecimento sobre o tipo de funções que relacionam as diferentes variáveis. Em modelos "caixa-preta" alguém pode tentar estimar tanto a forma dos relacionamentos entre as variáveis quanto os parâmetros numéricos nestas funções. Sem informação a priori deve-se tentar utilizar funções tão gerais quanto possível, para tentar cobrir todos os diferentes modelos que podem estar sendo representados. O problema de utilizar um grande conjunto de funções para descrever um sistema é que estimar os parâmetros se torna uma tarefa muito difícil quando a quantidade de parâmetros cresce. Qualquer modelo que não é totalmente uma "caixatransparente" contém alguns parâmetros que são utilizados para ajustar o modelo ao sistema que ele irá descrever. Se a modelagem é feita por uma rede neural, por exemplo, a otimização dos parâmetros é chamada de treinamento. Em modelagem mais convencional, através de funções matemáticas, os parâmetros são determinados por um ajuste de curvas.

A complexidade de um modelo é um fator importante a ser levado em conta no seu desenvolvimento. Quanto maior o nível de detalhamento requerido pelo modelo, maior o número de funções requeridas para a sua descrição. Quanto maior o número de equações envolvidas, maior será o custo computacional para a resolução destas equações. Num caso extremo a simulação pode ser computacionalmente mais cara do que a execução (ou construção) do sistema modelado. A incerteza também poderia aumentar, pois para cada equação adicionada, mais parâmetros são necessários. Um pouco de incerteza sempre é adicionada com cada parâmetro. O modelo de gravitação proposto por Newton, por exemplo, é uma aproximação que não leva em conta fatores como a dilatação do espaço-tempo para altas velocidades. Mas esse modelo serve muito bem para descrever a gravitação de corpos celestes quando as dimensões não são microscópicas nem as velocidades próximas à da luz.

Uma parte importante do processo de modelagem é a avaliação do modelo proposto. Como saber ser um modelo matemático descreve bem o sistema? Esta não é uma questão fácil de responder. Usualmente tem-se um conjunto de medidas do sistema que são utilizadas na criação do modelo. Se o modelo foi bem construído, o modelo irá

adequadamente mostrar as relações entre as variáveis do sistema para estas medidas. Mas aqui surgem algumas questões: Como saber se o modelo descreve bem as propriedades do sistema entre os dados medidos (interpolação)? Como saber se o modelo descreve bem eventos fora da faixa de dados medidos (extrapolação)? A abordagem mais comum é dividir os dados medidos em duas partes: dados de ajuste e dados de verificação. Os dados de ajuste são utilizados para ajustar o modelo, isto é, estimar parâmetros utilizados pelo modelo. Os dados de verificação são utilizados para avaliar o modelo.

Este capítulo propõe um modelo que toma como entrada parâmetros que descrevem o hardware gráfico e a aplicação a ser executada, e gera como saída uma estimativa de performance. O foco do modelo é o processador de fragmentos da GPU, sendo assumido que os demais estágios do pipeline gráfico têm uma carga muito menor do que a do processador de fragmentos — ou seja, os demais estágios não serão limitadores da performance (gargalos) da execução do programa. O modelo permite estimar a performance do hardware em relação aos recursos apresentados no capítulo anterior. O modelo proposto é composto por módulos associados, abstratamente em série e/ou em paralelo. A decomposição modular visa controlar o nível de complexidade a ser representada por cada módulo (ou parte) do modelo. A funcionalidade de cada módulo deve ser, idealmente, independente da funcionalidade de todos os outros módulos do modelo. A resposta do modelo é dada pela composição das respostas dos módulos.

### 4.1 Características do Modelo

A proposta de um modelo da performance da GPU é oferecer uma aproximação do comportamento de performance de uma aplicação gráfica. Aplicações que utilizam o processamento em GPUs, tais como programas de ray-tracing, simulação de fluídos, simulação de movimento de muitos corpos, poderiam ter um ganho de performance se fossem efetuadas modificações na maneira em que são implementadas ou mapeadas para a arquitetura da GPU. O modelo deve satisfazer algumas características:

- **linearidade:** a utilização de equações lineares reduz o conjunto de relacionamentos possíveis entre as variáveis. Com um número reduzido de relacionamentos entre as variáveis o controle sobre estes relacionamentos tornase mais simples.

- **determinismo:** os resultados apresentados pelo modelo, devem ser sempre reproduzíveis: para os mesmos dados de entrada, saídas iguais devem ser geradas. O hardware gráfico é determinístico: para um mesmo conjunto de dados e instruções, o resultado produzido pelo hardware gráfico é o mesmo.

- invariância temporal: o tempo não é considerado como uma variável de decisão, nem como parâmetro ou variável de estado. O tempo é representado apenas como uma variável de saída.

Existem outras características que são desejáveis na construção do modelo:

• **modularidade** – a implementação em estágios torna o modelo mais simples e controlável, uma vez que os resultados de uma etapa servem como

entrada para a próxima. É desejável que os estágios possam ser combinados de mais de uma maneira distinta. A combinação dos estágios permite ao simulador imitar o comportamento das diferentes associações existentes entre os recursos do hardware.

- modelo de desaceleração o modelo deve prever uma performance máxima possível e então com base nos parâmetros de entrada, essa performance é reduzida até à obtenção da estimativa de performance final. Na GPU, cada recurso que é utilizado diminui a performance de acordo com a carga a que está sujeito.

- o modelo deve produzir resultados em unidades comparáveis às medidas práticas esta característica é importante para avaliação do modelo. Os números retornados pelo modelo devem ser em unidades relevantes para a quantificação sendo realizada, por exemplo Quadros Por Segundo (FPS, do inglês *Frames Per Second*) ou tempo necessário para o desenho de um quadro.

- o modelo deve ser alimentado com informação sobre a utilização dos recursos o modelo deve considerar recursos disponibilizados pelo hardware, tais como freqüência de operação do pipeline, número de pipelines, número de fragmentos a serem processados, número de instruções presentes nas classes de programas que se pretende utilizar no hardware gráfico e características da aplicação acessos a texturas, tamanho de triângulos e coerência dos blocos de desvios.

## 4.2 Proposição do Modelo

O modelo proposto segue a caracterização discutida na seção anterior. Em termos de linearidade, o modelo utiliza funções que são lineares por partes em cada um dos módulos (estágios). Em termos de determinismo o modelo garante que quando alimentado com dados iguais, a saída será sempre a mesma. Em termos de invariância temporal, o modelo não utiliza o tempo como um de seus dados de entrada. O modelo estima a performance da GPU, quando alimentado com parâmetros da GPU, do programa e dos dados a processar. O modelo é composto de partes que podem ser associadas, abstratamente, em paralelo ou em série.

O modelo usa como parâmetros de entrada os mesmos recursos que se escolheu como relevantes para estimativa de performance – seção 3.4:

- A frequência de operação do processador de fragmentos

- O número de pipelines presente em cada processador de fragmentos

- O número de ciclos do programa sendo executado no processador de fragmentos

- O número de fragmentos por quadro

- O tamanho dos triângulos desenhados em cada quadro

- O tamanho do bloco de coerência dos fragmentos sendo processados

- O tamanho das texturas sendo acessadas

#### O formato de armazenamento das texturas

O modelo proposto é composto de vários estágios: um estágio inicial e uma série de módulos adicionais que determinam penalidades baseadas nas características da aplicação – figura 4.1. O estágio inicial fornece os resultados que seriam obtidos com a performance máxima. Os demais módulos são responsáveis por estimar a perda de performance devido a carga imposta aos recursos oferecidos pela GPU. Estes módulos são alimentados com uma série de parâmetros que são informados ao modelo pelo usuário. A seguir serão descritas as partes do modelo e como elas estão associadas umas com as outras.

Figura 4.1: Estrutura do modelo Proposto; O modelo é composto de estágios (lógicos) que vão aproximando sucessivamente a estimativa de performance.

### 4.2.1 Modelo Básico

Os dois primeiros estágios do modelo – figura 4.1 – são responsáveis pela estimativa de performance máxima para uma aplicação. O regime de mais alta performance da GPU requer que o programa de fragmentos utilizados não contenha instruções de tomada de desvio dinâmicas (sempre toma ou nunca toma os desvios), utilize triângulos grandes (mais de 1000 fragmentos por triângulo) e não realize acessos a texturas. Os parâmetros de entrada que permitem a estimativa de performance máxima são:

• velocidade do processador – velocidade do processador de fragmentos, frequência de operação, medida em ciclos por segundo (Hz). O processador de fragmentos tem a capacidade de aplicar um ciclo do programa de

fragmentos em um fragmento que está em um pipeline a cada ciclo da frequência de operação.

• **número de pipelines** — o processador de fragmentos em geral possui mais de um pipeline, sendo que por cada pipeline processa um ciclo do programa por fragmento por ciclo de relógio.