# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

#### **LUCAS MACHADO**

# **KL-Cut Based Remapping**

Thesis presented in partial fulfillment of the requirements for the degree of Master of Microelectronics

Prof. Dr. André Inácio Reis Advisor

Prof. Dr. Renato Perez Ribas Co-advisor

Porto Alegre, May 2013.

#### CIP - CATALOGING-IN-PUBLICATION

Machado, Lucas

KL-Cut Based Remapping / Lucas Machado. – Porto Alegre: PGMICRO da UFRGS, 2013.

88 f.:il.

Thesis (Master) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica, Porto Alegre, BR – RS, 2013. Advisor: André Inácio Reis; Co-advisor: Renato Perez Ribas.

1. Digital Circuits. 2. Logic Synthesis. 3. Technology Remapping. 4. Cut Enumeration. 5. KL-cuts. 6. Multiple output blocks. I. Reis, André Inácio. II. Ribas, Renato Perez. III. KL-Cut Based Remapping.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos Alexandre Netto

Vice-Reitor: Prof. Rui Vicente Oppermann

Pró-Reitor de Pós-Graduação: Prof. Aldo Bolten Lucion Diretor do Instituto de Informática: Prof. Flávio Rech Wagner Coordenador do PGMICRO: Prof. Ricardo Augusto da Luz Reis

Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

"Engineers like to solve problems.

If there are no problems handily available,

they will create their own problems to solve."

— Dilbert

## **ACKNOWLEDGEMENTS**

I thank my advisor André Reis for his ideas, support, good critics and sense of humor, which guided me during the development of this work. Also, I need to thank my co-advisor Renato Ribas, for his understanding, encouraging, personal and professional guidance, which helped me since I was an undergraduate student.

I am grateful for the help and support of the whole LogiCS group, but especially for some people: Osvaldo Martinello, who performed the work that inspired mine; Mayler Martins, which work on logic minimization (and all the possible variations we discussed) was crucial to get the results I had; Vinicius Callegaro, who helped me a lot on Java development, and implemented the mapping tool (with the very specific details) used in this work; and Oendel Merlo, who implemented the SDC parser in all variations I asked, which is also used in this work.

Also, I thank my friends from Lajeado and from Porto Alegre, which were there for me in all times, during school, during graduation, during my research time, and helped me to be the person I am today.

I need to thank immensely my family: my father Carson Machado, my mother Gisele Machado and my brother Jonas Machado. I missed them a lot during the time I was out, but they were, are and will always be my support to everything, and the giants that took me in their shoulders and made me look further.

Last but not least, my girlfriend Rafaela Bortolini has my deepest gratitude. She gave me the encouragement, the understanding, the love and caring more than I needed. She gave me the north and help that I needed in life, and also to finish this work.

This research was partially funded by Nangate Inc. under a Nangate/UFRGS research agreement, by CAPES and CNPq funding agencies, by FAPERGS under grant 11/2053-9 (Pronem), and by the European Community's Seventh Framework Programme under grant 248538 – Synaptic.

## **ABSTRACT**

This work introduces the concept of k-cuts and kl-cuts on top of a mapped circuit in a netlist representation. Such new approach is derived from the concept of k-cuts and kl-cuts on top of AIGs (and inverter graphs), respecting the differences between these two circuit representations. The main differences are: (1) the number of allowed inputs for a logic node, and (2) the presence of explicit inverters and buffers in the netlist. Algorithms for enumerating k-cuts and kl-cuts on top of a mapped circuit are proposed and implemented. The main motivation to use kl-cuts on top mapped circuits is to perform local optimization in digital circuit logic synthesis.

The main contribution of this work is a novel iterative remapping approach using *kl*-cuts, reducing area while keeping the timing constraints attained. The use of complex gates can potentially reduce the circuit area, but they have to be chosen wisely to preserve timing constraints. Logic synthesis commercial design tools work better with simple cells and are not capable of taking full advantage of complex cells. The proposed iterative remapping approach can exploit a larger amount of logic gates, reducing circuit area, and respecting global timing constraints by performing an STA (static timing analysis) check. Experimental results show that this approach is able to reduce up to 38% in area of the combinational portion of circuits for a subset of IWLS 2005 benchmarks, when compared to results obtained from logic synthesis commercial tools.

Another contribution of this work is a novel yield model for digital integrated circuits (IC) manufacturing, considering lithography printability problems as a source of yield loss. The use of regular layouts can improve the lithography, but it results in a significant area overhead by introducing regularity. This is the first approach that considers the tradeoff of cells with different level of regularity and different area overhead during the logic synthesis, in order to improve overall design yield. The technology remapping tool based on kl-cuts developed was modified in order to use such yield model as cost function, improving the number of good dies per wafer, with promising interesting results.

**Keywords:** Digital circuits, logic synthesis, technology mapping, cut enumeration, static timing analysis, remapping, lithography.

## Remapeamento baseado em cortes KL

### **RESUMO**

Este trabalho introduz o conceito de cortes k e cortes kl sobre um circuito mapeado, em uma representação netlist. Esta nova abordagem é derivada do conceito de cortes k e cortes kl sobre AIGs (and inverter graphs), respeitando as diferenças entre essas duas formas de representar um circuito. As principais diferenças são: (1) o número de entradas em um nodo do grafo, e (2) a presença de inversores e buffers de forma explícita no circuito mapeado. Um algoritmo para enumerar cortes k e cortes kl é proposto e implementado. A principal motivação de usar cortes kl sobre circuitos mapeados é para realizar otimizações locais na síntese lógica de circuitos digitais.

A principal contribuição deste trabalho é uma abordagem nova de remapeamento iterativo, utilizando cortes kl, reduzindo a área do circuito e respeitando as restrições de temporização do circuito. O uso de portas lógicas complexas pode potencialmente reduzir a área total de um circuito, mas elas precisam ser escolhidas corretamente de forma a manter as restrições de temporização do circuito. Ferramentas comerciais de síntese lógica trabalham melhor com portas lógicas simples e não são capazes de explorar eventuais vantagens em utilizar portas lógicas complexas. A abordagem proposta de remapeamento iterativo utilizando cortes kl é capaz de explorar uma quantidade maior de portas lógicas com funções lógicas diferentes, reduzindo a área do circuito, e mantendo as restrições de temporização intactas ao fazer uma checagem STA (análise temporal estática). Resultados experimentais mostram uma redução de até 38% de área na parte combinacional de circuitos para um subconjunto de *benchmarks* IWLS 2005, quando comparados aos resultados de ferramentas comerciais de síntese lógica.

Outra contribuição deste trabalho é um novo modelo de rendimento (yield) para fabricação de circuitos integrados (IC) digitais, considerando problemas de resolução da etapa de litografia como uma fonte de diminuição do yield. O uso de leiautes regulares pode melhorar bastante a resolução da etapa de litografia, mas existe um aumento de área significativo ao se introduzir a regularidade. Esta é a primeira abordagem que considera o compromisso (trade off) de portas lógicas com diferentes níveis de regularidade e diferentes áreas durante a síntese lógica, de forma a melhorar o yield do projeto. A ferramenta desenvolvida de remapeamento tecnológico utilizando cortes kl foi modificada de forma a utilizar esse modelo de yield como função custo, de forma a aumentar o número de boas amostras (dies) por lâmina de silício (wafer), com resultados promissores.

**Palavras-Chave:** circuitos digitais, síntese lógica, mapeamento tecnológico, enumeração de cortes, análise temporal estática, remapeamento, litografia.

# LIST OF FIGURES

| Figure 1.1 – Picture of the Moore's "Law" in the Computer History Museum showing         |              |

|------------------------------------------------------------------------------------------|--------------|

| the number of dies per wafer in linear scale, California, United States of America (Ju   |              |

| 2012)Figure 1.2: Logic synthesis in the standard cell design flow                        |              |

| Figure 2.1: Truth tables representing the (a) AND, (b) OR and (c) NOT logical            | . 21         |

|                                                                                          | . 26         |

| operationsFigure 2.2: Truth table representing function f                                |              |

| Figure 2.3: Schematic representation of (a) NOT, (b) AND and (c) OR operators            |              |

| Figure 2.4: Boolean network mapped from Equation (2.3)                                   |              |

| Figure 2.5: Boolean network mapped from Equation (2.5)                                   |              |

| Figure 2.6: Boolean functions in the same P-equivalence class                            |              |

| Figure 2.7: Boolean functions in the same NP-equivalence class.                          |              |

| Figure 2.8: Boolean functions in the same NPN-equivalence class.                         | . 29<br>. 29 |

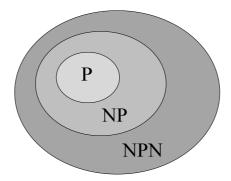

| Figure 2.9: Venn diagram showing the relationship between Boolean functions              | . 2)         |

| equivalence classes: P, NP and NPN                                                       | 30           |

| Figure 2.10: An example of directed acyclic graph                                        |              |

| Figure 2.11: Example of AND-inverter graph.                                              |              |

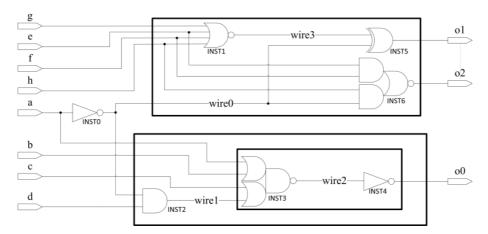

| Figure 2.12: Example of mapped circuit.                                                  |              |

| Figure 2.13: An example of a logic tree.                                                 | . 32         |

| Figure 2.14 An AIG example illustrating covering using kl-cuts. Nodes a, b, c, d, f, g   |              |

| and h are primary inputs. Nodes u and v are primary outputs. (a) A covering using 5-     |              |

| cuts. (b) A covering using 3-2-cuts. (MARTINELLO, 2010)                                  |              |

| Figure 2.15: Process to obtain cell delay and output transition time through the NLDI    |              |

| extracting the values from a Liberty file. It is necessary to know the input transition  | ŕ            |

| time and the output load, and perform a bilinear interpolation in the values read in the | e            |

| Liberty file.                                                                            | . 36         |

| Figure 3.1 Exaustive approach for computing R[f] <sub>P</sub> (HINSBERGER; KOLLA, 1988)  | 39           |

| Figure 3.2 Reducing search space by cutting non-maximal branches (HINSBERGER             | .,           |

| KOLLA, 1998)                                                                             | . 40         |

| Figure 3.3 Example of Boolean factoring using Functional Composition.                    |              |

| (MARTINS, 2012)                                                                          | . 41         |

| Figure 3.4 Cost calculation and the first cut of the tree removed. (CORREIA, 2004).      | . 42         |

| Figure 3.5 Example of logic tree covering (before inverter minimization).                |              |

| (CORREIA, 2004)                                                                          | . 42         |

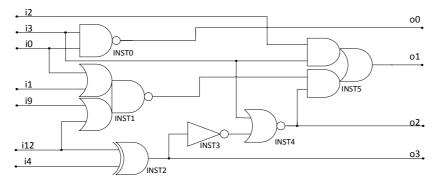

| Figure 4.1 Combinational circuit example to demonstrate k-cuts and kl-cuts               |              |

| computation.                                                                             |              |

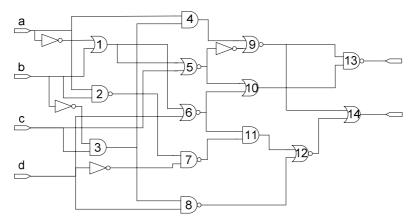

| Figure 4.2 And-inverter graph (AIG) representing a circuit.                              |              |

| Figure 4.3 Mapped circuit structurally similar to the AIG of Figure 4.2.                 |              |

| Figure 4.4 Pseudo-code for kl-cuts enumeration on top of a mapped circuit                | . 46         |

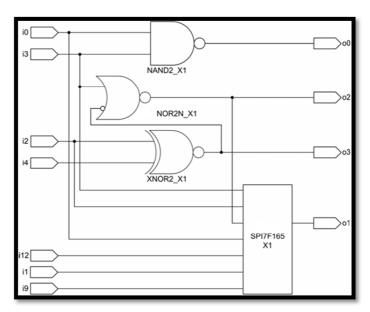

| Figure 4.5 Example of kl-cut found in a commercial benchmark                        | . 47 |

|-------------------------------------------------------------------------------------|------|

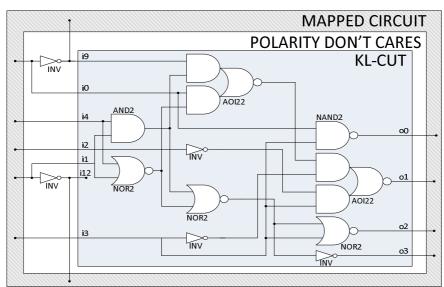

| Figure 4.6 Example of Figure 4.3 remapped with polarity don't cares information     | . 47 |

| Figure 4.7 Example of Figure 4.3 remapped without polarity don't cares information. | . 48 |

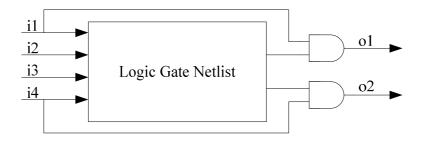

| Figure 4.8 Logic circuit example                                                    | . 48 |

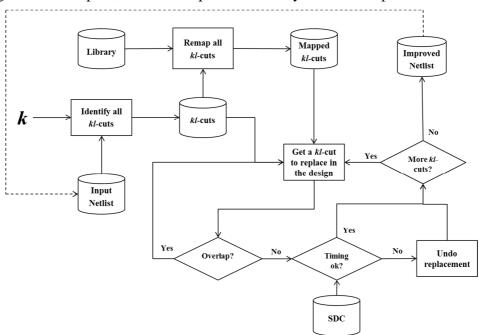

| Figure 5.1 Proposed kl-cut remapping flow                                           | . 49 |

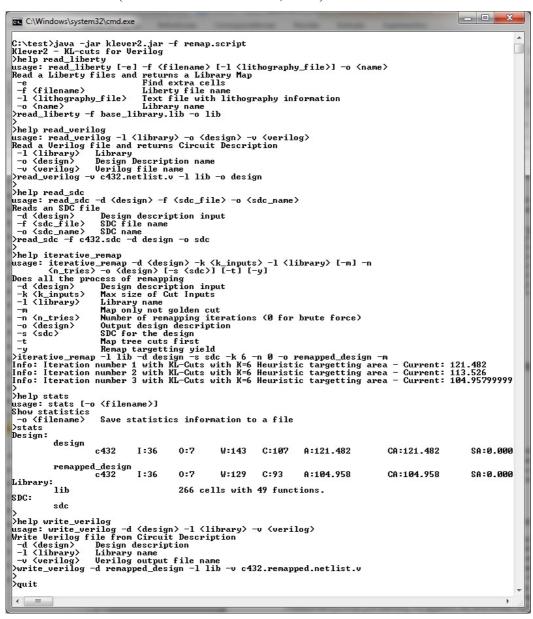

| Figure 5.2 Example of a complete remapping script                                   | . 50 |

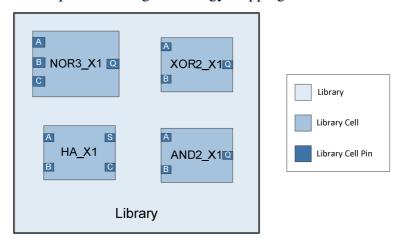

| Figure 5.3 Cell information read from a Liberty file                                | . 51 |

| Figure 5.4 Example of a library with four different logic gates.                    | . 52 |

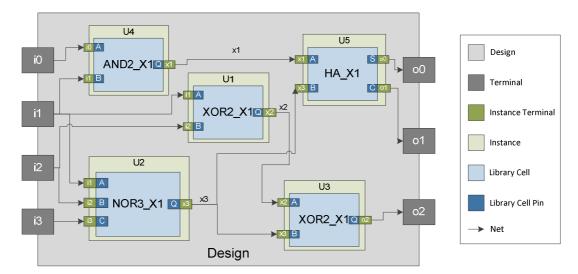

| Figure 5.5 Example of structural Verilog.                                           | . 52 |

| Figure 5.6 Example of the circuit data structure.                                   | . 53 |

| Figure 5.7 Example of kl-cut data structure representation                          | . 54 |

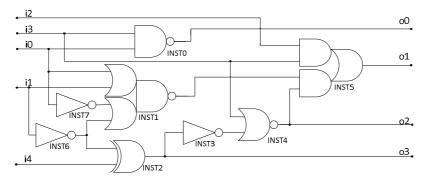

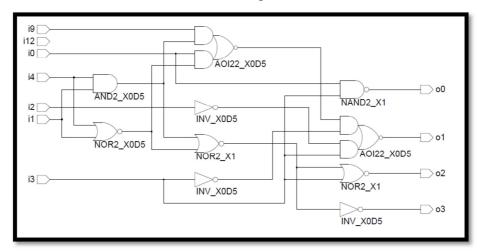

| Figure 5.8 Example of kl-cut input in the remapping approach                        | . 56 |

| Figure 5.9 Example of Figure 5.8 remapped by the proposed approach                  | . 57 |

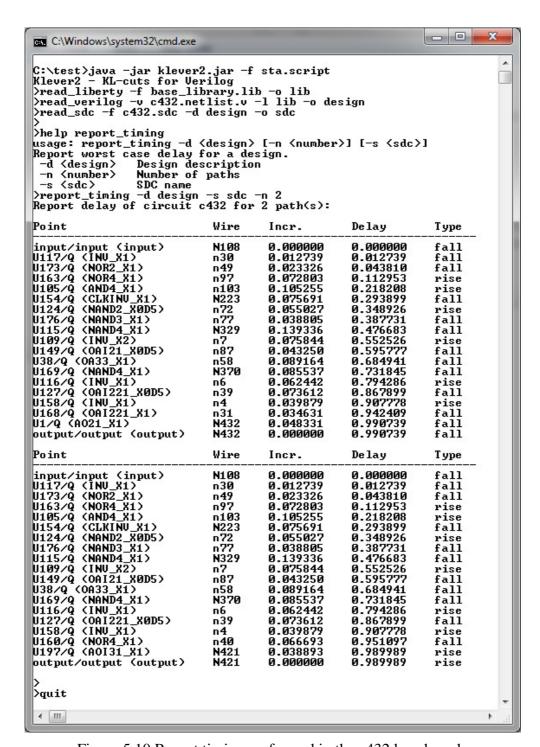

| Figure 5.10 Report timing performed in the c432 benchmark                           | . 59 |

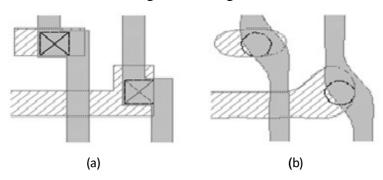

| Figure 6.1 Comparison between (a) designed layout and (b) lithography simulation of | f    |

| the designed layout.                                                                | . 62 |

| Figure 6.2 Passing technology information to the remapping tool                     | . 68 |

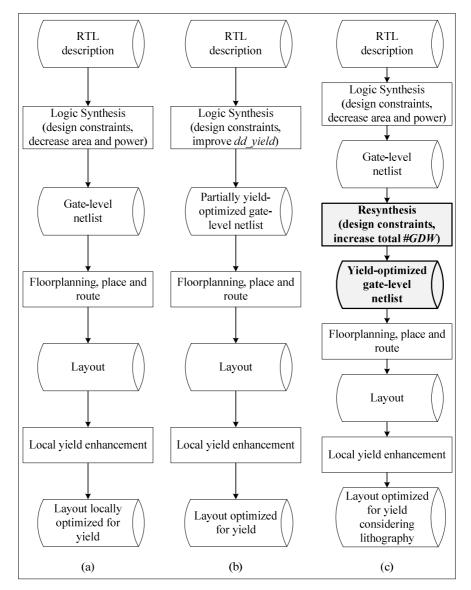

| Figure 6.3 (a) Standard "yield-aware" flow, (b) Flow proposed by Nardi (2004), and  | (c)  |

| the flow propose by this work.                                                      |      |

|                                                                                     |      |

# LIST OF TABLES

| Table 2.1: The k-cuts for all nodes of the AIG shown in Figure 2.11                                        | 33 |

|------------------------------------------------------------------------------------------------------------|----|

| Table 3.1 Relationships allowed in multi-level logic factoring                                             | 40 |

| Table 4.1 All k-cuts with k=5 for all nodes of the combinational circuit example of                        |    |

| Figure 4.1                                                                                                 | 44 |

| Table 5.1 Commands currently read in the STA engine developed                                              | 54 |

| Table 5.2 Original and factorized logic expressions of the kl-cut remapping example.                       | 56 |

| Table 5.3 Different paths analysed in the STA check                                                        | 58 |

| Table 6.1 Values of CHSci derived according to Equation (6.13) considering a wafer                         | of |

| 600 cm <sup>2</sup>                                                                                        |    |

| Table 6.2. Values of #GDW considering a die of 4 cm <sup>2</sup> on a wafer of 600 cm <sup>2</sup> for the |    |

| reference cells, and the same number of cell instances for 1D-restr and 2D-restr cells;                    |    |

| sld=1                                                                                                      |    |

| Table 7.1 Comparison of the worst delay given by a commercial STA tool and the ST                          | Α  |

| engine developed for this work.                                                                            | 72 |

| Table 7.2 Libraries used for area reduction experiments.                                                   | 72 |

| Table 7.3 ISCAS'85 benchmarks synthesized with commercial tool A                                           | 73 |

| Table 7.4 ISCAS'85 benchmarks synthesized with commercial tool B                                           | 74 |

| Table 7.5 ISCAS'85 benchmarks synthesized with commercial tool A remapped with                             |    |

| the proposed methodology.                                                                                  | 74 |

| Table 7.6 ISCAS'89 benchmarks synthesized with commercial tool A                                           | 75 |

| Table 7.7 ISCAS'89 benchmarks synthesized with commercial tool A remapped with                             |    |

| the proposed methodology.                                                                                  |    |

| Table 7.8 ITC'99 benchmarks synthesized with commercial tool A                                             |    |

| Table 7.9 ITC'99 benchmarks synthesized with commercial tool A remapped with wi                            |    |

| the proposed methodology.                                                                                  |    |

| Table 7.10 Libraries used for manufacturing improvement experiments                                        |    |

| Table 7.11 Manufacturability results for reference library.                                                |    |

| Table 7.12 Manufacturability results for 2D-gridded library.                                               |    |

| Table 7.13 Manufacturability results for 1D-restricted library.                                            |    |

| Table 7.14 Comparison between 1D-restricted library with reference library                                 | 81 |

# **CONTENTS**

| ABST      | FRACT                                        | 7  |

|-----------|----------------------------------------------|----|

| RESU      | UMO                                          | 9  |

| LIST      | OF FIGURES                                   | 11 |

|           | OF TABLES                                    |    |

| LIST      | OF ABBREVIATIONS AND ACRONYMS                | 17 |

| 1.        | INTRODUCTION                                 | 19 |

| 1.1       | Logic synthesis                              | 20 |

| 1.2       | Motivation                                   | 21 |

| 1.3       | Objectives                                   | 22 |

| 1.4       | Thesis organization                          | 23 |

| 2.        | TECHNICAL BACKGROUND                         | 25 |

| 2.1       | Boolean functions                            | 25 |

| 2.2       | Boolean expressions                          | 26 |

| 2.3       | Boolean networks                             | 27 |

| 2.4       | Equivalence of logic functions               | 28 |

| 2.5       | Data structures                              | 30 |

| 2.5.      | .1 Directed acyclic graphs                   | 30 |

| 2.5.      | .2 And-inverter graph                        | 30 |

| 2.5.      | .3 Mapped circuit                            | 31 |

| 2.5.      | .4 Logic tree                                | 31 |

| 2.6       | Cuts on AIGs                                 | 32 |

| 2.6.      | .1 K-cuts                                    | 32 |

| 2.6.      | .2 KL-cuts                                   | 33 |

| 2.7       | Cell library                                 | 34 |

| 2.8       | Technology mapping                           | 34 |

| 2.9       | Static Timing Analysis                       | 35 |

| <b>3.</b> | STATE-OF-THE-ART                             |    |

| 3.1       | Technology mapping                           | 37 |

| 3.2       | Boolean matching                             | 38 |

| 3.3       | Boolean factoring                            | 39 |

| 3.4       | Logic tree mapping                           |    |

| 4.        | CUTS ON MAPPED CIRCUITS                      |    |

| 4.1       | Differences between AIGs and mapped circuits | 43 |

| 4.1.      | .1 Number of nodes inputs                    | 43 |

| 4.1.      | .2 Inverters as nodes or edges               | 43 |

| 4.2       | K-cuts                                       | 44 |

| 4.3       | KL-cuts                                      | 45 |

| 4.4       | Enumeration algorithm                        | 46 |

| 4.5       | Polarity don't cares                         | 47 |

| 4.6        | Degrees of freedom                               | 48        |

|------------|--------------------------------------------------|-----------|

| <b>4.7</b> | Conclusion                                       | 48        |

| <b>5.</b>  | KL-CUT BASED REMAPPING                           | 49        |

| 5.1        | Remapping using KL-cuts                          |           |

| 5.2        | KL-cut remapping flow                            |           |

| 5.2        |                                                  |           |

| 5.2        | .2 Verilog parser and data structure             | 52        |

| 5.2        | .3 SDC parser and data structure                 | 53        |

| 5.2        | .4 KL-cut enumeration and data structure         | 53        |

| 5.2        | .5 KL-cut P-group                                | 54        |

| 5.2        | .6 KL-cut remapping approach                     | 55        |

| 5.2        | .7 KL-cut replacement                            | 56        |

| 5          | 5.2.7.1 KL-cuts overlapping                      | 57        |

| 5          | 5.2.7.2 STA checking engine                      | 57        |

| 5          | 5.2.7.3 Greedy choice and iterative remap        | 58        |

| 5.3        | Conclusion                                       |           |

| 6.         | MANUFACTURABILITY COST FUNCTION                  | <b>61</b> |

| 6.1        | Design for manufacturability                     | <b>61</b> |

| 6.2        | Yield background                                 |           |

| 6.3        | Yield model                                      | <b>63</b> |

| 6.4        | Yield as a cost function                         | <b>65</b> |

| 6.5        | Yield remapping tool                             | <b>67</b> |

| 6.6        | Conclusion                                       | <b>69</b> |

| <b>7.</b>  | RESULTS                                          | <b>71</b> |

| <b>7.1</b> | Precision of STA engine                          | <b>71</b> |

| <b>7.2</b> | Area as a cost function                          | <b>71</b> |

| 7.2        | r                                                |           |

| 7.2        | 2 ISCAS benchmarks area results                  | 72        |

|            | '.2.2.1 ISCAS' 85 benchmarks area results        |           |

|            | 7.2.2.2 ISCAS'89 benchmarks area results         |           |

| 7.2        | .3 ITC'99 benchmarks area results                | 76        |

| 7.3        | Manufacturability as a cost function             | <b>78</b> |

| 7.3        |                                                  |           |

| 7.3        | .2 ISCAS'85 benchmarks manufacturability results |           |

| 8.         | CONCLUSIONS AND FUTURE WORK                      | 83        |

| 8.1        | Future work                                      | 84        |

| REFI       | ERENCES                                          | 85        |

## LIST OF ABBREVIATIONS AND ACRONYMS

AIG And-inverter graph

ASIC Application Specific Integrated Circuit

CAD Computer-Aided Design

CHS Criticality of Hot Spots

CMOS Complementary Metal Oxide Semiconductor

CMP Chemical Metal Polishing

DAG Directed acyclic graph

DFM Design For Manufacturability

DH Design House

EDA Electronic Design Automation

FC Functional Composition

GDW Good Dies per Wafer

IWLS International Workshop of Logic & Synthesis

LEF Library Exchange Format

HDL Hardware Description Language

NLDM Nonlinear Delay Model

NPN Negation Permutation Negation

OPC Optical Proximity Correction

PI Primary Input

PO Primary Output

POS Product of Sums

PSM Phase Shift Mask

QoR Quality of Results

RET Resolution Enhancement Technique

ROBDD Reduced Ordered Binary Decision Diagram

RTL Register Transfer Level

SDC Synopsys Design ConstraintsSLD Severity of Lithography Defects

SOP Sum of Products

STA Static Timing Analysis

VLSI Very-Large-Scale Integration

### 1. INTRODUCTION

The world has changed a lot in the past fifty years. Most areas of human knowledge, if not all, have improved significantly and these remarkable advancements happened much faster than ever before. Problems that no one could ever think back then are now solved in smartphones. The medicine has great diagnostic machines, a car is able to drive itself taking pictures of the streets, and talking with someone anywhere in the world is not a problem at all. All these achievements in this brave new world have a major source: the integrated circuits (IC). In 1965, Gordon Moore stated that the number of transistors in a chip would double every 24 months (MOORE, 1965), as seen in the Figure 1.1. This trend predicted by Moore guided the evolution of computers and its use in every field. Also, the use of computers to create new and better computers emerged the electronic design automation (EDA) industry, creating a virtuous circle and enabling this fast growing in technology in the recent years.

Figure 1.1 – Picture of the Moore's "Law" in the Computer History Museum showing the number of dies per wafer in linear scale, California, United States of America (June, 2012)

Looking at the Figure 1.1, a question hangs in the air: "how long will this trend continue?" The scaling down of the current technology, based on MOS transistors, is reaching a physical limit. The semiconductor most used to manufacture ICs is the Si, and the lattice spacing of a Si crystal is around 0.5 nm (SZE, 2006). This means that there are approximately 10 atoms of Si (or doping elements) within 5 nm. A variability of 1 atom (which is very low) in the manufacturing process of 5 nm transistors will likely produce 10% of variability between transistors (which is quite a lot). This phenomenon is known as discrete random doping and it is just one of several different effects that exist in deep nanometer scaling of current CMOS technology (SZE, 2006). Nowadays, the manufacturing process is about 20 nm and has already lots of obstacles to make it work. Clearly, this trend will likely have an end soon.

Besides CMOS scaling, several research topics investigate the next technology to substitute CMOS, such as quantum computing, graphene, and carbon nanotubes. However, until now, no feasible and effective substitute for CMOS has been found. On the other hand, besides decreasing the size of transistors and investigating new technologies, there are good alternatives that can be investigated and developed in order to produce better and cheaper ICs, even with the current CMOS technology. For instance, developing more powerful EDA tools, with higher quality-of-results (QoR), will improve current IC performance and lower down its costs.

Before EDA tools, ICs were designed by hand. The first microprocessors were drawn in engineering paper and color pencils, and then manufactured in primitive semiconductor planar technology. After the first computers, it was possible to create tools to help with the drawings, and then to place the transistors and route its wires. In mid-80's, the hardware description languages (HDL) emerged, changing completely the way that ICs were designed. The logic synthesis tools starting from RTL descriptions were introduced, trying to obtain the best hardware implementation for a given RTL hardware description. Notice that logic synthesis tasks are very complex since many variables must be taken into account, and trying all possibilities is not computationally feasible. Consequently, in order to obtain good results, within reasonable time-to-market, several heuristics were created, generating sub-optimal results. Therefore, logic synthesis tools still have room for improvements and this work tries to explore this.

# 1.1 Logic synthesis

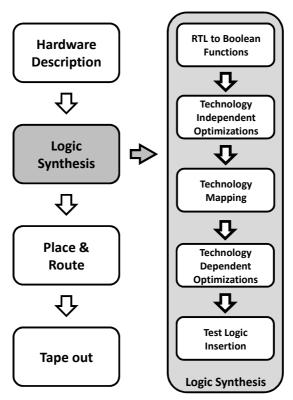

Logic synthesis is an important area of study in the field of very large scale integration (VLSI) design automation, being responsible for the transformation of a circuit behavior description into a netlist of logic gates for a given technology, i.e. a digital mapped circuit. The logic synthesis is also an important process in the application specific integrated circuit (ASIC) standard cell design flow, followed by the physical synthesis where the placement and the routing of the logic gates are performed, as illustrated in Figure 1.2.

According to Figure 1.2, the logic synthesis process can be divided into five stages. In the first step, a hardware description is compiled and transformed in a technology independent circuit representation. This circuit representation can be an and-inverter graph (AIG), for instance. Then, several optimizations are performed in this circuit representation. In AIGs, it is important to reduce the number of nodes (related to area) and reduce the logic depth (related to delay) (MISHCHENKO, 2006). The next step is to map the circuit representation using logic gates, usually given by a technology standard cell library, known as technology mapping. After a covering step, several

optimizations are performed in order to: (1) meet the design constraints, such as delay; and (2) make cell area and power consumption as low as possible. The last step is the test logic insertion.

As already been stated, logic synthesis is a very complex task. The necessity of having a reasonable solution within time-to-market led to several heuristics, generating sub-optimal results, and left room for improvements. Finding optimal solutions may be feasible only for small circuits. In order to improve the QoR, an additional step was proposed, after the logic synthesis process. This extra phase, known as remapping or resynthesis (DE MICHELI, 1994; KUNZ, 1997), performs local transformations at the gate level (netlist) in order to improve the cost function of interest, such as cell area and power consumption.

Figure 1.2: Logic synthesis in the standard cell design flow.

#### 1.2 Motivation

Before the EDA industry and the scaling down of the transistor size, the development of ICs was very straightforward. There was a transistor network, which should be handmade and drawn in engineering papers, and all the process was understood and made by the development team. When the EDA industry began, enabling the development of larger circuits, along with the scaling down of the transistor size, numerous challenges appeared. Nowadays, besides the designed circuit working in the performance defined and having the smallest cell area and power consumption as possible, there are other concerns such as manufacturability, routing congestion, interconnection delay, leakage power, aging effects, radiation effects, lithography issues, and so on.

As the challenges arised, the EDA developers had to improve their tools in order to handle these new bottlenecks. The tools are being used and changed in the past 25

years, passing from several different generations. Every new problem tackled by the tool certainly made its code harder to read and harder to change. There is a rumor that the core of the world's most used commercial logic synthesis tool, is a black box that will probably never be changed again. Notice that, if new problems emerge or if new techniques to solve the current problems are discovered, there are basically two ways to incorporate them. An approach could be redoing all the code to perform all logic synthesis process, incorporating the new ideas and tackling the new problems. However, it is important to understand that a tool of more than 25 years of success will hardly be substituted by a new tool in any design house (DH). Also, the tool gives already very good results.

The motivation of this work is to provide an alternative approach: to perform the remapping of the gate level netlist given by a commercial tool, and to improve one or more cost functions of interest, using new strategies and tackling new problems that may arise.

## 1.3 Objectives

Remapping or resynthesis is not a new idea. Different approaches for resynthesis are already used to improve circuits after mapping, or even during the technology independent phase. In the work of (FIŠER, 2010), it is shown that the ABC tool (Berkeley Logic Synthesis and Verification Group, 2012) is able to achieve better results by performing iterative synthesis in random smaller parts of the circuit (subcircuits) instead of performing synthesis in the circuit as a whole. It is important to notice that local optimizations can be applied in the results of different phases of logic synthesis: technology independent and technology dependent. From a technology independent point-of-view, local context can be extracted through windowing (MISHCHENKO, 2006) or by k-cut enumeration (PAN, 1994). The k-cuts approach can be considered a superior method to derive sub-circuits, since it is able to control the number of inputs of the Boolean functions present in a sub-circuit. For this reason, variations of k-cuts have been proposed, such as factor cuts (CHATTERJEE, 2006-b), priority cuts (MISHCHENKO, 2007) and kl-cuts (MARTINELLO JR., 2010). Interestingly, these advances in k-cut enumeration are strongly linked to the AIG data structure, and therefore to the technology independent phase of logic synthesis.

Approaches to local optimization of mapped circuits (i.e. remapping) adopt circuit partitioning techniques that do not consider the complexity of the Boolean functions in the resulting sub-circuits. For this reason, these remapping approaches lose local context, and need to investigate the surrounding environment (BENINI, 1998) to detect controllability and observability don't cares (SAVOJ, 1990), i.e. degrees of freedom. In the context of k-cuts in AIGs, the observability don't cares are incorporated in the sub-circuits due to the use of k-cut dominance.

The objective of this work is to bring the concept of k-cuts and kl-cuts from AIGs in order to be used on top of mapped netlists in a context of technology remapping. The kl-cut based remapping, when compared to the approaches proposed in the literature, introduces three important advantages: (1) to control the support cardinality; (2) all outputs affected by the cut inputs are found, making possible the logic sharing between outputs; and (3) a new concept of mapping flexibility through polarity don't cares, which is explained further in Section 4.5.

In order to validate the *kl*-cuts approach, an algorithm to enumerate *kl*-cuts on top of mapped circuits is proposed and implemented. Moreover, technology mapping techniques are implemented in order to improve a given cost function. In this work, two cost functions are considered: area and manufacturability. Furthermore, a static timing analysis (STA) tool is implemented in order to improve the cost functions of interest without affecting the performance obtained by the commercial tool. Hence, everything is put in a remapping flow and results are presented.

## 1.4 Thesis organization

The remaining of this thesis is organized as follows.

**Chapter 2:** *Technical background* – Provides the technical knowledge necessary to understand the concepts presented herein.

**Chapter 3:** *State-of-the-art* – Gives a broad vision of technology mapping and also provides the state of the art in important related topics to this thesis, such as Boolean factoring, Boolean matching and logic tree covering.

Chapter 4: Cuts on mapped circuits – Presents the first contribution of this thesis, the enumeration of k-cuts and kl-cuts on top of mapped circuits, and algorithms used for that.

**Chapter 5:** *KL-cut based remapping* – Describes the second contribution of this work, i.e. a complete flow, which is able to remap a circuit by extracting *kl*-cuts and replacing back, reducing circuit area.

**Chapter 6:** *Manufacturing cost function* – This is the third contribution of this work, which is a discussion about yield and lithography as a logic synthesis cost function, improving the number of good dies per wafer.

**Chapter 7:** Results – Presents and discusses the experimetal results. First, an analysis of the STA engine developed for this work is shown. Then, remapping results for IWLS 2005 benchmarks (IWLS 2005 benchmarks, 2012) are shown, reducing circuit area. The use of complex logic gates is also discussed. Finally, results of remapping using the manufacturing cost function are presented.

**Chapter 8:** Conclusions and future work – Outlines the conclusions and major contributions of this work, and also indicates future works.

## 2. TECHNICAL BACKGROUND

This chapter provides a review of technical concepts that are useful to the complete understanding of the remaining of this work. It comprises logic synthesis and logic circuit design topics, such as Boolean functions, expressions and networks, equivalence classes of logic functions, logic synthesis data structures, cuts on AIG, description of cell library, technology mapping, and static timing analysis. Readers with background knowledge on these topics can skip the following sections without loss in the understanding of the following chapters.

#### 2.1 Boolean functions

The Boolean set is defined as  $B = \{0, 1\}$ , where 0 and 1 represent two well defined logic states, such as true (1) or false (0). An *n*-dimensional Boolean set  $B^n$ , is composed of  $2^n$  distinct *Boolean vectors* with length *n*. For instance,  $B^1 = \{0, 1\}$ ,  $B^2 = \{00, 01, 10, 11\}$ ,  $B^3 = \{000, 001, 010, 011, 100, 101, 110, 111\}$ ,  $B^4 = \{0000, 0001, 0010, 0011, 0100, 0101, 0110, 0111, 1000, 1001, 1010, 1011, 1100, 1101, 1111\}$ , and so on.

A Boolean function f is a function that relates every element in the n-dimensional Boolean set  $B^n$  (the function domain) into one element of the Boolean set B (the function image), such that  $f: B^n \to B$ . This means that each Boolean vector of length n is associated by a Boolean function to either 0 or 1. The Boolean function f has f has f has f boolean variables. A Boolean variable can assume any value of f has f i.e. it can assume the values 0 or 1. A Boolean vector is also known as f variable assignment, which means that each position in the Boolean vector represents a variable assigned either to 0 or 1. For instance, the Boolean vector 0000 has the four variables assigned to 0.

A very usual way to represent a Boolean function is a *truth table*, such as the tables of Figure 2.1. On the left side of each table, each row represents a Boolean vector and each column represents the corresponding Boolean variables. On the right side, the columns represent the function names and the rows represent the value assumed by the function for the corresponding Boolean vector.

There are several logical operations that can be done with Boolean variables in order to generate different Boolean functions. The three basic Boolean operations are: AND  $(f_1)$ , OR  $(f_2)$  and NOT  $(f_3)$ , as seen in Figure 2.1. The operations AND and OR are binary, meaning that they must be applied to at least two operands. The AND operation returns 1 only if all operands are 1, returning 0 otherwise, as seen in Figure 2.1a. The OR operation returns 0 only if all operands are 0, returning 1 otherwise, as seen in Figure 2.1b. The NOT operation is a unary operation, which means that it is applied to only one operand, and applies a negation of the operand: if the operand is 0, the NOT returns 1, and vice-versa, as seen in Figure 2.1c.

| Α | В   | f1 |   | A | В   | f2 |   |    |            |

|---|-----|----|---|---|-----|----|---|----|------------|

| 0 | 0   | 0  |   | 0 | 0   | 0  |   | A  | f3         |

| 0 | 1   | 0  |   | 0 | 1   | 1  |   | 0  | 1          |

| 1 | 0   | 0  | • | 1 | 0   | 1  | • | 1  | 0          |

| 1 | 1   | 1  | • | 1 | 1   | 1  | • |    |            |

|   | (a) | •  |   |   | (b) |    |   | (0 | <b>c</b> ) |

Figure 2.1: Truth tables representing the (a) AND, (b) OR and (c) NOT logical operations.

## 2.2 Boolean expressions

Besides a truth table, a Boolean function can also be represented as a *Boolean expression*. In this case, the Boolean operators are represented as the following symbols: AND operator is represented as \* or ·, the OR operator is represented as +, and the NOT operator is represented as ! or ¬. These operators are applied to the variables of the function in order to represent correctly its functionality. Each time a Boolean variable appears in a Boolean expression, it is counted as one literal. The implementation of a Boolean expression with fewer literals is preferred, since it will likely use less logic elements, as discussed in Section 2.3.

Although a Boolean expression represents exactly one Boolean function, a Boolean function can be represented by numerous Boolean expressions. For example, let's take a look on the function f, represented in the truth table of Figure 2.2. Extracting the Boolean vectors that evaluate the function to 1, and representing them as Boolean expressions in order to represent the correct functionality of f, the result is the Equation (2.1), a sum-of-products (SOP).

| a        | b | c | d      | f                                              |

|----------|---|---|--------|------------------------------------------------|

| 0        | 0 | 0 | 0      | 0                                              |

| 0        | 0 | 0 | 1      | 1                                              |

| 0        | 0 | 1 | 0      | 1                                              |

| $0 \\ 0$ | 0 | 1 | 1      | 1                                              |

| 0        | 1 | 0 | 0      | 0                                              |

| 0        | 1 | 0 | 1      | 0                                              |

| $0 \\ 0$ | 1 | 1 | 0      | 0                                              |

| 0        | 1 | 1 |        | 1<br>0<br>0<br>0<br>1<br>0<br>0<br>0<br>1<br>0 |

| 1        | 0 | 0 | 1<br>0 | 0                                              |

| 1        | 0 | 0 | 1      | 0                                              |

| 1        | 0 | 1 | 0      | 0                                              |

| 1        | 0 | 1 | 1      | 1                                              |

| 1        | 1 | 0 | 0      | 0                                              |

| 1        | 1 | 0 | 1      | 1                                              |

| 1        | 1 | 1 | 1<br>0 | 1                                              |

| 1        | 1 | 1 | 1      | 1                                              |

Figure 2.2: Truth table representing function *f*.

$$f = (! \ a * ! \ b * ! \ c * \ d) + (! \ a * ! \ b * ! \ d * \ c) + (! \ a * ! \ b * \ c * \ d) + (! \ a * \ b * \ c * \ d) + (! \ a * \ b * \ c * \ d) + (! \ a * \ b * \ c * \ d)$$

$$+ (! \ b * \ a * \ c * \ d) + (! \ c * \ a * \ b * \ d) + (! \ d * \ a * \ b * \ c) + (a * \ b * \ c * \ d)$$

$$(2.1)$$

Similarly, extracting the Boolean vectors that evaluate the function to 0, and representing them as Boolean expressions in order to represent the correct functionality of f, the result is the Equation (2.2), a product-of-sums (POS).

$$f = (! \ a + ! \ b + ! \ c + ! \ d) * (! \ a + ! \ c + ! \ d + b) * (! \ a + ! \ c + b + d) * (! \ a + ! \ d + b + c)$$

$$* (! \ b + ! \ c + ! \ d + a) * (! \ b + ! \ c + a + d) * (! \ b + ! \ d + a + c) * (! \ c + ! \ d + a + b)$$

$$(2.2)$$

These two representations are straightforward, since they simply use the representation of the Boolean vectors as expressions, applying the correct logic operations in order to represent correctly the Boolean function. However, the SOP and POS representations have several literals. In Equation (2.1) and Equation (2.2) there are 32 literals each. In order to reduce the number of literals, the first approaches were with two-level minimizations (COUDERT, 1994). The two-level minimizations of the SOP and POS representations are in Equations (2.3) and (2.4), respectively, with 14 literals.

$$f = (!a * !b * c) + (!a * !b * d) + (a * b * c) + (a * b * d) + (c * d)$$

(2.3)

$$f = (!a + b + c) * (!a + b + d) * (!b + a + c) * (!b + a + d) * (c + d)$$

(2.4)

Further optimizations can be applied in order to decrease even more the number of literals, through multi-level minimizations, also known as *Boolean factoring* (BRAYTON, 1987). More details about Boolean factoring can be seen in Section 3.3. For instance, the minimal literal count expression of the function f can be seen in Equation (2.5), with 8 literals.

$$f = !((!c*!d) + ((!c+!d)*(a+b)*(!a+!b)))$$

(2.5)

#### 2.3 Boolean networks

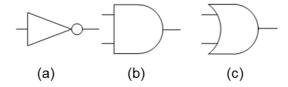

Figure 2.3 shows the schematic representation of the basic Boolean operators. In order to represent a Boolean function through a *Boolean network* schematic, the symbols of Figure 2.3 can be used to represent its implementation. Notice that the circle in the output of the NOT operator representation in Figure 2.3a, also known as inverter, shows the negation of this operator. The Figure 2.3b shows the representation of an AND operator, and the Figure 2.3c shows the representation of an OR operator. The NAND operator is created by adding a circle in the output of an AND operator, generating the AND output negated. The NOR operator is created by adding a circle in the output of an OR operator, generating the OR output negated. The NAND and NOR operators can be seen in Figure 2.4 and Figure 2.5.

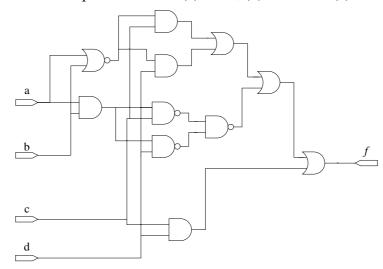

The Boolean network can be directly derived from the Boolean expression. This derivation is not straightforward from the truth table representation, for example. Also, the representation of a Boolean function as a Boolean network shows the importance of reducing the number of literals in the corresponding Boolean expression. Notice that the the minimized SOP expression of f (Equation (2.3), with 14 literals) produces a larger Boolean network than the minimum expression of f (Equation (2.5), with 8 literals), as seen in Figure 2.4 and Figure 2.5.

Figure 2.3: Schematic representation of (a) NOT, (b) AND and (c) OR operators.

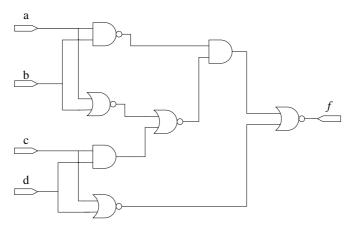

Figure 2.4: Boolean network mapped from Equation (2.3).

Figure 2.5: Boolean network mapped from Equation (2.5).

## 2.4 Equivalence of logic functions

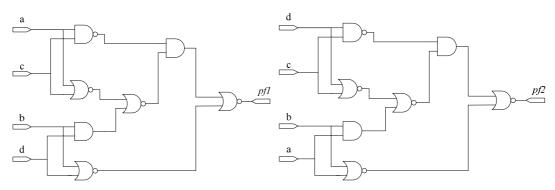

Consider the following operations in logic functions: (P) permutation of one or more input variables; (Ni) negation of one or more input variables; and (No) negation of the function. If a function g is equivalent to function h by operation P, then the functions g and h are P-equivalent. In Figure 2.6, two Boolean networks are shown representing two distinct Boolean functions pf1 and pf2, but in the same P-equivalence class (also at the same P-equivalence class that function f in Figure 2.5).

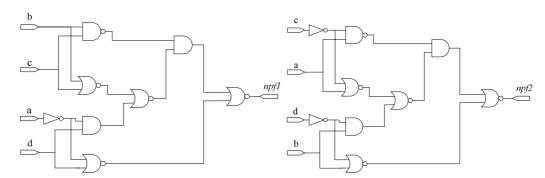

Also, if a function  $g_I$  is equivalent to a function  $h_I$  by performing the operations P and Ni, then the functions  $g_I$  and  $h_I$  are *NP-equivalent*. In Figure 2.7, two Boolean networks are shown representing two distinct Boolean functions npfI and npf2, but at the same NP-equivalence class (also at the same NP-equivalence class that function f in Figure 2.5, and functions pfI and pf2 in Figure 2.6).

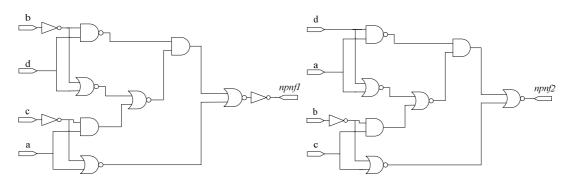

Finally, if a function  $g_{12}$  is equivalent to a function  $h_{12}$  by performing the operations P, No and Ni, then the functions  $g_{12}$  and  $h_{12}$  are NPN-equivalent. In Figure 2.8, two Boolean networks are shown representing two distinct Boolean functions npnf1 and npnf2, but at the same NPN-equivalence class (also in the same NPN-equivalence class that function f in Figure 2.5, functions pf1 and pf2 in Figure 2.6, and functions npf1 and npf2 in Figure 2.7).

Figure 2.6: Boolean functions in the same P-equivalence class.

Figure 2.7: Boolean functions in the same NP-equivalence class.

Figure 2.8: Boolean functions in the same NPN-equivalence class.

Notice that in all these equivalence classes, the core of the circuit remained the same. This characteristic is very useful in the technology mapping phase of logic synthesis. Also, these equivalence classes have a relationship, shown in the Venn diagram of Figure 2.9. For instance, there are a total of 65,536 Boolean functions with four variables, which can be classified in 3984 P-equivalence classes, 402 NP-equivalence classes or 222 NPN-equivalence classes (SASAO, 1999).

Figure 2.9: Venn diagram showing the relationship between Boolean functions equivalence classes: P, NP and NPN.

#### 2.5 Data structures

A Boolean network can be represented through different data structures. Each data structure is more appropriate for different objectives and manipulations. Several data structures are used in this work, and the following subsections describe them.

### 2.5.1 Directed acyclic graphs

Graphs are widely used data structures in computer science, due to its efficient way of representing things and the also efficient algorithms created for graphs data structures. In order to represent a combinational circuit using a graph, it is necessary to guarantee the following conditions: (1) the edges must have a direction, i.e. the edges are directed; and (2) there are no cycles (cycles are prohibited in combinational circuits). These restrictions led to the use of directed acyclic graphs (DAGs) to represent circuits. DAGs can be used as a direct translation of a Boolean network into a graph data structure. An example of DAG can be seen in Figure 2.10.

Figure 2.10: An example of directed acyclic graph.

#### 2.5.2 And-inverter graph

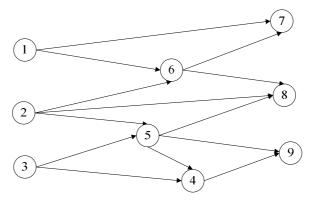

An AND-inverter graph (AIG) is a specific type of a DAG, where each node has either zero incoming edges, the primary inputs (PIs), or two incoming edges, the AND nodes. Each edge can be negated or not. Some nodes are marked as primary outputs (POs). AIGs were created in order to perform fast transformations of circuits, since it is a very simple data structure (MISHCHENKO, 2006). An example of an AIG can be seen in Figure 2.11, where the nodes a, b and c are PIs, and the rest of the nodes are AND nodes. Also, the nodes i, h, g and f are marked as POs.

Figure 2.11: Example of AND-inverter graph.

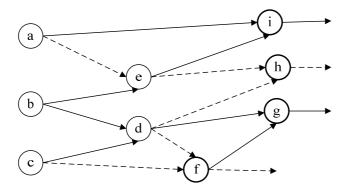

### 2.5.3 Mapped circuit

A combinational mapped circuit C is a specific type of DAG with three types of nodes: the PI nodes, the *logic gate* nodes and the PO nodes. If a node of C has no incoming edges and one or more outgoing edges, it is a PI. If a node of C has up to m incoming edges, where m is an integer value such that  $m \ge 1$ , and one or more outgoing edges, it is a *logic gate* node. If a node of C has one incoming edge and no outgoing edges, it is a PO. An example of mapped circuit can be seen in Figure 2.12.

Figure 2.12: Example of mapped circuit.

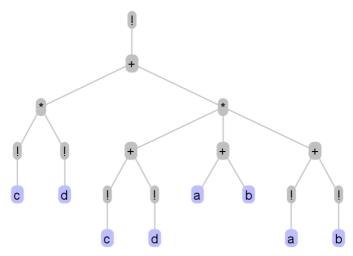

### 2.5.4 Logic tree

A tree is a particular case of DAG in which the fanout of every node is equal to one. A logic tree is a specific type of tree in which the internal nodes are logic nodes, which represent logic functions such as AND and OR. A logic tree is also a direct translation of a Boolean expression into a data structure. An example of a logic tree is depicted in Figure 2.13.

It is computationally hard to map a DAG representing a circuit into logic gates, due to the several possibilities of mapping. The partitioning of DAG into several logic trees,

i.e. a forest of logic trees, reduces greatly the complexity of the DAG technology mapping, at the cost of reducing the solution space and producing a mapping result of lower quality. This approach will be explored in this work.

Figure 2.13: An example of a logic tree.

#### 2.6 Cuts on AIGs

For scalability reasons, AIG is being used to represent circuits, since it is a very simple data structure (MISHCHENKO, 2006). Several transformations can be done with AIGs in order to reduce the number of nodes (area) or decrease the logic depth (delay). One way is to extract parts of an AIG through cuts and improve them locally. A cut of a node n in an AIG is a set of nodes c such that every path between a PI and n contains a node in c. A cut of n is irredundant if no subset of it is also a cut. This section describes k-cuts and kl-cuts on AIGs.

#### 2.6.1 K-cuts

A k-feasible cut of an AIG  $\mathcal{G}$  is an irredundant cut containing k or fewer inputs. Let A and B be two sets of cuts, and let the auxiliary operation  $\bowtie$  be the operation described in the Equation (2.6).

$$A \bowtie B \equiv \{a \cup b \mid a \in A, b \in B, |a \cup b| < k\}$$

(2.6)

Notice that the  $\bowtie$  operation is commutative, since the  $\cup$  operation is also commutative. Let  $\Phi_{\mathcal{K}}(n)\Phi_{K}$  be the set of k-feasible cuts of  $n \in \mathcal{G}$  and, if n is an AND node, let  $n_{1}$  and  $n_{2}$  be its inputs. Then,  $\Phi_{\mathcal{K}}(n)\Phi_{K}$  is defined recursively as described in Equation (2.7).

$$\Phi_{\mathcal{K}}(n) \equiv \begin{cases} \{n\}, & : n \text{ is a PI} \\ \{n\} \cup \{\Phi_{\mathcal{K}}(n_1) \bowtie \Phi_{\mathcal{K}}(n_2)\} & : otherwise \end{cases}$$

(2.7)

The  $\bowtie$  operation can easily remove the redundant cuts by comparing the cuts with one another. The k-cuts for all nodes of the AIG shown in the Figure 2.11 are described in Table 2.1.

| Node | k-cuts                                       |

|------|----------------------------------------------|

| a    | {a}                                          |

| b    | {b}                                          |

| С    | {c}                                          |

| d    | {d}, {b, c}                                  |

| e    | {e}, {a, b}                                  |

| f    | {f}, {d, c}, {b, c}                          |

| g    | {g}, {d, f}, {d, c}, {b, c}                  |

| h    | {h}, {e, d}, {a, b, d}, {b, c, e}, {a, b, c} |

| i    | $\{i\}, \{a, e\}, \{a, b\}$                  |

Table 2.1: The *k*-cuts for all nodes of the AIG shown in Figure 2.11.

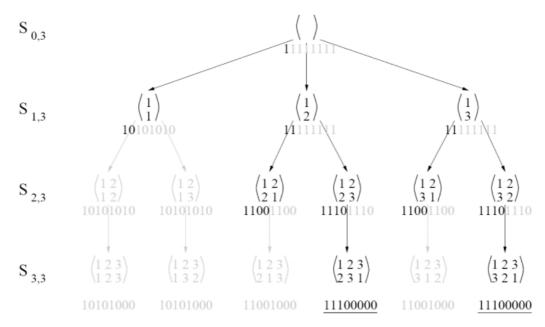

#### **2.6.2** KL-cuts

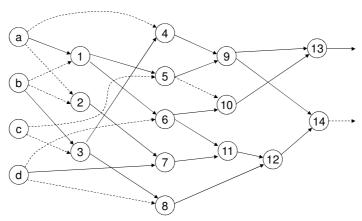

The *k*-cuts are an efficient way to represent a region of an AIG regarding one output generation. However, when it comes to multiple output regions, multiple *k*-cuts would be needed. The *kl*-cuts (MARTINELLO JR., 2010) make use of multiple outputs to overcome this issue.

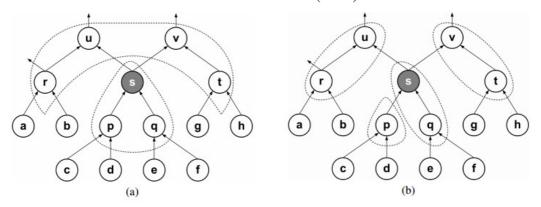

A kl-cut defines a sub-graph  $\mathcal{G}_{kl}$  of  $\mathcal{G}$  which has no more than k inputs and no more than l outputs. It is represented as two sets of nodes  $\{\mathcal{G}_k, \mathcal{G}_l\}$ , being  $\mathcal{G}_k$  the inputs set and  $\mathcal{G}_l$  the outputs set. If a node n belongs to a path between  $n_k \in \mathcal{G}_k$  and  $n_l \in \mathcal{G}_l$ , being  $n \notin \mathcal{G}_k$ , then n is contained in  $\mathcal{G}_{kl}$ . Notice that all nodes in  $\mathcal{G}_l$  are contained in  $\mathcal{G}_{kl}$ . However,  $\mathcal{G}_{kl}$  does not contain any node of  $\mathcal{G}_k$ . A kl-cut is said to be complete when all the following conditions are attained: (1) every path between a PI and a node  $n_l \in \mathcal{G}_l$  contains a node in  $\mathcal{G}_k$ ; (2) every path between a node contained in  $\mathcal{G}_{kl}$  and a PO contains a node in  $\mathcal{G}_l$ ; (3) no kl-cut defined by a subset of  $\mathcal{G}_k$  and the same  $\mathcal{G}_l$  is complete; and (4) no kl-cut defined by the same  $\mathcal{G}_k$  and a subset of  $\mathcal{G}_l$  is complete. Two examples of AIG covering using kl-cuts can be seen in Figure 2.14. If the kl-cuts with k=5 and l=3 (or simply 5-3-cuts) are computed, a resulting possible covering of this AIG is in Figure 2.14a. Another covering using 3-2 cuts is shown in Figure 2.14b. Further details on kl-cuts for AIGs can be seen in the work of Martinello (2010).

Figure 2.14 An AIG example illustrating covering using *kl*-cuts. Nodes *a, b, c, d, f, g* and *h* are primary inputs. Nodes *u* and *v* are primary outputs. (a) A covering using 5-3-cuts. (b) A covering using 3-2-cuts. (MARTINELLO, 2010)

## 2.7 Cell library

A logic gate, or a logic cell, is an element that performs a certain logic or memory function. The logic gates that implement Boolean functions are used to map the combinational part of logic circuits. Logic gates that perform memory function, such as latches and flip-flops, are used to create temporal barriers in order to generate sequential circuits, i.e. circuits that work in a well determined clock period.

A cell library is a finite set of logic gates. Traditionally, these logic gates are previously built and characterized through electrical simulations, resulting in well-defined cells to be used in the technology mapping. This approach is widely used and is known as *library-based* technology mapping, where the exact physical area, power consumption and delay of the cells are previously known. It is expected that a larger amount of logic gates would result in a higher QoR, since there are more options to reduce circuit area, for example. However, due to the high complexity of the technology mapping algorithms and the applied heuristics, a larger amount of logic gates does not necessarily improve the QoR.

A cell library is divided into several files. However, for logic synthesis two files are usually used: the *Liberty* file and the LEF file. The Liberty file is a standard text file that has the general library information, such as operating conditions (voltage, process and temperature), interconnections delay model, templates for timing and power tables, units for capacitance, voltage, time, etc. Also, the Liberty file has the information about all logic gates of the library, such as timing tables for each timing arc, logic function, input capacitances, power consumption tables, area, and so on. The library exchange format (LEF) file is a standard text file used to describe the geometrical shapes of the library cells layout, and also some geometrical restrictions of the IC manufacturing using this cell library. The standard cell flow has this name due to the standard height of the logic gates, and the information about the standard height is in the LEF file.

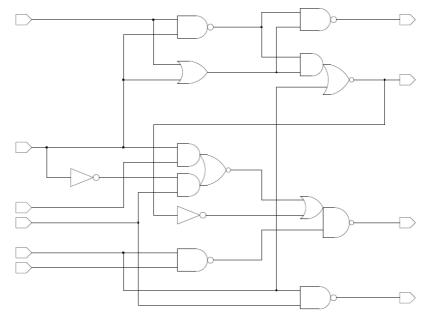

# 2.8 Technology mapping

Technology mapping is an important phase in the logic synthesis, which transforms a technology independent circuit description into a gate netlist of a technology library, i.e. a mapped circuit. It can be decomposed into three phases: decomposition, matching and covering.

Decomposition is the process that transforms the initial representation of the circuit into a simpler representation, more restricted, in order to make the process less computationally hard. In this step, it is applied structural transformations to the design representation, such as breaking the design graph into logic trees.

Once the circuit graph is computationally tractable, the matching step starts. The matching tries to find the parts of the graphs that can be implemented by a cell (or more than one cell) present in the library. In this step, the identification of Boolean functions in the same equivalence class is important, since a logic gate can implement different Boolean functions by performing the permutation of inputs, for instance.

Finally, the covering step chooses a subset of the match results in such a way that the entire circuit is covered, while optimizing one or more cost function such as area, delay and power. The result of the covering is a gate netlist that must correspond to the correct logic network received as input, i.e. all nodes of the input Boolean network must be covered.

The technology mapping is a phase that is crucial for a good QoR in the final circuit layout. The physical synthesis results depend directly on the technology mapping results. Also, it is important to notice that all steps in the technology mapping are important. Optimal algorithms for matching and covering deliver low quality results if the input design graph is not efficiently decomposed. This dependence in the previous structure is a problem known as *structural biasing* (CHATTERJEE, 2006-a).

# 2.9 Static Timing Analysis

Sequential digital circuits must be analyzed in order to check if there are no timing violations. This analysis is very important to determine if the design works correctly at the expected performance. Different approaches exist in order to check if there are no timing violations.

An approach to evaluate timing is through timing simulation, which is a method to perform timing analysis by testing all possible input vectors in the design. Timing simulation is a task that demands a lot of computational effort (BHASKER, 2009), since all different possibilities of inputs must be tested, i.e. a design with n inputs must check  $2^n$  input vectors and check if any of these input vectors violates timing constraints. This means that a design with 100 inputs would have to test  $1.26*10^{30}$  input vectors and propagate these vectors towards the design outputs, which is clearly a computational hard task.

An alternative approach to evaluate timing is the static timing analysis (STA). The static timing analysis is a fast way to analyze timing, considering only the worst case at each logic gate of the design. It is static, since it is the worst case, independent of the input vector. Also, since CMOS logic gates have different rise and fall characteristics, both cases must be considered. There is a small "penalty" in using this approach: STA is pessimist, since it considers only the worst cases. However, it is important to notice that it is better to have a timing check that guarantees that the design works, and in a reasonable time, since the timing check must be done several times in all phases of the design flow.

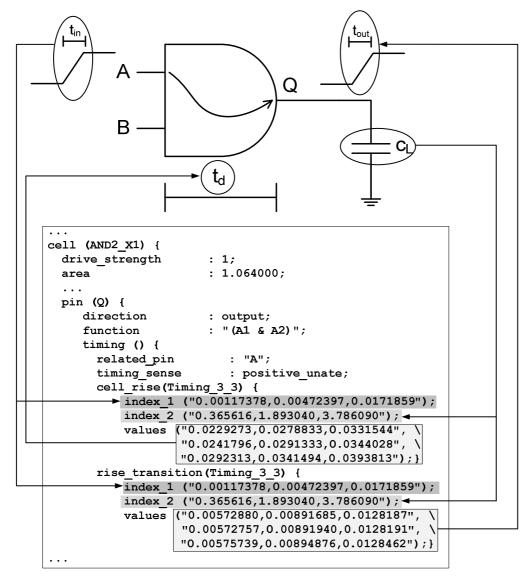

There are several delay models to determine the delay of a logic gate. The delay model most used in the standard cell design flow is the nonlinear delay model (NLDM). It determines the output transition time  $(t_{out})$  and the output delay  $(t_d)$  of a logic gate through the input transition times  $(t_{in})$  of the gate inputs and the capacitance load  $(c_L)$  at the gate output (BHASKER, 2009). Cells timing tables are read from Liberty files of the cell libraries, and using the  $t_{in}$  and the  $c_L$ , it is possible to obtain the correct  $t_{out}$  and  $t_d$  through bilinear interpolation. In Figure 2.15 shows which values are necessary to know in order to perform the bilinear interpolation and calculate the output transition time and cell delay, for a timing arc of an AND gate of 2 inputs, for the rise condition.

Any timing analysis tool is able to determine the circuit delays only due to the circuit itself. The environment conditions and restrictions must be informed to the timing analysis tool through the timing constraints in order to make such analysis more realistic. Timing constraints define, for example, the clock period and uncertainty, the input and output delays, input transition times and output loads. The standard format text file to inform the tool the timing constraints is the Synopsys design constraints (SDC) file.

In order to evaluate the worst case delay of a sequential circuit, which determines its performance (clock period), it can be applied the critical path method. In this method,

the delay is propagated from the inputs (or registers outputs) to the outputs (or registers inputs), considering only the worst case timing arc at each cell (for rise and fall). Clock uncertainty time and setup time must be added in registers endpoints. The input transitions of the evaluated cell are either: the input transition times defined in the SDC, in the case of an input pin, or the output transition times of the previous logic gates. The output load of the evaluated cell is the output load defined in the SDC, in the case of an output pin, added by all the input capacitances of all the cells the evaluated cell is driving. In the paths that involve input and output pins, input and output delays must be considered. The worst case delay is the largest delay from all endpoints (circuit outputs or register inputs).

Figure 2.15: Process to obtain cell delay and output transition time through the NLDM, extracting the values from a Liberty file. It is necessary to know the input transition time and the output load, and perform a bilinear interpolation in the values read in the Liberty file.

### 3. STATE-OF-THE-ART

This chapter presents a broad vision about the technology mapping algorithms existent in the literature, showing their limitations and heuristics. Then, state-of-the-art algorithms on Boolean matching, Boolean factoring and logic tree mapping algorithms are shown, and as they were adapted to be used in this work.

# 3.1 Technology mapping

DAGON was the first technology mapping algorithm, which was proposed by Keutzer (1987). Keutzer noticed that the tasks performed by a software compiler were very similar to the tasks performed by the technology mapping. The pattern matching of sub-graphs of a circuit representation using library cells are very similar to the matching of sub-parts of a computer program using an instruction set of a computer processor. The subject graph circuit is a binary tree represented with a string. But the first technology mapping algorithm had some drawbacks. The structural matching approach performed by DAGON, and the representation of the circuit given in its input, restrict the search space performed by the mapping, affecting negatively the quality of the resulting mapped circuit. Another issue is that the algorithm requires all isomorphic matches stored in each node of the circuit tree representation, until the very end of the circuit covering. This led to a restriction of using cell libraries with a large number of cells, because the number of cells affects directly the number of pattern matchings found in each node.

The first method that used logic trees as subject graph was proposed by Detjens (1987). It has some similarities with DAGON, and some additions. It was the first work that proposed the use of a pair of inverters in every non-inverted net of the circuit representation. This approach increases the solution space, impacting positively in the quality of the resulting mapped circuit. However, the approach proposed by Detjens had to create several decompositions for each library cell available, increasing exponentially the amount of pattern matchings, and also limiting the use of larger cell libraries.

Mailhot (1993) improved the technology mapping algorithm by improving the comparison between the sub-trees and the cells of the library using ROBDDs (NARAYAN, 1997). Like the previous algorithms presented (KEUTZER, 1987; DETJENS, 1987), the proposed approach split the initial circuit DAG into a forest of trees and maps them individually. But since ROBDDs are a canonical form of representing circuits, the matches did not depend in the structure of the sub-trees, but in the Boolean function it represented. However, this Boolean comparison was computationally expensive, also limiting the size of the cell library used.

An approach to minimize the dependence in the initial graph representation was proposed by Lehman (1995), using a dynamic reorganization. The decomposition step

was integrated with the pattern matching by making sub-graphs functionally equivalent but structurally different associated, for each node of the circuit DAG. This approach increased the search space, but it is also impractical for large circuits since the graph size increases exponentially.

Stok (1999) proposed the algorithm *wavefront*, similar to Lehman's approach but with no scalability problems. The circuit was mapped directly in the DAG, using a delay model independent of the cell output load. In order to prevent the DAG of increasing exponentially by inserting different representations for each node, the steps of decomposition, pattern matching and covering are executed in parallel in a "window" of parameterizable logic depth. This "window" performs the mapping from the inputs to the outputs, and has better results and runtime if compared with its predecessors.

The state-of-the-art in library-based technology mapping approaches is still the work presented by Chatterjee (2006-a) It brings together several techniques used in logic synthesis integrated in order to benefit the technology mapping. The pattern matching is performed by Boolean matching and the data structure used is the AIG. This algorithm and its improvements are all incorporated in the academic logic synthesis tool ABC (Berkeley Logic Synthesis and Verification Group, 2012).

By performing this holistic view of some of the most important technology mapping approaches presented in the literacture, which the commercial tools are strongly based, some limitations were observed. Two are important limitations that this work tries to take advantage: (1) the scalability issues due to the use of a large cell library, and (2) the scalability issues of performing mappings with a large solution space in large circuits.

# 3.2 Boolean matching

The pattern matching is an important step in the technology mapping, which can be performed using a structural analysis, i.e. comparing two structures if they are the same, as it can be done in the circuits of the Figure 2.6. This comparison is computationally easy and several technology mapping algorithms took advantage of this to have faster results. However, a logic function can have numerous structures to represent it, and therefore a structural matching obtains very limited results.

Another way to perform pattern matching is through a functional (Boolean) analysis of the two functions. This comparison is computationally harder than a structural matching, but it is much more powerful, since it does not depend on the structural implementation of the circuit. This work uses Boolean matching in order to check if two functions are in the same P-equivalence class.

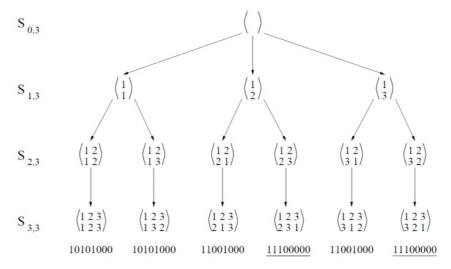

A well-known Boolean matching algorithm for any type of function was proposed by Hinsberger (1998). The method is based on the definition of a canonical representative function R[f] for each equivalence class f. The matching between two functions happen when the representative function calculated is the same:  $R[f_1] = R[f_2]$ .

A function can be defined through a truth table, which can be represented as a bit string. The method proposed by Hinsberger (1998) uses the largest number that the given function can represent permutating the input variables as the representative function. For example, Figure 3.1 shows an exhaustive approach for finding this representative function for a function of three variables. In the Figure 3.1, the values in the parenthesis show in the top the variable selected (1, 2 or 3), and the position in the function in which the function was set (1, 2 or 3). Notice that the input variables must

obey a very strict ordering. Also, notice that the leftmost value (10101000) represents the truth table of the input function, since it places the variable 1 in the position 1, the variable 2 in the position 2 and the variable 3 in the position 3. In this case, the representative function is 1110000 since it is the largest value found.

The computation of which branch gives the largest value can be done earlier, choosing the next branch at each tree level. This is done in the Figure 3.2, where the search space was reduced by deciding the largest function value earlier.

Another reduction that can be done in order to reduce further the amount of computation is to only check the variables in the same *symmetry* class. Two variables a and b of a function f are in the same symmetry class when they can be exchanged without changing the resulting function: f(a,b) = f(b,a). In the Figure 3.2, the variables 2 and 3 are in the same symmetry class for this function, and therefore only one of the branches should be checked: (1,2) or (1,3).

In the work of Martinello (2010), it is proposed an extension of this Boolean matching algorithm in order to match multiple-output functions, where it is defined a PP-equivalence class. This extension is very important to group kl-cuts in the same equivalence class and improve the remapping flow runtime, with no affect in the quality of the resulting circuit.

Figure 3.1 Exaustive approach for computing  $R[f]_P$  (HINSBERGER; KOLLA, 1988)

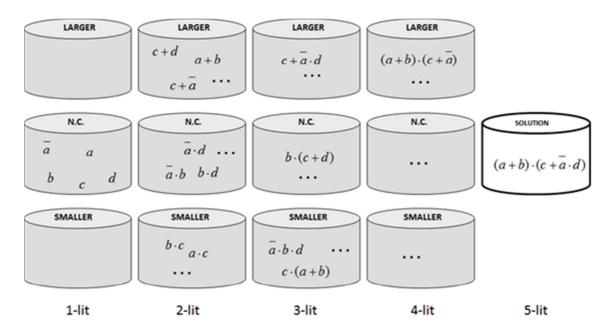

# 3.3 Boolean factoring

Factoring is the process of deriving a parenthesized algebraic equation representing a given logic function (BRAYTON, 1987). Factoring algorithms can be classified into algebraic and Boolean.

The algebraic factoring has its basis in polynomial division, pretending that the Boolean variables behave like real numbers. The basic concept is that, given the functions f and p, the algorithm tries to find functions q and r such that  $f = p \cdot q + r$ . The function p is called a divisor of f if r is not null, and a factor if r is null. Some relationships can be used to simplify the results during factoring. The relationships used in algebraic factoring are shown in the left column of Table 3.1. Algebraic factoring is usually very fast, but commonly the results are far from optimal.

Figure 3.2 Reducing search space by cutting non-maximal branches (HINSBERGER; KOLLA, 1998)

Table 3.1 Relationships allowed in multi-level logic factoring

| Relationships allowed                                   | Relationships allowed                   |

|---------------------------------------------------------|-----------------------------------------|

| in algebraic and                                        | only for Boolean                        |

| Boolean factoring                                       | factoring                               |

| a•b= b•a                                                | a+a' = 1                                |

| a+b= b+a                                                | a•a' = 0                                |

| $a^{\bullet}(b^{\bullet}c) = (a^{\bullet}b)^{\bullet}c$ | a•a= a                                  |

| a+(b+c) = (a+b)+c                                       | a+a= a                                  |

| $a\bullet(b+c) = a\bullet b + a\bullet c$               | a+1 = 1                                 |

| a•1 = a                                                 | $a+(b \bullet c) = (a+b) \bullet (a+c)$ |

| a•0 = 0                                                 |                                         |

| a+0 = a                                                 |                                         |

On the other hand, Boolean factoring algorithms achieve better results, but they can be very time and memory consuming, since it is an NP-complete task. The state-of-the-art Boolean factoring algorithm was presented in the work of Martins (2012), using the functional composition (FC) paradigm. The FC exact algorithm uses dynamic programming and a bottom-up approach to find minimum literal logic expressions. But the exact approach is impractical to be used in a remapping flow, since it uses a lot of time and memory. In the same work presented by Martins (2012), several heuristics were added to this algorithm in order to make it faster and have still obtain very good results. The FC heuristic algorithm has comparable runtime to previous works and results in logic expressions with smaller literal count. An example of how the FC heuristic algorithm works is shown in the Figure 3.3: from the function variables (selected in the correct polarity) the functions are associated until the target function is found.

Figure 3.3 Example of Boolean factoring using Functional Composition. (MARTINS, 2012)

Besides the FC heuristic algorithm, this work uses a modified version of it, regarding the use of the XOR operator (MARTINS, 2012), and also logic sharing. In order to use logic sharing, two approaches were used. A simpler approach was to use the other outputs functions (all outputs but the current output being factorized) as input to the FC algorithm as one literal functions. Another approach was to identify partial logic functions that were used by more than one output and use a dynamic cost to these intermediate functions (one literal or more), according to the effective use of them.

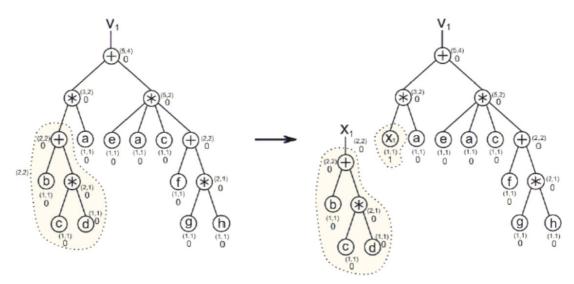

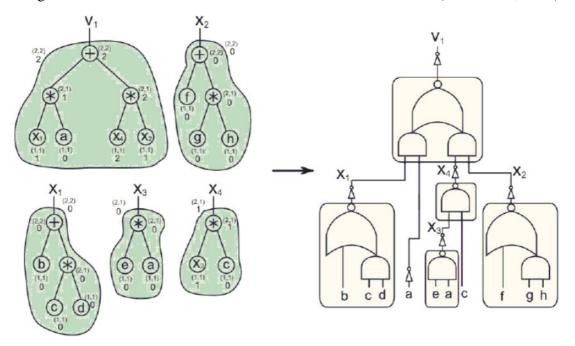

# 3.4 Logic tree mapping

The output of the FC algorithm is a set of logic expressions. This logic expressions can be represented as logic trees and mapped, resulting in a mapped circuit. This logic tree mapping is not straightforward and requires several transformations to obtain a good logic tree covering.