# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

#### **GUSTAVO NEUBERGER**

## **Protecting Digital Circuits Against Hold Time Violations Due to Process Variations**

Thesis presented in partial fulfillment of the requirements for the degree of Doctor of Microelectronics

Prof. Dr. Ricardo Reis Advisor Prof. Dr. Gilson Wirth Co-Advisor

#### CIP - CATALOGAÇÃO NA PUBLICAÇÃO

Neuberger, Gustavo

Protecting Digital Circuits Against Hold Time Violations Due to Process Variations / Gustavo Neuberger – Porto Alegre: Programa de Pós-Graduação em Microeletrônica, 2007.

108 f.:il.

Thesis (PhD) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica. Porto Alegre, BR – RS, 2007. Advisor: Ricardo Augusto da Luz Reis; coadvisor: Gilson Wirth.

1. Process Variability. 2. Hold Time Violations. 3. Clock Skew. 4. Race Immunity. 5. Integrated circuit design. I. Reis, Ricardo Augusto da Luz. II. Wirth, Gilson. III. Title.

#### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. José Carlos Ferraz Hennemann Vice-Reitor: Prof. Pedro Cezar Dutra Fonseca

Pró-Reitora de Pós-Graduação: Profa. Valquíria Linck Bassani Diretor do Instituto de Informática: Prof. Flávio Rech Wagner

Coordenador do PGMicro: Prof. Henri Boudinov

Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

#### **ACKNOWLEDGEMENTS**

First, I would like to thank my family, especially my parents, Lotário Neuberger and Isabel Marta Neuberger, for the support given in all my life.

I am also very grateful to my advisors, Ricardo Reis and Gilson Wirth, for the technical support, and also to Fernanda Kastensmidt, that also helped significantly in this work. I would like to thank as well any other professor of the university that has contributed during my PhD.

One important step in this work and in my life was the time I spent abroad, in Germany. I would like to thank my advisors during that time, Christian Pacha and Ralf Brederlow, for all the help, both technical and to adapt to a new country. I am also grateful to all friends I have made during that time in Germany.

I thank all the friends I have made in these years; they are so many that is difficult to cite them all. From them, I would like to thank especially Renato Hentschke, because together we formed a great team to compete in the CADAthlon competition, and we got the 2<sup>nd</sup> place on 2005.

## **CONTENTS**

| LIST OF ABBREVIATIONS AND ACRONYN                                                                                     | IS7            |

|-----------------------------------------------------------------------------------------------------------------------|----------------|

| LIST OF FIGURES                                                                                                       | 9              |

| LIST OF TABLES                                                                                                        | 13             |

| ABSTRACT                                                                                                              | 15             |

| RESUMO                                                                                                                | 17             |

| 1 INTRODUCTION                                                                                                        | 19             |

| 2 PROCESS VARIABILITY                                                                                                 | 23             |

| 2.1 Sources and types of variations                                                                                   |                |

| 2.2 Specific issues                                                                                                   |                |

| 2.2.1 Lithography                                                                                                     |                |

| 2.2.2 Doping                                                                                                          |                |

| 2.3 Impact on circuit design                                                                                          | 26             |

| 3 FLIP-FLOPS AND HOLD TIME VIOLATION                                                                                  | ONS29          |

| 3.1 Flip-flop timing metrics                                                                                          |                |

| 3.1.1 Setup time                                                                                                      |                |

| 3.1.2 Hold time                                                                                                       |                |

| 3.1.3 Clock-to-output delay                                                                                           |                |

| 3.1.4 Data-to-output delay                                                                                            |                |

| 3.1.6 Internal race immunity                                                                                          |                |

| 3.2 Hold time violations                                                                                              |                |

| 4 CIRCUITS UNDER TEST                                                                                                 |                |

|                                                                                                                       | 35             |

|                                                                                                                       |                |

|                                                                                                                       | 35             |

| 4.1 Inverter Sensitivity                                                                                              | 35<br>36       |

| 4.1 Inverter Sensitivity                                                                                              | 35<br>36<br>37 |

| <ul> <li>4.1 Inverter Sensitivity</li> <li>4.2 FF sensitivity</li> <li>4.3 Hold Time Violation Probability</li> </ul> |                |

| <ul> <li>4.1 Inverter Sensitivity</li></ul>                                                                           |                |

| 4.1 Inverter Sensitivity                                                                                              |                |

| 5.4                                                            | Final Circuit and Layout                                                                                             | 44                       |

|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------|

| 6 E                                                            | XPERIMENTAL RESULTS                                                                                                  | 49                       |

| 6.1<br>6.2<br>6.3<br>6.4                                       | Measurement Flow and Setup                                                                                           | 50<br>51                 |

| 6.4.1<br>6.4.2<br>6.4.3<br>6.4.4<br>6.4.5                      | Different Wafers of a Same Technology  Different Technologies at Nominal Conditions  Different Temperatures          | 54<br>55<br>56<br>57     |

|                                                                | YSTEMATIC AND RANDOM VARIABILITY                                                                                     |                          |

| 7.1<br>7.2                                                     | Separation Methods                                                                                                   |                          |

| 8 N                                                            | ORMALITY TESTS                                                                                                       | 67                       |

| 8.1.1<br>8.1.2<br>8.1.3                                        | Anderson-Darling Test                                                                                                | 67<br>68<br>69           |

|                                                                | ROBABILITY OF HOLD TIME VIOLATIONS                                                                                   |                          |

| 9.1<br>9.2<br>9.3<br>9.3.1<br>9.3.2<br>9.3.3<br>9.3.4<br>9.3.5 | Simulation of Dependence of Race Immunity on Vdd                                                                     | <b>75 83</b> 84 86 87 88 |

|                                                                | PROTECTING CIRCUITS AGAINST HOLD TIME VIOLATIONS                                                                     |                          |

| 10.2.<br>10.2.<br>10.2.                                        | Motivation Protection against Hold Time Violations  1 Vdd Reduction 2 Increasing Flip-Flop Race Immunity 3 Padding   | 92<br>92<br>93<br>93     |

| 11                                                             | CONCLUSION                                                                                                           | 97                       |

| REF                                                            | ERENCES                                                                                                              | 99                       |

| TEM                                                            | ENDIX PROTEÇÃO DE CIRCUITOS DIGITAIS CONTRA FALHAS DE<br>PO DE HOLD DEVIDO À VARIABILIDADE DO PROCESSO DE<br>RICAÇÃO |                          |

### LIST OF ABBREVIATIONS AND ACRONYMS

ASIC Application Specific Integrated Circuit

CLK Clock

CMOS Complementary Metal Oxide Semiconductor

DFT Design for Test

DSP Digital Signal Processor

EDA Electronic Design Automation

EUV Extreme Ultra Violet

FF Flip-Flop

IC Integrated Circuit

IR Current-Resistance (IR drop)

LER Line Edge Roughness

$\begin{array}{cc} L_g & & \text{Gate Length} \\ \text{MC} & & \text{Monte Carlo} \end{array}$

MOSFET Metal-Oxide-Semiconductor Field Effect Transistor

NBTI Negative Bias Threshold Instability

nFET Field Effect Transistor type N

NMOS Metal-Oxide-Semiconductor type N

PC Personal Computer

PMOS Metal-Oxide-Semiconductor type P

R Resistance

RO Ring Oscillator

σ Standard DeviationSOI Silicon on Insulator

t<sub>ox</sub> Oxide Thickness

V<sub>body</sub> Body Voltage

VDSM Very Deep Sub Micron

V<sub>T</sub> Threshold Voltage

W Width

## **LIST OF FIGURES**

| Figure 2.1. | Expected technology scaling.                                                                                                                                                                                                                                              | 23       |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| _           | Number of dopant atoms versus scaling.                                                                                                                                                                                                                                    |          |

| _           | Threshold variability.                                                                                                                                                                                                                                                    |          |

| _           | •                                                                                                                                                                                                                                                                         |          |

| •           | Impact of number of critical paths.                                                                                                                                                                                                                                       |          |

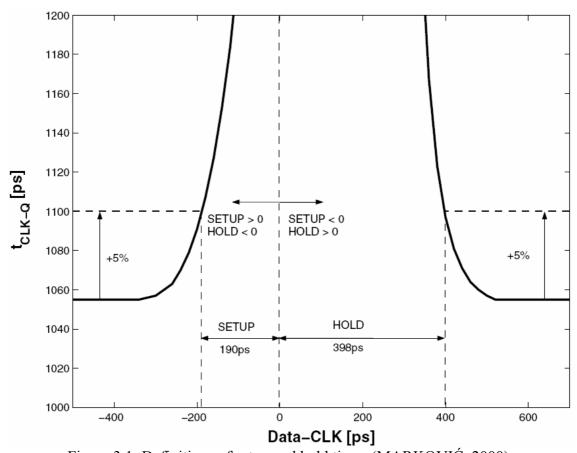

| •           | Definitions of setup and hold times                                                                                                                                                                                                                                       |          |

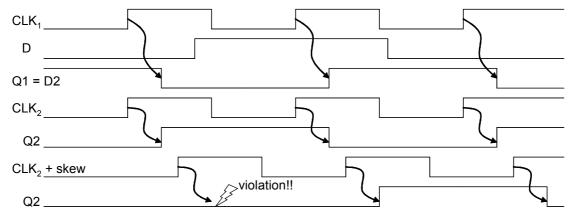

|             | Timing diagram showing hold time violation.                                                                                                                                                                                                                               |          |

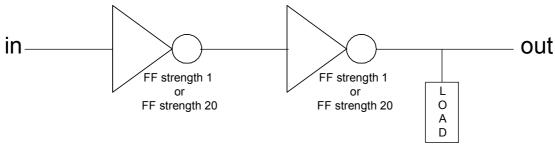

| Figure 4.1: | Logic circuit to investigate delay variability.                                                                                                                                                                                                                           | 35       |

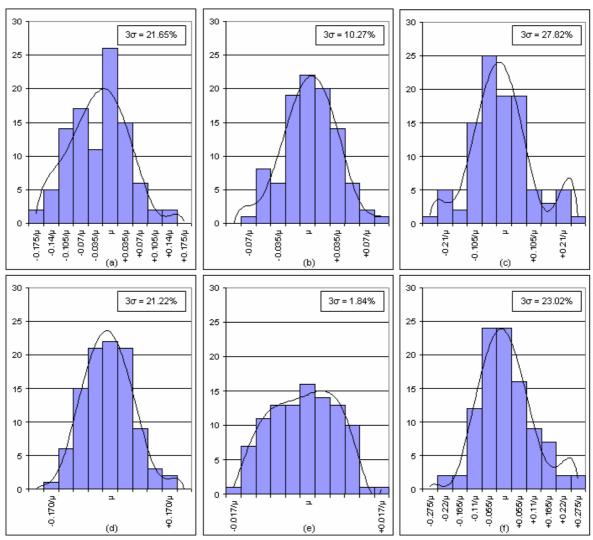

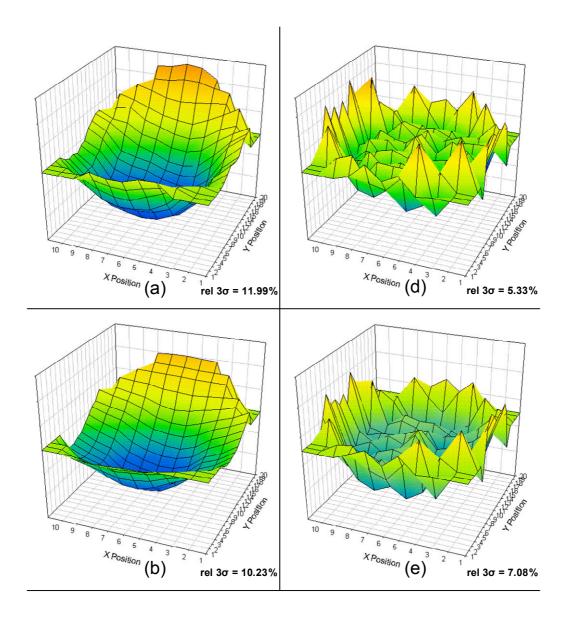

| Figure 4.2: | Monte Carlo simulation results for rising transitions: small inverters (1x) and (a) only global variations, (b) only local variations, and (c) both variations; large inverters (20x) and (d) only global variations, (e) only local variations, and (f) both variations. |          |

| Figure 4.3: | FF parameter variability: (a) delay, (b) setup time and (c) hold time                                                                                                                                                                                                     | 37       |

| Figure 4.4: | Circuit with FFs and inverters to check hold time violation.                                                                                                                                                                                                              | 38       |

| Figure 4.5: | Different test circuits with sensitivity to hold time violations.                                                                                                                                                                                                         | 39       |

| Figure 5.1: | Schematics of the programmable delay line for the clock skew emulation.                                                                                                                                                                                                   | 41       |

| Figure 5.2: | Final layout of the load elements.                                                                                                                                                                                                                                        | 42       |

| Figure 5.3: | Final layout of the programmable delay line                                                                                                                                                                                                                               | 43       |

| Figure 5.4: | Schematics: (a) ring oscillator with delay line, (b) frequency divider and (one stage of the frequency divider.                                                                                                                                                           |          |

| Figure 5.5: | Schematic of the shift register.                                                                                                                                                                                                                                          | 44       |

| Figure 5.6: | Final schematic of the circuit to be fabricated.                                                                                                                                                                                                                          | 44       |

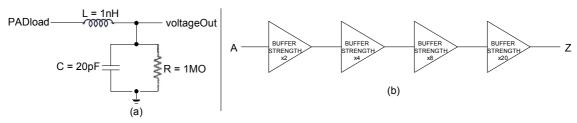

| Figure 5.7: | (a) PAD model and (b) driving buffer                                                                                                                                                                                                                                      | 45       |

| Figure 5.8: | Final 130nm layout of the complete fabricated circuit                                                                                                                                                                                                                     | 45       |

| Figure 5.9: | Final 90nm layout of the complete fabricated circuit                                                                                                                                                                                                                      | 46       |

|             | ): Final layout with PADs.                                                                                                                                                                                                                                                |          |

| Figure 6.1: | Measurement flow.                                                                                                                                                                                                                                                         | 50       |

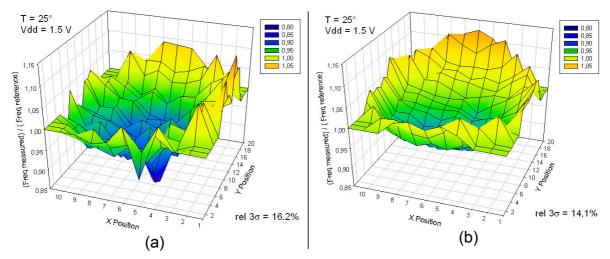

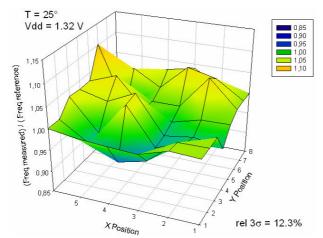

| _           | Normalized frequency variability in 130nm technology (a) over wafer 1, (over wafer 2                                                                                                                                                                                      | b)<br>51 |

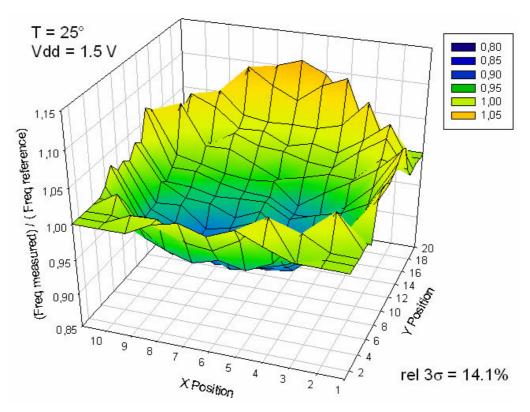

| Figure 6.3: | Normalized frequency variability in 90nm technology over the wafer 51                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

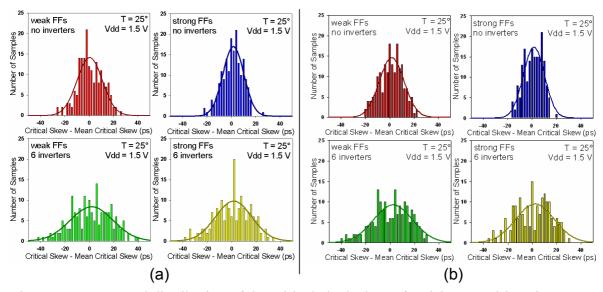

| Figure 6.4: | Measured distribution of the critical clock skews for rising transitions in 130nm technology (a) wafer 1, (b) wafer 2                                                                                                                                                                                                                                                                                                                                             |

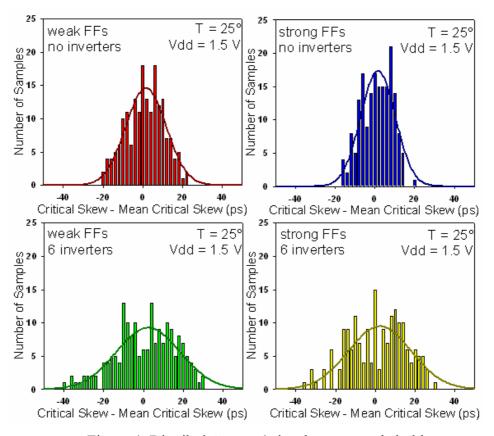

| Figure 6.5: | Measured distribution of the critical clock skews for rising transitions in 90nm technology                                                                                                                                                                                                                                                                                                                                                                       |

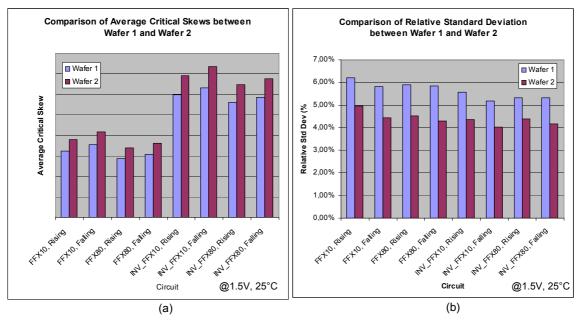

| Figure 6.6: | Comparison between 130nm wafer 1 and wafer 2 – (a) average critical skew and (b) relative standard deviation                                                                                                                                                                                                                                                                                                                                                      |

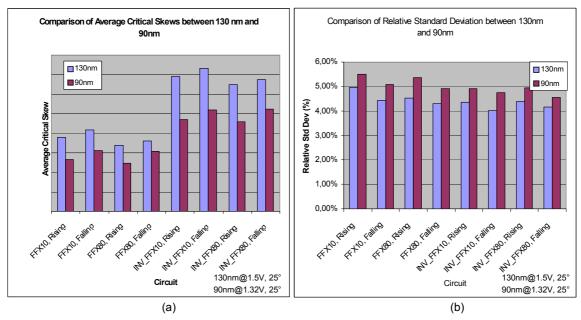

| Figure 6.7: | Comparison between 130nm wafer 2 and 90nm wafer – (a) average critical skew and (b) relative standard deviation                                                                                                                                                                                                                                                                                                                                                   |

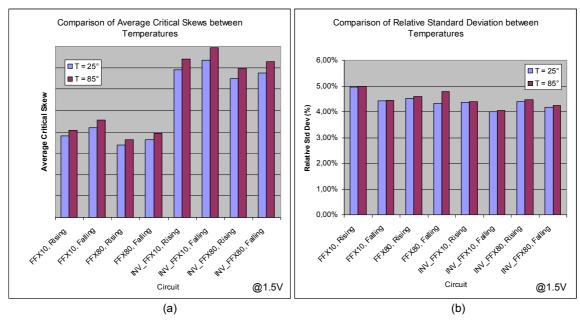

| Figure 6.8: | Comparison between $T = 25^{\circ}$ and $T = 85^{\circ}$ in 130nm wafer $2 - (a)$ average critical skew and (b) relative standard deviation.                                                                                                                                                                                                                                                                                                                      |

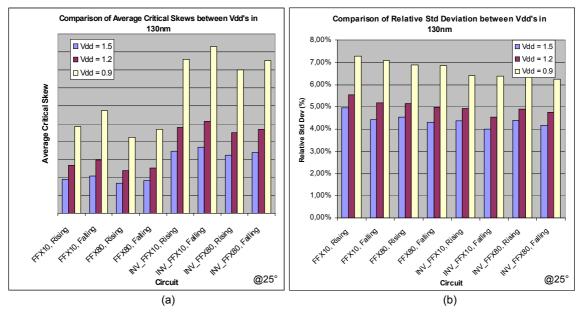

| Figure 6.9: | Comparison between Vdd = $1.5$ V, $1.2$ V and $0.9$ V in $130$ nm wafer $2-(a)$ average critical skew and (b) relative standard deviation                                                                                                                                                                                                                                                                                                                         |

| Figure 6.10 | 2: Comparison between Vdd = 1.32V, 1.2V and 0.9V in 90nm wafer – (a) average critical skew and (b) relative standard deviation                                                                                                                                                                                                                                                                                                                                    |

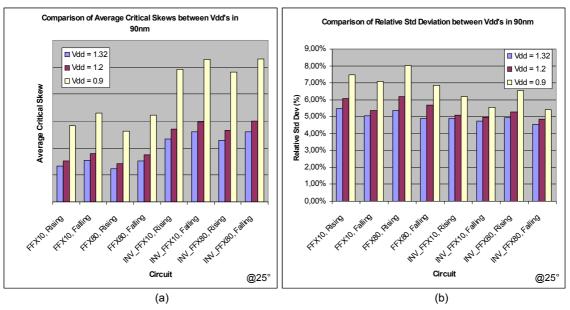

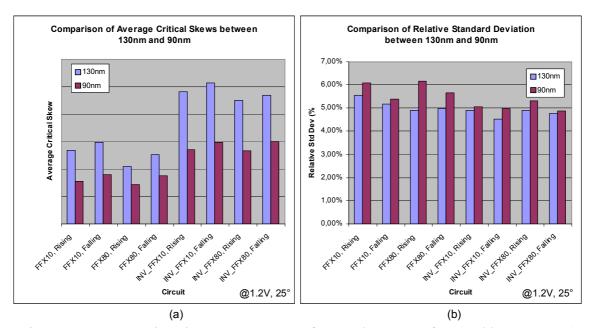

| Figure 6.11 | : Comparison between 130nm wafer 2 and 90nm wafer at $Vdd = 1.2V - (a)$ average critical skew and (b) relative standard deviation                                                                                                                                                                                                                                                                                                                                 |

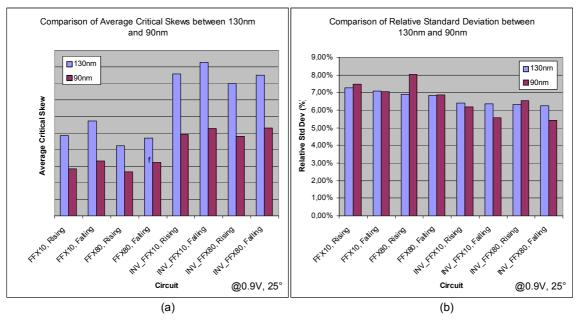

| Figure 6.12 | 2: Comparison between 130nm wafer 2 and 90nm wafer at $Vdd = 0.9V - (a)$ average critical skew and (b) relative standard deviation                                                                                                                                                                                                                                                                                                                                |

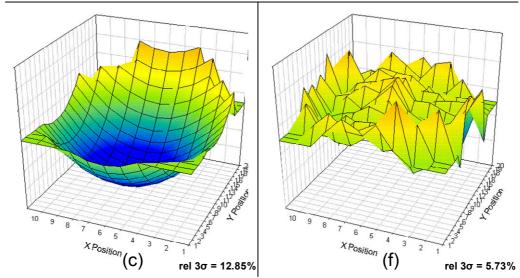

| Figure 7.1: | Variability curves in 130nm wafer: (a) systematic variability using the method Moving Average with 3x3 window, (b) systematic variability using the method Moving Average with 5x5 window, (c) systematic variability using the method Curve Fitting, (d) residual variability using the method Moving Average with 3x3 window, (e) residual variability using the method Moving Average with 5x5 window, (f) residual variability using the method Curve Fitting |

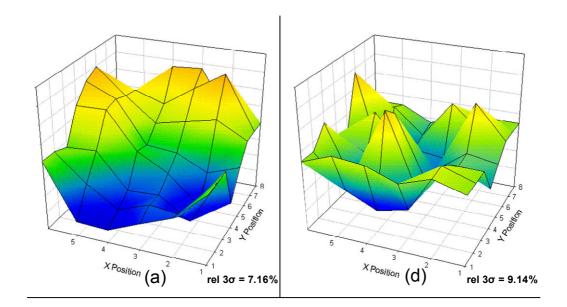

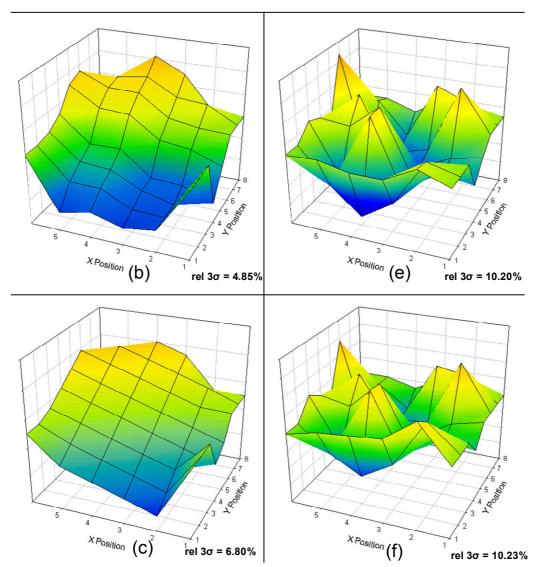

| Figure 7.2: | Variability curves in 90nm wafer: (a) systematic variability using the method Moving Average with 3x3 window, (b) systematic variability using the method Moving Average with 5x5 window, (c) systematic variability using the method Curve Fitting, (d) residual variability using the method Moving Average with 3x3 window, (e) residual variability using the method Moving Average with 5x5 window, (f) residual variability using the method Curve Fitting  |

| Figure 8.1: | Comparison between 130nm wafer 2 and 90nm wafer at $Vdd = 1.2V - (a)$ average critical skew and (b) relative standard deviation                                                                                                                                                                                                                                                                                                                                   |

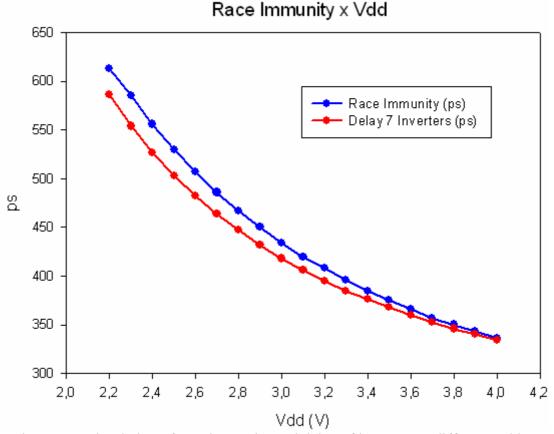

| Figure 9.1: | Simulation of race immunity and delay of inverters at different Vdd's76                                                                                                                                                                                                                                                                                                                                                                                           |

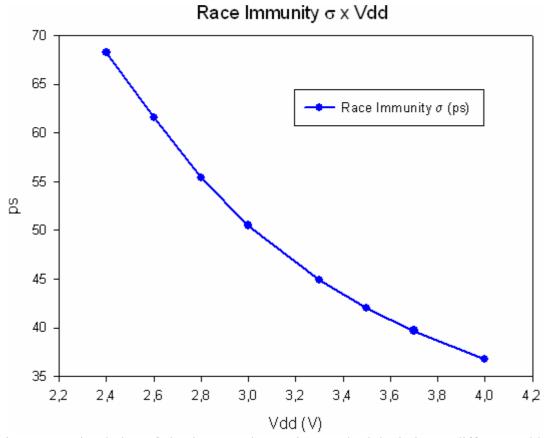

| Figure 9.2: | Simulation of absolute race immunity standard deviation at different Vdd's.                                                                                                                                                                                                                                                                                                                                                                                       |

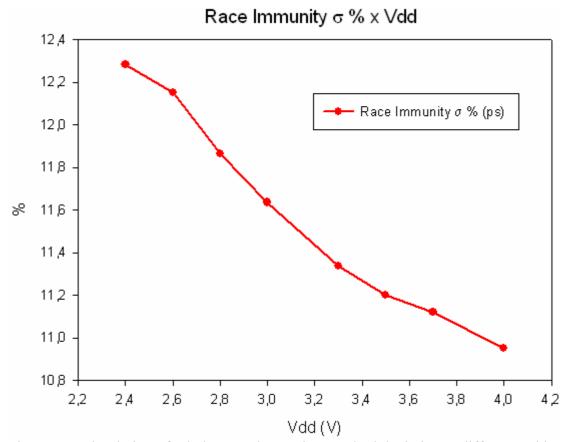

| Figure 9.3: | Simulation of relative race immunity standard deviation at different Vdd's                                                                                                                                                                                                                                                                                                                                                                                        |

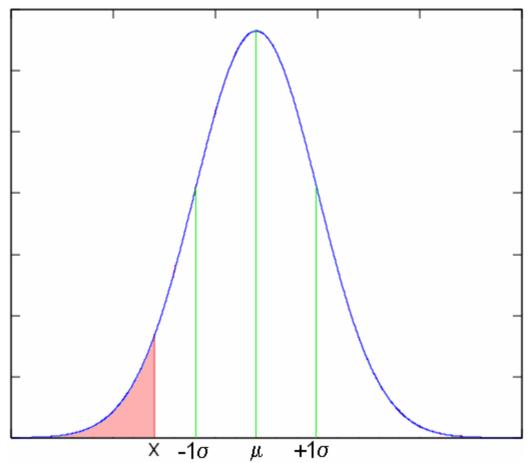

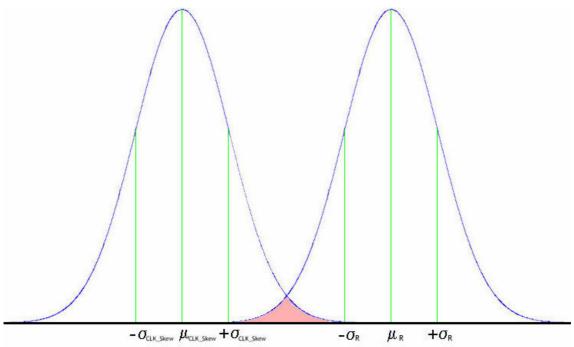

| Figure 9.4: | Calculation of hold time violation probability (cumulative distribution function)                                                                                                                                                                                                                                                                                                                                                                                 |

| Figure 9.5: Calculation of hold time violation probability considering clock skew as a normal distribution. |      |

|-------------------------------------------------------------------------------------------------------------|------|

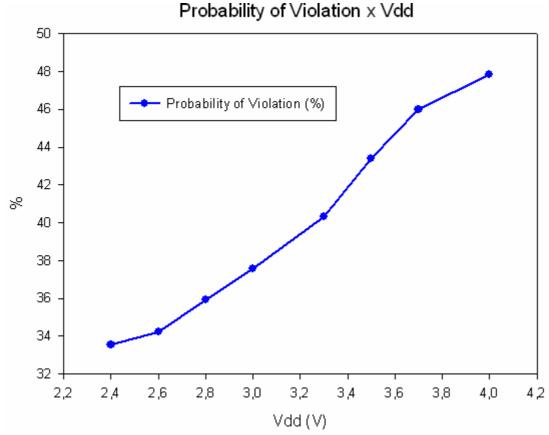

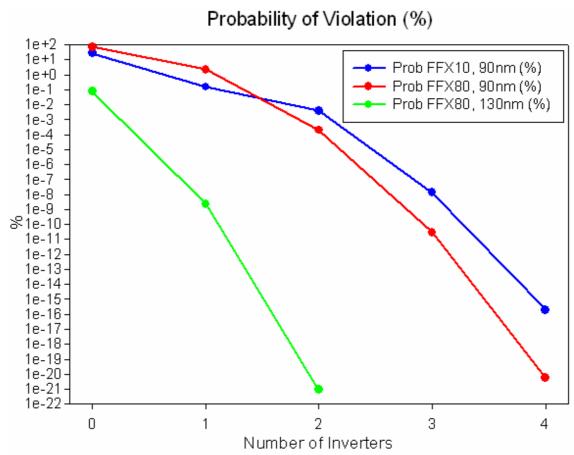

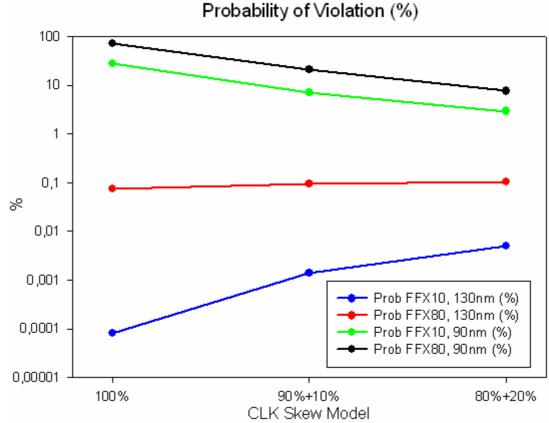

| Figure 9.6: Probability of hold time violation using simulated data.                                        | . 81 |

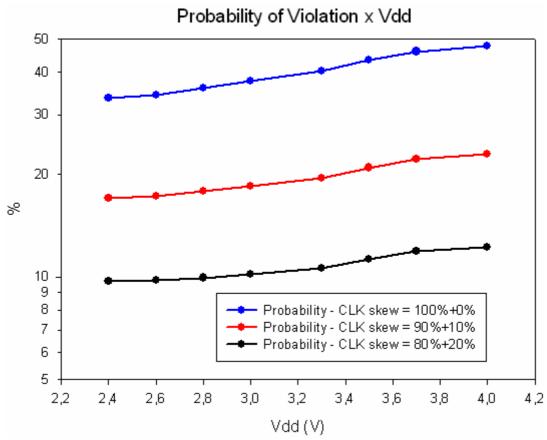

| Figure 9.7: Probability of hold time violation using simulated data, for different clock skew models.       |      |

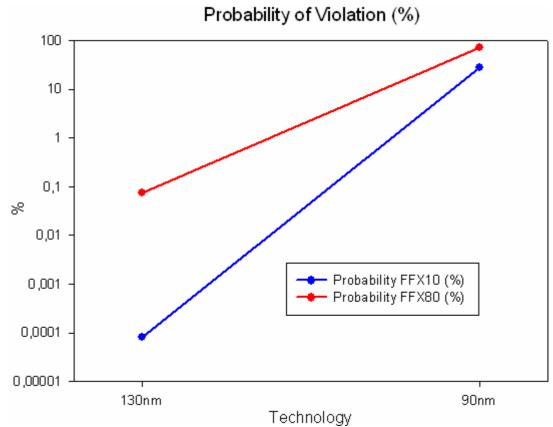

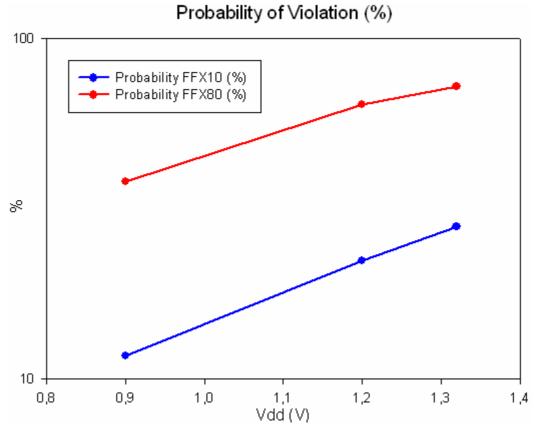

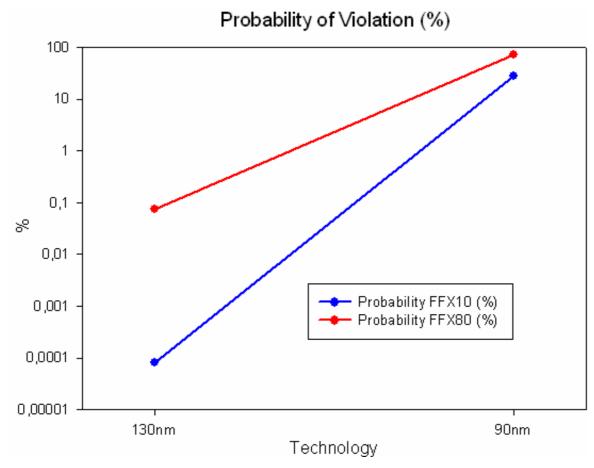

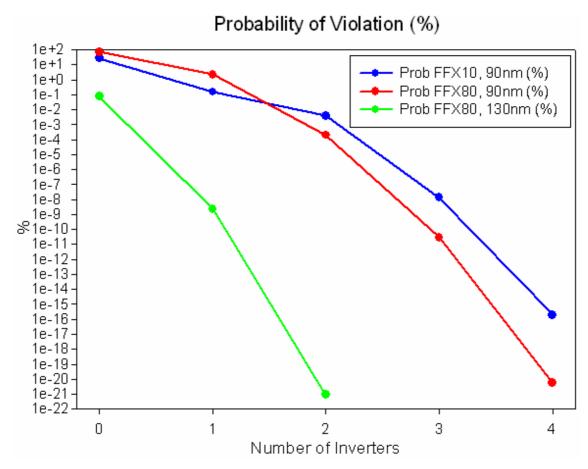

| Figure 9.8: Probability of violation for different technologies.                                            | . 84 |

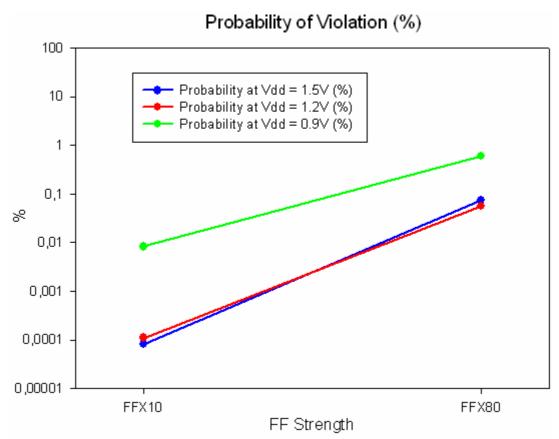

| Figure 9.9: Probability of violation for different FFs in 130nm.                                            | . 85 |

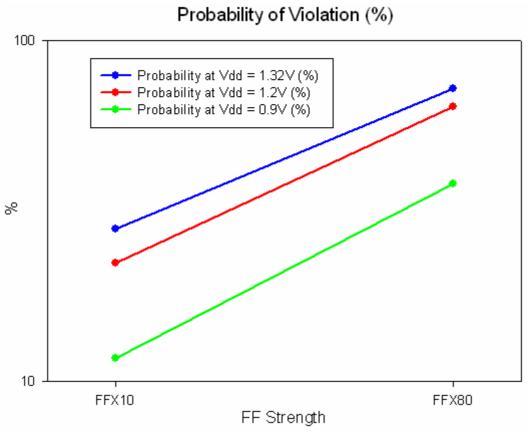

| Figure 9.10: Probability of violation for different FFs in 90nm.                                            | . 86 |

| Figure 9.11: Probability of violation for different Vdd's in 90nm.                                          | . 87 |

| Figure 9.12: Probability of violation for different padding.                                                | . 88 |

| Figure 9.13: Probability of violation for different clock skew models                                       | . 89 |

| Figure 10.1: Algorithm of padding considering race immunity variability                                     | . 94 |

## **LIST OF TABLES**

| Table 2.1: | Matrix of variations.                                                                                                                                                                                                  | 24  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 2.2: | Shot noise for different energy quanta.                                                                                                                                                                                | 25  |

| Table 6.1: | Normalized hold time violations in 130nm wafer 1 at V <sub>DD</sub> =1.5V and T=25°                                                                                                                                    |     |

| Table 6.2: | Normalized hold time violations in 130nm wafer 2 at V <sub>DD</sub> =1.5V and T=25°                                                                                                                                    |     |

| Table 6.3: | Normalized hold time violations in 90nm wafer at $V_{DD}$ =1.32V and T=25°.                                                                                                                                            | 53  |

|            | Total, systematic and random residual variability in the critical clock skew using the $3x3$ moving average method in $130$ nm wafer 2 at $V_{DD}$ =1.5V and T=25°                                                     | 65  |

|            | Total, systematic and random residual variability in the critical clock skew using the $3x3$ moving average method in 90nm wafer at $V_{DD}$ =1.32V and $T$ =25°                                                       | 65  |

|            | Wilks-Shapiro and Anderson-Darling normality tests, kurtosis and skewnes for total, systematic and random residual variability for frequency data in 130nm wafer 2 at $V_{DD}$ =1.5V and T=25°.                        |     |

|            | Wilks-Shapiro and Anderson-Darling normality tests, kurtosis and skewnes for total, systematic and random residual variability for test path of weak FF no inverters, in 130nm wafer 2 at $V_{DD}$ =1.5V and T=25°     | Ξs, |

|            | Wilks-Shapiro and Anderson-Darling normality tests, kurtosis and skewnes for total, systematic and random residual variability for test path of strong FFs, no inverters, in 130nm wafer 2 at $V_{DD}$ =1.5V and T=25° |     |

|            | Wilks-Shapiro and Anderson-Darling normality tests, kurtosis and skewnes for total, systematic and random residual variability for test path of weak FF 6 inverters, in 130nm wafer 2 at $V_{DD}$ =1.5V and T=25°      | ₹s, |

|            | Wilks-Shapiro and Anderson-Darling normality tests, kurtosis and skewnes for total, systematic and random residual variability for test path of strong FFs, 6 inverters, in 130nm wafer 2 at $V_{DD}$ =1.5V and T=25°  |     |

| Table 8.6: | Wilks-Shapiro and Anderson-Darling normality tests, kurtosis and skewnes for total, systematic and random residual variability for frequency data in 90nm wafer at $V_{DD}$ =1.32V and T=25°                           |     |

| Table 8.7  | Wilks-Shapiro and Anderson-Darling normality tests, kurtosis and skewness for total, systematic and random residual variability for test path of weak FFs, no inverters, in 90nm wafer at $V_{DD}$ =1.32V and T=25°73     |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 8.8  | Wilks-Shapiro and Anderson-Darling normality tests, kurtosis and skewness for total, systematic and random residual variability for test path of strong FFs, no inverters, in 90nm wafer at $V_{DD}$ =1.32V and T=25°73   |

| Table 8.9  | Wilks-Shapiro and Anderson-Darling normality tests, kurtosis and skewness for total, systematic and random residual variability for test path of weak FFs, 6 inverters, in 90nm wafer at $V_{DD}$ =1.32V and T=25°74      |

| Table 8.10 | 0: Wilks-Shapiro and Anderson-Darling normality tests, kurtosis and skewness for total, systematic and random residual variability for test path of strong FFs, 6 inverters, in 90nm wafer at $V_{DD}$ =1.32V and T=25°74 |

#### **ABSTRACT**

With the shrinking of CMOS technology, the circuits are more and more subject to variability in the fabrication process. Statistical process variations are a critical issue for circuit design strategies to ensure high yield in sub-100nm technologies. In this work we present an on-chip measurement technique to characterize hold time violations of flip-flops in short logic paths, which are generated by clock-edge uncertainties in synchronous designs. Using a precise programmable clock-to-data skew generation circuit, a measurement resolution of ~1ps is achieved to emulate race conditions. Statistical variations of hold time violations are measured in a 130nm and 90nm lowpower CMOS technology for various register-to-register configurations, and also different conditions of temperature and Vdd. These violations are a critical issue in large designs with thousands of short paths, as if only one of these fails, the whole circuit will not work at any frequency. Using the measured results, the variability is divided between systematic and random residual using mathematical methods. Normality tests are applied to this data to check if they are normal Gaussians or not. The probability of hold time violations considering our measured data and typical clock skews is calculated, showing that the problem of hold time violations is increasing with technologic advances. Finally, an algorithm to protect digital circuits against hold time violations in short paths is presented.

**Keywords:** Process Variability, Hold Time Violations, On-Chip Testing, Clock Skew, Flip-Flop Characterization, Race Immunity, Microelectronics.

#### Protecting Digital Circuits Against Hold Time Violations Due to Process Variations

#### **RESUMO**

Com o desenvolvimento da tecnologia CMOS, os circuitos estão ficando cada vez mais sujeitos a variabilidade no processo de fabricação. Variações estatísticas de processo são um ponto crítico para estratégias de projeto de circuitos para garantir um yield alto em tecnologias sub-100nm. Neste trabalho apresentamos uma técnica de medida on-chip para caracterizar violações de tempo de hold de flip-flops em caminhos lógicos curtos, que são geradas por incertezas de borda de relógio em projetos síncronos. Usando um circuito programável preciso de geração de skew de relógio, uma resolução de medida de ~1ps é alcançada para emular condições de corrida. Variações estatísticas de violações de tempo de hold são medidas em tecnologias CMOS de 130nm e 90nm para diversas configurações de circuitos, e também para diferentes condições de temperatura e Vdd. Essas violações são um ponto crítico em projetos grandes com milhares de caminhos curtos, pois se apenas um desses caminhos falhar, todo o circuito não vai funcionar em qualquer frequência. Usando os resultados medidos, a variabilidade é dividida entre sistemática e randômica residual usando métodos matemáticos. Testes de normalidade são aplicados a estes dados para verificar de eles são Gaussianos normais ou não. A probabilidade de violações de tempo de hold considerando nossos resultados medidos e skews de relógio típicos é calculada, mostrando que o problema de violações de tempo de hold aumenta com o avanço da tecnologia. Finalmente, um algoritmo para proteger circuitos digitais contra violações de tempo de hold em caminhos curtos é apresentado.

**Palavras-Chave:** Variabilidade de Processo, Violações de Tempo de Hold, Teste On-Chip, Skew de Relógio, Caracterização de Flip-Flop, Imunidade a Corrida, Microeletrônica.

#### 1 INTRODUCTION

With the development of Very-Deep Sub-Micron (VDSM) technologies, process variability is becoming increasingly important and is a very important issue in the design of complex circuits. Process variability is the statistical variation of process parameters, meaning that these parameters do not have always the same value, but become a random variable, with a given mean value and standard deviation. This effect can lead to several issues in digital circuit design.

The logical consequence of this parameter variation is that circuit characteristics, as delay and power, also become random variables. Because of the delay variability, not all circuits will now have the same performance, but some will be faster and some slower. However, the slowest circuits may be so slow that they will not be appropriate for sale. On the other hand, the fastest circuits that could be sold for a higher price can be very leaky, and also not very appropriate for sale. A main consequence of power variability is that the power consumption of some circuits will be different than expected, reducing reliability, average life expectancy and warranty of products. Sometimes the circuits will not work at all, due to reasons associated with process variations. At the end, these effects result in lower yield and lower profitability.

To understand these effects, it is necessary to study the consequences of variability in several aspects of circuit design, like logic gates, storage elements, clock distribution, and any other that can be affected by process variations. The main focus of this work will be storage elements.

Modern synchronous digital designs necessarily include a large amount of flip-flops (FF) in pipeline stages to improve data throughput. FF timing is determined by the CLK-Q propagation time, setup time and hold time. The setup time is the amount of time that the data input must be ready before the clock edge, while the hold time is the amount of time the flip-flop input data must remain stable after the clock edge. The variation of the propagation time due to process variability has been already investigated by Monte Carlo simulation (DAO, 2001). While statistical variations of setup and propagation times in critical paths are essential for maximum chip performance, a violation of the hold time in short FF-logic-FF paths leads to a chip failure due to a generation of races in the pipeline. Race conditions are caused by the combination of short paths, clock skew, and jitter between sending and receiving FFs, and process variations. The internal race immunity is a figure of merit to characterize the robustness of a FF against race conditions and is defined as the difference between

clock-to-Q delay and hold time. Hence, the race immunity can vary greatly between different FF types (MARKOVIĆ, 2001).

Since modern digital CMOS designs, such as microprocessors, DSP cores, and dedicated hardware accelerators typically comprise thousands of FFs, a statistical analysis of the internal race immunity in combination with clock uncertainties is mandatory. Especially scan chains for DFT schemes (HUANG, 2003), where FFs are connected in a serial fashion to build up a shift register during test mode, are sensitive since no logic is placed between the FFs. Therefore, several techniques for diagnosis of single or even multiple hold time failures in scan chains are proposed (HUANG, 2003) (EDIRISOORIYA, 1995) (GUO, 2001) (LI, 2005). There are also techniques to diagnose these failures in generic short logic paths (WANG, 2004) and buffer insertion to increase the delay of these paths. For example, hold time fixing, or padding, is typically done during chip design (SHENOY, 1993). However, depending on the design and FF properties, without detailed analysis of the critical clock skew and process variability, the extra delay introduced during hold-time fixing can be over or under estimated.

In this work, we therefore present a statistical analysis of the critical clock skew in several test paths, due to process variability in 130nm and 90nm CMOS technology. To facilitate an on-wafer test, a measurement circuit with a precision compatible to the speed of the technology is needed.

Once measured data is made available, several analyses may be performed on the data. Mathematical methods will be used to separate the variability between systematic and random residual, since each one of them can have different effects and different methods to cope with them.

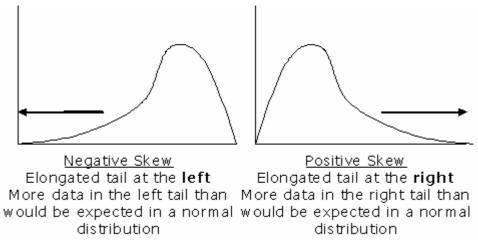

One issue that must be addressed is whether the measured distributions are normal Gaussian distributions or not. Different normality tests are available to check if this assumption is true. Although most process parameter distributions are known to be normal Gaussian, it is not necessarily true that higher level measures (delay, hold time, etc) will be Gaussian also.

Another important task to see the relevance of the issue of hold time violations is to combine the data on expected clock skews available in the literature with our data on FF race immunity. A circuit with a small clock skew will probably not pose problems regarding hold time violations, no matter how small the race immunity is; it is also true that a large clock skew can be catastrophic to this issue even if the FFs have large race immunity. So, the probability of hold time violations considering all the data available about race immunity and clock skew must be evaluated.

With all the data and analyses available, it is possible to propose methods to protect digital circuits against these issues, and to check if the empirical techniques used in the industry are in fact the most effective ones.

This thesis is organized as follows. Chapter 2 discusses the basic aspects and causes of process variability. Chapter 3 presents the FF characterization, and shows the impact of FF parameters on the hold time violation probability. In Chapter 4, we show the circuits that will be used as test cases. Chapter 5 contains the extra circuits needed to perform on-chip measurement. Chapter 6 presents the measurement results already obtained, that will be the basis to further analysis. The separation of variability between systematic and random residual, together with the mathematical methods used to

perform this task, is addressed in Chapter 7. The normality tests generally used to check if a distribution is a normal Gaussian distribution, and the results achieved with our data are presented in Chapter 8. Chapter 9 shows the calculation of probability of hold time violations when combining our measured data with typical clock skews reported in literature. Chapter 10 presents the options available to protect digital circuits against hold time violations, both after and before circuit fabrication. Finally, in the Chapter 11, we present the conclusions of this thesis.

#### 2 PROCESS VARIABILITY

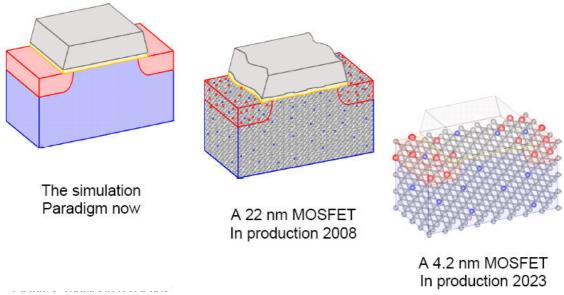

Parameter variability has always been an issue in integrated circuits. However, comparing with the size of devices, it is relatively increasing with technology evolution, as the device size shrinks in a larger scale than our control over them. Also, in the past, the variations were mostly due to imperfect process control, but now intrinsic atomistic variations become more important, as devices of atomic sizes are achieved. This parameter variation causes uncertainties in circuit design, as in timing, power dissipation, and others important properties. Figure 2.1 shows the technology scaling, to exemplify how small the devices are becoming. Approaching the atomic scale is very difficult to control the process, as only one atom can make a huge difference.

Figure 2.1: Expected technology scaling (ASENOV, 2003).

This chapter will address the main aspects of process variability. First, we will identify the different sources and types of variations. Then we enter in specific issues that cause variations, as lithography and doping. Finally, we must analyze the true impact on circuit design.

#### 2.1 Sources and types of variations

The variations can have different sources and types, as presented in (FRANK, 2004). The sources can be divided between process variations, environment variations and temporal variations. Process variations are variations due to lack of control on the fabrication process, since no two devices are exactly the same at atomic level. Environment variations are variations due to lack of perfect control over the environment (temperature, voltage, etc) in which the circuit must operate. Finally, temporal variations are variations which cause the device to behave differently at different times, as NBTI, for example.

The types of variations can be divided in global and local. Global are variations in the value of a parameter for the entire wafer, while local are device-to-device variations within any single chip. This distinction is important because these types require different statistical treatment for proper determination of impact on yield.

With these two classifications, we can build a matrix of variations, as shown in (FRANK, 2004). This matrix is presented in table 2.1.

|        | Process                                                                                                                                                  | Environment                                        | Temporal                                                                                                      |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| Global | <l<sub>g&gt; and <w>, <layer<br>thicknesses&gt;, <r>'s,<br/><doping>, <t<sub>ox&gt;, <v<sub>body&gt;</v<sub></t<sub></doping></r></layer<br></w></l<sub> | Operating temperature range, V <sub>DD</sub> range | <nbti> and Hot electron shifts</nbti>                                                                         |

| Local  | Line Edge Roughness (LER), Discrete doping, Discrete oxide thickness, R and V <sub>body</sub> distributions                                              | Self-heating, Hot spots, IR drops                  | Distribution of NBTI,<br>Voltage noise, SOI V <sub>body</sub><br>history effects, Oxide<br>breakdown currents |

Table 2.1: Matrix of variations.

The main focus here is about process variations, both global and local effects. In the next section we will discuss specific issues about process variations.

#### 2.2 Specific issues

The process parameter variations are caused by different aspects of circuit fabrication. The two major sources of process variations are the fabrications steps of lithography and doping. These two will be discussed in detail.

#### 2.2.1 Lithography

The lithographic sources of variations are the cause of both global and local variations. Imperfect lithographic process control and errors in alignment, rotation and magnification are the problems that lead to global variations. The critical dimensions are sensitive to focus, dose (intensity and time), resist sensitivity (chemical variations) and layer thicknesses (AUSSCHNITT, 2003) (BRUNNER, 2001).

The local lithographic variations are due to pattern sensitivity (interference effects from neighboring shapes), interference effects from buried features, and LER (Line Edge Roughness) (BRUNNER, 2003).

LER, which is primarily a discreteness effect, is due to sources of statistical variation in chemically amplified resists. These variations include fluctuations in the total dose due to finite number of quanta (shot noise), fluctuations in the photon absorption positions, nanoscale non-uniformities in the resist composition, statistical variations in the extend of acid-catalyzed deprotection, and statistical effects in polymer chain dissolution. For example, table 2.2 shows the estimated dose uncertainty for a 50nm contact hole, with different lithographic processes.

| Lithography     | Energy (eV) | Resist Dose<br>(mJ/cm²) | # quanta per<br>50nm pixel | 3σ dose<br>variation |

|-----------------|-------------|-------------------------|----------------------------|----------------------|

| 193nm           | 6.4         | 20                      | 500,000                    | 0.4%                 |

| EUV – 13.5nm    | 92          | 2                       | 3400                       | 5%                   |

| X-Ray $-1.3$ nm | 920         | 40                      | 6800                       | 4%                   |

| E-beam          | 50,000      | $150 (3 \mu C/cm^2)$    | 470                        | 14%                  |

| Ion-beam        | 100,000     | $50 (0.5 \mu C/cm^2)$   | 78                         | 34%                  |

Table 2.2: Shot noise for different energy quanta.

#### 2.2.2 Doping

The doping process causes mainly local variations, as there are less and less dopant atoms in the transistor channel, in every new technology node. Working with few atoms can lead to a strong variability in the threshold voltage, which is proportional to the square root of the number of dopant atoms.

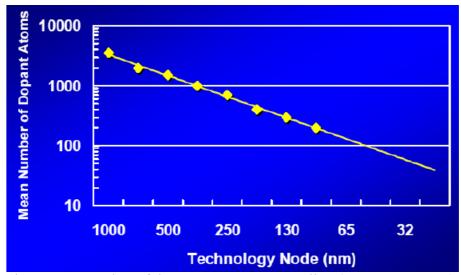

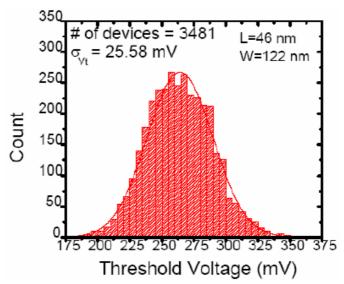

As showed in (FRANK, 2000), the number of dopant atoms in the depletion layer of a MOSFET has been scaling roughly as  $L_{\rm eff}^{1.5}$ . Statistical variation in the number of dopants, N, varies as  $N^{-1/2}$ , increasing  $V_T$  uncertainty for small N. And also, specific  $V_T$  uncertainties depend on the details of the doping profiles. Figure 2.2 shows a graphic of the scaling of number of dopant atoms versus scaling.

Figure 2.2: Number of dopant atoms versus scaling (BORKAR, 2004).

This doping uncertainty has a huge impact in the threshold voltage variability. (FRANK, 2002) shows an experiment with  $V_T$  measurements on 3481 identical SOI nFETs, all of single experimental macro on a single wafer (figure 2.3). The standard deviation can be up to 10% of the mean threshold value.

Figure 2.3: Threshold variability (FRANK, 2002).

## 2.3 Impact on circuit design

Process variations and intrinsic device variations cause logic and memory yield loss. Since the variations are Gaussian, and not bounded, it is not possible to absolutely guarantee functionality. Therefore, circuit designers must learn how to cope with variability, and the design must be based on achieving a target yield (90%, 98%, etc). The design automation tools must have means to evaluate correctly the yield.

Today, EDA tools evaluate the designs using corners. Designers usually simulate using nominal parameter values, worst case values, and best case values. And they attempt to achieve high yield at the worst case. This is clearly too pessimistic, as with process variations, it is very rare that all the devices will simultaneously show this worst case value. It is much more possible that some of them go to one direction and others to another. This leads to statistical timing analysis tools. Now, the paths do not have one deterministic timing result, but one statistical result.

According to (ROHRER, 2006), it is necessary to verify the product response to all variations. The main responses are in power and frequency. Power variability includes variation in IDDQ (Vth fluctuation, temperature spread, voltage drop) and AC power spread (device capacitance, metal capacitance), while frequency variability includes Lg variations, thermal variations, voltage variations, and metal thickness variations. Another important product response is the possibility of failure due to setup time and hold time violations, which are a consequence of delay variability and clock skew.

In general, the fabricated circuits will show a Gaussian range of performance. Some will be so slow that will not be sold, while others will be very fast, but also too leaky. The ones near the mean value will be the good ones that go to the market.

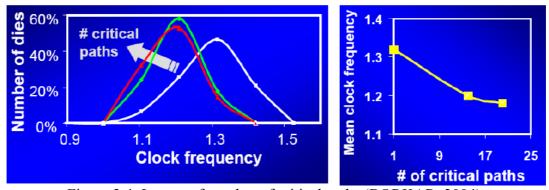

Another serious issue related to variability and circuit design is the performance loss with the increase of the number of critical paths. As they are uncorrelated, with many critical paths, the probability that only one becomes slower than the nominal case is larger. Figure 2.4 shows the impact of the number of critical paths on performance.

Figure 2.4: Impact of number of critical paths (BORKAR, 2004).

These are the main problems that can be seen in circuit design due to process variability. It is important to develop techniques to cope with these problems, to achieve better performance and higher yield, increasing profit.

#### **3** FLIP-FLOPS AND HOLD TIME VIOLATIONS

Digital circuits necessarily include storage elements to ensure correct operation. The most common are the flip-flops (FFs). Although they are not very difficult to use, their operation must be understood and they must be characterized due to their timing metrics. They are not immune to failures, and one failure that FFs can present is the hold time violation, if they are not carefully designed. This chapter discusses FF operation and metrics, and hold time violations.

#### 3.1 Flip-flop timing metrics

FFs are edge-triggered clocked storage elements. They are frequently built from latches (MARKOVIĆ, 2000). They connect the input data to the output data in the clock's rising (or falling) edge, holding the signal stable until the next rising (falling) edge. FFs are usually used to store data during a short or long time and also to store data only during a pipeline cycle of a circuit. Transitions at the FF input do not propagate to its output, unless during the edge of the clock cycle. However, to ensure correct operation, FF data and clock input must satisfy some timing restriction.

As defined in (MARKOVIĆ, 2000), the FF timing metrics can be physical: setup time, hold time, clock-to-output delay and data-to-output delay; or synthetic, built to help system design: delay and internal race immunity. This section will detail all of them.

#### 3.1.1 Setup time

The common definition of setup time is the time interval before the active clock edge during which data is not allowed to change, in order to ensure FF correct operation (HODGES 1988) (RABAEY 1996) (DALLY 1998). However, this classical definition is not very precise, because there is an increase in clock-to-output delay when data arrives very close to setup time.

An alternative definition for setup time, frequently used by ASIC standard cell libraries, is based in the fact that a 5% increase from the nominal value in the clock-to-output delay can be tolerated. With this assumption, (MARKOVIĆ, 2000) makes the following definition:

"Setup time is the minimum data-to-clock offset that causes the clock-to-output delay to be 5% higher than its nominal value.

- 1) Setup of logic '1' is the setup time measured when data undergoes a 0-1 transition.

- 2) Setup of logic '0' is the setup time measured when data undergoes a 1-0 transition."

Setup time can be positive or negative, depending especially on the FF circuit topology. Figure 3.1 shows the graphical definition of setup time.

Figure 3.1: Definitions of setup and hold times (MARKOVIĆ, 2000).

#### 3.1.2 Hold time

Hold time is analogous to the setup time, but measured after the active clock edge. In (MARKOVIĆ, 2000), hold time is also defined based on the tolerance to an increase in the delay:

"Hold time is the minimum time interval during which a new data has to retain its value after the active clock edge so that clock-to-output delay is 5% higher than its nominal value.

- 1) Hold of logic '1' is the hold time measured when data undergoes a 0-1 transition.

- 2) Hold of logic '0' is the hold time measured when data undergoes a 1-0 transition."

If data changes too fast, the circuit may not work correctly. As setup time, hold times can also be positive or negative, depending mainly on circuit topology.

#### 3.1.3 Clock-to-output delay

According to (MARKOVIĆ, 2000), the clock-to-output delay is the delay measured from the active clock edge to the output. It depends on the data-to-clock offset, clock slope, supply voltage, and output load. The rising and falling delays cannot, in general, be identical because the two cases will experience a variety of rising and falling delays (HARRIS 1999).

#### 3.1.4 Data-to-output delay

The last physical metric is the data-to-output delay. It is the delay measured from a 0-1 or 1-0 data transition to the output, assuming that the FF is clocked correctly. The data-to-output delay is not a good metric of a FF performance because it depends on the arrival of new input data relative to clock (MARKOVIĆ, 2000).

#### **3.1.5 Delay**

For high-level system design, it is important to have one relevant metric to describe the true impact of the FF in the circuit. It is possible to reduce the metric to one FF delay parameter with respect to system performance (STOJAN 1999). It is defined as following:

"The delay of a FF is the sum of its clock-to-output delay (measured at setup time) and setup time."

This definition is independent on simulation setup, avoiding misconceptions present in literature about FF speed, often characterized as clock-to-output delay (SVEN 1998) (BALSARA 2000).

#### 3.1.6 Internal race immunity

The synchronous digital systems are subjected to clock skew, which is the maximum difference between two different FF clock inputs. So, maximal clock skew that a system can tolerate is determined by FFs. To quantify this FF timing metric, the concept of internal race immunity is introduced (MARKOVIĆ, 2000):

"Internal race immunity of a FF is the difference between its clock-to-output delay and hold time."

Equation 3.1 gives the formula of this definition.

$$R = t_{CLK-Q} - t_{hold} \tag{3.1}$$

This is a helpful metric to help designers to prevent against timing failures due to short-paths (races). It also tells the maximum clock skew that a FF can tolerate. However, different FFs have different race immunities. Typically, faster FFs have smaller race immunity, and slower FFs, such as the master-slave FF, have larger race immunity.

#### 3.2 Hold time violations

The most common source of timing failures in high-speed digital systems is the lack of race immunity (race immunity is smaller than the clock skew). It is usually named hold time violations, or race conditions.

Considering two logically adjacent FFs, controlled by CLK1 and CLK2, with no logic between them, they are potentially subjected to a clock skew. If the clock skew is large enough, i.e. CLK2 arrives after CLK1 and exceeds the internal race immunity  $t_{CLK-Q} - t_{hold}$  of the FF, a race is produced and detected if the output of both FFs are of same value at same time (Q1(t)=Q2(t)). The violation can be detected by initializing the FFs with opposite values, and applying a pulse in the data input, as shown in figure 3.2. As long as Q1(t) $\neq$ Q2(t) pipeline operation is correct.

Figure 3.2: Timing diagram showing hold time violation.

Equation 3.2 describes the timing conditions in the case of a violation. Especially, fast FFs with large hold times are sensitive to hold time violations.  $\Delta t_{var}$  includes variations from different sources.

$$t_{CLK-Q} - t_{hold} - t_{CLKskew} - \Delta t_{var} < 0$$

(3.2)

It is possible to see that the FF race immunity (that is inherent to the FF type and transistor sizes used in the design), the maximum clock skew found in the circuit, and process variations contribute to the probability of a hold time violation. If the clock uncertainty is very well controlled and race immunity is large enough, process variability plays a minor role, but this is not the case of the majority of semi-custom

designs that have to meet short time-to-market. Usually, the clock uncertainty and race immunity are of about the same order of magnitude, as it is going to be presented later on this text.

#### 4 CIRCUITS UNDER TEST

The circuits can be very sensitive to process variability, but different circuits can have different sensibilities. To have representative results, the circuits that will be fabricated to be tested must be carefully chosen. First, the sensitivity of the logic circuits will be verified through simulation in 130nm and 90nm technologies, however only the results for 90nm will be shown in this chapter. Using MC simulations, the sensitivity of inverters (representing generic combinational circuits) and FFs will be measured. Combining them, we will verify if hold time violations are a potential problem, and if they can be generated by process variations. Finally, the circuits chosen for fabrication and measurement in silicon will be shown.

#### 4.1 Inverter Sensitivity

We know from the process specifications the expected variability of the process parameters. However, it does not tell about the true effect in the delay variability of the logic circuits. The sensitivity of these logic circuits must be analyzed to find the potential problem. A chain of two inverters will be used to investigate it (figure 4.1). Monte Carlo simulations with 100 iterations were performed to estimate both the global and local variations. Different inverter sizes were also analyzed: the smallest one found in the cell library and the biggest one (20 times the size of the former).

Figure 4.1: Logic circuit to investigate delay variability.

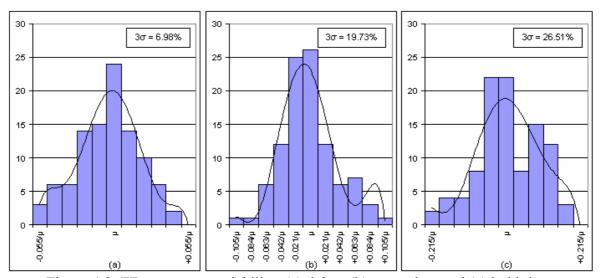

The simulations showed that the inverters present high delay variability, closely modeled by a Gaussian curve. It can be described by the mean of the results, and the relative standard deviation. Figure 4.2 shows the results of rising transitions delay, for

all combinations of inverters and sources of variability (global, local and both). The exact mean values had to be omitted due to confidentiality reasons, but they are in the range of a typical 90nm process.

Figure 4.2: Monte Carlo simulation results for rising transitions: small inverters (1x) and (a) only global variations, (b) only local variations, and (c) both variations; large inverters (20x) and (d) only global variations, (e) only local variations, and (f) both variations.

The results show that, for the small cell, the global variability is about two times larger than the local variability. However, in the larger cell, the difference between them is more than 10 times larger, due to the great decrease of the impact of the local variations.

#### 4.2 FF sensitivity

The sequential elements must also be characterized in its sensitivity to variations. Three different parameters are important in this case: delay, setup time and

hold time. The FFs to be tested are master-slave edge-triggered type D FFs. They are of the smallest driving capacity in the library. Besides the D and CLK inputs, the FF also has the signals RN, TI, TE. RN is a reset signal, while TI (test input) and TE (test enable) are for test purposes, to be used in a boundary scan chain. These inputs help to decrease the hold time, and they were used instead of normal FFs because they are commonly used in commercial products to increase testability.

The same methodology was applied, using Monte Carlo simulations to measure the mean and the deviation of the delay, setup time and hold time. Figure 4.3 shows the results for rising transitions.

Figure 4.3: FF parameter variability: (a) delay, (b) setup time and (c) hold time.

The results show that the FF delay has a smaller relative variability than the inverters, but the absolute variability is about three times larger, because of the much larger FF delay. The setup and hold time deviation have about the same value as the inverters (because they are not as large as the delay).

## 4.3 Hold Time Violation Probability

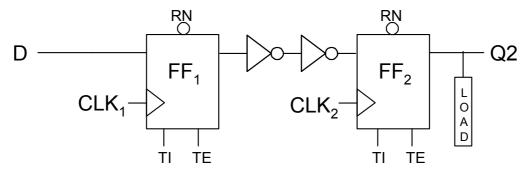

Examining the sensitivity of FFs and inverters, one can notice that they can vary by several picoseconds. Now let's put it all together to look into the probability of a hold time violation being produced. Figure 4.4 shows the circuit initially used to measure this. It has a logic path between two FFs, and the FFs have two different clock inputs. By delaying CLK2 in relation to CLK1, we are producing an artificial clock skew.

Figure 4.4: Circuit with FFs and inverters to check hold time violation.

To detect a violation, the FFs must be initialized with opposite values, and then a transition must be applied in the input. If there is no clock skew, FF1 will change to the new input value, and FF2 will change to the previous FF1 value. If the clock skew is increased, the circuit still operates correctly while the skew is smaller than the delay of the logic path. Using a parametric simulation, the skew was increased by steps of 1ps, until the FF2 does not sample the correct value, characterizing a hold time violation. The exact skew which makes the path fails is called critical clock skew, and is determined by a parametric simulation using the nominal process parameters.

Using this methodology, the critical clock skew was found for this configuration and also for other ones. It was compared with the typical clock skews achieved by complex circuits in the same technology. They were in the same magnitude order, showing that it is a potential problem.

The next step was to determine the impact of process variations on the hold time violation probability. To do so, the skew was fixed as the critical clock skew, and Monte Carlo simulation was performed. Then we can see the percentage of times that the circuit will fail, even though it should work using nominal parameters. The percentage of violations in this case was 48%. To have an idea about the standard deviation, the simulation was repeated decreasing and increasing the skew by 3ps. The percentage of failing circuits was 17% and 82%, respectively. This showed that a fine resolution is needed for the precise measurement of the critical skews, since within a small range of 3ps, the difference between the percentage of violations was large.

#### 4.4 Test Circuits for Fabrication

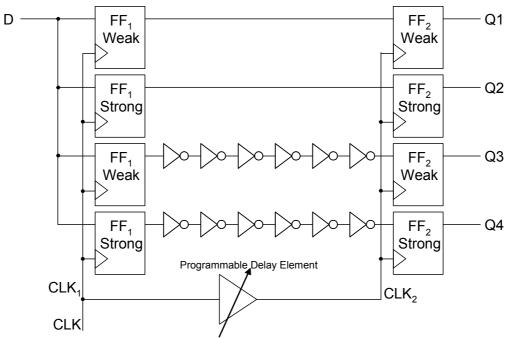

After examining that the hold time violations are a real possibility, we must decide which circuits will be fabricated in silicon to provide a wide analysis of the variability. Four different paths were then chosen.

The two basic configurations are two simple pipeline stages with two master-slave edge-triggered FFs without logic between them, representing one stage of a scan chain. Further pipelines including six small inverters between the FFs, represent short logic paths. The FFs used in this work are conventional rising edge-triggered master-slave FFs composed of CMOS transmission gates in the forward propagation path and C<sup>2</sup>MOS latches in the feedback loops (GEROSA, 1994) with typical library extensions such as input and output node isolations and local clock buffers.

For each configuration a version with the weakest FF of the standard cell library, i.e. smallest transistor sizes and hence largest sensitivity to process variations, and a version with 8x increased driving strength is used. Comparing the results of both it is possible to analyze the impact of different transistor dimensions on the variability. The inverters used in both versions are of the minimum size, since these configurations represent typical non-critical paths where large driving capability is not required. Figure 4.5 shows the different 4 combinations of circuits under test.

To emulate clock uncertainties, the sending and receiving FFs are controlled by different clock signals. The clock signal CLK2 of the receiving FFs is generated by a programmable delay line. If this artificial clock skew is large enough, i.e. CLK2 arrives after CLK1 and exceeds the internal race immunity  $t_{\text{CLK-Q}}$ - $t_{\text{HOLD}}$  of the FF, a race is produced and detected if the output of both FFs are of same value at same time (Q1(t)=Q2(t)). The violation can be detected by initializing the FFs with opposite values, and applying a pulse in the data input. As long as Q1(t) $\neq$ Q2(t) pipeline operation is correct.

Figure 4.5: Different test circuits with sensitivity to hold time violations.

The programmable delay element must be able to provide an adequate resolution for good statistics. By simulation, it was verified that a resolution that would be able to achieve in the available technology was about 1ps. The next section shows the development of the circuitry able to test the circuits showed in this section.

## **5** MEASUREMENT CIRCUITS

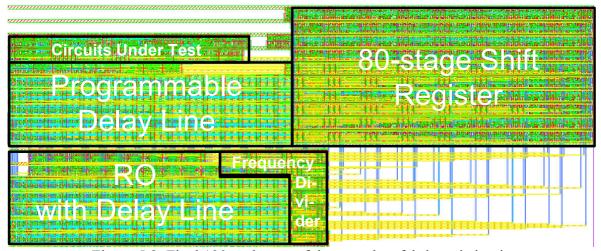

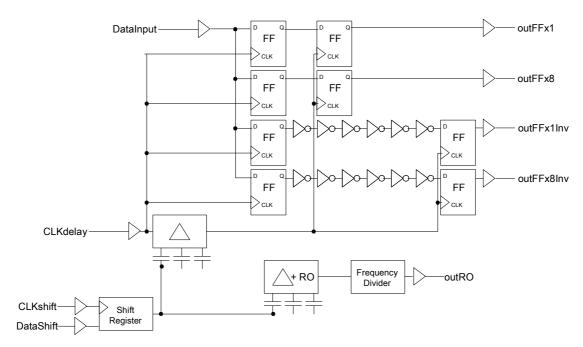

In this chapter, it is shown all circuits that are needed to perform the measurement of the test circuits on wafer, as published in (NEUBERGER, 2006). First, the delay line that will produce the artificial skew between the FF clocks is discussed. Then the ring oscillator needed to calibrate the delay line is showed. The next step is the design of a shift register to reduce the number of inputs. Finally, we put it all together and show the final layout.

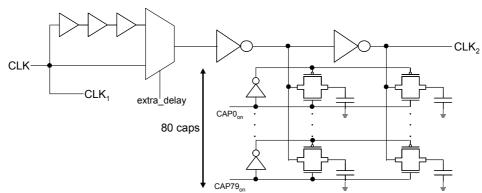

## 5.1 Programmable Delay Line

As stated in the previous section, we need a scheme to produce an artificial skew between the clocks of the two FFs in the circuit under test. It must be programmable over different skews, and must have an accurate enough resolution for the given technology, to produce good statistics. The chosen structure able to do this was a programmable delay line.

To specify the critical clock skew producing a hold time violation, the artificial skew is programmable over a wide range of 80 steps corresponding to a resolution of ~1ps. The delay line is composed of two inverters, and 80 NMOS gate capacitances as load elements connected to the inverters via pass transistors. The capacitances and transistors were carefully designed to be able to achieve steps of the desired resolution.

For coarse-grain clock skew shifting a multiplexer to enable or disable a further buffer chain is added. It is needed because the versions with 0 or 6 inverters have very different critical clock skews, so the buffer chain needs an equivalent delay of about 6 inverters. Fig. 5.1 shows the implemented circuit.

Figure 5.1: Schematics of the programmable delay line for the clock skew emulation.

An essential part of the delay line is the design of the load elements (the NMOS and PMOS pass transistors, and the NMOS gate parasitic capacitance). Different transistor widths and configurations were tried until the resolution of 1ps could be achieved. Even the extracted parasitic capacitances in the layout had a great impact in the achievable delay, and caused a redesign in the layout. Figure 5.2 shows the final layout of the small cell composed by these 3 transistors.

Figure 5.2: Final layout of the load elements.

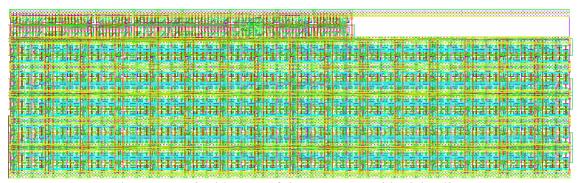

The final layout of the complete programmable delay line is shown in figure 5.3. The first row is composed by the 2 inverters, multiplexer and buffers, while in the other rows there are the 80 programmable parasitic capacitances.

Figure 5.3: Final layout of the programmable delay line.

## 5.2 Ring Oscillator

Once the delay line is designed, we must use a method to measure the delay that is actually programmed on it. It is not possible to just program a specific number of capacitances and consider that the delay is the one achieved by simulation. It is necessary to measure the delay externally.

To measure the absolute time produced by a specific setting of the programmable delay line, it is additionally placed in the middle of a ring oscillator. The ring oscillator is connected to an 11-stage frequency divider to monitor the output frequency. Thus, it is possible to determine the programmed delay based on measuring and comparing the frequencies achieved with different numbers of capacitances.

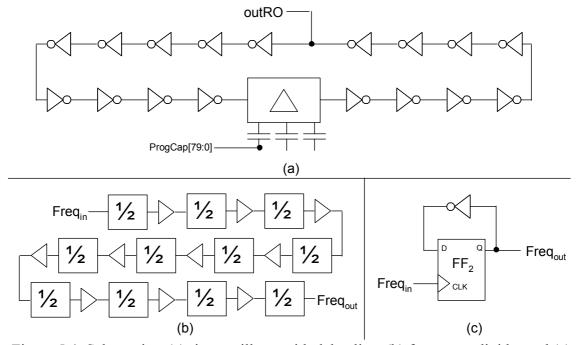

The ring oscillator was designed with 17 inverters plus the delay line. In the output of the oscillator, 11 stages of a frequency divider were used to achieve externally a frequency that the available equipments would be able to measure with enough precision. The frequency divider is very simple, composed by a FF and an inverter. Figure 5.4 shows the schematics of these components.

Figure 5.4: Schematics: (a) ring oscillator with delay line, (b) frequency divider and (c) one stage of the frequency divider.

## 5.3 Shift Register

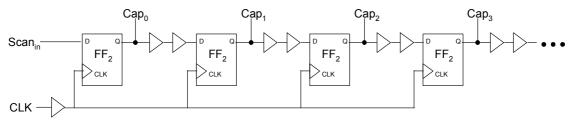

After the design of the delay line, it was verified that many input pins would be needed to program all over the 80 different configurations. To reduce the number of pins, the methodology of programming was changed to serial. A chain of 80 flip-flops in a shift register scheme was implemented to allow the delay line programming. By doing so, the 80 pins were substituted by only two: scan\_in for data input and CLKscan to control the FFs clock. The drawback is the extra time needed for programming before the measurement itself. But it was the only option, since the available probecard had only 24 pins. Figure 5.5 shows the shift register. Two buffers were included between each FF to avoid hold time violations.

Figure 5.5: Schematic of the shift register.

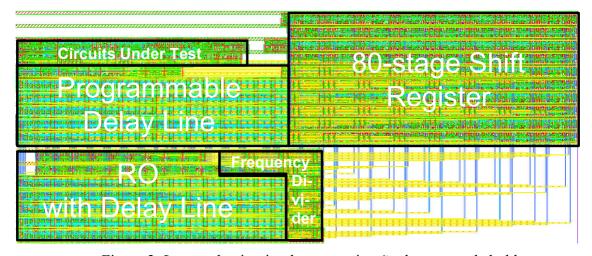

## 5.4 Final Circuit and Layout

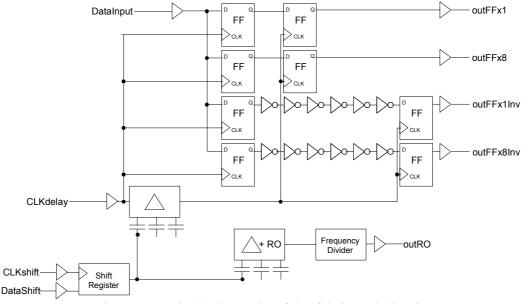

After the design of all blocks, it is time to put them all together. Figure 5.6 shows the final block-based schematic. In the top right are the four circuits under test. They are driven by the same input, but they have each one its own output. The CLK1 signal is provided externally for the test circuits and the delay line. The delay line then creates the delayed CLK2 and sends it to the four paths. Both the delay line that sends the CLK signals and the one in the middle of the ring oscillator are programmed by the shift register. The shift register needs one data and one clock input. The output of the ring oscillator goes to the 11-stage frequency divider. The ring oscillator and the frequency divider use a different Vdd than the rest of the circuit, to avoid voltage drop due to the high switching activity. All the inputs and outputs of the circuit are buffered.

Figure 5.6: Final schematic of the fabricated circuit.

Looking to the circuits, it is possible to see that the total number of PADs needed is 15. This is less than the number of PADs in the available probecard (24 PADs). The circuit was then manufactured and it was be possible to measure it without problems. The final modification must include a buffer able to drive the PADs. To design it, we must use a PAD model. The buffer able to drive it was composed of a set of buffers in increasing scale. Figure 5.7 shows the PAD model and the driving buffer.

Figure 5.7: (a) PAD model and (b) driving buffer.

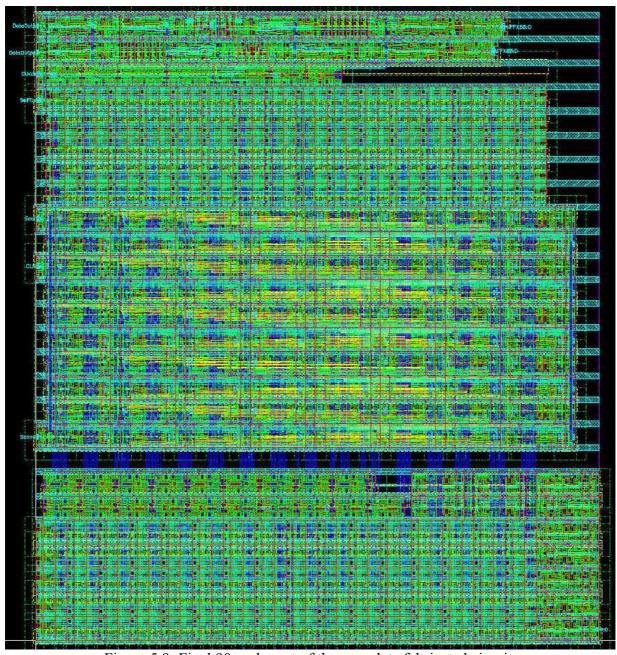

After the design of the circuits, the layout is straightforward. The circuits are very regular, resulting in simple placement and routing. A full-custom methodology was used, to minimize area and delay and to decrease the impact of process variations in parts other than the circuits under test. Figure 5.8 shows the final layout in a 130nm technology and its blocks, while in figure 5.9 it is possible to see the 90nm layout.

Figure 5.8: Final 130nm layout of the complete fabricated circuit.

Figure 5.9: Final 90nm layout of the complete fabricated circuit.

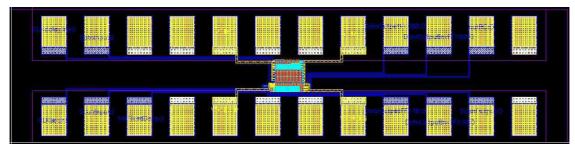

The final step is to route the inputs and outputs to the PADs. A template for the PADs, with 24 of them, was used, but not all of them are needed. The input PADs were placed in the left, the outputs in the right, and power (the two pairs of Vdd and Gnd) in the middle. It is shown in the figure 5.10.

Figure 5.10: Final layout with PADs.

After the complete layout was finished, a final design rule check was performed, and simulations with extracted parasitics. It worked as expected. The circuit is ready for fabrication.

## **6** EXPERIMENTAL RESULTS

In this chapter, we discuss the setup of the equipments needed to perform the measurements, and results found in these measurements. First, the basic setup is shown; and then the measurement flow followed in each circuit measurement is drawn. All the measured data with the different combinations (technologies, temperature, Vdd's) is shown in the second part of this chapter.

## 6.1 Measurement Flow and Setup

The circuits were fabricated in 130nm and 90nm low power CMOS technology, and two wafers in 130nm and one wafer in 90nm were measured. Each 130nm wafers has 182 chips, but the 90nm wafer only 36 (there were other circuits on the same die, leading to a larger die size). The total size of the 130nm chip is 180 x 71 $\mu$ m, while the size of the 90nm is 70 x 77  $\mu$ m. The measurements are done at different temperature and voltage source conditions.

The wafers were not sliced and encapsulated for individual measurement, but measured directly with a Süss prober, to allow a spatial analysis of the results over the wafer. The prober has its temperature controlled.

A Tektronix DG2030 data generator was used to provide the inputs. It has 8 independent sources, but only 6 of them were used (data input and clock input for the test circuits, data input and clock input for the shift register, a signal to choose between the two delay line configurations, and a signal to trigger the oscilloscope). The oscilloscope was a Tektronix TDS5054. It has only 4 channels, while 5 are needed (the four test circuit outputs, and the ring oscillator output). So, the measurement had to be done in two steps, changing the cables between them: first the measurement of only the ring oscillator frequencies, and second the test of the circuits. Moreover, two voltage sources were used to provide the power to the circuit.

All the equipments were connected to a PC, and the measurement process was partially automated via the PC using the software LabVIEW. The LabVIEW programs were carefully designed and modularized, so there are different modules for all different tasks (data generator initialization, oscilloscope initialization, frequency measurement, etc). In the end, there is one top level module that uses them all to perform the complete measurement.

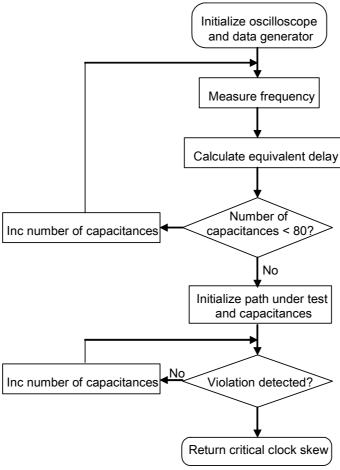

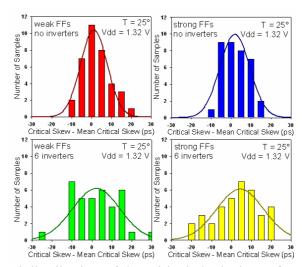

For the measurement, first the settings for all combinations of the 80 capacitances are written into the shift register. Then the frequencies of the ring oscillator are