# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

#### GUILHERME AUGUSTO FLACH

# Discrete Gate Sizing and Timing-Driven Detailed Placement for the Design of Digital Circuits

Thesis presented in partial fulfillment of the requirements for the degree of Doctor on Microelectronics

Marcelo de Oliveira Johann Advisor

Ricardo Augusto da Luz Reis Coadvisor

#### CIP - CATALOGING-IN-PUBLICATION

Flach, Guilherme Augusto

Discrete Gate Sizing and Timing-Driven Detailed Placement for the Design of Digital Circuits / Guilherme Augusto Flach. – Porto Alegre: PGMICRO da UFRGS, 2015.

104 f.: il.

Thesis (Ph.D.) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica, Porto Alegre, BR–RS, 2015. Advisor: Marcelo de Oliveira Johann; Coadvisor: Ricardo Augusto da Luz Reis.

1. Discrete Gate Sizing. 2. Timing-Driven Detailed Placement. 3. Lagrangian Relaxation. 4. EDA. 5. Microelectronic. I. Johann, Marcelo de Oliveira. II. Reis, Ricardo Augusto da Luz. III. Título.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos Alexandre Netto

Vice-Reitor: Prof. Rui Vicente Oppermann

Pró-Reitor de Pós-Graduação: Prof. Vladimir Pinheiro do Nascimento

Diretor do Instituto de Informática: Prof. Luís da Cunha Lamb

Coordenador do PGMICRO: Prof. Fernanda Gusmão de Lima Kastensmidt Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

# **ACKNOWLEDGMENTS**

To my family...

## **ABSTRACT**

Electronic design automation (EDA) tools play a fundamental role in the increasingly complexity of digital circuit designs. They empower designers to create circuits with several order of magnitude more components than it would be possible by designing circuits by hand as was done in the early days of microelectronics. In this work, two important EDA problems are addressed: gate sizing and timing-driven detailed placement. They are studied and new techniques developed. For gate sizing, a new Lagrangian-relaxation methodology is presented based on local timing information and sensitivity propagation. For timing-driven detailed placement, a set of cell movement methods are created using drive strength-aware optimal formulation to driver/sink load balancing. Our experimental results shows that those techniques are able to improve the current state-of-the-art.

**Keywords:** Discrete Gate Sizing, Timing-Driven Detailed Placement, Lagrangian Relaxation, EDA, Microelectronic.

# Dimensionamento de Portas Discreto e Posicionamento Detalhado Dirigido a Desempenho para o Projeto de Circuitos Digitais

# **RESUMO**

Ferramentas de projeto de circuitos integrados (do inglês, electronic design automation, ou simplesmente EDA) têm um papel fundamental na crescente complexidade dos projetos de circuitos digitais. Elas permitem aos projetistas criar circuitos com um número de componentes ordens de grandezas maior do que seria possível se os circuitos fossem projetados à mão como nos dias iniciais da microeletrônica. Neste trabalho, dois importantes problemas em EDA serão abordados: dimensionamento de portas e posicionamento detalhado dirigido a desempenho. Para dimensionamento de portas, uma nova metodologia de relaxação Lagrangiana é apresentada baseada em informação de temporarização locais e propagação de sensitividades. Para posicionamento detalhado dirigido a desempenho, um conjunto de movimentos de células é criado usando uma formação ótima atenta à força de alimentação para o balanceamento de cargas. Nossos resultados experimentais mostram que tais técnicas são capazes de melhorar o atual estado-da-arte.

**Palavras-chave:** Dimensionamento de Portas Discreto, Posicionamento Detalhado Dirigido à Desempenho, Relaxação Lagrangiana, EDA, Microeletrônica.

## LIST OF ABBREVIATIONS AND ACRONYMS

ABU Average Bin Utilization

AWE Asymptotic Waveform Evaluation

CAD Computed-Aided Design

DP Dynamic Programming

EDA Electronic Design Automation

eTNS Total Negative Slack for Early Timing Mode

eWNS Worst Negative Slack for Early Timing Mode

HPWL Half-Perimeter Wirelength

ICCAD International Conference on Computer Aided Design

ISPD International Symposium in Physical Design

KKT Karush-Kuhn-Tucker

LCB Local Clock Buffer

LDP Lagrangian Dual Problem

LR Lagrangian Relaxation

LRS Lagrangian Relaxation Sub-Problem

ITNS Total Negative Slack for Late Timing Mode

IWNS Worst Negative Slack for Late Timing Mode

MOR Model Order Reduction

NP Nondeterministic Polynomial Time

PP Primal Problem

PRIMA Passive Reduced-order Interconnect Macromodeling Algorithm

QoR Quality of Results

QS Quality Score

RC Resistor (R) - Capacitor (C)

RLC Resistor (R) - Inductor (L) - Capacitor (C)

RTL Register Transfer Level

SA Simulated Annealing

SSTA Statistical Static Timing Analysis

STA Static Timing Analysis

StWL Steiner Tree Wirelength

TDDP Timing-Driven Detailed Placement

TDP Timing-Driven Placement

TNS Total Negative Slack

VLSI Very Large Scale Integration

WNS Worst Negative Slack

# **LIST OF SYMBOLS**

| f | Femto |

|---|-------|

|   |       |

$\mu$  Micron/Mean

m Milli

n Nano

$\Omega$  Ohms

p Pico

∑ Summation

$\sigma$  Standard deviation

$V_{th}$  Threshold Voltage

# **LIST OF FIGURES**

| Figure 1.1:  | Design Flow of Digital Synchronous Circuits                          | 22  |

|--------------|----------------------------------------------------------------------|-----|

| Figure 1.2:  | Iterations over the Design Flow with Increasing Levels of Accuracy . | 24  |

| Figure 2.1:  | Static Timing Analysis in the Design Flow                            | 25  |

| Figure 2.2:  | A combinational circuit and its timing graph                         | 26  |

| Figure 2.3:  | Timing Sense                                                         | 27  |

| Figure 2.4:  | D-type Register (Flip-Flop)                                          | 29  |

| Figure 2.5:  | Timing diagram for a positive edge-triggered register (flip-flop)    | 30  |

| Figure 2.6:  | Lookup Table                                                         | 30  |

| Figure 2.7:  | Timing characteristics of a timing arc                               | 31  |

| Figure 2.8:  | A Simple RC Network                                                  | 32  |

| Figure 2.9:  | Model Order Reduction                                                | 33  |

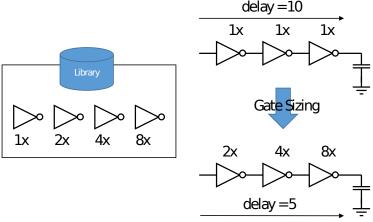

| Figure 3.1:  | Gate Sizing Problem                                                  | 35  |

| Figure 3.2:  | Sources of Leakage Current                                           | 37  |

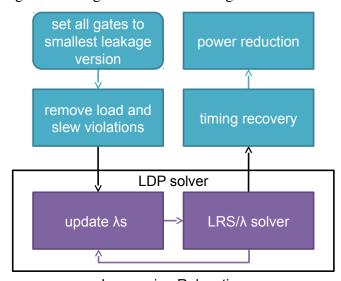

| Figure 4.1:  | Basic algorithm to solve the Lagrangian dual problem                 | 46  |

| Figure 4.2:  | An example circuit                                                   | 47  |

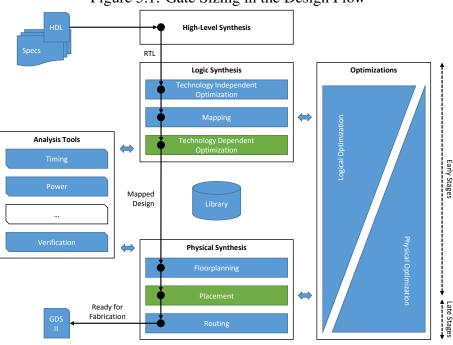

| Figure 5.1:  | Gate Sizing in the Design Flow                                       | 50  |

| Figure 5.2:  | Local timing evaluation after a gate has been sized                  | 52  |

| Figure 5.3:  | High-level view of our gate selection flow                           | 53  |

| Figure 5.4:  | Lambda-Delay Cost Computation                                        | 57  |

| Figure 5.5:  | Delay Sensitivity Computation                                        | 58  |

| Figure 5.6:  | Slack Compression                                                    | 68  |

| Figure 5.8:  | Sizes and Vth Changes                                                | 69  |

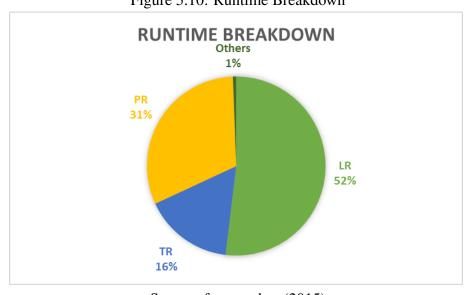

| Figure 5.10: | Runtime Breakdown                                                    | 69  |

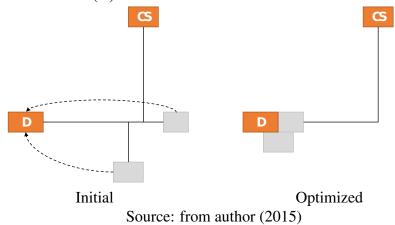

| Figure 6.1:  | Influence of Placement on Wirelength                                 | 73  |

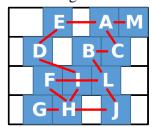

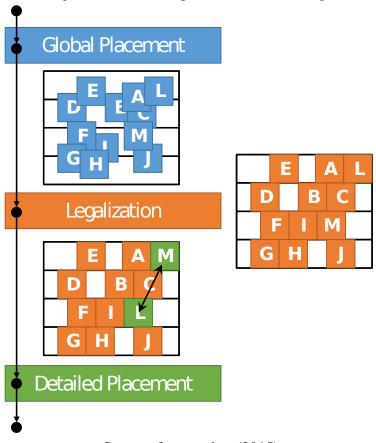

| Figure 6.3:  | Main Steps of a Placement Stage                                      | 74  |

| Figure 7.1:  | Timing-Driven Detailed Placement in the Design Flow                  | 78  |

| Figure 7.2:  | Legalization via Nearest White Space Search                          | 80  |

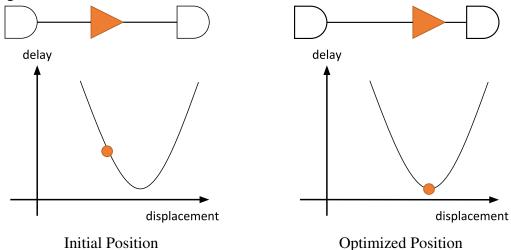

| Figure 7.4:  | Buffer Balancing Technique aims to find a buffer position that mini- | 0.1 |

| D' 7.6       | mizes timing violation.                                              | 81  |

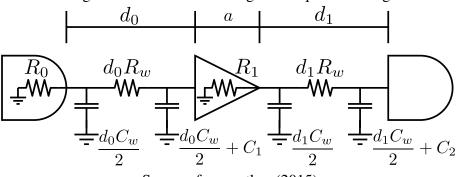

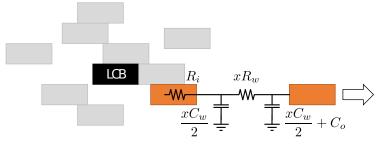

| Figure 7.6:  | Buffer Balancing Technique Modeling                                  | 81  |

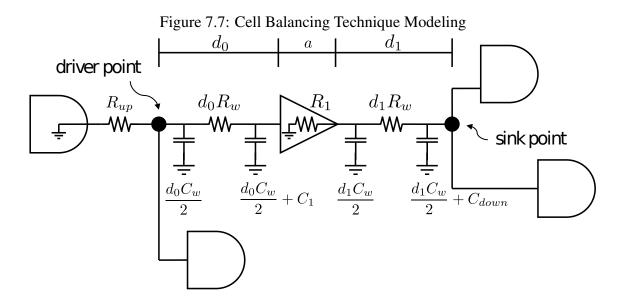

| Figure 7.7:  | Cell Balancing Technique Modeling                                    | 82  |

| Figure 7.8:  | Load Reduction of critical nets. Non-critical sinks (gray cells) are | 0.4 |

|              | moved closer to their driver cell (D)                                | 84  |

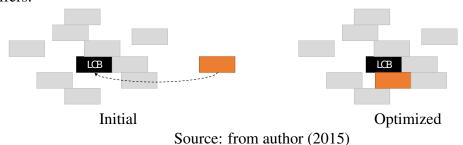

| Figure 7.10: | Useful Clock Skew Optimization by Moving Registers Closer to Lo- |    |  |  |

|--------------|------------------------------------------------------------------|----|--|--|

|              | cal Clock Buffers                                                | 35 |  |  |

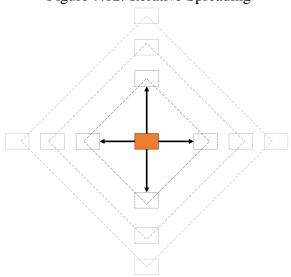

| Figure 7.12: | Iterative Spreading                                              | 35 |  |  |

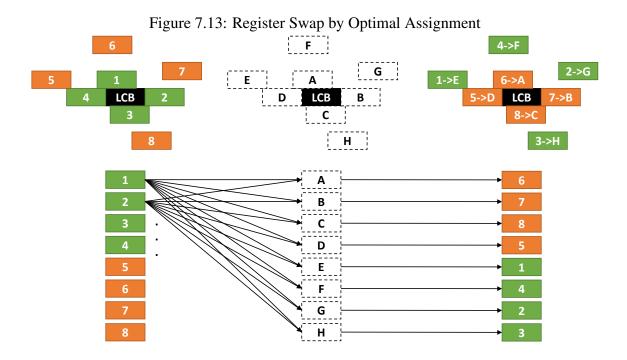

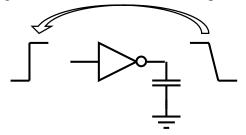

| Figure 7.13: | Register Swap by Optimal Assignment                              | 36 |  |  |

| Figure 7.14: | Register-to-Register Early Violation Path Fix                    | 37 |  |  |

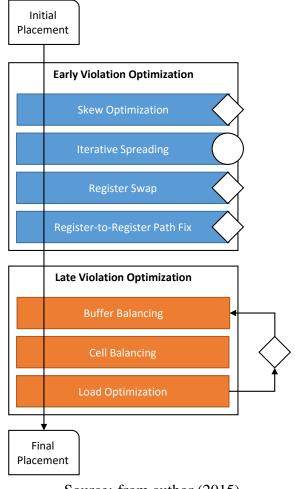

| Figure 7.15: | Timing-Driven Detailed Placement Flow                            | 38 |  |  |

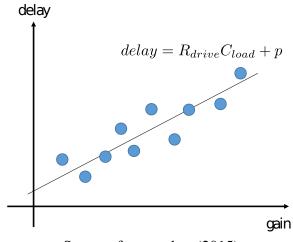

| Figure 7.16: | Estimating the Driver Resistance of a Timing Arc (Cell) 9        | 90 |  |  |

| Figure 7.17: | Reference Slew Computation                                       | 1  |  |  |

# **LIST OF TABLES**

| Table 2.1:                             | Information provided by a STA tool for pins                                                                 | 28             |

|----------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------|

| Table 3.1:<br>Table 3.2:<br>Table 3.3: | Sizing Classification                                                                                       | 36<br>42<br>43 |

| Table 5.1:<br>Table 5.2:               | Definitions of some terms used in this work                                                                 | 52             |

| Table 5.3:<br>Table 5.4:<br>Table 5.5: | are taken from the corresponding papers                                                                     | 65<br>66<br>67 |

| Table 5.6:                             | results                                                                                                     | 70             |

| Table 7.1:                             | Moves Developed in this Thesis                                                                              | 79             |

| Table 7.2:<br>Table 7.3:               | Configuration of the ICCAD 2015 Contest benchmarks                                                          | 89<br>91       |

| Table 7.4:                             | Improvement of this flow over the initial placement results for long maximum displacement.                  | 92             |

| Table 7.5:                             | Improvement of this flow over the initial placement results for short maximum displacement.                 | 92             |

| Table 7.6:                             | Comparison of this flow and results from the 1st place at ICCAD 2015 contest for long maximum displacement  | 93             |

| Table 7.7:                             | Comparison of this flow and results from the 1st place at ICCAD 2015 contest for short maximum displacement | 93             |

| Table 7.8:                             | Average improvement on quality score per move type for long maximum displacement                            | 94             |

| Table 7.9:                             | Impact on results when pin importance (criticality and centrality) is used in Cell Balancing.               | 95             |

| Table 7.10:                            | Impact on results when bad move filtering is disabled                                                       | 95             |

# **CONTENTS**

| 1 IN  | NTRODUCTION                                               | 21 |

|-------|-----------------------------------------------------------|----|

| 1.1   | Design Flow of Digital Synchronous Circuits               | 22 |

| 1.1.1 | Logic and Physical Synthesis Merging                      | 23 |

| 1.1.2 | Design Flow Iterations                                    | 23 |

| 1.2   | Contributions and Scope of This Thesis                    | 24 |

| 2 S   | TATIC TIMING ANALYSIS (STA)                               | 25 |

| 2.1   | Timing Graph                                              | 26 |

| 2.2   | Timing Mode                                               | 26 |

| 2.2.1 | Late (Max)                                                | 26 |

| 2.2.2 | Early (Min)                                               | 27 |

| 2.3   | Timing Sense                                              | 27 |

| 2.4   | Timing Information                                        | 27 |

| 2.5   | Timing Propagation                                        | 28 |

| 2.5.1 | False Paths                                               | 29 |

| 2.6   | Timing Tests                                              | 29 |

| 2.7   | Timing Models                                             | 30 |

| 2.7.1 | Cells                                                     | 30 |

| 2.7.2 | Interconnections                                          | 31 |

| 3 G   | ATE SIZING                                                | 35 |

| 3.1   | Sizing Problem Classification                             | 35 |

| 3.2   | Sizing Formulation                                        | 36 |

| 3.3   | Gate Sizing for Leakage Power Minimization                | 36 |

| 3.4   | Challenges                                                | 38 |

| 3.5   | Related Work                                              | 38 |

| 3.5.1 | Early Work                                                | 39 |

| 3.5.2 | State-of-the-Art                                          | 41 |

| 3.5.3 | Summary                                                   | 42 |

| 4 G   | ATE SIZING VIA LAGRANGIAN RELAXATION                      | 45 |

| 4.1   | Lagrangian Relaxation                                     | 45 |

| 4.1.1 | Solving the Lagrangian Dual Problem                       | 46 |

| 4.2   | Applying Lagrangian Relaxation in the Gate Sizing Problem | 47 |

| 4.2.1 | Lagrangian Relaxation                                     | 48 |

| 4.2.2 | Simplification of $\mathcal{LRS}_{\lambda}$               | 48 |

| 5 N        | EW DISCRETE GATE SIZING AND VTH ASSIGNMENT FLOW US- |                  |

|------------|-----------------------------------------------------|------------------|

| IN         | IG LAGRANGIAN RELAXATION                            | 49               |

| 5.1        | Contributions                                       | 49               |

| 5.2        | Scope                                               | 49               |

| 5.3        | Background                                          | 50               |

| 5.4        | Performance Optimization                            | 51               |

| 5.5        | <b>Definitions</b>                                  | 52               |

| <b>5.6</b> | Flow Overview                                       | 53               |

| <b>5.7</b> | Lagrangian Relaxation                               | 53               |

| <b>5.8</b> | Solving LDP                                         | 55               |

| 5.9        | Solving $LRS/\lambda$                               |                  |

| 5.9.1      | Local Timing Update                                 | 56               |

| 5.9.2      | Lambda-Delay Cost                                   | 57               |

| 5.9.3      | Lambda-Delay Sensitivity                            | 58               |

| 5.9.4      | Gate Version Selection                              | 60               |

| 5.9.5      | Modeling Interconnections                           | 61               |

| 5.10       | Improving the Lagrangian Relaxation Solution        | 62               |

| 5.10.1     |                                                     | 62               |

| 5.10.2     |                                                     | 62               |

| 5.11       | Experimental Setup                                  | 64               |

| 5.11.1     |                                                     | 64               |

| 5.12       | Results on ISPD 2012 Contest Benchmarks             | 64               |

| 5.12.1     | r 8                                                 | 65               |

| 5.12.2     | r                                                   | 66               |

| 5.12.3     | r in a real real real real real real real re        | 66               |

| 5.12.4     | 2                                                   | 66               |

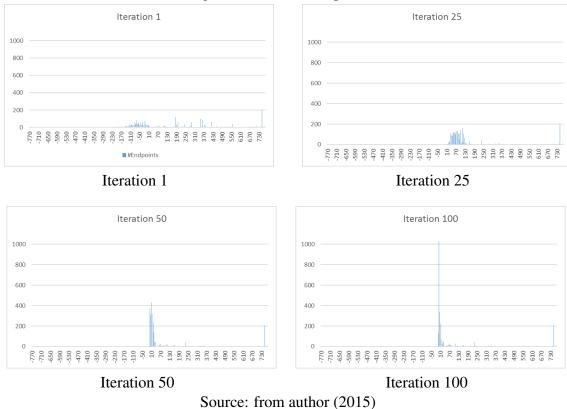

| 5.12.5     |                                                     | 68               |

| 5.13       | Results on ISPD 2013 Contest Benchmarks             | 69<br>70         |

| 5.14       | Conclusions                                         | 70               |

| 6 P        | LACEMENT                                            | 73               |

| 6.1        | Timing-Driven Detailed Placement                    | 74               |

| 6.2        | Related Works                                       | 75               |

|            |                                                     |                  |

|            | RIVE STRENGTH AWARE CELL DISPLACEMENT FOR TIMING-   |                  |

|            | RIVEN DETAILED PLACEMENT                            | 77<br>           |

| 7.1        | Contributions                                       | 77               |

| 7.2        | Scope                                               | 77               |

| 7.3        | Criticality and Centrality                          | 78<br><b>7</b> 0 |

| 7.4        | Moves                                               | 79<br><b>7</b> 0 |

| 7.4.1      | Legalization                                        | 79<br>70         |

| 7.4.2      | Filtering out Bad Moves                             | 79               |

| 7.5        | Late Optimization                                   | 80               |

| 7.5.1      | Buffer Balancing                                    | 80               |

| 7.5.2      | Cell Balancing                                      | 82               |

| 7.5.3      | Load Optimization                                   | 83               |

| <b>7.6</b> | Early Optimization                                  | 84<br>84         |

| , n I      | NEW LIMITHY 2010                                    | X/I              |

| 7.6.2      | Iterative Spreading                                   | 85 |

|------------|-------------------------------------------------------|----|

| 7.6.3      | Register Swap                                         | 85 |

| 7.6.4      | Register-to-Register Path Fix                         | 86 |

| 7.7        | Flow                                                  | 87 |

| <b>7.8</b> | Experimental Setup                                    | 88 |

| 7.8.1      | Quality Score                                         | 89 |

| 7.8.2      | Benchmarks                                            | 89 |

| 7.8.3      | Assumptions and Limitations                           | 89 |

| <b>7.9</b> | Library Characterization                              | 90 |

| 7.9.1      | Move Gains                                            | 93 |

| 7.9.2      | Impact of Pin Importance (Criticality and Centrality) | 94 |

| 7.9.3      | Impact of Filtering Out Bad Moves                     | 94 |

| 7.10       | Conclusions                                           | 95 |

| 8 F        | FINAL REMARKS                                         | 97 |

| REFI       | ERENCES                                               | 99 |

## 1 INTRODUCTION

During the 1950-70's, humanity has experienced a shift from analog and mechanical components to digital in the mainstream technology. This change marks the beginning of the Digital Revolution, which, as the Agriculture and Industrial counterparts, brought several improvements in the well-being of the mankind.

The digital technology allows much faster, reliable and cheap computation and communication. Digital signals are more tolerant to noise. Data can be sent through long distances and even tolerate errors by sophisticated error-correcting methods. Moreover by using only two discrete values to represent information, the systems are simplified making them easier to design, test and produce compared to an analog circuit with about the same number of components.

Two technological breakthroughs can be pointed out as the main milestones in the Digital Revolution: the invention of transistor and the very-large scale integration (VLSI).

The transistor was invented in 1947 by American physicists John Bardeen, Walter Brattain, and William Shockley. It is a semiconductor device that can be used as a switch enabling fast, non-mechanical computation. It is the basic building-block of modern circuits.

But was not until the late 60's and early 70's that the real impact of transistors took place as new technologies enabled several transistors and other components to be built out of the same block. From that point on, the number of components integrated into a same chip has been doubled approximately every two years, following Moore's observation from 1975 referred to as Moore's Law (MOORE, 1975).

As the number of components grew, the complexity of designing an integrated circuit also increased. First designs were literally designed by hand, but this soon became a bottleneck and the first software to aided the circuit design were created in mid-1970's. In early 1980's, the idea of using programming languages and compiling them to hardware started to consolidate (MEAD; CONWAY, 1979). This notion further pushed the development of computer-aided design (CAD) software for chip design, currently known as Electronic Design Automation (EDA) software. Today all digital circuit designs are done using EDA tools from the translation of high-level hardware description languages to the output file format used to fabricated them.

Several steps are required to design an integrated circuit, each step being composed by one or more EDA tools which are run in a sequential or iterative way. Other tools are also used to measure the circuit performance, power consumption among other characteristics. These steps and measurement tools compose the design flow of digital circuits.

In this work, new observations and techniques for gate sizing and timing-driven detailed placement steps of the design flow are presented. These techniques are implemented as stand-alone EDA tools and the results obtained are reported and analysed.

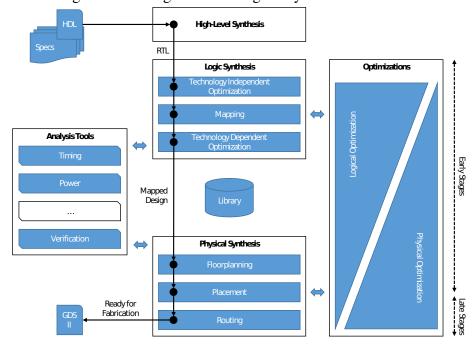

## 1.1 Design Flow of Digital Synchronous Circuits

The design flow is a set of steps performed to convert a design specification to a low-level description which is not just ready to be fabricated, but is optimized and meet the requirements from the specification.

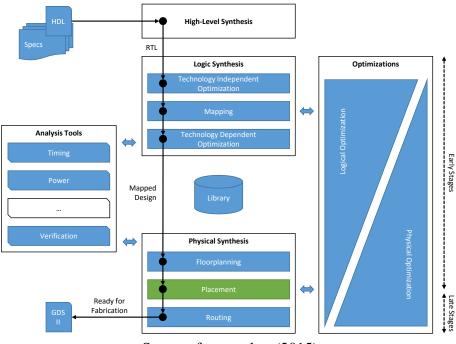

A typical design flow for digital synchronous circuits using the standard cell methodology is presented in Figure 1.1. Standard cell methodology, which is the dominant design methodology, translates a design description to a description where pre-characterized components or cells from a library are used. Other methodologies do exists as full-custom and library-free automatic generation, but they are out of scope of this work.

Figure 1.1: Design Flow of Digital Synchronous Circuits

Source: from author (2015)

It should be noted that the flow presented in Figure 1.1 is only a reference flow, the actual flow used by designers may vary, although the overall idea is the same.

The design flow is divided into three main phases -(1) high-level synthesis, (2) logic synthesis and (3) physical synthesis - responsible to bring the design state gradually more closely to the optimized and low-level state required for fabrication.

In the high-level synthesis phase, the circuit specification is translated into a register-transfer level (RTL) abstraction. RLT represents the circuit as data and control signals flowing through logical operations between storage elements (referred to as registers). This representation is closely related to the final design implementation in the sense that it uses the two basic components of circuit designs: storage and logic elements.

Logic synthesis takes the RTL representation, optimizes it and create an implementable design representation by mapping the storage and logic elements to a library of standard elements previously built for the target technology. After mapping, more optimizations are performed. Among the techniques used during logic synthesis are logic minimization, sizing, restructuring, retiming, buffering.

Finally, during the physical synthesis a floorplanning for the optimized and mapped circuit is defined. After that, elements are placed and the interconnections between them

are generated.

In general, each phase is broken down into steps, which may be further subdivided. A step is composed by a core method responsible to achieve the specific goal of that step combined with calls to other more general optimization procedures.

Several optimization methods are available and used throughout the flow as structuring, re-time, gate sizing, buffer insertion, placement optimization, routing optimization. These methods can be called several times during the design flow and a typical flow may have several different implementation of each kind of optimization method applying different strategies.

Measurement tools as timing analysis, power analysis, verification among others support the steps and optimization techniques providing up-to-date information about the current state of the design. Many methods use built-in analysis tools, though usually these built-in tools use more simplified models to trade-off accuracy and runtime.

## 1.1.1 Logic and Physical Synthesis Merging

In early days, logic synthesis and physical synthesis were two completely separated phases. However this wall between them – as some authors referred it to – started to be teared down due to the increase of interconnection importance to define the circuit characteristics in newer technologies.

This merge happened in both ways. Logic synthesis methods start to use more accurate interconnection and physical information and physical synthesis methods start to call optimization methods that were only called during logic synthesis before. So, beside the iterations, the flow itself is now designed in such a way to allow this kind of iteration between logic and physical synthesis.

#### 1.1.2 Design Flow Iterations

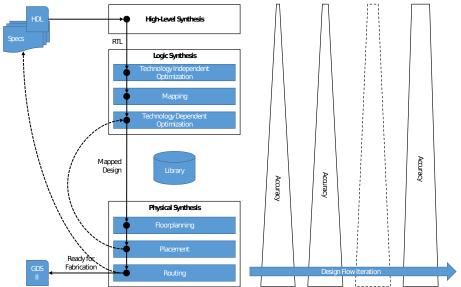

The design of an integrated circuit usually takes several iterations over the design flow to be finished. An iteration happens any time the flow is restarted in an early stage to use more precise or detailed data obtained in a later stage. This processes and the increase of modeling accuracy is depicted in Figure 1.2.

Figure 1.2: Iterations over the Design Flow with Increasing Levels of Accuracy

Source: from author (2015)

# 1.2 Contributions and Scope of This Thesis

In this work the gate sizing and placement optimization method are studied and new techniques are developed. They are developed intended to be used in early stages of the design flow, although they can be extended to work on more sophisticated models suitable for late stages. Both method have an important impact on the timing closure of the design, playing a direct role to meet the timing requirements.

# 2 STATIC TIMING ANALYSIS (STA)

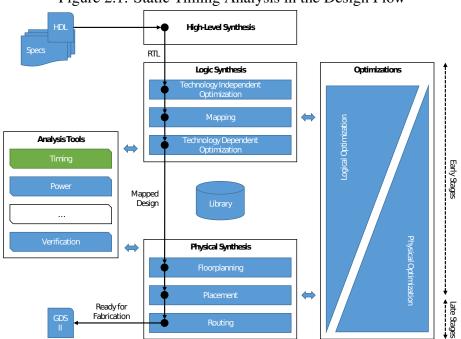

Static timing analysis (STA) is a fast method for asserting and verifying the timing of a circuit independently of the stimulus applied to it. The analysis is called static as the timing characteristics of elements are usually computed assuming that other signals are not changing. STA computes the upper and lower bounds of the amount of time signals take to propagate inside the circuit through its several elements and interconnections. These bounds are then used to guarantee that the circuit will work properly in the specified frequency.

STA is generally available as a sign-off tool in the design flow as shows Figure 2.1, although some methods may implement their own simplified, built-in static timing analysis for performance reasons. It is executed several times during the design flow using different levels of accuracy depending on the physical information available or the accuracy required. It is not uncommon to perform a STA using simplified timing models even if detailed timing information is already available to trade-off accuracy and runtime.

Figure 2.1: Static Timing Analysis in the Design Flow

Source: from author (2015)

# 2.1 Timing Graph

For the purpose of static timing analysis, a digital circuit is composed by combinational and sequential cells whose pins are connected via interconnections allowing signals to propagate.

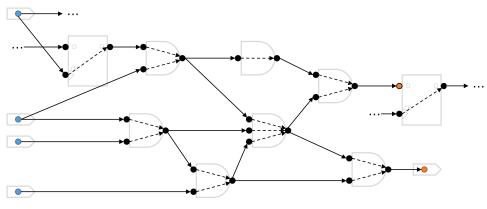

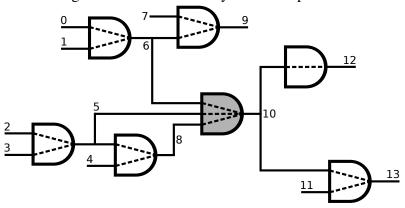

A static timing analysis is performed on a directed graph where nodes represent the cell pins and edges represent the path connecting such pins. A design and its respective graph model is exemplified in Figure 2.2.

Figure 2.2: A combinational circuit and its timing graph.

Source: from author (2015)

Edges are also more commonly referred to as timing arcs and they are classified in two categories depending on the element that the edge describes. If an edge connects two pins of a same cell, it is called a cell timing arc. On the other hand, if an edge connects two pins of different cells it is called a net timing arc.

# 2.2 Timing Mode

A static timing analysis is performed typically in two modes: late and early. These two modes compute the upper and lower propagation delay bounds representing the worst and best case scenarios respectively. Some other methods as Statistical Static Timing Analysis (SSTA) (GULATI; KHATRI, 2009) may be used to compute the circuit delay using variability ranges, but they are out of the scope of this work.

In general, different characterizations for cells and interconnections are used for each timing mode. For early mode, the interconnections and cells are supposed to work on their best case scenario, i.e, as fast as possible. On the other hand, for late mode, the interconnections and elements are expected to work on their worst case scenario, i.e. as slow as possible.

#### **2.2.1** Late (Max)

The late mode computes the worst case scenario returning the maximum time signals take to propagate through the timing graph.

The late mode is used to verify the maximum frequency the circuit can operate - a central goal in circuit design. That is why it is the most common mode and many times during the flow it is the only mode being asserted.

#### **2.2.2** Early (Min)

The early mode compute the best case scenario returning the minimum time signals take to propagate through the timing graph. This information is useful to eliminate some kind of timing violations caused when a pin changes its state before the storage element has time to store the value.

## 2.3 Timing Sense

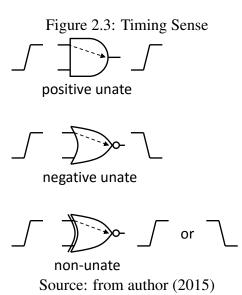

Cell timing arcs have a timing sense, which indicates the direction of an output transition w.r.t. the direction of the input transition assuming that the other inputs are constant. The direction of a transition can be either rising or falling. The timing senses are depicted in Figure 2.3.

A timing arc is *positive unate* if the direction of the signal is kept when propagating through the arc. Timing arcs of non-inverting buffers, ORs, ANDs are positive unate.

A timing arc is *negative unate* if the direction of the signal is inverted when propagating through the arc. Timing arcs of inverters, NORs, NANDs are negative unate.

The arc is called *non-unate* when it may be inverting or non-inverting depending on the values of other inputs. Timing arcs of XOR, XNOR are non-unate. By definition, the timing arcs from clock to the data output of sequential elements are also marked as non-unate as the signal does not actually propagates through them, but depends on the data stored.

# 2.4 Timing Information

Typically a STA tool provides several information about pins and timing arcs that designers and tools can made use of to identify violations and room for improvements. For timing arcs, the delay and slew are provided. Table 2.1 summarizes the typical data provided for pins.

By definition, the late and early slack at pin P are defined as in Equation (2.1) and Equation (2.2).

| Data          | Symbol    | Description                                                    |  |  |

|---------------|-----------|----------------------------------------------------------------|--|--|

| arrival time  | $at_P$    | The maximum (late mode) or minimum (early mode) time           |  |  |

|               |           | a signal takes to reach the pin $P$ .                          |  |  |

| required time | $rat_P$   | The time a signal is required to reach pin $P$ to avoid timing |  |  |

|               |           | violation.                                                     |  |  |

| slack         | $slack_P$ | Indicates the amount of time the signal reaching pin $P$ can   |  |  |

|               |           | be delayed (late mode) or sped up (early mode) without         |  |  |

|               |           | causing violation. Negative values indicate the amount of      |  |  |

|               |           | time required to fix the violation.                            |  |  |

| slew          | $slew_P$  | Indicate the slew at pin $P$ .                                 |  |  |

Table 2.1: Information provided by a STA tool for pins.

$$slack_P^{early} = at_P - rat_P (2.1)$$

$$slack_P^{late} = rat_P - at_P (2.2)$$

# 2.5 Timing Propagation

The models used to define the timing characteristics of elements and hence the timing characteristics of timing arcs may vary, but the overall idea of timing propagation in STA is the same.

Starting from primary inputs, the delay is propagated through timing arcs by summing the arrival time at the input pin of the timing arc with the timing arc delay. When multiple timing arcs converge to a same pin, the maximum delay for late mode or the minimum delay for early mode is propagated. Similarly, the largest slew for late mode or the smallest slew for early mode are propagated to a pin when multiple timing arcs converge. The basic arrival time propagation method for static timing analysis for late mode can be written as in Algorithm 2.1.

```

Algorithm 2.1: Arrival Time Propagation

```

- 1 set arrival time of path startpoints

- **2 for** each pin j in topological order **do**

- $at_i \leftarrow -\infty$

- **for** each timing arc  $i \rightarrow j$  **do**

Then, from endpoints to startpoint, require times are propagated by subtracting the timing arcs delays. Wherever two or more timing arcs converge to a same pin, the maximum required time is propagated for early mode and the minimum required time is propagate for late mode. The basic required time propagation method for static timing analysis for late mode can be written as in Algorithm 2.2.

#### **Algorithm 2.2:** Required Time Propagation

```

1 set required time of path endpoints

```

```

2 for each pin i in reverse topological order do

```

```

at_i \leftarrow +\infty

```

```

for each timing arc i \rightarrow j do

```

#### 2.5.1 False Paths

Some paths represented in the timing graph may never be stimulated in the actual design. This may be caused due to logical contradictions or simply because the design does not use them. Such paths are called false paths. Usually STA tools allow designers to define such paths by disabling some timing arcs so that signal does not propagate through them.

## 2.6 Timing Tests

Once the arrival times have been propagated through the timing graph, the slack at endpoints are verified. A timing violation occurs whenever the slack at an endpoint is negative. For late mode, a timing violation occurs when the arrival time at an endpoint is larger than the required time at that same endpoint. Analogously, for early mode, a timing test fails when the arrival time is smaller than the required time.

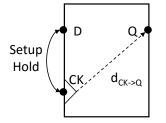

For the discussion in this work, a D-type register (flip-flop) as shown in Figure 2.4 is assumed where D is the input pin, CK is the clock pin and Q is the output pin. Other types of flip-flops can be handled in a similar way.

Figure 2.4: D-type Register (Flip-Flop)

Source: from author (2015)

In order to retain the data correctly, the data signal at D must be stable before and after the clock signal reaches the storage element via CK pin as illustrated in Figure 2.5. The time required before is defined as the *setup time*  $(t_{setup})$  and the time required after is defined as the *hold time*  $(t_{hold})$ .

When the clock signal is received, the data stored by the register is not immediately available at its output pin. The time required to the data to be available after the clock signal arrives is defined as  $d_{CK\to Q}$  (usually read as "clock to Q"). The  $CK\to Q$  timing arc is modeled in the same way as the a non-unate combinational timing arc.

For sequential elements, in the late mode, the required time is defined as a specified clock period, T plus the clock signal latency to reach the sequential cell,  $l_o^{early}$ , less the setup time as in Equation (2.3).

Clock signal

D data stable setup hold

Q data stable

Figure 2.5: Timing diagram for a positive edge-triggered register (flip-flop).

Source: from author (2015)

$$rat_D^{setup} = rat_D^{late} = T + l_o^{early} - t_{setup}$$

(2.3)

In the early mode, the required time is defined as the clock latency,  $l_o^{late}$ , plus the hold time as in Equation (2.4).

$$rat_D^{hold} = rat_D^{early} = l_o^{late} + t_{hold} (2.4)$$

# 2.7 Timing Models

STA can be used with several different timing models for cells and interconnections. In this section, some of the most common models are presented.

#### 2.7.1 Cells

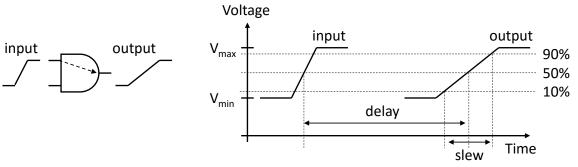

Cell delays can be modeled as simple as a constant value, linear equations or non-linear equations usually described by look-up tables. Look-up tables are the standard industry model for synthesis. Basically it is a two-dimensional table containing several samples of a timing characteristic of a cell (i.e. delay, output slew). The data is generated by accurate electrical simulation. The table is addressed by a load (capacitance) and an input slew as shown in Figure 2.6.

Figure 2.6: Lookup Table

Source: from author (2015)

The timing characteristic of a timing arc are represented in Figure 2.7. Delay is measured from the time the input signal reaches 50% of the logical-one voltage value to the time the output signal reaches 50%. Slew is typically measured as the amount of time required for a signal to go from 10% to 90% (or 20% to 80%) and vice versa.

Figure 2.7: Timing characteristics of a timing arc.

Source: from author (2015)

#### 2.7.2 Interconnections

The interconnection simulation for sophisticated models is the most timing consuming part of a STA. Several models may be used depending on the accuracy required or the information available. Sophisticated models can handle several aspects of interconnections including crosstalk, noise and can fairly estimate the values from a full electrical simulation.

#### 2.7.2.1 Lumped

The lumped model is not actually a delay model as it represents the interconnection by a single capacitance. This capacitance is summed to the load a cell is driving. In spite of its simplicity and inaccuracy, it is used as a fast estimate of the delay due to interconnection mainly in early stages of the design flow.

#### 2.7.2.2 Elmore Delay

Electrical simulation is very timing consuming. Generally the timing information is required to be updated several times in the design flow, and therefore, for highly-iterative methods, electrical simulation may be prohibitive.

The Elmore delay model (ELMORE, 1948) can be used as a fast, upper bound approximation of the actual delay of an RC network.

For trees-like networks (acyclic networks), the Elmore delay,  $D(P_j)$ , at a pin  $P_j$  can be computed recursively as shown in Equation (2.5) where  $R_{i\to j}$  is the resistance connecting  $P_i$  to  $P_j$  and  $C_{down}$  is the sum of all capacitances from  $P_i$  down to the tree leaves.

$$D(P_j) = D(P_i) + R_{i \to j} C_{down}$$

(2.5)

For mesh-like networks (cyclic networks), it can be computed throughout a nodal analysis replacing capacitances by current sources of same magnitude and removing all voltage sources (MUSTAFA CELIK LARRY PILEGGI, 2002). The node voltage is the Elmore delay of the respective node.

Therefore we can find the Elmore delay for each RC network node,  $\vec{\tau}$ , by solving the linear system presented in Equation (2.6) where G is the conductance matrix of the RC network and  $\vec{c}$  is the capacitance associated with each network node.

$$G\vec{\tau} = \vec{c} \tag{2.6}$$

Since the Elmore delay is related to the RC value of nodes, we can write the Equation (2.6) in a more straightforward fashion. The inverse of G is the resistance matrix, R, so we can write Equation (2.6) as in Equation (2.7).

$$G\vec{\tau} = \vec{c} \to \vec{\tau} = G^{-1}\vec{c} \to \vec{\tau} = R\vec{c} \tag{2.7}$$

For an RC network with n nodes, the conductance matrix G is an  $n \times n$  symmetric matrix, which is built as follow. Let  $r_{ij}$  be the resistance connecting node i to node j and  $r_i$  the resistance connecting node i to ground (drive resistance) so the conductance matrix,  $G = [g_{ij}]$ , is defined by Equation (2.8).

$$g_{ij} = \begin{cases} -\frac{1}{r_{ij}} & i \neq j\\ \frac{1}{r_i} + \sum_{k=1, k \neq i}^{n} \frac{1}{r_{ik}} & i = j \end{cases}$$

(2.8)

Now we present a simple example on how to build the Elmore system for the RC network shown in Figure 2.8. The corresponding linear system is shown in Equation (2.9).

$\begin{array}{c|c} & & & \\ \hline \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ &$

Figure 2.8: A Simple RC Network

Source: from author (2015)

$$\begin{bmatrix} \frac{1}{R_0} + \frac{1}{R_{01}} + \frac{1}{R_{02}} & -\frac{1}{R_{01}} & -\frac{1}{R_{02}} \\ -\frac{1}{R_{01}} & \frac{1}{R_1} + \frac{1}{R_{01}} + \frac{1}{R_{12}} & -\frac{1}{R_{12}} \\ -\frac{1}{R_{02}} & -\frac{1}{R_{12}} & \frac{1}{R_2} + \frac{1}{R_{02}} + \frac{1}{R_{12}} \end{bmatrix} \begin{bmatrix} \tau_0 \\ \tau_1 \\ \tau_2 \end{bmatrix} = \begin{bmatrix} c_0 \\ c_1 \\ c_2 \end{bmatrix}$$

(2.9)

Since matrix G is sparse and positive semi-definite (BHATIA, 2006) we can use the Incomplete Cholesky Conjugate Gradient method (SHEWCHUK, 1994) to solve the linear system in Equation (2.6).

#### 2.7.2.3 Model Order Reduction (MOR)

Model order reduction works by creating a simplified (or reduced) model of the interconnection as exemplified in Figure 2.9. This reduced model is then simulated using electrical simulation.

Figure 2.9: Model Order Reduction

Driver Model

Reduced Interconnection Model

Sink Model

Sink Model

Sink Model

response to input transition computed

Source: from author (2015)

MOR techniques can be classified into two types: (1) moment matching-based MOR techniques and (2) node elimination-based MOR techniques (KIM; KIM, 2009).

MOR techniques based on moment matching reduce an interconnection into a small model by matching some of the interconnection moments. Some moment matching-based MOR techniques are Asymptotic Waveform Evaluation (AWE) (PILLAGE; HUANG; ROHRER, 1989), Passive Reduced-order Interconnect Macromodeling Algorithm (PRIMA) (ODABASIOGLU; CELIK; PILEGGI, 1998), Pade via Lanczos (FELDMANN; FRE-UND, 1995). As the important moments are preserved, these techniques usually present a good accuracy. However the macro-model does not represent directly a linear RLC interconnection, which may be an issue for some applications.

Node elimination-based MOR techniques reduce an interconnection directly by removing less important nodes. The reduced model represent a linear RC interconnection. Although they are less accurate when compared with the moment matching techniques, these methods are more efficient. Some examples of node elimination-based MOR techniques are TICER (SHEEHAN, 1999) and  $R^2$ -Power (CHE et al., 2009).

## 3 GATE SIZING

Gate sizing also referred as gate selection is a process where the sizes of the design components are set as illustrated in Figure 3.1. It is a very effective way to tune the design to meet timing and reduce area and power consumption by selecting proper components sizes as the component sizes define how fast the component will be and how much power/area it will use.

Figure 3.1: Gate Sizing Problem

Source: from author (2015)

Roughly speaking, the larger the component size, the faster it is at expense of more power consumption and area occupied. However by just sizing all components to the largest size one does not guarantee the fastest design as a larger component imposes a larger load to its driver, which then become slower. This dependency among component delays makes the gate sizing problem very challenging. A good gate sizing method must understand this delay dependency and trade-off the components speeds with the energy or area consumed by them.

# 3.1 Sizing Problem Classification

Sizing can be divided into two categories: (1) transistor sizing and (2) gate sizing. Each category can be solved into two different domains: (1) continuous and (2) discrete. These combinations are summarized in Table 3.1.

Usually the continuous sizing is associated to the transistor sizing problem and the discrete sizing is associated to the gate sizing problem, but this is not mandatory. Moreover the continuous modeling is more suitable for the full-custom design methodology whereas

Table 3.1: Sizing Classification

| Component  | Domain | Continuous | Discrete |

|------------|--------|------------|----------|

| Transistor |        |            |          |

| Gate       |        |            |          |

the discrete modeling is applied typically to the standard-cell methodology. Continuous modeling also find their role in several discrete algorithms where they are used directly or indirectly to guide the discrete optimization.

Continuous modeling almost always use convex models that can be solved optimally in polynomial time. On the other hand, the discrete modeling is proved to be NP-Hard (LI, 1993) so that no polynomial time algorithm can be devised, unless P=NP. This imposes several challenges to the development of efficient discrete sizing algorithms. In the continuous version, the issue is the correlation between the convex models and the actual behaviour of the components. In the discrete version the major concern is keeping the runtime under control.

# 3.2 Sizing Formulation

Gate sizing is usually formulated in one of three basic ways:

- minimize either area or power subject to performance constraint;

- maximize performance subject to area and/or power constraints;

- maximize performance.

These formulations can be extended to handle other constraints as maximum load, maximum transition time, etc and other objective function as well, but they describe the core idea of the sizing problem. The formulation aiming only performance with no constraints is used to verify the limits of the design performance and be used as a starting point for power and area optimization.

The circuit performance is usually measured by means of a Static Timing Analysis (STA) as explained in Chapter 2. The analysis may use different gate and wire models. Most common gate models for delay are the equivalent driver resistance, RC tree and look-up tables generated from accurate electrical simulation. Interconnections are most commonly modeled via lumped capacitance or RC tree. Tree delays are computed using Elmore delay or reduced-order models.

# 3.3 Gate Sizing for Leakage Power Minimization

In this work, the gate sizing for leakage power minimization under speed constraints is studied. A new flow for gate sizing and threshold voltage assignment is developed using as basic the Lagrangian Relaxation formulation for gate sizing.

Power consumption has been a major barrier for circuit performance. Although the overall power dissipated by a circuit decreases for a new technology, the power dissipated per unit area usually increases. This power-limited performance scenario combined with the rise of the mobile era and with the need for low-power devices, highlights the importance of power minimization techniques (BUTZEN; RIBAS, 2005).

The power consumed by components can be broken down into two components: dynamic power and static power. Dynamic power is the power consumed by the components when they are changing states. For instance, the output of a logic cell transitioning from zero to one is causing dynamic power consumption. On the other hand, the static power or leakage power is consumed constantly independent of state changes.

Leakage power has become a main concern in deep submicron process technology nodes (65nm and below), where it could account for 30-50% of the total design power consumption (SHIFREN, 2011). Leakage power is mainly caused by unwanted subthreshold currents in the transistor channel when the transistor is turned off. Figure 3.2 presents the sources of leakage power for a planar technology.

Figure 3.2: Sources of Leakage Current

gate leakage

subthreshold leakage

reverse-biased

Junction BTBT

Source: (BUTZEN; RIBAS, 2005)

Gate sizing is a standard and effective technique for power minimization and hence suitable for addressing the aforementioned problems. For a standard-cell based design flow, the gate sizing task is to select the right versions for the gates available in a library so that the power is minimized while keeping the circuit performance within the specification. However, the gate selection problem was shown to be NP-Hard (LI, 1993), so that no optimal, polynomial time algorithm can be designed unless P = NP. This combinatorial optimization problem becomes even more challenging as the designs get more and more complex and the number of sizable components keep growing. Therefore efficient and effective heuristics need to be developed.

#### 3.3.0.1 A Word on FinFet Technology

In recent years, the FinFET technology consolidated and is now in production mode. This technology brings more control over the leakage power and hence a significant reduction in the leakage power consumption by up to 50% is achieved so that dynamic power has become the main concern.

However, this does not mean the leakage power still has no impact on the total power consumption. Improvements on leakage power can still provide a good increase in battery life of mobile devices. Moreover, not all designs have being converted to FitFET as this decision involves other factors, but ultimately the cost factor is the most prominent.

Although the focus of this method is leakage power, it can be extended to handle dynamic power as well if switch activity is available. Therefore, although FinFET technology may shadow the improvements brought by this work, the techniques and the flow presented in this thesis still can provide power savings or be extended to handle dynamic power and other objectives associated with transistor sizes.

## 3.4 Challenges

The challenges of the gate sizing for high performance designs can be summarized as follows (OZDAL; BURNS; HU, 2011):

- 1. **Discrete cell sizes**: Standard-cell based-flow is the dominant methodology to design digital circuits implying that only a limited number of gate types are available. The limited number of gate types rather than easing the problem, makes it combinatorial in nature and hence hard to solve efficiently.

- Cell timing models: Standard-cell delay is typically non-linear and non-convex so

that direct and efficient application of mathematical optimization as linear and convex programming is only possible on simplified delay models. Over simplification

may lead to far from optimal results.

- 3. **Complex timing constraints**; In high-performance designs several timing constraints must be handled such as timing overrides, multi-cycle paths, transparent paths, multiple clock events, false paths, etc. If the method does not take into account such constraints, it may become too inaccurate.

- 4. **Interconnect timing models**: Interconnect delay is a major contributor to the overall design delay. Ignoring it or using simplified interconnect delay models such as lumped capacitance and Elmore delay may lead to incorrect timing information and to over designing as simplified model usually overestimates the actual interconnect delay.

- 5. **Many near-critical paths**: In high performance design many paths are near-critical decreasing the efficiency of sizing methods that rely only on the optimization of the critical path. In this case, when the critical path is fixed, other paths may start to violate timing. Therefore sizing engines should handle many paths at same time to avoid dead-locks.

- 6. **Large design sizes**: Designs or even blocks in designs can easily reach the million gates count so that the sizing engines must scale to handle such huge number of components. Methods that rely on frequent timing updates may not be suitable for such designs.

## 3.5 Related Work

In this chapter, some of the works on transistor and mainly gate sizing are reviewed and summarized. The early works on gate sizing focused on the continuous domain where individual transistors or gates can be set to any size within a lower and an upper limit. Along with simplified models, a convex mathematical formulation can be devised (SCHEFFER; LAVAGNO; MARTIN, 2006), which can then be solved in some extent efficiently in polynomial time (BOYD; VANDENBERGHE, 2004). The continuous formulation was a straightforward fit for the full-custom methodology, which was the main methodology for the early days of circuit design.

Later on, methods for discrete gate sizing started to be developed as the standard-cell methodology consolidated. In the discrete formulation, the gate sizing problem becomes an assignment problem where sizes or, more generally, implementations of the gates are picked up from a library. Differently from the continuous counterpart, the discrete formulation is proved to be a NP-hard problem (LI, 1993).

Many discrete methods are inspirited by the continuous formulation or use it directly to guide the optimization process. This is not surprising as the assumptions made in the continuous side can be seen as a relaxation of the discrete formulation.

Several different approaches for gate sizing have been used in the literature:

- simulated annealing;

- linear programming;

- network flow;

- convex optimization (including geometric programming);

- Lagrangian relaxation;

- sensitivity and

- slew budgeting.

Lagrangian relaxation, sensitivity and network flow based approaches seem to be the most suitable ones for current design sizes as they scaled well and can be used for the discrete gate sizing problem.

Simulated annealing was successfully applied in the ISPD 2012 Gate Sizing Contest, but it suffers from scalability issues and do not seem to be an acceptable method for current designs. Although the method won the contest, later works achieved much better results in much less time.

Convex optimization including geometric programming only works on simplified convex or posynomial models which may not capture the non-linear, non-convex nature of the gate delays. On the other hand, they guarantee the optimal solution (under the simplified model) and can be used in the early stages of the design flow or as guide for the discrete gate sizing.

#### 3.5.1 Early Work

One of the first works automating the gate sizing problem was developed by Ruehli et al.<sup>1</sup> from IBM (RUEHLI; WOLFF; GOERTZEL, 1977) aiming power minimization under timing constraint. In that initial work, gate delay is proportional to the inverse of the gate size and the power is directly proportional to the size. Lumped capacitance is used to model the wires. The authors report gains of 3 up to 10 times in power when compared to an unoptimized design that meets timing. The main drawback is that the timing model does not consider that a change in a gate size changes the load capacitance of its driver.

Almost a decade later, the transistor sizing method, TILOS, was published (FISH-BURN; DUNLOP, 1985). TILOS can operate in three modes (1) area minimization under

<sup>&</sup>lt;sup>1</sup>Out of curiosity. The last author of the paper, Gerald Goertzel, had worked in the Manhattan Project.

timing constraint, (2) timing minimization under area constraint and (3) area-delay product minimization. Gate delay is modeled using RC networks and the authors show that this model leads to a convex delay model for the entire circuit. Even though the authors cite that the convex model can be solved by general purpose solvers, they indeed developed a sensitivity-based heuristic to trade-off accuracy and runtime. The method works by sizing the transistor with the largest delay to size sensitivity on the most critical path. First, TILOS is used to generate a rough initial solution. Then, in the second phase, the sizing problem is converted to a mathematical optimization problem in a smaller parameter space where a method of feasible directions is applied to find the optimal solution. TILOS was chosen one of the best works of the 20 years of ICCAD conference (KUEHLMANN, 2003).

In 1987, Aesop (HEDLUND, 1987) tool for transistor sizing using linear model is presented. Berkelaar and Jess (BERKELAAR; JESS, 1990) present a method to power minimization under timing constraint using linear programming. The non-linear gate delay is broken into a piecewise linear function, which is suitable to formulate the problem as a linear program.

The first work to cope directly with discrete gate sizing was developed by Chan (CHAN, 1990) in 1990. Previous works only handled discrete gate sizing by rounding the sizes obtained from continuous formulation. Chan, on the other hand, proposed a traverse algorithm to propagate timing constraints, then backward substitution applying cell sizes available in a library. The proposed algorithm runs in pseudo-polynomial time for tree structures. For non-tree structures, multiple-fanout cells are implicitly cloned to create a tree like structure where the algorithm for trees can be used. The algorithm does not depend on a specific gate delay model. Also the cost for a gate size is generic and can be, for instance, the cell area or cell power. However, as the algorithm needs to propagate a list of possible gate sizes, it becomes impractical for large circuits.

In 1993, the tool ASAP (DUTTA; NAG; ROY, 1994) for transistor sizing using simulated annealing was presented using the Alpha-Power Law MOSFET Model (SAKNRAI; NEWTON, 1990). Also in 1993, different from previous approach, Sapatnekar et. al (SAPATNEKAR et al., 1993) took full advantage of the convex formulation by using convex programming to find an exact solution.

In 1996 (COUDERT, 1996) and 1997 (COUDERT, 1997), Oliver presented a greedy algorithm for discrete gate sizing aiming industrial designs. Different from previous works, Oliver used an accurate gate delay based on look-up tables. The greedy algorithm works by traversing the circuit, selecting new sizes for gates, but without resizing them. Every size change is stored as a move. After all gates have been processed, the moves that minimize power keeping the circuit performance are selected.

A sequential quadratic programming (SQP) approach to concurrent gate and wire sizing was presented by Menezes in 1997 (MENEZES; BALDICK; PILEGGI, 1997). In their work, the authors present an efficient way to compute the sensitivities to feed the SQP.

Chen, et at. (CHEN; CHU; WONG, 1999), published a key work on gate sizing in 1999. They presented a concise formulation for the gate sizing problem avoiding the exponential grow of path delay constraints. With this new formulation, the number of constraints grows linearly with the number of pins. Moreover, the authors shown how the Lagrangian Relaxation formulation could be significantly reduced using Karush-Kuhn-Tucker (KKT) conditions. Then a fast and optimal algorithm was designed to solve the gate and wire sizing simultaneously.

In 2002, Tennakoon et at. (TENNAKOON; SECHEN, 2002) proposed a fast gradient-based pre-processing step for Lagrangian relaxation that provides an effective set of initial Lagrange multipliers, which improved the runtime up to  $200\times$  compared to previous works.

#### 3.5.2 State-of-the-Art

The gate options are a combination of transistor widths and threshold voltages  $(V_{th})$  available in a gate library. Some recent works (LIU; HU, 2010; OZDAL; BURNS; HU, 2011; RAHMAN; TENNAKOON; SECHEN, 2011) apply Lagrangian Relaxation to solve the discrete gate sizing problem using KKT conditions (CHEN; CHU; WONG, 1999) to simplify the Lagrangian Relaxation Sub-problem (LRS). In our approach KKT conditions are also applied and combined with the proposed method.

A Lagrangian Relaxation based formulation for gate sizing and device parameter selection is presented in (OZDAL; BURNS; HU, 2011). The objective is to minimize leakage power on high-performance industrial designs. Lagrangian Relaxation and Dynamic Programming (DP) are used to find the optimized solution. In the LR formulation, timing constraints are introduced in the objective function. An accurate sign-off timer is used to compute the slack values after each LR iteration. The LRS is modeled as a graph and the discrete gate version characteristics are based on timing tables provided by the gate library. A DP algorithm based on critical tree extraction is proposed to solve the LRS optimization problem for discrete gates.

In (RAHMAN; SECHEN, 2012), a threshold voltage  $(V_{th})$  assignment algorithm that employs a cost function which is globally aware of the entire circuit is presented. The objective of the post-synthesis algorithm is to minimize leakage power while solving the delay constraints. Gates are swapped to a higher  $V_{th}$  to absorb the available slack in the design without sacrificing delay. The delay constraint is iteratively pushed out by  $\delta$  time units, each time enabling additional gates to have their threshold voltages increased. The leakage power is iteratively reduced to a minimum value and then starts to increase substantially. Gate upsizing is required to re-establish the original delay target.

In (REIMANN et al., 2013), (HU et al., 2012), (LI et al., 2012) and (LIVRAMENTO et al., 2013) the infrastructure based on the ISPD 2012 Gate Sizing Contest is used. (REIMANN et al., 2013) presents a flow composed by a set of heuristic algorithms to address the discrete gate sizing and Vt assignment problem. The proposed flow combines the Fanout-of-4 rule, the Logical Effort concept and uses Simulated Annealing (SA) as the main engine. The solution achieved the second and first positions in the two rankings of the ISPD Contest in 2012.

A sensitivity-guided meta-heuristic approach to gate sizing that integrates timing and power optimization is presented in (HU et al., 2012). The proposed heuristic has two stages: Global Timing Recovery and Power Reduction with Feasible Timing. Global Timing Recovery seeks violation-free solutions, and then Power Reduction with Feasible Timing iteratively reduces total leakage power of sizing solutions by local search. At each stage of the optimization flow, the space of sensitivity functions is parametrized and transversed to find the best configurations of sensitivity by independent multistarts. After each multistart, all obtained solutions are compared and the best/non-dominated solutions are retained. This is accomplished by adapting the go-with-the-winners (ALDOUS; VAZIRANI, 1994) meta-heuristic. The optimization is purely deterministic in that the multistart procedure begins with the small set of the best-seen solutions. Solutions after each stage are ensured to be feasible, which enables pruning of dominated solutions by

go-with-the-winners. The results are comparable to other works, but the method is slow compared to (LI et al., 2012).

A framework for gate-version selection in modern high-performance low-power designs with library-based timing model is presented in (LI et al., 2012). The framework can be divided into three stages. First, the best design performance with all possible gate-versions is achieved by a Minimum Clock Period Lagrangian Relaxation method, which extends the traditional LR approach to control the difficulties in the discrete scenario. Upon a timing-valid design, the timing-constrained power optimization problem is solved by min-cost network flow. Finally, a power pruning technique is used to take advantage of the residual slacks due to the conservative network flow construction. The technique produces good power results, but worse than (HU et al., 2012), however in a faster way with a linear empirical runtime.

(LIVRAMENTO et al., 2013) proposes a Lagrangian Relaxation formulation for leakage power minimization that incorporates into the objective function the maximum gate input slew and the maximum gate output capacitance constraints in addition to the usual timing constraints. A fast topological greedy heuristic to solve the Lagrangian Relaxation Subproblem and a complementary procedure to fix the few remaining slew and capacitance violations is proposed. Despite all the improvements achieved by recent research works, there is still significant room for improvements. This can be observed as the best results for some of the benchmarks are found by different algorithms. They also differ a lot in terms of runtime, and it is desirable to identify which operations are consuming computational effort without contributing to the solution.

## **3.5.3 Summary**

In Table 3.2 the main characteristics of continuous sizing methods are shown. In Table 3.3 the main characteristics of discrete sizing methods are shown.

| Work                                  | Year | Sizing Type     | Gate Model                         | Net Model          | Optimization Methods             |

|---------------------------------------|------|-----------------|------------------------------------|--------------------|----------------------------------|

| (RUEHLI; WOLFF; GOERTZEL, 1977)       | 1977 | Gate            | Inverse of Size                    | Lumped Capacitance | Newton                           |

| (FISHBURN; DUNLOP, 1985)              | 1985 | Transistor      | RC                                 | N/A                | Sensitivity                      |

| (BERKELAAR; JESS, 1990)               | 1990 | Gate            | Pice-Wise Linear                   | Linear             | Linear Programming               |

| (SAPATNEKAR et al., 1993)             | 1993 | Transistor      | RC (Elmore De-<br>lay)             | N/A                | Convex Programming               |

| (MENEZES; BALDICK; PILEGGI, 1997)     | 1997 | Gate            | Driver Resistance                  | RC Tree (Elmore)   | Sequential Quadratic Programming |

| (CHEN; CHU; WONG, 1999)               | 1999 | Gate            | Driver Resistance                  | RC Tree (Elmore)   | Lagrangian Relaxation            |

| (SRIVASTAVA; SYLVESTER; BLAAUW, 2004) | 2000 | Transistor      | Alpha-Power<br>Law MOSFET<br>Model | N/A                | Sensitivity Based                |

| (TENNAKOON; SECHEN, 2002)             | 2002 | Gate            | Driver Resistance                  | RC Tree (Elmore)   | Lagrangian Relaxation            |

| (BOYD et al., 2005)                   | 2002 | Gate Transistor | RC RCsistance                      | RC Tree (Elmore)   | Geometric Programming            |

| (POSSER et al., 2012)                 | 2012 | Transistor      | Driver Resistance                  | RC Tree (Elmore)   | Geometric Programming            |

| (ALEGRETTI et al., 2013)              | 2013 | Transistor      | Driver Resistance                  | RC Tree (Elmore)   | Geometric Programming            |

Table 3.2: Summary of Works on Continuous Gate Sizing

Table 3.3: Summary of Works on Discrete Gate Sizing

| Work                              | Year | Sizing Type | Gate Model                                    | Net Model          | Optimization Methods                      |

|-----------------------------------|------|-------------|-----------------------------------------------|--------------------|-------------------------------------------|

| (CHAN, 1990)                      | 1990 | Gate        | [Generic]                                     | N/A                | Greedy                                    |

| (COUDERT, 1996)                   | 1996 | Gate        | Lookup Table                                  | N/A                | Multiple Moves                            |

| (COUDERT, 1997)                   | 1997 | Gate        | Lookup Table                                  | N/A                | Multiple Moves                            |

| (NGUYEN et al., 2003)             | 2003 | Gate        | Lookup Table                                  | N/A                | Sensitivity Linear Programming            |

| (SHAH et al., 2005)               | 2005 | Gate        | Equivalent Driver<br>Resistance (El-<br>more) | N/A                | Geometric Programming                     |

| (CHOU; WANG; CHEN, 2005)          | 2005 | Transistor  | Posynominal Ap-<br>proximation                | N/A                | Lagrangian Relaxation                     |

| (CHINNERY; KEUTZER, 2005)         | 2005 | Gate        | Lookup Table                                  | Lumped Capacitance | Sensitivity Linear Programming            |

| (REN; DUTT, 2008)                 | 2008 | Gate        | Driver Resistance                             | Lumped Capacitance | Network Flow                              |

| (LIU; HU, 2010)                   | 2009 | Gate        | Lookup                                        | Elmore             | Greedy                                    |

| (HU; KETKAR; HU, 2009)            | 2009 | Gate        | Elmore Delay                                  | N/A                | Dynamic Programming                       |

| (OZDAL; BURNS; HU, 2011)          | 2011 | Gate        | [Generic]                                     | [Generic]          | Dynamic Programming Lagrangian Relaxation |

| (HUANG; HU; SHI, 2011)            | 2011 | Gate        | RC (Elmore De-<br>lay)                        | N/A                | Lagrangian Relaxation                     |

| (ZHOU et al., 2011)               | 2011 | Gate        | Linear Fit                                    | RC Tree (Elmore)   | Dynamic Programming                       |

| (RAHMAN; TENNAKOON; SECHEN, 2011) | 2011 | Gate        | Logical Effort                                | Lumped Capacitance | Lagrangian Relaxation<br>Branch-and-Bound |

| (OZDAL; BURNS; HU, 2012)          | 2011 | Gate        | [Generic]                                     | [Generic]          | Dynamic Programming Lagrangian Relaxation |

| (RAHMAN; SECHEN, 2012)            | 2012 | Gate        | Lookup                                        | RC Tree            | Greedy                                    |

| (HU et al., 2012)                 | 2012 | Gate        | Lookup                                        | Lumped Capacitance | Sensitivity                               |

| (LIVRAMENTO et al., 2013)         | 2013 | Gate        | Lookup                                        | Lumped Capacitance | Lagrangian Relaxation                     |

| (REIMANN et al., 2013)            | 2013 | Gate        | Lookup                                        | Lumped Capacitance | Simulated Annealing                       |

## 4 GATE SIZING VIA LAGRANGIAN RELAXATION

## 4.1 Lagrangian Relaxation

Lagrangian Relaxation is a useful mathematical technique to find or to approximate the optimum solution of optimization (minimization or maximization) problems with hard constraints. It has been successfully applied to solve several problems in EDA such as floor-planning, placement, routing and gate sizing among others.

The main idea behind Lagrangian Relaxation is to rewrite the optimization problem in an easier version, removing the hard constraints and adjusting the objective function to take into account the constraint violations.

Given the optimization problem, also called the *primal problem*, in Equation (4.1),

minimize

$$f(x)$$

subject to  $g_i(x) \le 0$  i = 1, 2, ..., n

$h_j(x) = 0$  j = 1, 2, ..., m

$$(4.1)$$

a simpler or *relaxed problem* is written moving the hard constraints to the objective as shown in Equation (4.2)

minimize

$$\mathcal{L}(x, \lambda, \mu)$$

subject to  $\lambda_i \in \Re_+ i = 1, 2, ..., n$

$\mu_i \in \Re_- i = 1, 2, ..., m$  (4.2)

where

$$\mathcal{L}(x,\lambda,\mu) = f(x) + \sum \lambda_i g_i(x) + \sum \mu_j h_j(x)$$

(4.3)

•

The relaxed constraints are multiplied by the so called Lagrange multipliers,  $\lambda_i$  and  $\mu_j$ , which can be seen as a weight indicating how much that specific constraints is being violated. Not all constraints need to be moved to the objective and the choice of which constraints should be relaxed is problem dependent. However the relaxed version should be easier to solve than the original problem.

The key property of the relaxed problem is that its solution is always a lower bound to the solution of the original problem for any set  $\{\lambda_i, \mu_j\}$ . That is,

$$\mathcal{L}(\tilde{x}, \lambda, \mu) \le f(\hat{x}) \tag{4.4}$$

where  $\tilde{x}$  is the optimal solution for the relaxed problem and  $\hat{x}$  is the optimal solution of the original problem.

Considering this propriety, the main idea of Lagrangian relaxation is to find the maximum lower bound, which may ultimately approach the optimal solution of the original problem. This leads to another optimization problem, called the *dual problem*, which aims to find the largest lower bound as defined by Equation (4.5).

maximize min

$$f(x) + \sum \lambda_i g_i(x) + \sum \mu_j h_j(x)$$

subject to  $\lambda_i \geq 0 \text{ i = 1, 2, ..., n}$   $(4.5)$

$\mu_j \in \Re \text{ j = 1, 2, ..., m}$