# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

#### ALEXANDRA LACKMANN ZIMPECK

## Timing Vulnerability Factor Analysis in Master-Slave D Flip-Flops

Thesis presented in partial fulfillment of the requirements for the degree of Master of Computer Science

Advisor: Prof. Dr. Ricardo Augusto da Luz Reis

Co-advisor: Prof. Dr. Fernanda Lima Kastensmidt

Porto Alegre 5<sup>th</sup> February 2016

#### CIP - CATALOGAÇÃO NA PUBLICAÇÃO

#### L. Zimpeck, Alexandra

Timing Vulnerability Factor Analysis in Master-Slave D Flip-Flops / Alexandra L. Zimpeck - 2016.

104 f.: il.

Advisor: Ricardo Augusto da Luz Reis Co-advisor: Fernanda Lima Kastensmidt

Dissertation (master) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação. Porto Alegre, BR – RS, 2016.

1.Microelectronics 2. Soft Errors 3. Window of Vulnerability 4. Timing Vulnerability Factor 5. Environmental Variability

#### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos Alexandre Netto

Vice-Reitor: Prof. Rui Vicente Oppermann

Pró-Reitor de Pós-Graduação: Prof. Vladimir Pinheiro do Nascimento

Diretor do Instituto de Informática: Prof. Luís da Cunha Lamb

Coordenador do PPGC: Prof. Luigi Carro

Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

#### **AGRADECIMENTOS**

Em primeiro lugar gostaria de agradecer aos meus PAIS, Alexandre e Dulcinara, pelo amor incondicional e incentivo aos estudos recebido desde as primeiras etapas da minha vida. A eles que sempre me motivaram a ir atrás dos meus sonhos, minha eterna gratidão. Eu não chegaria até aqui sem o apoio deles.

Ao meu IRMÃO Lucas, tão pequeno, mas de sabedoria enorme, o maior e melhor presente que meus pais podiam ter me dado. Aquele que muitas vezes não entendeu a minha ausência, mas que sempre que precisei, esteve ao meu lado. A toda a minha FAMÍLIA e aos meus AMIGOS que sempre torceram por mim e que compreenderam os vários momentos importantes em que eu não pude estar presente. Ao AMOR André Furlan, pelo companheirismo, paciência e apoio durante a reta final deste trabalho.

Aos meus COLEGAS de laboratório e de disciplinas da UFRGS, Gracieli, Felipe, Geancarlo, Calebe, Walter, Jucemar, Mateus, Tiago, Tania, Guilherme, Vitor, Adriel, Jorge, Louise, Vladimir, Lucas, Vinícius, Jody, Augusto e Cícero, muito obrigada por toda a ajuda que me deram na realização deste trabalho e pela amizade ao longo deste tempo. Especialmente, agradeço a Cristina Meinhardt por todo incentivo a pesquisa científica desde a graduação até os dias de hoje, e também por me aconselhar em todas as dúvidas que tive durante todos esses anos.

Ao meu ORIENTADOR, professor Ricardo Reis, por sempre acreditar no meu potencial, por me incentivar a continuar na pós-graduação e por me auxiliar em todas as etapas durante o mestrado. Agradeço também a minha COORIENTADORA, professora Fernanda Kastensmidt, por todas as discussões e apoio que foi dado para a realização deste trabalho. E por fim, agradeço a todos os PROFESSORES que passaram pela minha vida, desde as séries iniciais até os dias de hoje e que contribuíram com os seus conhecimentos para minha formação.

#### **ABSTRACT**

Technology scaling has brought undesirable issues to maintain the exponential growth rate and it raises important topics related to reliability and robustness of electronic systems. Currently, modern super pipelined microprocessors typically contain many millions of devices with ever decreasing load capacitances. This factor makes circuits more sensitive to environmental variations and it is increased the probability to induce a soft error. Soft errors in sequential circuits occur when a single energetic particle deposits enough charge near a sensitive node. Master-slave flip-flops are the most adopted sequential elements to work as registers in pipeline and finite state machines. If a bit-flip happens inside them, they lose the previous stored information and may cause an incorrect system operation. To provide reliable systems that can cope with radiation effects, this work analysis the Timing Vulnerability Factor (TVF) of some master-slave D flip-flops topologies in pipeline stages under different operating conditions. The effective time window, which the bit-flip can still be captured by the next stage, is defined as Window of Vulnerability (WOV). TVF corresponds to the time that a flip-flop is vulnerable to radiation-induced soft errors according to WOV and clock frequency. In the first step of this work, it is determined the dependence between the TVF with the fault propagation to the next stage through a combinational logic with different propagation delays and with different nanometer technological models, including also high performance and low power versions. All these simulations were made under the pre-defined nominal conditions in technology files. The variability manifests with an increase or decreases to initial specification, where the main problem is the uncertainty about the value stored in sequential. In this way, the second step of this work evaluates the impact that environmental variability effect causes in TVF. Some simulations were redone considering supply voltage and temperature variations in different master-slave D flip-flop topologies configurations. To achieve better results, it is necessary to try to decrease the TVF values to reduce the vulnerability to bit-flips. The propagation delay between two sequential elements and higher clock frequencies collaborates to reduce TVF values. Moreover, all the information can be easily integrated into Electronic Design Automation (EDA) tools to help identifying the most vulnerable master-slave flip-flops before mitigating or replacing them by radiation hardened ones

**Keywords:** Microelectronics, Soft Errors, Window of Vulnerability, Timing Vulnerability Factor, Environmental variability.

## Análise do Fator de Vulnerabilidade Temporal em Flip-Flops Mestre-Escravo do tipo D

#### **RESUMO**

O dimensionamento da tecnologia trouxe consequências indesejáveis para manter a taxa de crescimento exponencial e levanta questões importantes relacionadas com a confiabilidade e robustez dos sistemas eletrônicos. Atualmente, microprocessadores modernos de superpipeline normalmente contêm milhões de dispositivos com cargas nos nós cada vez menores. Esse fator faz com que os circuitos sejam mais sensíveis a variabilidade ambiental e aumenta a probabilidade de um erro transiente acontecer. Erros transientes em circuitos sequenciais ocorrem quando uma única partícula energizada deposita carga suficiente perto de uma região sensível. Flip-Flops mestreescravo são os circuitos sequencias mais utilizados em projeto VLSI para armazenamento de dados. Se um bit-flip ocorrer dentro deles, eles perdem a informação prévia armazenada e podem causar um funcionamento incorreto do sistema. A fim de proporcionar sistemas mais confiáveis que possam lidar com os efeitos da radiação, este trabalho analisa o Fator de Vulnerabilidade Temporal (Timing Vulnerability Factor -TVF) em algumas topologias de flip-flops mestre-escravo em estágios de pipeline sob diferentes condições de operação. A janela de tempo efetivo que o bit-flip ainda pode ser capturado pelo próximo estágio é definido com janela de vulnerabilidade (WOV). O TVF corresponde ao tempo que o flip-flop é vulnerável a erros transientes induzidos pela radiação de acordo com a WOV e a frequência de operação. A primeira etapa deste trabalho determina a dependência entre o TVF com a propagação de falhas até o próximo estágio através de uma lógica combinacional com diferentes atrasos de propagação e com diferentes modelos de tecnologia, incluindo também as versões de alto desempenho e baixo consumo. Todas as simulações foram feitas sob as condições normais pré-definidas nos arquivos de tecnologia. Como a variabilidade se manifesta com o aumento ou diminuição das especificações iniciais, onde o principal problema é a incerteza sobre o valor armazenado em circuitos sequenciais, a segunda etapa deste trabalho consiste em avaliar o impacto que os efeitos da variabilidade ambiental causam no TVF. Algumas simulações foram refeitas considerando variações na tensão de alimentação e na temperatura em diferentes topologias e configurações de flip-flops mestre-escravo. Para encontrar os melhores resultados, é necessário tentar diminuir os valores de TVF, pois isso significa que eles serão menos vulneráveis a bit-flips. Atrasos de propagação entre dois circuitos sequenciais e frequências de operação mais altas ajudam a reduzir o TVF. Além disso, estas informações podem ser facilmente integradas em ferramentas de EDA para ajudar a identificar os flip-flops mestre-escravo mais vulneráveis antes de mitigar ou substituí-los por aqueles tolerantes a radiação.

**Palavras-chave:** Microeletrônica, Soft Errors, Janela de Vulnerabilidade, Fator de Vulnerabilidade Temporal, Variabilidade Ambiental.

#### LIST OF ABBREVIATIONS AND ACRONYMS

AVF Architecture Vulnerability Factor

CMP Chemical-Mechanical Planarization

CMOS Complementary Metal-Oxide Semiconductor

IC Integrated Circuits

EDA Electronic Design Automation

FA Full-Adder FF Flip-Flop

FinFET Fin-Shaped Field-Effect Transistor

GND Ground

HA Half-Adder

HP High-Performance

ITRS International Technology Roadmap for Semiconductors

LE Logical Effort

LET Linear Energy Transfer

LP Low Power

LSTP Low Standby Power

MOSFET Metal-Oxide Semiconductor Field-Effect Transistor

MS Master-Slave

MTS Minimum Transistor Sizing

NBTI Negative Bias Temperature Instability

NFET N Field-Effect Transistor

NMOS N-channel Metal-Oxide Semiconductor

OTS Optimized Transistor Sizing

PDP Power-Delay-Product

PFET P Field-Effect Transistor

PMOS P-channel Metal-Oxide Semiconductor

PTM Predictive Transistor Model

PVT Process, Voltage and Temperature

RDF Random Dopant Fluctuation

SCE Short-Channel Effects

SE Soft Errors

SEB Single Event Burnout

SEE Single Event Effects

SEFI Single Event Functional Interrupt

SEL Single Event Latchup

SER Soft Error Rate

SEU Single Event Upset

SET Single Event Transient

SMSFF Standard Master-Slave D Flip-Flop

SPICE Simulation Program with Integrated Circuits Emphasis

SR Set-Reset

STA Static Timing Analysis

TGMSFF Transmission-Gate Master-Slave D Flip-Flop

TVF Timing Vulnerability Factor

VDD Supply Voltage

VLSI Very Large Scale Integration

WFF Workfunction Fluctuation WOV Window of Vulnerability

WPMSFF Write-Port Master-Slave D Flip-Flop

# LIST OF FIGURES

| Figure 1.1: Complete sequence of events from ionization until a failure                                   | 15   |

|-----------------------------------------------------------------------------------------------------------|------|

| Figure 1.2: Evolution of variability perspective in bulk CMOS nanotechnologies                            |      |

| Figure 1.3: Clock frequency trends in the last decades                                                    |      |

| Figure 2.1: Silicon substrate ionization due to impact of energetic particles and the pulses generated by | 7    |

| this effect                                                                                               |      |

| Figure 2.2: Charge collection mechanism when soft errors occur at PN-junction                             | 25   |

| Figure 2.3: Classification of Single Event Effects in ICs                                                 | 25   |

| Figure 2.4: Upsets possibilities: combinational or sequential logic circuits                              | 26   |

| Figure 2.5: (a) Single Event Transient and (b) Single Event Upset on a circuit                            | 27   |

| Figure 2.6: Logical masking in a combinational circuit                                                    | 27   |

| Figure 2.7: Electrical masking in a combinational circuit                                                 |      |

| Figure 2.8: Latch-window masking in a combinational circuit                                               | 28   |

| Figure 2.9: Typical current waveform of one single event                                                  | 29   |

| Figure 3.1: Symbol and timing diagram for positive (a) latch and (b) flip-flop                            | 30   |

| Figure 3.2: Structure and timing diagram of master-slave D flip-flop                                      | 31   |

| Figure 3.3: Propagation and transition delays for combinational logic circuits                            | 32   |

| Figure 3.4: Propagation delay, hold and setup times for sequential logic circuits                         | 33   |

| Figure 3.5: Factors that can cause harm to a clock signal                                                 |      |

| Figure 3.6: Pipeline design of typical circuits                                                           | 34   |

| Figure 3.7: Timing diagram analysis for setup time slack                                                  |      |

| Figure 3.8: SET versus SEU error rate (DODD et. al, 2004)                                                 | 35   |

| Figure 3.9: Window of Vulnerability according to                                                          |      |

| Figure 3.10: Window of Vulnerability for master and slave latches working on a rising edge MS flip-fl     | op   |

|                                                                                                           |      |

| Figure 3.11: Effect of the WOV for different propagation delays (Tprop) at same clock period              |      |

| Figure 3.12: Effect of the TVF when clock frequency increases for the same propagation delay              | . 40 |

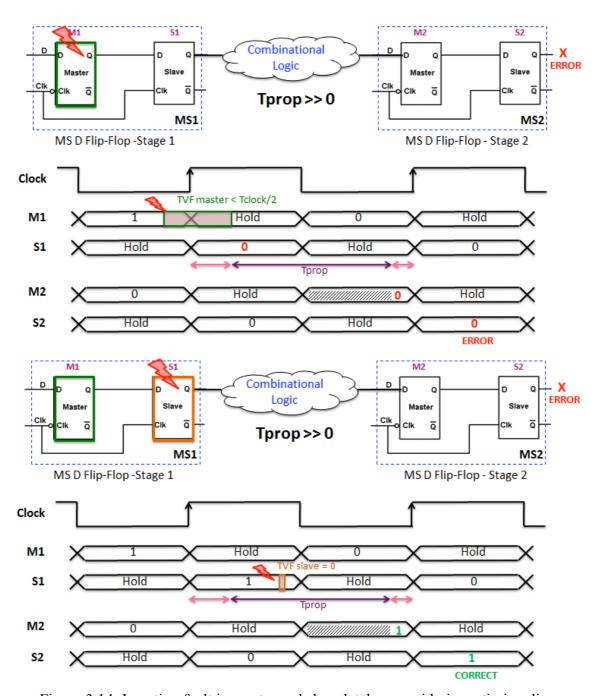

| Figure 3.13: Insertion fault in (a) master and (b) slave latches considering a timing diagram without     |      |

| propagation delay between MS D Flip-Flops                                                                 | . 41 |

| Figure 3.14: Insertion fault in master and slave latches considering a timing diagram with a large        |      |

| propagation delay between MS D Flip-Flops                                                                 |      |

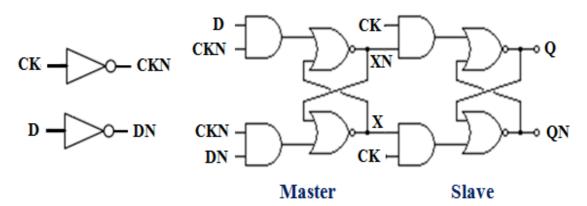

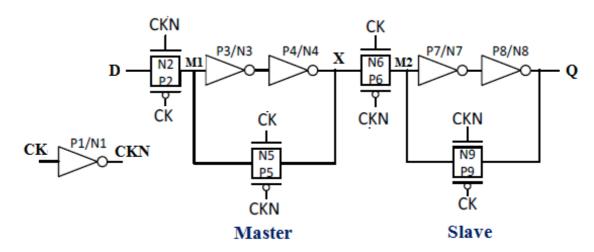

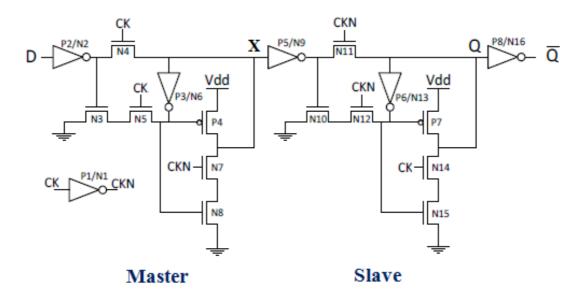

| Figure 4.1: Standard Master-Slave D Flip-Flop (SMSFF)                                                     |      |

| Figure 4.2: Transmission Gate Master-Slave D Flip-Flop (TGMSFF)                                           |      |

| Figure 4.3: Write-Port Master-Slave Flip-Flop (WPMSFF)                                                    |      |

| Figure 4.4: Pipeline design with inverters between flip-flops                                             |      |

| Figure 4.5: Double exponential current source in SPICE                                                    |      |

| Figure 4.6: SET propagation until to reach a sequential circuit output                                    |      |

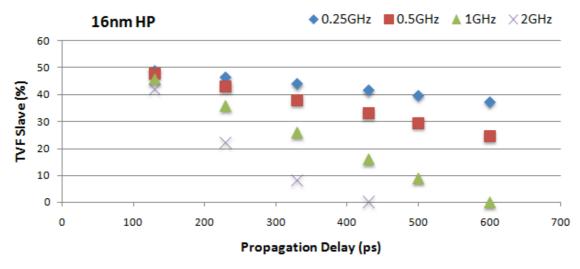

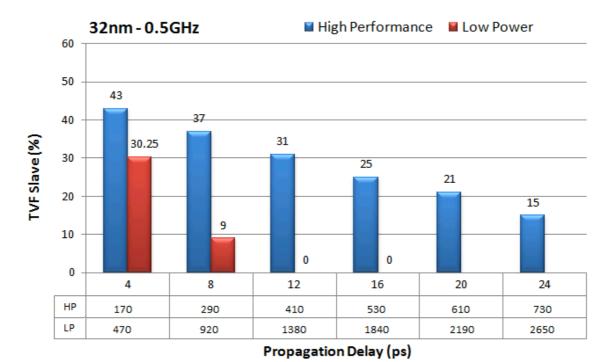

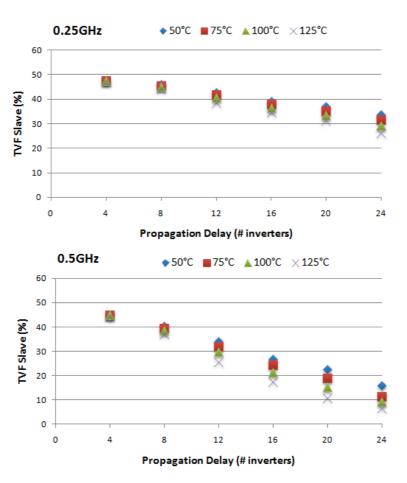

| Figure 5.1: Impact on TVF with frequency and propagation delay variations                                 |      |

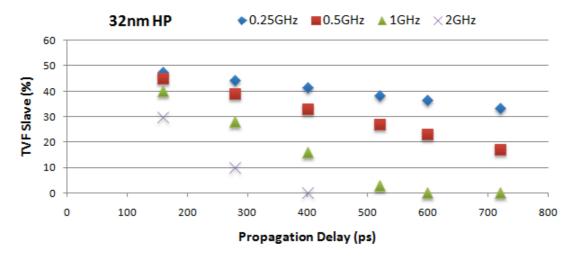

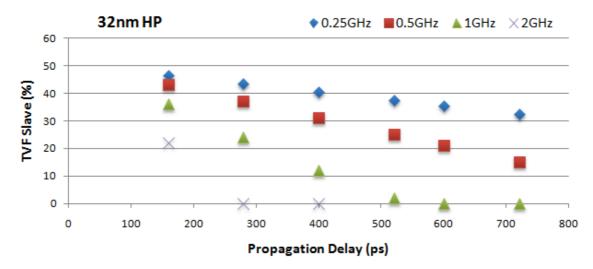

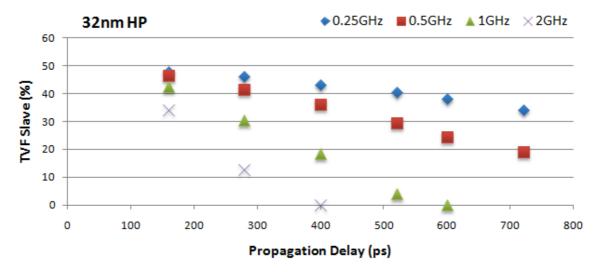

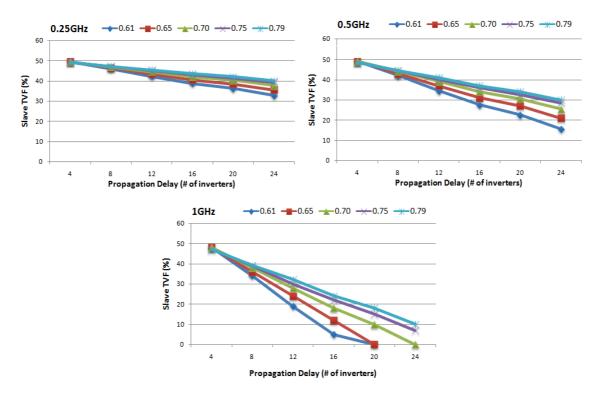

| Figure 5.2: TVF for the slave latch of SMSFF for 32nm/HP                                                  |      |

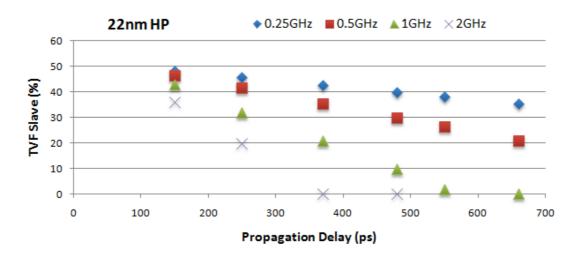

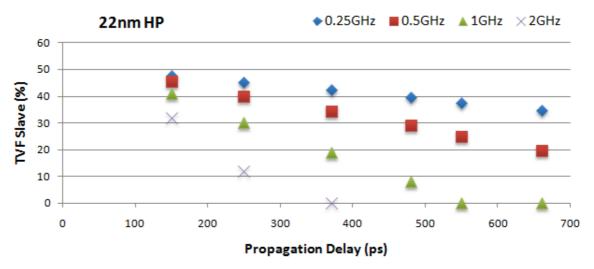

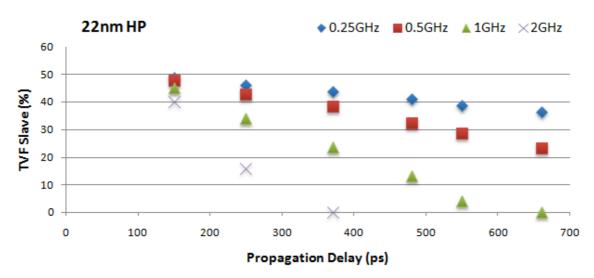

| Figure 5.3: TVF for the slave latch of SMFF for 22nm/HP                                                   |      |

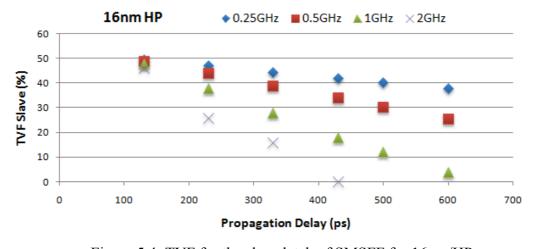

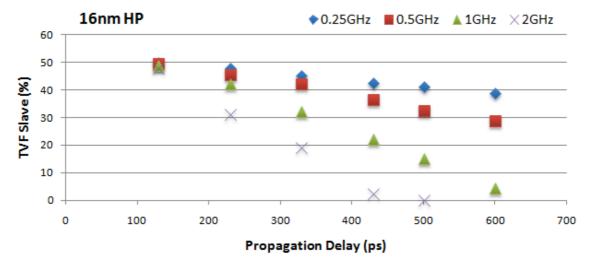

| Figure 5.4: TVF for the slave latch of SMFF for 16nm/HP                                                   |      |

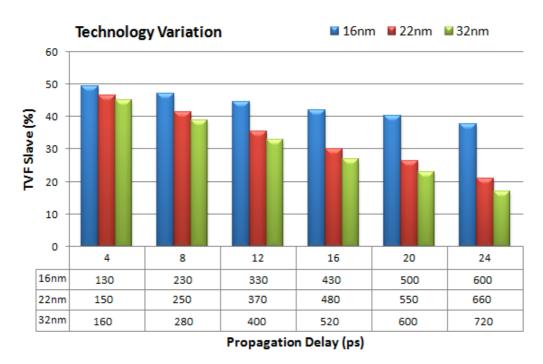

| Figure 5.5: TVF of slave latch as function of the different technology nodes at 0.5GHz                    | 52   |

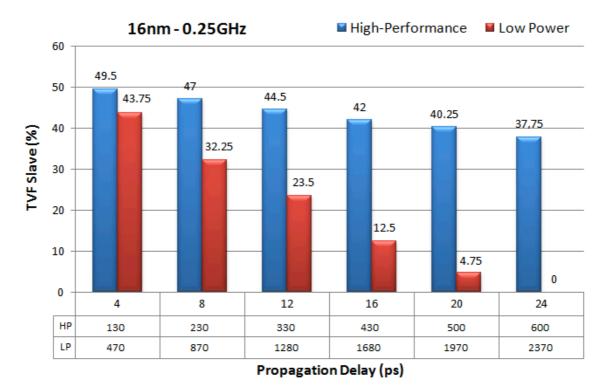

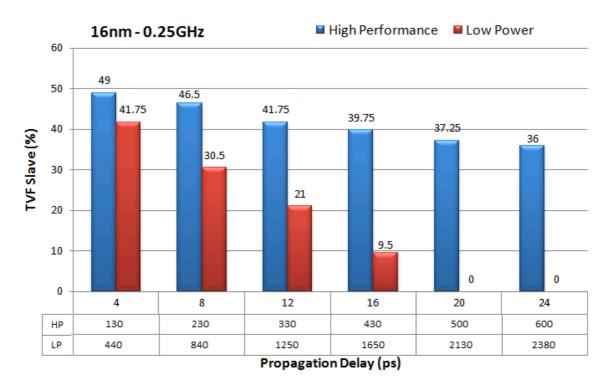

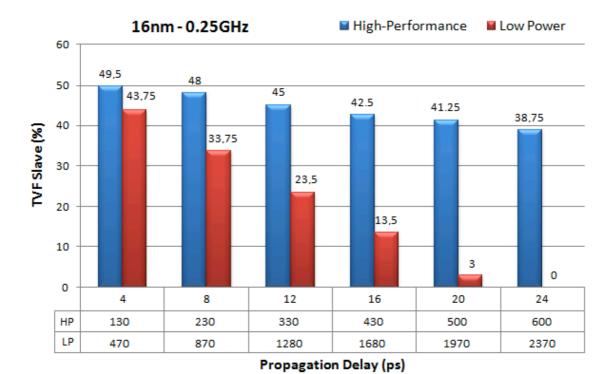

| Figure 5.6: TVF for slave latch of SMSFF at 0.25GHz for 16nm High-Performance and Low Power               |      |

| versions                                                                                                  | . 54 |

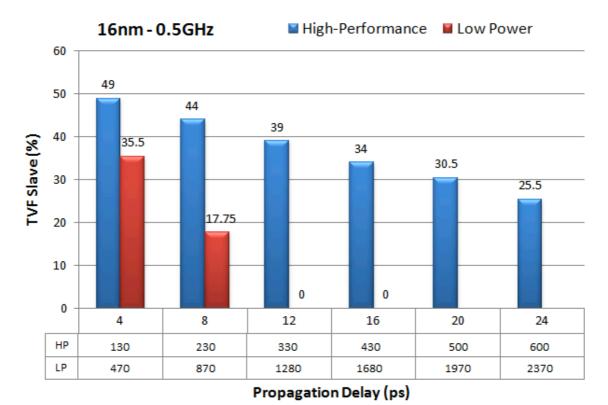

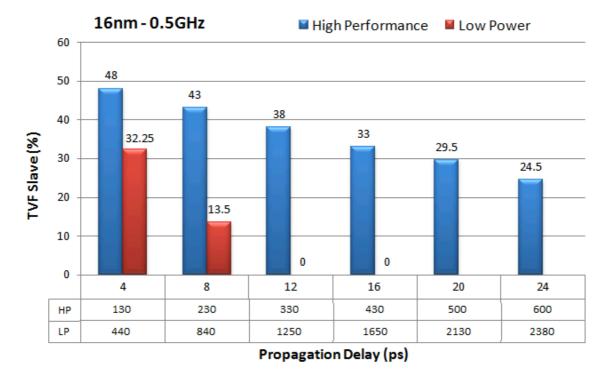

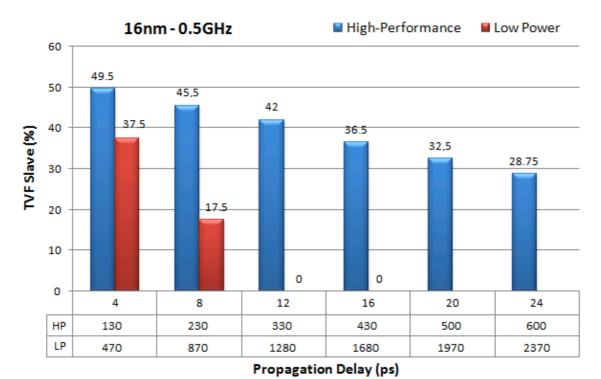

| Figure 5.7: TVF for slave latch of SMSFF at 0.5GHz for 16nm High-Performance and Low Power                |      |

| versions                                                                                                  | . 54 |

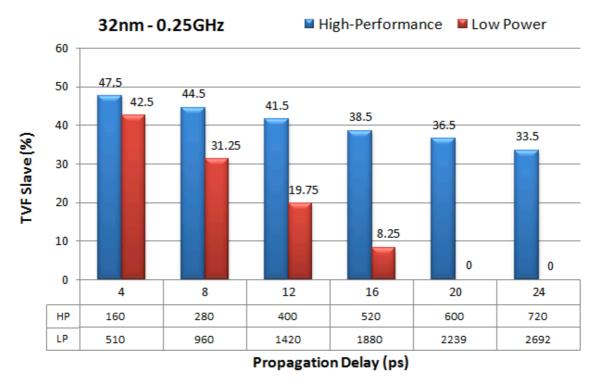

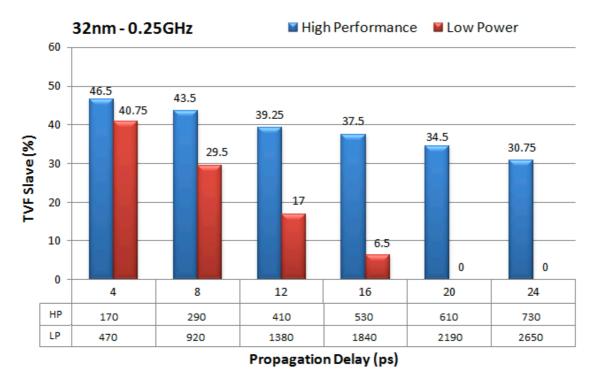

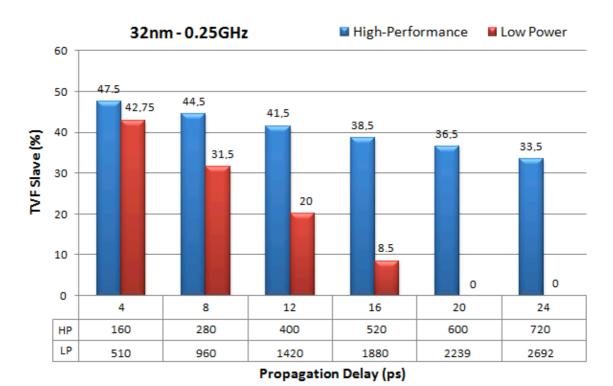

| Figure 5.8: TVF for slave latch of SMSFF at 0.25GHz for 32nm High-Performance and Low Power           |

|-------------------------------------------------------------------------------------------------------|

| versions                                                                                              |

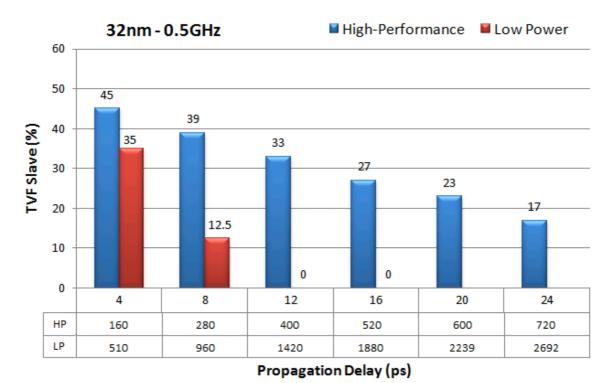

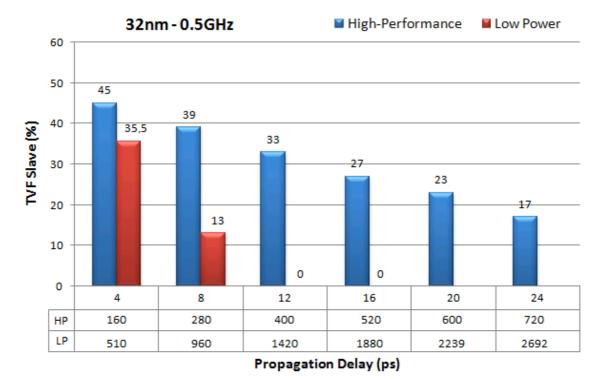

| Figure 5.9: TVF for slave latch of SMSFF at 0.5GHz for 32nm High-Performance and Low Power            |

| versions                                                                                              |

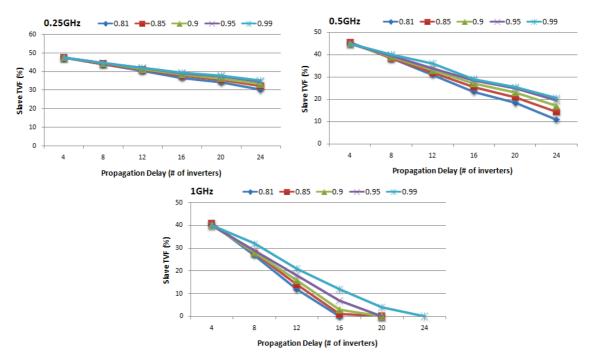

| Figure 5.10: TVF for the slave latch of TGMSFF for 32nm/HP                                            |

| Figure 5.11: TVF for the slave latch of TGMSFF for 22nm/HP                                            |

| Figure 5.12: TVF for the slave latch of TGMSFF for 16nm/HP                                            |

| Figure 5.13: TVF for slave latch of TGMSFF at 0.25GHz for 16nm High-Performance and Low Power         |

| versions                                                                                              |

| Figure 5.14: TVF for slave latch of TGMSFF at 0.5GHz for 16nm High-Performance and Low Power          |

| versions                                                                                              |

| Figure 5.15: TVF for slave latch of TGMSFF at 0.25GHz for 32nm High-Performance and Low Power         |

| versions                                                                                              |

| Figure 5.16: TVF for slave latch of TGMSFF at 0.5GHz for 32nm High-Performance and Low Power          |

| versions                                                                                              |

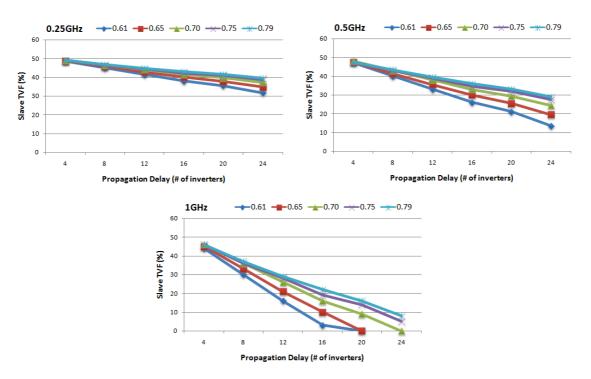

| Figure 5.17: TVF for the slave latch of WPMSFF for 32nm/HP                                            |

| Figure 5.18: TVF for the slave latch of WPMSFF for 22nm/HP                                            |

| Figure 5.19: TVF for the slave latch of WPMSFF for 16nm/HP                                            |

| Figure 5.20: TVF for slave latch of WPMSFF at 0.25GHz for 16nm High-Performance and Low Power         |

| versions64                                                                                            |

| Figure 5.21: TVF for slave latch of WPMSFF at 0.5GHz for 16nm High-Performance and Low Power          |

| versions64                                                                                            |

| Figure 5.22: TVF for slave latch of WPMSFF at 0.25GHz for 32nm High-Performance and Low Power         |

| versions                                                                                              |

| Figure 5.23: TVF for slave latch of WPMSFF at 0.5GHz for 32nm High-Performance and Low Power          |

| versions                                                                                              |

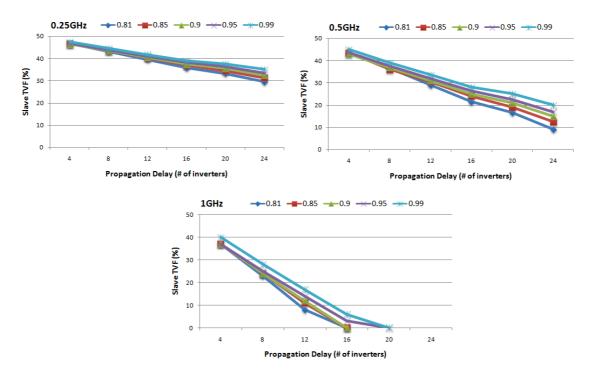

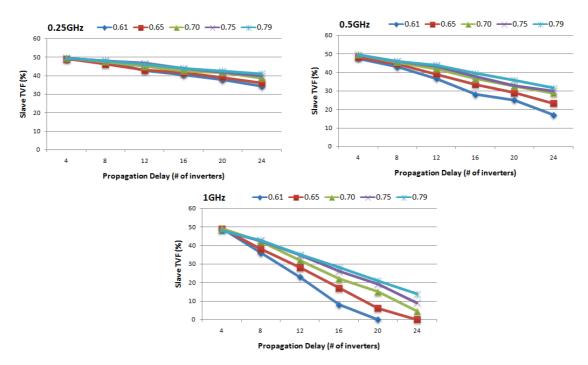

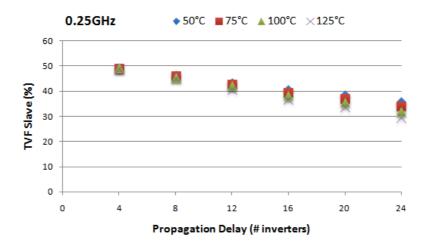

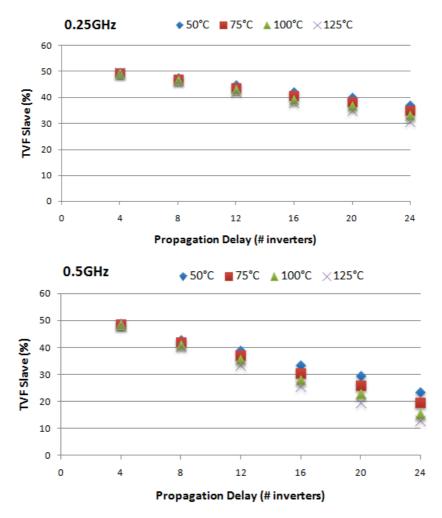

| Figure 6.1: TVF of slave latch for SMSFF at 16nm technology node in different clock frequencies under |

| voltage variations                                                                                    |

| Figure 6.2: TVF of slave latch for SMSFF at 32nm technology node in different clock frequencies under |

| voltage variations                                                                                    |

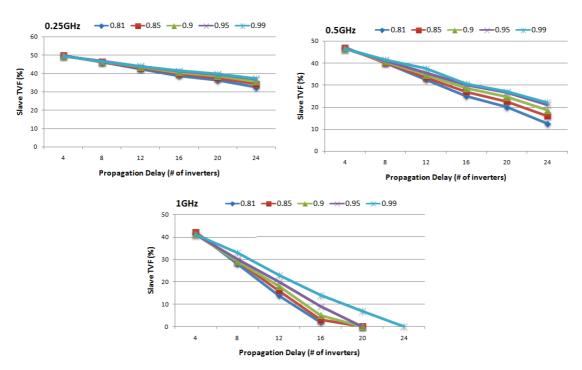

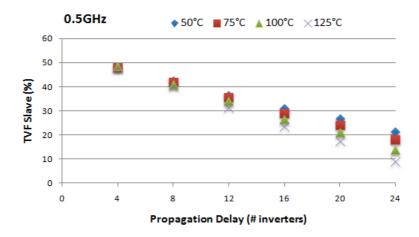

| Figure 6.3: TVF of slave latch for TGMSFF at 16nm technology node in different clock frequencies      |

| under voltage variations                                                                              |

| Figure 6.4: TVF of slave latch for TGMSFF at 32nm technology node in different clock frequencies      |

| under voltage variations                                                                              |

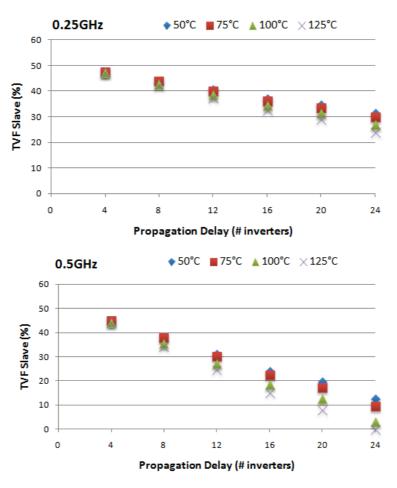

| Figure 6.5: TVF of slave latch for WPMSFF at 16nm technology node in different clock frequencies      |

| under voltage variations                                                                              |

| Figure 6.6: TVF of slave latch for WPMSFF at 32nm technology node in different clock frequencies      |

| under voltage variations                                                                              |

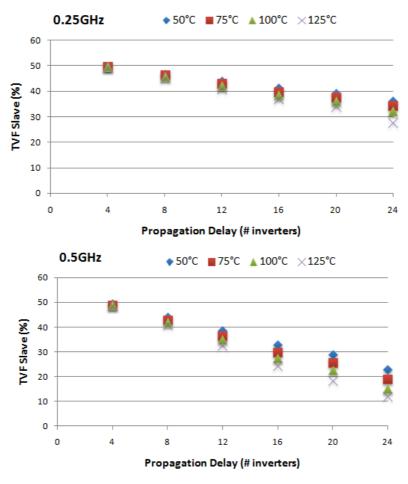

| Figure 6.7: TVF of slave latch for SMSFF at 16nm technology node in higher clock frequencies under    |

| temperature variations 73                                                                             |

| Figure 6.8: TVF of slave latch for SMSFF at 32nm technology node in higher clock frequencies under    |

| temperature variations 74                                                                             |

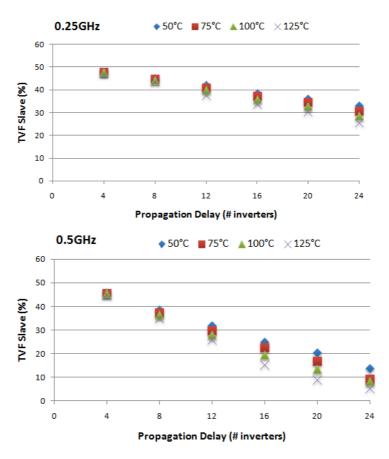

| Figure 6.9: TVF of slave latch for TGMSFF at 16nm technology node in higher clock frequencies under   |

| temperature variations 76                                                                             |

| Figure 6.10: TVF of slave latch for TGMSFF at 32nm technology node in higher clock frequencies under  |

| temperature variations 77                                                                             |

| Figure 6.11: TVF of slave latch for WPMSFF at 16nm technology node in higher clock frequencies under  |

| temperature variations 78                                                                             |

| Figure 6.12: TVF of slave latch for WPMSFF at 32nm technology node in higher clock frequencies under  |

| temperature variations                                                                                |

## LIST OF TABLES

| Table 2.1: Main evidences of soft errors in commercial systems                               | 21 |

|----------------------------------------------------------------------------------------------|----|

| Table 4.1: Nominal Parameters from PTM technologies                                          | 45 |

| Table 4.2: Variations of ±10% of the nominal power supply                                    | 48 |

| Table 5.1: TVF for the master latch of SMSFF for 32nm/22nm/16nm/HP technologies              | 53 |

| Table 5.2: TVF for the master latch of TGMSFF for 32nm/22nm/16nm/HP technologies             | 58 |

| Table 5.3:TVF for the master latch of WPMSFF for 32nm/22nm/16nm/HP technologies              | 63 |

| Table 6.1: Propagation delay approximations for different supply voltages at 16nm technology |    |

| Table 6.2: Propagation delay approximations for different supply voltages at 32nm technology | 67 |

| Table 6.3: Propagation delay approximations for different temperatures at 16nm technology    |    |

| Table 6.4: Propagation delay approximations for different temperatures at 32nm technology    |    |

| Table 6.5: TVF for the master and slave latches of SMSFF at 1GHz in 16nm technology          |    |

| Table 6.6: TVF for the master and slave latches of SMSFF at 1GHz in 32nm technology          |    |

| Table 6.7: TVF for the master and slave latches of TGMSFF at 1GHz in 16nm technology         |    |

| Table 6.8: TVF for the master and slave latches of TGMSFF at 1GHz in 32nm technology         |    |

| Table 6.9: TVF for the master and slave latches of WPMSFF at 1GHz in 16nm technology         |    |

| Table 6.10: TVF for the master and slave latches of WPMSFF at 1GHz in 32nm technology        |    |

| Table 7.1: List of publications related to radiation effects on integrated circuits          |    |

| Table 7.2: List of publications related to variability in FinFET devices                     | 84 |

# **CONTENTS**

| LIS                                                     | ST OF ABBREVIATIONS AND ACRONYMS                                                                            | 7              |

|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------|

| LIS                                                     | ST OF FIGURES                                                                                               | 9              |

| LIS                                                     | ST OF TABLES                                                                                                | 11             |

| ΑB                                                      | SSTRACT                                                                                                     | 5              |

| RE                                                      | SUMO                                                                                                        | 6              |

| 1                                                       | INTRODUCTION                                                                                                | 14             |

| 1.1                                                     | Related Researches                                                                                          | 18             |

| 1.2                                                     | Motivation and Contributions                                                                                | 19             |

| 1.3                                                     | Work Organization                                                                                           | 20             |

| 2                                                       | RADIATION EFFECTS IN INTEGRATED CIRCUITS                                                                    | 21             |

| 2.1                                                     | Main Sources of Radiation-Induced Faults                                                                    | 22             |

|                                                         |                                                                                                             |                |

| 2.2                                                     | Charge Collection Mechanism                                                                                 |                |

| 2.2                                                     | Charge Collection Mechanism                                                                                 | 23             |

|                                                         |                                                                                                             | 23             |

| 2.3                                                     | Single Event Effects                                                                                        | 23<br>25<br>28 |

| 2.3<br>2.4                                              | Single Event Effects  Transient Pulse Modeling                                                              | 23<br>25<br>28 |

| <ul><li>2.3</li><li>2.4</li><li>3</li></ul>             | Single Event Effects  Transient Pulse Modeling  SEQUENTIAL LOGIC CIRCUITS                                   | 23252830       |

| <ul><li>2.3</li><li>2.4</li><li>3</li><li>3.1</li></ul> | Single Event Effects  Transient Pulse Modeling  SEQUENTIAL LOGIC CIRCUITS  Timing analysis and clock issues | 23252830       |

| 4   | METHODOLOGY                                                                                            | 43         |  |  |  |  |

|-----|--------------------------------------------------------------------------------------------------------|------------|--|--|--|--|

| 4.1 | Transient Fault Simulation                                                                             | 46         |  |  |  |  |

| 4.2 | Environmental Variability Simulation48                                                                 |            |  |  |  |  |

| 5   | EXPERIMENTAL RESULTS AT NOMINAL CONDITIONS                                                             | 49         |  |  |  |  |

| 5.1 | Standard Master-Slave D Flip-Flop                                                                      |            |  |  |  |  |

| 5.2 | Transmission Gate Master-Slave D Flip-Flop                                                             | 56         |  |  |  |  |

| 5.3 | Write-Port Master-Slave D Flip-Flop                                                                    | 61         |  |  |  |  |

| 6   | EXPERIMENTAL RESULTS UNDER ENVIRONMENTAL VA                                                            | ARIABILITY |  |  |  |  |

| 6.1 | Voltage Variations                                                                                     |            |  |  |  |  |

|     | <ul><li>Standard Master-Slave D Flip-Flop</li><li>Transmission Gate Master-Slave D Flip-Flop</li></ul> |            |  |  |  |  |

|     | 1.1.2 Transmission Gate Master-Slave D Flip-Flop                                                       |            |  |  |  |  |

| 6.2 | Temperature Variations                                                                                 |            |  |  |  |  |

|     | .2.1 Standard Master-Slave D Flip-Flop                                                                 |            |  |  |  |  |

|     | .2.2 Transmission Gate Master-Slave D Flip-Flop                                                        |            |  |  |  |  |

| 6   | .2.3 Write-Port Master-Slave D Flip-Flop                                                               | 78         |  |  |  |  |

| 7   | CONCLUSIONS                                                                                            | 81         |  |  |  |  |

| 7.1 | Future Works                                                                                           | 83         |  |  |  |  |

| 7.2 | Scientific Production                                                                                  | 83         |  |  |  |  |

| RE  | FERENCES                                                                                               | 85         |  |  |  |  |

| ΑP  | PENDIX: VARIABILITY IN FINFET DEVICES                                                                  | 91         |  |  |  |  |

#### 1 INTRODUCTION

As the transistor size shrinks, integrated circuits (IC) can contain tens millions of sequential logic elements, such as latches and flip-flops, as well as combinational logic elements in the same chip, satisfying the demand for higher density, more functionality and low power consumption (ANGHEL et. al, 2007b). However, technology scaling also brings undesirable issues to maintain the exponential growth rate and raises important topics related to reliability and robustness of electronic systems. The most common unwanted effects presented in nanometer technologies are aging effects, process and environmental variability. These effects significantly increase the leakage currents and radiation-induced Soft Errors (SE) (ANGHEL et. al, 2007a; ORSHANSKY et. al, 2008).

The manufacturing process in sub-micron technologies demands modifications in the physical design due to the miniaturization of components. It is defined more complex layout rules (MEINHARDT, 2014). These modifications collaborate directly with the increase of process and environmental variability on CMOS devices. Moreover, technology scaling has been reducing the load capacitances and supply voltages that impact on the minimal charge required to induce a soft error (HUBERT et. al, 2013). A relevant matter today in the semiconductor industry is to cope mainly with these variability factors.

Soft errors occur when a single energetic particle deposits enough charge near a sensitive node in a sequential or combinational circuit. In bulk CMOS technologies, any PN-junction of the PMOS or NMOS transistors is considered a sensitive region (BAUMANN, 2005). The main sources of energetic particles that contribute to radiation effects are protons and electrons trapped in the Van Allen belts, heavy ions trapped in the magnetosphere, galactic cosmic rays and solar flares (VELAZCO et. al, 2007).

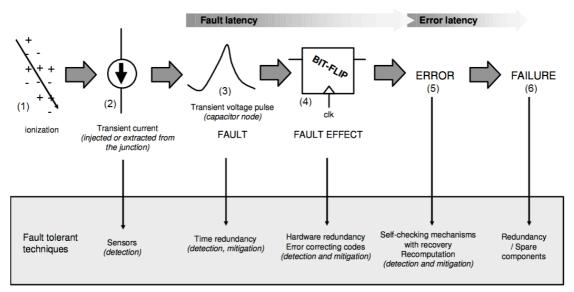

Fig. 1.1 shows the complete sequence of events from ionization until a failure, and the fault tolerance technique more suitable for each stage to guarantee the design of reliable circuits. The ionization (1) happens when an energetic particle strikes in the PN-junction of a transistor. The path formed due to ionization, results in a set of electron-hole pairs that generate a transient current due to the collected charge from the junction (2). If the collected charge is high enough to exceed the critical charge (Qcrit), where the on-transistor cannot balance the current, the transient voltage pulse appears and it causes a fault (3). The fault consists in an unexpected behavior that can change

the data state of logic gates, memory cells, registers, latches or flip-flops (DODD et. al, 2003).

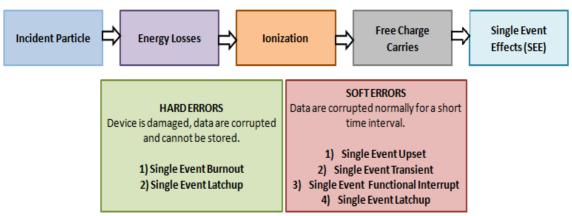

This phenomenon is known as Single Event Effects (SEE) and it produces a wide range of effects that can be divided into permanent, intermittent or transient faults. Permanent faults remain for long periods till a corrective action is taken, whereas transient faults appear and disappear in a short time interval (MUKHERJEE, 2008).

Figure 1.1: Complete sequence of events from ionization until a failure (KASTENSMIDT, 2007)

Two most common single events due to soft errors are Single Event Upset (SEU) and Single Event Transient (SET), which have been gaining prominence due the critical charge decreases with technology scaling. SEU or bit-flip occurs when an ionized particle hit inside a sequential logic while SETs happen when an ionized particle hits in a combinational logic (BRAMNIK et. al, 2013). Fault effects always will depend on the type of SEE. For example, the fault effect of SEUs is the inversion of an original stored data (4). If the SET has been propagated and the next sequential element latched in time this effect, the SET will become an SEU (BENEDETTO et. al, 2004).

Faults may or not lead a system to an error. An error is the manifestation of a fault and it generates value changes in internal operations (5). Permanent faults can cause permanent/hard errors; intermittent faults can cause intermittent errors, and transient faults can cause transient/soft errors. If the faults and errors cannot be masked or tolerated, the system malfunction will be visible to the user. This is commonly known as a failure (6). Faults detected early in designs can use simpler and cheaper techniques to tolerate them. The time period that a fault occurs until the moment that manifests itself as an error is defined as fault latency. Similarly, the time period that the error occurs until the moment that itself manifests as a failure is defined as error latency (WEBER, 2002).

Technology scaling introduced another important concern related to variability effects. Variability is the manufacturing-induced variations in a component. The main problem associated with them is the uncertainty about the correct circuit operation. Each circuit may present a different behavior, as a high deviation on performance or abnormal power consumption (SAHA, 2010). Moreover, variability generates many modifications along the lifetime of a circuit due to unexpected behaviors. It can accelerate the circuit degradation and make the circuit inappropriate for its initial purpose (GSS, 2010).

The variability can be divided into three factors (NASSIF, 2008): environmental, reliability and physical. Environmental factors appear during the operation of a circuit. The most common examples are the power supply and temperature variations. Reliability factors are related to transistor aging due the high electrical fields presented in modern circuits. Electromigration and Negative Bias Temperature Instability (NBTI) are classical problems in the reliability area. Finally, the physical factors are associated to variations of geometric or electrical parameters. In the majority of cases, physical variations are caused during the lithography step of the fabrication process.

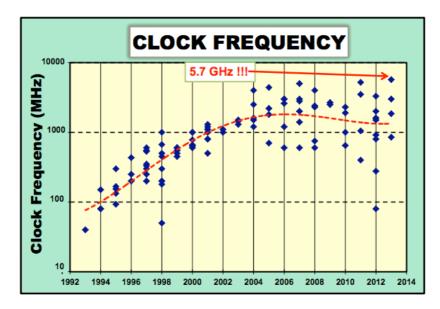

Fig. 1.2 shows the evolution of variability perspective in recent years. The technology scaling has already presented a significant raise of variability effects since the 65nm technology node. The performance commitment is one of the disadvantages brought by variability effects. According to Fig. 1.3, the performance prediction cannot be reached in last decades. The red curve indicates the maximum frequency achieved in each year, and it is possible to see that the performance gain started to stabilize between 2006 and 2008. This behavior happens due to the variability effects and also it has relation with other challenges brought by technology scaling.

| High Volume<br>Manufacturing | 2006  | 2008           | 2010                          | 2012       | 2014       | 2016     | 2018 |

|------------------------------|-------|----------------|-------------------------------|------------|------------|----------|------|

| Technology Node<br>(nm)      | 65    | 45             | 32                            | 22         | 16         | 11       | 8    |

| Integration Capacity (BT)    | 4     | 8              | 16                            | 32         | 64         | 128      | 256  |

| Delay = CV/I<br>Scaling      | ~0.7  | >0.7           | 1                             | Delay Scal | ing will S | low Dowr | 1    |

| Energy/Logic Op<br>Scaling   | >0.5  | >0.5           | Energy Scaling will Slow Down |            |            |          |      |

| Variability                  | Mediu | Medium High Ve |                               | y High     |            |          |      |

Figure 1.2: Evolution of variability perspective in bulk CMOS nanotechnologies (BORKAR, 2009)

Figure 1.3: Clock frequency trends in the last decades (ISSCC, 2013)

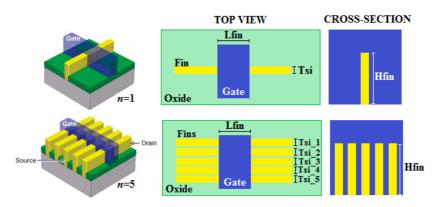

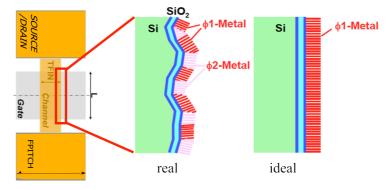

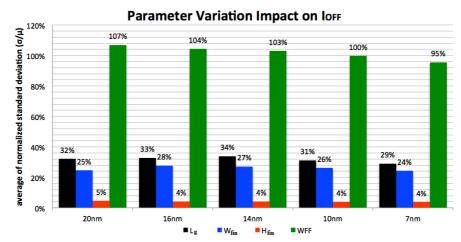

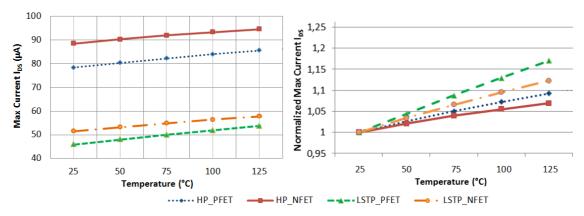

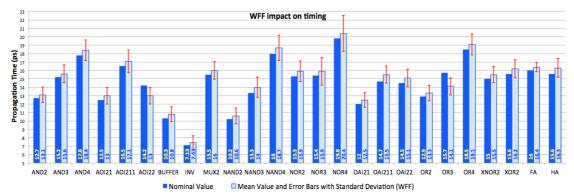

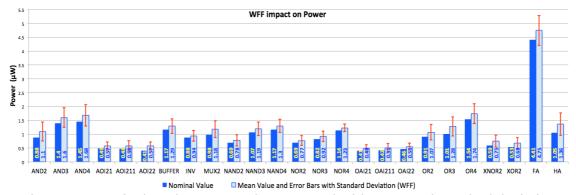

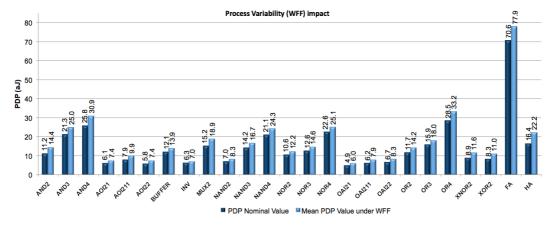

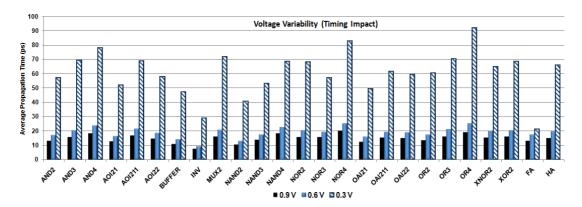

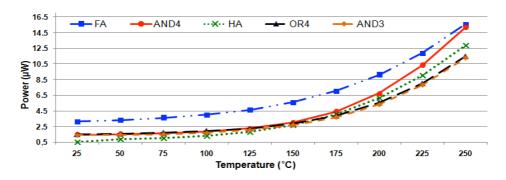

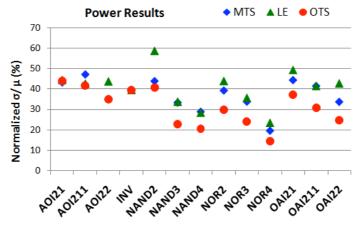

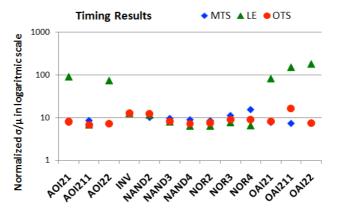

Although bulk CMOS technology have been used in integrated circuits designs for several decades. At each new technology node, it suffers from undesirable leakage currents and Short-Channel Effects (SCE) (KING, 2005). According to the ITRS analysis (ITRS, 2011), FinFET (Fin-Shaped Field Effect Transistor) technology is pointed as the main multigate device to replace bulk CMOS in sub-22nm technology nodes to continue with technology scaling. The appendix shows a brief report of the research related to this subject that was done in parallel with this dissertation. The research has consisted in the analysis of the impact of process, voltage and temperature (PVT) variations on timing and total power in FinFET technology nodes.

Master-Slave Flip-Flops (MSFF) are the most adopted sequential elements in Very Large Scale Integration (VLSI) designs to storage data in registers and in finite state machines. If a bit-flip occurs inside them, they may lose the previous stored information, followed by an incorrect system operation. In order to provide reliable systems to cope with radiation and variability effects, this work analyses the Window of Vulnerability (WOV) and the Timing Vulnerability Factor (TVF) in different MS D Flip-Flops topologies in pipeline stages.

The effective time window, which the bit-flip can still be captured by the next stage, is defined as Window of Vulnerability (WOV) (NGUYEN et. al, 2005). TVF corresponds to the time that a flip-flop or a latch is vulnerable to radiation-induced soft errors according to WOV and clock frequency (SEIFERT et. al, 2004). In addition to the clock frequency, the TVF also depends of process technology, the logic propagation delay between two sequential elements and environmental variations. To achieve better results, it is necessary to try to decrease the TVF values to reduce the vulnerability to bit-flips. The next subchapters describe related researches, motivations and contributions of this work.

#### 1.1 Related Researches

Many studies have compared FFs topologies regarding to performance, power consumption and timing characteristics in nanotechnologies, but neither of these showed a detailed analysis about the window of vulnerability of MSFF in a pipeline design. In (GIACOMOTTO et. al, 2007), a set of memory elements was analyzed in a real application, and it was proved that the most efficient flip-flops are identified through a pipeline structure. (ALIOTO, 2010) proposed a design flow for MS flip-flops to reach the better relation between power consumption and propagation delays. The interconnection delays also were considered in this flow. (ALIOTO, 2011) showed a comparison for a large quantity of FFs topologies in the energy-delay-area domain of nanometer CMOS flip-flops.

(SEIFERT and TAM, 2004) described a method for computing TVF of MS flip-flops and flow-through latches of a high-performance microprocessor, capturing the impact of sequential elements in your typical operating environment. This paper demonstrated that TVF has a high dependency with a propagation delay between two sequential circuits in a pipeline, and it varies between 0% and 50%. (HEIJMEN, 2008) created an approach to make an accurate estimation of the contribution of flip-flops to the Soft Error Rate (SER) of an IC. His approach is based on a set of expressions to calculate the TVF of master and slave latches, but it is only applicable to frequencies below 1GHz. (BRAMNIK et. al, 2013) introduced a novel technique for computing TVF in modern complex synchronous designs, where all key inputs are based on static timing data readily available in most design databases.

A complete explanation of variability concerns in bulk CMOS technologies sub-90nm is shown in (MASUDA et. al, 2005). (KUMAR, 2010) and (BORKAR, 2003) explore the performance of devices and interconnections when the temperature suffers variations. These works also describe the increase in fault susceptibility when temperature oscillations occur. Various analysis and comparisons have been carried out to evaluate variability effects in flip-flops, (NEUBERGER et. al, 2007), (REBAUD et. al, 2008) and (LOTZE et. al, 2008) showed the impact of variations on timing characteristics in different flip-flops topologies. (ALIOTO et. al, 2015) investigated the impact of all fundamental sources of variations on performance and robustness against hold time violations in some MS flip-flops. The analysis has considered process, voltage, temperature and clock slope variations in 65nm CMOS technology.

#### 1.2 Motivation and Contributions

Latches and flip-flops are widely adopted in VLSI systems due the ability to control flow and storage data. Moreover, sequential elements are the most instantiated cell in digital integrated circuits, representing from 30% to 50% of the total circuit area (OKLOBDZIJA et. al, 2003). Radiation effects in ICs can range from low magnitude noises or large transient pulses that are able to generate transient upsets or soft errors affecting the data integrity.

Using radiation-hardened devices will often solve the radiation effects problem, but these circuits have some disadvantages. The hardened circuits are more expensive than non-hardened circuits and not all circuits are available in a hardened version. Hardened circuits are usually fabricated using mature technologies, and they have sale limitations (KASTENSMIDT, 2007). So, it is very important to study techniques to mitigate the radiation effects in non-hardened circuits. The prediction of the time quantity that non-hardened sequential circuits are vulnerable to upsets is crucial to guarantee the integrity of stored data.

Previous works calculate the window of vulnerability without considering the setup time of master and slave latches, but electrical simulations have been made and it was proved that the setup time of latches is also sensitive to bit-flips. For this, all analysis in our research were made respecting the definition provided in references, but the setup time was taken into account to calculate the WOV of MS Flip-Flops.

This work analyzes three different MSFF topologies under bit-flip in a pipeline design to determine the window of vulnerability and the timing vulnerability factor of master and slave latches. The first goal is to verify how much the variation of some parameters impact the WOV and TVF of FFMS listed below at nominal conditions:

- 1. Standard Master-Slave D Flip-Flop (SMSFF)

- 2. Transmission-Gate Master-Slave D Flip-Flop (TGMSFF)

- 3. Write-Port Master-Slave D Flip-Flop (WPMSFF)

The parameters analyzed in this work determines the dependence between TVF with operational frequency, with the fault propagation to the next stage through a combinational logic with different propagation delays and with different nanometer technological models, also considering High Performance (HP) and Low Power (LP) versions. All the simulations were made using the HSPICE electrical simulator.

The variability can manifest itself causing an increase or a decrease to the initial specification (SAHA, 2010). The main problem is the uncertainty about the value stored in sequential elements. For example, there are circuits that present operational frequency oscillations due to variability effects. In this way, the second goal is to evaluate the TVF of MSFF topologies against environmental variability effects with supply voltage and temperature variations.

The proposed study is important to demonstrate how to analyze the WOV and TVF of MSFFs, as well as to show the real impact of the choice of technology and operating frequency in designs under radiation. The dependency to TVF between diverse path delays and environmental variability also is crucial to determine the design vulnerability.

#### 1.3 Work Organization

This dissertation is divided as follows. Chapters 2 and 3 introduce the theoretical foundation for full comprehension of this work. The methodology utilized to validate the contributions of this work can be seen in chapter 4. Finally, results are shown in chapters 5 and 6 with a methodological sequence to highlight the main results. A brief description of each chapter is presented below:

<u>Chapter 2: Radiation Effects in Integrated Circuits</u> - This chapter shows the main sources of radiation, the explanation of charge collection mechanism, case-studies of Single Event Effects, how transient faults are modeled electrically as well as the challenges faced in nanometer technologies.

<u>Chapter 3: Sequential Logic Circuits</u> - This chapter presents the basic concepts related with sequential circuits, including timing analysis and clock issues for MS D flip-flops. Furthermore, this chapter also explores how the WOV and TVF are measured, and how the propagation delay and clock frequency can contribute to reduce them.

<u>Chapter 4: Methodology</u> - This chapter describes the characteristics of three topologies of MS D flip-flops studied in this work and the pipeline design utilized in this research. Moreover, information about the nanometer technological models, operational frequencies, path delays and environmental variability utilized to obtain the experiment results also are present in this chapter.

<u>Chapter 5: Experimental Results at Nominal Conditions</u> - This chapter contains the TVF results for the three topologies FFMS considering different operational frequency, path delays and technologies models with nominal values corresponding to each examined technology.

<u>Chapter 6: Experimental Results under Environmental Variability</u> - This chapter also contain the TVF results and it is very similar to chapter 5. The difference is that the analysis is made under environmental variability, with supply voltage and temperature variations.

<u>Chapter 7: Conclusions</u> - This chapter has a set of conclusions that validate and reinforce the importance of contributions presented in this work. Potential future works and the main publications in conferences and journals during the master course also are presented.

#### 2 RADIATION EFFECTS IN INTEGRATED CIRCUITS

Radiation consists in electromagnetic activity or particle incidence with high energy, which in contact with a particular material produces effects on it. Radiation effects can be very simple as low magnitude pulses or they can generate large magnitude pulses able to change the data in sequential or combinational logic elements. The Earth's atmosphere acts like a radioactive filter and it decreases the radiation intensity that impacts the Earth (BOUDENOT, 2007). However, the radiation incident continues to affect integrated systems even operating at sea level.

Reported problems due to particle strikes in commercial systems are unusual because the major companies do not like to reveal problems in their chips. Some reports that radiation could affect electronic devices are shown in Table I. May and Woods described in their landmark paper about the first evidence of soft errors from alpha particles in chip packaging modules (MAY et. al, 1979). Ziegler and Lanford predicted the occurrence of soft errors due to cosmic rays radiation at sea level (ZIEGLER et. al, 1979). Then, the first real evidence of soft errors from cosmic rays in semiconductors came in 1984, but it was not released by IBM Corporation.

Table 2.1: Main evidences of soft errors in commercial systems

| Year | Company/University                | Reports                                                                                                |

|------|-----------------------------------|--------------------------------------------------------------------------------------------------------|

| 1962 | NASA/AT&T                         | Electrons in Van Allen belt cause degradation in some Telstar Satellite components.                    |

| 1978 | Intel Corporation                 | Chip packing modules got contaminated due to the impact of alpha particles.                            |

| 1984 | IBM Corporation                   | Soft errors in the systems due to cosmic radiation.                                                    |

| 1987 | IBM Corporation                   | Chip manufacturing process got contaminated due to the impact of alpha particles.                      |

| 2000 | Sun Microsystems                  | Error protection scheme implemented for Ultra SPARCII servers was insufficient to handle soft errors.  |

| 2004 | Cypress<br>Semiconductor          | Single soft error crashed an interleaved system farm.                                                  |

| 2005 | Los Alamos<br>National Laboratory | 2048-CPU server system frequently crashed because of cosmic ray.                                       |

| 2008 | AIRBUS                            | The aircraft made two abrupt descents due to the soft error that caused fault onboard computer system. |

Source: Adapted from (MUKHERJEE, 2008)

#### 2.1 Main Sources of Radiation-Induced Faults

There are different sources to induce transient faults in semiconductor devices. In general, the most common sources are process variability, thermal cycling, erratic fluctuations of minimum voltage and radiation external to the chip (MUKHERJEE, 2008). Various particles generated by sun activity contribute to radiation effects. They can be divided between energetic particles such as electrons, protons and heavy ions, and electromagnetic radiation, which can be X-ray, gamma ray or ultraviolet light (BARTH, 1997). The energetic particles that induce soft errors in silicon chips due to ionization of atomic electrons are known as alpha particles or neutrons.

Alpha particles are emitted from solder bumps or interactions with radioactive impurities such as uranium, thorium or radium present in the packaging materials through alpha decay process (MUKHERJEE, 2008). The structure of these particles consists of two protons and two neutrons bound together into a particle identical to a helium nucleus. Alpha particles lose its kinetic energy through interactions with the electrons when penetrates into the material, and thus leaves an ionization trail (BAUMANN, 2005). There are some materials that aim to minimize the emission of these particles, but these materials are very expensive. Furthermore, it is very difficult to eliminate them completely (DUPONT et. al, 2002).

Neutrons are the most frequent cause of upset at ground level and they are related to cosmic ray events (NORMAND, 2001). Soft errors caused by neutrons arise from interactions between cosmic ions and oxygen/nitrogen in the upper atmosphere (KASTENSMIDT, 2007). When atoms break apart, protons persist for long durations before decaying and it forms the majority of primary cosmic rays in earth's outer atmosphere. When primary cosmic rays collide with atmospheric atoms it is produced complex cascades of secondary particles, which constitutes the secondary cosmic rays. Primary and secondary cosmic rays are known as high-energy cosmic rays. If low-energy cosmic rays interact with the boron existing in some p-type dopants in semiconductor chips, other particles can be created (BAUMANN et. al, 2000).

Primary cosmic rays are composed of galactic and solar particles. Galactic particles arise from stellar flares, supernova explosions or other cosmic activity whereas solar particles arise from the sun. Galactic particles have more probability of reaching the sea level because its energy to penetrate the earth is bigger. Secondary cosmic rays are composed of secondary particles as pions, muons, protons and neutrons that if collided with other atmospheric atoms can create a new shower of particles. The neutron flux is strongly dependent on altitude, longitude and latitude. At terrestrial altitudes, less than 1% of primary cosmic rays reach the sea level (ZIEGLER et. al, 1981).

It is important to highlight that the kinetic energy of alpha particles is lower than typical neutrons that affect CMOS technology, but alpha particles generate more problems when they hit transistors. This happens because the impact of alpha particles immediately generates a track of electron-hole pairs in the substrate that deposits a significant amount of charge at a node while neutrons do not create it directly.

#### 2.2 Charge Collection Mechanism

The charge generated by the impact of particles varies depending on the ion type, incident angle and impact site. The way as energetic particles interacts with silicon is different when the impact is due to neutrons or alpha particles. Alpha particles interact directly with electrons present on the substrate while neutrons interact through inelastic or elastic collisions. Experimental results show that inelastic collisions are the main cause of soft error due to neutrons, because they create secondary particles (SRINIVASAN, 1996).

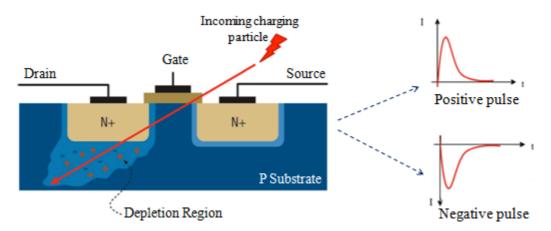

The collision of energetic particles causes a strong field perturbation and it creates a track of electron-hole pairs with a high carrier concentration that deposits energy in the material (MESSENGER, 1982). This track contains equal number of electrons and holes. If ionization track transverses the depletion region, the electric field collects the carries generating a transient current pulse at the node, which can be negative or positive. Fig. 2.1 illustrates the moment that a particle strikes a node in a semiconductor device and it generates a pulse. The pulse can be positive or negative according to the transistor. NMOS transistors may present negative pulses, in other words, a discharge in the node, while PMOS transistors may present positive pulses or a charge in the node.

The disturbance caused for the impact depends on energy lost per unit track length known as linear energy transfer (LET). For every 3.6eV (electron volts) of energy loss by the particle, one electron-hole pair is created in the silicon substrate. The LET depends on the mass/energy of the particle and the material in which it is traveling. The highest LET values are obtained when more massive and energetic particles impact denser materials (BAUMANN, 2005). In this way, the width of the transient voltage pulse is dependent on the energy of the particle, the charge stored at a node and the charge collection of the affected junction. The duration and amplitude of transient voltage pulse depend on electrical characteristics of the struck node like resistance and capacitance. In nanometer technologies, the duration of transient voltage is around few hundreds of pico seconds to few nano seconds (LISBOA et. al, 2007).

Figure 2.1: Silicon substrate ionization due to impact of energetic particles and the pulse generated by this effect. Adapted from (SAWANT, 2012)

The impact of neutrons occurs similarly to alpha particles one. The difference is that the impact of neutrons in the silicon substrate does not directly create electron-hole pairs. Instead, neutrons collide with the nuclei in the semiconductor resulting in the emission of energetic secondary particles. These new particles cause ionization tracks and they generate electron-hole pairs enough to cause a transient current pulse. The probability to create secondary particles is slight. A number of neutrons greater than a number of alpha particles are necessary to produce a transient fault with the same impact on a semiconductor device. (MUKHERJEE, 2008).

In bulk CMOS technologies, any PN-junction of the PMOS or NMOS transistors is considered a sensitive region (BAUMANN, 2005). Depending on the charge that is collected, a short occurs for a little time period in the impacted PN-junction, producing a transient pulse. There are cases that the pulses have a low magnitude and the initial value of the node is not modified. However, if the pulse exceeds the critical charge (Qcrit) and it turns on the gate of the opposite transistor, it will cause a circuit malfunction.

The nodes are more sensitive to upsets due the voltage supply  $(V_{DD})$  and nodal capacitance  $(C_{node})$  reductions to improve performance and power consumption at new technologies. These reductions are directly related to the charges stored at circuit nodes  $(Q_{node})$ , as shows Eq. 1.1. In this way, the stored charge in each node also becomes smaller and it affects the critical charge, reducing the quantity of charge required to corrupt the stored information at circuit nodes (JAHINUZZAMAN et. al, 2009). Consequently, soft errors susceptibility increases due to advanced technology.

$$Q_{\text{node}} = C_{\text{node}} * V_{\text{DD}}$$

(1.1)

Fig. 2.2 shows the charge collection mechanism in a drain terminal of PMOS transistor of an inverter gate. The current flows through the struck PN-junction of PMOS transistor and the expected value of the output of inverter gate is '0'. The transistor in on-state also conducts a current trying to balance the current generated by particle strike. If the collected charge is low and the transistor in on-state balances the current before the node capacitance is charged, the fault is not seen. On the other hand, if the collected charge is high enough and it exceeds the critical charge, a voltage change at the node occurs. This behavior happens similarly for the NMOS transistor. Depending on the transistor in on-state, the collected charge is eliminated through VDD or GND, making the node to return to its correct state (WANG et. al, 2008).

Figure 2.2: Charge collection mechanism when a soft error occurs at PN-junction (WANG et. al, 2008)

#### 2.3 Single Event Effects

Faults caused by a single energetic particle, which can take on many forms, are called Single Event Effects (SEE) (O'BRYAN, 2000). With technology scaling, the device dimensions are suffering reductions, and the circuit speed is increasing. These factors have collaborated with the increase of SEE occurrence in the ICs (DODD et. al, 2004). The charge deposited by a single ionizing particle can produce a wide range of effects like Single Event Upset (SEU), Single Event Transient (SET), Single Event Functional Interrupt (SEFI), Single Event Latchup (SEL) and Single Event Burnout (SEB). Fig. 2.3 shows a simple diagram to represent the sequence of events from incident particle until an SEE, as well as the classification of SEE divided into soft errors and hard errors. In some cases, SEB and SEL are also classified as hard error.

Figure 2.3: Classification of Single Event Effects in ICs

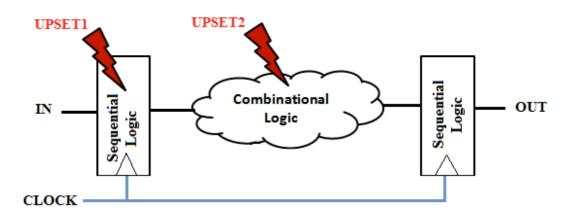

When a single energetic particle interacts with silicon, the upset can reach the combinational logic or the sequential logic as shown in Fig. 2.4. (CRAIN et. al, 2001; ALEXANDRESCU et. al, 2002). The data from the first sequential cell is released to the combinational logic only when a clock edge occurs and at this moment, the logic operations are performed. The results of combinational logic normally reach the next sequential sometime before the next clock edge. At this clock edge, whatever is the data in the input of the second sequential, which is in agreement with the setup and hold times, it will be stored in a sequential circuit.

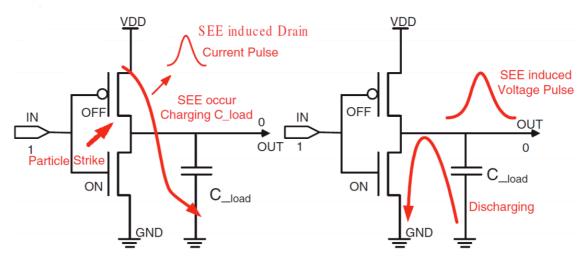

If a charged particle strikes a memory element, such as a latch or flip-flop, it may invert the stored original value, producing a Single Event Upset or in other words, a bit-flip (BAUMANN, 2002). When a charged particle hits the combinational logic block, it also generates a transient current pulse. This circumstance is known as Single Event Transient (LEAVY et. al, 1991). If the fault propagates up to an input of the next sequential and if this data comply with timing constraints, an incorrect value will be stored. Moreover, an SET will become an SEU in the circuit.

Figure 2.4: Upsets possibilities: combinational or sequential logic circuits. Adapted from (KASTENSMIDT et. al, 2006)

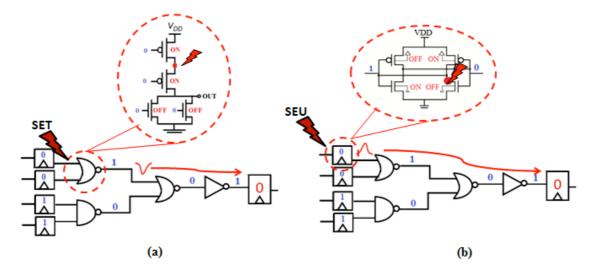

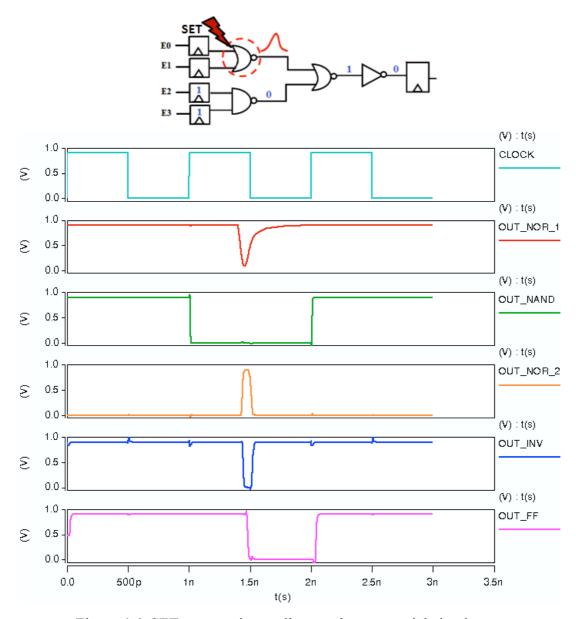

Fig. 2.5 exemplifies the most common single event effects that happen on the circuits. First, the SET occurs in a sensitive node in a NOR gate and it generates a pulse in the combinational logic (a). This pulse was propagated and it reached the sequential logic to the right, which stored the incorrect value '0'. Memory cells have two stable states, one that represents a stored value '0' and one that represents a stored value '1'. In each state, there are two transistors in on-state and two transistors in off-state. In the second case (b), an energetic particle hits in the sequential logic in one of the two sensitive nodes. So, an SEU occurs (reverse the transistor state) and it affects the rest of the circuit because the incorrect value also is stored in the sequential logic to the right.

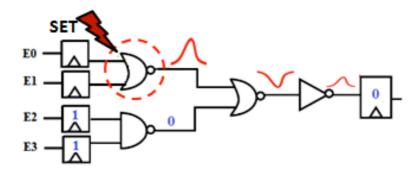

Figure 2.5: (a) Single Event Transient and (b) Single Event Upset on a circuit

There are some cases where a transient pulse will be masked, and it will not be captured by the sequential elements. In this case, the fault will not lead to errors or failures visible to the user. Moreover, the circuit keeps a correct value in the output because the faults are masked still in origin. There are three kinds of masking commonly observed in logic blocks: logical masking, electrical masking and latch window masking (LIDEN et. al, 1994; SHIVAKUMAR, 2002).

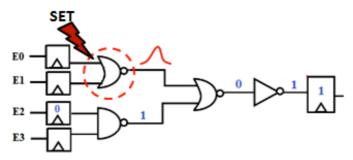

The logical masking happens when a particle strike affects a portion of the circuit. However, the hit node is not relevant to determine the final output. In this way, the output can be determined only by inputs not affected by a particle. For example, the first input of NAND gate in Fig. 2.6 is '0', and then, the second input is not important because the final result will always be '1'. So, if a particle impacts one of inputs, the error will not be seen in the last output. According to truth table, the same happens with a NOR gate, if one input is equal to '1', the final result will always be '0'.

Figure 2.6: Logical masking in a combinational circuit

The electrical masking happens when the fault impacts the circuit node, but the current pulse generated is attenuated through the combinational logic and it disappears before being stored by a forward latch. For example, in Fig. 2.7, NOR gate has an SET in the first input, but the effect that it causes is mitigated when is propagated until the output of an inverter. The fault reaches the forward latch, but the pulse has a small

amplitude that is interpreted as a logical value. So, the latch will store the correct value, which in this case, is equal to '0'.

Figure 2.7: Electrical masking in a combinational circuit

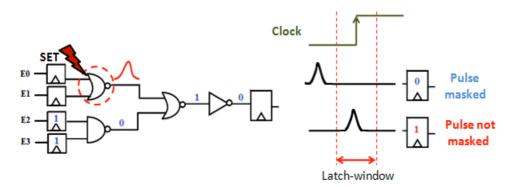

When a transient pulse cannot be masked logically or electrically, it propagates until it reaches a sequential circuit. Latch-window masking happens when the pulse is not captured by a latching window of a sequential logic. In Fig. 2.8, if the pulse at the NOR gate was not masked by one of the methods that were already been presented, the memory element can mask it according to the latch-window. On the right of Fig. 2.8, it is shown a clock cycle with its latching window. If the SET is captured when a clock transition happened, a wrong value will be stored. Finally, the rate that SETs get latched as errors depends on the clock frequency and the topology of sequential circuits.

Figure 2.8: Latch-window masking in a combinational circuit

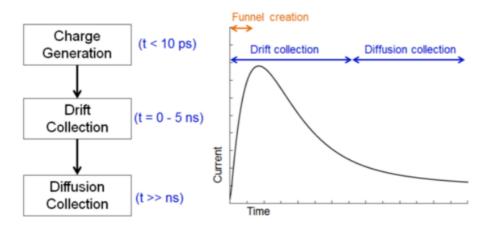

#### 2.4 Transient Pulse Modeling

Depending on fabrication process and the sensitive nodes, different shapes of transient currents can be observed (DODD, 2005; FERLET-CAVROIS, 2006). After the silicon particle ionization, the charge collection proceeds through two mechanisms: drift and diffusion. When the resultant ionization track traverses the depletion region, carriers are rapidly collected by the high electric field. This charge collection is known as drift. The crossing of particles through the depletion region is responsible for temporary deformation in a funnel shape. This effect is called funneling and it causes an increase in the collected charge efficiency due to the increase of the depletion region area (BAUMANN, 2005). Finally, diffusion process collects all the other carries generated

besides the depletion layer. The typical current waveform resulting from the additional collect charge induced by particle incidence can be seen in Fig. 2.9.

Figure 2.9: Typical current waveform of one single event (CUMMINGS, 2010)

Charge deposition mechanism is widely used and it is modeled by a double exponential current pulse, which is given by Eq. 2.1, Eq. 2.2 and Eq. 2.3 (MESSENGER, 1982). These equations are based on the current node algorithm, which aims to convert the circuit described in a matrix and solving a linear equation that is generated from Kirchhoff's current law (HO et al., 1975).

$$I_{P}(t) = I_{0} (e^{-t/\tau \alpha} - e^{-t/\tau \beta})$$

(2.1)

$$I_0 = Q_{coll}/(\tau \alpha - \tau \beta) \tag{2.2}$$

$$Q_{coll} = 10.8 * L * LET$$

(2.3)

The terms of equations above represent:

$I_0$  = the maximum charge collection current;

$Q_{coll}$  = the collected charge;

$\tau \alpha$  = the collection time constant of the junction;

$\tau\beta$  = the time constant for initially establishing the ion track;

L = the charge collection depth;

In bulk silicon, a typical charge collection depth for a heavy ion is approximately 2µm. For every 1MeV.cm<sup>2</sup>/mg, an ionizing particle deposits about 10.8fC of electronhole pairs along each micron of its track (MAVIS et. al, 2002).

## **3** SEQUENTIAL LOGIC CIRCUITS

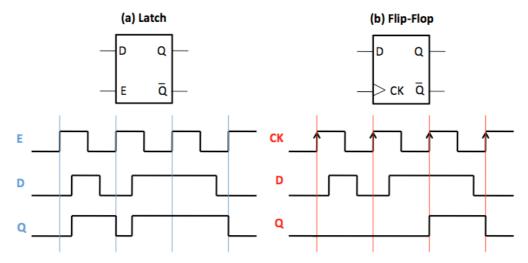

Logic circuits for digital systems can be of two types: combinational circuits and sequential circuits. A combinational circuit is composed by a set of logic gates, which determine the output values directly from the current input values. On the other hand, sequential circuits depend on the current input values, and they also depend on preceding input value (RABAEY et. al, 2003). Sequential circuits act as memories, remembering data storage in the system. In addition to logic gates, the main elements used in sequential circuits are latches and flip-flops to store one bit of information. Fig. 3.1 shows the symbol and the timing diagram of two main elements of sequential circuits.

Figure 3.1: Symbol and timing diagram for a positive (a) latch and (b) flip-flop

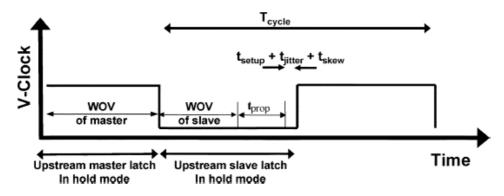

A latch is a level-sensitive circuit with two main operating modes: transparent mode and hold mode. Latches are in transparent mode, if they are enabled to receive data such that the D input passes its value to the Q output during all phases. Latches are in hold mode, if they are not enabled to receive data such that the last value stored in Q output is maintained until the next level change occur. Moreover, latches can be classified as positive or negative depending on the phase of clock period that they are in transparent mode. For example, a positive latch passes the D input values to the Q output when the clock signal is high as shown in the timing diagram of Fig. 3.1 (a). A latch is essential in the construction of an edge-triggered flip-flop.

Flip-Flops are edge-triggered circuits that also have the transparent and hold modes. Contrary to latches, flip-flops only copy the D input value to Q output on a clock transition remaining with this value until other clock transition occurs. Flip-flops can be also classified as positive or negative, it depends if the circuit captures the data on a positive or a negative edge-triggered. For example, a positive flip-flop passes the D input value to the Q output when a  $0 \rightarrow 1$  clock transition occurs as shown the timing diagram in Fig. 3.1 (b). The inputs must be stable for a short period around the clock edge to meet setup and hold requirements.

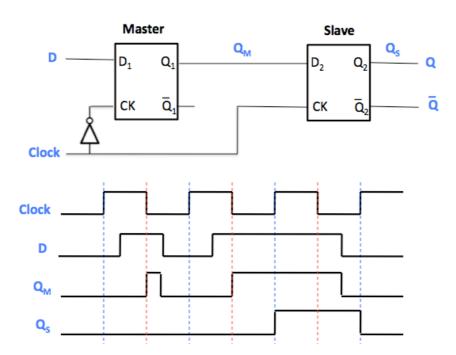

In real circuits, the flip-flops are designed as a master-slave structure composed of positive and negative latches in cascade controlled by complementary clock signals. Fig. 3.2 shows the structure of master-slave D flip-flop sensible to rising edge. The operation is very simple: when the clock signal is low, the master latch is in transparent mode and the slave latch is storing the previous value. If a positive clock transition happens, the master latch only stores the value between two latches while the slave latch in transparent mode puts the D input values on the Q output.

According to the timing diagram in Fig. 3.2, the master latch is negative and all data in the D input will be transfered to  $Q_M$  when the clock is low. Similarly, all data present in  $Q_M$  input will be transfered to  $Q_S$  when the clock is high because the slave latch is positive. In the figure below, it is assumed that  $Q_S$  and Q outputs are equal as well as  $Q_M$  is equal to  $D_2$  too. To create a master-slave D flip-flop sensible to falling edge it is only necessary to reverse the clock signal that feeds the two latches. These flip-flops form the basic elements of shift registers, which are an essential part of several electronic devices.

Figure 3.2: Structure and timing diagram of master-slave D flip-flop

#### 3.1 Timing analysis and clock issues

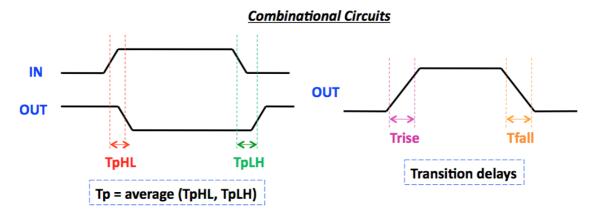

Due to parasitic elements, like channel resistance and gate capacitance, when an input changes, the output is not going to change instantaneously (NUNES, 2014). The time that the output takes to answer a stimulus in the input is defined as propagation delay (Tp/Tprop). To compare combinational logic circuits regarding performance, it is important to know the propagation times called high-low delay (Tp<sub>HL</sub>) and low-high delay (Tp<sub>LH</sub>). The propagation times are measured by convention from the 50% of the signal, assuming that the switching threshold is located in the middle of the waveform, as shows Fig. 3.3 on the left. So, the propagation delay of circuits is given by the average of propagation times.

Furthermore, propagation delays have relation to slopes of the input and output signals. Transition delays are introduced to quantify these slopes and they express how fast a signal transits between the different levels (RABAEY et. al, 2003). The time required for a signal transition from 0 to 1 or from 1 to 0 are defined as the rise (Trise) and fall times (Tfall), respectively. These times are measured between 10% and 90% of the output waveform, as shows Fig. 3.3 on the right. In summary, these times indicate the amount of time needed to reflect a stable value at output until another input change occurs.

Figure 3.3: Propagation and transition delays for combinational logic circuits

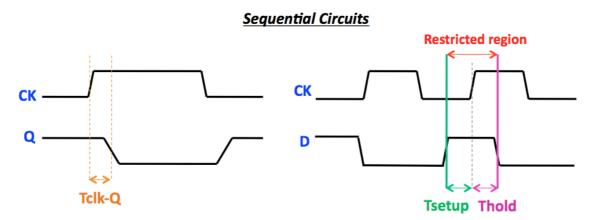

Propagation delay in flip-flops is commonly measured as the time that the data in D input takes to appear in the Q output from the moment that clock edge trigger happens (Tclk-Q), as shows the Fig. 3.4 on the left. In the case of latches, timing characteristics are measured in relation to the D input and Q output (T<sub>D-Q</sub>). By convention, the propagation delay of a sequential circuit is also measured from the 50% of the signal assuming that the switching threshold is located exactly in the middle of the waveform.

There are two important timing constraints that if they are violated for any flip-flop in the circuit, the circuit cannot operate correctly. These restrictions are shown in Fig. 3.4 on the right. Setup time (Tsetup) indicates the time that the data input must be stable before the clock transition trigger. The hold time (Thold) is the amount of time that the data input must be valid after the clock transition trigger. All circuits must be designed respecting the restricted region. The data signal needs to arrive at least before the clock

edge of the setup time and it remains without changes until at least till the hold time after the clock edge.

Figure 3.4: Propagation delay, hold and setup times for sequential logic circuits

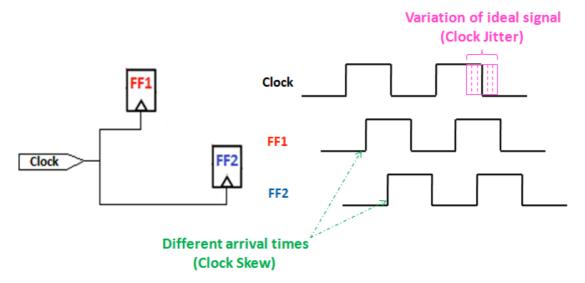

In the literature, it is normally assumed that the clock signal is a perfect one. However, this is not a safe assumption because in real applications, the clock signal suffers some changes. There are two main factors known as clock skew and clock jitter that can cause harm to a clock signal. Cells in a core are placed in different regions and the clock signal is distributed from a single source to all sequential elements of the circuit. The clock skew is defined as the difference in the arrival time of clock signal to any two flip-flops fed by the source. On the other hand, the clock jitter is defined as the undesired variation of a signal in relation to the ideal position in time. Both effects can be seen with more details in Fig. 3.5.

Figure 3.5: Clock skew and clock jitter causes harm to a clock signal

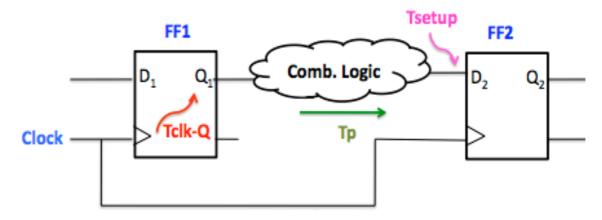

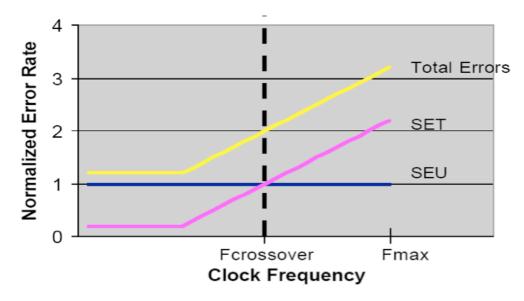

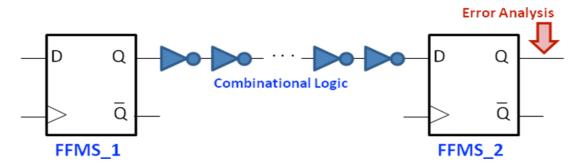

Timing analysis and clock issues presented above are directly related to the clock frequency of sequential circuits. In a typical circuit, pipeline designs are composed of two flip-flops and a combinational logic between them, as shown Fig. 3.6. Each one these structures has a data arrival time and a data required time. Eq. 3.1 gives the data arrival time, where Tclk-Q is the propagation delay of the first flip-flop, Tp is the propagation delay of combinational logic and Tsetup is the setup time of the second flip-flop. It is crucial to minimize the data arrival time to obtain the maximum clock possible frequency. The data required time corresponds to a full clock period as shown by Eq. 3.2.

Figure 3.6: Pipeline design of typical circuits

Data arrival time =

$$Tclk-Q + Tp + Tsetup$$

(3.1)

Data required time =

$$T$$

clock (3.2)

Static Timing Analysis (STA) tools consider the data arrival time to compare it to the clock period defined in the constraints file. This time must be smaller than the clock period defined previously to meet the timing enclosure. If the circuit does not operate exactly in the defined frequency, a slack is created. Slack is defined as the difference between the data arrival time and the data required time for a timing path, and it determines if the pipeline design is working at the specified frequency. Zero setup slack indicates that the pipeline design works exactly at the specified frequency, and there is no margin available in the circuit. However, it is possible that a pipeline design operates at frequencies lower than one pre-defined previously. In this case, this gap between the frequencies generates a positive setup slack that can be shown in Fig. 3.7. Negative slack implies that the pipeline design does not operate in the pre-defined frequency.

Figure 3.7: Timing diagram analysis for setup time slack

#### 3.2 Soft Error Rate (SER)

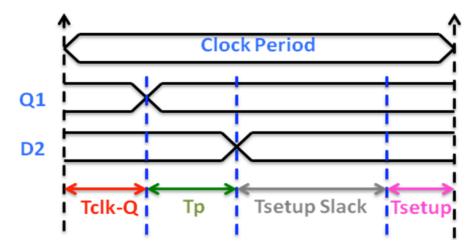

Technology scaling also decreases the probability of electrical masking in combinational logic circuits. This happens because a high transistor density generates small combinational logic depth and it reduces the propagation delays between memory elements. In this way, the pulse cannot be attenuated enough by combinational logic and the quantity of SETs that can get latched as errors in sequential circuits becomes higher. Since the delay of circuits is smaller, the clock frequency is becoming larger, allowing that circuits to process more data in less time (DODD et. al, 2004). Currently, the curve of SEU in Fig. 3.8 does not represent a constant because the number of SEU also increases as well as the technology advanced. For this reason, it is important to study the behavior of sequential circuits under radiation since both single event effects (SET and SEU) contribute significantly to the Soft Error Rate. SER is the rate at which a device encounters soft errors during a system operation.

Figure 3.8: Soft Error Rate in last decades (DODD et. al, 2004)

The Soft Error Rate of a circuit can be estimated by Eq. 3.3 (NGUYEN et. al, 2003):

$$SER^{Circuit} = \sum_{i \text{ over all nodes}} (SER^{Nominal}_{i} * TVF_{i} * AVF_{i})$$

(3.3)

where the nominal SER (SER<sup>Nominal</sup><sub>i</sub>) refers to the underrated SER that is independent of the circuit environment. The impact that the circuit environment and the architecture have on SER are accounted by the Timing Vulnerability Factor (TVF<sub>i</sub>) and by the Architecture Vulnerability Factor (AVF<sub>i</sub>). AVF is the probability that a fault in a device *i* will be observed by the system or by the user. Since TVF and AVF are two independent concepts, this work is focused on the calculation of TVF under different operating conditions. The explanation of TVF is presented in subchapter 3.4. A complete methodology to compute the AVF can be seen in (MUKHERJEE et. al, 2003).

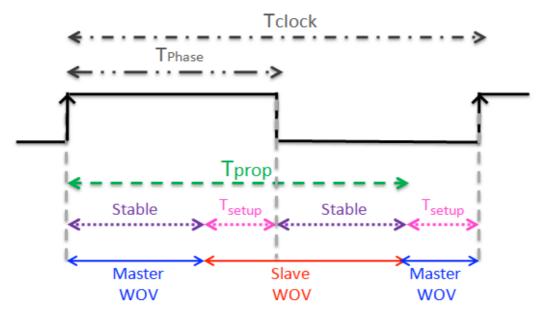

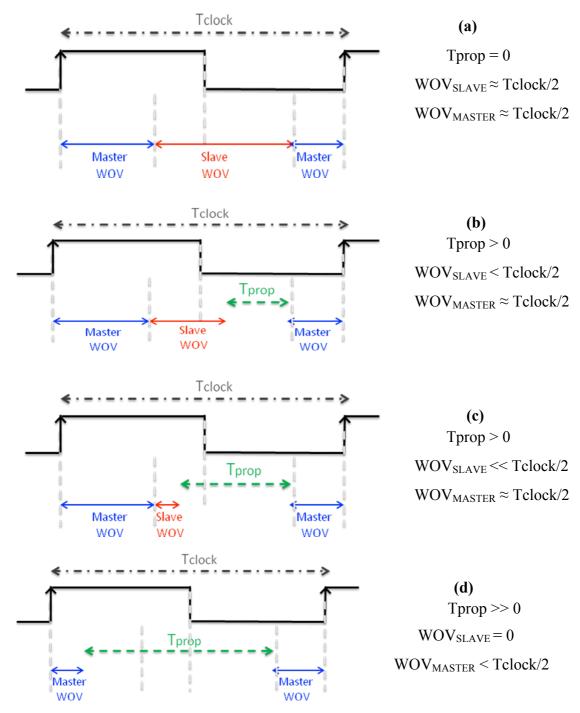

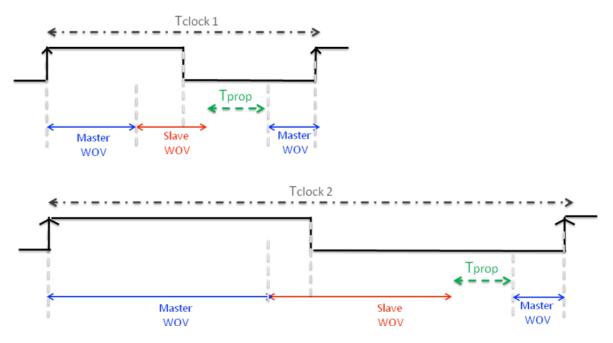

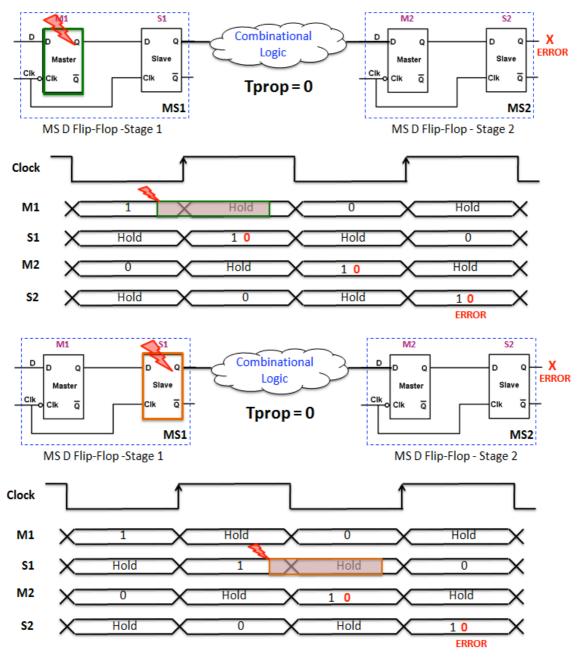

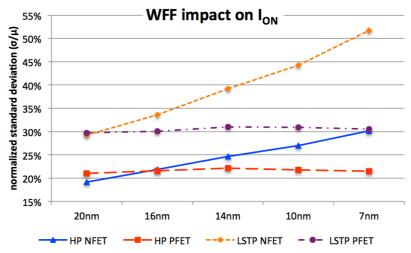

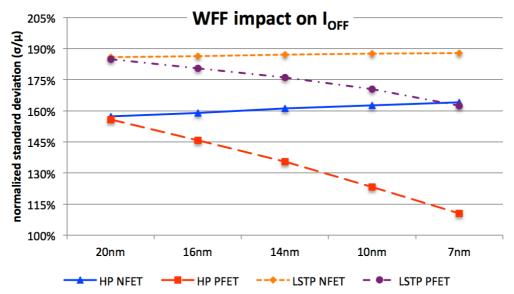

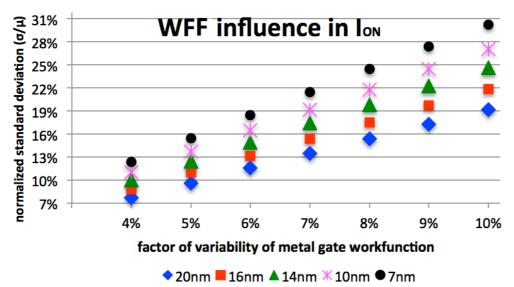

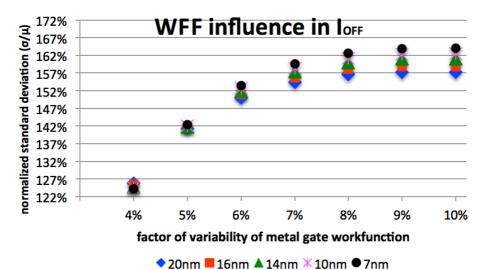

#### 3.3 Window of Vulnerability (WOV)