### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

#### **EDSON LUIZ PADOIN**

# **Energy-aware load balancing approaches to** improve energy efficiency on HPC systems

Thesis presented in partial fulfillment of the requirements for the degree of Doctor of Computer Science

Advisor: Prof. Dr. Philippe Olivier Alexandre

Navaux

Advisor during Ph.D.

Internship: Prof. Dr. Jean-François Méhaut

#### **CIP** — **CATALOGING-IN-PUBLICATION**

Padoin, Edson Luiz

Energy-aware load balancing approaches to improve energy efficiency on HPC systems / Edson Luiz Padoin. – Porto Alegre: PPGC da UFRGS, 2016.

153 f.: il.

Thesis (Ph.D.) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação, Porto Alegre, BR-RS, 2016. Advisor: Philippe Olivier Alexandre Navaux; Advisor during Ph.D. Internship: Jean-François Méhaut.

1. Load Balancing. 2. DVFS. 3. Energy Efficiency. I. Navaux, Philippe Olivier Alexandre. II. Méhaut, Jean-François. III. Título.

#### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos Alexandre Netto Vice-Reitor: Prof. Rui Vicente Oppermann

Pró-Reitor de Pós-Graduação: Prof. Vladimir Pinheiro do Nascimento

Diretor do Instituto de Informática: Prof. Luis da Cunha Lamb

Coordenador do PPGC: Prof. Luigi Carro

Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

#### **ACKNOWLEDGMENTS**

First, I would like to thank my advisor Philippe Olivier Alexandre Navaux for having accepted me as his PhD. student. For all the ideas and motivation during this PhD period. Thank, also by opportunities, meetings, conferences and projects and mainly by encouraging the internship in France where I had the opportunity to work in LIG team. I also would like to thank sandwich-advisor Jean-François Méhaut, for all suggestions and by scientific support on our work research.

The CAPES-Brazil through PDSE program that sponsored my internship abroad and French-Brazilian HPC-GA project that provided opportunity for travelling attending meetings and conferences.

I would like to all friends and colleagues members of the GPPD and LIG research teams by their support and help during the PhD. A main and special thanks to all of my family by comprehension and patience in my absence: thank you for understanding and supporting me.

#### **ABSTRACT**

Current HPC systems have made more complex simulations feasible, yielding benefits to several research areas. To meet the increasing processing demands of these simulations, new equipment is being designed, aiming at the exaflops scale. A major challenge for building these systems is the power that they will require, which current perspectives reach the GigaWatts. To address this problem, this thesis presents an approach to increase the energy efficiency using of HPC resources, aiming to reduce the effects of load imbalance to save energy.

We developed an energy-aware strategy, called ENERGYLB, which considers platform characteristics, and the load irregularity and dynamicity of the applications to improve the energy efficiency. Our strategy takes into account the current computational load and clock frequency, to decide whether to call a load balancing strategy that reduces load imbalance by migrating tasks, or use Dynamic Voltage and Frequency Scaling (DVFS) technique to adjust the clock frequencies of the cores according to their weighted loads. As different processor architectures can feature two levels of DVFS granularity, per-chip DVFS or per-core DVFS, we created two different algorithms for our strategy. The first one, FG-ENERGYLB, allows a fine control of the clock frequency of cores in systems that have few tens of cores and feature per-core DVFS control. On the other hand, CG-ENERGYLB is suitable for HPC platforms composed of several multicore processors that do not allow such a fine-grained control, i.e., that only perform per-chip DVFS. Both approaches exploit residual imbalances on iterative applications and combine dynamic load balancing with DVFS techniques. Thus, they reduce the clock frequency of underloaded computing cores, which experience some residual imbalance even after tasks are remapped.

We evaluate the applicability of our approaches using the CHARM++ parallel programming system over benchmarks and real world applications. Experimental results present improvements in energy consumption and power demand over state-of-the-art algorithms. The energy savings with ENERGYLB used alone were up to 25% with our FG-ENERGYLB algorithm, and up to 27% with our CG-ENERGYLB algorithm. Nevertheless, residual imbalances were still present after tasks were remapped. In this case, when our approaches were employed together with these load balancers, an improvement in energy savings of up to 56% is achieved with FG-ENERGYLB and up to 36% with CG-ENERGYLB. These savings were obtained by exploiting residual imbalances on iterative applications.

By combining dynamic load balancing with the DVFS technique, our approach is able to reduce the average power demand of parallel systems, reduce the task migration among

the available resources, and keep load balancing overheads low.

Keywords: Load Balancing. DVFS. Energy Efficiency.

# Abordagens de Balanceamento de Carga ciente de energia para melhorar a eficiência energética em sistemas HPC

#### **RESUMO**

Os atuais sistemas de HPC tem realizado simulações mais complexas possíveis, produzindo benefícios para diversas áreas de pesquisa. Para atender à crescente demanda de processamento dessas simulações, novos equipamentos estão sendo projetados, visando à escala exaflops. Um grande desafio para a construção destes sistemas é a potência que eles vão demandar, onde perspectivas atuais alcançam GigaWatts. Para resolver este problema, esta tese apresenta uma abordagem para aumentar a eficiência energética usando recursos de HPC, objetivando reduzir os efeitos do desequilíbrio de carga e economizar energia. Nós desenvolvemos uma estratégia baseada no consumo de energia, chamada ENERGYLB, que considera características da plataforma, irregularidade e dinamicidade de carga das aplicações para melhorar a eficiência energética. Nossa estratégia leva em conta carga computacional atual e a frequência de clock dos cores, para decidir entre chamar uma estratégia de balanceamento de carga que reduz o desequilíbrio de carga migrando tarefas, ou usar técnicas de DVFS par ajustar as frequências de clock dos cores de acordo com suas cargas computacionais ponderadas. Como as diferentes arquiteturas de processador podem apresentam dois níveis de granularidade de DVFS, DVFS-por-chip ou DVFS-por-core, nós criamos dois diferentes algoritmos para a nossa estratégia. O primeiro, FG-ENERGYLB, permite um controle fino da frequência dos cores em sistemas que possuem algumas dezenas de cores e implementam DVFS-por-core. Por outro lado, CG-ENERGYLB é adequado para plataformas de HPC composto de vários processadores multicore que não permitem tal refinado controle, ou seja, que só executam DVFS-por-chip. Ambas as abordagens exploram desbalanceamentos residuais em aplicações interativas e combinam balanceamento de carga dinâmico com técnicas de DVFS. Assim, eles reduzem a frequência de clock dos cores com menor carga computacional os quais apresentam algum desequilíbrio residual mesmo após as tarefas serem remapeadas. Nós avaliamos a aplicabilidade das nossas abordagens utilizando o ambiente de programação paralela CHARM++ sobre benchmarks e aplicações reais. Resultados experimentais presentaram melhorias no consumo de energia e na demanda potência sobre algoritmos do estado-da-arte. A economia de energia com ENERGYLB usado sozinho foi de até 25% com nosso algoritmo FG-ENERGYLB, e de até 27% com nosso algoritmo CG-ENERGYLB. No entanto, os desequilíbrios residuais ainda estavam presentes após as serem tarefas remapeadas. Neste caso, quando as nossas abordagens foram empregadas em conjunto com outros balanceadores de carga, uma melhoria na economia de energia de até 56% é obtida com FG-ENERGYLB e de até 36% com CG-ENERGYLB. Estas economias foram obtidas através da exploração do desbalanceamento residual em aplicações interativas. Combinando balanceamento de carga dinâmico com DVFS nossa estratégia é capaz de reduzir a demanda de potência média dos sistemas paralelos, reduzir a migração de tarefas entre os recursos disponíveis, e manter o custo de balanceamento de carga baixo.

Palavras-chave: Balanceamento de Carga, DVFS, Eficiência Energética.

#### LIST OF ABBREVIATIONS AND ACRONYMS

AMPI Adaptive Message Passing Interface

API Application Programming Interface

APM Advanced Power Management

ARM Advanced RISC Machine

BMC Baseboard Management Controller

BRAMS Brazilian developments on the Regional Atmospheric Modeling System

BRGM Bureau de Recherches Géologiques et Minières

CFD Computational Fluid Dynamics

ChaNGa Charm N-body GrAvity

DARPA Defense Advanced Research Projects Agency

DVFS Dynamic Voltage and Frequency Scaling

EDP Energy-Delay Product

FEM Finite Element Method

FLOPS Floating-Point Operation per Second

FVM Finite Volume Methods

GPU Graphics Processing Unit

HPC High Performance Computing

HPCGA High Performance Computing for Geophysics Applications

HPL High Performance Linpack

IPMI Intelligent Platform Management Interface

JLESC Joint Laboratory for Exascale Computing

LICIA Laboratoire International en Calcul Intensif et Informatique Ambiante

LIG Laboratoire d'Informatique de Grenoble

MSR Model-Specific Registers

NAMD NAnoscale Molecular Dynamics

NUMA Non-Uniform Memory Access

PAPI Performance API

PCU Power Control Unit

PDP Power-Delay Product

PPL Parallel Programming Laboratory

PSU Power Supply Unit

RAMS Regional Atmospheric Modeling System

RAPL Running Average Power Limit

RISC Reduced Instruction Set Computer

RTS RunTime System

TCO Total Cost of Ownership

## LIST OF FIGURES

| Figure 1.1 Instantaneous power demand in different scenarios.                                                                                          | .20 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 1.2 Accumulated processor occupation measured during execution of the application using GREEDYLB load balancer with different processors counts | 20  |

| application using GREEDTED load balancer with different processors counts                                                                              | .20 |

|                                                                                                                                                        | 27  |

| Figure 2.2 Application dynamicity                                                                                                                      | 29  |

| Figure 4.1 Overview of the fine-grained algorithm                                                                                                      |     |

| Figure 4.2 Overview of the coarse-grained algorithm.                                                                                                   |     |

| Figure 4.3 ENERGYLB implementation.                                                                                                                    | .70 |

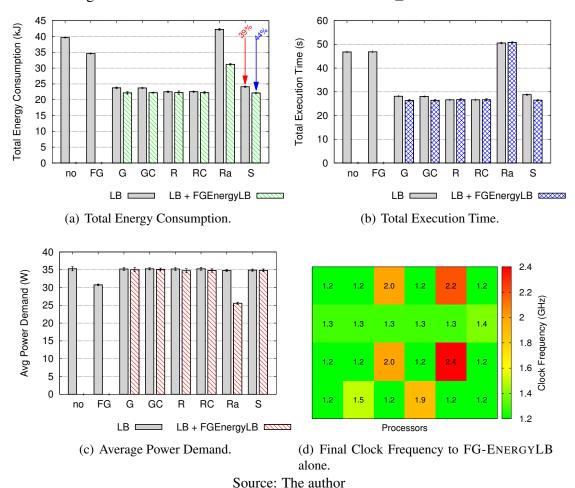

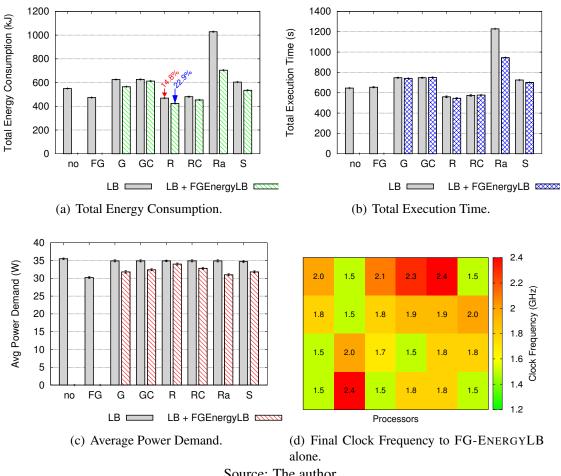

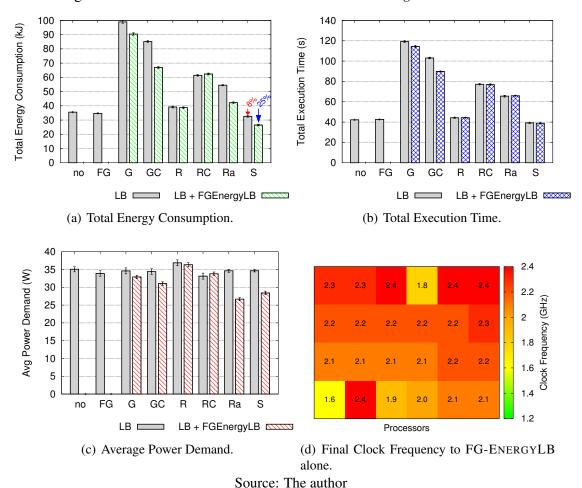

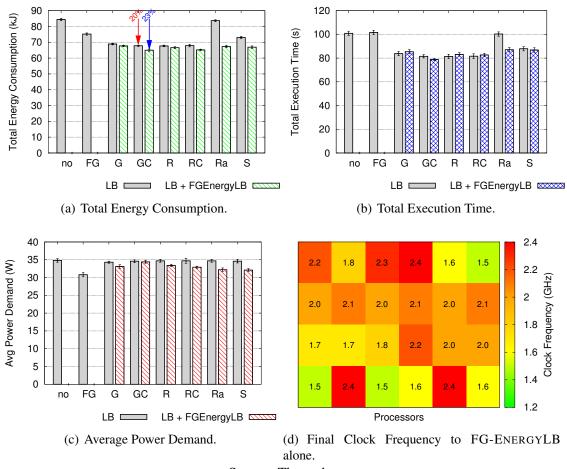

| Figure 5.1 Evaluation of FG-ENERGYLB with <i>lb_test</i> benchmark                                                                                     | .81 |

| Figure 5.2 Instantaneous power measured during execution of the imbalanced <i>lb_test</i>                                                              |     |

| benchmark using different load balancers.                                                                                                              | 83  |

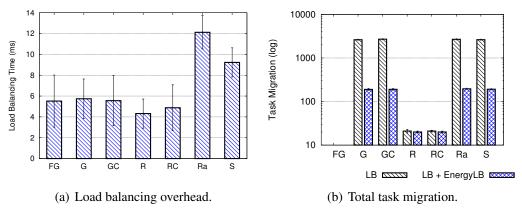

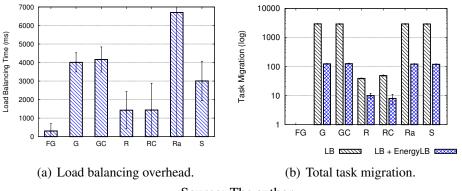

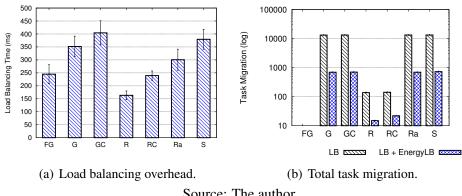

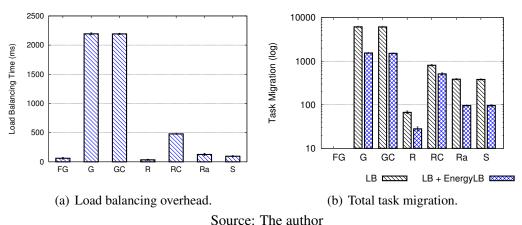

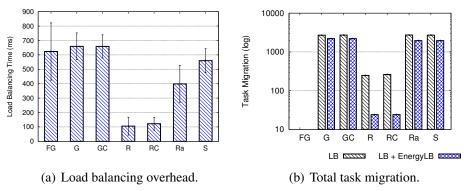

| Figure 5.3 Load balancing overhead and total task migration to <i>lb_test</i> with differ-                                                             | 0.6 |

| ent load balancers                                                                                                                                     |     |

| Figure 5.4 Evaluation of FG-ENERGYLB with <i>ComprehensiveBench</i> benchmark                                                                          |     |

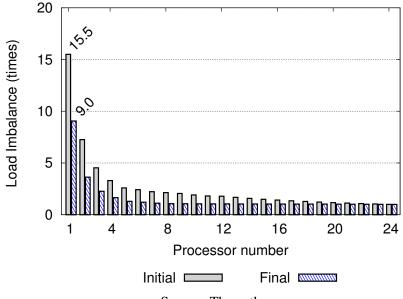

| Figure 5.5 Load imbalance relation between processors at initial and final execution                                                                   |     |

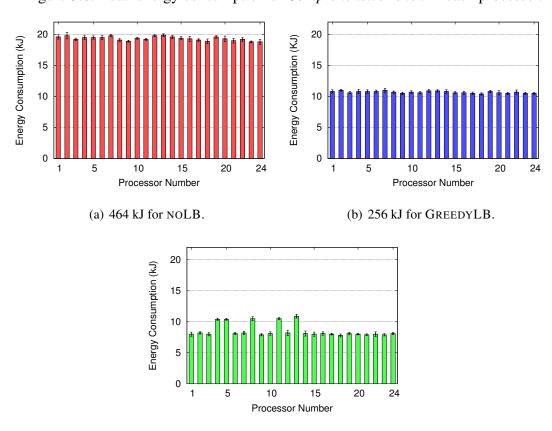

| Figure 5.6 Total energy consumption of ComprehensiveBench in each processor                                                                            |     |

| Figure 5.7 Evaluation of FG-ENERGYLB with <i>Ondes3D</i> application                                                                                   | 92  |

| Frequency for <i>Ondes3D</i> when used FG-ENERGYLB alone                                                                                               | 03  |

| Figure 5.9 Load balancing overhead and Total task migration to <i>Ondes3D</i> with                                                                     | .93 |

| different load balancers.                                                                                                                              | 93  |

| Figure 5.10 Evaluation of FG-ENERGYLB with <i>Lulesh</i> application                                                                                   |     |

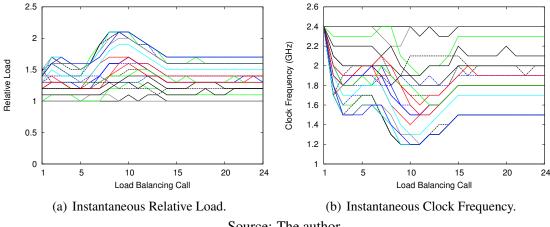

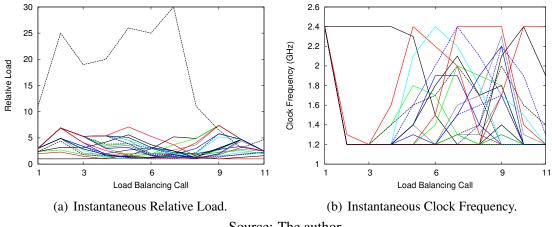

| Figure 5.11 Comparison of Instantaneous Relative Load with Instantaneous Clock                                                                         | • , |

| Frequency for <i>Lulesh</i> when used FG-ENERGYLB alone.                                                                                               | 95  |

| Figure 5.12 Load balancing overhead and Total task migration to <i>Lulesh</i> with dif-                                                                |     |

| ferent load balancers.                                                                                                                                 | 96  |

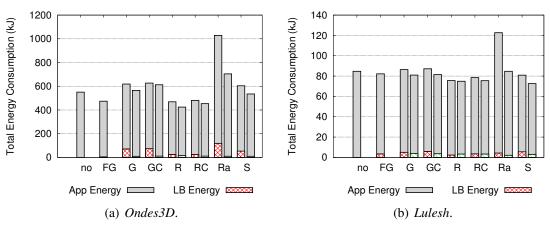

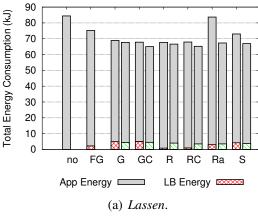

| Figure 5.13 Energy spend with load balancing over total energy consumption for                                                                         |     |

| each real application.                                                                                                                                 | 97  |

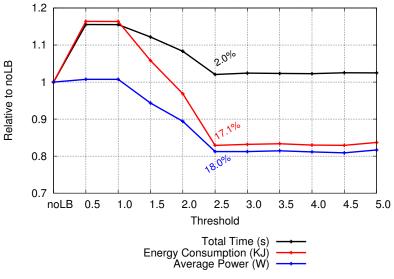

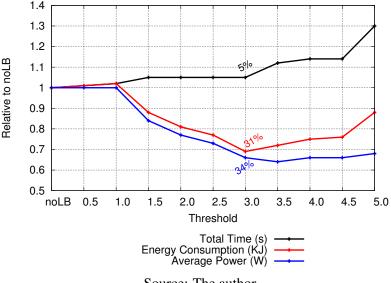

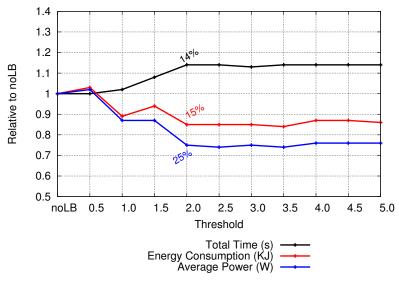

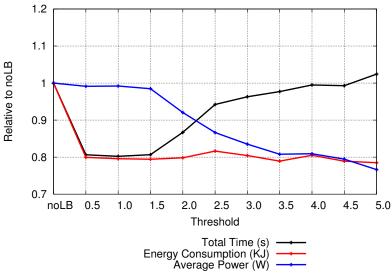

| Figure 5.14 FG-ENERGYLB comparison with different threshold value on <i>Ondes3D</i> .                                                                  | 100 |

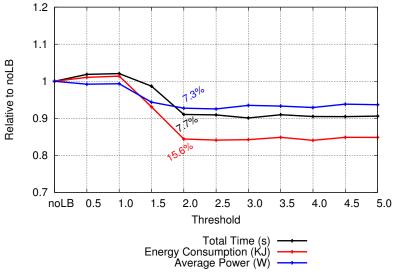

| Figure 5.15 FG-ENERGYLB comparison with different threshold value on Lulesh                                                                            |     |

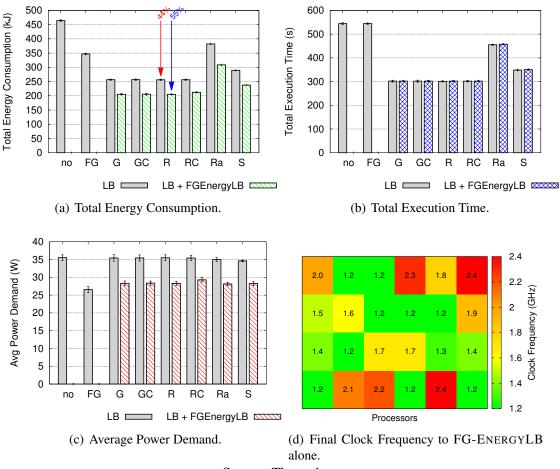

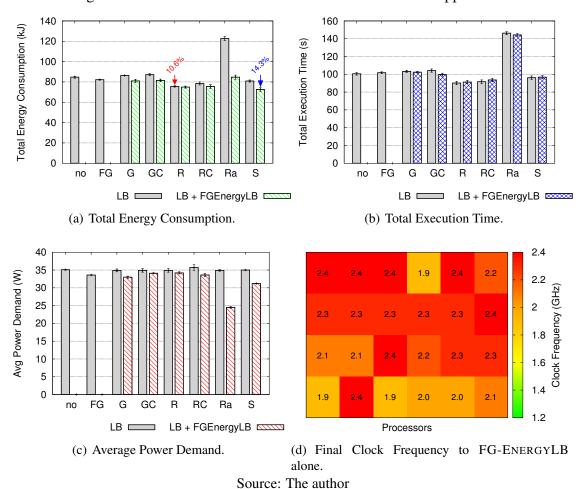

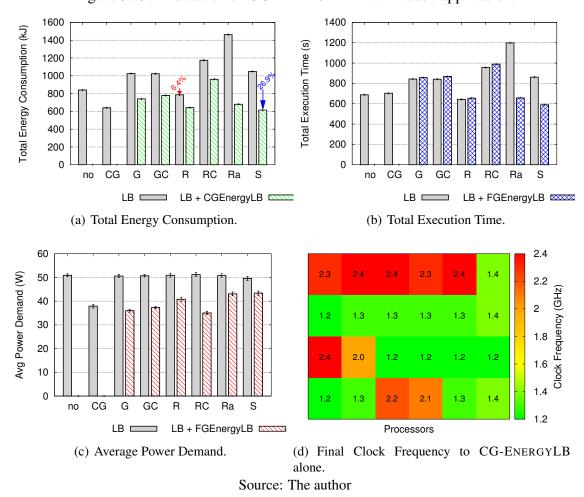

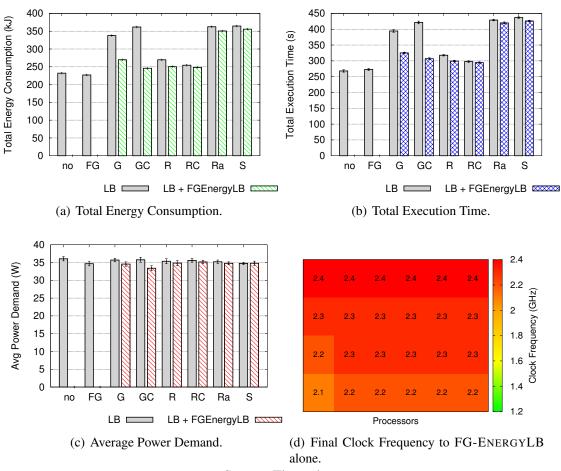

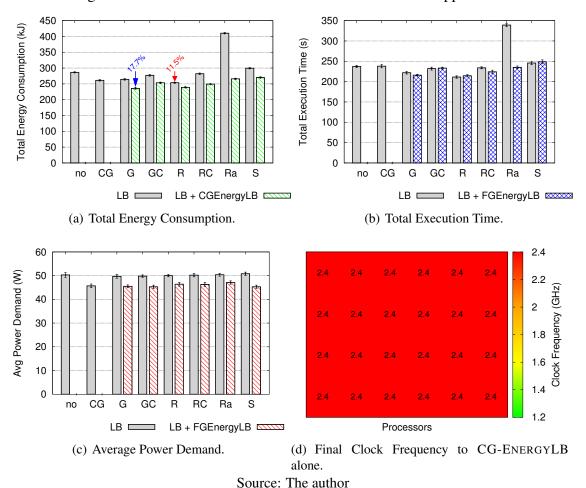

| Figure 5.16 Evaluation of CG-ENERGYLB with <i>Ondes3D</i> application                                                                                  | 104 |

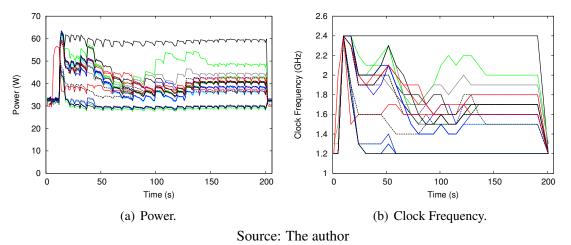

| Figure 5.17 Instantaneous power demand and clock frequency measured during the                                                                         |     |

| execution of <i>Ondes3D</i> with CG-ENERGYLB.                                                                                                          |     |

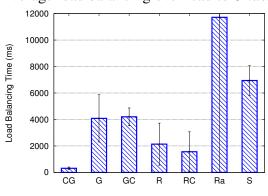

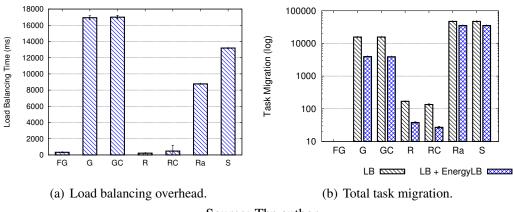

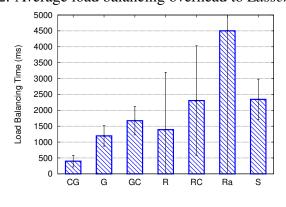

| Figure 5.18 Average load balancing overhead to <i>Ondes3D</i> application                                                                              |     |

| Figure 5.19 Evaluation of CG-ENERGYLB with <i>Lulesh</i> application.                                                                                  |     |

| Figure 5.20 Average load balancing overhead to <i>Lulesh</i> application                                                                               | 110 |

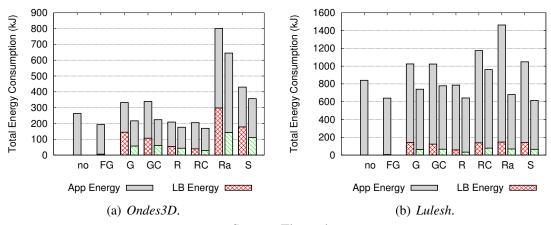

| Figure 5.21 Energy spend with load balancing over total energy consumption for                                                                         | 111 |

| each real application.                                                                                                                                 | 111 |

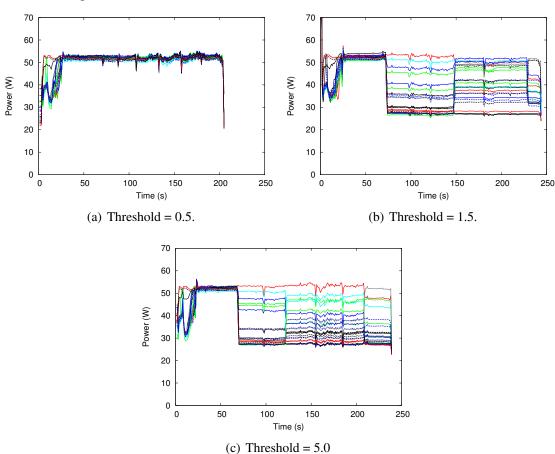

| Figure 5.22 CG-ENERGYLB comparison with different threshold value on <i>Ondes3D</i> .                                                                  |     |

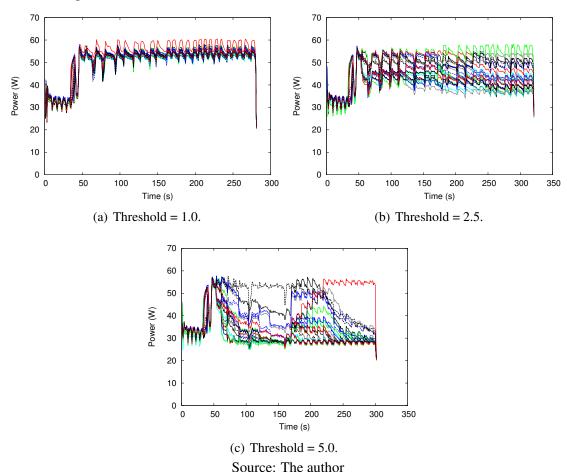

| Figure 5.23 Power evaluation to different threshold value on <i>Ondes3D</i>                                                                            |     |

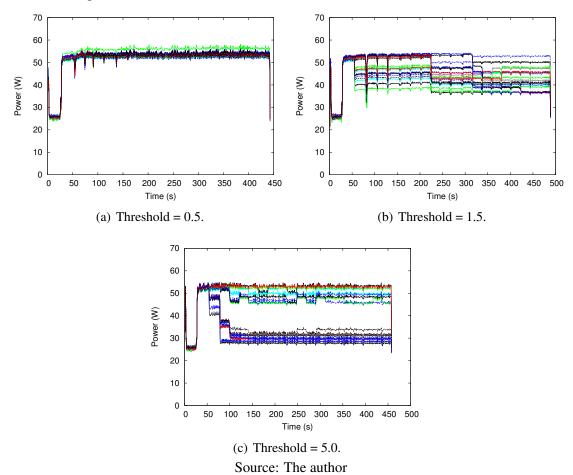

| Figure 5.24 CG-ENERGYLB comparison with different threshold value on <i>Lulesh</i>                                                                     |     |

| Figure 5.25 Power evaluation to different threshold value on <i>Lulesh</i>                                                                             | 113 |

| Figure A.1 Evaluation of FG-ENERGYLB with <i>kNeighbor</i> benchmark                                                                                   | 137 |

| Figure A.2 Load balancing overhead and Total task migration to <i>kNeighbor</i> load                                                                   |     |

| balancer with different load balancers.                                                                                                                | 138 |

| Figure A.3 | Evaluation of FG-ENERGYLB with stencil 4D benchmark                  | .140 |

|------------|----------------------------------------------------------------------|------|

| Figure A.4 | Load balancing overhead and Total task migration to stencil 4D load  |      |

| balan      | cer with different load balancers.                                   | .141 |

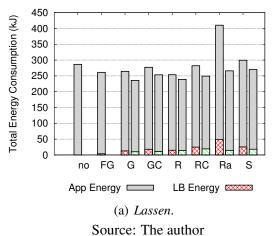

| Figure A.5 | Evaluation of FG-ENERGYLB with Lassen application                    | .144 |

| Figure A.6 | Comparison of Instantaneous Relative Load with Instantaneous Clock   |      |

| Frequ      | ency for Lassen when used FG-ENERGYLB alone                          | .145 |

| Figure A.7 | Load balancing overhead and Total task migration to Lassen with dif- |      |

| ferent     | load balancers                                                       | .146 |

| Figure A.8 | Energy spend with load balancing over total energy consumption for   |      |

| each i     | real application                                                     | .147 |

| Figure A.9 | FG-ENERGYLB comparison with different threshold value on Lassen      | .148 |

| Figure D 1 | Evaluation of CG-ENERGYLB with <i>Lassen</i> application             | 140  |

| _          | 11                                                                   |      |

| Figure B.2 | Average load balancing overhead to Lassen application                | .150 |

| Figure B.3 | Energy spend with load balancing over total energy consumption for   |      |

| each 1     | real application                                                     | .152 |

| Figure B.4 | CG-ENERGYLB comparison with different threshold value on Lassen      | .153 |

| Figure B.5 | Power evaluation to different threshold value on Lassen              | .153 |

## LIST OF TABLES

| Table 2.1 | Examples of scientific application and dynamicity.                       | 32 |

|-----------|--------------------------------------------------------------------------|----|

|           | Strategies characteristics.                                              |    |

|           | Load balancing algorithms comparison in terms of make decision criteria  |    |

| Table 3.1 | DVFS strategies comparison in terms of applicability.                    | 59 |

| Table 4.1 | Description of variables used in algorithms.                             | 63 |

| Table 4.2 | Comparison of the proposed algorithms with the state of the art in terms |    |

| of de     | cision criteria                                                          | 74 |

| Table 5.1 | Benchmarks and real world applications characteristics                   | 78 |

| Table 5.2 | Summary of the input parameters of benchmarks and real applications      | 79 |

| Table 5.3 | List of load balancers abbreviations used in the presentation of results | 80 |

| Table 5.4 | Total execution time, energy consumption and average power demand        |    |

| meas      | sured to <i>lb_test</i> benchmark                                        | 84 |

| Table 5.5 | Average load balancing duration in seconds for each real application     | 97 |

| Table 5.6 | Summary of the input parameters of real applications1                    | 03 |

| Table 5.7 | Total energy consumption and improvements for CG-ENERGYLB and            |    |

| other     | load balancers1                                                          | 06 |

| Table 5.8 | Average load balancing duration in seconds for each real application 1   | 11 |

| Table A.1 | Average load balancing duration in milliseconds for each benchmark1      | 42 |

| Table A.2 | Percentage of energy spend with load balancing over the total energy     |    |

| cons      | umption for each benchmark1                                              | 43 |

| Table A.3 | Average load balancing duration in seconds for each real application1    | 46 |

| Table A.4 | Percentage of energy spend with load balancing over the total energy     |    |

| cons      | umption for each real application1                                       | 47 |

|           | Average load balancing duration in seconds for each real application1    | 51 |

| Table B.2 | Percentage of energy spend with load balancing over the total energy     |    |

| cons      | umption for each real application1                                       | 52 |

|           |                                                                          |    |

# CONTENTS

| 1 INTRODUCTION                                                         | 16 |

|------------------------------------------------------------------------|----|

| 1.1 Problem Statement and Motivation                                   | 18 |

| 1.2 Objectives and Contributions                                       | 21 |

| 1.3 Scientific Context                                                 | 22 |

| 1.4 Text Organization                                                  |    |

| 2 LOAD BALANCING OVERVIEW                                              |    |

| 2.1 Characterization of Computational Load                             | 25 |

| 2.1.1 Scientific Applications                                          | 26 |

| 2.1.1.1 Regular and Irregular Applications                             |    |

| 2.1.1.2 Static and Dynamic Applications                                | 28 |

| 2.1.1.3 Iterative and Non-Iterative Applications                       | 28 |

| 2.1.2 Scientific Application Classes                                   | 29 |

| 2.2 Load Balancing Heuristics                                          | 32 |

| 2.2.1 Load Balancing Decisions                                         | 33 |

| 2.3 Related Work on Load Balancing                                     |    |

| 2.3.1 Centralized Strategies                                           | 35 |

| 2.3.1.1 Basic Centralized Load Balancing Strategies                    | 36 |

| 2.3.1.2 Centralized Load Balancing Strategies using Communication Data |    |

| 2.3.1.3 Centralized Topology-Aware Load Balancing Strategies           |    |

| 2.3.1.4 Centralized Temperature-Aware Load Balancing Strategies        |    |

| 2.3.1.5 Centralized Energy-Aware Load Balancing Strategies             |    |

| 2.3.2 Distributed Strategies                                           | 40 |

| 2.3.2.1 Basic Distributed Load Balancing Strategies                    | 41 |

| 2.3.3 Hierarchical or Multi-Level Strategies                           |    |

| 2.3.3.1 Basic Hierarchical Load Balancing Strategies                   | 42 |

| 2.4 Discussion                                                         | 43 |

| 3 ENERGY CONSUMPTION OVERVIEW                                          | 46 |

| 3.1 Energy Consumption Metrics                                         | 47 |

| 3.1.1 Power Demand                                                     | 47 |

| 3.1.2 Energy Consumption                                               | 48 |

| 3.2 Energy Consumption Evaluation                                      |    |

| 3.2.1 Power and Energy Measurement                                     | 49 |

| 3.2.1.1 External Measurement                                           | 49 |

| 3.2.1.2 Integrated Measurement                                         | 50 |

| 3.3 Related Work on Frequency Scaling                                  |    |

| 3.3.1 Frequency Scaling on Idle Resources                              |    |

| 3.3.2 Frequency Scaling on Power or Energy Budget                      |    |

| 3.3.3 Frequency Scaling on Communication Periods                       |    |

| 3.3.4 Frequency Scaling on Kernel Governors                            |    |

| 3.3.5 Frequency Scaling on Performance Prediction                      |    |

| 3.4 Discussion                                                         |    |

| 4 PROPOSED ENERGY-AWARE LOAD BALANCERS                                 | 61 |

| 4.1 EnergyLB: Energy-Aware Load Balancing                              |    |

| 4.1.1 FG-ENERGYLB: Fine-Grained EnergyLB                               |    |

| 4.1.1.1 FG-ENERGYLB Algorithm                                          |    |

| 4.1.1.2 FG-ENERGYLB Algorithm Properties                               |    |

| 4.1.2 CG-ENERGYLB: Coarse-Grained EnergyLB                             |    |

| 4.1.2.1 CG-ENERGYLB Algorithm                                          |    |

| 4.1.2.2 CG-ENERGYLB Algorithm Properties             | 68  |

|------------------------------------------------------|-----|

| 4.2 Implementation Details                           | 68  |

| 4.2.1 CHARM++ Parallel Programming                   | 69  |

| 4.2.2 Energy Modules                                 | 70  |

| 4.2.3 ENERGYLB Phases                                | 71  |

| 4.3 Discussion                                       |     |

| 5 LOAD BALANCERS EVALUATION                          | 75  |

| 5.1 Evaluation Methodology                           |     |

| 5.1.1 Experimental Environment                       |     |

| 5.1.2 Benchmarks and Irregular Applications          | 76  |

| 5.1.3 Load Balancers                                 | 78  |

| 5.1.4 Power and Energy Monitoring                    | 78  |

| 5.1.5 Test Execution Details                         | 79  |

| 5.2 FG-ENERGYLB Evaluation                           | 80  |

| 5.2.1 Evaluation on Benchmarks                       | 81  |

| 5.2.2 Evaluation on Real Applications                |     |

| 5.2.2.1 Percentage of Energy Spent on Load Balancing | 96  |

| 5.2.2.2 Threshold Evaluation                         | 98  |

| 5.3 CG-ENERGYLB Evaluation                           | 102 |

| 5.3.1 Evaluation on Real Applications                | 103 |

| 5.3.1.1 Percentage of Energy Spent on Load Balancing | 110 |

| 5.3.1.2 Threshold Evaluation                         | 112 |

| 5.4 Overall Results                                  |     |

| 6 CONCLUSIONS AND FUTURE WORK                        | 119 |

| 6.1 Contributions                                    |     |

| 6.2 Perspectives of Future Work                      |     |

| 6.3 Published Papers                                 | 122 |

| REFERENCES                                           | 125 |

| APPENDIX A — FG-ENERGYLB EVALUATION                  |     |

| A.1 Evaluation on Benchmarks                         | 137 |

| A.1.1 Percentage of Energy Spent on Load Balancing   | 141 |

| A.2 Evaluation on Real Applications                  |     |

| APPENDIX B — CG-ENERGYLB EVALUATION                  | 149 |

| B.1 Evaluation on Real Applications                  | 149 |

#### 1 INTRODUCTION

Parallel scientific applications have been influencing the way science is done for decades. These applications have ever-increasing demands in terms of performance and resources, due to their great complexity and large data-sets. In order to meet these demands, the performance of High Performance Computing (HPC) platforms has been growing exponentially for years (LAROS et al., 2009; DONG; CHEN; TANG, 2010).

Current PFlops (10<sup>15</sup> floating point operation per second) systems allow reaching increasingly accurate results for several scientific applications, such as climate modeling, oil exploration and atomic simulation. However, this exponential increase in computational performance also leads to an exponential growth in power demand, i.e., the rate of power (watt) consumed directly of a power supply (HSU; FENG, 2005; LAROS et al., 2009; DONG; CHEN; TANG, 2010; ALVES et al., 2010; PADOIN et al., 2013a).

The main focus of HPC systems has been performance, and today the HPC community works toward building Exascale systems (i.e., EFlops), which will provide unprecedented computational power, allowing to solve even larger scientific problems. Conceiving Exascale supercomputers by scaling the current technology, these systems could demand over a GigaWatt of power (HSU; FENG; ARCHULETA, 2005; FENG; CAMERON, 2007), which is equivalent to the entire production of a medium size nuclear power plant (WEHNER; OLIKER; SHALF, 2009). In this way, a global research effort has risen to try to break this barrier while avoiding such high power demands, since the electric company must provide to customers this power when they turn the equipment on.

In recent decades, supercomputers were compared almost exclusively by their computing performance, also defined by runtime or total execution time, as in the context of this thesis. For instance, the Top500 list was established to rank supercomputers regarding processing speed (DONGARRA; MEUER; STROHMAIER, 2014). Nonetheless, given the exponential growth in power demand of HPC systems (LAROS et al., 2009; DONG; CHEN; TANG, 2010), and responding to the energy efficiency problem, the HPC community started new initiatives that take into account both performance and power demand (REN; SUDA, 2010). An example is the Green500 list. It considers the ratio between performance and power (Flops/W) to define the energy efficiency of parallel machines (GE et al., 2007; FENG; LIN, 2010; SUBRAMANIAM; FENG, 2010; CAMERON, 2010; SCOGLAND; SUBRAMANIAM; FENG, 2012).

In this context, the first challenge to the development of energy efficient HPC

systems and applications lies on increasing their performance while reducing their power demand. Indeed, reducing power demand and saving energy have become one of the main concerns of the HPC community. Thus, to build future systems we need to take into account power demand and energy consumption constraints and ways to improve energy efficiency (BARKER et al., 2009; YOUNGE et al., 2010; PADOIN et al., 2013b; PADOIN et al., 2014). In this context, current processors have incorporated solutions to improve energy efficiency. Some processor models have temperature sensors to avoid overheating and reduce cooling costs. Others also feature mechanisms that allow controlling voltage through Dynamic Voltage and Frequency Scaling (DVFS). By using DVFS, the processor's clock frequency can be reduced and, consequently, reduces its instantaneous power demand and the total energy consumption. However, this reduction in processor's clock frequency also causes a reduction on application performance.

To attend to the increasing demand for processing, a second challenge arises when HPC systems grow in number of processors. This complicates the efficient use of all resources at the hardware level. To run scientific applications on these complex parallel systems, the application's work (or computing load) is divided into tasks or processes. However, as the computational load of a scientific applications may not be equally divided due to dynamic or irregular characteristics, the application may be executed and end up with an imbalanced load. These characteristics are present in several scientific applications and contributes to a reduced energy efficiency on parallel systems, since the most heavily loaded processor determines the application's performance. Several load balancing strategies have been used to improve the load distribution across processors and to achieve an efficient use of all available resources of a parallel machine. However, these strategies work with a NP-Hard problem, doing exhaustive searches and can take processing time and may even degrade the performance if they are not well applied (LEUNG, 2004; BRUCKER; BRUCKER, 2007).

Therefore, the challenge of designing more energy efficient applications is to improve the use of all hardware resources available in the parallel systems, providing near optimal performance for applications and at the same time improve the energy efficiency of the systems. This pursuit is also motivated by the current energy cost of HPC systems. Some supercomputers demand more than 10 MW of power, which costs several million dollars per year in energy, i.e., the power demand integrated over a specified time period. Beyond that, it generates emissions of millions metric tons of carbon dioxide. Furthermore, the total cost of equipment maintenance, will overcome in a few years the cost

of the hardware infrastructure acquisition (TORRELLAS, 2009; STEIGERWALD et al., 2011; PERAZA et al., 2013; RAJOVIC et al., 2014).

In this context, state-of-the-art research focuses on either power demand or load balancing strategies separately. Several proposal have used DVFS, however this technique may cause performance degradation and an increase of the total execution time of parallel applications. Other proposals have used load balancing strategies to reduce the overall execution time, and, consequently, save energy. However, these strategies have used only computational load ignoring power demand or total energy consumption.

In the context of this thesis, we improve the energy efficiency of parallel systems when running load imbalanced applications. We provide new load balancing strategies that collect system information from each node of the parallel machine and collect information from tasks of the application, in order to take decision more accurately and to manage power demand while the imbalanced application is running. Our approach combines dynamic load balancing with the DVFS technique in order to reduce the clock frequency of underloaded cores, which have some residual imbalance.

#### 1.1 Problem Statement and Motivation

Several scientific applications take advantage of the parallelism offered by large HPC systems to simulate different natural phenomena. However, to satisfy their increasing processing demand, we end up increasing the power demand of these systems. This is an issue, since they have reached near of the limit specified by DARPA report (KOGGE et al., 2008).

Taking into account power constraints, issues such as power demand and energy consumption are increasingly discussed in the HPC community. Nowadays, the energy efficiency of parallel systems is a major challenge in scientific research. In this context, our research problem is to efficiently use all hardware resources available in parallel machines to provide the best performance possible and, at the same time, reduce the power demand to improve the energy efficiency of parallel HPC systems.

Generally, approaches to reduce the power demand are used separately of research for increasing application's performance. Several approaches have been applied to mitigate the imbalanced workloads and achieve an efficient use of all parallel resources. However, most of these approaches focus on reducing the execution time of the applications by improving the load distribution, but neglecting power consumption. Other approaches

have used power controls of current microarchitectures to change the voltage level, reducing then their operating frequency and saving power, without taking into account the load distribution.

Load balancing strategies exploit the load imbalances of tasks and achieve reductions in the total execution time. These reductions are relevant in the perspective of energy consumption, since energy is saved when hardware resources are used for a shorter time. However, some imbalance may still remain after making decisions and task migrations. In this thesis, we call this remaining load imbalance left by the load balancers of *residual imbalance*. In this context, it is possible to achieve even greater energy savings if the runtime system is able to exploit the residual imbalances to fine tune the voltage and frequency of cores accordingly. In this case, the challenge lies in reducing the energy consumption of the application while maintaining its performance.

In this context, iterative imbalanced applications are potential candidates for energy consumption improvements. These parallel applications are present on different scientific fields. Molecular dynamics, structural dynamics, weather forecast (MICHALAKES; VACHHARAJANI, 2008), cosmological modeling simulation (DIKAIAKOS; STADEL, 1996; JETLEY et al., 2008), seismic wave propagation simulations (DUPROS et al., 2008), physics (SHIERS, 2007), and oil exploration (PANETTA et al., 2009), are examples of applications that can benefit from load balancing schemes to improve performance. Our proposal is that these schemes still leave space for energy optimization.

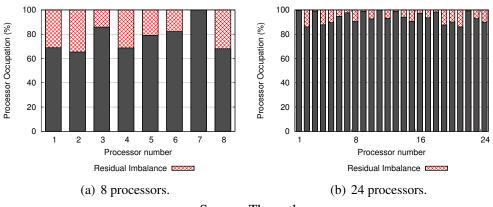

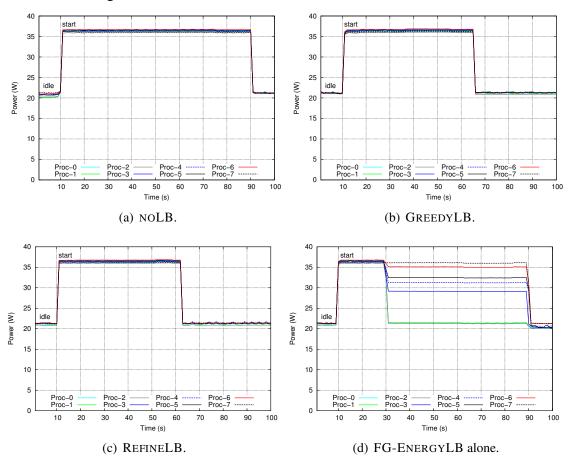

In an experimental evaluation, tests were performed using 8 and 24 cores (one on each processor) of the parallel machine presented in Section 5.1. We ran a small test with *Ondes3D* (DUPROS et al., 2008), a seismic wave simulation that uses the CHARM++ parallel programming framework (KALÉ; KRISHNAN, 1993; CHARM++, 2014). Figures 1.1 presents the power demand measured on 8 processors during the execution of the iterative application in different scenarios. In the first scenario (Figure 1.1(a)), the application executes a balanced workload, without any load balancer. In the second scenario (Figure 1.1(b)), the same workload is executed with GREEDYLB (KALÉ; KRISHNAN, 1993), a load balancer that uses a greedy approach further discussed in Section 5.1.3. As it can be observed, GREEDYLB had almost no effect on both execution time and power demand, since the workload is originally balanced.

In the third scenario the application executes an imbalanced workload (Figure 1.1(c)). In this case, GREEDYLB was able to improve the performance of the application, reducing its execution time by 22% when compared to the same workload without a load

load balancer.

Figure 1.1: Instantaneous power demand in different scenarios.

Source: The author

GREEDYLB.

balancer. We also observe that even though the power demand remained the same. It's important to observe that the application consumed less energy in this case, due to its shorter execution time.

(a) Balanced application without (b) Balanced application with (c) Imbalanced application with

GREEDYLB.

Load balancers improve the performance of imbalanced applications by making a better load distribution among the available processors. However, they can take sub optimal decisions, which may result in some load remaining imbalanced after task migrations. This may happen due to characteristics of the application that prevent a perfectly balanced mapping to be achieved, or due to limitations of the load balancing heuristics, as the problem that they are trying to solve is NP-Hard (LEUNG, 2004).

Figure 1.2: Accumulated processor occupation measured during execution of the application using GREEDYLB load balancer with different processors counts.

Source: The author

The accumulated occupation (usage percent) of each processor used during the execution of the application with GREEDYLB is shown in the Figure 1.2. When running the application in 8 processors a residual imbalance of up to 34% is achieved (Figure 1.2(a)). Using the same workload to each task and running the application in 24 processors, (Figure 1.2(b)), a different load distribution is achieved, where a residual imbalance of up to 14% is present. We notice that this residual imbalance is considerably high in several scenarios, for example, in irregular or dynamic applications, in which the processors are

underused. In scenarios like this, DVFS techniques can be used to reduce its frequency and, consequently its power demand to save energy.

Based on the state-of-the-art research that focuses on either increasing the application's performance or reducing its power demand, we make the case that both strategies, dynamic load balancing and DVFS, could be used together. Our hypothesis to achieve a better energy efficiency in parallel systems when running load imbalanced applications is that precise tasks and machine information can help load balancing algorithms in their decisions, in order to manage power demand considering residual imbalance while the application is running.

#### 1.2 Objectives and Contributions

The objective of this thesis is **to enhance the global load balancing distribution of applications, reduce the idleness and increase the energy efficiency of HPC systems using information about the load and power demand of processors.** We intend to unite two areas, dynamic load balancing and DVFS, following the hypothesis that system information, for example, processor occupation or residual imbalance of the parallel platform and load information of imbalanced applications can be used to improve the efficacy of load balancing strategies. Considering this objective, our main contributions are as follows:

• We introduce a new energy-aware load balancing algorithm called ENERGYLB, to save energy on iterative applications that present imbalanced loads. Our strategies can reduce the power demand during execution, saving energy and improving the application performance according to its load characteristic. We have implemented two algorithms for our proposed ENERGYLB, using the existing CHARM++ framework, which implements a model of migratable object. The first one, called *Fine-Grained EnergyLB* (FG-ENERGYLB), is suitable for platforms composed of few tens of cores and that allow per core DVFS. The second one, *Coarse-Grained EnergyLB* (CG-ENERGYLB), is suitable for platforms composed of several processors and that do not allow per core DVFS. Our approaches can be applied alone or attached to other load balancers to save energy. When it is used attached, in a first step, a load balancer runs its algorithm to achieve a better load distribution. After

- that, ENERGYLB computes the residual imbalance and adjusts the clock frequency according to residual load imbalance, to save energy (PADOIN et al., 2014).

- We evaluate our proposed approaches and demonstrate the improvements in performance and energy savings. For this purpose, we run a set of benchmarks and real world applications. The results were compared to other state-of-the-art algorithms and show a reduction in power demand and in the amount of the energy saving incurring in very low overhead (PADOIN et al., 2014).

- We proposed and developed a tool named **EMonDaemon** to collect power and energy consumption on homogeneous and heterogeneous systems. This contribution is motivated due to current platforms having different interfaces to collect power and energy data from different equipment or tools. In some of these tools, the collected data can be analyzed only after the execution of the application. This makes it difficult to correlate performance with power and energy consumption. Another difficulty is that some equipment have sensors that enable the measurement only of the processor with a low granularity, while others allow only the measurement of entire machine. For example, recent Intel Sandy-Bridge-EP processors have MSR registers that enable the measurement of the accumulated energy of each processor, core, RAM and/or GPU. On the other hand, MPSoCs like Odroid, feature processors and have sensors to measure the instantaneous power of each cluster. These power sensors, not present in older systems, make it possible to analyze energy consumption with a fine granularity. Our solution can be applied to measure performance, instantaneous power and energy consumption on heterogeneous systems with Intel and ARM big.LITTLE processors, correlating performance with power and energy consumption during runtime (PADOIN et al., 2015).

#### 1.3 Scientific Context

This research is being developed in the Institute of Informatics of the *Univer-sidade Federal do Rio Grande do Sul* (UFRGS) in cooperation with the *Laboratoire d'Informatique de Grenoble* (LIG) of the *Université Grenoble Alpes*. In the context of this thesis, the work has been conducted within two research groups. In UFRGS, the research has been developed in the Parallel and Distributed Processing Group (GPPD), and in LIG, during internship period, the research was conducted in the Nanosimulations and

Embedded Applications for Hybrid Multicore Architectures (NANOSIM) group.

As result of the cooperation and collaboration between the two research groups, an associate laboratory called of *Laboratoire International en Calcul Intensif et Informatique Ambiante* (LICIA) was created. Besides that, there was some cooperation of the two groups as part of the *High Performance Computing for Geophysics Applications* (HPC-GA) project. So, our research has benefited from the experience of researchers of the two groups and their common research areas, more specifically, dynamic load balancing algorithms, task migration, dynamic process control and scientific real world applications.

On dynamic load balancing algorithms, Pilla (PILLA et al., 2012; PILLA et al., 2014) developed load balancing algorithms that work at runtime level and combine application information about the machine topology gathered during execution. This approach improves the distribution of tasks over a parallel platform in order to mitigate load imbalance and costly communications.

Rodrigues (RODRIGUES et al., 2009; RODRIGUES et al., 2010) proposed a load balancing approach to reduce the execution time of applications by reducing the load imbalance and costly communications in a real world application, BRAMS. In same context, Tesser (TESSER et al., 2014b) evaluated the use of dynamic load balancing in CHARM++ to improve the performance of *Ondes3D*, a seismic wave propagation simulator developed by BRGM. *Ondes3D* was ported to AMPI and a performance evaluation was done using four load balancers available on CHARM++ and two topology aware load balancers, the NUCOLB (PILLA et al., 2012) and HWTOPOLB (PILLA et al., 2014), both strategies developed by Laércio L. Pilla.

Our work also has a collaboration with the Parallel Programming Laboratory (PPL) of the University of Illinois at Urbana-Champaign (UIUC) within the Joint Laboratory for Exascale Computing (JLESC) (PADOIN et al., 2014b) and (PADOIN et al., 2014a). This collaboration is very important to our research since we used CHARM++, the runtime system developed by PPL, to implement and test our proposed energy-aware load balancing algorithms. Besides that, the results were presented in 12th Workshop on Charm++ and its Applications (PADOIN et al., 2014c).

#### 1.4 Text Organization

The remaining chapters of this thesis are structured as follows:

- Chapter 2 reviews the basic concepts about load balancing strategies, which are relevant to this thesis. We discuss how the load balancing impacts the use the resources available in parallel machines, since it can interfere in the performance of parallel applications and on the energy consumption of entire system. We detail the behavior of parallel applications, characterize load balancing, and describe the most known strategies for load balancing. We also evaluate scientific applications in the context of load balancing;

- Chapter 3 presents a review of basic concepts and metrics to measure energy consumption, showing the quantities involved in the measurement that are relevant to the development of this thesis. In this context, we provide a discussion about energy evaluation. We also present a review of the state of the art, contextualizing the addressed issue, research and technological advances related to energy consumption;

- Chapter 4 proposes the Energy-Aware Load Balancer (ENERGYLB) to improve the

energy efficiency of parallel systems when running load imbalanced applications.

In this chapter, we described in detail our two proposed load balancing strategies,

divided into motivation and contribution. We also discuss algorithms and implementation details. Our approaches propose combining dynamic load balancing and

DVFS considering the characteristics of the application and of the system to make

decisions;

- Chapter 5 presents an experimental evaluation of our Energy-Aware Load Balancing approach. In this chapter, we discuss the methodology of the validation of our proposed load balancers. We present the parallel system, the benchmarks, the real world applications, and other available load balancers. These were used in a set of tests to measure the runtime, power demand and energy consumption improvements and compare them with our proposed strategies;

- Chapter 6 summarizes our conclusions and contributions as well as outlining perspectives for the future work;

- **Appendix A** presents an experimental evaluation of our Centralized Energy-Aware Load Balancer using benchmarks and real world applications; and

- **Appendix B** presents an experimental evaluation of our Hierarchical Energy-Aware Load Balancer using benchmarks and real world applications.

#### 2 LOAD BALANCING OVERVIEW

Applications has been distributed across all system processors aiming achieve high performance and attend the computational demands of scientific simulations. Since several applications suffer from load imbalance, which can reduce performance and scalability, the workload is partitioned according to specific load balancing strategies aiming efficiently use all parallel resources of HPC systems. Load imbalance also contributes to the inefficiency of parallel applications, since the runtime of an application is defined by the most loaded processor. Therefore, achieving a balanced load is one of the main issues to reach high performance, especially when dynamic and irregular problems are computed.

Load balancing (LB) strategies are techniques widely used to achieve a better distribution of tasks or computational load across processors of a parallel machine. They aim to reduce the load imbalance, avoid overloaded processors and decrease the contention in communication resources. Load balancing has been studied extensively, since it is present in several applications from different scientific fields. Therefore, scientific applications are potential candidates for performance improvements through load balancing. Several approaches and combinatorial algorithms that have been proposed to reduce the execution time focusing mainly in increasing resources usage at the hardware level.

In this chapter, we present the state of the art on load balancing strategies for scientific applications. We review the previous fundamental results related to the topic of this thesis. In the first section, we detail the main characteristics of computational load and scientific applications. Load balancing heuristics and load balancing categories are presented in Sections 2.2 and 2.3, respectively. Finally, we present the concluding remarks of this chapter, highlighting some points regarding the context of this thesis.

#### 2.1 Characterization of Computational Load

Parallel scientific applications have allowed addressing grand challenges in science. Scientific applications such as molecular dynamics simulations, natural phenomena forecast, seismic models and weather forecasting are run in HPC systems aiming at more accurate results and shorter execution times.

Research on the HPC field aims to provide faster supercomputer systems to run even bigger simulations creating a better understanding and predicting natural phenom-

ena. However, these applications are constantly increasing the amount of data to be processed aiming a higher precision, demanding a larger number of processing cores, and consuming large amounts of energy to run. To attend to this demand, supercomputers are scaling their performance exponentially over the years leading to an exponential growth in power demand (DONG; CHEN; TANG, 2010; GERARDS et al., 2014).

Furthermore, several scientific applications are complex and have tasks with different or dynamic computational loads that often result in load imbalance and poor scaling. Therefore, in order to determine if an application can benefit from load balancing strategies, their behavior needs to be analyzed.

In the context of this thesis, the load balancing problem can be defined as follows: given a parallel machine with a set of processors and the set of tasks of a parallel application, each task with its own computational load and communication needs, we want to find the mapping that best equalizes the tasks. An important issue for load balancing strategies is how to obtain the information about computation and communication, which will be used for making load balancing decisions. Another issue is that load balancing can incur in an increase in the overall execution time due the time spent on the load evaluation, decision making and task migration (WATTS; TAYLOR, 1998; CHARM++, 2014; TALLENT; ADHIANTO; MELLOR-CRUMMEY, 2010; PEARCE et al., 2012).

Currently, most load balancing strategies make decisions leaving aside the energy consumption of the computer system. Given the high power demand of current systems, however, the energy costs need to be taken into account during load balancing. In this scenario, there is a demand for load balancing strategies able to better manage and reduce the energy consumption of newer systems. An interesting approach would be to investigate the use of power demand information together with computational loads to guide scheduling decisions in order to increase the energy efficiency of parallel systems.

#### 2.1.1 Scientific Applications

Scientific applications have been used in simulations enabling research in several areas of knowledge. The computational load of large scientific applications are divided into a number of tasks to be processed in parallel by an HPC system. Depending of the programming language used, these tasks may be implemented as processes in MPI, threads in OpenMP, and active objects in CHARM++. However, this may not generate the expected performance gains, due to application characteristics, such as load imbalance

and excessive communication between tasks. To deal with such characteristics, these applications may require special strategies to make efficient use of all available resources.

In this context, load balancers can help to detect imbalance and to migrate tasks in order to redistribute the workload and enhance the use of computing resources.

In several applications, the computational load, also called *load* in this thesis context, cannot be equally divided. In this way, they can be ranked in two groups: Regular and Irregular Applications, as discussed in the subsection following.

#### 2.1.1.1 Regular and Irregular Applications

Regular applications are those whose tasks have similar execution times in a given application period. During the task creation, their computational load can be equally divided among all tasks. When running this type of application on an HPC system, it is easier to achieve a high processor occupation or resource usage, therefore reaching a higher computational efficiency at the hardware level. For applications with regular loads, static load balancing can easily reach an effective work distribution.

On the other hand, Irregular Applications are those whose computational load cannot be divided in a way that their tasks have similar loads. This is the case of many scientific applications and in addition, for many of these scientific applications, task loads cannot be predicted at start time. This way, it becomes harder to achieve a high processor occupation and an efficient use of the available resources. Furthermore, scaling these applications on current HPC systems is more complex, due to the increased difficulties in scheduling. Examples of irregular applications are state-space search, combinatorial optimization, and recursive parallel codes (LIFFLANDER; KRISHNAMOORTHY; KALÉ, 2012).

Figure 2.1 illustrates an example of regularity present in the computational load during the application's task creation.

Figure 2.1: Application regularity.

Load

(a) Regular Load.

(b) Irregular Load.

Source: The author

Other applications have a data-set, which can cause load variations during their execution, making it difficult to predict their behavior. Based on these characteristics, applications can be classified as Static and Dynamic Applications.

#### 2.1.1.2 Static and Dynamic Applications

Some applications have a computational load defined at creation time and it usually remains constant or static throughout the execution. Load balancing algorithms can be applied in these static applications to achieve a better performance using application information gathered during execution time (ICHIKAWA; YAMASHITA, 2000; LEGRAND et al., 2004; MARTÍNEZ et al., 2011; PILLA, 2014).

On the other hand, a significant number of applications have a behavior in which the computational load of tasks varies during execution, making it difficult to predict the load of their tasks. We call them dynamic applications. In this case, we say they have a dynamic load distribution.

Information gathered before execution is not important to load balancing algorithms when they are applied in dynamic applications. Their decisions take into account the current workload of each task periodically, every time a certain number of iterations has elapsed. This behavior is present in a large number of parallel scientific applications, making it even more difficult to run them on heterogeneous or non-dedicated systems (CYBENKO, 1989; HUMMEL et al., 1996; BAHI; CONTASSOT-VIVIER; COUTURIER, 2005; CARIÑO; BANICESCU, 2008; GALINDO; ALMEIDA; BADÍA-CONTELLES, 2008).

Figure 2.2 presents an example of dynamicity present in the computational load during the application's execution.

According to their regularity and dynamicity, scientific applications can also be classified as Iterative and Non-Iterative. We will discuss these two in the next subsection.

#### 2.1.1.3 Iterative and Non-Iterative Applications

Iterative applications are those where consecutive iterations have a similar behavior in computation load. That is, these iterations, also known as time steps, have a similar pattern of communication and computation, which can be used to make decisions in load balancing (MENON; KALÉ, 2013).

In iterative applications, the computational load of each task can be evaluated in

(a) Static Load.

(b) Dynamic Load.

Figure 2.2: Application dynamicity.

Source: The author

the first iterations and reevaluated every time a certain number of time steps is completed. This allows the current load to be used for predicting the future load. In these strategies, information about load and communication is usually saved in databases to later be used in load balancing decisions.

This kind of application is predominant in real world simulations. For instance, simulations of atoms moving in a structural molecular, NAnoscale Molecular Dynamics (NAMD) (PHILLIPS et al., 2002), climate or weather simulation, cosmological and seismic wave simulation are all examples of iterative applications.

Different from the first type, non-iterative applications do not have any correlation between time steps. This behavior is harder to predict. The difficult increases even more when some of these parallel applications create new tasks in runtime. Thus, creating new computational load and unbalancing the load of the whole system (ZHENG, 2005).

#### 2.1.2 Scientific Application Classes

We selected different classes of scientific applications and examples of applications to verify the regularity and dynamicity of their computational load and the communication. These classes are:

#### • Cosmological Simulations

The first class of scientific application we analyzed is cosmological simulations. Applications of this class have a unique communication pattern. For example, solvers used in gravitational simulations for the N-body problem generally use

methods such as hybrid codes, particle-mesh methods and tree-methods (BHATELÉ et al., 2011). Examples of cosmological simulations include Parallel K-D tree GRAVity code (PkdGRAV) (DIKAIAKOS; STADEL, 1996) and Charm N-body GrAvity solver (ChaNGa) (JETLEY et al., 2008).

PkdGRAV's code contains a data tree structured where the root-cell of this tree represents the entire simulation volume and ChaNGa's code represents N-body with boundary conditions of isolated stellar systems.

#### • Molecular Dynamics

The second class of scientific applications we selected is molecular dynamic (MD). These applications focus on the simulation of bio molecular systems involving the computation of forces on a system of N-atoms (BHATELÉ et al., 2011; MEI et al., 2011). Several parallel implementations have been developed for scaling MD codes on current HPC systems by dividing of atoms into cells. So, in each iteration, the force is computed for all pairs of atoms that are within a specified distance, resulting in a computational load proportional to the number of atoms in each cell. These algorithms are considered dynamic due to their load imbalance. This behavior is caused by the variable number of atoms in each cell and by movement of atoms between cells over time.

LeanMD is a scalable parallel application for MD that simulates the behavior of atoms based on the Lennard-Jones potential (PHILLIPS et al., 2002). The algorithm, implemented using the CHARM++ runtime system, performs a computation similar to the force calculation in NAnoscale Molecular Dynamics (NAMD) (NELSON et al., 1996; BHATELÉ; KALÉ; KUMAR, 2009; MENON; KALÉ, 2013).

#### • Seismic Wave Simulations

The third class of scientific applications we studied is seismic wave propagation models. Currently, these applications are one of the research topics on HPC due its high demand of processing power. Seismic wave applications can be used to simulate the propagation of waves in a region and predict the consequences of future earthquakes.

*Ondes3D* is an example of the seismic wave simulation class. Its algorithm was implemented using several different frameworks, including MPI and CHARM++ (TESSER et al., 2014b). Their main characteristics are the high memory consumption and processing cost. In addition, the data access pattern during the stages of the application that is regular (DUPROS et al., 2008).

#### • Unstructured Grid

Unstructured grid implementations have been one of the most efficient ways to solve large computational fluid dynamics (CFD) problems and are the fourth class we analyzed. Grid partitioning is a widely used method to decompose computational problems into parallel tasks. It is used mainly in applications where the computational load of the grid or the grid organization changes during the application's execution. The ability of dynamically organize the grid is attractive for increasing the usage of the available resource and achieving higher performance. In this case, dynamic load balancing techniques can be applied to partitioning of unstructured grids, aiming at improving the computational load balanced (BHATELÉ et al., 2011).

Finite Volume Methods (FVM) and Finite Element Methods (FEM) have been commonly employed to solve problems in this class. However, the cost of their data structures results in more complex implementation (HIRSCH, 2007).

#### • Weather Forecasting

Weather forecasting is another scientific applications class we analyzed. These applications are employed to predict the state of the atmosphere in a location at a specific time (MICHALAKES; VACHHARAJANI, 2008). Models such as the Regional Atmospheric Modeling System (RAMS) (WALKO et al., 2000), and its Brazilian variant, (BRAMS, 2011; RODRIGUES et al., 2010), are implemented by dividing the globe and the atmosphere into a three-dimensional mesh.

The computational load of these models is considered irregular with load imbalance. This happens because tasks may present different workloads depending on input data (MENON; KALÉ, 2013). Dynamicity in load is also present due to phenomena moving through the simulated area. The communication of this application class generally has a regular and static behavior, similar to seismic wave simulations (PILLA, 2014).

Table 2.1 summarizes some examples of the scientific applications according to the dynamicity of their computational load and communication, which some applications are used in thesis.

Table 2.1: Examples of scientific application and dynamicity.

| Class                    | Application | Load          | Communication |

|--------------------------|-------------|---------------|---------------|

| Cosmological Simulations | ChaNGa      | Dynamic       | Static        |

| Molecular Dynamics       | NAMD        | Dynamic       | Static        |

| Seismic Wave Simulations | Ondes3D     | Dynamic       | Static        |

| Unstructured Grid        | CFD         | Dynamic       | Dynamic       |

| Weather Forecasting      | RAMS        | Static mainly | Static        |

Source: The author

#### 2.2 Load Balancing Heuristics

Load imbalance is one of the challenge problems in parallel applications. Load imbalance is caused by a distribution of load that forces some processes to be idle between synchronizations (TALLENT; ADHIANTO; MELLOR-CRUMMEY, 2010). In this context, load balancing techniques are used to achieve a better computational load distribution, and to avoid load imbalance in parallel applications. Their main goal is to increase the resource utilization. This is usually achieved by avoiding processor overloading, and also mapping tasks in a way that decreases the communication cost.

Load balancing is considered a NP-Hard problem, due the application and platform characteristics and also due the hard solutions to achieve a balanced mapping (LE-UNG, 2004; EL-REWINI; ABD-EL-BARR, 2005; BRUCKER; BRUCKER, 2007).

For this reason, currently we have several different load balancing heuristics. These heuristics can use several kinds of information, being currently processor load the most used. Besides the load of the processor, heuristics can use the load of individual core, the processor speed, the memory hierarchy, communication costs, network topology and migration costs (CHARM++, 2014; EL-REWINI; ABD-EL-BARR, 2005).

Current load balancer strategies uses a relation to compute the load imbalance  $(L_t)$  present in the system (PEARCE et al., 2012; TALLENT; ADHIANTO; MELLOR-CRUMMEY, 2010). Most of them compute  $L_t$  as the ratio between the maximum load and average load, as presented in Equation 2.1:

$$L_{\iota} = \frac{L_{max}}{L_{ava}} - 1 \tag{2.1}$$

where  $L_{max}$  is the load of the most loaded processor, and  $L_{avg}$  is the average load of all the processors. So, periodically, the load balancer strategy obtains the load information and computes the load imbalance.

This equation is used in some load balancing strategies, since a parallel program only finishes its execution when the most loaded processor completes all its tasks. This way, the total execution time of an application is generally defined by the most loaded processor. This means that all other processors will remain waiting for it to complete its work. So,  $L_{max}$  represents the current execution time of the application. On the other hand,  $L_{avg}$  represents the ideal execution time of the application when the load of all processors is balanced (LEUNG, 2004).

In some parallel programming models, for example CHARM++, the load balancing is based on a heuristic known as the *principle of persistence* for iterative applications. This principle states that in some types of applications, the computational loads and communication patterns tend to persist over time, even in dynamically evolving computations. This behavior allows to use recent history as an indication for predicting load or communication in near future iterations (KALÉ, 2002; KALÉ; KRISHNAN, 1993; CHARM++, 2014; ZHENG et al., 2011; MENON et al., 2013). The principle of persistence is valid for a large class of iterative HPC applications (SAROOD; MENESES; KALÉ, 2013). It can be used as an automatic method to obtain load information without manually predicting the load (ZHENG et al., 2010; ZHENG et al., 2011).

#### 2.2.1 Load Balancing Decisions

Making the right load balancing decisions is one of the most important problems when trying to achieve an optimal load balance. However, making this decision generates overhead, since in each load balancing step is necessary to get the load information from all processors, make the decisions, and, if necessary, migrate the tasks between processors. Choosing the right interval between calls to the load balancer, is decisive to reduce the load balance overhead.

Some load balancing strategies run the algorithm to make decisions in periods of time specified previously by the user. However, if the strategy is performed very frequently, it may incur in a reduction of performance, because the load balancing overhead or also called load balancing times, may exceed its benefits. On the other hand, if the load balancer is invoked in long time periods, the load imbalance may increase too much and also result in loss of performance. So, even when the strategy detects that there is load imbalance,  $L_{\iota} > 0$ , according to Equation 2.1, it may not yet be useful to invoke the load balancer due to their own overhead.

Considering this, some current strategies are designed aiming at dynamicity. They analyze the application issues and the platform behavior to make decisions on runtime, without specified parameters. As a solution to decrease the load balancing overhead, several recent strategies have adopted a *threshold* to determine if load balancing must be performed or not. That is, the load balancing heuristics will only execute if  $L_{\iota} > threshold$ . Most current strategies use heuristics together with *threshold* to define the load imbalance.

Zheng (ZHENG et al., 2010; ZHENG et al., 2011) for example, uses a similar model to the one shown the Equation 2.1 to compute the load imbalance  $(L_t)$ . To define the *threshold* they have used a benchmark to create tasks (t) on available processors (p) where t > p.

In each load balancing invocation, the strategy gets load information of each task on every processor and defines the current load of the most overloaded processor. The current load before load balancing is called  $L_{max}$  and after load balancing is called as  $L'_{max}$ . This way, the *threshold* is defined as the gain from load balancing  $(L_{max} - L'_{max})$  in relation to the cost of load balancing  $(C_{lb})$ . So, the load balancer will only execute when:

$$gain(L_{max} - L'_{max}) > C_{lb}$$

(2.2)

This is, the load balancing strategy will only be executed when its estimated (the gains *threshold*) are higher than its estimated own execution time.

#### 2.3 Related Work on Load Balancing

Load balancing strategies can be classified into two categories. In the first category, the approaches are applied when new tasks are created in the applications. In these strategies, also called of task scheduling, the tasks are the basic unit of work for load balancing. Thus, the load balancer makes decisions on task pool. These applications are typically *non-iterative*, as described in Subsection 2.1.2.

The second category, called periodic load balancing are the strategies suitable for *iterative* applications, such as NAMD, FEM, climate simulation and others. In these applications, the computation typically consists of a number of iterations or time steps. Wherein consecutive iterations have similar behaviors. Therefore, load balancing strategies in this category make load balancing decisions every time a certain number of itera-

tions is executed.

This means that, in iterative applications, the load balancing heuristics is performed with a defined frequency. After performing a specific number of iterations, the application is stopped and the load balancer strategy gets information, based on which it decides if it is necessary to migrate some of the tasks, in order to improve the load balance. As discussed in Subsection 2.2.1, this decision making process, performed by the load balancer can be expensive in terms of application execution time.

Periodic load balancing strategies have been used on iterative applications that have persistent load patterns. These strategies make predictions of future computation load based on past information. Their decisions assume that the load will not change significantly in the following iterations, as discussed in Subsection 2.1.1.3.

Several strategies have been proposed to address the load balancing problem. They can be classified based on where the decisions are made. Some strategies employ a centralized approach, where load information is collected on a single processor, in which the decisions can be made sequentially. Other strategies aim at a better scalability, when used in larger scale systems, with a large number of processors. These strategies adopt distributed approaches where distributed processors make decisions using their local view of the system. A third kind of strategies, seeks to reduce the excessive data collection by using a hierarchical structure. In this case, the decisions are made at each level of the hierarchy. These three classes of strategy are briefly discussed in the following sections.

#### 2.3.1 Centralized Strategies

Centralized strategies make load balancing decisions on a single processor. Load and communication data of the entire machine is accumulated in a specific processor, which runs a sequential decision process based on this information. In these strategies, the process of collecting information from all processors can impose a high overhead in the system. So, centralized approaches are only recommended to system with smaller amounts of processors. Otherwise, the load balancer may run into problems of scalability and memory usage (ICHIKAWA; YAMASHITA, 2000; LEGRAND et al., 2004; PHILLIPS et al., 2002; GALINDO; ALMEIDA; BADÍA-CONTELLES, 2008; BHATELÉ et al., 2008; CARIÑO; BANICESCU, 2008; MARTÍNEZ et al., 2011; ZHENG et al., 2011).

#### 2.3.1.1 Basic Centralized Load Balancing Strategies

In this subsection, we will present examples of basic centralized load balancers. We call them basic, because they only consider the load on their decisions. They are:

GREEDYLB is an aggressive scheduling algorithm. This strategy employs a greedy

heuristics to make its decisions using only computational loads information. This

algorithm does not take into account other information and also does not considers

the current place of tasks into processors to decide the migrating tasks (KALÉ;

KRISHNAN, 1993).

The algorithm sorts the tasks in decreasing load order, and iteratively maps the task with the highest load to the least loaded core. Thus, this centralized strategy can be used to quickly mitigate load imbalance not limiting the number of objects migrated (ZHENG et al., 2011).

• REFINELB - makes decisions considering the current load distribution, differently from GREEDYLB, which makes load balancing decisions from scratch. REFINELB improves the load balance by incrementally adjusting the existing mapping. The refinement has a limit, or threshold, on the number of objects that can be migrated. This is done to diminish the overhead in the application. So, this approach migrates only a fraction of objects, therefore reducing data migration. This makes REFINELB be more efficient than GREEDYLB in some applications (KALÉ; KR-ISHNAN, 1993).

In its first step, REFINELB's algorithm divides the cores in two groups according to a previously defined load threshold. So, a core is considered overloaded when its load is greater than the threshold. In the second step, the algorithm verifies the possible migrations from the overloaded cores to non-overloaded cores. REFINELB tries to reach a load distribution that leaves the core loads close to the average. This algorithm is less aggressive than GREEDYLB, because it works over the current task mapping. The load imbalance is incrementally reduced every time these steps are repeated.

RANDCENTLB - differently from GREEDYLB and REFINELB, this load balancer

algorithm does not take into account any information about the application or platform to make its decisions. It randomly assigns all tasks to all processors available (KALÉ; KRISHNAN, 1993).

## 2.3.1.2 Centralized Load Balancing Strategies using Communication Data

Besides the computational load, some centralized load balancers also consider communication data on their decisions. In this subsection, we will present some load balancers available in this category: