### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

#### PEDRO FILIPE LEITE CORREIA DE TOLEDO

MOSFET Zero-Temperature-Coefficient (ZTC) Effect Modeling and Analysis for Low Thermal Sensitivity Analog Applications

Thesis presented in partial fulfillment of the requirements for the degree of Master of Microeletronics

Advisor: Prof. Dr. Hamilton Duarte Klimach

Coadvisor: Prof. Dr. Eric Fabris

#### CIP - CATALOGING-IN-PUBLICATION

de Toledo, Pedro Filipe Leite Correia

MOSFET Zero-Temperature-Coefficient (ZTC) Effect Modeling and Analysis for Low Thermal Sensitivity Analog Applications / Pedro Filipe Leite Correia de Toledo. – Porto Alegre: PGMICRO da UFRGS, 2015.

147 f.: il.

Thesis (Master) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica, Porto Alegre, BR–RS, 2015. Advisor: Hamilton Duarte Klimach; Coadvisor: Eric Fabris.

1. ZTC Bias Point. 2. GZTC Bias Point. 3. CMOS Analog Integrated Circuits. 4. Low Temperature Sensitivity Transconductors. 5. Voltage Reference. 6. Current Reference. I. Klimach, Hamilton Duarte. II. Fabris, Eric. III. Título.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos Alexandre Netto

Vice-Reitor: Prof. Rui Vicente Oppermann

Pró-Reitor de Pós-Graduação: Prof. Vladimir Pinheiro do Nascimento

Diretor do Instituto de Informática: Prof. Luis da Cunha Lamb

Coordenador do PGMICRO: Prof. Gilson Inácio Wirth

Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

### **ACKNOWLEDGMENTS**

During the development of this thesis, I started a new family with my wife, Claudia Camerini Correa de Toledo and my son, Pietro Camerini Correa de Toledo. That changed my life goals and boosted the completion of this work. I would like especially to thank my wife for all the motivation, support and patience during my whole graduate studies at the Federal University of Rio Grande do Sul. Mainly during conference periods where she had to take care of our child alone while I was presenting works related to this thesis.

I would like to thank to my parents, **Bernardino Marques Toledo** and **Sineide Leite da Silva**, and my beautiful sisters **Thais Toledo** e **Adriana Toledo**, for all support given to my master's studies and life in Porto Alegre.

My advisors, **Prof. Hamilton Klimach** and **Prof. Eric Fabris**, for the excellent discussions that helped me mature and learn so much in the field of microelectronics. The same remarks apply to **Prof. Sergio Bampi**.

My friends of NSCAD group, Renê Timbo, Diogo Santana, Helga Dornelas, Alonso Schmidt, Jhon Caicedo, and in particular **David Cordova**, for all discussions in the lab and meetings. **David Cordova** made a tremendous contribution to this thesis since two of the circuits presented in this work were designed and measured by him.

My friends of lab 110 Analog/RF group, Arthur Liraneto, Filipe Baumgratz, Renato Campana, Sandro Binsfeld, Oscar Mattia, Márlon Lorenzetti, Rafael Schultz, Luís Rodovalho, Bruno Canal, Moacir Monteiro, Arthur Oliveira, Roger Zamparette, Gabriel Guimarães, Pedro Toledo, David Cordova, Fernando Carrion, Marcelo Pedrini, Thales Ribeiro and Yi Chen Wu for the discussions in the lab and meetings.

All administrative people, who have been working hard to keep all the infrastructure of the Instituto de Informática and Graduate Program in Microelectronics fully available to me.

PRONEX/CNPq and Capes for the funding support given to this research. The IC-Brazil program, NSCAD support to Cadence tools and MOSIS for the MOSIS Educational Program (MEP), which gave the opportunity to fabricate some circuits presented here.

### **ABSTRACT**

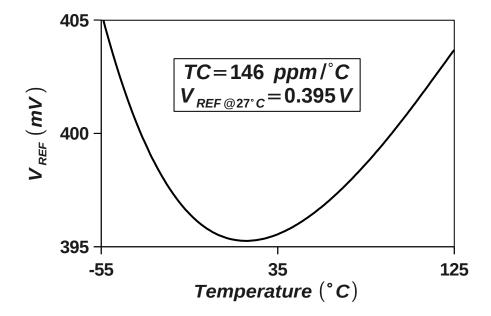

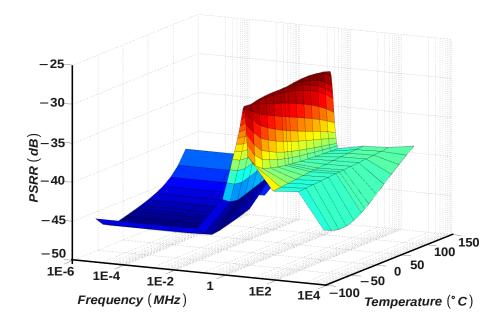

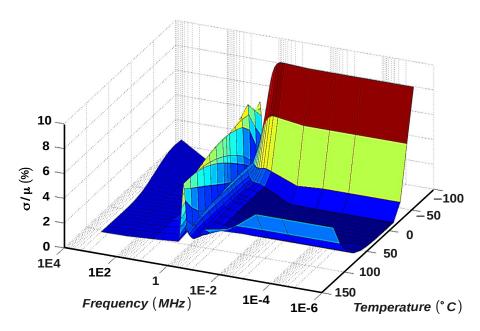

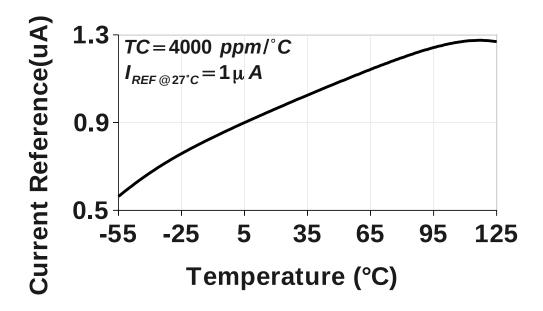

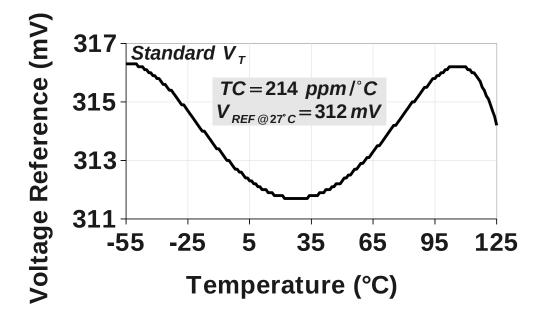

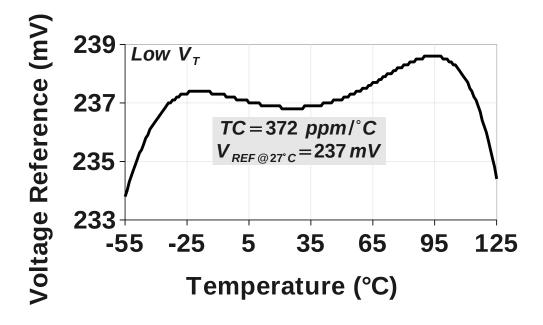

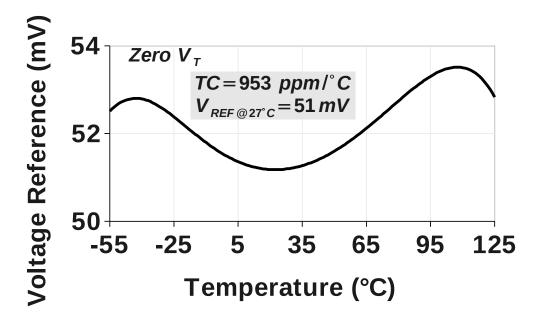

Continuing scaling of Complementary Metal-Oxide-Semiconductor (CMOS) technologies brings more integration and consequently temperature variation has become more aggressive into a single die. Besides, depending on the application, room ambient temperature may also vary. Therefore, procedures to decrease thermal dependencies of eletronic circuit performances become an important issue to include in both digital and analog Integrated Circuits (IC) design flow. The main purpose of this thesis is to present a design methodology for a typical CMOS Analog design flow to make circuits as insensitivity as possible to temperature variation. MOSFET Zero Temperature Coefficient (ZTC) and Transconductance Zero Temperature Coefficient (GZTC) bias points are modeled to support it. These are used as reference to deliver a set of equations that explains to analog designers how temperature will change transistor operation and hence the analog circuit behavior. The special bias conditions are analyzed using a MOSFET model that is continuous from weak to strong inversion, and both are proven to occur always from moderate to strong inversion operation in any CMOS fabrication process. Some circuits are designed using proposed methodology: two new ZTC-based current references, two new ZTC-based voltage references and four classical Gm-C circuits biased at GZTC bias point (or defined here as GZTC-C filters). The first current reference is a Self-biased CMOS Current Reference (ZSBCR), which generates a current reference of 5  $\mu$ A. It is designed in an 180 nm process, operating with a supply voltage from 1.4V to 1.8 V and occupying around  $0.010mm^2$  of silicon area. From circuit simulations the reference shows an effective temperature coefficient  $(TC_{eff})$  of 15 ppm/°C from -45 to +85°C, and a fabrication process sensitivity of  $\sigma/\mu = 4.5\%$ , including average process and local mismatch. Simulated power supply sensitivity is estimated around 1%/V. The second proposed current reference is a Resistorless Self-Biased ZTC Switched Capacitor Current Reference (ZSCCR). It is also designed in an 180 nm process, resulting a reference current of 5.88  $\mu$ A under a supply voltage of 1.8 V, and occupying a silicon area around  $0.010mm^2$ . Results from circuit simulation show an  $TC_{eff}$  of 60 ppm/°C from -45 to +85 °C and a power consumption of 63  $\mu$ W. The first proposed voltage reference is an EMI Resisting MOSFET-Only Voltage Reference (EMIVR), which generates a voltage reference of 395 mV. The circuit is designed in a 130 nm process, occupying around 0.0075  $mm^2$  of silicon area while consuming just 10.3  $\mu$ W. Post-layout simulations present a  $TC_{eff}$  of 146 ppm/°C, for a temperature range from -55 to +125°C. An EMI source of 4 dBm (1  $V_{nn}$ amplitude) injected into the power supply of circuit, according to Direct Power Injection (DPI) specification results in a maximum DC Shift and Peak-to-Peak ripple of -1.7 % and 35.8m  $V_{pp}$ , respectively. The second proposed voltage reference is a 0.5V Schottky-based Voltage Reference (SBVR). It provides three voltage reference outputs, each one utilizing different threshold voltage MOSFETs (standard- $V_T$ , low- $V_T$ , and zero- $V_T$ ), all available in adopted 130 nm CMOS process. This design results in three different and very low reference voltages: 312, 237, and 51 mV, presenting a  $TC_{eff}$  of 214, 372, and 953 ppm/°C in a temperature range from -55 to 125°C, respectively. It occupies around 0.014  $mm^2$  of silicon area for a total power consumption of 5.9  $\mu$ W. Lastly, a few example Gm-C circuits are designed using GZTC technique: a single-ended resistor emulator, an impedance inverter, a first order and a second order filter. These circuits are simulated in a 130 nm CMOS commercial process, resulting improved thermal stability in the main performance parameters, in the range from 27 to 53 ppm/°C.

**Keywords:** ZTC Bias Point, GZTC Bias Point, CMOS Analog Integrated Circuits, Low Temperature Sensitivity Transconductors, Voltage Reference, Current Reference.

# MODELAMENTO E ANÁLISE DO EFEITO DE COEFICIENTE NULO DE TEMPERATURA (ZTC) DO MOSFET PARA APLICAÇÕES ANALÓGICAS DE BAIXA SENSIBILIDADE TÉRMICA

### **RESUMO**

A contínua miniaturização das tecnologias CMOS oferece maior capacidade de integração e, consequentemente, as variações de temperatura dentro de uma pastilha de silício têm se apresentado cada vez mais agressivas. Ademais, dependendo da aplicação, a temperatura ambiente a qual o CHIP está inserido pode variar. Dessa maneira, procedimentos para diminuir o impacto dessas variações no desempenho do circuito são imprescindíveis. Tais métodos devem ser incluídos em ambos fluxos de projeto CMOS, analógico e digital, de maneira que o desempenho do sistema se mantenha estável quando a temperatura oscilar. A ideia principal desta dissertação é propor uma metodologia de projeto CMOS analógico que possibilite circuitos com baixa dependência térmica. Como base fundamental desta metodologia, o efeito de coeficiente térmico nulo no ponto de polarização da corrente de dreno (ZTC) e da transcondutância (GZTC) do MOSFET são analisados e modelados. Tal modelamento é responsável por entregar ao projetista analógico um conjunto de equações que esclarecem como a temperatura influencia o comportamento do transistor e, portanto, o comportamento do circuito. Essas condições especiais de polarização são analisadas usando um modelo de MOSFET que é contínuo da inversão fraca para forte. Além disso, é mostrado que as duas condições ocorrem em inversão moderada para forte em qualquer processo CMOS. Algumas aplicações são projetadas usando a metodologia proposta: duas referências de corrente baseadas em ZTC, duas referências de tensão baseadas em ZTC, e quatro circuitos gm-C polarizados em GZTC. A primeira referência de corrente é uma Corrente de Referência CMOS Auto-Polarizada (ZSBCR), que gera uma referência de 5  $\mu$ A. Projetada em CMOS 180 nm, a referência opera com uma tensão de alimentação de 1.4 à 1.8 V, ocupando uma área em torno de  $0.010mm^2$ . Segundo as simulações, o circuito apresenta um coeficiente de temperatura efetivo ( $TC_{eff}$ ) de 15 ppm/ $^{\circ}$ C para -45 à +85 °C e uma sensibilidade à variação de processo de  $\sigma/\mu=4.5\%$  incluindo efeitos de variabilidade dos tipos processo e descasamento local. A sensibilidade de linha encontrada nas simulações é de 1%/V. A segunda referência de corrente proposta é uma Corrente de Referência Sem Resistor Auto-Polarizada com Capacitor Chaveado (ZSCCR). O circuito é projetado também em 180 nm, resultando em uma corrente de referência de 5.88  $\mu$ A, para uma tensão de alimentação de 1.8 V, e ocupando uma área de  $0.010mm^2$ . Resultados de simulações mostram um  $TC_{eff}$  de 60 ppm/°C para um intervalo de temperatura de -45 à +85  $^{o}$ C e um consumo de potência de 63  $\mu$ W. A primeira referência de tensão proposta é uma Referência de Tensão resistente à pertubações eletromagnéticas contendo apenas MOSFETs (EMIVR), a qual gera um valor de referência de 395 mV. O circuito é projetado no processo CMOS 130 nm, ocupando em torno de 0.0075  $mm^2$  de área de silício, e consumindo apenas 10.3  $\mu$ W. Simulações pós-leiaute apresentam um  $TC_{eff}$  de 146 ppm/°C, para um intervalo de temperatura de -55 à +125°C. Uma fonte EMI de 4 dBm (1  $V_{pp}$  de amplitude) aplicada na alimentação do circuito, de acordo

com o padrão Direct Power Injection (DPI), resulta em um máximo de desvio DC e ondulação Pico-à-Pico de -1.7 % e 35.8m  $V_{pp}$ , respectivamente. A segunda referência de tensão é uma Tensão de Referência baseada em diodo Schottky com 0.5V de alimentação (SBVR). Ela gera três saídas, cada uma utilizando MOSFETs com diferentes tensões de limiar (standard- $V_T$ , low- $V_T$ , e zero- $V_T$ ). Todos disponíveis no processo adotado CMOS 130 nm. Este projeto resulta em três diferentes voltages de referências: 312, 237, e 51 mV, apresentando um  $TC_{eff}$  de 214, 372, e 953 ppm/ $^{o}$ C no intervalo de temperatura de -55 à 125 $^{o}$ C, respectivamente. O circuito ocupa em torno de 0.014  $mm^2$ , consumindo um total de 5.9  $\mu$ W. Por último, circuitos gm-C são projetados usando o conceito GZTC: um emulador de resistor, um inversor de impedância, um filtro de primeira ordem e um filtro de segunda ordem. Os circuitos também são simulados no processo CMOS 130 nm, resultando em uma melhora na estabilidade térmica dos seus principais parâmetros, indo de 27 à 53 ppm/ $^{o}$ C.

**Palavras-chave:** Ponto de Operação ZTC, Ponto de Operação GZTC, Circuitos Integrados Analógicos CMOS, Transcondutores com baixa sensibilidade térmica, Referências de Tensão, Referências de Corrente.

### LIST OF FIGURES

| 1.1  | temperature variation. Temperature gradient between a microprocessor core and an on-chip cache.                                                                                                                                                                                                                                                                        | 21         |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 1.2  | Impact of technology scaling on power density. $\alpha$ features each tech-                                                                                                                                                                                                                                                                                            |            |

|      | nological node ( $\mu m$ )                                                                                                                                                                                                                                                                                                                                             | 22         |

| 1.3  | CPU cooling system                                                                                                                                                                                                                                                                                                                                                     | 22         |

| 1.4  | TCP/IP offload accelerator engine fabricated in 90nm CMOS                                                                                                                                                                                                                                                                                                              | 23         |

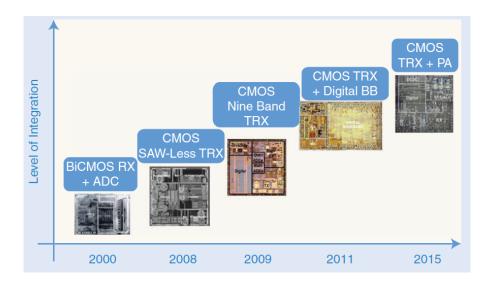

| 1.5  | Trends in integration strategies                                                                                                                                                                                                                                                                                                                                       | 24         |

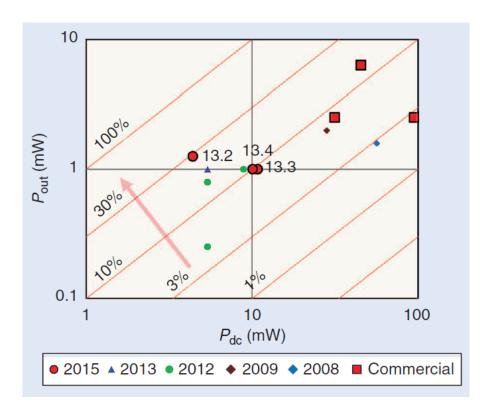

| 1.6  | Ultra-low-power 2.4-GHz wireless transmit efficiency. The arrow shows the desired trends. All symbols except the red squares represent ISSCC papers. The ISSCC 2015 paper numbers are indicated next to the red circles.                                                                                                                                               | 24         |

|      |                                                                                                                                                                                                                                                                                                                                                                        |            |

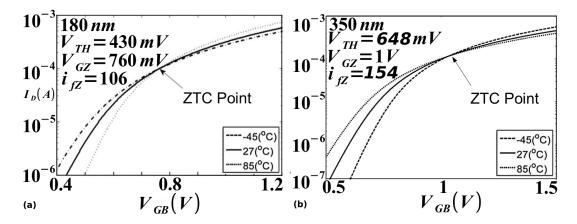

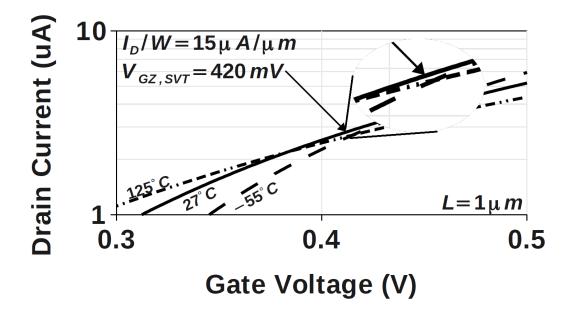

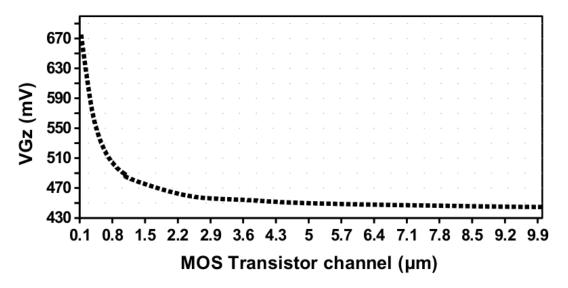

| 2.1  | NMOSFET ZTC point for (a) 180nm and (b) 350 nm processes                                                                                                                                                                                                                                                                                                               | 28         |

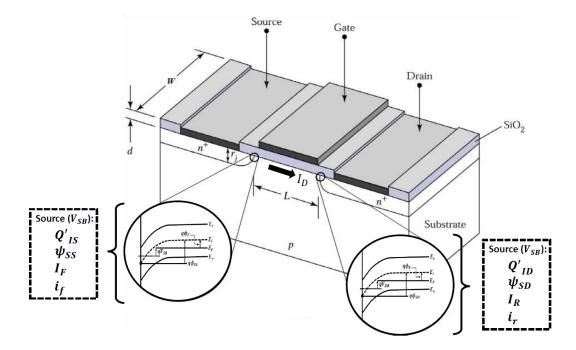

| 2.2  | Planar MOSFET transistor                                                                                                                                                                                                                                                                                                                                               | 29         |

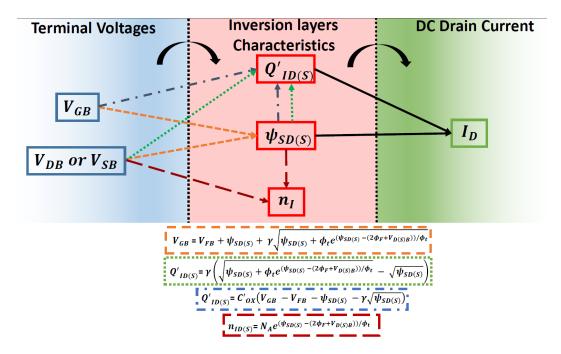

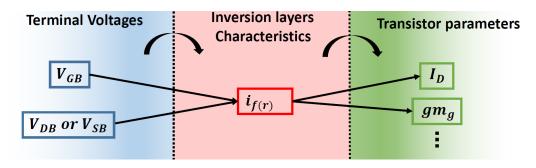

| 2.3  | Connections among external voltages, interfaces characteristics and drain current                                                                                                                                                                                                                                                                                      | 30         |

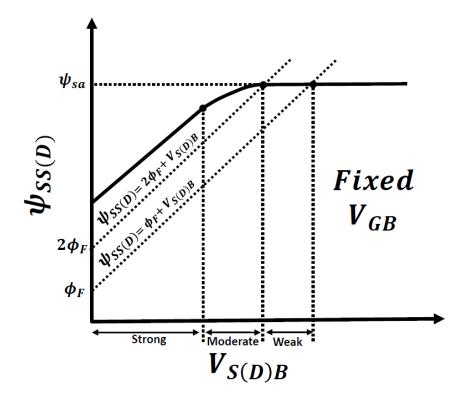

| 2.4  | $V_{S(D)B}$ vs. $\psi_{SS(D)}$                                                                                                                                                                                                                                                                                                                                         | 31         |

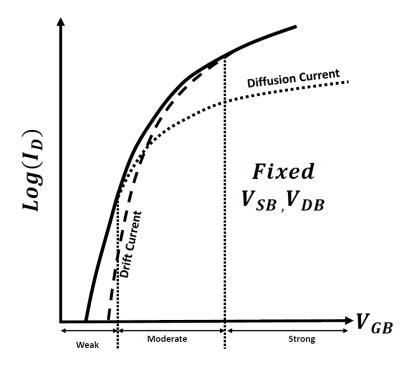

| 2.5  | $I_D$ Drift and diffusion current comprise ids                                                                                                                                                                                                                                                                                                                         | 32         |

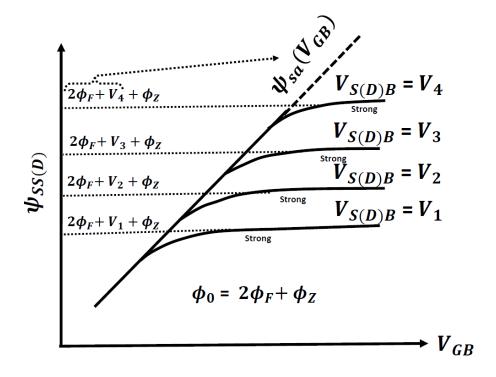

| 2.6  | $V_{GB}$ vs. $\psi_{SS(D)}$                                                                                                                                                                                                                                                                                                                                            | 33         |

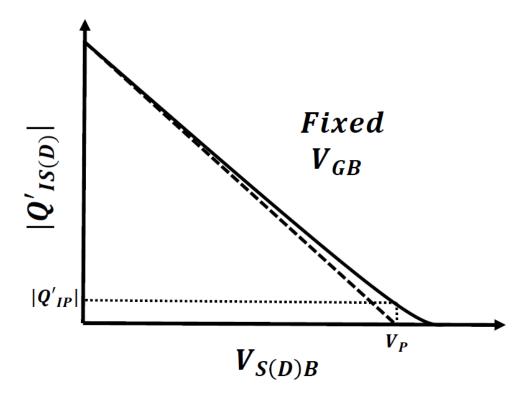

| 2.7  | $Q_{I(D)S}'$ vs. $V_{S(D)B}$                                                                                                                                                                                                                                                                                                                                           | 34         |

| 2.8  | $\Im(D)S$ VS. $VS(D)B$                                                                                                                                                                                                                                                                                                                                                 | <i>J</i> 1 |

| 2.0  | drain current using UICM model                                                                                                                                                                                                                                                                                                                                         | 34         |

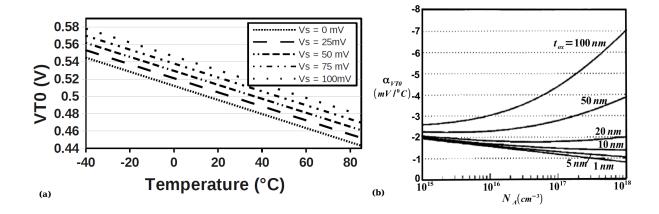

| 2.9  | (a) $V_{T0}$ versus temperature for different values of $V_{SB}$ (0 to 100 mV) and $V_{GB}=900mV$ in a 180nm CMOS process (b) $\alpha_{V_{T0}}$ vs. $N_A$ for                                                                                                                                                                                                          | 36         |

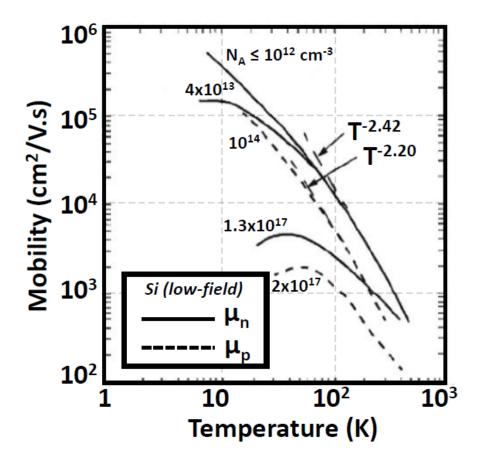

| 2.10 | different $t_{ox}$                                                                                                                                                                                                                                                                                                                                                     | 37         |

| 2.10 | $\mu$ vs. temperature for different $N_A$                                                                                                                                                                                                                                                                                                                              | 31         |

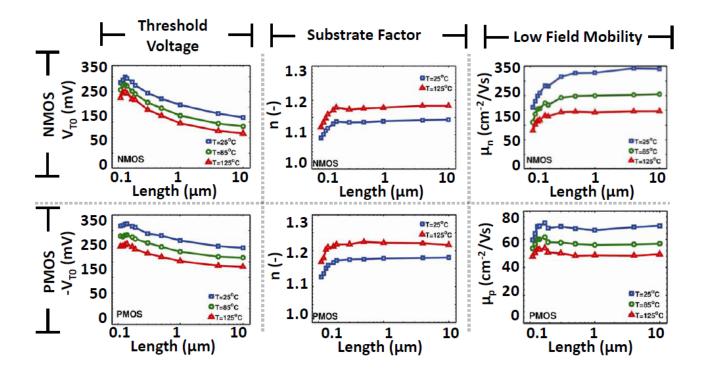

| 2.11 | tion (right), as a function of channel length and temperature, NMOS (upper) and PMOS (lower) devices of a 110 nm CMOS technology.                                                                                                                                                                                                                                      | 38         |

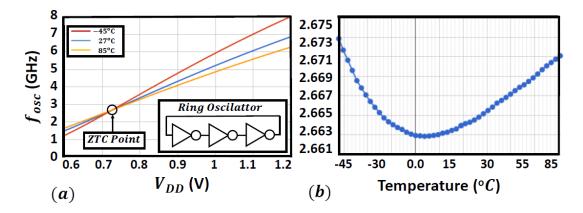

| 2.12 | (a) Oscillation frequency $(f_{osc})$ vs. supply voltage $(V_{DD})$ for different temperature and (b) Oscillation frequency $(f_{osc})$ vs. temperature. These are simulated data of 130 nm CMOS technology using an inverter with L = 130nm, $W_n$ = 130 nm and $W_p$ = 520 nm. L is length, $W_n$ and $W_p$ are the widths of NMOS and PMOS transistor, respectively | 40         |

|      |                                                                                                                                                                                                                                                                                                                                                                        |            |

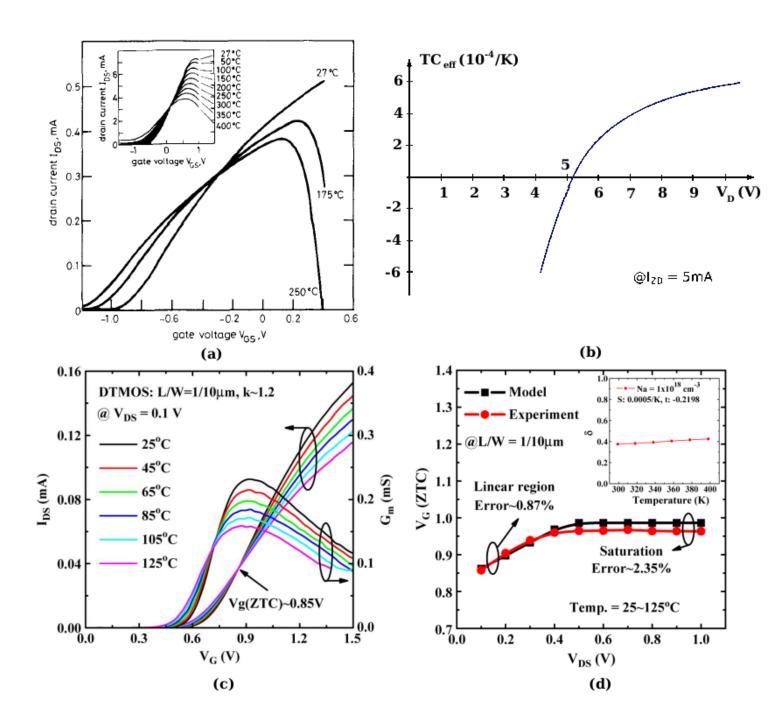

| 2.13 | (a) Measured characteristics for DMESFET of form factor W/L = 50/2 in linear ragion and saturation ragion (b) TC for Diodo Zan                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | 50/2 in linear region and saturation region (b) $TC_{eff}$ for Diode Zenner for different terminal voltage. (c) Experimental $I_D$ vs. $V_G$ and                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|      | $g_m$ characteristics of n-channel DTMOS in the linear region over a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

|      | temperature range of $25^{\circ}C$ to $125^{\circ}C$ . Note that the ZTC point is 0.85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|      | V when $V_{DS} = 0.1$ V in the linear region. (d) Theoretical values of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

|      | the ZTC point model and actual experimental data of the DTMOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|      | transistor in both the linear and saturation regions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 44 |

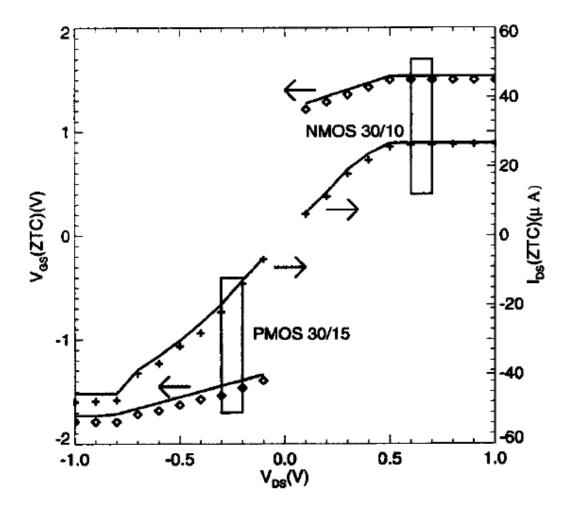

| 2.14 | Measured and simulated gate bias $(V_{GZ})$ and drain current $(I_{DZ})$ at                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 77 |

| 2.17 | the ZTC point with drain bias $(V_{GZ})$ and that current $(T_{DZ})$ at the ZTC point with drain bias $(V_{DS})$ in both linear and saturation regions for NMOS $(\frac{W}{L} = \frac{30\mu m}{10\mu m})$ and PMOS $(\frac{W}{L} = \frac{30\mu m}{5\mu m})$                                                                                                                                                                                                                                                                                                                                  | 45 |

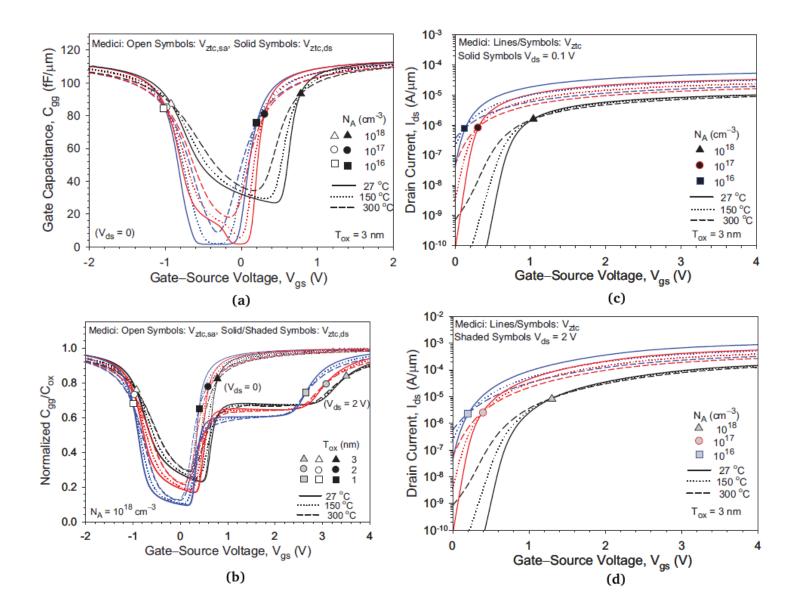

| 2.15 | Gate capacitance versus gate voltage for (a) different body doping (at                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 43 |

| 2.13 | Vds = 0) and (b) different gate-oxide thickness (at Vds = 2 V), at 27 °C (solid line), 150 °C (dotted line), and 300 °C (dashed line) from an ideal MOS transistor, with the corresponding ZTC points extracted                                                                                                                                                                                                                                                                                                                                                                              |    |

|      | from the numerical data (symbols). Drain current versus gate voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

|      | in (c) linear (Vds = 0.1 V) and (d) saturation (Vds = 2 V) modes for different body doping as indicated, at 27 °C (solid line), 150 °C (dotted line), and 300 °C (dashed line) from an ideal MOS transistor, with the corresponding ZTC points extracted from the numerical data                                                                                                                                                                                                                                                                                                             |    |

|      | (symbols)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 46 |

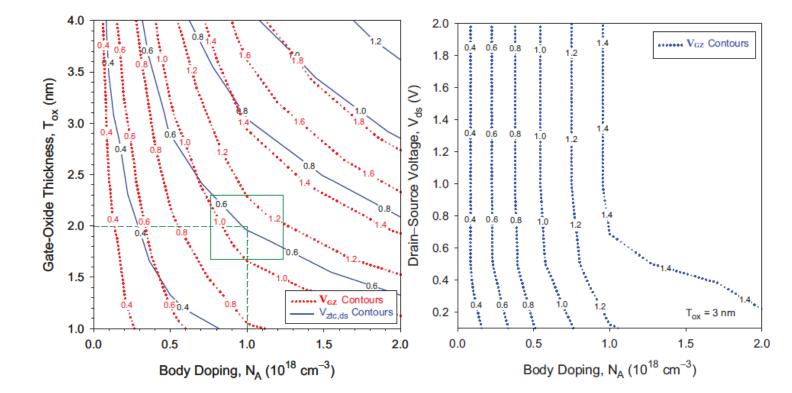

| 2.16 | (a) Contour plots of constant $V_{ztc,ds}$ (solid line) and $V_{GZ}$ (dotted line) extracted from the compact ZTC charge and current models, respec-                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

|      | tively, due to body doping and gate oxide thickness variations. The box illustrates a process window around the nominal values of $N_A = 10^{18} \ cm^{-3}$ and $t_{ox} = 2$ nm, which predicts a potential $V_{ztc,ds}$ variation from 0.5 V to 0.7 V and $V_{GZ}$ variation from 0.85 to 1.3 V, respectively, if the variations in $N_A$ and $t_{ox}$ are given within the box. (b) Contour plot of constant $V_{GZ}$ extracted from the compact ZTC drain current model at any $V_{DS}$ due to body doping variations for devices operating in partial, dynamic, and full depletion modes | 47 |

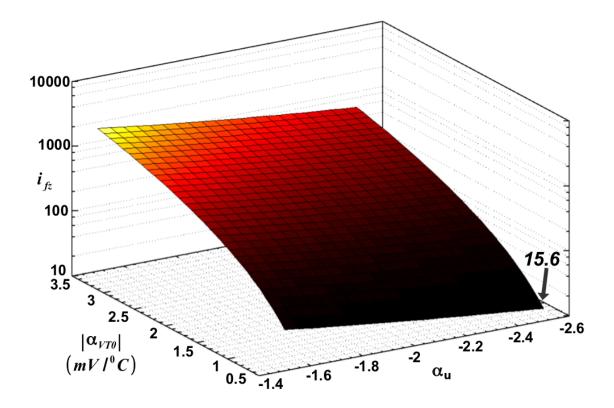

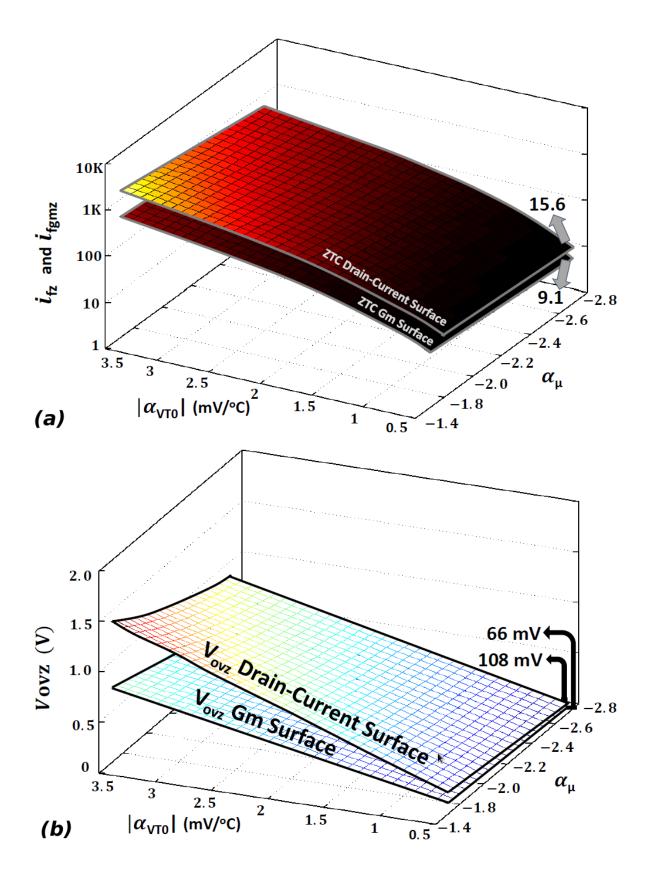

| 2.17 | ZTC forward inversion level Surface (ZTCS). Graphic made with the script of appendix C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 52 |

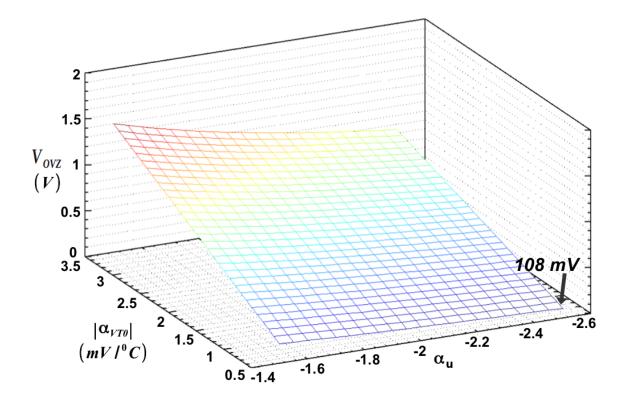

| 2.18 | $V_{OVZ}$ - the ZTC overdrive voltage. Graphic made with the script of appendix C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 53 |

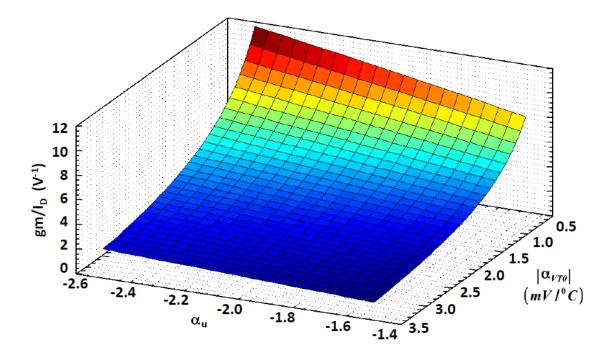

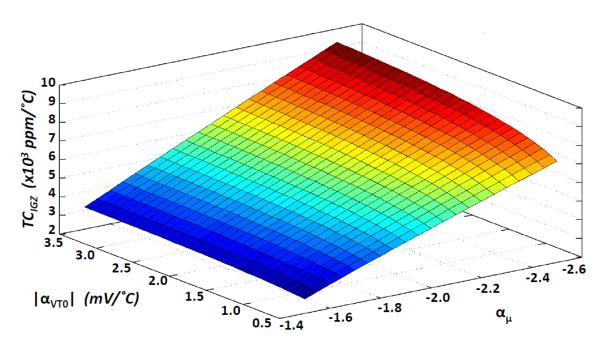

| 2.19 | $(\frac{g_{mg}}{I_D})_Z$ or $g_{mg}$ over $I_D$ biased on $i_{fz}$ . Graphic made with the script of appendix C                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 54 |

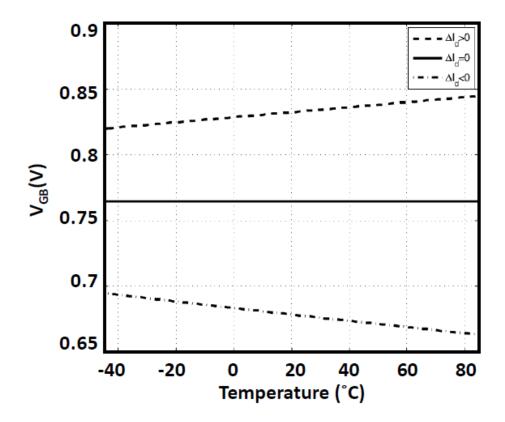

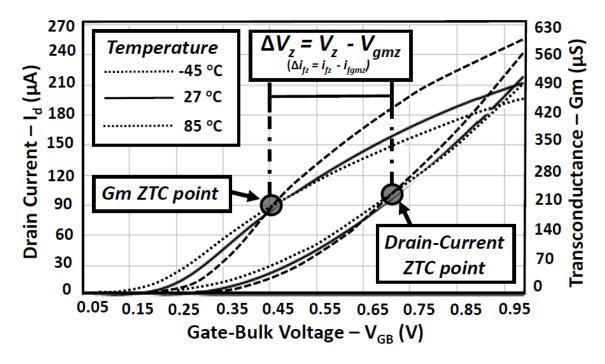

| 2.20 | $V_{GB}(T)$ for $\Delta I_d > 0$ , $\Delta I_d = 0$ and $\Delta I_d < 0$ . Simulated data from 180 nm CMOS technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 56 |

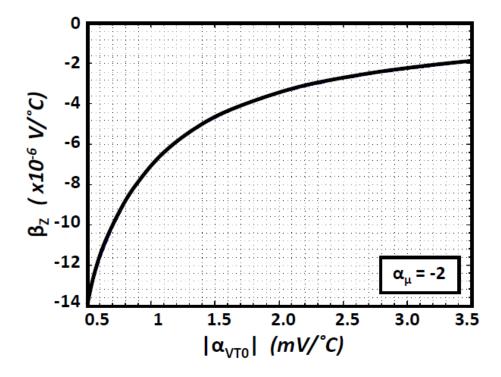

| 2.21 | $\beta_z$ in function of $ \alpha_{V_{T0}} $ . Note that, for adopted assumption $\alpha_{\mu} \approx -2$ , $\beta_z$ is always negative since it is only dependent of $\alpha_{V_{T0}}$ . Graphic made with the script of appendix C                                                                                                                                                                                                                                                                                                                                                       | 56 |

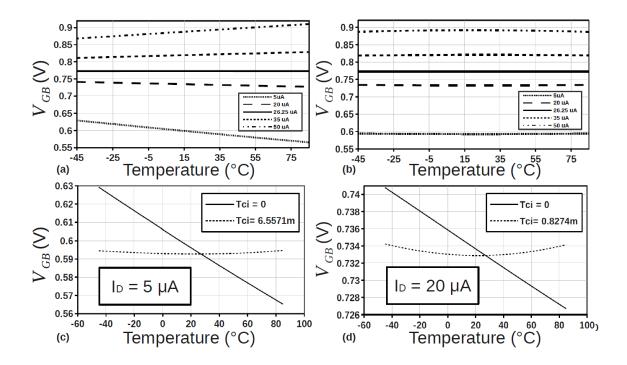

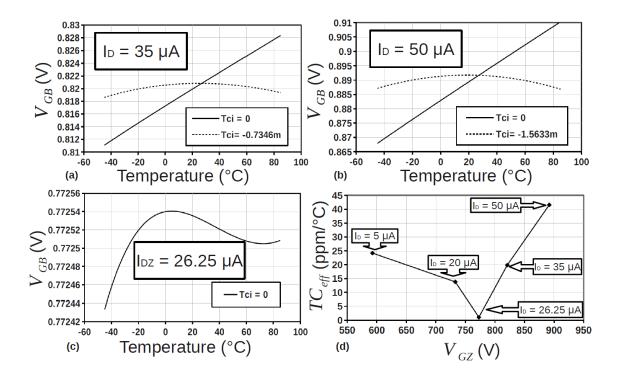

| 2.22 | (a) simulations data for a diode-connected NMOS transistor (W/L = $2.5\mu m/1\mu m$ ) in 180 nm CMOS technology with five different bias current (5, 20, 26.25, 35, 50 $\mu A$ ), yielding distinct $V_{GB}$ temperature dependence. (b) $V_{GB}$ versus temperature enforcing right $TC_I$ that cancels PTAT or CTAT behavior. (c) Zoom for $I_D = 5\mu A$ . (d) Zoom                                                                                                                                                                                                                       |    |

|      | for $I_D = 20\mu A$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 57 |

| 2.23 | (a) Zoom for $I_D=35\mu A$ . (b) Zoom for $I_D=50\mu A$ . (c) Zoom for $I_D=26.25\mu A$ . (d) $TC_{eff}$ for each vicinity condition                                                                                                                                                       | 58                              |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

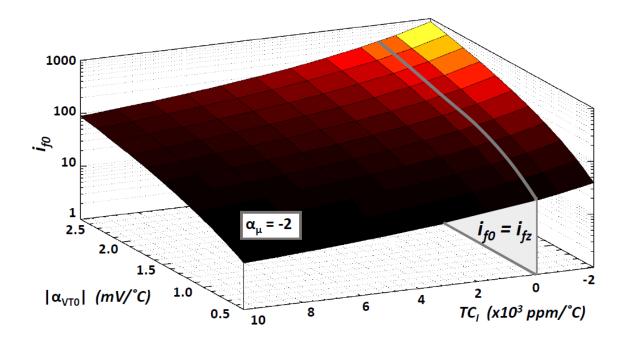

| 2.24 | $i_{f0}$ in function of $TC_I$ and $\alpha_{V_{T0}}$ . Graphic made with the script of appendix C                                                                                                                                                                                          | 59                              |

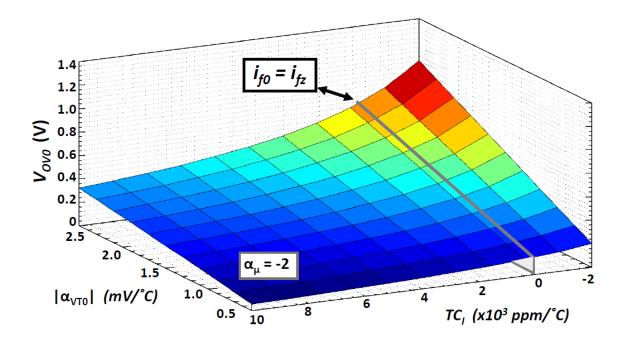

| 2.25 | Overdrive voltage change around ZTC point ( $TC_I = 0$ ) for different values of current temperature coefficients ( $TC_I$ ). Graphic made with the script of Appendix C.                                                                                                                  | 60                              |

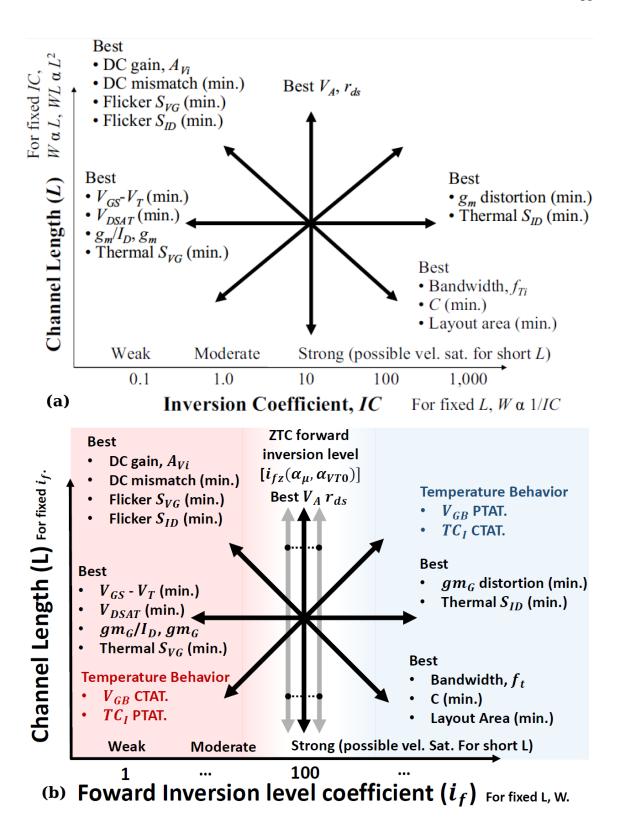

| 2.26 | (a) The MOSFET operating plane illustrating tradeoffs in performance for the selected inversion coefficient and channel length. Copyright John Wiley and Sons Limited. (b) MOSFET operating plane translated to UCIM presented before including temperature behavior of MOSFET transistor. | 61                              |

| 2.27 | (a) ZTC forward inversion level surface (ZTCS) and GZTC forward inversion level surface (GZTCS) (b) overdrive voltage for the ZTC $(V_{OVZ})$ and GZTC bias point $(V_{OVGZ})$ as a function of the values for                                                                             |                                 |

| 2.28 | $\alpha_{\mu}$ and $\alpha_{V_{T0}}$ . Graphics made with the script of Appendix C ZTC and GZTC condition for a PMOS transistor in a 130 nm process with $V_{T0}=250$ mV. These curves have been plotted using $V_{DS}=100$                                                                | 64                              |

| 2.29 | $V_{GS}$                                                                                                                                                                                                                                                                                   | <ul><li>65</li><li>65</li></ul> |

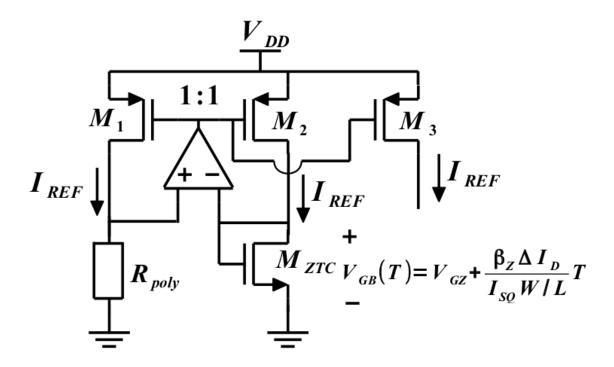

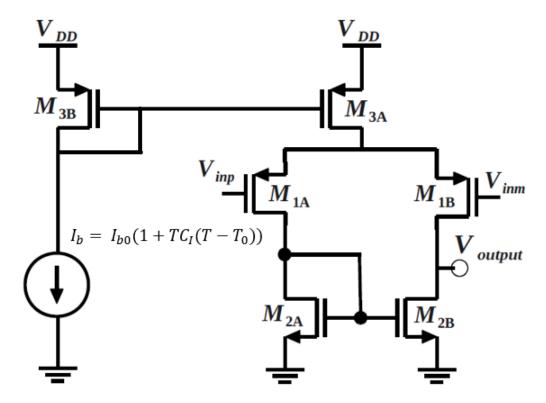

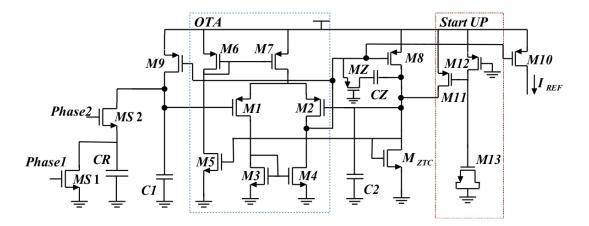

| 3.1  | Idea of proposed Self-biased CMOS Current Reference based on ZTC                                                                                                                                                                                                                           |                                 |

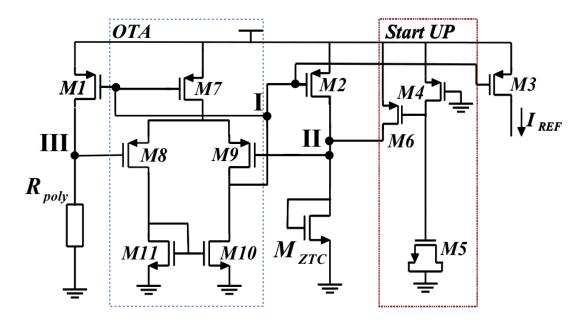

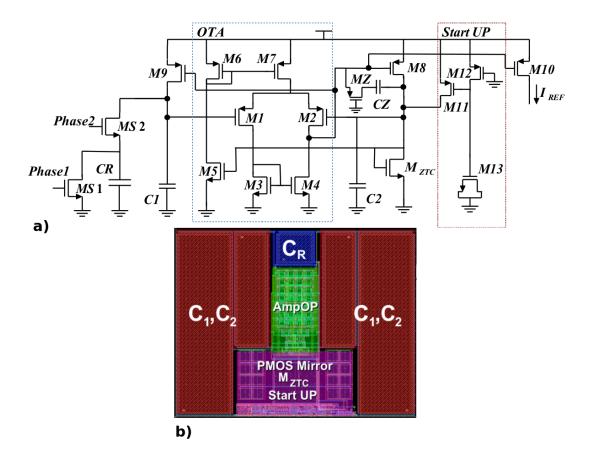

| 3.2  | Operation Condition                                                                                                                                                                                                                                                                        | 67<br>68                        |

| 3.3  | dition                                                                                                                                                                                                                                                                                     | 69                              |

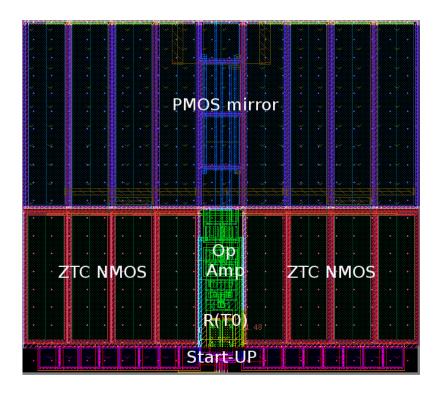

| 3.4  | Layout - $100\mu \text{m} \times 100\mu \text{m}$                                                                                                                                                                                                                                          | 70                              |

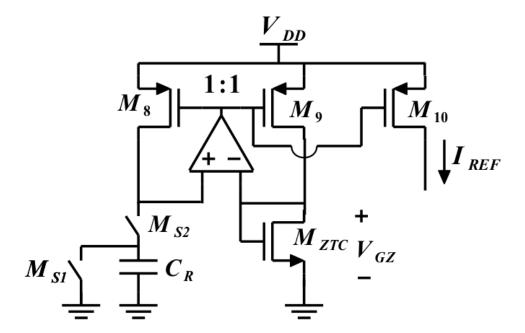

| 3.5  | Idea of proposed Resistorless Self-Biased ZTC Switched Capacitor Current Reference.                                                                                                                                                                                                        | 72                              |

| 3.6  | (a) The ZTC Switched Capacitor Current Reference (ZSCCR). (b) ZSCCR Layout - $100\mu m$ X $100\mu m$ in 180 nm CMOS process                                                                                                                                                                | 73                              |

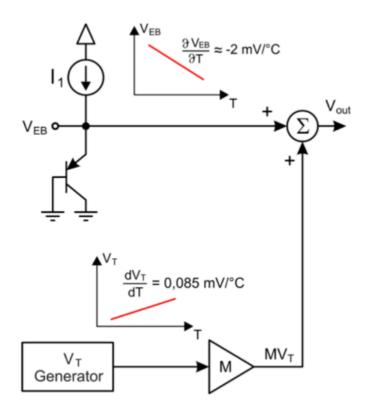

| 3.7  | Basic concept of a bandgap voltage reference                                                                                                                                                                                                                                               | 76                              |

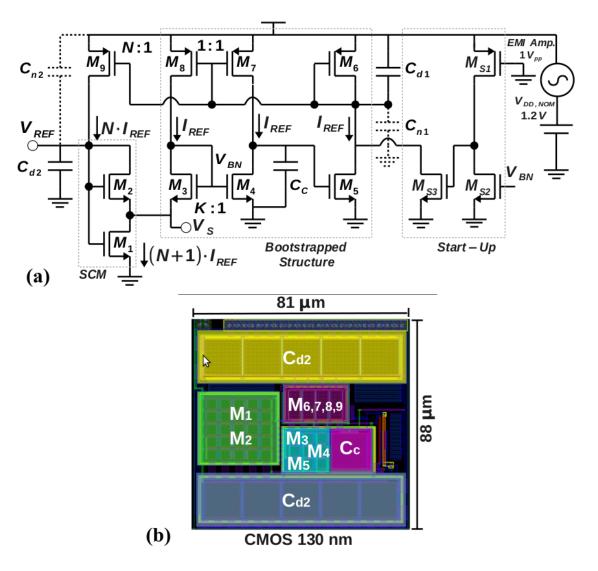

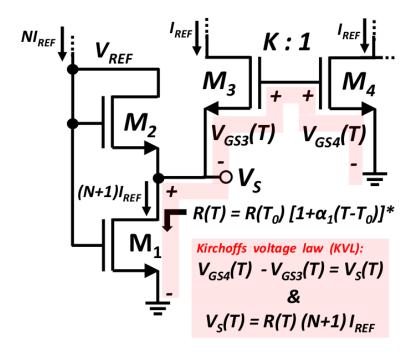

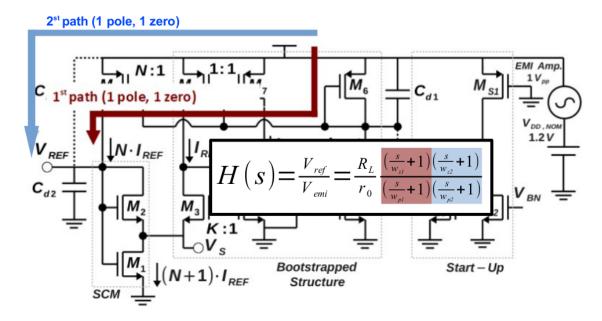

| 3.8  | (a) Proposed EMI resisting CMOS voltage reference schematic circuit. (b) Layout Area: $81 \mu m \times 88 \mu m$                                                                                                                                                                           | 77                              |

| 3.9  | The thermal cancellation strategy used in proposed EMI Resisting MOSFET-Only Voltage Reference                                                                                                                                                                                             | 78                              |

| 3.10 | Poles and Zeros related to nodes and feedback capacitance in proposed EMI Voltage reference, respectively.                                                                                                                                                                                 | 80                              |

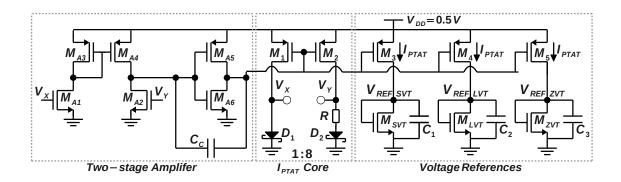

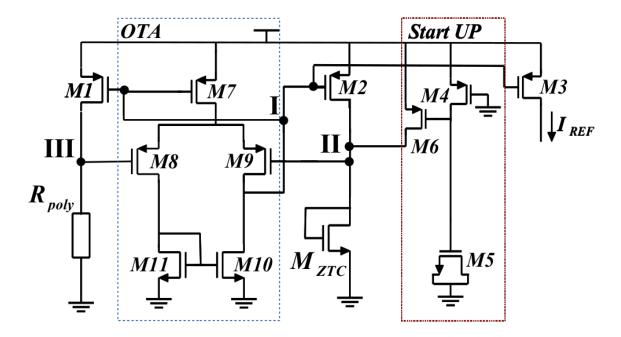

| 3.11 | Proposed 0.5-V CMOS voltage reference schematic circuit                                                                                                                                                                                                                                    | 82                              |

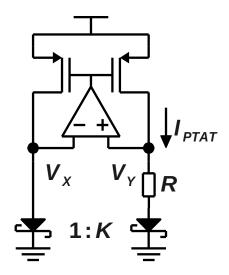

| 3.12 | Low-voltage supply PTAT current reference                                                                                                                                                                                                                                                  | 83                              |

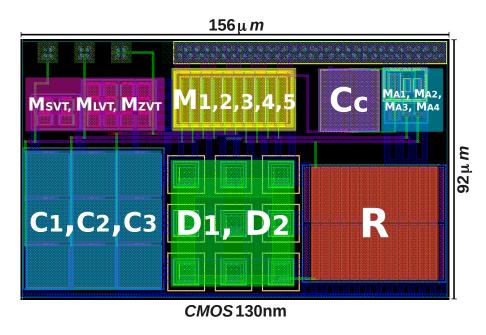

| 3.13 | Proposed 0.5-V CMOS voltage reference layout                                                                                                                                                                                                                                               | 84                              |

| 3.14 | PMOS differential pair with active load                                                                                                                                                                                                                                                    | 85                              |

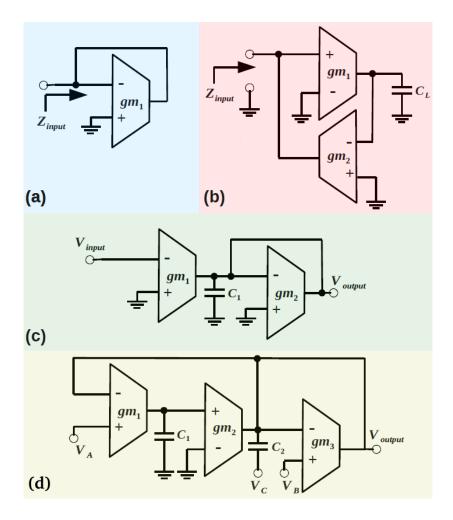

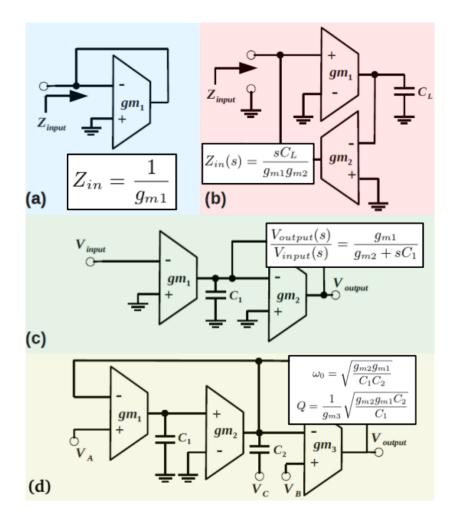

| 3.15 | (a) single-ended resistor emulator (b) impedance inverter (c) first order filter (d) second order filter.                                                                                                                                                                                  | 87                              |

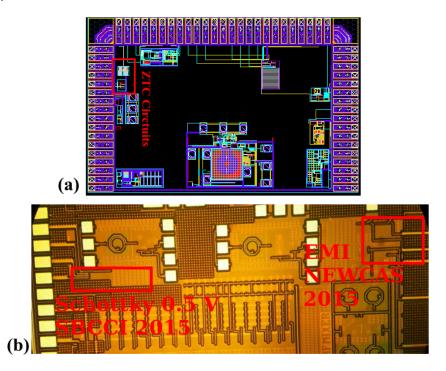

| 4.1  | (a) Test die inside of MLM2013 reticle (b) Micrograph of IBM 130 nm die                                                                                                                                                                                                                    | 89                              |

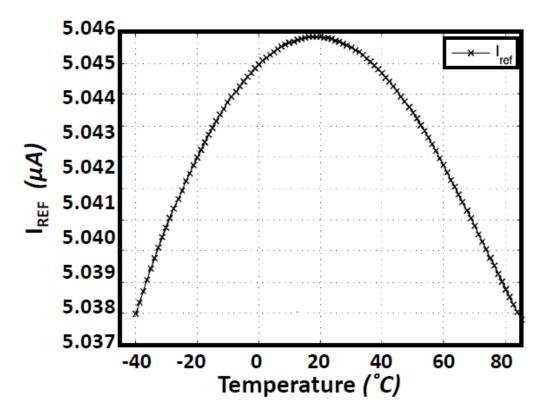

| 4.2                | Self-biased CMOS Current Reference based on ZTC Operation Condition                                                                                | 90       |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 4.3                | Current Reference vs. temperature                                                                                                                  | 91       |

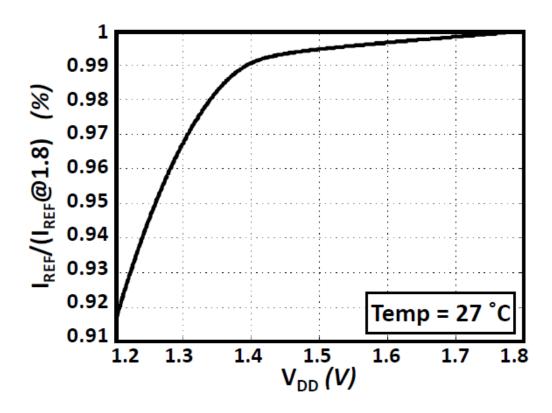

| 4.4                | Normalized Power Supply Sensitivity                                                                                                                | 91       |

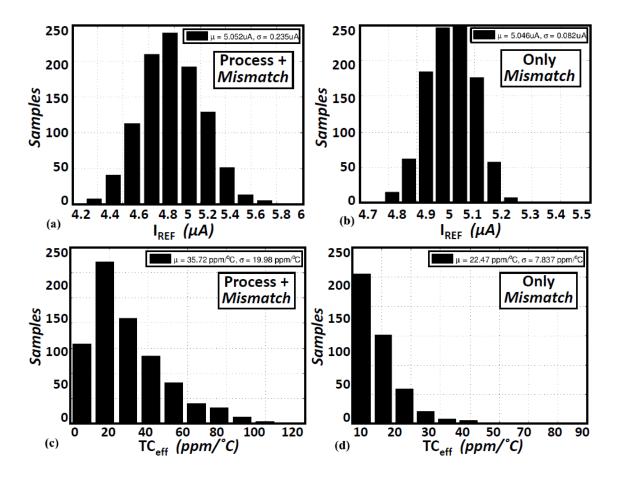

| 4.5                | (a) $I_{REF}$ Monte Carlo simulation including process and mismatch.                                                                               | 71       |

| 4.3                | (a) $I_{REF}$ Monte Carlo simulation including process and inistraction.<br>(b) $I_{REF}$ Monte Carlo simulation only for mismatch. (c) $TC_{eff}$ |          |

|                    | Monte Carlo simulation only for inismatch. (c) $TC_{eff}$<br>Monte Carlo simulation including process and mismatch. (d) $TC_{eff}$                 |          |

|                    | Monte Carlo simulation only for mismatch                                                                                                           | 93       |

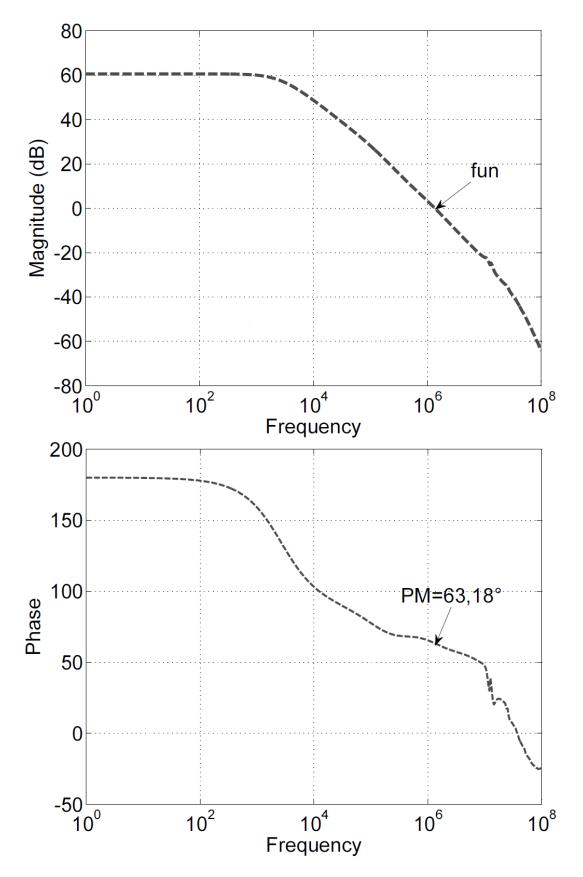

| 4.6                | ZTC Switched Capacitor Current Reference (ZSCCR)                                                                                                   | 94       |

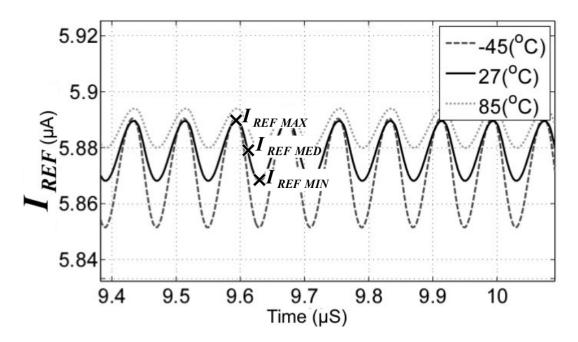

| 4.0<br>4.7         | $I_{REF}$ in time domain                                                                                                                           | 95       |

| 4. <i>7</i><br>4.8 | $I_{REF}$ in time domain                                                                                                                           | 95<br>95 |

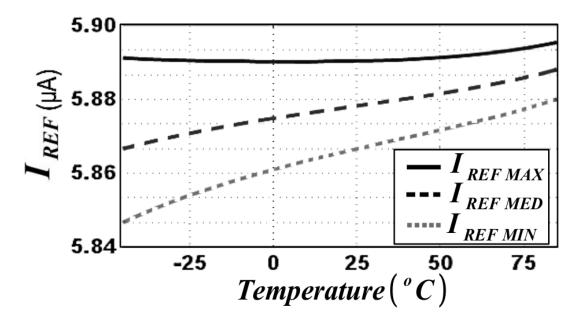

| 4.0<br>4.9         | 1                                                                                                                                                  | 93       |

| 4.9                | Gain loop transfer function. (a) Magnitude (b) Phase. PSS+PSTB                                                                                     | 96       |

| 4.10               | analyzes were performed for this result                                                                                                            | 90<br>98 |

| 4.10               | Proposed EMI resisting CMOS voltage reference schematic circuit.                                                                                   |          |

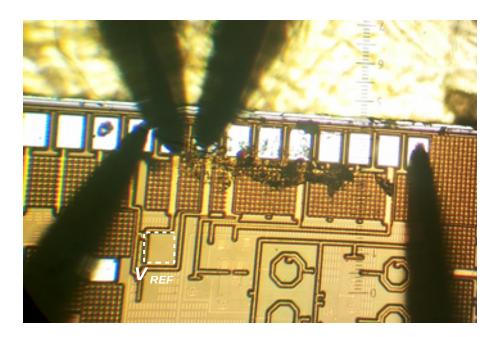

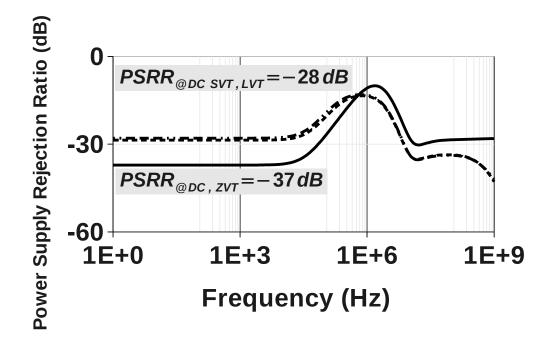

| 4.11               | $V_{REF}$ vs Temperature. (b) Power Supply Rejection Ratio of $V_{REF}$                                                                            | 98       |

| 4.12               | $V_{REF}$ Power Supply Rejection Ratio                                                                                                             | 99       |

| 4.13               | $V_{REF}$ Power Supply Rejection Ratio                                                                                                             | 99       |

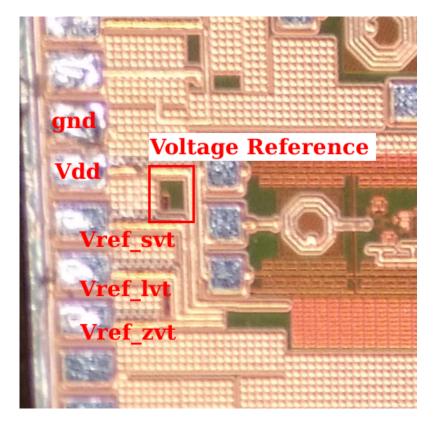

| 4.14               | Micrograph of a small area of the chip, fabricated in IBM 130nm,                                                                                   | 100      |

| ~                  | where the proposed $V_{REF}$ is highlighted                                                                                                        | 100      |

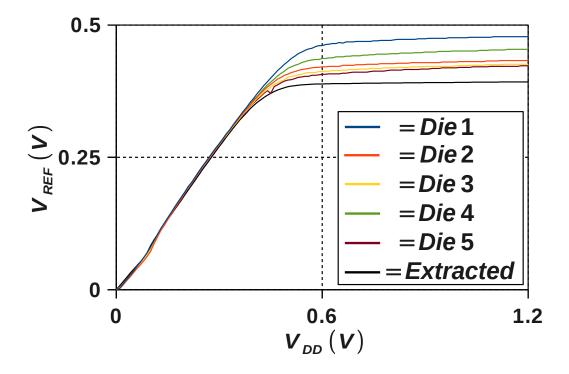

| 4.15               | $V_{REF}$ vs. $V_{DD}$ , dies # 1-5                                                                                                                | 101      |

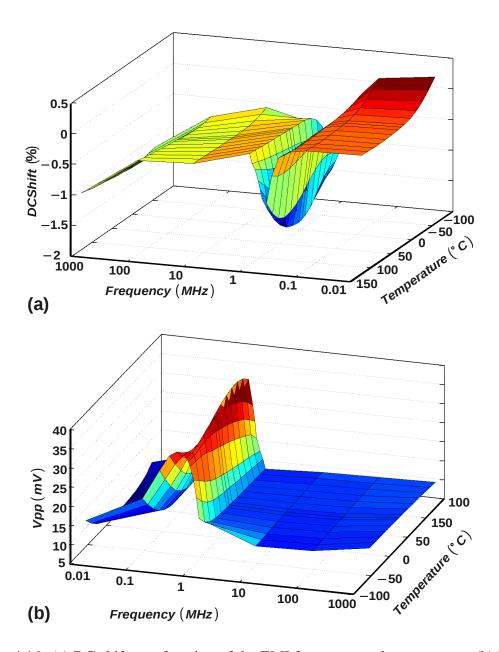

| 4.16               | (a) DC shift as a function of the EMI frequency and temperature. (b)                                                                               |          |

|                    | Peak-to-peak ripple on $V_{REF}$ as a function of the EMI frequency and                                                                            | 400      |

|                    | temperature. EMI level = 4 dBm                                                                                                                     | 102      |

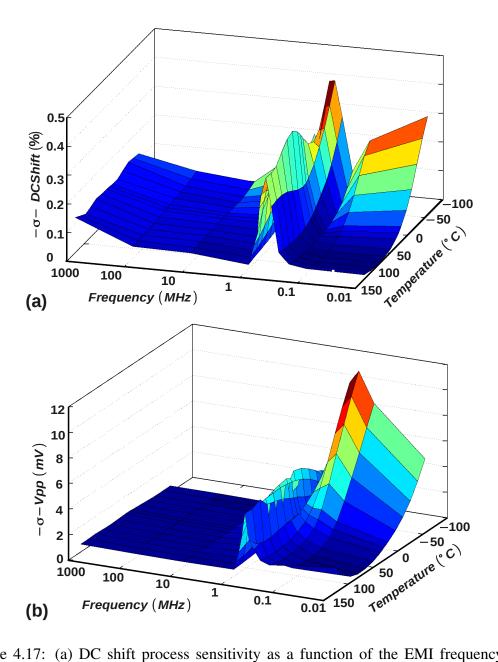

| 4.17               | (a) DC shift process sensitivity as a function of the EMI frequency                                                                                |          |

|                    | and temperature. (b) Peak-to-peak ripple process sensitivity on $V_{REF}$                                                                          |          |

|                    | as a function of the EMI frequency and temperature. EMI level = 4                                                                                  | 100      |

| 4.40               | dBm                                                                                                                                                | 103      |

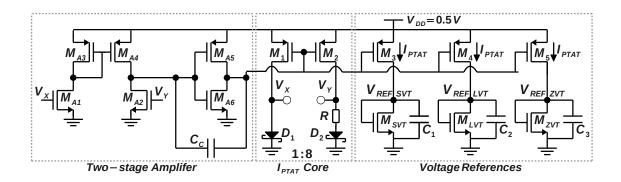

| 4.18               | Proposed 0.5-V CMOS voltage reference schematic circuit                                                                                            |          |

| 4.19               | PTAT current reference variation over temperature                                                                                                  |          |

| 4.20               | Voltage reference (standard- $V_T$ ) variation over temperature                                                                                    |          |

| 4.21               | Voltage reference (low- $V_T$ ) variation over temperature                                                                                         |          |

| 4.22               | Voltage reference (zero- $V_T$ ) variation over temperature                                                                                        |          |

| 4.23               | Power supply rejection ratio of the proposed voltage reference                                                                                     | 108      |

| 4.24               | Micrograph of our proposed 0.5 V Voltage Reference in IBM 130 nm                                                                                   |          |

|                    | die                                                                                                                                                | 109      |

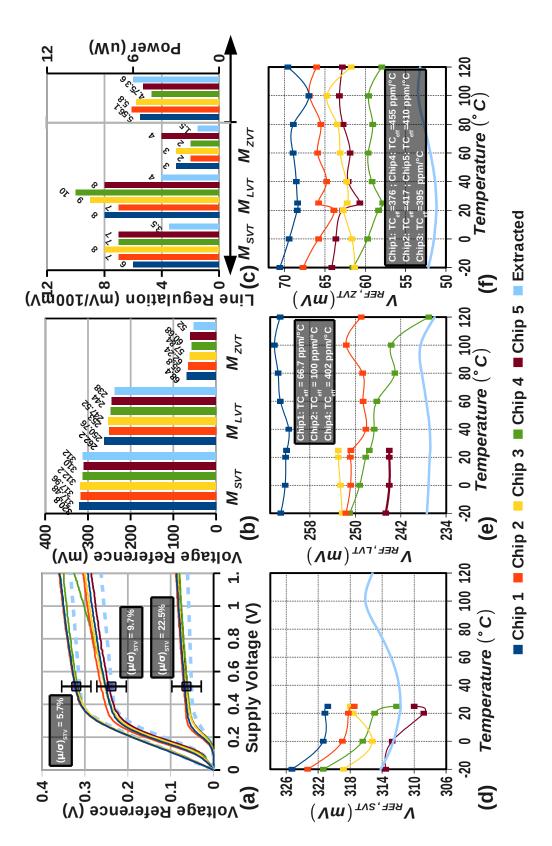

| 4.25               | (a) Measurements line sensitivity for 5 samples (b) $V_{REF}$ for each                                                                             |          |

|                    | sample (c) All Line Regulation (LR) measurements for each out-                                                                                     |          |

|                    | put (d,e,f) $V_{REF}$ versus temperature for $V_{REF,SVT}$ , $V_{REF,LVT}$ and                                                                     |          |

|                    | $V_{REF,ZVT}$ reference voltages, respectively                                                                                                     | 110      |

| 4.26               | (a) single-ended resistor emulator (b) impedance inverter (c) first or-                                                                            |          |

|                    | der filter (d) second order filter.                                                                                                                | 112      |

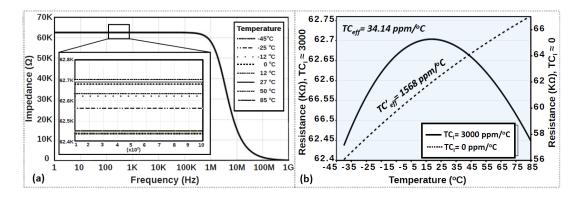

| 4.27               | (a) Input impedance of single-ended resistor emulator (b) Equivalent                                                                               |          |

|                    | Resistance vs. Temperature. Effective Temperature Coefficient is                                                                                   |          |

|                    | given by $TC_{eff} = rac{I_{REF_{max}} - I_{REF_{min}}}{(T_{max} - T_{min})I_{REF(T_0)}}$                                                         | 112      |

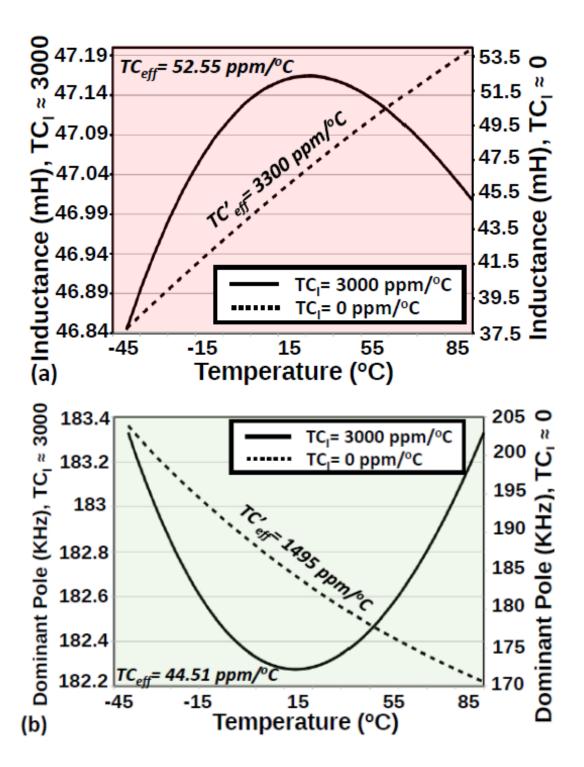

| 4.28               | (a) Equivalent Inductance vs. Temperature (b) Dominant Pole vs.                                                                                    |          |

|                    | Temperature                                                                                                                                        | 113      |

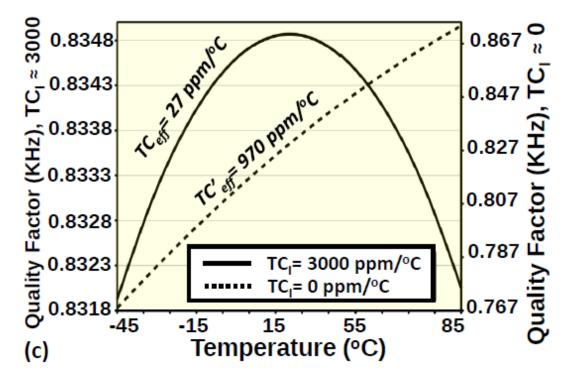

| 4.29               | Quality Factor vs. Temperature                                                                                                                     | 114      |

|                    |                                                                                                                                                    |          |

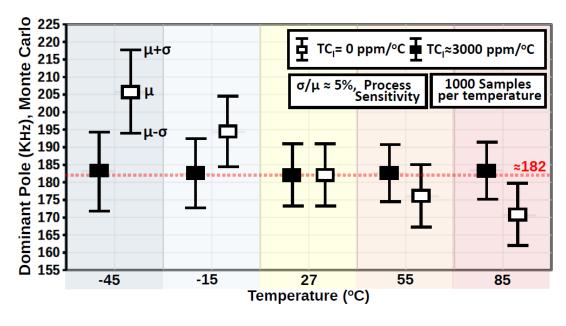

| 4.30 | Dominant pole Monte Carlo simulations for a temperature range of -45 to 85°C. For each temperature (-45,-15, 27, 55 and 85 °C), 1000 |

|------|--------------------------------------------------------------------------------------------------------------------------------------|

|      | samples were performed                                                                                                               |

| 5.1  | Second order effects on ZTC bias point                                                                                               |

| 5.2  | Short channel effects on ZTC bias point                                                                                              |

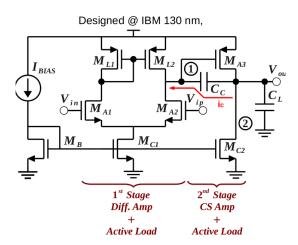

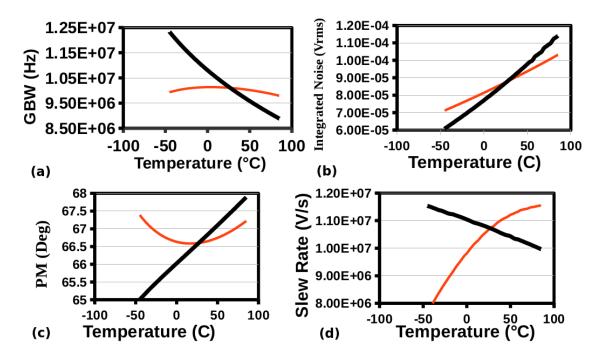

| A.1  | Classical two-stage Miller amplifier                                                                                                 |

| A.2  | Miller Amplifier: (a) GBW (b) Integrated Noise (c) PM (d) Slew Rate. 129                                                             |

| C.1  | Script Structure                                                                                                                     |

### **LIST OF TABLES**

| 2.1         | MOSFET Parameters extraction for 110 nm CMOS technology            | 38  |

|-------------|--------------------------------------------------------------------|-----|

| 2.2         | ZTC Operating Point with $\frac{W}{L} = \frac{10\mu m}{1\mu m}$    | 43  |

| 2.3         | MOSFET ZTC Operating Point                                         | 43  |

| 3.1         | Device Sizing of proposed ZSBCR                                    | 71  |

| 3.2         | Device Sizing of proposed ZSCCR                                    | 75  |

| 3.3         | Device Sizing of proposed EMIVR                                    | 81  |

| 3.4         | Device Sizing of proposed SBVR                                     | 84  |

| 4.1         | Comparison of CMOS Current References                              | 92  |

| 4.2         | Comparison of CMOS Current References                              | 97  |

| 4.3         | Simulated Performance of the voltage reference                     | 100 |

| 4.4         | Comparison with other works                                        | 104 |

| 4.5         | Simulated Performance of the SUB-1V $V_{DD}$ Schottky based refer- |     |

|             | ence                                                               | 108 |

| 4.6         |                                                                    | 109 |

| <b>A.</b> 1 | Miller amplifier specifications                                    | 129 |

### LIST OF ABBREVIATIONS AND ACRONYMS

CMOS Complementary metal-oxide-semiconductor

IC Integrated Circuits

ZTC Zero Temperature Coefficient

GZTC Transconductance Zero Temperature Coefficient

MOSFET Metal-oxide-semiconductor Field Effect Transistor

NMOSFET N-channel MOSFET

PMOSFET P-channel MOSFET

ZSCCR Resistorless Self-Biased ZTC Switched Capacitor Current Reference

ZSBCR ZTC Self-biased CMOS Current Reference

EMI Electro-Magnetic Interference

EMIVR EMI Resisting MOSFET-Only Voltage Reference

SBVR Schottky-based Voltage Reference

TCP/IP Transmission Control Protocol/Internet Protocol

SOC System-on-Chip

IOT Internet of Things

SDCR Software Defined Cognitive Radio

WSN Wireless Sensor Network

RF Radio Frequency

PA Power Amplifier

ISSCC International Solid-State Circuits Conference

MESFET Metal-Semiconductor Field Effect Transistor

SOI Silicon on Insulator

3D Three Dimensions

DC Direct Current

AC Alternate Current

UCCM Unified Charge-Control Model

ADF Analog Design Flow

UICM Unified Current Control Model

BSIM Berkeley Short-Channel IGFET Model

DIBL Drain-Induced Barrier Lowering

ITD Inverted Temperature Dependence

STA Static Timing Analysis

DTMOS Dynamic Threshold Voltage MOSFET

VLSI Very-Large-Scale Integration

PD-SOI Partially Depleted Silicon-on-Isolator

ZTCS ZTC Forward Inversion Level Surface

PTAT Proportional to Temperature Absolute Temperature

CTAT Complementary to Temperature Absolute Temperature

TC Temperature Coefficient

GZTCS GZTC Forward Inversion Level Surface

OTA Operational Transconductance Amplifier

KVL Kirchoff's Voltage Law

GBW Gain-bandwidth Product

FEA Feasibility Optimization

DNO Deterministic Nominal Optimization

YOP Yield Optimization

MIM Metal-Insulator-Metal

PSRR Power Supply Rejection Ratio

SBCR Self-Biased Current Reference

SCM Self-Cascode MOSFET

PN p-type and n-type

OA Operational Amplifiers

RC Resistor-Capacitor

CML Current-Mode-Latch

CL-LDO Capacitor-Less Low Drop-Out

PCB Printed-Circuit Board

LNTA Low Noise Transconductance Amplifier

LNA Low Noise Amplifier

PVT Process-Voltage-Temperature

IBM International Business Machines Corporation

MLM Multi-Layer Mask

MC Monte Carlo

PSS Periodic Steady-State

PSTB Periodic Stability

KHz KiloHertz

MHz MegaHertz

GHz GigaHertz

DPI Direct Power Injection

dBm decibel-milliwatts

dB Decibel

VR Voltage-Reference

LR Line Regulation

SVT Standard VT

LVT Low VT

ZVT Zero VT

IEEE Institute of Electrical and Electronics Engineers

### **CONTENTS**

| 1 II       | NTRODUCTION                                                                                              | 20 |

|------------|----------------------------------------------------------------------------------------------------------|----|

| 1.1        | Thermal effects in CMOS digital circuits                                                                 | 20 |

| 1.2        | Thermal effects in CMOS analog and mixed-signal circuits                                                 | 23 |

| 1.3        | Motivation                                                                                               | 25 |

| 1.4        | Contributions and Thesis Organization                                                                    | 25 |

| 2 T        | HE ZERO TEMPERATURE COEFFICIENT (ZTC) CONDITION                                                          | 27 |

| 2.1        | Continuous all-regime MOSFET model                                                                       | 28 |

| 2.2        | MOSFET thermal dependence                                                                                | 36 |

| 2.3        | ZTC Condition                                                                                            | 39 |

| 2.4        | MOSFET Bias ZTC Condition Analysis                                                                       | 48 |

| 2.4.1      | ZTC Bias from Strong Inversion MOSFET Model                                                              | 48 |

| 2.4.2      | ZTC Bias from UICM All-regime MOSFET Model                                                               | 50 |

| 2.4.3      | ZTC Bias Vicinity Condition from UICM Model                                                              | 54 |

| 2.5        | MOSFET Transconductance ZTC Condition                                                                    | 62 |

| 3 A<br>3.1 | ANALOG APPLICATIONS USING ZTC CONDITION Self-biased CMOS Current Reference based on ZTC Operation Condi- | 66 |

|            | tion - ZSBCR                                                                                             | 66 |

| 3.1.1      | Circuit Analysis                                                                                         | 67 |

| 3.1.2      | Circuit Design                                                                                           | 69 |

| 3.1.3      | Layout                                                                                                   | 70 |

| 3.2        | Resistorless Self-Biased ZTC Switched Capacitor Current Reference -                                      |    |

|            | ZSCCR                                                                                                    | 71 |

| 3.2.1      | Circuit Analysis and Design                                                                              | 72 |

| 3.2.2      | Layout                                                                                                   | 74 |

| 3.3        | <b>Electromagnetic Interference (EMI) Resisting MOSFET-Only Voltage</b>                                  |    |

|            | Reference - EMIVR                                                                                        | 75 |

| 3.3.1      | Circuit Analysis and Design                                                                              | 77 |

| 3.3.2      | Layout                                                                                                   | 81 |

| 3.4        | 0.5 V Supply Schottky-diode based Voltage Reference - SBVR                                               | 81 |

| 3.4.1      | Circuit Analysis and Design                                                                              | 82 |

| 3.4.2      | Layout                                                                                                   | 84 |

| 3.5        | GZTC Based Gm-C Filters                                                                                  | 85 |

| 3.5.1      | Circuit Analysis and Design                                                                              | 87 |

|                                                                                                                                                                                                                                                  | IONS AND MEASUREMENTS RESULTS                                                                                                                                                                        | 89                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

|                                                                                                                                                                                                                                                  | sed CMOS Current Reference based on ZTC Operation Condi-<br>SBCR                                                                                                                                     | 90                                                   |

| 4.2 Resistor ZSCCR                                                                                                                                                                                                                               | less Self-Biased ZTC Switched Capacitor Current Reference -                                                                                                                                          |                                                      |

| Referen<br>4.4 0.5 V Su                                                                                                                                                                                                                          | magnetic Interference (EMI) Resisting MOSFET-Only Voltage ce - EMIVR                                                                                                                                 | 105                                                  |

| 4.5 GZTC I                                                                                                                                                                                                                                       | Based Gm-C Filters                                                                                                                                                                                   | 111                                                  |

|                                                                                                                                                                                                                                                  | SION                                                                                                                                                                                                 |                                                      |

| REFERENCE                                                                                                                                                                                                                                        | s                                                                                                                                                                                                    | 119                                                  |

| LIST OF PUB                                                                                                                                                                                                                                      | LICATIONS                                                                                                                                                                                            | 126                                                  |

| APPENDIX A                                                                                                                                                                                                                                       | IMPACT OF TEMPERATURE VARIATIONS ON TWO-STAG                                                                                                                                                         | F                                                    |

| ,                                                                                                                                                                                                                                                | MILLER AMPLIFIER                                                                                                                                                                                     | _                                                    |

| $\begin{array}{ll} \textbf{B.1} & \frac{\partial \mu}{\partial T} = \frac{\mu \alpha}{T} \\ \textbf{B.2} & \frac{\partial \phi_t}{\partial T} = \frac{\phi}{T} \\ \textbf{B.3} & \frac{\partial \phi_t^2}{\partial T} = \frac{2}{T} \end{array}$ | EXPRESSIONS                                                                                                                                                                                          | 130<br>130<br>131                                    |

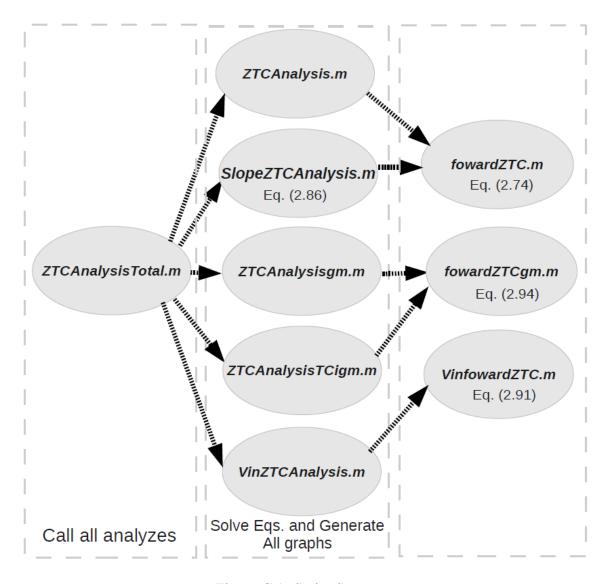

| C.1 ZTCAn<br>C.2 ZTCAn<br>C.3 SlopeZT<br>C.4 ZTCAn<br>C.5 ZTCAn<br>C.6 VinZTC<br>C.7 fowardZ<br>C.8 fowardZ                                                                                                                                      | OCTAVE SCRIPTS alysisTotal.m alysis.m CAnalysis.m alysisgm.m alysisTCigm.m CAnalysis.m                                                                                                               | 134<br>134<br>135<br>136<br>137<br>138<br>141<br>141 |

| <ul><li>D.2 MODEI</li><li>D.2.1 MODI</li><li>D.2.2 APLIC</li><li>D.3 CONCI</li></ul>                                                                                                                                                             | SUMMARY IN PORTUGUESE  DUÇÃO - CAPÍTULO 1  LAMENTO ZTC E SUAS APLICAÇÕES - CAPÍTULO 2, 3 E 4  ELAMENTO ZTC - CAPÍTULO 2  CAÇÕES BASEADAS EM ZTC - CAPÍTULO 3 E 4  LUSÃO - CAPÍTULO 5  EALHOS FUTUROS | 143<br>143<br>143<br>144<br>146                      |

### 1 INTRODUCTION

Solid-state circuits and temperature have had a close relationship since the beginning of electrical physical and electronics developments. In 1600 CE, William Gilbert described how increasing temperature reduced the attraction between oppositely charged objects [GILBERT (1600)]. In 1821 CE, Sir Humphry Davy presented to the Royal Society of London the results of an experiment in which [SMITH; CO (1840)] "the conducting power of metallic bodies varied with the temperature, and was lower, in some inverse ratio, as the temperature was higher." One year later, in 1822 CE, Thomas Johann Seebeck noted that when the junction temperature of two dissimilar metals increased, a current was created. This phenomenon is the Seebeck or thermoelectric effect [SEEBECK (1840)]. One of the most important temperature-related material discoveries happened in 1833 when Michael Faraday noticed that silver sulphide was conductive at high temperatures and nearly insulating at low temperatures [FARADAY (1839)]. This was in direct contrast to the temperature dependence observed in metals, which become less conductive as the temperature is increased. Faraday had discovered the semiconductor, and the reasoning behind this new relationship between temperature and current was later linked to the thermal excitation of carriers.

Afterwards, a similar principle was discovered by Jean Charles Athanase Peltier in 1834 CE, who found that when current flows through such a junction, heat is absorbed from one end of the junction and moved to the other [PELTIER (1834)]. This effect is material dependent; the material's majority carrier determines whether heat flows in the same direction as the current or the opposite direction. The Peltier effect (or Peltier–Seebeck effect) is now commonly used in electronic heat transfer and cooling systems, including small electric refrigerators. The Peltier and Seebeck effects have also been examined for regulating chip temperature and recycling thermal energy back into electrical[GOULD et al. (2008)]. The findings of Davy, Seebeck, Peltier, and Faraday have laid the foundation for the impact of temperature on current electronic systems.

### 1.1 Thermal effects in CMOS digital circuits

In current literature, there are two definitions of temperature variation that can affect system performance: global temperature variations and local temperature variations. Changes in ambient temperature or cooling capacity cause global temperature variations (Cooler uses Seebeck-Peltier effect to control and minimize the impact of temperature on chip performance). For instance, the United States military IC requirements define the range of ambient temperature extend from -55 °C to 125 °C as operation regime [DE-FENSE (2012)]. The intra-die disparity in power dissipation between active units and inactive units can result in severe hot spots on a chip. These disparities define local tem-

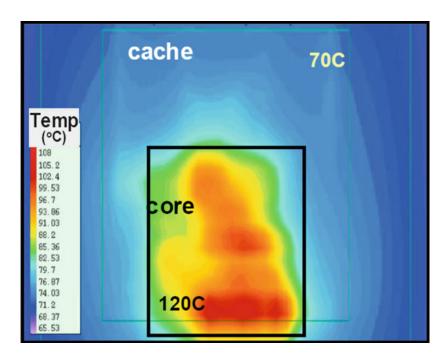

Figure 1.1: Thermal map of an integrated microprocessor highlighting on-chip temperature variation. Temperature gradient between a microprocessor core and an on-chip cache.

perature variation. Intra-die temperature variations exceeding 50  $^{o}$ C have been reported at [SATO et al. (2005)].

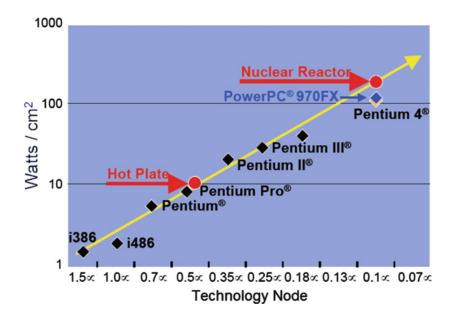

From current CMOS digital design point of view, power dissipation in silicon is related to temperature through the material's thermal conductivity, measured in Watts per meter Kelvin (W/(m·K)). This relation translates as where in the digital core the activity is concentrated, and the temperature is the highest. At the same time, variations in temperature affect the conductivity of the material, i.e., alters transistor performance inside of each logic gate, which affects the speed of computation in the systems. These changes in temperature inside digital circuits can have catastrophic effects on system performance and functionality, and are becoming increasingly problematic as technologies scale. In other words, as power dissipation increase beyond our ability to distribute and remove the generated heat, local temperatures will continue to rise. The potential for delay failure will grow consequently affecting the time slack of the whole system. To illustrate, Fig. 1.1 shows a typical thermal map between a cache memory and an integrated microprocessor [SATO et al. (2005)]. In more advanced technological nodes, thermal activity has been more aggressive as shown in Fig. 1.2. The cause is due to more powerful digital processing capability per area [SATO et al. (2005)].

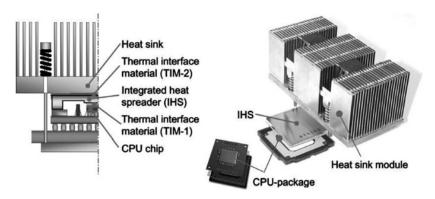

The performance degradation in CMOS digital circuits due to changes in temperature (global temperature variation) and/or problem of power dissipation (local temperature variation) has brought about the development of better cooling systems (external temperature control) and immense improvements in optimizing on-chip power dissipation (internal temperature control). Fig. 1.3 shows a common implementation of a passive cooling system, including the chip, heat spreader, and heat sink [WOLPERT; AMPADU (2012)]. Thermal interface material is a high thermal conductivity substance used to improve the flow of heat between each separate component. This technique is a method to control the IC temperature externally.

Besides external thermal control (e.g. using cooler), on-chip mechanisms for thermal

Figure 1.2: Impact of technology scaling on power density.  $\alpha$  features each technological node ( $\mu m$ ).

Figure 1.3: CPU cooling system.

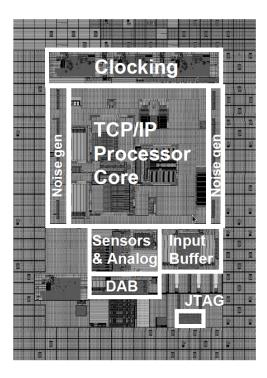

control can be adopted as well. In applications with larger power densities, digital designers can try to reduce the occurrence of hotspots. They can, for example, be reduced at design level using thermally-aware floorplanning techniques [WOLPERT; AMPADU (2012)], in which units with large power dissipation are spread evenly across the chip. Another strategy is to use adaptive measures such as thermal throttling which improve reliability by adjusting the processor frequency and supply voltage when high-temperature spots are detected. For instance, Fig. 1.4 shows a TCP/IP offload accelerator engine fabricated in 90nm CMOS, which improves reliability by adjusting the processor frequency and supply voltage when high-temperature conditions are identified. These adaptive systems can be useful for mobile applications as well, detecting when a chip is brought into a hot environment and reducing its processor speed to avoid timing failures [TSCHANZ et al. (2007)].

Figure 1.4: TCP/IP offload accelerator engine fabricated in 90nm CMOS.

### 1.2 Thermal effects in CMOS analog and mixed-signal circuits

In addition to ambient temperature variations, temperature changes due to internal power dissipation also affect analog circuits. Bias conditions and performances such as gain, bandwidth, slew rate, offsets, noise, impedance, stability are modified (See, for example, the temperature variation impact on classical CMOS two-stage Miller Amplifier in Appendix A). This effect has been more evident on the current trend of mixed-signal System-on-Chip (SoC) solutions. Internet of Things (IoT), Software Defined Cognitive Radios (SDCR), and Wireless Sensor Network (WSN) are few applications examples that enforce even more the current trend for SoC solutions: integration of digital and Analog/RF parts in a unique chip [NARENDRA; FUJINO; SMITH (2015)]. For these IC systems, variations on circuit performance changed by different temperature operation will be increasingly visible, thus justifying that techniques to mitigate these performances degradations is of great importance for analog circuits. Fig 1.5 depicts some current (2000-2015) state-of-art SoCs that have the digital and Analog/RF part integrated into the same die.

The digital core is not the only responsible for chip self-heating (Section 1.1). In wireless communications SoCs, for example, some Radio Frequency (RF) blocks are also power hungry. The Power Amplifier (PA) will also contribute to SoC temperature increase. Fig. 1.6 shows state-of-art Ultra-low-power 2.4-GHz wireless transmit efficiency (PA inside it), and it reveals that commercial chips consuming around 30-100 mW with efficiency between 3-30% can be found in the market. This power consumption level certainly contributes to the change of temperature profile spread all over SoC. Indeed, ambient temperature, digital core operation mode, and analog circuit consumption cause temperature variation within a mixed-signal SoC. This variation demands that, in addition to proper functioning of the digital part, the analog section must operate correctly fulfilling all required performances under the required temperature range.

Figure 1.5: Trends in integration strategies.

Figure 1.6: Ultra-low-power 2.4-GHz wireless transmit efficiency. The arrow shows the desired trends. All symbols except the red squares represent ISSCC papers. The ISSCC 2015 paper numbers are indicated next to the red circles.

#### 1.3 Motivation