## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

### VINÍCIUS DAL BEM

# SAT-Based Environment for Logical Capacity Evaluation of Via-Configurable Block Templates

Thesis submitted in partial fulfillment of the requirements for the degree of Doctor in Microelectronics.

Advisor: Prof. Dr. Renato Perez Ribas Co-advisor: Prof. Dr. André Inácio Reis

### CIP - CATALOGAÇÃO NA PUBLICAÇÃO

Dal Bem, Vinícius

SAT-Based Environment for Logical Capacity Evaluation of Via-Configurable Block Templates / Vinícius Dal Bem. – 2016. 95 f.:il.

Orientador: Renato Perez Ribas; Co-orientador: André Inácio Reis. Tese (Doutorado) — Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica. Porto Alegre, BR — RS, 2015.

Manufacturing yield. Nanometer technology. Photolithography. Structured ASIC. Regular layout. Via-configurable. CAD. Computer Aided Design. SAT. Satisfiability. Block templates. Logical capacity

1.Manufacturing yield. 2.Nanometer technologies. 3. Photolithography. 4. Structured ASIC. 5.Regular layout. 6. Viaconfigurable. 7.CAD. 8.Computer Aided Design. 9.SAT. 10. Satisfiability. 11. Block templates. 12. Logical capacity. I. Ribas, Renato Perez. II. Reis, André Inácio. III. SAT-Based Environment for Logical Capacity Evaluation of Via-Configurable Block Templates.

#### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos Alexandre Netto

Vice-Reitor: Prof. Rui Vicente Oppermann

Pró-Reitor de Pós-Graduação: Prof. Vladimir Pinheiro do Nascimento

Diretor do Instituto de Informática: Prof. Luís da Cunha Lamb

Coordenador do PGMICRO: Profa. Fernanda Gusmao de Lima Kastensmidt Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

#### ACKNOWLEDGEMENTS

I hope the readers don't mind, but I'll allow myself writing the acknowledgements in Portuguese so my gratitude will be better transmitted.

Dedico esta tese à minha esposa, Daniela, que me apoiou infinitamente, que nos momentos mais difíceis transformou cansaço e angústia em sorrisos, e que fez com que um futuro vazio se transformasse na visão de uma vida feliz. Obrigado, amo você!

Agradeço à minha família, pelo carinho, pelo suporte emocional e financeiro, e pelo exemplo de dedicação ao trabalho.

Agradeço à Renato Perez Ribas e Paulo Francisco Butzen, por serem referências para mim, pessoais e profissionais, durante toda essa jornada acadêmica.

Agradeço aos meus amigos, por compartilharem sua genialidade no meio profissional e pelos momentos de alegria fora dele.

#### **ABSTRACT**

Structured ASICs with regular layouts comprise a design-based solution for IC manufacturing yield loss in nanometer technologies caused by photolithography distortions. Via-configurable structured ASICs is even a more restrictive digital IC design method, based on the repetition of a block template comprising all layout layers except the vias one. The choice of such a design strategy impacts greatly the final circuit characteristics, arising the need for specific CAD tools to allow template evaluation and comparison in different aspects. This work presents a SAT-based CAD environment for evaluating the logical capacity aspect of viaconfigurable block templates. The proposed environment is able to support any user-defined template, and behaves efficiently when applied to block templates presented in related literature.

**Keywords**: Manufacturing yield. Nanometer technology. Photolithography. Structured ASIC. Regular layout. Via-configurable. CAD. Computer-aided design. SAT. Satisfiability. Block templates. Logical capacity. Digital IC design.

# Ambiente SAT para Avaliação da Capacidade Lógica de Padrões de Bloco Configuráveis por Vias

#### **RESUMO**

ASICs estruturados com leiautes regulares representam uma das soluções para a perda de rendimento de fabricação de circuitos integrados em tecnologias nanométricas causada pela distorção de fotolitografia. Um método de projeto de circuitos integrados ainda mais restritivo resulta em ASICs estruturados configuráveis apenas pelas camadas de vias, que são compostos pela repetição do mesmo modelo de bloco em todas as camadas do leiaute, exceto as camadas de vias. A escolha do modelo de bloco tem grande influência nas características do circuito final, criando a demanda por novas ferramentas de CAD que possam avaliar e comparar tais modelos em seus diversos aspectos. Esta tese descreve um ambiente de CAD baseado em SAT, capaz de avaliar o aspecto de capacidade lógica em padrões de blocos configuráveis por vias. O ambiente proposto é genérico, podendo tratar quaisquer padrões de bloco definido pelo usuário, e se comporta de maneira eficiente quando aplicado aos principais padrões já publicados na literatura.

**Palavras-chave**: Rendimento de fabricação. Tecnologias nanométricas. Fotolitografia. ASICs estruturados. Leiaute regular. CAD. SAT. Modelos de bloco. Capacidade lógica. Circuitos integrados digitais.

# FIGURES LIST

| Figure 1.1 - Manufacturing variability changing the electrical characteristics of dies, in this case, frequency and standby leakage current of microprocessors in a wafer. (BOKAR, 2003) |       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|                                                                                                                                                                                          | .12   |

| Figure 1.2 - Discrepancy between drawn layout (assuming perfect rectangle shapes) and                                                                                                    |       |

| manufactured circuit layers by photolithography process (KUHN, 2007)                                                                                                                     | .13   |

| Figure 1.3 - Scheme connecting this thesis to the introduced scenario of yield loss and one                                                                                              |       |

| its main sources: photolithography process distortions.                                                                                                                                  |       |

| Figure 2.4 - Relationship among regular layouts, via-configurable layouts, structured ASIC                                                                                               |       |

| and via-configurable structured ASICS (VCSA).                                                                                                                                            |       |

| Figure 2.5 - Block template example (a); and the vias configuration in this template example                                                                                             |       |

|                                                                                                                                                                                          |       |

| to implement an INV (b) and a NOR3 (c) logical functions.                                                                                                                                | . 1 / |

| Figure 2.6 - Block template example (a), a NOR3 logical function implemented by                                                                                                          | 1.0   |

| configuring two block instances (b) and a circuit designed by VCSAs combination (c)                                                                                                      |       |

| Figure 2.7 - 5-VCC block template (a) and INVA block template (b)                                                                                                                        |       |

| Figure 2.8 - VCGA block built by the association of VCC and INVA blocks (RAN, 2006).                                                                                                     |       |

| Figure 2.9 - Example of transistor networks that can (a) and can not (b) be expressed in a 5-                                                                                            |       |

| VCC.                                                                                                                                                                                     |       |

| Figure 2.10 - VCTA-6T block template.                                                                                                                                                    | .22   |

| Figure 2.11 - VCTA design method for blocks placement (with mirrored diffusions) and                                                                                                     |       |

| global routing (with metal line extensions).                                                                                                                                             |       |

| Figure 2.12 - VCLB-SLVC5P block template.                                                                                                                                                |       |

| Figure 2.13 - VCLB design method for blocks placement and global routing                                                                                                                 |       |

| Figure 2.14 - Polysilicon masks based on VCTA (a), VCC (b), INVA (c), VCLB (d)                                                                                                           |       |

| Figure 2.15 - M1 masks based on VCTA (a), VCC (b), INVA (c), VCLB (d)                                                                                                                    |       |

| Figure 2.16 - Comparison between drawn layout (a) and lithography simulation (b) of patte                                                                                                | rn    |

| samples.                                                                                                                                                                                 | .26   |

| Figure 2.17 - Neighboring influence: aggressive (a), negligible (b) and helpful (c)                                                                                                      | .27   |

| Figure 2.18 - EPE hotspots, achieved from lithography simulation on masks depicted in                                                                                                    |       |

| Figure 2.14 and in Figure 2.15, followed by image inspection algorithm.                                                                                                                  | .28   |

| Figure 2.19 - M1 and polysilicon histograms of edge placement error (EPE) values, obtaine                                                                                                |       |

|                                                                                                                                                                                          | .29   |

| Figure 2.20 - Design flow in (LI, 2008) at left, (DAL BEM, 2011b) at right, evidencing the                                                                                               |       |

| use of a characterizer to compose a library that is used by a mapping tool                                                                                                               |       |

| Figure 2.21 - Flow for defining the lists of functions                                                                                                                                   |       |

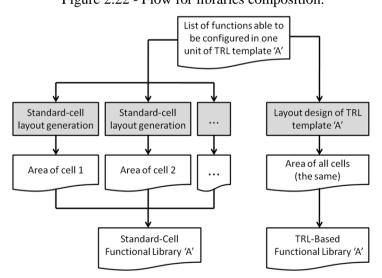

| Figure 2.22 - Flow for libraries composition.                                                                                                                                            |       |

| Figure 2.23 - Aspects to consider when evaluating design quality of a VCSA template                                                                                                      |       |

| Figure 4.24 - SAT-based flow for VCSA block templates logical capacity evaluation                                                                                                        |       |

| Figure 4.25 - Examples of possible diffusion layouts.                                                                                                                                    |       |

| Figure 4.26 - Examples of possible poly matching among p and n planes.                                                                                                                   |       |

| Figure 4.27 - Layout elements taken in consideration in a sample layout.                                                                                                                 |       |

| Figure 4.28 - Nodes taken in consideration in a sample transistor network                                                                                                                |       |

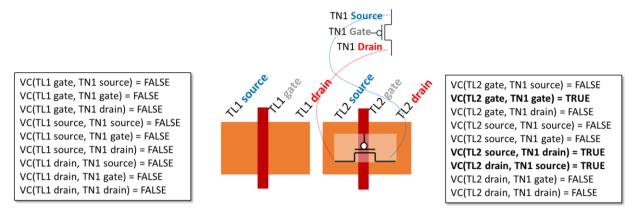

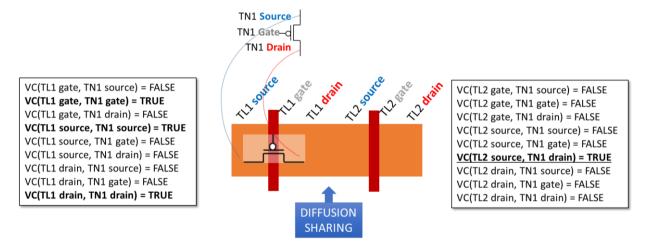

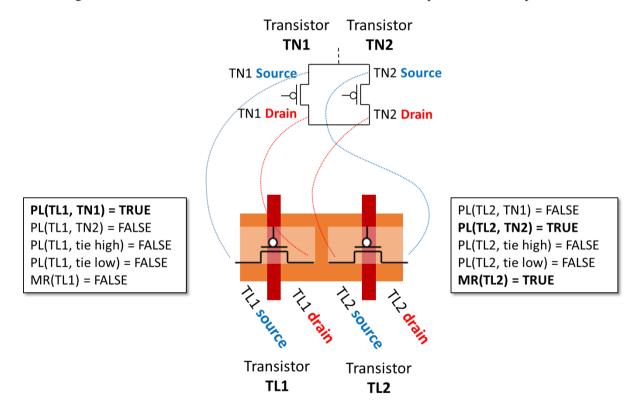

| Figure 4.29 - VC variables crossing layout elements with network nodes.                                                                                                                  |       |

| Figure 4.30 - Very simple examples layout template and transistor network                                                                                                                |       |

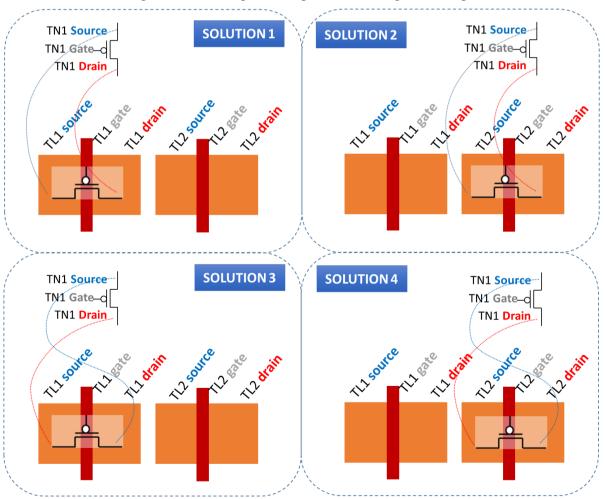

| Figure 4.31 - Fitting solution possibilities on given example.                                                                                                                           |       |

|                                                                                                                                                                                          |       |

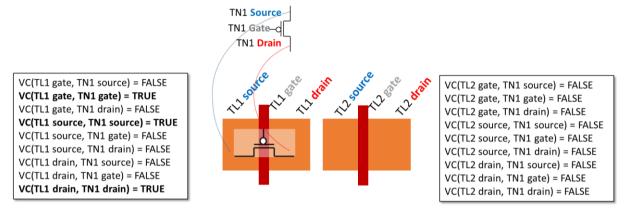

| Figure 4.32 - Expected values on VC variable of solution 1                                                                                                                               |       |

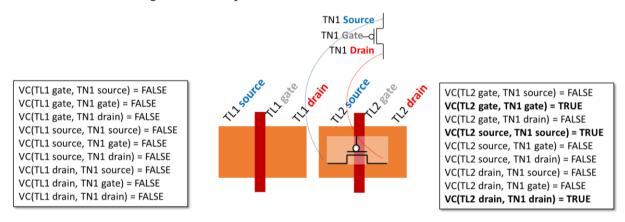

| Figure 4.33 - Expected values on VC variable of solution 3                                                                                                                               |       |

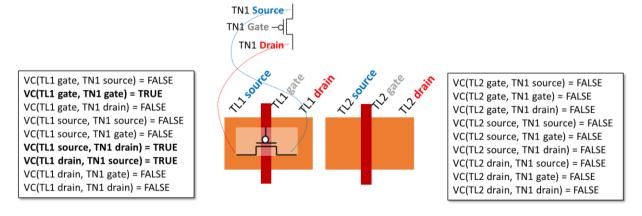

| Figure 4.35 - Expected values on VC variable of solution 4                              | 56  |

|-----------------------------------------------------------------------------------------|-----|

| Figure 4.36 - Diffusion sharing case: TRUE value in VC "spreads" over connected element | ts. |

|                                                                                         | 56  |

| Figure 4.37 - Variables PL and MR attribution and its visual "placement" interpretation | 58  |

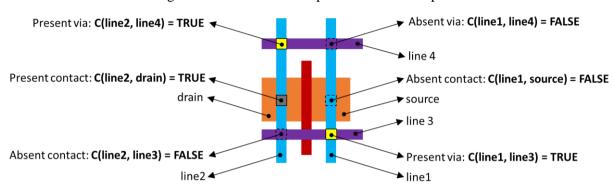

| Figure 4.38 - Variable C expected values example.                                       | 59  |

| Figure 4.39 - Example of poly and diffusion rules' application                          | 60  |

| Figure 4.40 - Unidirectional upward propagation concept illustration                    | 61  |

| Figure 4.41 - VC variable TRUE value propagating upward trough virtual layers           | .64 |

| Figure 4.42 - Hierarchy and dependencies of variables and rules of developed SAT model. | 66  |

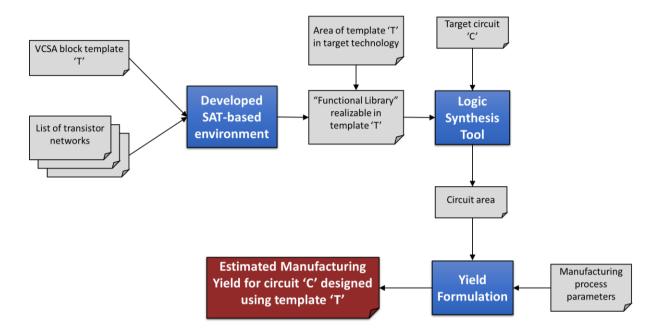

| Figure 5.43 - Realizable networks of Nangate Open Cell Library in three VCSA templates. | .70 |

| Figure 5.44 - Realizable networks of 4-inputs PClass in three VCSA templates            | 71  |

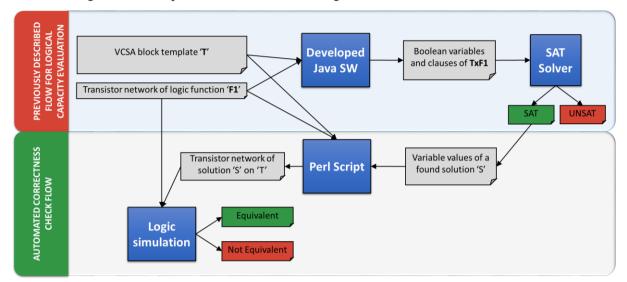

| Figure 5.45 - Implemented flow for checking correctness of reached SAT results          | 73  |

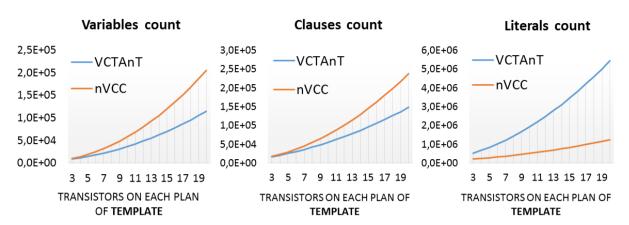

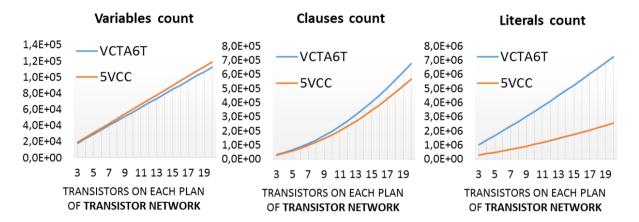

| Figure 5.46 - Two instances of 5VCC block template described as a new template          | 74  |

| Figure 5.47 - Developed SAT model variables, clauses and literals count behavior as     |     |

| templates transistors count increases                                                   | 75  |

| Figure 5.48 - Developed SAT model variables, clauses and literals count behavior as     |     |

| transistor networks increase.                                                           | 75  |

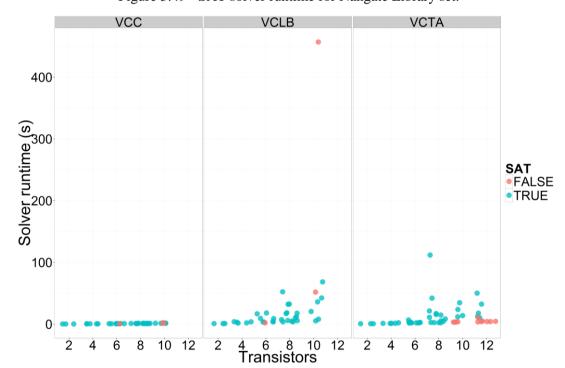

| Figure 5.49 - SAT solver runtime for Nangate Library set.                               | 76  |

| Figure 5.50 - SAT solver runtime for 4-input P-Class.                                   | 77  |

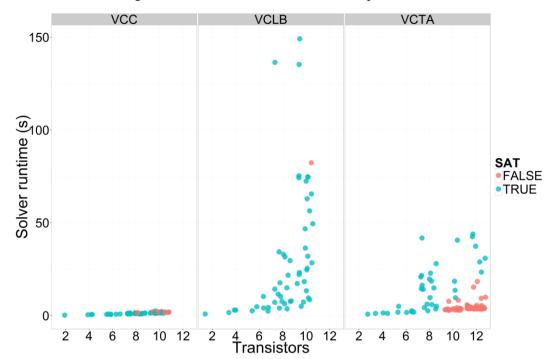

| Figure 6.51 – Manufacturing yield estimation flow for a given VCSA template and target  |     |

| circuit.                                                                                | 79  |

# **TABLES LIST**

| Table 2.1 - Average and worst cases of EPE                                                | 29 |

|-------------------------------------------------------------------------------------------|----|

| Table 2.2 - n-ViaCC-realizable non-equivalent functions (RAN, 2006a)                      | 35 |

| Table 2.3 - Functional coverage of n-ViaCC (RAN, 2006a)                                   | 35 |

| Table 2.4 - Number of logic functions from the input list which fits each tested VCTA     |    |

| template variants, according their resources                                              | 37 |

| Table 2.5 - Number of cells in standard-cell library example and one VCLB variant, called |    |

| SLV5P (TUNG, 2011)                                                                        | 37 |

| Table 5.6 - Library transistor networks SAT results for several VCSA templates            | 68 |

| Table 5.7 - Summary of runtime (in seconds) of solver run on Nangate Library networks set |    |

|                                                                                           | 77 |

#### LIST OF ABREVIATIONS

2D Two-Dimensional

ASIC Application Specific Integrated Circuit

BDD Binary Decision Diagram CAD Computer Aided Design

CMOS Complementary Metal-Oxide-Semiconductor

CNF Conjunctive Normal Format

CSC Complete State Coding

DFM Design for Manufacturing

EPE Edge Placement Error

ESD Electrostatic Discharge

FPGA Field-Programmable Gate Array

GND Ground Supply

HCI Hot-Carriers Injection

IC Integrated Circuit

INVA Inverters Array

NBTI Negative Bias Temperature Instability

OPC Optical Proximity Correction

PD Pull-Down

PDK Process Design Kit

PU Pull-Up

PLA Programmable Logic Array RAM Random Access Memory

RET Resolution Enhancement Techniques

SAT Satisfiability

SEE Single Event Effects SOC System-on-Chip

STG Signal Transistion Graphs

TDDB Time Dependent Dielectric Breakdown

TRL Transistors Regular Layout

TTSPM Two-terminal Series-Parallel Multigraph)

VCC Via-Configurable Cell

VCGA Via-Configurable Gate Array

VCLB Via-Configurable Logic Block

VCSA Via-Configurable Structured ASICs

VCTA Via-Configurable Transistors Array

VDD Power supply

# **SUMMARY**

| 1 INTRODUCTION                                                 | 12             |

|----------------------------------------------------------------|----------------|

| 2 VIA-CONFIGURABLE STRUCTURED ASICS (VCSA)                     | 16             |

| 2.1 VCSA Block Templates                                       |                |

| 2.2 VCSA Block Templates in Literature                         | 19             |

| 2.2.1 VCC                                                      | 19             |

| 2.2.2 VCTA                                                     | 21             |

| 2.2.3 VCLB                                                     | 22             |

| 2.3 Evaluation Methods of VCSA Block Templates                 | 24             |

| 2.3.1 Lithography-based Evaluation                             | 24             |

| 2.3.2 Electrical Performance Evaluation                        | 30             |

| 2.3.3 Logical Capacity Evaluation                              | 31             |

| 3 SAT IN CAD                                                   | 39             |

| 3.1 Definitions                                                | 39             |

| 3.2 SAT Complexity                                             | 40             |

| 3.3 SAT Application in CAD Problems                            | 41             |

| 3.4 Case of interest: standard-cells regular routing using SAT | 43             |

| 4 SAT MODEL FOR VCSA BLOCKS LOGICAL CAPACITY EVALU             | <b>ATION48</b> |

| 4.1 Requirements                                               | 48             |

| 4.2 SAT Model Construction                                     | 51             |

| 5 EXPERIMENTAL RESULTS                                         | 67             |

| REFERENCES                                                     | 80             |

| APPENDIX A - CLASS DIAGRAM OF IMPLEMENTED SOFTWARE.            | 86             |

| APPENDIX B - TEXTUAL DESCRIPTION OF VCSA BLOCK TEMPL           | ATES86         |

#### 1 INTRODUCTION

In the last decades, the microelectronics industry advancing has been strongly based on the dimensions reduction of manufactured semiconductor devices. However, as CMOS technology shrinks, a series of previously ignored effects has become significant and new manufacturing and design challenges arise.

Negative-bias temperature instability (NBTI) can be mentioned as a transistors aging effect that became more aggressive in most recent technologies, being treated in massive research work (VATTIKONDA, 2006; BUTZEN, 2010; BUTZEN, 2012).

Among other effects that presenting similar characteristics are single-event effects (SEE), electrostatic discharge (ESD), time-dependent dielectric breakdown (TDDB), hot-carriers injection (HCI), IR-drop, electromigration and, as the main subject of this work: manufacturing variability (BOKAR, 2003; ORSHANSKY, 2008; WONG, 2008)

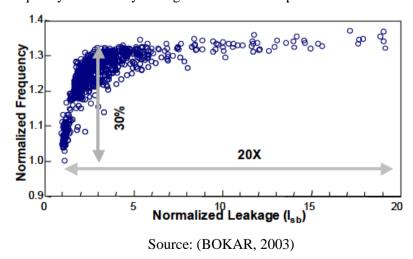

Manufacturing variability impacts directly the production yield as it may change some die characteristics to beyond the specifications, as illustrated in Figure 1.1. Even when the manufacturing variation is not critical enough to cause pre-sale rejection of dies, it may reduce their operation margins, automatically limiting their lifetime against the mentioned aging effects.

Figure 1.1 - Manufacturing variability changing the electrical characteristics of dies, in this case, frequency and standby leakage current of microprocessors in a wafer.

The manufacturing variability in nanometer technologies is caused by a variety of sources, and can be classified as random, like dopants distribution, and as systematic, like photolithography distortions. This thesis focuses on the last one, illustrated in Figure 1.2.

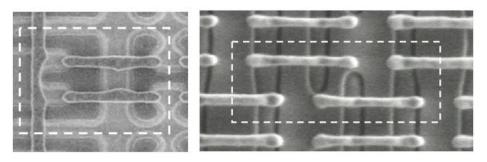

Figure 1.2 - Discrepancy between drawn layout (assuming perfect rectangle shapes) and manufactured circuit layers by photolithography process.

Source: (KUHN, 2007)

Even more specifically, this work focuses on a single design strategy for reducing the photolithography distortion that is the use of via-configurable regular layouts. Such layouts comprise a small set off patterns, easing the tuning of the manufacturing process.

Alternative solutions to photolithography distortion problems include resolution enhancement techniques (RETs) as optical proximity correction (OPC) (CHIANG, 2007). OPC is an automatic layout changing procedure which aims to increase the similarity between the (originally) drawn layout and the produced die. Techniques for increasing design robustness, like inserting logic redundancy or increasing operation margin, do not reduce the suffered variation but mitigates its impact. However, both mentioned solutions do not bring the regular layouts benefits: predictable layout neighboring influence and, in cases where some layers are made by a repeated standard, the reduced production cost and fasten time-to-market. Moreover, all mentioned solutions may be combined.

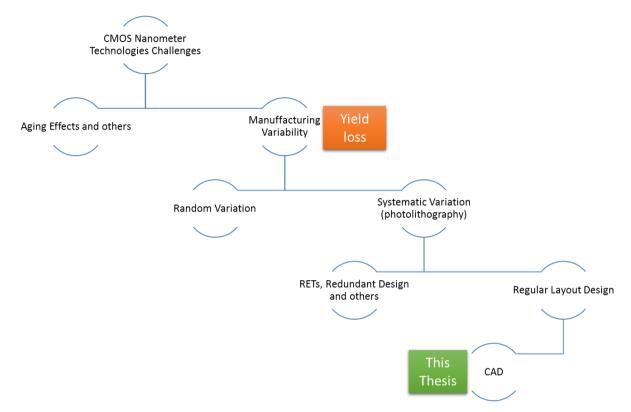

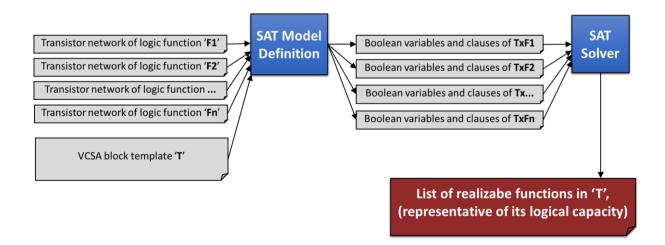

The main goal of this thesis is to present a novel CAD environment to solve feasibility of a transistors network on a pre-defined layout template. Such CAD environment aims to increase efficiency of design methods based on via-configurable regular layouts, contributing to reduce photolithography distortion, so reducing manufacturing variability and increasing production yield. Figure 1.3 summarizes this proposal and its relationship to the stated problems and alternative solutions.

More specifically, the main contribution of the proposed CAD tool is to be able to answer if a given logic transistors network can be expressed in a given VCSA (viaconfigurable structured ASICs) layout template.

The main open question investigated herein is whether there is an automated, efficient and exact (not heuristic) method based on Boolean formulation to reach such answer.

Figure 1.3 - Scheme connecting this thesis to the introduced scenario of yield loss and one of its main sources: photolithography process distortions.

Once a general mechanism to reach this answer is built, the logical capacity of any VCSA layout template can be evaluated by repeating the process for several transistor networks. Choosing the VCSA layout template with higher logical capacity is expected to cause a reduction in the final circuit area and, consequently, amortizing manufacturing yield loss.

Until the present date, no other author has published a tool or method able to accomplish this goal for any transistor network and any layout template. The tools in related literature are always made for a specific layout template as will be detailed later on this text.

The remaining of this text is organized as follows: Chapter 2 provides the needed background in Via-Configurable Structured ASICs (VCSAs) and the main proposed block templates in related literature; Chapter 3 contains an introduction about computer-aided design (CAD) problems translated to satisfiability (SAT) models; Chapter 4 describes the developed SAT model for extracting the logical capacity of VCSA block templates; Chapter 5 brings achieved results, whereas Chapter 6 draws conclusions and insights about future work.

#### 2 VIA-CONFIGURABLE STRUCTURED ASICS (VCSA)

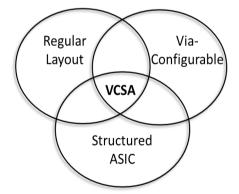

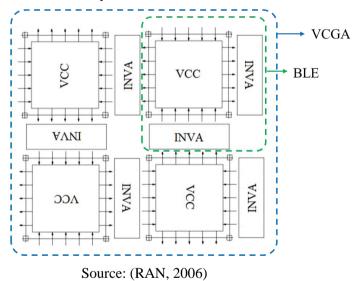

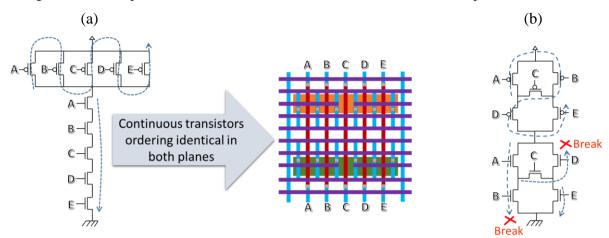

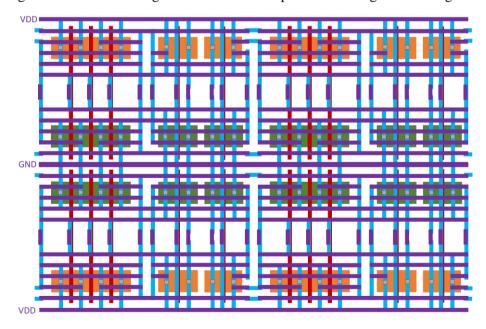

The target design method or layout strategy may intersect to various labels. "Structured ASIC" is often used to refer layouts made by repeating a block template, as in (TSAI, 2012) and in (TUNG, 2012). This expression may be used when the layout is configurable by via layers, as mentioned in the references. However, it is not always restricted to this characteristic. "Regular fabrics" or "regular layout" are also labels used for this kind of design method, as in (RAN, 2004a; RAN, 2004b). Moreover, they are too general, being used in regular cells design methods, as observed in (JHAVERI, 2010), and even to refer some routing strategies (SUTO, 2012). Thus, to avoid misunderstandings, from now on, the default label to refer the studied design method will be the very specific term "Via-Configurable Structured ASICs" (VCSA). This way, it becomes clear that we are focusing on regular layouts (or fabrics) composed by some standard blocks repetition (structured ASIC). However, the only non-repetitive layer used for the circuit functionality configuration are the via layers. Figure 2.4 highlights of the chosen design method and its resulting layout class.

Figure 2.4 - Relationship among regular layouts, via-configurable layouts, structured ASICs and via-configurable structured ASICS (VCSA).

Among the reasons to explore VCSAs are: the reduced production and mainly redesign cost, due to the reduced set of configurable masks; the reduction on layout design costs, since a single template is used for all digital cells; the extremely predictable layout neighboring influence, reducing uncertainty and variations on manufactured circuit, as well as increasing RETs adherence.

Mask-configurable gate arrays (MPGAs) do not represent a new design approach, as demonstrated by Van Noije's proposal (VAN NOIJE, 1985), and several following optimizations, as Quick Customized Logic (QCL) (DONG, 1993) and Maragata (LIMA,

2000), all customizable by metal layers. However, such previous work did not focus on lithography optimization or manufacturing variability mitigation, but in reducing costs through pre-manufactured layers (possibly shared among several customers) and faster design or prototyping cycles. Therefore, even fitting the concept of mask-programmable gate arrays, a VCSA differ fundamentally from these past approaches as it presents pre-designed layers instead of pre-manufactured ones, and also the concern of a litho-friendly regular layout, even more restrictive than older MPGAs. Other modern regular mask-programmable design approaches, as in (BOBBA, 2015), also differ from VCSAs in the same point: not intended for lithography process, but for other manufacturing process candidates.

It is important to state clearly that the VCSA design method is not proposed herein, it is just a naming convention adopted in this text and absent in related literature using this design method, as each paper seems to adopt a different term.

#### 2.1 VCSA Block Templates

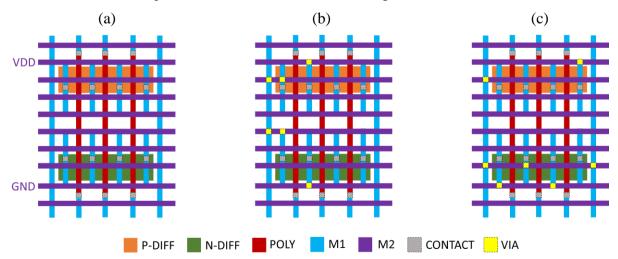

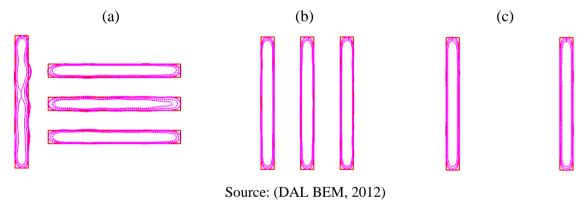

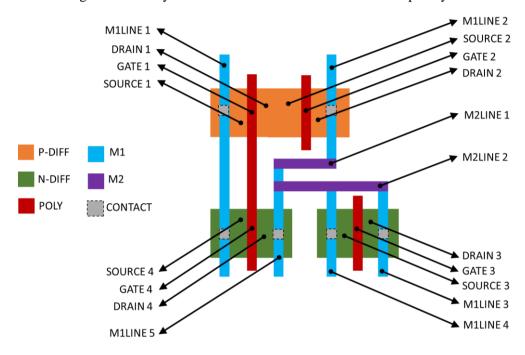

VCSAs are built by placing and connecting blocks as much as digital circuits using standard cell design method are built by placing and connecting cells from a library. However, in VCSAs, it is not possible to observe any difference between the blocks if the via layers are not observed. The set of layers that present identical layout patterns for all VCSA blocks comprises the "block template". Figure 2.5 demonstrates a VCSA block template, and how different functionalities are configured in this template only by different vias placement on them.

Figure 2.5 - Block template example (a), and the vias configuration in this template example to implement an INV (b) and a NOR3 (c) logical functions.

Figure 2.6 depicts another block template. Observe that this template is smaller in terms of resources as the available transistors and metal lines. One single instance of such block is not able to express a logical function as the "NOR3" depicted in the previous template example. However, it can be achieved by correctly configuring and connecting two block instances, as shows Figure 2.6(b). Ultimately, any logic function or digital circuit can be expressed if the number of block instances is high enough, as long as the template is able to express a basic set of logic functions and global routing resources are available.

In this document, the set of realizable logic functions into a single instance of a block template will be labeled in this text as the template "logical capacity", and not as "functional expression capability" or "function implementation capability" or "configurability capability" as in (RAN, 2006a) and in (LI, 2008), even they all presenting the same meaning.

Figure 2.6 - Block template example (a), a NOR3 logical function implemented by configuring two block instances (b) and a circuit designed by VCSAs combination (c).

Logical capacity is not the only attribute that may be evaluated in a VCSA block template. The template area itself is an attribute of interest, and is intuitively correlated to logical capacity: among two templates requiring similar area, the one presenting higher logical capacity is a better choice as will probably result in a smaller final circuit. However, the expected scenario is that templates with higher logical capacity present larger areas. The transistor sizing strategy also may differ among block templates, as can be observed in the previous and subsequent examples, and impacts electrical performance of the final circuit. Even the chosen layout patterns to compound the block template are important on its evaluation, as some patterns (as "L" shapes) will cause higher distortions during the photolithography processes, increasing the discrepancy between drawn layout and

manufactured circuit, and decreasing manufacturing yield. This last described attribute is referred as how much "litho-friendly" a block template is or if it is "lithography-aware".

The mentioned set of block template attributes highlights that, even when working with an extremely regular class of layouts, still there is a wide range of design choices. Therefore, several different block template proposals arise in related literature, and the main ones are discussed in the next subsection.

#### 2.2 VCSA Block Templates in Literature

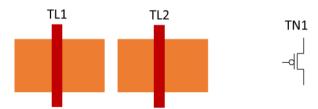

From now on, all explanations about layouts assume the conventional CMOS technology, p-type and n-type diffusions, transistor gate formed by polysilicon (or simply "poly"), and connections by metal lines (in which "M1" or "metal1" means the metal level closer to diffusions). However, all discussion and models herein are still valid if any of these materials are replaced by the ones in newer technologies.

#### 2.2.1 VCC

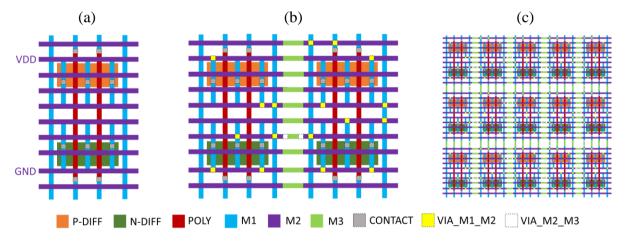

"Via-configurable cell" (VCC) is a VCSA block template proposed by Y. Ran *et al.* in (RAN, 2004a). VCC related work progresses in (RAN, 2004b; RAN, 2004c), culminating in (RAN, 2006a) and in (RAN, 2006b). Figure 2.7 depicts a VCC template or, more specifically, the 5-VCC, which is the VCC variation containing 5 transistors in each plane. Figure 2.7 also shows another template called "inverters array" (INVA), which serves as auxiliary logic to VCC. Both VCC and INVA are combined in the proposed placement and routing scheme compose a larger block template named VCGA (via-configurable gate array), shown in Figure 2.8.

Observe in Figure 2.7 that every crossing between M1 and M2 is a potential place for a via, while all contacts are already placed. The global routing strategy is detailed in (RAN, 2006b) and makes the entire circuit configurable only through the via layers customization.

The main characteristics of the VCC template are:

- Poly matching between p-type and n-type transistors.

- No diffusion breaks

- Pre-defined metal lines for supply (VDD and GND)

- Only two metal lines able to connect both p and n planes

The main differences of the INVA template to the VCC one are:

- Present some diffusion breaks

- Diffusion breaks aligned in both p and n planes

- Several metal lines able to connect both p and n planes

Figure 2.7 - 5-VCC block template (a) and INVA block template (b).

Figure 2.8 - VCGA block built by the association of VCC and INVA blocks.

These templates present connections possibilities restricted by the poly matching and the diffusion abutments. However, these characteristics are very efficient in optimizing the template area. In VCC case, there is also no diffusion breaks, meaning that any transistor network expressed in this template must present the same control ordering in both planes, forming a continuous path through all transistors.

Figure 2.9 illustrates transistor networks with and without such characteristic, and their relationship to the VCC template.

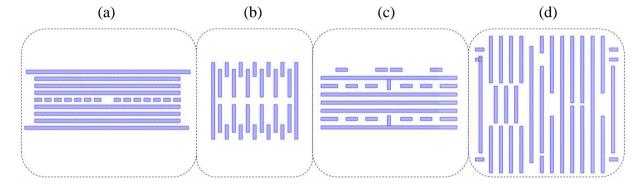

Figure 2.9 - Example of transistor networks that can (a) and cannot (b) be expressed in a 5-VCC.

If two transistor networks present Eulerian paths starting from supply nodes, they can be connected at this node, creating a single continuous path. This fact, together with the presence of only two metal lines in VCC capable of connecting p and n planes, induces the conclusion that this template is intentionally designed to support at most two simultaneous logic functions (or transistor networks).

#### 2.2.2 VCTA

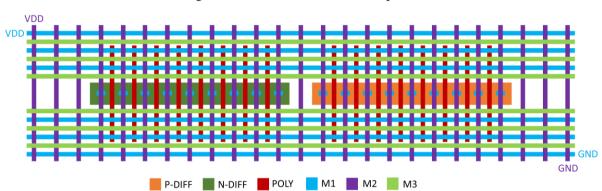

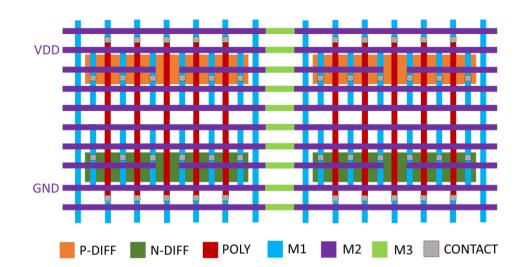

"Via-configurable transistors array" (VCTA) is a VCSA block template proposed by M. Pons *et al.* in (PONS, 2010). Another study about the same template is presented in (PONS, 2011). Figure 2.10 depicts a VCTA template or, more specifically, the VCTA-6T: the VCTA variation comprising 6 functional transistors and 2 dummy transistors in each plane. Observe in Figure 2.10 that every crossing between M1 and M2, or M2 and M3, is a potential place for a via, while each M1 above diffusions is a potential place for a contact. The proposed placement and routing scheme for this template, shown in Figure 2.11, relies exclusively on VCTA blocks with alternated orientation. It is possible to observe in Figure 2.11 that the global routing strategy requires customization of metal layers, even with predefined fixed metal layers pattern inside the VCTA blocks.

The main characteristics of the VCTA template are:

- Independent poly stripes in p-type and n-type transistors;

- No diffusion breaks;

- Pre-defined metal lines for supply (VDD and GND);

- Several metal lines able to connect both p and n planes;

- High maximum number of vias;

- Contacts layer is not pre-defined (both contacts and vias configurable).

Figure 2.10 - VCTA-6T block template.

Figure 2.11 - VCTA design method for blocks placement (with mirrored diffusions) and global routing (with metal line extensions).

VCTA presents higher flexibility for transistor network configuration, as the transistor gates at the template layout are not matched in both p and n planes. This flexibility impacts in template area. However, area does not seem to be the focus of this template anyway, as this is the only template to add dummy poly stripes for making lithography process even more predictable. Another very particular characteristic of this template is the need of modifying the most of layout layers in a circuit re-design (increasing considerably the production cost) because not only vias but also contacts are used to configure the blocks logic functions, and global routing does not present a standard fabric, requiring changes in metal layers to build the connections.

#### 2.2.3 VCLB

"Via-configurable logic block" (VCLB) is a not a single template but a set of VCSA block templates detailed by H. Tung *et al.* in (TUNG, 2012), as a result of several previous

work exploring the subject (LI, 2008; TUNG, 2009; CHEN, 2010). Figure 2.12 depicts a VCLB template, or more specifically its most explored variation, the SLVC5P template. Observe in Figure 2.12 that every crossing between M1 and M2 is a potential place for a via. The proposed placement and routing scheme for this template, shown in

Figure 2.13, consists basically of side-by-side block instances, making the entire circuit configurable only through the via layers personalization.

Figure 2.12 - VCLB-SLVC5P block template.

Figure 2.13 - VCLB design method for blocks placement and global routing.

The main characteristics of the VCLB template are:

Poly matching between p-type and n-type transistors;

- Present some diffusion breaks:

- Diffusion breaks aligned in both p and n planes;

- Pre-defined metal lines for supply (VDD and GND);

- Several metal lines able to connect both p and n planes.

VCLBs are middle-term alternatives to VCC and VCTA. They are not as areaoptimized as VCC and not as regular or lithography-aware as VCTA, but still configures circuit functionality only by the vias mask and present increased flexibility on expressing transistor networks due to the diffusion breaks and metal lines crossing both planes.

#### 2.3 Evaluation Methods of VCSA Block Templates

All exposed block templates present a different set of characteristics that makes each one the most convenient choice in a particular scenario or for a certain set of target circuits. It brings up the need for evaluating and comparing methods to aid the choice of the most appropriate template to be used during VCSA-based layout design.

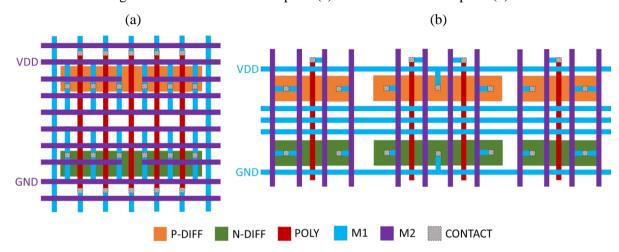

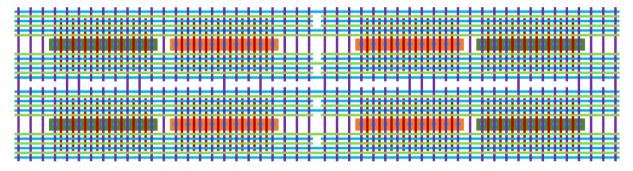

#### 2.3.1 Lithography-based Evaluation

The analysis of how much a layout is lithography-aware can be either qualitative or quantitative.

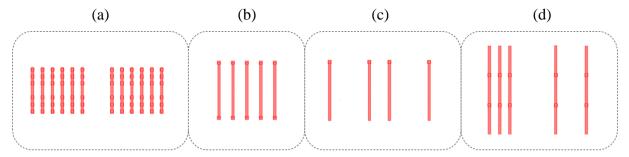

On the basis of a qualitative analysis, there is a different expected behavior for each layout layer. Layout layers such as diffusions or higher metal levels are not totally prone to lithography errors that are more likely to occur in their relationship with other layers like contacts and vias. However, layers with smaller feature sizes, like polysilicon and M1, are usually considered more critical, since they are also candidates to errors as shorts and opens, and their electrical characteristics are more influenced by dimensions variation. Polysilicon and M1 masks of layouts based on the VCSA templates, addressed in previous section, are depicted in Figure 2.14 and in Figure 2.15

Figure 2.14 - Polysilicon masks based on VCTA (a), VCC (b), INVA (c), VCLB (d).

Figure 2.15 - M1 masks based on VCTA (a), VCC (b), INVA (c), VCLB (d).

It is possible to analyze such masks according to two aspects, the layout patterns themselves and their neighboring, as detailed below.

#### a) Layout Patterns

As already stated, designing layouts with smaller amount of patterns, *i.e.*, increasing the circuit regularity, is expected to improve the efficiency of resolution enhancement techniques (RETs) and manufacturing yield. However, some patterns are more difficult to print using photolithography. Hence, two circuits with the same regularity degree can achieve different manufacturing yield, according to their particular layout pattern characteristics.

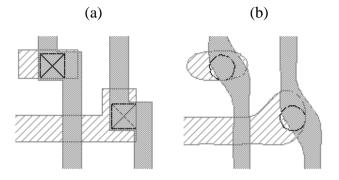

The rough idea is that the corners of shapes are quite hard to manufacture with high layout fidelity. It makes some patterns, like L-shapes, jogs in lines and end-of-lines, usually not effective in lithography process. Figure 2.16 illustrates such remarks. Thus, from the layout point-of-view, guidelines for lithography-aware design may include the use of unidirectional lines and avoid segmentation.

Figure 2.16 - Comparison between drawn layout (a) and lithography simulation (b) of pattern samples.

Source: (DAL BEM, 2012)

Notice that the lines in Figure 2.14(a) and in Figure 2.15(a) are unidirectional and the segmentation is restricted, whereas the patterns in the two next columns of these figures present some increasing in number of line breaks and two small jogs. Figure 2.14(d) and Figure 2.15(d), in turn, present many different patterns. From the previous statements, it is possible to consider the columns in Figure 2.14 and in Figure 2.15 ordered according to the lithography difficulty, being the pattern in Figure 2.14(a) and in Figure 2.15(a) the most effective to manufacturing process.

#### b) Neighboring

The quality of printed patterns does not depend only on their own shape, but also on the influence of near patterns. In lithography-aware designs, the intra-cell shapes and distances are carefully selected, such that neighboring impact is helpful instead of aggressive. Figure 2.17 (a) depicts aggressive neighboring lines influence, whereas Figure 2.17 (b) and Figure 2.17 (c) illustrate a negligible influence becoming a suitable one through the pitch adjustment.

Pitch adjustment and dummy lines insertion are design-for-manufacturing (DFM) techniques for controlling this impact that, again, shows the convenience of unidirectional lines. In the VCTA description (PONS, 2010), the authors are the only one to explicitly mention that the first and the last poly lines in each transistor netlist plane are intended to be dummy, with exclusive purpose of lithography improvement. Its enhanced regularity also simplifies the pitch adjustment. In VCC and INVA approaches, there is no explicit mention about pitch adjustment or dummy lines insertion. However, as all lines respect a common grid, these techniques would be easily applied. In VCLB approach, distances are not exact

multiples, as can be seen in Figure 2.14(c) and in Figure 2.15(c). Thus, adjusting lines to a common pitch may imply significant area penalty.

The neighboring influence analysis must consider not only intra-cell shapes but also the inter-cell relationship, which is a very hard task when using conventional standard cell libraries, since there are many possible neighboring patterns. The use of identical transistor arrays, as in VCSA templates, makes such impact very predictable due to the similarity of neighboring layouts. However, it is not ensured that the intra-cell DFM characteristics automatically extend to global scenario. The VCGA architecture, presented in (RAN, 2006a), can be used as example. This architecture comprises VCC blocks surrounded by rotated INVA blocks, making possible aggressions like the one illustrated in Figure 2.17(a), which were not present on the individual analysis of these sub-blocks.

Figure 2.17 - Neighboring influence: aggressive (a), helpful (b) and negligible (c).

### c) Lithography awareness quantification

There are several different methods of quantifying how much a design is lithography-aware. The fast-Fourier-transform 2D approach is not efficient when comparing layouts with similar lithographic behavior (JHAVERI, 2007). The FOCSI method measures regularity of circuits, but does not take into account critical patterns as described in the previous qualitative analysis (PONS, 2012). Edge placement error (EPE), in turn, is a very simple concept, which basically exposes the difference of printed edges when comparing to the original layout (MITRA, 2005). This concept is used for the measurements exposed later in this section.

EPE is usually connected to fast lithography simulation techniques in order to estimate the number of hotspots in large circuits. However, the use of fast lithography simulation is not appropriate in context of VCSA design method, since the neighboring influence is very predictable. Thus, simulations can rely only on blocks and not on the entire circuit. It makes detailed lithography simulations much faster and eliminates the need for fast approximated algorithms. Also, as the lithography behavior of templates are not supposed to be very different, the EPE data must be as precise as possible.

In order to achieve the following results on the studied VCSA templates, available in (DAL BEM, 2012), the EPE data is generated using lithography simulations performed using a commercial tool. These simulations are followed by an image inspection algorithm running over pixel precision. This algorithm comprises a list of all found EPE distances in the lithography simulation, composing a very detailed analysis on its data.

The evaluated layouts are the ones already depicted in Figure 2.14. They are built over the predictive FreePDK 45nm technology rules, using the minimum allowed distances (FREEPDK, 2012). Only M1 and polysilicon masks were taken into account.

Figure 2.18 shows the visual representation of EPE achieved data. The highlighted hotspots are placed mainly at end-of-lines and jogs, as previewed in the qualitative analysis. Another critical pattern evidenced is the polysilicon enclosure around contact.

Figure 2.18 - EPE hotspots, achieved from lithography simulation on masks depicted in Figure 2.14 and in Figure 2.15, followed by image inspection algorithm.

Table 2.1 lists the average and the worst case values of EPE, obtained by image inspection over each template.

**VCLB**

21.429

|          | EPE per mask (nm)  |                 |                   |                |  |

|----------|--------------------|-----------------|-------------------|----------------|--|

| Template | M1<br>(worst case) | M1<br>(average) | Poly (worst case) | Poly (average) |  |

| VCTA     | 15.714             | 0.494           | 5.714             | 0.995          |  |

| VCC      | 14.286             | 0.818           | 11.429            | 0.484          |  |

| INVA     | 24 286             | 0.748           | 10,000            | 0.392          |  |

Table 2.1 - Average and the worst cases of EPE

Source: (DAL BEM, 2012)

10.000

0.510

0.490

In M1 masks, it is possible to observe that the worst case values are significantly decreased in templates which follow the unidirectional lines rule, as the VCTA and the VCC ones. On the other hand, average values are dominated by the presence of segmentation, which is high in VCC and INVA approaches.

In polysilicon masks, the worst case values seem to have strong relationship to the chosen pitch, which is narrower in the VCTA. The average values increase mainly due to the increasing of the number of poly contacts, suffering also with end-of-lines distortions. In this case, the strategy of inserting poly contacts only in the poly stripes extremities is advantageous, as adopted in VCC and INVA.

Figure 2.19 shows EPE results through histogram representation. It details the values' deviation, which could not be extracted from the data in Table 2.1. It evidences how the worst case values on M1 of INVA and VCLB do not represent the overall behavior of these templates, corresponding to very specific points, so being easily repaired. It is also possible to observe clearly the superiority on lithography quality of polysilicon lines with fewer contacts.

Figure 2.19 - M1 and polysilicon histograms of edge placement error (EPE) values, obtained by image inspection over lithography simulations.

Source: (DAL BEM, 2012)

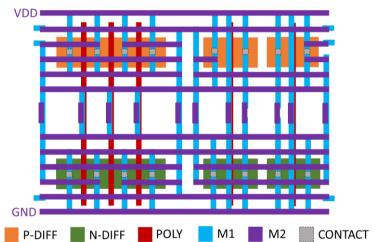

#### 2.3.2 Electrical Performance Evaluation

Electrical performance can be defined as the speed of signals transitions and the power consumption of a cell, block or circuit. The evaluation of the electrical performance of VCSA-based designs are similar to the ones implemented in standard cells methodology. It is based on extracting a transistor network (and its parasitic elements) from the layout of each configuration/function, and using a characterizer tool to electrically simulate such arcs transitions to obtain timing and power consumption data for that cell. At this point, comparisons between the cells are already possible, but usually it is more appropriate to perform such an analysis at circuit level, using the set of characterized cells as the input library to a circuit mapping tool.

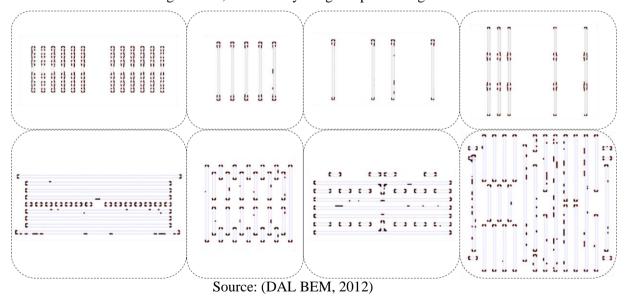

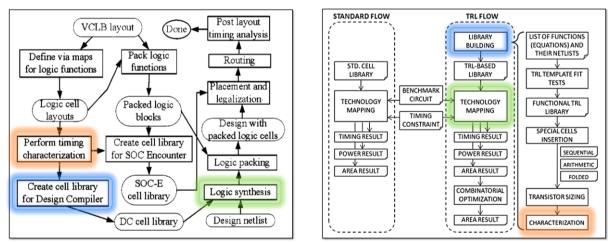

Examples of this approach including library characterization followed by circuits mapping is found in (LI, 2008), (TUNG, 2011), (DAL BEM, 2011b) and in (NOURY, 2012). Figure 2.20 exemplifies some of the design flows on such references, exposing their similarity.

Figure 2.20 - Design flow in (LI, 2008) at left, (DAL BEM, 2011b) at right, evidencing the use of a characterizer to compose a library that is used by a mapping tool.

The electrical performance is influenced by the template transistor sizing strategy (MARRANGHELLO, 2011). In VCSA block templates related literature, different alternatives are employed. In (TUNG, 2011), the transistor sizes are chosen to achieve roughly equal rise and fall output transition times. In (RAN, 2006a) and in (DAL BEM, 2011b), minimum transistor sizes for the target technology are used. Also in (DAL BEM, 2011b), another sizing strategy is presented: transistor widths that achieve good compromise

between area and delay, obtained from the performance analysis on ring oscillators and from samples of critical paths in sample circuits.

Besides transistor sizing, another technique for enhancing electrical performance is the transistor folding (or fingering), defined by connecting parallel transistors sharing the same control signal. As mentioned in (PONS, 2010), this technique emulates wider transistors whose width is a multiple of the basic transistor, behaving as a discrete transistor sizing strategy. In (RAN, 2006a), the combination of folding technique and minimum sized transistors is brought as possible solution to meet the circuit timing requirements, however, no deep analysis is performed. This combination is also present in (DAL BEM, 2011b), where the use of the folding for creating alternative P/N ratios is also mentioned. In the VCSA block templates context, the folding technique is more suitable for buffers and inverters, as they usually underuse the available template resources and have great potential for improving circuit's timing performance.

Observing the achieved results on the mentioned references, it is possible to conclude that timing and power constraints commonly are not the bottleneck of using VCSA-based designs, but area. In (TUNG, 2011), the circuits designed using the most efficient proposed templates (SLVC5P variants) presented an increase of 15% to 51% in circuit delay when compared to standard-cell design approach. The increasing in power consumption ranged from 30% to 86%, whereas circuit area overhead varies from 151% to 232%. In (RAN, 2006a), the circuits designed using the proposed VCGA template, when compared to the same circuits designed using standard-cells, an increasing in circuit delay of 33%, 17% in power consumption, and 116% in area overhead. Similarly, when using VCTA, mapped benchmark circuits presented an average augmentation of 4% in power consumption, respecting the same timing constraints, and resulting an area overhead of around 100% (DAL BEM, 2011b).

#### 2.3.3 Logical Capacity Evaluation

The logical capacity of a given VCSA block template is the set of different logical functions that a single instance of such block can express by its vias configuration. This attribute carries an inherent relationship to the block template area: usually, a template with more layout resources (as transistors and metal lines) presents a larger logical capacity but also requires a larger area, composing a "trade-off" scenario. This trade-off is critical, since a mistaken tuning on it can cause prohibitive area penalty, as demonstrates the work presented in (DAL BEM, 2011a) and in (DAL BEM, 2011b), summarized below.

#### Impact on circuits area

The area overhead and circuit performance penalty are the most critical drawbacks of regular layout design in comparison to the most popular standard cell design. Complex functions can be used to reduce the overall number of transistors of the design, to mitigate the cost of adopting a more restrictive design space for improving lithography yield.

The extensive investigation presented in this section is based on the VCSA template called VCTA, proposed by Pons *et al.* (PONS, 2010), as such approach is quite interesting in terms of design flexibility due to very fine-grained configurability.

Each VCTA unit has a pre-defined number of metal lines (interconnection wiring) and transistors (PMOS and NMOS). Each amount of the available resources chosen is treated as "template variant". We will assume that a single design cannot use more than one template variant at the same time.

The comparison between VCSA design and standard cell based circuit was performed on the technology mapping step. In summary, a set of benchmark circuits were mapped addressing different cell libraries and the resulting circuit area were compared. Thus, in order to evaluate both design methodologies, the libraries were generated focusing on that, and applied as input for the mapping task.

To build the VCSA based-libraries, we should know which logic functions fit well and do not overflow the target template resources. The first part of this task was to convert the logic functions into transistor networks, and then extracted the information of its minimum required resources for cell implementation. A specific tool, named TRL-profiler, described later on this text, was developed for that purpose.

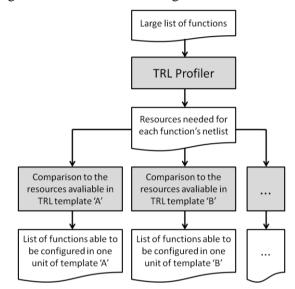

Once the minimum required layout resources for implementing a list of functions have been defined by our TRL-profiler tool, it could be matched to the resources offered by the different template variants under evaluation. This way, the template acts as a filter to select the functions which fits it. Figure 2.21 illustrates the flow related to the composition of the lists of functions.

Those lists were the basis of libraries generation. A library description carries a large variety of information. Usually, the most important data for the mapping tool are the functional behavior (logic equation) as well as the timing, power consumption and area characteristics of each cell. In order to balance the timing and power consumption in both approaches the same transistor sizing was applied. In this way, the equivalent VCTA and

standard cell libraries had the same logic functions and similar timing and power characteristics. The main difference is actually related to the cell area. In VCTA template variant, each cell had the same area to respect the regularity constraints, whereas in standard cell the library height were optimized to a minimum possible value. Figure 2.22 illustrates the applied flow for composing the set of libraries.

Figure 2.21 - Flow for defining the lists of functions.

Source: (DAL BEM, 2011a)

Figure 2.22 - Flow for libraries composition.

Source: (DAL BEM, 2011a)

After building the cell libraries, the mapping process were performed considering a set of benchmark circuits, and applying each one of the libraries generated. Making so, all possible template-benchmark combinations are reached for both VCTA and standard cell design styles.

A set of 21 different VCTA template variants has been tested, comprising all possible combinations among 2, 4 and 6 input M1 lines, and 2 to 8 transistors in each plan (pull-up PMOS and pull-down NMOS). Each of the 21 generated lists of logic functions, corresponding to each evaluated template variant, were considered as basis to compose both VCTA and standard cell libraries, totalizing 42 distinct cell libraries to be used in the mapping of benchmark circuits. A set of 14 combinational ISCAS85 benchmark circuits (BRGLEZ, 1985) was applied in the experimental analysis. Each benchmark was mapped taking into account all the 42 generated cell libraries.

The circuit area obtained for the same benchmark mapped addressing different VCTA template variants had shown an average difference of 52% in respect to the best area attained. In the worst case scenario, comparing always the less efficient tested VCTA template variant against the best one, for all benchmarks, the average area difference goes up to 151%.

These data demonstrate how the logical capacity versus block area trade-off is critical, and the next step is to discuss the practical issues of its tuning, being the starting point to have available, at least, both template information, the block area and its logical capacity. The block template area is easily obtained by drawing a single block layout respecting the rules of the desired target technology. However, obtaining the block logical capacity is not a trivial task. The current available methods in literature are summarized as follows.

#### Logical capacity extraction methods

In (RAN, 2006a), the logical capacity of VCC template is obtained over the dual-Euler trail principle. Consider the graph representation of a transistor network. A trail in a graph is an alternating sequence of nodes and incident edges beginning and ending with nodes, with no edge repeated. A dual trail is a pair of trails, one in pull-up and other in pull-down plane, which consist of the same sequence of edges. A dual-Euler trail is a dual trail which includes all of the edges of a dual TTSPM (two-terminal series-parallel multigraphs). If an *n*-literal function has a single dual-Euler trail, it can be implemented in a *n*-VCC, because of this characteristic single transistor stripe in each plan.

Therefore, all of n-VCC realizable functions are enumerated by finding all of the dual-Euler trails with n edges. In that work, only non-equivalent functions are taken into account and, when possible, concatenation of two trails is performed, i.e., two functions sharing the same template. A pseudo-code for finding all dual-Euler rails based on pair-wise concatenation is described in (RAN, 2006a), and the obtained logical capacity is summarized in Table 2.2 and in Table 2.3. In Table 2.3, TF stands for Total Functions and RF stands for realizable functions, while FC stands for Functional Coverage.

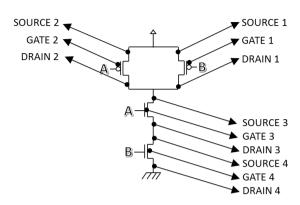

The method applied for VCC template is not valid for VCTA one, as in this last template, the transistor gate stripe of both pull-up and pull-down planes are not aligned. In the original approach (PONS, 2010), only the implementation of a reduced set of logic functions in VCTA is investigated: an inverter, an XOR, a 2-input NAND, a 4-input NAND, an AND-OR and an OR-AND. In a posterior, analysis in (DAL BEM, 2011a), a specific tool is developed, called TRL-profiler. The TRL-profiler needs a set of transistor networks as input, which will pass through a "fit" test in a target VCTA variant. This approach is not similar as the used in (RAN, 2006a), which is exhaustive, reaching all the functions by construction.

Table 2.2 - n-ViaCC realizable non-equivalent functions (RAN, 2006a).

| n | f = f(x)                  | $\overline{f} = \overline{f}(x_1, \cdots, x_n)$ |  |  |

|---|---------------------------|-------------------------------------------------|--|--|

| 2 | $x_1x_2$                  | $x_1 + x_2$                                     |  |  |

| 3 | $x_1x_2x_3$               | $x_1 + x_2 x_3$                                 |  |  |

| 3 | $x_1(x_2+x_3)$            | $x_1 + x_2 + x_3$                               |  |  |

|   | $x_1x_2x_3x_4$            | $x_1 + x_2 x_3 x_4$                             |  |  |

|   | $x_1(x_2+x_3x_4)$         | $x_1 + x_2 + x_3 x_4$                           |  |  |

| 4 | $x_1x_2(x_3+x_4)$         | $x_1 + x_2(x_3 + x_4)$                          |  |  |

|   | $x_1(x_2+x_3+x_4)$        | $x_1 + x_2 + x_3 + x_4$                         |  |  |

|   | $x_1x_2 + x_3x_4$         | $(x_1+x_2)(x_3+x_4)$                            |  |  |

|   | $x_1x_2x_3x_4x_5$         | $x_1 + x_2 x_3 x_4 x_5$                         |  |  |

|   | $x_1(x_2+x_3x_4x_5)$      | $x_1 + x_2 + x_3 x_4 x_5$                       |  |  |

|   | $x_1x_2(x_3+x_4x_5)$      | $x_1 + x_2(x_3 + x_4x_5)$                       |  |  |

|   | $x_1(x_2+x_3+x_4x_5)$     | $x_1 + x_2 + x_3 + x_4 x_5$                     |  |  |

|   | $x_1x_2x_3(x_4+x_5)$      | $x_1 + x_2 x_3 (x_4 + x_5)$                     |  |  |

| 5 | $x_1(x_2+x_3(x_4+x_5))$   | $x_1 + x_2 + x_3(x_4 + x_5)$                    |  |  |

|   | $x_1x_2(x_3+x_4+x_5)$     | $x_1 + x_2(x_3 + x_4 + x_5)$                    |  |  |

|   | $x_1(x_2+x_3+x_4+x_5)$    | $x_1 + x_2 + x_3 + x_4 + x_5$                   |  |  |

|   | $x_1x_2 + x_3x_4x_5$      | $x_1x_2 + x_3 + x_4x_5$                         |  |  |

|   | $x_1x_2 + x_3(x_4 + x_5)$ | $(x_1+x_2)(x_3+x_4x_5)$                         |  |  |

|   | $(x_1+x_2)x_3(x_4+x_5)$   | $(x_1+x_2)(x_3+x_4+x_5)$                        |  |  |

Source: (RAN, 2006a)

Table 2.3 - Functional coverage of n-ViaCC (RAN, 2006a).

| n     | 2   | 3   | 4   | 5    | 6    | 7    | 8    |

|-------|-----|-----|-----|------|------|------|------|

| TF    | 2   | 4   | 10  | 24   | 66   | 180  | 522  |

| RF    | 2   | 4   | 10  | 22   | 50   | 112  | 280  |

| FC(%) | 100 | 100 | 100 | 91.7 | 75.8 | 62.2 | 53.6 |

Source: (RAN, 2006a)

For this reason, the TRL-profiler works extracting the following data for each possible logic gate implementation:

- a) number of input inverters, which represents the number of additional M1 lines required for internal connections;

- b) presence of output inverter, which represent an additional M1 line required for cell core output signal routing;

- c) PU-P and PD-N Euler path lengths (column heights), including breaks (isolated transistors) for each one;

- d) number of connections in internal PU-P and PD-N networks, which represents the use of an exclusive M1 for signal routing;

- e) verification if PU-P and PD-N Euler paths can begin from the VDD and GND power signals, respectively, because the remaining unused transistors in the column can be used to implement another logic gate whose Euler paths also begin in the same VDD and GND nodes.

Both items (a) and (b) above can be interpreted as a requirement of extra exclusive M1 vertical wires for each distinct input/output signal. If M3 is used for this purpose, then the signal must be connected down to M1, passing through M2, to access the polysilicon gates. Items (c) and (e) provide useful information for estimating the optimized number of switches and to determine the column height, *i.e.*, the number of pre-defined stacked transistors.

After extracting the itemized information for a given transistor network, a simple comparison to the available layout resources of the target VCTA variant is performed.

The following results use as input for the TRL-profiler a list of 4058 functions. This list comprises all possible Boolean functions with up to 4 inputs, excluding the ones equivalent by inputs permutation, named P-class<sup>1</sup> (SASAO, 1999), and the 76 functions of 5 and 6 inputs from the reference list known as Genlib, more specifically 'genlib\_44-6' (SENTOVICH, 1992). Table 2.4 provides the number of those 4058 functions that are able to be implemented over a single VCTA unit of each template variant evaluated.

<sup>&</sup>lt;sup>1</sup> In this case, "P" stands for "permutation". Do not mistake this P-class with the algorithms complexity P-class, in which the "P" stands for "polynomial", that will be mentioned later on this text.

| Table 2.4 - Number of logic functions from the input list which fits each evaluated VCTA template |  |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| variant, according its resources.                                                                 |  |  |  |  |  |  |  |

| Number of | Number of transistors at each plan |   |    |    |     |     |     |

|-----------|------------------------------------|---|----|----|-----|-----|-----|

| M1 lines  | 2                                  | 3 | 4  | 5  | 6   | 7   | 8   |

| 6         | 4                                  | 9 | 19 | 53 | 126 | 151 | 189 |

| 4         | 4                                  | 9 | 19 | 33 | 55  | 69  | 81  |

| 2         | 4                                  | 6 | 6  | 6  | 8   | 8   | 8   |

Source: (DAL BEM, 2011a)

In (TUNG, 2011), it is presented not a single but several VCLB block templates, and there is no specific tool for logical capacity extraction. It seems to be evaluated manually, performing trials of a pre-determined set of logical functions in each proposed template. Table 2.5 shows a comparison between the amount of functions in a standard cell library (STDL) against the number of realizable functions in one VCLB template variant (SLV5P).

Table 2.5 - Number of cells in standard cell library example and one VCLB variant, called SLV5P.

| Inputs | Number of functions |       |  |  |

|--------|---------------------|-------|--|--|

|        | STDL                | SLV5P |  |  |

| 2      | 11                  | 8     |  |  |

| 3      | 21                  | 12    |  |  |

| 4      | 16                  | 12    |  |  |

| 5      | 6                   | 4     |  |  |

| 6      | 6                   | 0     |  |  |

Source: (TUNG, 2011)

#### • Thesis' Contribution

As discussed above, the current methods in literature for determining the VCSA templates logical capacity are based on the characteristics of the target template, in a way that changing a feature in its design (*e.g.* removing or adding poly alignment between pull-up and pull-down planes) becomes the method unsuitable. There is a lack for a general and efficient method that could be applied over any VCSA block template.

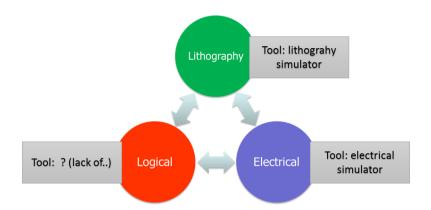

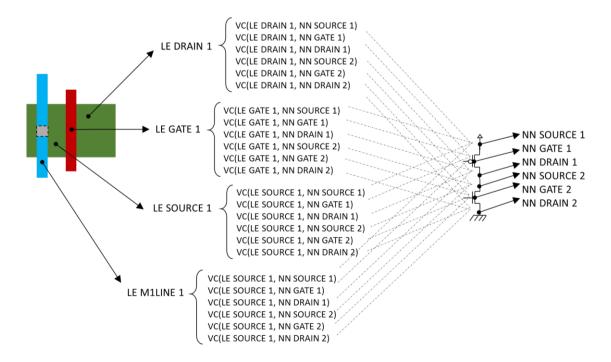

The lack for a tool to evaluate the logical capacity of any block template is highlighted especially when we observe the larger scenario of evaluating the design quality of a VCSA template. In this scenario, the analysis of the lithography efficiency is covered by lithography simulations, and electrical performance analysis covered by characterization tools, both general methods suitable to any block template, but there is no similar tool for covering logical capacity evaluation, as drawn in Figure 2.23.

This lack is fulfilled in this thesis. The Chapter 4 presents the proposed solution, while the background required to its understanding is exposed in the next chapter.

Figure 2.23 - Aspects to consider when evaluating design quality of a VCSA template.

#### 3 SAT IN CAD

This chapter provides basic background in SAT, beginning with fundamental definitions, followed by a discussion about SAT complexity and a list of applications on CAD problems, including details on a case of special interest.

#### 3.1 Definitions

"Satisfiability" and "SAT" are common abbreviations for Boolean Satisfiability Problem in computer science. It consists in determining if a logic formula is "satisfiable". "Logic formula" and "satisfiable" can be defined as follows.

A Boolean expression, also called logic formula, is composed by variables, operators and parentheses. The single purpose of parentheses is to set precedence on operations. The operators are:

- "AND" or "conjunction" or "Λ"

- "OR" or "disjunction" or "V"

- "NOT" or "negation" or "¬"

A formula is said to be "satisfiable" if it can be made TRUE by assigning appropriate logical values (TRUE or FALSE) to its variables. On the other hand, a logic formula is said to be "unsatisfiable" if it evaluates FALSE identically to all possible assignments to its variables.

A literal is either a variable, then called positive literal, or the negation of a variable, then called negative literal. A clause is a disjunction of literals (or a single literal). A formula is said to be in conjunctive normal form (CNF) if it is a conjunction of clauses (or a single clause).

For instance, "x1" is a positive literal, "¬x2" is a negative literal, "x1  $\vee$  ¬x2" is a clause, and "(x1  $\vee$  ¬x2)  $\wedge$  (¬x1  $\vee$  x2)  $\wedge$  ¬x1" is a formula in conjunctive normal form. This formula is satisfiable by choosing x1=FALSE, x2=FALSE, since (FALSE  $\vee$  ¬FALSE)  $\wedge$  (¬FALSE  $\vee$  FALSE)  $\wedge$  ¬FALSE evaluates to TRUE  $\wedge$  TRUE  $\wedge$  TRUE, so resulting TRUE. In contrast, the CNF formula (x1  $\wedge$  ¬x1), consisting of two clauses of one literal, is unsatisfiable, since for the two possibilities x1=TRUE and x1=FALSE it evaluates to TRUE  $\wedge$  ¬TRUE and FALSE  $\wedge$  ¬FALSE, resulting FALSE in both cases.

Every logic formula can be transformed into an equivalent conjunctive normal form, which may, however, be exponentially longer. For example, transforming the formula 3.1 into conjunctive normal form yields the equation 3.2.

$$(x1 \land y1) \lor (x2 \land y2) \lor \dots \lor (xn \land yn)$$

$$(3.1)$$

$$(x1 \lor x2 \lor ... \lor xn) \land (y1 \lor x2 \lor ... \lor xn) \land (x1 \lor y2 \lor ... \lor xn) \land$$

$$(y1 \lor y2 \lor ... \lor xn) \land ... \land (x1 \lor x2 \lor ... \lor yn) \land (y1 \lor x2 \lor ... \lor yn)$$

$$\land (x1 \lor y2 \lor ... \lor yn) \land (y1 \lor y2 \lor ... \lor yn).$$

$$(3.2)$$

Observe that equation 3.1 is a disjunction of 'n' conjunctions of 2 variables, whereas equation 3.2 comprises of '2<sup>n</sup>' clauses of 'n' variables.

# 3.2 SAT Complexity

Complexity classes are groups of computational problems related to the amount of resources (typically execution time) needed to be solved. Extensive explanation on complexity classes can be found in (BOVET, 1994), but a brief discussion is brought herein to better understand the SAT behavior.

P-class comprises problems that can be solved in polynomial time by a deterministic Turing machine. NP-class, in turn, comprises problems that can be solved in polynomial time by a non-deterministic Turing Machine. Clearly, P-class is included into NP-class. However, there is not yet widely accepted proof that P-class is different from NP-class in theory of computing (SRINIVASAN, 2011). Experimentally, some NP problems seems to be harder than P ones, being treated by algorithms that require super-polynomial time to find a solution.

NP-complete is a subclass of NP, and every NP problem can be reduced to a NP-complete problem in polynomial time. It can be said that NP-complete is the subset containing the hardest problems of NP, and the ones that are most unlikely to be in P class.

SAT is a problem with NP-complete complexity, as proved by Cook (COOK, 1971) and Levid (TRAKHTENBROT, 1974). Thus, there is not a known algorithm that solves SAT efficiently, correctly, and for all possible input instances, and it is usually believed that such an algorithm does not exist. However, many instances of SAT that occur in practice experimentally have been shown to be solved rather efficiently using SAT-solvers.

Depending on the particular structures of the used logic formulas, a special case of the Boolean satisfiability problem is configured. Such special case can be classified as SAT restriction or SAT extension. As expected, the problem complexity on SAT restrictions may be sometimes lower than the unrestricted SAT, but the extensions can only be more complex.

A SAT restriction that deserves special attention here is the one comprising only CNF formulas, sometimes called CNFSAT, which presents complexity in NP-class, like the unrestricted SAT problem.

An extension that has gained significant popularity, since 2003, is satisfiability modulo theories (SMT) that can enrich CNF formulas with linear constraints, arrays, all-different constraints, etc. Such extensions typically remain NP-complete, but very efficient solvers that can handle many such kinds of constraints are available nowadays.

# 3.3 SAT Application in CAD Problems

In last years, SAT formulation has been used to solve several CAD problems, as illustrated in this non-exhaustive list:

# PLA folding

Quintana *et al.*, in (QUINTANA, 1995), propose an algorithm for optimum PLA folding based on its formulation as a problem of Boolean satisfiability.

#### Asynchronous circuits synthesis

In (GU, 1995), it is presented a general and efficient partitioning approach to the synthesis of asynchronous circuits based on complete state coding (CSC) of signal transition graphs (STGs) satisfaction through satisfiability (SAT) model. In (KHOMENKO, 2003), the synthesis of asynchronous circuits is also addressed with SAT, but this time without the construction of the STGs, in a formulation that use only the information about causality and structural conflicts between the events involved in a finite and complete prefix of its unfolding. The same problem is also treated in (KHOMENKO, 2004), with an incremental SAT model.

#### FPGA routing

In (WOOD, 1998), it is developed a novel formulation of both signal routing and "routability" estimation that relies on a rendering of the routing constraints as a single large Boolean equation. In (NAM, 1999a), the authors also addresses the problem of detailed FPGA routing using Boolean formulation methods. These two last mentioned papers evolve to

(NAM, 2002). The previous attempts at FPGA routing using Boolean methods were based on binary decision diagrams that limited their scopes because of size limitations, but in (NAM, 2002), it is presented a FPGA detailed routing formulation for a new search-based satisfiability (SAT) that handles simultaneously all channels in an FPGA. In (HE, 2005), the author addresses a new segmented channel routing problem with pin rearrangements in FGPA technology, using an efficient SAT-based approach to solve the problem. The focus on routing FPGA multi-pin nets is clear in the SAT formulation in (MUKHERJEE, 2010). In (NAM, 1999b), the author presents a study on the FPGA routing through SAT, exposing that initial Boolean-based approaches for routing used binary decision diagrams (BDDs) to represent and solve the layout problem. However, BDDs limit the size and complexity of the FPGAs that can be routed, leading these approaches to concentrate only on individual FPGA channels.

### FPGA mapping

In (LING, 2005), the author presents a developed algorithm, based on Boolean satisfiability (SAT), that is able to map a small subcircuit into the smallest possible number of lookup tables (LUTs) needed to realize its functionality. In (SAFARPOUR, 2006), it is proposed a Boolean matching approach for FPGA technology mapping targeting networks of programmable logic blocks, and to do this the work breaks the original SAT problem into easier and smaller ones. In (HU, 2007), the author provides optimizations when addressing the same problem, by exploring function and architectural symmetries.

# Timing analysis

In (ROY, 2007), it is proposed an accurate technique based on SAT for computing critical delay of a circuit under a bounded delay model.

### Partitioning and placement of heterogeneous reconfigurable SoCs

The work in (WILDERMANN, 2011) presents three encoding variants that unify partitioning and placement of heterogeneous reconfigurable SoCs. In particular, their SAT-based approach uses a preprocessing mechanism that identifies partitioning which inevitably lead to unfeasibility and then incorporates this information into the symbolic encoding for calculating feasible placements.

### • Standard-cell layout

The work in (IIZUKA, 2004) proposes a cell layout synthesis method via Boolean satisfiability (SAT). However, as stated in (TAYLOR, 2007), its layout style is too much simplistic for several purposes (*e.g.* doglegs are not allowed in routes), and would result in much larger layout areas than those produced by other methods.

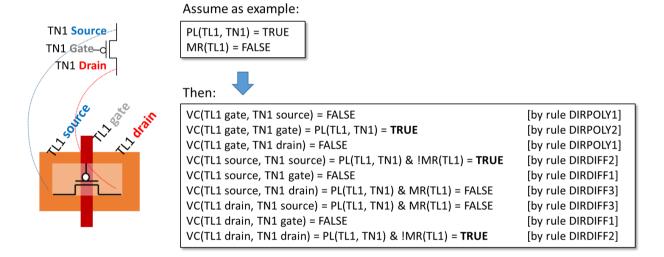

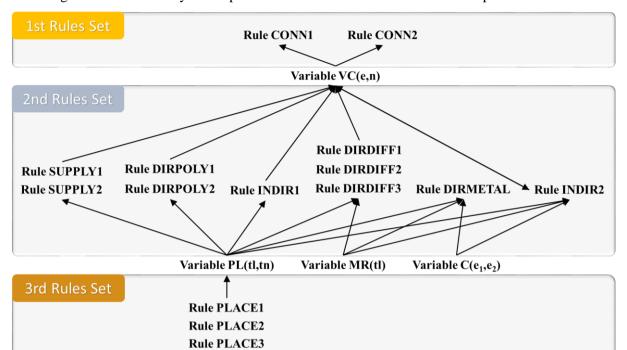

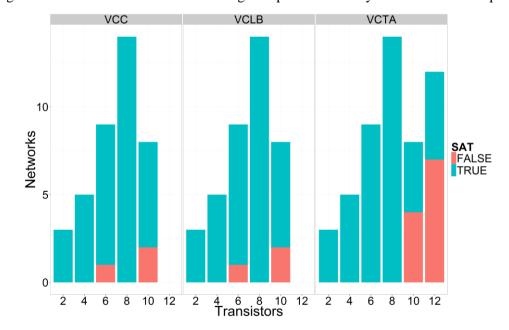

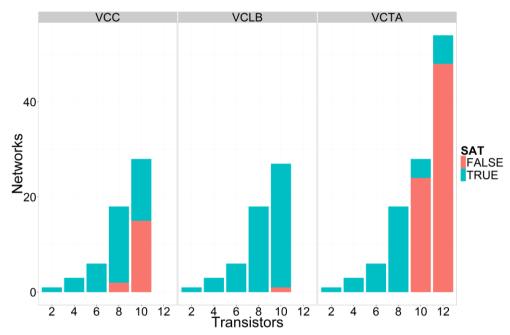

#### Standard cell routing