## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

#### JHON ALEXANDER GÓMEZ CAICEDO

# **CMOS Low-Power Threshold Voltage Monitor Circuits and Applications**

Thesis presented in partial fulfillment of the requirements for the degree of Master of Microeletronics

Advisor: Prof. Dr. Hamilton Klimach Coadvisor: Prof. Dr. Eric Fabris

#### CIP - CATALOGING-IN-PUBLICATION

Gómez Caicedo, Jhon Alexander

CMOS Low-Power Threshold Voltage Monitor Circuits and Applications / Jhon Alexander Gómez Caicedo. – Porto Alegre: PGMICRO da UFRGS, 2016.

83 f.: il.

Thesis (Master) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica, Porto Alegre, BR–RS, 2016. Advisor: Hamilton Klimach; Coadvisor: Eric Fabris.

1. Threshold voltage. 2. CMOS analog design. 3. Threshold voltage monitor circuit. 4. High-PSRR. 5. Resistorless. 6. Ultralow-power. 7. Voltage Reference. 8. Process Compensation. I. Klimach, Hamilton. II. Fabris, Eric. III. Título.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos Alexandre Netto

Vice-Reitor: Prof. Rui Vicente Oppermann

Pró-Reitor de Pós-Graduação: Prof. Vladimir Pinheiro do Nascimento

Diretor do Instituto de Informática: Prof. Luis da Cunha Lamb

Coordenadora do PGMICRO: Prof. Fernanda Gusmão de Lima Kastensmidt Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

## **ACKNOWLEDGEMENTS**

I would like to say thank to all the people that directly or indirectly collaborated in the development of this thesis, but first, I must say thank to professor Hamilton Klimach, that is the person whom me and this thesis owe him more. Thank for all the advices, suggestions, corrections, and especially, for all things that you taught me. Also, I thank to professors Eric Fabris and Sergio Bampi, for all the discussions that help me to mature and learn in the ICs field.

To the NSCAD team, for all our technical discussions, exchanges of knowledge, and to allow me to use their installations to work in my master. To my colleagues of the 110 lab, whom more than colleagues are friends.

A special thank, to my "novia" who supported me in turbulent moments, and reminded me, who I am, and why I am here. Also, to my dear friend Diogo who always was available to share a beer.

And finally to my family that with all their love, motivates me, strengthens me, and have conducted me to this moment.

## **ABSTRACT**

A threshold voltage  $(V_{T0})$  monitor is a circuit that ideally delivers the estimated  $V_{T0}$  value as a voltage at its output, for a given temperature range, without external biases, parametric setups, curve fitting or any subsequent calculation. It can be used in temperature sensors, voltage and current references, radiation dosimeters and other applications since the MOSFET  $V_{T0}$  dependence on the operation conditions is a very well modeled aspect. Also, it can be used for fabrication process monitoring and process variability compensation, since  $V_{T0}$  is a key parameter for the transistor behavior and modeling.

In this thesis, we present three novel circuit topologies, two of them being NMOS  $V_{T0}$  monitors and the last one being a PMOS  $V_{T0}$  monitor. The three structures are resistorless self-biased circuit topologies that present high power supply rejection, low line sensitivity, and allow the direct extraction of the threshold voltage for wide temperature and power supply voltage ranges, with small error. Its design methodology is based on the Unified Current Control Model (UICM), a MOSFET model that is continuous from weak to strong inversion and from triode to saturation regions. The circuits occupy small silicon area, consume just tens of nanoWatts, and can be implemented in any standard digital CMOS process, since they only use MOS transistors (does not need any resistor).

The  $V_{T0}$  monitors are used in different applications in order to prove their functionality, and behavior as part of a system. The applications vary from a reference voltage, that presents performance comparable with state-of-the-art works, to a configuration that allows to obtain a lower process variability, in the output of a self-biased circuit that generates a complementary to the absolute temperature (CTAT) voltage. In addition, exploiting the ability to operate as an specific current ( $I_{SQ}$ ) generator, that the  $V_{T0}$  monitors presented here offer, we introduced a new self-biased circuit that produces a CTAT voltage and is less sensitive to process variations, and can be used in band-gap voltage references.

**Keywords:** Threshold voltage, CMOS analog design, Threshold voltage monitor circuit, High-PSRR, resistorless, ultra-low-power, Voltage Reference, Process Compensation.

#### Circuitos Monitores de Tensão de Limiar CMOS de baixa potência e Aplicações

## **RESUMO**

Um monitor de tensão de limiar  $(V_{T0})$  é um circuito que, idealmente, entrega o valor do  $V_{T0}$  como uma tensão na saída, para uma determinada faixa de temperatura, sem a necessidade de polarização externa, configurações paramétricas, ajuste de curvas ou qualquer cálculo subsequente. Estes circuitos podem ser usados em sensores de temperatura, referências de tensão e corrente, dosímetros de radiação e outras aplicações, uma vez que a dependência do  $V_{T0}$  nas condições de operação é um aspecto bem modelado. Além disso, estes circuitos podem ser utilizados para monitoramento de processos de fabricação e para compensação da variabilidade do processo, uma vez que o  $V_{T0}$  é um parâmetro chave para o comportamento do transistor e sua modelagem.

Nesta tese, são apresentadas três novas topologias de circuitos, duas são monitores de  $V_{T0}$  NMOS e a terceira é um monitor de  $V_{T0}$  PMOS. As três estruturas são topologias de circuito auto-polarizadas que não utilizam resistências, e apresentam alta rejeição a variações na alimentação, baixa sensibilidade de Linea, e permitem a extração direta da tensão de limiar para grandes intervalos de temperatura e de tensão de alimentação, com pequeno erro. Sua metodologia de projeto é baseada no modelo unificado controlado por corrente (UICM), um modelo MOSFET que é contínuo, desde o nível de inversão fraca a forte e para as regiões de operação de triodo e saturação. Os circuitos ocupam uma pequena área de silício, consomem apenas dezenas de nanowatts, e podem ser implementados em qualquer processo padrão CMOS digital, uma vez que só utilizam transistores MOS (não precisa de nenhum resistor).

Os monitores de  $V_{T0}$  são utilizados em diferentes aplicações, a fim de investigar a sua funcionalidade e comportamento como parte de um sistema. As aplicações variam de uma tensão de referência, que apresenta um desempenho comparável ao estado da arte, para uma configuração que permite obter uma menor variabilidade com processo na saída de um circuito auto-polarizado que gera um tensão CTAT. Além disso, explorando a capacidade de funcionar como um gerador de corrente específica ( $I_{SQ}$ ) que os monitores de  $V_{T0}$  aqui apresentados oferecem, introduz-se um novo circuito auto-polarizado que gera um tensão CTAT, que é menos sensível a variações de processo, e pode ser usado em referências de tensão band-gap.

**Palavras-chave:** projeto analógico CMOS, Monitor de tensão de limiar, referência de tensão, ultra-baixo consumo, baixa alimentação.

## LIST OF FIGURES

| 1.1  | $I_{DS}$ vs $V_G$ in different scales                                                                  | 15 |

|------|--------------------------------------------------------------------------------------------------------|----|

| 1.2  | $I_{DS}$ and its diffusion and drift components vs $V_G$ for a MOSFET with                             |    |

|      | $V_{DS}=\phi_t/2$                                                                                      | 16 |

| 1.3  | $F(i_f)$ and its drift and diffusion components vs $i_f$                                               | 16 |

| 1.4  | Circuit configuration for measuring the $g_m/I_D$ characteristic in the                                |    |

|      | linear region                                                                                          | 18 |

| 1.5  | $g_m/I_D$ as a function of $V_G$                                                                       | 18 |

| 2.1  | Schematic of the circuit proposed by TSIVIDIS; ULMER                                                   | 21 |

| 2.2  | Schematic of the circuit proposed by ALINI et al                                                       | 22 |

| 2.3  | Schematic of the circuit proposed by WANG                                                              | 22 |

| 2.4  | (a) A transistor array with a size of $n \times m$ and (b) its equivalent                              |    |

|      | cascode circuit which corresponds to (c) a single MOS transistor with                                  |    |

|      | reduced $K$ and increased $V_T$                                                                        | 23 |

| 2.5  | Schematic of the circuit proposed by JOHNSON                                                           | 23 |

| 2.6  | Schematic of the circuit proposed by YU; GEIGER                                                        | 24 |

| 2.7  | Schematic of the circuit proposed by FIKOS; SISKOS                                                     | 25 |

| 2.8  | Schematic of the circuit proposed by SIEBEL; SCHNEIDER; GALUP-MONTORO                                  | 26 |

| 2.9  | Schematic of the circuit proposed by MATTIA; KLIMACH; BAMPI                                            | 27 |

| 2.10 | Schematic of the circuit proposed by MATTIA; KLIMACH; BAMPI                                            | 28 |

| 3.1  | Unbalanced $V_{T0}$ monitor circuit concept                                                            | 31 |

| 3.2  | Self-Cascode structure                                                                                 | 32 |

| 3.3  | Unbalanced $V_{T0}$ monitor circuit                                                                    | 32 |

| 3.4  | Unbalanced $V_{T0}$ monitor with an OA connected to improve LS and                                     |    |

|      | PSR                                                                                                    | 34 |

| 3.5  | Schematic of the proposed unbalanced $V_{T0}$ monitor                                                  | 34 |

| 3.6  | Pseudo-Differential Amplifier                                                                          | 35 |

| 3.7  | Unbalanced $V_{T0}$ monitor layout                                                                     | 36 |

| 3.8  | Difference between the theoretical value of $V_{T0}$ (UICM) and the sim-                               |    |

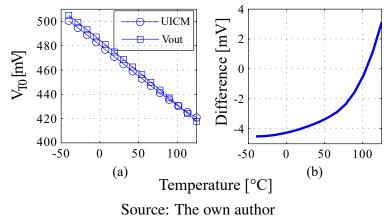

|      | ulated output of the $V_{T0}$ monitor (Vout)                                                           | 37 |

| 3.9  | Percentual error in the $V_{T0}$ extracted by the circuit                                              | 37 |

| 3.10 | Supply voltage sweep vs. supply current (blue) and output (red)                                        | 37 |

| 3.11 | PSR at the output, for -40 $^{\circ}$ C (green), 27 $^{\circ}$ C (blue), and 125 $^{\circ}$ C (red).   | 38 |

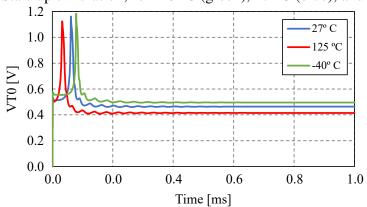

| 3.12 | Start-up simulation, for -40 $^{\circ}$ C (green), 27 $^{\circ}$ C (blue), and 125 $^{\circ}$ C (red). | 38 |

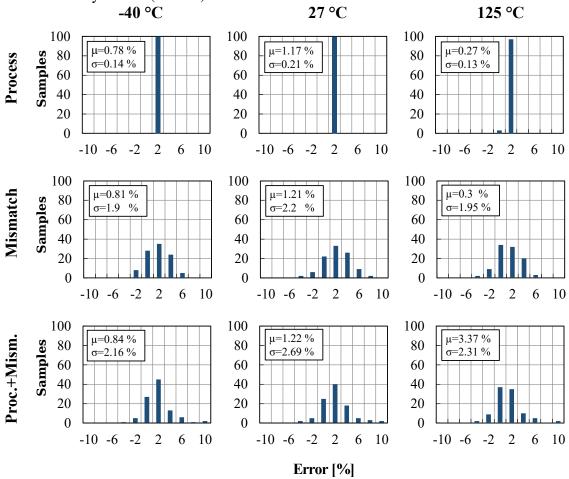

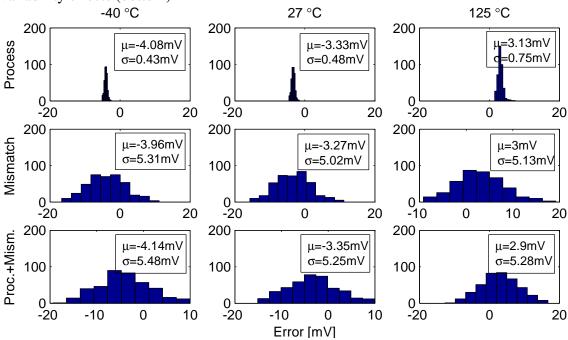

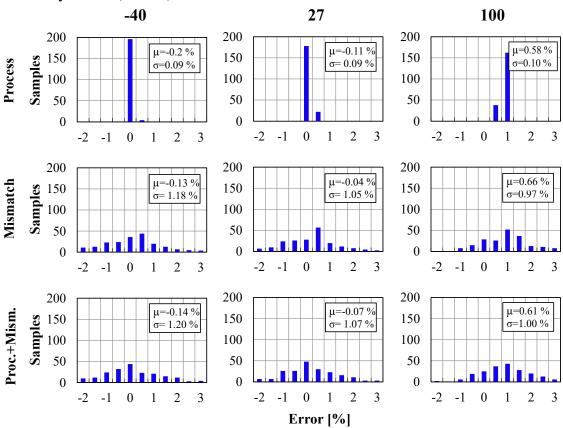

| 3.13       | Monte Carlo simulation results for Process (top), Mismatch (middle)                         |    |

|------------|---------------------------------------------------------------------------------------------|----|

|            | and both variability effects (bottom)                                                       | 39 |

| 3.14       | $V_{T0}$ monitor circuit basic topology                                                     | 40 |

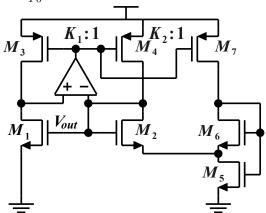

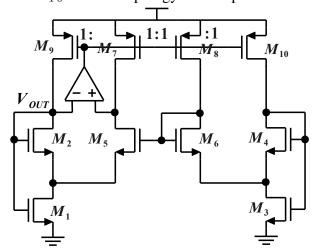

| 3.15       | $V_{T0}$ monitor topology with improved LS and PSR                                          | 41 |

| 3.16       | Pseudo-Differential Amplifier                                                               | 41 |

| 3.17       | $V_{T0}$ monitor with Start-Up circuit and improved LS and PSR                              | 42 |

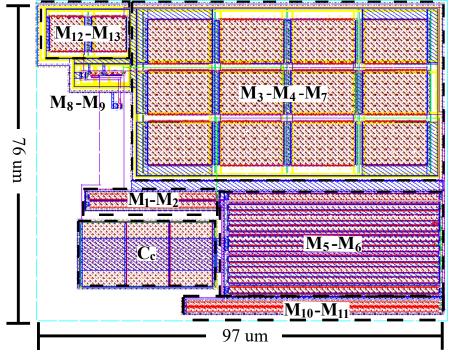

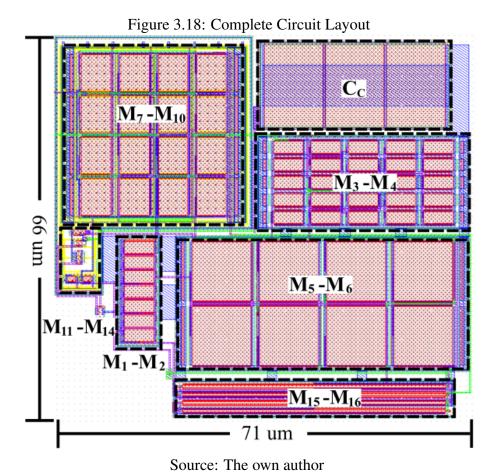

| 3.18       | Complete Circuit Layout                                                                     | 44 |

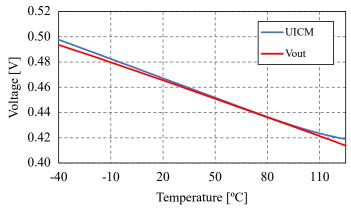

| 3.19       | (a) $V_{T0}$ value and (b) difference from the simulated monitor circuit                    |    |

|            | (Vout) and from the $g_m/I_D$ model (UICM) vs temperature                                   | 44 |

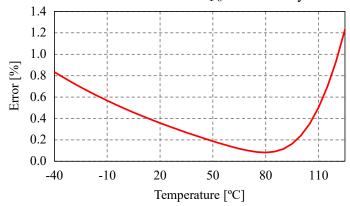

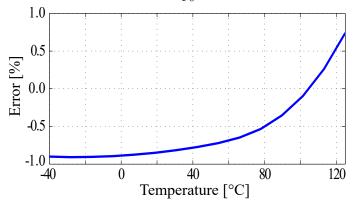

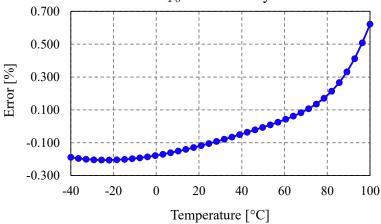

| 3.20       | Percentual error in the $V_{T0}$ monitored value over temperature                           | 45 |

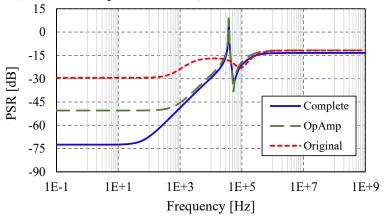

| 3.21       | PSR of the output over frequency                                                            | 45 |

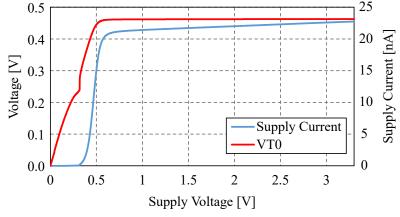

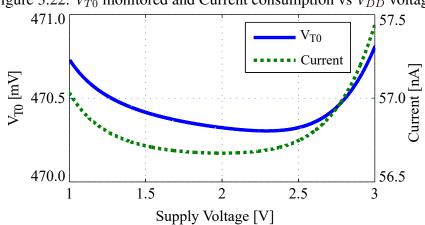

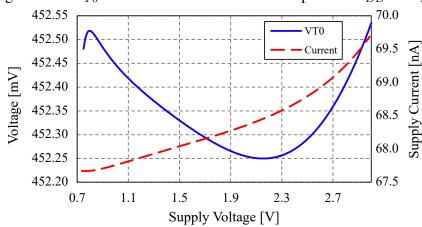

| 3.22       | $V_{T0}$ monitored and Current consumption vs $V_{DD}$ voltage                              | 46 |

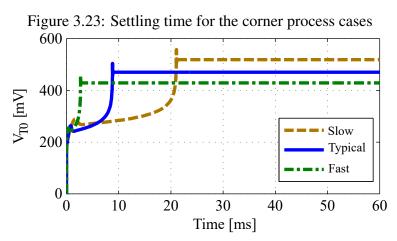

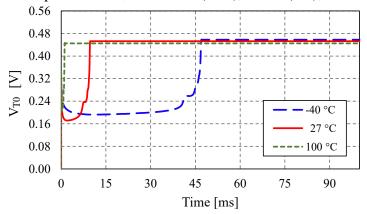

| 3.23       | Settling time for the corner process cases                                                  | 46 |

| 3.24       | Monte Carlo simulations for Process (top), Mismatch (middle) and                            |    |

|            | both variability effects (bottom)                                                           | 47 |

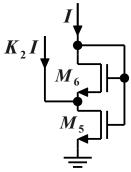

| 3.25       | $I_{SQ}$ current generator                                                                  | 49 |

| 3.26       | PMOS $V_{T0}$ monitor circuit                                                               | 50 |

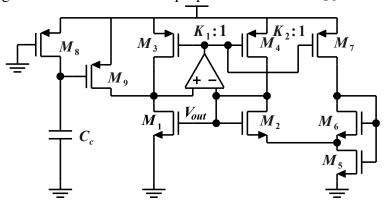

| 3.27       | PMOS $V_{T0}$ monitor circuit, with LS and PSR improvements                                 | 50 |

| 3.28       | PMOS pseudo-differential Amplifier                                                          | 51 |

| 3.29       | Proposed PMOS $V_{T0}$ monitor circuit                                                      | 51 |

| 3.30       | Difference between the theoretical value of $V_{T0}$ (UICM) and the sim-                    |    |

|            | ulated output of the $V_{T0}$ monitor (Vout)                                                | 53 |

| 3.31       | Percentual error in the $V_{T0}$ monitored by the circuit over temperature.                 | 54 |

| 3.32       | PSR at the output over frequency, for the original circuit (red), with                      |    |

|            | OA connected (green), and final implementation (blue)                                       | 54 |

| 3.33       | $V_{T0}$ monitored and Current consumption vs $V_{DD}$ voltage                              | 55 |

| 3.34       | Start-up simulation, for -40 °C (blue), 27 °C (red), and 125 °C (green).                    | 55 |

| 3.35       | Monte Carlo simulations for Process (top), Mismatch (middle) and                            |    |

|            | both variability effects (bottom)                                                           | 56 |

|            |                                                                                             |    |

| 4.1        | Process monitor circuit                                                                     | 58 |

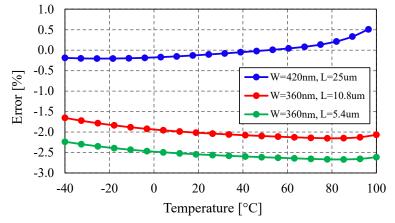

| 4.2        | Error in the output of the process monitor for different channel lengths.                   | 59 |

| 4.3        | $V_{T0}$ monitor topology with improved LS and PSR                                          | 60 |

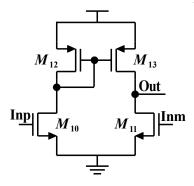

| 4.4        | Differential Pair PTAT generator schematic                                                  | 61 |

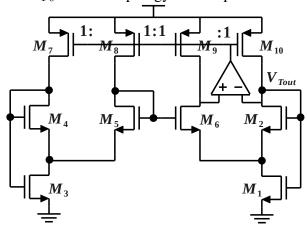

| 4.5        | Proposed voltage reference schematic                                                        | 62 |

| 4.6        | Proposed voltage reference layout                                                           | 64 |

| 4.7        | CTAT, PTAT and $V_{REF}$ voltages                                                           | 64 |

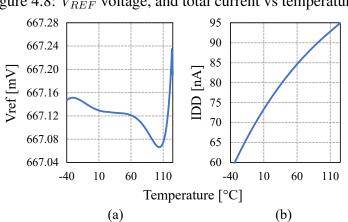

| 4.8        | $V_{REF}$ voltage, and total current vs temperature                                         | 64 |

| 4.9        | PSR in the output over frequency                                                            | 65 |

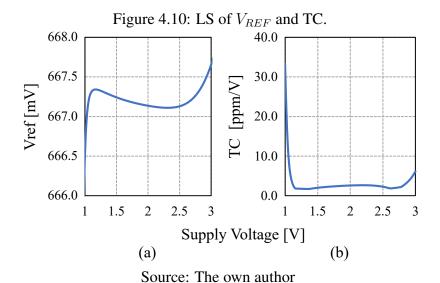

| 4.10       | LS of $V_{REF}$ and TC                                                                      | 65 |

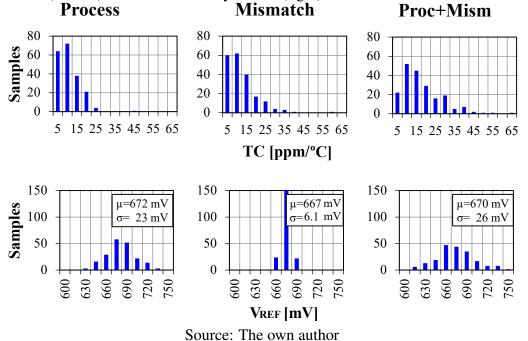

| 4.11       | Monte Carlo simulations of TC (top) and Vref (bottom) for Process                           |    |

|            | (left), Mismatch (middle) and both variability effects (right)                              | 66 |

| 4.12       | BJT bias concept                                                                            | 68 |

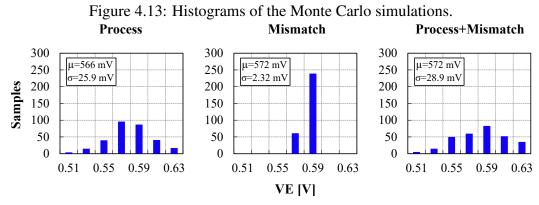

| 4.13       | Histograms of the Monte Carlo simulations                                                   | 69 |

| 4.14       | BJT bias with the $I_{SQ}$ current generator                                                | 71 |

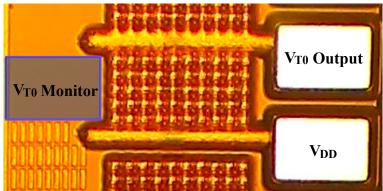

| <b>5</b> 1 | Misso shotomenhy of the helener d I/ manifest singuit felt in the dis-                      |    |

| 5.1        | Micro-photography of the balanced $V_{T0}$ monitor circuit fabricated in IBM 130 nm process | 75 |

|            |                                                                                             | 15 |

| C.1 | Start-up schematic | 82 |

|-----|--------------------|----|

|     |                    |    |

# LIST OF TABLES

| 2.1 | Comparison of recent $V_{T0}$ monitor circuits                     | 29 |

|-----|--------------------------------------------------------------------|----|

| 3.1 | Core transistors sizing                                            | 35 |

| 3.2 |                                                                    |    |

| 3.3 | Sizing of $M_1$ - $M_4$                                            | 43 |

| 3.4 | Sizing of the auxiliary structures                                 | 43 |

| 3.5 | Comparison of recent $V_{T0}$ monitor circuits                     | 47 |

| 3.6 | Sizing of $M_1$ - $M_4$ and $M_{14}$                               | 52 |

| 3.7 | Sizing of the auxiliary structures                                 |    |

| 4.1 | Sizing of $M_1$ - $M_4$ and $M_{14}$                               | 59 |

| 4.2 | Sizing of the core transistors of the voltage reference            | 63 |

| 4.3 | Comparison of recent CMOS Voltage References                       | 66 |

| 4.4 | Results of Monte Carlo simulations considering average process     | 70 |

| 4.5 | Results of Monte Carlo simulations considering average process and |    |

|     | mismatch variations                                                | 70 |

| 4.6 | Results of Monte Carlo simulations considering average process     | 71 |

| 4.7 | Results of Monte Carlo simulations considering average process and |    |

|     | mismatch variations                                                | 71 |

## LIST OF ABBREVIATIONS AND ACRONYMS

BGR Bandgap Voltage Reference

CMOS Complementary Metal Oxide Semiconductor

CTAT Complementary to Absolute Temperature

DUT Device Under Test

LS Line Sensitivity

MI Moderate Inversion

MOSFET Metal Oxide Semiconductor Field Effect Transistor

PSR Power Supply Rejection

PTAT Proportional to Absolute Temperature

SI Strong Inversion

TC Temperature Coefficient

VR Voltage Reference

WI Weak Inversion

## **CONTENTS**

| 1 INTRODUCTION       14         1.1 Threshold Voltage       14         1.1.1 Definition       15         1.1.2 Extraction Method       17         1.2 Threshold Voltage Monitor       17         1.3 Objectives       19         1.4 Organization       19         2 THRESHOLD VOLTAGE MONITORS OVERVIEW       20         2.1 Early Designs       20         2.2 Recent Development in $V_{T0}$ Monitors       25         2.3 Comparison of recent works and State of the Art       28         3 PROPOSED NMOS AND PMOS THRESHOLD VOLTAGE MONITORS       30         3.1 Unbalanced NMOS $V_{T0}$ monitor       30         3.1.1 $V_{T0}$ Monitor concept       31         3.1.2 Design Methodology       34         3.1.3 Results       35         3.2 Balanced NMOS $V_{T0}$ Monitor       39         3.2.1 Circuit Description       40 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1.1Definition151.1.2Extraction Method171.2Threshold Voltage Monitor171.3Objectives191.4Organization192THRESHOLD VOLTAGE MONITORS OVERVIEW202.1Early Designs202.2Recent Development in $V_{T0}$ Monitors252.3Comparison of recent works and State of the Art283PROPOSED NMOS AND PMOS THRESHOLD VOLTAGE MONITORS303.1Unbalanced NMOS $V_{T0}$ monitor303.1.1 $V_{T0}$ Monitor concept313.1.2Design Methodology343.1.3Results353.2Balanced NMOS $V_{T0}$ Monitor39                                                                                                                                                                                                                                                                                                                                                                        |

| 1.1.2       Extraction Method       17         1.2       Threshold Voltage Monitor       17         1.3       Objectives       19         1.4       Organization       19         2       THRESHOLD VOLTAGE MONITORS OVERVIEW       20         2.1       Early Designs       20         2.2       Recent Development in $V_{T0}$ Monitors       25         2.3       Comparison of recent works and State of the Art       28         3       PROPOSED NMOS AND PMOS THRESHOLD VOLTAGE MONITORS       30         3.1 $V_{T0}$ Monitor concept       31         3.1.1 $V_{T0}$ Monitor concept       31         3.1.2       Design Methodology       34         3.1.3       Results       35         3.2       Balanced NMOS $V_{T0}$ Monitor       39                                                                                     |

| 1.2Threshold Voltage Monitor171.3Objectives191.4Organization192THRESHOLD VOLTAGE MONITORS OVERVIEW202.1Early Designs202.2Recent Development in $V_{T0}$ Monitors252.3Comparison of recent works and State of the Art283PROPOSED NMOS AND PMOS THRESHOLD VOLTAGE MONITORS303.1 $V_{T0}$ Monitor concept313.1.1 $V_{T0}$ Monitor concept313.1.2Design Methodology343.1.3Results353.2Balanced NMOS $V_{T0}$ Monitor39                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1.3       Objectives       19         1.4       Organization       19         2       THRESHOLD VOLTAGE MONITORS OVERVIEW       20         2.1       Early Designs       20         2.2       Recent Development in $V_{T0}$ Monitors       25         2.3       Comparison of recent works and State of the Art       28         3       PROPOSED NMOS AND PMOS THRESHOLD VOLTAGE MONITORS       30         3.1       Unbalanced NMOS $V_{T0}$ monitor       30         3.1.1 $V_{T0}$ Monitor concept       31         3.1.2       Design Methodology       34         3.1.3       Results       35         3.2       Balanced NMOS $V_{T0}$ Monitor       39                                                                                                                                                                           |

| 1.4Organization192THRESHOLD VOLTAGE MONITORS OVERVIEW202.1Early Designs202.2Recent Development in $V_{T0}$ Monitors252.3Comparison of recent works and State of the Art283PROPOSED NMOS AND PMOS THRESHOLD VOLTAGE MONITORS303.1Unbalanced NMOS $V_{T0}$ monitor303.1.1 $V_{T0}$ Monitor concept313.1.2Design Methodology343.1.3Results353.2Balanced NMOS $V_{T0}$ Monitor39                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2THRESHOLD VOLTAGE MONITORS OVERVIEW202.1Early Designs202.2Recent Development in $V_{T0}$ Monitors252.3Comparison of recent works and State of the Art283PROPOSED NMOS AND PMOS THRESHOLD VOLTAGE MONITORS303.1Unbalanced NMOS $V_{T0}$ monitor303.1.1 $V_{T0}$ Monitor concept313.1.2Design Methodology343.1.3Results353.2Balanced NMOS $V_{T0}$ Monitor39                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.1       Early Designs       20         2.2       Recent Development in $V_{T0}$ Monitors       25         2.3       Comparison of recent works and State of the Art       28         3       PROPOSED NMOS AND PMOS THRESHOLD VOLTAGE MONITORS       30         3.1       Unbalanced NMOS $V_{T0}$ monitor       30         3.1.1 $V_{T0}$ Monitor concept       31         3.1.2       Design Methodology       34         3.1.3       Results       35         3.2       Balanced NMOS $V_{T0}$ Monitor       39                                                                                                                                                                                                                                                                                                                      |

| 2.2Recent Development in $V_{T0}$ Monitors252.3Comparison of recent works and State of the Art283PROPOSED NMOS AND PMOS THRESHOLD VOLTAGE MONITORS303.1Unbalanced NMOS $V_{T0}$ monitor303.1.1 $V_{T0}$ Monitor concept313.1.2Design Methodology343.1.3Results353.2Balanced NMOS $V_{T0}$ Monitor39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.3 Comparison of recent works and State of the Art       28         3 PROPOSED NMOS AND PMOS THRESHOLD VOLTAGE MONITORS       30         3.1 Unbalanced NMOS $V_{T0}$ monitor       30         3.1.1 $V_{T0}$ Monitor concept       31         3.1.2 Design Methodology       34         3.1.3 Results       35         3.2 Balanced NMOS $V_{T0}$ Monitor       39                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.3Comparison of recent works and State of the Art283PROPOSED NMOS AND PMOS THRESHOLD VOLTAGE MONITORS303.1Unbalanced NMOS $V_{T0}$ monitor303.1.1 $V_{T0}$ Monitor concept313.1.2Design Methodology343.1.3Results353.2Balanced NMOS $V_{T0}$ Monitor39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3 PROPOSED NMOS AND PMOS THRESHOLD VOLTAGE MONITORS       30         3.1 Unbalanced NMOS $V_{T0}$ monitor       30         3.1.1 $V_{T0}$ Monitor concept       31         3.1.2 Design Methodology       34         3.1.3 Results       35         3.2 Balanced NMOS $V_{T0}$ Monitor       39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3.1       Unbalanced NMOS $V_{T0}$ monitor       30         3.1.1 $V_{T0}$ Monitor concept       31         3.1.2       Design Methodology       34         3.1.3       Results       35         3.2       Balanced NMOS $V_{T0}$ Monitor       39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| $3.1.1$ $V_{T0}$ Monitor concept                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3.1.2       Design Methodology       34         3.1.3       Results       35         3.2       Balanced NMOS $V_{T0}$ Monitor       39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.1.3 Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| <b>3.2</b> Balanced NMOS $V_{T0}$ Monitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.2.1 Circuit Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3.2.2 Circuit Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.2.3 Simulations Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <b>3.3</b> Proposed PMOS $V_{T0}$ monitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3.3.1 Circuit Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3.3.2 Circuit Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.3.3 Simulation Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4 APPLICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4.1 Process Monitor and Modeling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4.2 Voltage References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4.2.1 Circuit Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4.2.2 Circuit Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4.2.3 Simulations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4.3 Process Variability Compensation Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4.3.1 Resistorless BJT bias                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4.3.2 Resistorless BJT bias compensated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.3.3 Resistorless BJT bias, using $I_{SQ}$ current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|            | ION          |          |   |      |        |

|------------|--------------|----------|---|------|--------|

| REFERENCES |              |          |   | <br> | <br>76 |

| APPENDIX A | LIST OF PUBL | ICATIONS | S | <br> | <br>80 |

| APPENDIX B | ACM MOSFET   | MODEL    |   | <br> | <br>81 |

| APPENDIX C | START-UP ANA | LYSIS    |   | <br> | <br>82 |

## 1 INTRODUCTION

The semiconductor industry was a 336 billion dollar market in 2014 (World Semiconductor Trade Statistics, 2015), and it has registered a constant growth in the last decades, solely in the U.S it was the industry with the largest growth in the last 35 years (Semiconductor Industry Association, 2014). This turns the semiconductor industry in one of the most prominent industries in the world. In addition, with the increasing of the Internet of things (IoT) and the necessity of the global connectivity, the integrated circuits (ICs) are ever more present in all aspects of human life, from heart monitors to space navigation systems.

In the heart of this industry is found the transistor, the main element in ICs, that year after year decreases its minimum size thanks to the lithography advances, thus allowing to integrate more elements per area. This increase in the quantity of transistors per area, allows to implement in a smaller area the same circuits that were fabricated before, thereby reducing cost. Another possibility is to add more features to the original system, maintaining the area of previous versions; this results in a more advanced system at the same cost of previous one.

This dissertation discuss one of the most important parameters of the transistor, the threshold voltage  $(V_{T0})$ . This chapter will give the necessary context to understand the developed work. First, the  $V_{T0}$  is introduced, together with its definition and the method to extract it. After that, the importance of the  $V_{T0}$  in microelectronics will be highlighted, for this some applications will be exposed, and then the  $V_{T0}$  monitor will be explained. Next, the objectives of this work will be presented and finally the organization of the text will be detailed.

## 1.1 Threshold Voltage

Few months later of the first successful fabrication of a MOSFET the first model based on  $V_{T0}$  appeared. This model, proposed by IHANTOLA; MOLL (1964), inspired during decades the development of many MOSFET models for SPICE simulation, such as level = 1,2,3 and BSIM. There is no surprise, therefore, that all the models that followed it inherited the  $V_{T0}$  as a fundamental parameter (ORTIZ-CONDE et al., 2013).

Since the first MOSFET model that used the  $V_{T0}$  was developed, there have appeared many models with different approaches and different definitions of the  $V_{T0}$ . PAO; SAH (1966) proposed the first surface potential model, which was based on a double-integration. This model establishes the basis of contemporary compact models. It also inspired BREWS (1978) and BACCARANI; RUDAN; SPADINI (1978) whose independently formulated charge-sheet models. This diversity in the models makes difficult to obtain a unified definition of the  $V_{T0}$  and the same happens with the methods to extract it.

In this work the UICM model was used for its simplicity and physical sustentation. This model, which is detailed in appendix B, takes advantages of the charge-sheet model, and the incrementally linear relationship between the inversion charge density and the surface potential. Next, a definition of the  $V_{T0}$  using the UICM model is delivered as well as a method to obtain its theoretical value.

#### 1.1.1 **Definition**

The threshold voltage can be understood as the voltage that must be applied in the gate of the transistor  $(V_G)$  in order to produce a behavioral change in the drain current  $(I_D)$  of the transistor. At the highest level of abstraction, this behavioral change refers to the voltage in which the current begins to flow. This definition even though is widely known and useful, especially for digital design, is not suitable for analog design, as will be explained.

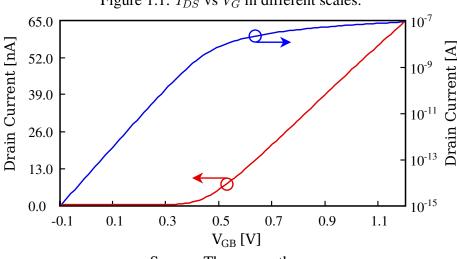

When  $I_D$  is plotted as a function of  $V_G$  (Figure 1.1), it seems that in fact there is a voltage in which the current starts to flow; however, when the current is plotted in a logarithmic scale it is clear that the current actually exists for voltages below that point. As even small currents are important in analog design, this high-level definition of the  $V_{T0}$  results improper. The logarithmic scale also allows to see that  $I_D$  presents two well defined behaviors. First,  $I_D$  behaves exponentially with respect to  $V_G$  for small voltages (weak inversion) while, for larger voltages it behaves quadratically (strong inversion).

Figure 1.1:  $I_{DS}$  vs  $V_G$  in different scales.

Source: The own author.

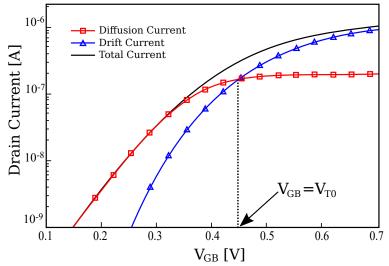

The change in the  $I_D$  behavior is because the physical process that generates the current for large and small values of  $V_G$  is different. As shown in Figure 1.2, the current in weak inversion is due to carrier diffusion, whereas the strong inversion current is mostly due to carrier drift (SIEBEL; SCHNEIDER; GALUP-MONTORO, 2012). This change in the behavior, which has a physical foundation, is used in order to create a more proper  $V_{T0}$  definition. Then, as shown in Figure 1.2, the  $V_{T0}$  is the voltage in which the drift and diffusion component of the current are equal.

Defined  $V_{T0}$  together with its physical meaning, it is possible to link the aforementioned concepts with the UICM model. This model defines  $I_D$  as a function of the forward

Figure 1.2:  $I_{DS}$  and its diffusion and drift components vs  $V_G$  for a MOSFET with  $V_{DS} = \phi_t/2$ .

Source: SIEBEL; SCHNEIDER; GALUP-MONTORO (2012).

and reverse inversion levels ( $F(i_f)$  and  $F(i_r)$ , respectively). The relationship between these inversion levels and the terminal voltages is given by

$$\frac{V_G - V_{T0}}{n\phi_t} - \frac{V_{S(D)}}{\phi_t} = F(i_{f(r)}) = \underbrace{\sqrt{1 + i_{f(r)}} - 1}_{\text{Drift}} + \underbrace{\ln(\sqrt{1 + i_{f(r)}} - 1) - 1}_{\text{Diffusion}}$$

(1.1)

where  $V_S$  and  $V_D$  are the source and drain voltages (all terminal voltages are referenced to the transistor bulk in the UICM model),  $\phi_t$  is the thermal voltage and n is the subthreshold slope factor. From (1.1) it is possible to see that a transistor with the source grounded and with  $V_G$  equal to  $V_{T0}$  has  $F(i_f)$  equal to zero. This, as expected, happens when the drift and diffusion components are equal, and as shown in Figure 1.3 occurs for an  $i_f$  equal to 3. Eq. (1.1) does not consider short-channel effects being valid only for long channel devices.

15

10

Diffusion Component

Drift Component

Total F(3)=0  $i_f$   $i_f$

Figure 1.3:  $F(i_f)$  and its drift and diffusion components vs  $i_f$ .

Source: The own author.

#### 1.1.2 Extraction Method

Just as there are many  $V_{T0}$  definitions, exist countless number of methods to extract the  $V_{T0}$  value. ORTIZ-CONDE et al. (2013) revised the most used methods and summarized about 12 works. As the  $V_{T0}$  was defined physically and through UICM model, only methods using this concepts are shown here. In the constant current (CC) method the MOSFET operates in the saturation region and it must be biased with a specific value of  $I_D$  in order to obtain an accurate value of  $V_{T0}$ . The CC method is the most direct procedure but presents the disadvantage of requiring a previous estimation of the sheet normalization transistor current ( $I_{SQ}$ ). On the other hand, in the  $g_{ch}/I_D$  and  $g_m/I_D$  methods, the MOS transistor operates in the linear region. These methods are similar and present a comparable accuracy; however, as the transconductance  $g_{ch}$ , it was preferred to use the  $g_m/I_D$  method in order to extract the theoretical value of  $V_{T0}$ .

The aim of the  $g_m/I_D$  extraction method is to obtain the  $V_{T0}$  value from a  $g_m/I_D$  vs  $V_G$  graph. For this, first it is necessary to get the value of the  $g_m/I_D$  relationship for the threshold condition ( $i_f = 3$ ). To do this, it is necessary to give some definitions from the UICM model. First, the source and drain transconductances are be given by

$$g_{ms(d)} = \frac{2I_S}{\phi_t} (\sqrt{1 + i_{f(r)} - 1})$$

(1.2)

where  $I_S$  is the specific current of the transistor. Then, using (B.1), (1.1), (1.2) and remembering that  $g_m$  is expressed mathematically as the derivative of  $I_D$  with respect to  $V_G$ , one obtains

$$\frac{g_m}{I_D} = \frac{dI_D}{I_D dV_G} = \frac{g_{ms} - g_{md}}{nI_D} = \frac{2}{n\phi_t(\sqrt{1 + i_f} + \sqrt{1 + i_r})}$$

(1.3)

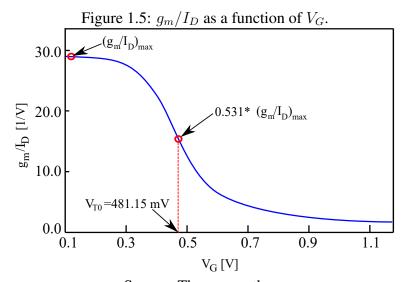

If it is assumed that the variation of n with  $V_G$  is small (n approximately constant for any  $i_f$ ), it is possible to get the  $g_m/I_D$  value from (1.3) for a given  $i_f$  and  $i_r$ . Then, as  $i_f$  is set for the threshold condition, just rest to obtain the value of  $i_r$ , which can be obtained from (1.1) once  $V_D$  is set in  $\phi_t/2$  in order to maintain the transistor in the linear region. Therefore,  $i_r=2.31$ , and  $g_m/I_D=0.531*(2/n\phi_t)=0.531*(g_m/I_D)_{\rm max}$ .

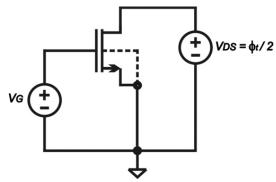

To apply the  $g_m/I_D$  extraction method the test-bench of Figure 1.4 is implemented. In this,  $V_{DS}$  is fixed at the desired bias condition  $(\phi_t/2)$ , and  $V_G$  varies from 0 to 1.2 V. The current is saved to obtain the  $g_m/I_D$  curve. Finally with the maximum value of the  $g_m/I_D$  relationship the point that corresponds to the threshold voltage condition is found. In Figure 1.5 an example for a 130 nm NMOS transistor I/O type of the IBM process with W=2  $\mu$ m and L=2  $\mu$ m is given. The transistor presents a  $(g_m/I_D)_{\rm max}=28.98$ , and therefore for the point in which  $(g_m/I_D)$ =15.38 it is found  $V_G=V_{TO}=481.15$  mV.

## 1.2 Threshold Voltage Monitor

The threshold voltage is such an important parameter in almost all the MOSFET models that accurate values of it for various geometries and bias conditions have to be determined to characterize the transistor for optimizing circuit design (TSAY; LIU; WU, 1996). Threshold voltage is also used to monitor the success of the fabrication process and for assessing and predicting device performance variability, because it depends sensitively on the device geometries, the gate-oxide thickness and the channel doping, as well as other

Figure 1.4: Circuit configuration for measuring the  $g_m/I_D$  characteristic in the linear region.

Source: SIEBEL; SCHNEIDER; GALUP-MONTORO (2012).

Source: The own author.

operation reliability factors (ORTIZ-CONDE et al., 2013). Thus, the measurement of  $V_{T0}$  is a fundamental step in process characterization and circuit design.

Other uses for the  $V_{T0}$  measurement are the compensation of process parameters, the cancellation itself in I –V and V–I conversion circuits, the production of correct bias conditions (FIKOS; SISKOS, 2001) and, lately, in the implementation of MOSFET radiation dosimeters. Also taking advantage of its excellent linearity with respect to temperature,  $V_{T0}$  can be used to do on-chip absolute or relative temperature sensing and full CMOS voltage references (CILINGIROGLU; HOON, 2003).

This range of applications makes the  $V_{T0}$  measurement an area of large interest. Traditionally, the threshold voltages of MOSFETs are extracted either from graphical methods or from numerical methods (ORTIZ-CONDE et al., 2013; THOMAS; HOLMAN, 1999); unfortunately, these methods are highly time-consuming and/or computationally intensive and cannot be suitably used for real-time on-chip applications (DASGUPTA; SAHA; SAMANTA, 2012).

These problems can be overcome by using a threshold voltage monitor, which is a circuit that ideally delivers the estimated  $V_{T0}$  value as a voltage at its output, for a given temperature range, without external biases, parametric setups, curve fitting or any subsequent calculation. As was cited above, the  $V_{T0}$  measurement can be used in countless

applications. This makes the  $V_{T0}$  monitor a multipurpose circuit, and therefore, it must present high performance in order to maintain the total yield of a system. The most important aspects in  $V_{T0}$  monitors are:

- Large range of temperature operation

- High Power Supply Rejection (PSR)

- Low Line Sensitivity (LS)

- Small error

- Low power consumption

- Include a Start-up stage

## 1.3 Objectives

Based on the wide range of applications in which the  $V_{T0}$  monitors can be used, and in the fact that none of the available topologies presents the minimum performance to be used as multi-purpose circuits, it can be concluded that the study and design of these circuits is of great interest. This thesis aims the implementation of PMOS and NMOS  $V_{T0}$  monitors that present high performance, making possible its integration in different systems. In addition, this thesis intends to develop some circuits using the proposed  $V_{T0}$  monitors, this in order to prove the behavior of the monitors as part of a system.

## 1.4 Organization

The text is organized as follows. Chapter 2 makes a summarized bibliography review in chronological order of  $V_{T0}$  monitors, and in the end of this section, a comparison between state-of-the-art works is given. After that, Chapter 3 shows the circuit analysis, circuit design, and post-layout results of the proposed NMOS and PMOS  $V_{T0}$  monitors. It also introduces the  $I_{SQ}$  generation, a concept used in the PMOS  $V_{T0}$  monitor implementation. Chapter 4 presents some applications of the proposed  $V_{T0}$  monitors, and finally, the conclusions and considerations for future work are included in Chapter 5. Some additional information, as the UICM model, can be found in the Appendix at the end of this text.

#### 2 THRESHOLD VOLTAGE MONITORS OVERVIEW

As was related in the last chapter, there are a lot of applications in which a  $V_{T0}$  monitor can be used. This versatility makes this circuit a structure of great interest, and has motivated through the years many authors to propose several topologies. First designs, in general, operate in strong inversion and use quadratic model. These designs were useful solutions at that time, but now they represent low-efficient circuits, since the strong inversion operation results in high power consumption. Recent works use the transistors in moderate and/or weak inversion, thus achieving low power consumption. Unfortunately, these circuits still present some problems associated to its integration, as it will be explained later on. In this chapter, we summarize chronologically the early designs in  $V_{T0}$  monitors, then we expose the most recent advances in the area, and finally we summarize and compare the most important works.

## 2.1 Early Designs

The first work related to the extraction of the  $V_{T0}$  value using a circuit was published by TSIVIDIS; ULMER (1979). In Figure 2.1 it is shown the proposed circuit. In this structure, the bias current  $I_R$  of the centre string is scaled, and mirrored by the PMOS current mirror ( $M_G$ - $M_H$ ) and the NMOS cascode current mirror ( $M_A$ - $M_D$ ). Since all the transistors that were used for this design operate in strong inversion, and in the saturation region, their drain current can be approximately given by:

$$I = \frac{1}{2}Sk(V_{GS} - V_{T0})^2 \tag{2.1}$$

where S is the aspect ratio of the transistor W/L (being W and L the width and length of the transistor respectively), and  $k = \mu_n C'_{ox}$ . Considering the remaining transistors and (2.1), we obtain an expression for the output voltage  $V_X$ ,

$$V_X = m \left( V_{T0} + \sqrt{\frac{2I_E}{S_E k_E}} \right) - \left( V_{T0} + \sqrt{\frac{2I_F}{S_F k_F}} \right)$$

(2.2)

where  $I_E$  and  $k_E$  are the common values of I and k of the transistors  $\mathbf{M}_{E1}$ - $\mathbf{M}_{Em}$ , and  $I_F$  and  $k_F$  are the values of I and k of the transistor  $\mathbf{M}_F$ . Now, if the circuit is biased and sized in order to maintain the relation  $I_F/I_E = m^2 S_F/S_E$  it is obtained that  $V_X$  is equal to:

$$V_X = (m-1)V_{T0} (2.3)$$

It is clear that a voltage equal (m = 2) or proportional to  $V_{T0}$  can be obtained. In the same paper, Tsividis presents a second structure for which the same equations are valid.

The second circuit presents the advantage of delivering its output as a voltage referenced to the ground and not to  $V_{DD}$ . The author also comments about the possibility of the implementation of a PMOS  $V_{T0}$  monitor if a triple-well process is available. This circuit was for almost 10 years the state-of-the-art, although it presented at its output an error higher than 10%.

V<sub>DD</sub>

M<sub>G</sub>

M<sub>H</sub>

M<sub>E</sub>

M<sub>E</sub>

M<sub>E</sub>

M<sub>B</sub>

Figure 2.1: Schematic of the circuit proposed by TSIVIDIS; ULMER

Source: TSIVIDIS; ULMER (1979).

ALINI et al. (1992) proposed the circuit shown in Figure 2.2. The main idea is to bias with the same current ( $I_{do}$ ) two transistors, M1 and M2, which present an aspect ratio relationship

$$S_2/S_1 = \alpha^2 \tag{2.4}$$

Using (2.1) and (2.4), the relationship between the overdrive voltages of M1 and M2 can be written as:

$$V_{ov1} = \alpha V_{ov2} \tag{2.5}$$

Then, if the  $V_{GS}$  of transistor M2 is amplified by  $\alpha$ , it is obtained in the output of the subtractor:

$$V_2 - V_1 = \alpha(V_{ov2} + V_{T0}) - (V_{ov1} + V_{T0}) = (\alpha - 1)V_{T0}$$

(2.6)

Finally, after amplifying by a factor of  $1/(\alpha-1)$ , the output of the circuit  $V_{out}=V_{T0}$  is obtained. This implementation, even though presents an error relatively low (4%), has a big complexity due to the amplifiers and the subtractor, which in the case of Alini were implemented using BJT transistors. Another problem intrinsic to this structure is, that any mismatch between the bias current, or the M1-M2 transistors, results in an error in the  $V_{T0}$  value.

WANG (1992) found a similar solution to that presented by Alini, but instead of biasing two transistors with a current source, he generates the current by biasing the gate of

Ido V1 V1 V0ut V2 V1 V0ut V1 V0ut

Figure 2.2: Schematic of the circuit proposed by ALINI et al.

Source: ALINI et al. (1992).

one of the transistors, and then, bias the other one by using a PMOS current mirror. In this way, he does not need a current source, but instead, he needs a bias voltage.

The circuit is shown in Figure 2.3, and works as follows. A voltage  $V_B$  bias the transistor  $M_0$ , which generates a current. This current is copied by a PMOS current mirror, into an array of nxm transistors (Figure 2.4). Assuming that all the transistors are equal, and using the quadratic model, we can obtain:

$$V_O = \frac{n}{\sqrt{m}}V_B + n\left(1 - \frac{1}{\sqrt{m}}\right)V_{T0} \tag{2.7}$$

If  $m=n^2$  the expression is simplified to  $V_O=V_B+(n-1)V_{T0}$ . Now, taking the difference between  $V_B$  and the  $V_O$ , we obtain

$$\Delta V_O = V_B - V_O = (n-1)V_{T0} \tag{2.8}$$

Then, an array of  $2 \times 4$  transistors leads in the output, a voltage that is equal to the  $V_{T0}$  value. This implementation has the advantage of using transistors of the same size, which improves the matching of the transistors and also allows to implement common centroid structures. On the other hand, the structure presents the problem of using an additional voltage, as was above mentioned, and additionally, the circuit does not deliver the  $V_{T0}$  value referenced to ground but as a differential voltage.

$\begin{array}{c|c} & V_{DD} \\ \hline current mirror \\ IN & OUT \\ \hline \\ I_d & \Delta V_O \\ \hline \\ N \times n^2 \\ transistor \\ array \\ \hline \\ V_O \\ \hline \end{array}$

Figure 2.3: Schematic of the circuit proposed by WANG

Source: WANG (1992).

(c)

Figure 2.4: (a) A transistor array with a size of  $n \times m$  and (b) its equivalent cascode circuit which corresponds to (c) a single MOS transistor with reduced K and increased  $V_T$

Source: WANG (1992).

(a)

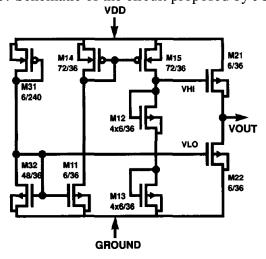

Figure 2.5 shows the  $V_{T0}$  monitor proposed by JOHNSON (1993). This topology presents two main differences with Wang's topology. First, a stage to bias transistor M11 (M<sub>0</sub> in Wang's circuit) was added, thus resolving the necessity for an additional voltage, and turning the circuit a self-bias structure. The second difference is the two-transistor differential amplifier added to the output. This stage takes the differential voltage ( $\Delta V_O$  in Figure 2.3 or VHI-VLO in Figure 2.5) and delivers it as a ground-referenced voltage.

Figure 2.5: Schematic of the circuit proposed by JOHNSON

Source: JOHNSON (1993).

Equations (2.7) and (2.8) are valid also for this circuit, but for simplicity, the last one is repeated here, taking into account the nomenclature of Figure 2.5.

$$VHI - VLO = V_{T0} (2.9)$$

Now, assume that transistor M21 and M22 are identical and that both are in saturation. Writing the  $V_{GS}$  voltages for these transistors,  $V_{GS21} = VHI - VOUT$ , and also  $V_{GS22} = VLO$ . Since M21 and M22 carry the same current, they must also have identical  $V_{GS}$ , thus:

$$VOUT = VHI - VLO = V_{T0} (2.10)$$

This topology was known as an input-free  $V_{T0}$  monitor, because different from previous works, it does not need any voltage or current additionally to the supply voltage which is a big advantage. Nonetheless, the circuit cannot be implemented in any CMOS standard process, since it does not use a common voltage to bias the bulk of all the NMOS transistors.

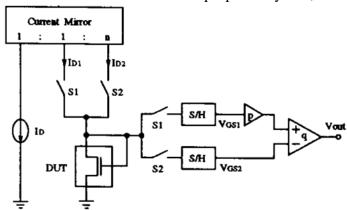

Until now, all the structures are based on two transistors with a known aspect ratio relationship that are biased with the same current. These structures, in general, present the problem that any mismatch between the two transistors will directly affect the  $V_{T0}$  value delivered. YU; GEIGER (1994) proposed a solution to this problem by using only one transistor, and a switched capacitor implementation. The circuit is shown in Figure 2.6. In this circuit, the output of a current mirror  $I_{D1}$  (with S1 closed and S2 open) and  $I_{D2}$  (with S1 open and S2 closed) are applied to a test transistor, which operates in the saturation region. Using the quadratic model (2.1), we obtain:

$$I_{D1} = \frac{1}{2} Sk(V_{GS1} - V_{T0})^2$$

(2.11)

$$I_{D2} = \frac{1}{2} Sk (V_{GS2} - V_{T0})^2$$

(2.12)

Observe that k, S and  $V_{T0}$  are the same in (2.11) and (2.12) because only one test transistor is used. Then, using the relation  $I_{D1} = nI_{D2}$ , it is possible to obtain:

$$V_{T0} = \frac{1}{\sqrt{n} - 1} (\sqrt{n} V_{GS1} - V_{GS2})$$

(2.13)

Assume that a complementary non-overlapping clock drives switches S1 and S2. When S1 is closed,  $V_{GS1}$  is sampled and multiplied by p, and when S2 is closed,  $V_{GS2}$  is sampled and subtracted from  $pV_{GS1}$ . The result is then multiplied by q. Hence,  $V_{out}$  is:

$$V_{out} = q(pV_{GS1} - V_{GS2}) (2.14)$$

From (2.13), (2.14), and assuming  $p = \sqrt{n}$  and  $q = m/(\sqrt{n} - 1)$ , results in  $V_{out} = mV_{T0}$ . Therefore, this circuit can deliver a multiple of  $V_{T0}$  by choosing an integer m. Then,  $V_{T0}$  can be obtained by choosing n = 4 and m = 1, that results in p = 2 and q = 1.

Figure 2.6: Schematic of the circuit proposed by YU; GEIGER

Source: YU; GEIGER (1994).

As was aforementioned, this implementation has a great advantage over the others, because its accuracy is not dependent on the matching of two transistors. Notwithstanding, to achieve this, the circuit uses many structures, as two sample and hold circuits and one differential amplifier, increasing the complexity, and the area when compared with other implementations.

After that, multiple solutions were developed, but it was, probably, Fikos's implementation the most remarkable structure. The circuit is shown in Figure 2.7 and its operation is explained as follows. Considering that all transistors of the circuit operate in saturation, with the ratios  $(S_1 = S_2 = S_3 = S_4/4)$ , and assuming that the  $I_D$  of each transistor follows the simple quadratic law (2.1), then:

$$I_{D1} = I_{D2}$$

:  $V_S = V/2$  (2.15)

$$I_{D3} = I_{D4}$$

:  $V_O = V_{T0}$  (2.16)

Figure 2.7: Schematic of the circuit proposed by FIKOS; SISKOS

Source: FIKOS; SISKOS (2001).

In order to compensate the mismatch problem and some second order effects, the authors added an offset block together with a feedback. The offset was implemented with a simple structure in cascade with the  $V_{T0}$  monitor, thus, this circuit achieves a low error, with a low complexity. Additionally, it was the first structure designed taking care of the power consumption, but even so, the operation in the strong inversion region makes its consumption higher than some tens of micro Watts.

## **2.2** Recent Development in $V_{T0}$ Monitors

Other structures, besides those already presented, as CILINGIROGLU; HOON (2003); SENGUPTA (2004); WANG; TARR; WANG (2004); VLASSIS; PSYCHALINOS (2007) were developed before 2012. All of them operate using the same principle: bias two transistors in strong inversion with a given aspect ratio, and then compare its gate-to-source voltage. The big problem with this approach is the high power consumption, associated to the operation of the transistor in the strong inversion region.

In the last 5 years new structures with low-power consumption have appeared. To accomplish that, these new circuits operate in the weak or/and moderate inversion, taking advantage that there is not speed requirement for  $V_{T0}$  monitors.

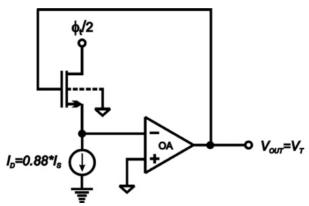

SIEBEL; SCHNEIDER; GALUP-MONTORO (2012) proposed the circuit shown in Figure 2.8. According to the authors "in this circuit, since the MOS transistor operates at low current levels and in the linear region, it is less affected by second order effects" (2012, p. 2).

As the circuit is based on the  $g_{ch}/I_D$  methodology, we present the mathematical explanation, before explain the circuit operation. Using (B.3) and (B.4) from the UICM model (see Appendix B), it is obtained that, if a transistor operates under an inversion level  $i_f=3$  and with  $V_S=0$ , then its  $V_{GB}$  must be equal to  $V_{T0}$ . Now, if we also set  $V_{DS}=\phi_t/2$ , we obtain  $i_r=2.12$  and  $I_D=0.88*I_S$ . Then, looking to the circuit in Figure 2.8, we can recognize that, because the transistor is biased with a current equal to  $0.88\times I_S$ , and presents a  $V_S=0$  and  $V_D=\phi_t/2$ , it must have  $V_{GB}=V_{T0}$ . This condition is achieved through the use of the OPAMP, that create a feedback.

This circuit was implemented using discrete elements, reason for which it is not possible to compare its behaviour with that of other structures. Also it is important to remember that, even when the circuit is simple, some problems need to be resolved in order to implement an integrated version, as for example find a circuit that generates a current exactly equal to  $0.88 \times I_S$ .

Figure 2.8: Schematic of the circuit proposed by SIEBEL; SCHNEIDER; GALUP-MONTORO

Source: SIEBEL; SCHNEIDER; GALUP-MONTORO (2012).

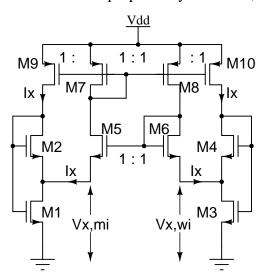

In 2014, MATTIA; KLIMACH; BAMPI proposed a new monitor, based on the well-known current source of Figure 2.9. It is important to highlight that, although the circuit is the same presented by SERRA-GRAELLS; HUERTAS (2003), its functionality is different.

This circuit, as the one proposed by Siebel, is designed using the UICM model, and is based on the fact that a transistor that operates under an inversion level  $i_f=3$  with  $V_S=0$  will have a  $V_{GB}=V_{T0}$ , as was above explained. Then, suppose that in the circuit shown in Figure 2.9, M1 operates under such condition ( $i_f=3$ ), being in the moderate inversion region. M2 is kept saturated too, and sharing the same gate voltage, but with a source voltage different from zero. Using (B.3) and (B.4) for M2, knowing that  $V_{G1}=V_{G2}=V_{T0}$  and  $I_{D1}=K1I_{D2}$ , leads to (2.17).

$$V_{s2} = -\phi_t F(i_{f2}) = -\phi_t F\left(\frac{3S_1}{K1S_2}\right)$$

(2.17)

Thus, a voltage proportional to  $\phi_t$  needs to be attached to the source terminal of M2, in order to maintain the equality of (2.17). This condition is achieved by using the self-cascode

Figure 2.9: Schematic of the circuit proposed by MATTIA; KLIMACH; BAMPI

Source: MATTIA; KLIMACH; BAMPI (2014a).

(SC) composed by transistors M3 and M4. In this configuration, the lower transistor (M3) works in triode, while the upper transistor (M4) operates in saturation. Consequently, the voltage in the output node of the SC is determined by:

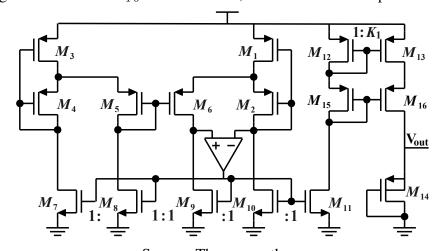

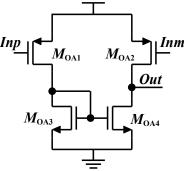

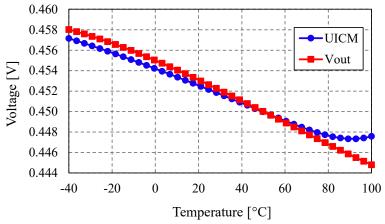

$$V_{DS3} = \phi_t [F(i_{f3}) - F(i_{f4})] \tag{2.18}$$