# Adaptação de uma Plataforma para Avaliação da Confiabilidade de Sistemas de Comunicação em FPGAs

Autor: Eduardo Nunes de Souza Orientador: Prof. Dr. Gabriel Luca Nazar {ensouza, glnazar}@inf.ufrgs.br

## **INTRODUÇÃO**

Os sistemas de comunicação utilizam FPGAs (Field Programmable Gate Arrays) extensivamente para a implementação de seus projetos. Quando expostos a determinados ambientes, os FPGAs apresentam um alto índice de falhas devido a partículas ionizantes presentes no meio. Dessa forma, se faz necessário avaliar o impacto dessas falhas através de simulações, que necessitam de estímulos apropriados para que se obtenham medições relevantes.

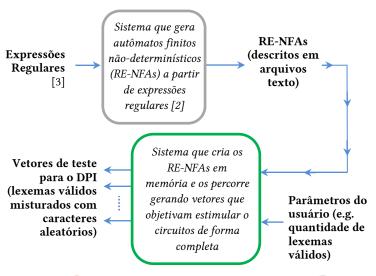

Neste trabalho, a aplicação utilizada é o DPI (*Deep Packet Inspection*) que consiste em monitorar o tráfego de entrada e saída de dispositivos de rede para detectar possíveis atividades maliciosas, como vírus, spam ou cobrir outras vulnerabilidades de software. A maior parte dos ataques maliciosos possui algum tipo de assinatura, assim o DPI busca reconhecer esses padrões que estão trafegando pela rede. Em outras palavras, o DPI faz o reconhecimento de expressões regulares – tarefa que pode ser bastante eficiente em FPGAs. O dispositivo utilizado para realizar os testes é o FPGA Xilinx Virtex-5 XUPV5-LX110T (apresentado na figura abaixo).

#### **METODOLOGIA**

## **RESULTADOS EXPERIMENTAIS**

### **CONSIDERAÇÕES FINAIS**

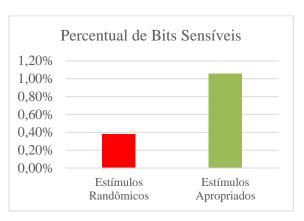

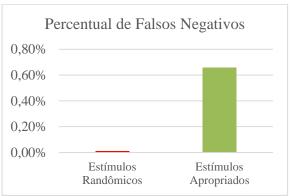

Ao utilizar a ferramenta desenvolvida para estimular o circuito de maneira completa, foi possível notar a presença de falsos negativos (não observados com estímulos randômicos) e o número de bits sensíveis observados quase triplicou. A detecção de falsos negativos é de especial importância, pois eles podem indicar relevantes ameaças de segurança.

#### REFERÊNCIAS

- [1] Gabriel L. Nazar e Luigi Carro, "Fast Single-FPGA Fault Injection Platform". IEEE, International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems (DFT), 2012.

- [2] Yi-Hua E. Yang e Viktor K. Prasanna, "High-Performance and Compact Architecture for Regular Expression Matching on FPGA". IEEE Trans. Comput., vol. 61, no. 7, pp. 1013-1025, Julho de 2012.

- [3] "SNORT", http://www.snort.org/.

Universidade Federal do Rio Grande do Sul Instituto de Informática

Av. Bento Gonçalves, 9500 – Campus do Vale, Bloco IV CP 15064, 91501-970 – Porto Alegre, RS – Brasil