# Implementação e avaliação de uma arquitetura CGRA sem banco de registradores

### **Laurien Santin**

Orientada por Luigi Carro Universidade Federal do Rio Grande do Sul

lsantin@inf.ufrgs.br

# INTRODUÇÃO

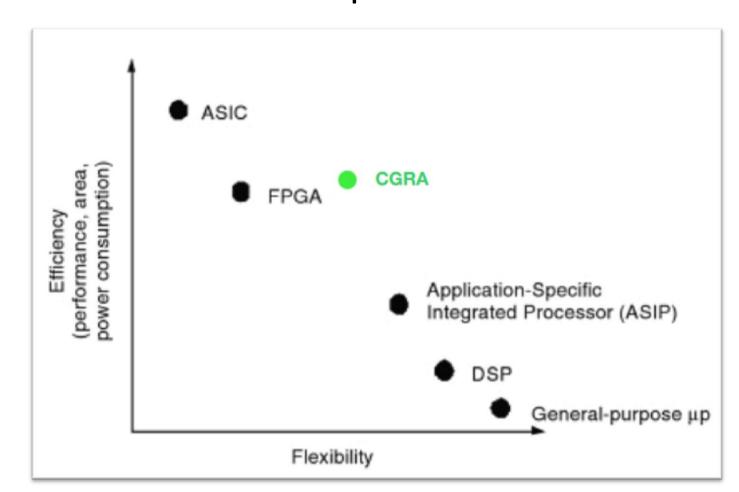

Tivemos um grande avanço na área de microprocessadores nos últimos anos. Todavia, apesar de sua melhora no desempenho, tanto em termos de eficiência temporal como energética, Circuitos Integrados de Aplicação Específica (ASICs) ainda têm performance superior. Nesse contexto arquiteturas reconfiguráveis ganham certo destaque, por balancear a flexibilidade de microprocessadores com a performance de ASICs.

(Fonte: Fine and Coarse-Grain Reconfigurable Computing, Springer)

Arquiteturas reconfiguráveis podem ser de grão fino ou grosso. Arquiteturas de grão grosso (CGRAs) são menos flexíveis que as de grão fino, porém mais fáceis de programar e possuem reconfiguração mais rápida.

### **OBJETIVO**

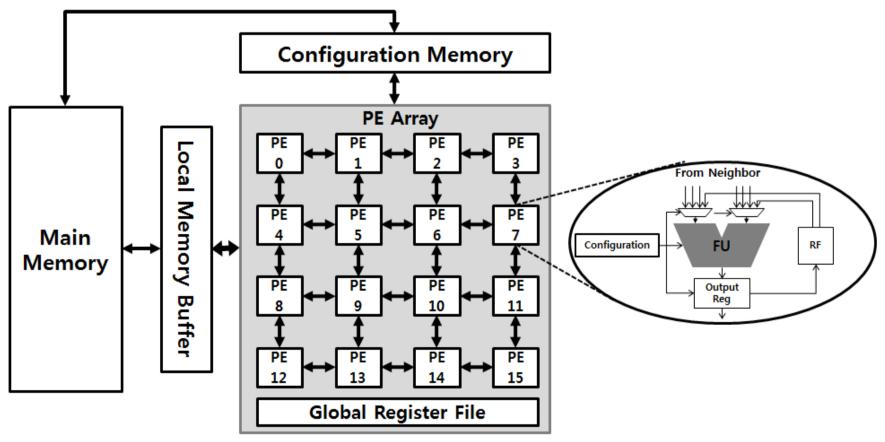

A estrutura usual de um CGRA possui um banco de registradores e pode possuir ligações diretas entre elementos de processamento (PEs) vizinhos, para a troca mais rápida de informação. O banco de registradores, no entanto, acaba exigindo um grande número de portas para leitura e escrita, uma vez que se tem vários PEs. Isso faz com que ocupe um espaço grande e torne-se caro. Além disso, o multiplexador em sua entrada, que determina que registrador se está lendo ou escrevendo, gera um atraso alto, transformando-o no gargalo da arquitetura.

(Fonte: http://cccp.eecs.umich.edu/research/cgra.php)

O objetivo do trabalho é propor uma solução alternativa que ocupe menos área e seja mais eficiente, reduzindo o tempo de processamento.

# **METODOLOGIA**

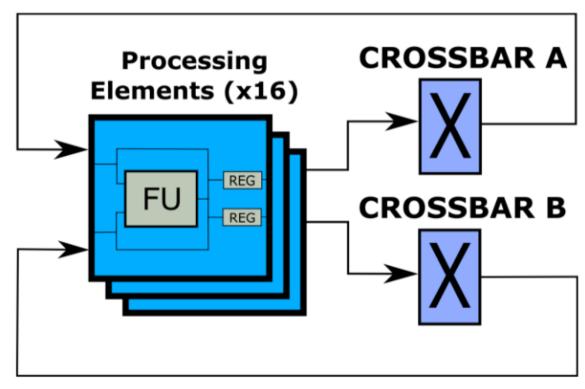

A solução proposta é uma arquitetura sem banco de registradores (Register File Free – Refree).

O Refree é uma arquitetura *Very Long Instruction Word* (VLIW), com 16 PEs, o que implica em potenciais 16 instruções executadas por ciclo de relógio. Entretanto, esse paralelismo depende essencialmente de um bom compilador, que é o responsável por identificar as instruções que podem ser executadas simultaneamente.

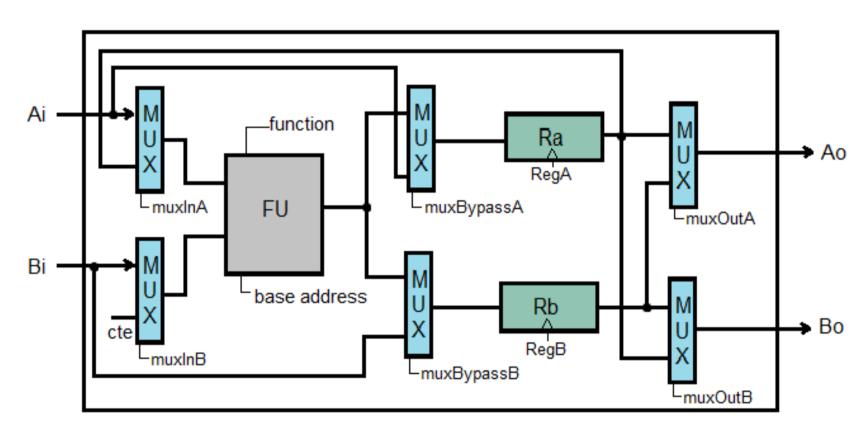

Estrutura interna de cada PE.

Em vez de um banco de registradores, cada PE possui dois registradores livres e é conectada a duas redes *crossbar*. Essas redes farão a conexão entre os PEs, realizando a troca de dados de uma forma mais rápida e eficiente.

(Fonte: Lume - Repositório Digital da UFRGS)

Uma implementação incompleta dessa arquitetura já existia, necessitando de ajustes e finalização. Instruções que faltavam foram implementadas e as modificações requeridas, realizadas para concluir essa etapa.

## **CONCLUSÃO**

Modificações efetuadas:

- > Instruções de controle de fluxo adicionadas

- GOTO e BRANCH

- > Tamanho da instrução alterado

- Novos bits de configuração

- Constante para branch

- Estrutura da PE alterada

# Trabalhos futuros:

Realizar testes para comprovar o funcionamento do código e análise de desempenho e área, em comparação com a arquitetura MIPS

# REFERÊNCIAS

- JOST, Tiago T. RefreeMIPS: A CGRA-based MIPS architecture. 2014. 51p. Trabalho de Conclusão de Curso. UFRGS, Porto Alegre.

- TODMAN, T. J., et al. Reconfigurable computing: architectures and design methods. IEE Proceedings: Computers and digital techniques. Vol. 152, No. 2, p. 193-207, March, 2005.

- SUTTER, B.; RAGHAVAM, P., LAMBRECHTS, A.; Coarse-Grained Reconfigurable Array Architectures. In: \_\_\_\_\_. Handbook of Signal Processing Systems. Boston: Springer US, 2010. p. 449-484.