# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

#### ESCOLA DE ENGENHARIA

Curso de Pós-Graduação em Engenharia Elétrica - CPGEE

# TESTE DE SISTEMAS INTEGRADOS UTILIZANDO CONTROLADORES ESPECÍFICOS

LEANDRO JOSÉ CASSOL

Dissertação para obtenção do título de Mestre em Engenharia

Porto Alegre

2002

#### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

#### ESCOLA DE ENGENHARIA

Curso de Pós-Graduação em Engenharia Elétrica - CPGEE

# TESTES DE SISTEMAS INTEGRADOS UTILIZANDO CONTROLADORES ESPECÍFICOS

LEANDRO JOSÉ CASSOL

Engenheiro Eletricista

Dissertação apresentada ao Curso de Pós-Graduação em Engenharia Elétrica - CPGEE, como parte dos requisitos para a obtenção do título de Mestre em Engenharia. Área de concentração: Instrumentação Eletro-Eletrônica. Desenvolvida no Laboratório de Prototipação e Testes do Departamento de Engenharia Elétrica da Universidade Federal do Rio Grande do Sul.

Porto Alegre 2002

# TESTE DE SISTEMAS INTEGRADOS UTILIZANDO CONTROLADORES ESPECÍFICOS

## LEANDRO JOSÉ CASSOL

Esta dissertação foi julgada adequada para a obtenção do título de Mestre em Engenharia e aprovada em sua forma final pelo Orientador e pela Banca Examinadora.

Orientador:

Prof. Marcelo Soares Lubaszewski, UFRGS

Dr. pelo Institut National Polytechnique de Grenoble

Banca Examinadora:

Prof. Marius Strum, USP

Dr. pela Universidade de São Paulo – USP – 1983

Prof. Luigi Carro, UFRGS

Dr. pela Universidade Federal do Rio Grande do Sul – UFRGS – 1996

Prof. Renato Perez Ribas, UFRGS

Dr. pelo Institut National Polytechnique de Grenoble - INPG - 1998

Coordenador do CPGEE:

Prof. Dr. Carlos Eduardo Pereira

Porto Alegre, março de 2002.

A minha familia, em especial a minha mãe Maria Helena, minhas irmãs Nabel e Rosângela e minha filha Rafaela pelo apoio, carinho, incentivo e amor.

## **AGRADECIMENTOS**

É uma tarefa que me agrada e que, no entanto, considero ingrata por ter que agradecer em um curto espaço de tempo a tantas pessoas que de uma maneira ou outra me ajudaram em um percurso longo de êxitos, alguns fracassos e muito trabalho.

Começo por agradecer à CAPES pela provisão da bolsa de mestrado, ao DELET pelas condições de trabalho e a todos os Professores do Curso de Pós-Graduação em Engenharia Elétrica – CPGEE que se dispuseram a passar um pouco dos seus conhecimentos. Em especial ao Professor Dr. Marcelo Lubaszewski a quem desejo expressar a minha profunda gratidão pela paciência, orientação e motivação destes anos. De igual modo agradeço ao Professor Dr. Luigi Carro e a Érika Cota, pela disponibilidade e ajuda.

Aos Professores que fazem parte da banca examinadora por terem aceito o convite e por último desejo manifestar meus agradecimentos a todos os meus colegas pelo ótimo convívio, amizade e ajuda, em especial aos amigos Fabiano Toson, Erik Schüler, Osvaldo Betat, Adriane Parraga, Maria da Glória Flores (Dodóia), Rafael Zeilmann e Ronaldo Husemann.

# **SUMÁRIO**

| LIST  | TA DE FIGURAS                                                           | viii |

|-------|-------------------------------------------------------------------------|------|

| LIST  | TA DE TABELAS                                                           | X    |

| LIST  | TA DE ABREVIATURAS E SÍMBOLOS                                           | xi   |

| RES   | UMO                                                                     | xii  |

| ABS   | TRACT                                                                   | xiii |

| 1     | INTRODUÇÃO                                                              | 1    |

| 1.1   | Motivação                                                               | 1    |

| 1.2   | OBJETIVOS DO TRABALHO                                                   | 3    |

| 1.3   | Organização da Dissertação                                              | 4    |

| 2     | TESTES EM CIRCUITOS INTEGRADOS                                          | 5    |

| 2.1   | SISTEMAS INTEGRADOS EM UM ÚNICO CHIP                                    | 5    |

| 2.2   | Núcleos de Hardware                                                     | 6    |

| 2.3   | Exigências do Teste em Sistemas Integrados                              | 8    |

| 2.4   | ARQUITETURA DE TESTE CONCEITUAL                                         | 11   |

| 2.5   | MECANISMO DE ACESSO AO TESTE                                            | 12   |

| 2.6   | PADRÃO IEEE P1500                                                       | 13   |

| 2.6.1 | Linguagem de Descrição do Teste de Núcleos de Hardware                  | 14   |

| 2.6.2 | Arquitetura Escalonável                                                 | 15   |

| 2.7   | PADRÃO IEEE STD. 1149.1 (BOUNDARY-SCAN)                                 | 18   |

| 3     | CONTROLADORES DE TESTE                                                  | 21   |

| 3.1   | Custos e Precisão de Equipamentos Automáticos Externos<br>Teste (ATEs). |      |

| 3.2   | CONTROLADORES INTERNOS                                                  | 24   |

| 3.2.1 | Microprocessadores Reutilizados para Produzir Controladores de Teste    | 24   |

| 3.2.2 | Microprocessadores Dedicados ao Controle de Teste                       | 32   |

| 4     | O CONTROLADOR DE TESTE MET                                              | 37   |

| 4.1   | LINGUAGEM STIL                                                          | 38   |

| 4.2   | PROPOSTA DA ARQUITETURA MET                                           | 40  |

|-------|-----------------------------------------------------------------------|-----|

| 4.2.1 | Instruções do Microcontrolador                                        | 40  |

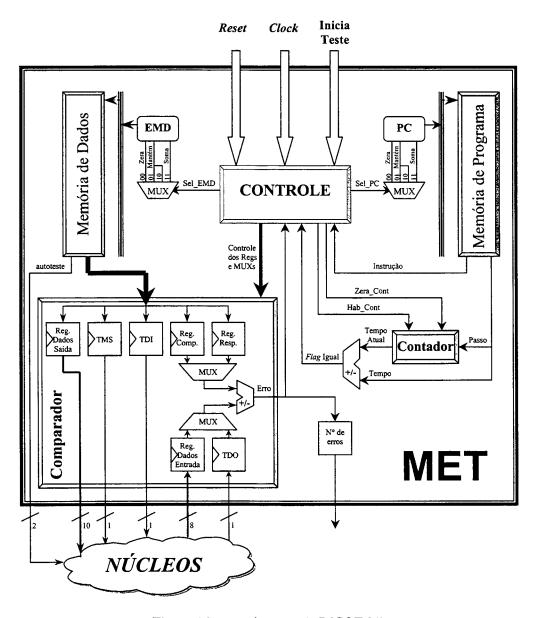

| 4.3   | COMPONENTES PRINCIPAIS DA ARQUITETURA MET                             | 43  |

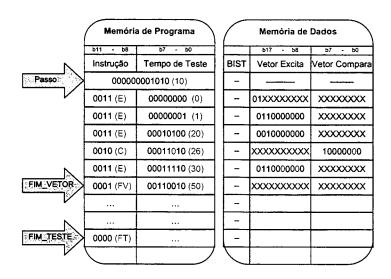

| 4.3.1 | Memória de Programa                                                   | 44  |

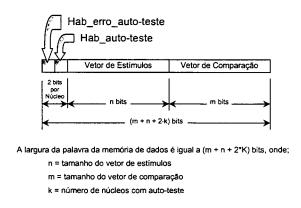

| 4.3.2 | Memória de Dados                                                      | 45  |

| 4.3.3 | Contador de Eventos                                                   | 46  |

| 4.3.4 | Comparador                                                            | 47  |

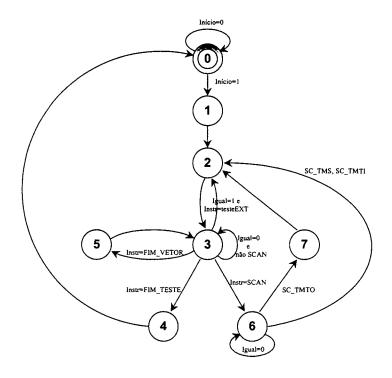

| 4.3.5 | Controle                                                              | 47  |

| 4.4   | Execução do Teste                                                     | 49  |

| 4.5   | Exemplo de Programa de Teste <i>Scan</i> para um Núcleo Basea em JTAG |     |

| 4.6   | RESULTADOS ENTRE SÍNTESES                                             | 52  |

| 5     | ESTUDO DE CASOS                                                       | 54  |

| 5.1   | CONTROLANDO TESTE EXTERNO                                             | 55  |

| 5.2   | CONTROLANDO TESTE SCAN                                                | 58  |

| 5.3   | CONTROLE DO TESTE COM VETORES COMPACTADOS                             | 65  |

| 5.3.1 | Codificação Golomb e Compactação                                      | 66  |

| 5.3.2 | Descompactação                                                        | 68  |

| 5.4   | TESTE SCAN PARALELO DE NÚCLEOS.                                       | 74  |

| 5.5   | IMPACTO DO TAMANHO DA MEMÓRIA NO TESTE                                | 75  |

| 5.6   | CONTROLANDO TESTE BIST NO 8051                                        | 82  |

| 5.7   | WRAPPERS PARAMETRIZADOS                                               | 87  |

| 5.8   | OPERAÇÕES DE SALTOS NOS ENDEREÇADORES DAS MEMÓRIAS                    | 90  |

| 6     | CONCLUSÕES                                                            | 92  |

| REF   | ERÊNCIAS BIBLIOGRÁFICAS                                               |     |

| ANE   | XOS                                                                   | 100 |

# LISTA DE FIGURAS

| Figura 2.1 - Sistema integrado que utiliza hierarquia de blocos funcionais e Lógica Definida pelo Usuário (LDU) [ZOR 97] | Q        |

|--------------------------------------------------------------------------------------------------------------------------|----------|

| Figura 2.2 - Comparação entre os testes de uma placa e de um sistema integrado [ZOR 97]                                  |          |

| Figura 2.3 - Arquitetura conceitual para o teste de sistemas integrados [ZOR 98]                                         | _        |

| Figura 2.4 - Sistema integrado com núcleos utilizando o padrão P1500 [ADH 99]                                            |          |

| Figura 2.5 - Arquitetura conceitual do wrapper segundo IEEE P1500 [MAR 00b]                                              |          |

| Figura 2.6 - Arquitetura IEEE std. 1149.1                                                                                |          |

| Figura 2.7 - Diagrama de estados do controlador de TAP.                                                                  | 19<br>20 |

| Figura 3.1 - Esquema de teste proposto em [PAP 99]                                                                       |          |

| Figura 3.2 - Diagrama de blocos da transferência de dados de teste do testador para o <i>chip</i> .                      |          |

| Figura 3.3 - Palavra de substituição.                                                                                    |          |

| Figura 3.4 - Diagrama de blocos da arquitetura de teste proposto por [JAS 99]                                            |          |

| Figura 3.5 - Arquitetura BIST utilizando controlador interno [DRE 98]                                                    |          |

| Figura 3.6 - Diagrama de blocos do sequenciador.                                                                         |          |

| Figura 3.7 - Exemplo de estrutura de teste em forma de anel.                                                             |          |

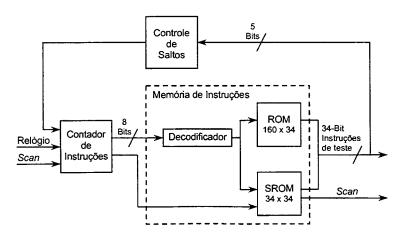

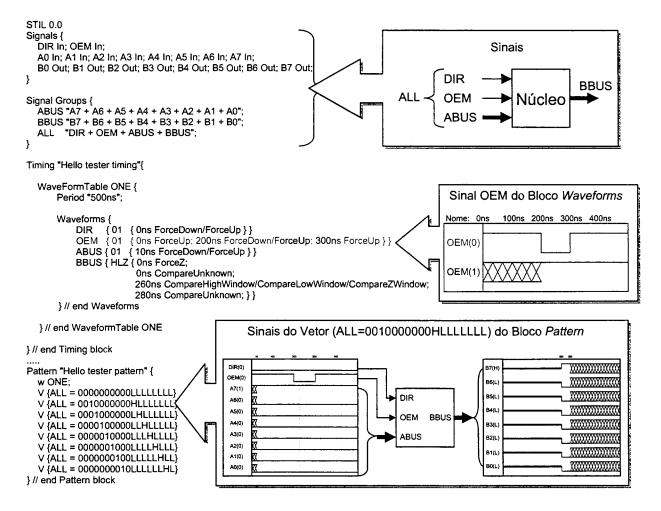

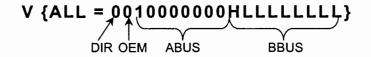

| Figura 4.1 - Exemplo de programa STIL.                                                                                   |          |

| Figura 4.2 - Segundo vetor do bloco <i>Pattern</i> .                                                                     |          |

| Figura 4.3 - Arquitetura MET [COT 01].                                                                                   |          |

| Figura 4.4 - Palavra da memória de dados.                                                                                |          |

| Figura 4.5 - Memória de programa e de dados para o exemplo de código STIL                                                |          |

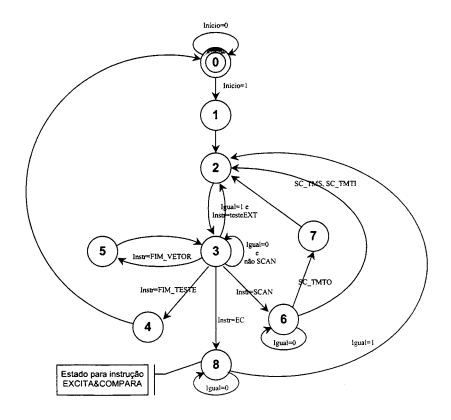

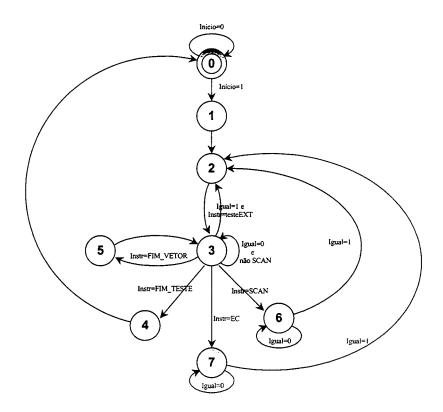

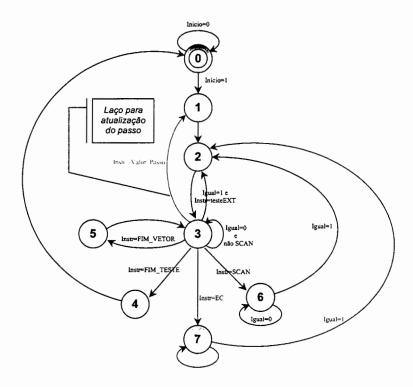

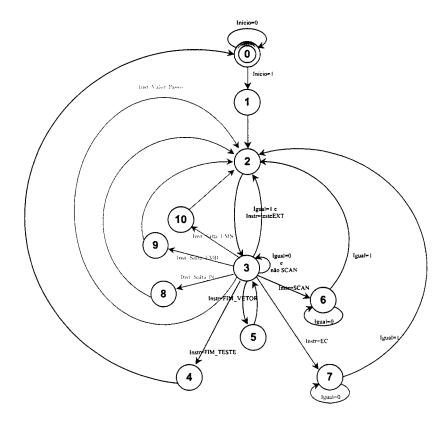

| Figura 4.6 - Diagrama de estados do bloco de controle do MET                                                             |          |

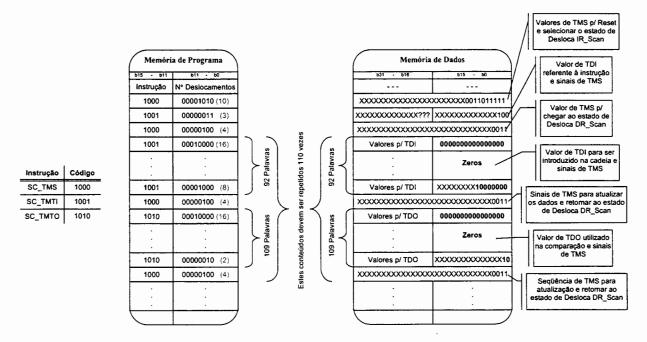

| Figura 4.7 - Memória de programa e de dados com valores para um teste scan                                               |          |

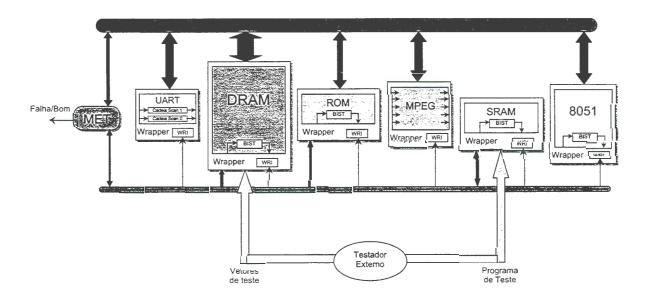

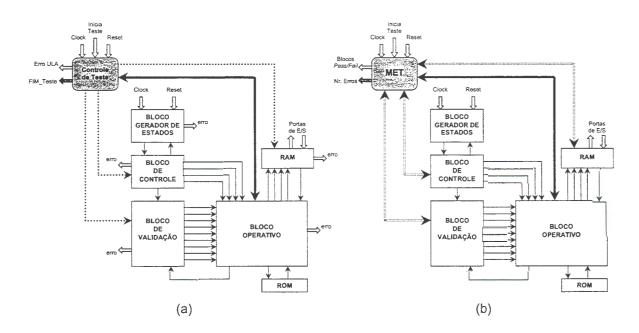

| Figura 5.1 - Sistema com controle de teste interno.                                                                      |          |

| Figura 5.2 - Diagrama de estados do bloco de controle com instrução at-speed                                             |          |

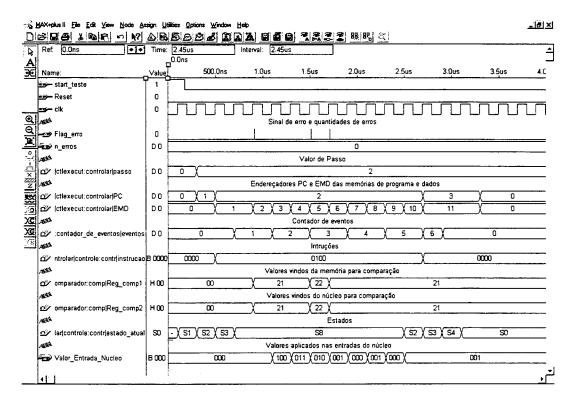

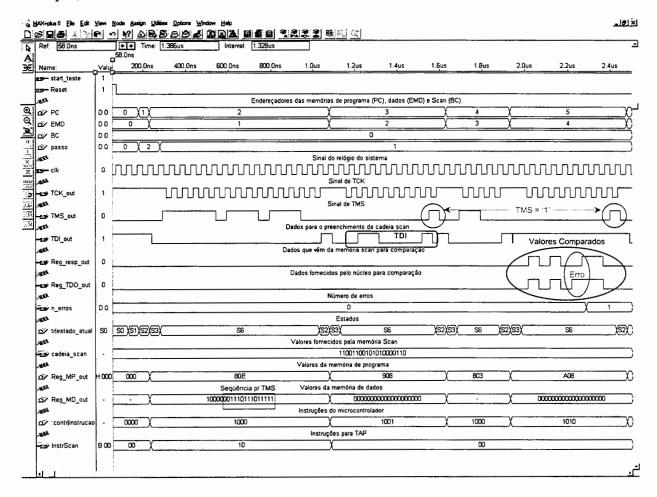

| Figura 5.3 - Simulação para um teste externo at-speed                                                                    |          |

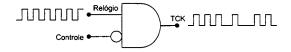

| Figura 5.4 - Esquema utilizado para geração do sinal de TCK.                                                             |          |

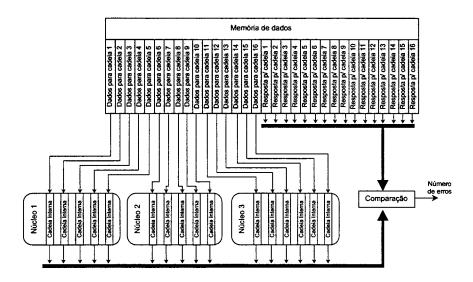

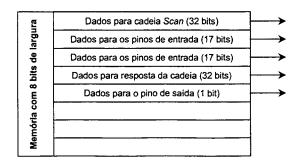

| Figura 5.5 - Organização dos dados de teste scan nas memórias do MET                                                     | 60       |

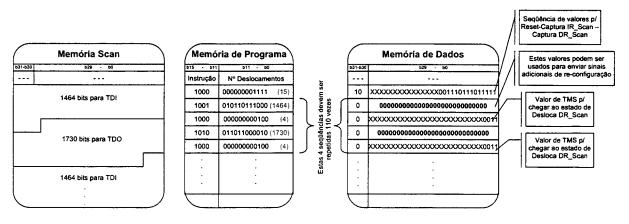

| Figura 5.6 - Organização dos dados para um teste scan utilizando três memórias                                           |          |

| Figura 5.7 - Diagrama de estado                                                                                          |          |

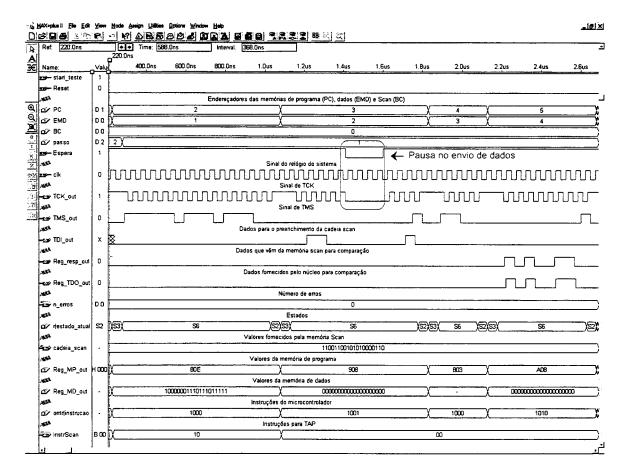

| Figura 5.8 - Simulação de um teste scan utilizando 3 memórias.                                                           | 65       |

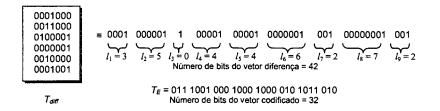

| Figura 5.9 - $T_{diff}$ e o vetor codificado $T_E$                                                                       | 68       |

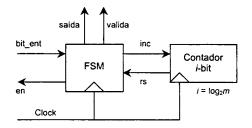

| Figura 5.10 - Diagrama em blocos do decodificador usado para descompactação                                              |          |

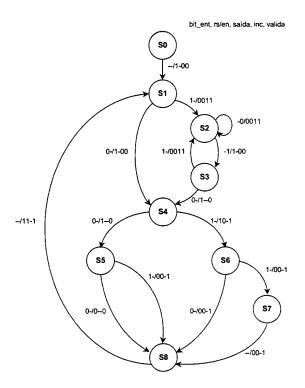

| Figura 5.11 - Diagrama de estados de um decodificador Golomb com $m = 4$                                                 | 69       |

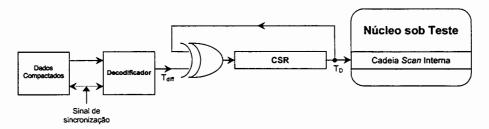

| Figura 5.12 - Arquitetura de descompactação baseada em CSR                                                               |          |

| Figura 5.13 - Arquitetura de descompactação baseada no uso de cadeia scan                                                |          |

| Figura 5.14 - Simulação com sinal de espera no processo de teste                                                         |          |

| Figura 5.15 - Arquitetura para o teste de vários núcleos a partir de uma memória Scan con                                |          |

| vetores compactados.                                                                                                     | 73       |

| Figura 5.16 - Carga paralela de várias cadeias com o uso de um módulo de memória                                         |          |

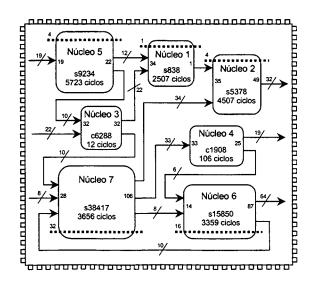

| Figura 5.17 - Sistema utilizado como exemplo.                                                                            |          |

| Figura 5.18 - Organização dos dados na memória para o teste do circuito s838                                             |          |

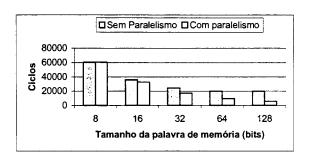

| Figura 5.19 - Variação do tempo de teste em função da largura de palayra da memória                                      | 79       |

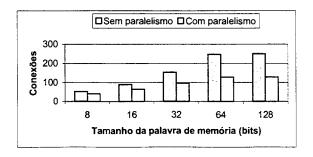

| Figura 5.20 - Variação na quantidade de conexões em função da largura da memória       | . 79 |

|----------------------------------------------------------------------------------------|------|

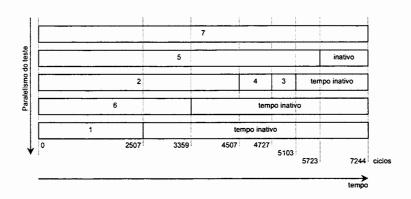

| Figura 5.21 - Planejamento de tempo de teste atendendo restrições de projeto           | . 82 |

| Figura 5.22 - (a) diagrama em blocos da descrição BIST 8051. (b) diagrama em blocos da |      |

| descrição BIST 8051 com o controlador MET.                                             | . 83 |

| Figura 5.23 - Diagrama de estados do bloco de controle com passo variável              | . 87 |

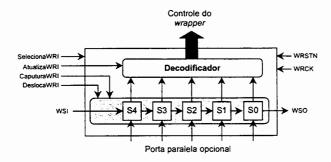

| Figura 5.24 - Arquitetura do registrador de instruções do wrapper.                     | . 88 |

| Figura 5.25 - Formato das instruções de salto.                                         | . 90 |

| Figura 5.26 - Diagrama de estados do bloco de controle com instruções de saltos        |      |

# LISTA DE TABELAS

| Tabela 2.1 - Exemplos de núcleos de hardware classificados por funcionalidade [GUP97]   | 7    |

|-----------------------------------------------------------------------------------------|------|

| Tabela 3.1 - Parâmetros para o cálculo de custos de ATEs                                | . 23 |

| Tabela 3.2 - Rendimento versus precisão do testador.                                    | . 23 |

| Tabela 4.1 - Codificação das instruções.                                                | . 42 |

| Tabela 4.2 - Primeira sequência de definição dos sinais.                                | . 50 |

| Tabela 4.3 - Segunda sequência de definição dos sinais.                                 | .51  |

| Tabela 4.4 - Comparativo de performance e área entre circuitos                          | . 52 |

| Tabela 5.1 - Dados sobre os circuitos benchmarks s298 e s344                            | . 56 |

| Tabela 5.2 - Comparativo da quantidade de bits de memória para teste scan               | .63  |

| Tabela 5.3 - Exemplo de codificação Golomb para m = 4.                                  | . 67 |

| Tabela 5.4 - Comparação entre frequência interna e frequência externa para              |      |

| descompactação Golomb.                                                                  | .73  |

| Tabela 5.5 - Dados referentes ao processo de teste dos benchmarks do sistema exemplo da |      |

| figura 5.16                                                                             | . 76 |

| Tabela 5.6 - Ciclos e hardware extra para uma conexão exclusiva com um ATE              | .77  |

| Tabela 5.7 - Tempo de teste para cada bloco do microcontrolador 8051                    | . 85 |

| Tabela 5.8 - Codificação das instruções.                                                | . 86 |

| Tabela 5.9 - Comparação entre modelos de configurações de wrappers [LAZ 02]             | . 89 |

| Tabela 5.10 - Comparativo entre diversas implementações do MET                          | .91  |

|                                                                                         |      |

## LISTA DE ABREVIATURAS E SÍMBOLOS

ASIC Application Specific Integrated Circuit

ATE Automatic Test Equipment

BIST Built-In Self-Test

CI Circuito Integrado

CPU Central Processing Unit

CTL Core Test Language

DFT Design for Testability

DMA Direct Memory Access

DRAM Dynamic Random Access Memory

DSP Digital Signal Processing

FPGA Field Programmable Gate Array

FSM Finite State Machine

IEEE Institute of Electrical and Electronic Engineers

JTAG Joint Test Action Group

LDU Lógica Definida pelo usuário

LFSR Linear Feedback Shift Register

MET Microprocessor for Embedded Test

MISR Multiple Input Shift Register

MPEG Motion Pictures Experts Group

PCB Printed Circuit Board

RAM Random Access Memory

RISC Reduced Instruction Set Computer

ROM Ready Only Memory

SOC System on Chip

SRAM Static Random Access Memory

TAP Test Access Port

TDI Test Data Input

TDO Test Data Output

TMS Test Mode Select

UART Universal Asynchronous Receiver/Transmitter

ULA Unidade Lógica e Aritmética

VHDL Very high speed integrated circuits (VHSIC) Hardware Description

Language

VSI Virtual Socket Interface

WRI Wrapper Register Instruction

## **RESUMO**

O presente trabalho tem como objetivo a avaliação do controle interno do teste em sistemas baseados em núcleos de hardware. No intuito de analisar os problemas e as exigências do teste em SOCs, alguns sistemas são aqui criados utilizando-se a descrição VHDL de um controlador de teste, alguns circuitos *benchmarks* e uma descrição de um microcontrolador 8051 auto-testável. Problemas referentes ao controle de diferentes estratégias de teste (externo, scan, BIST, etc) são abordados e formas de resolver estes problemas são descritas. Também abordam-se problemas referentes ao teste em nível de sistema, como por exemplo, requisitos de memória e conexões. Mudanças são sugeridas e implementadas no controlador de teste, a fim de melhorar seu desempenho e flexibilizar seu uso em diversas circunstâncias distintas em termos de requisitos de estratégias de teste.

## **ABSTRACT**

This work aims at evaluating the internal test control in core-based systems. In order to analyze problems and requirements of testing core-based systems, some systems are herein built making use of a VHDL description of a test controller, of some benchmark circuits and of a description of a self-testing 8051 microcontroller. Problems related to controlling different test strategies (external testing, scan, BIST, etc) are covered and ways of solving those problems are described. Problems related to the system level testing, such as memory and connection requirements, are also discussed. Changes are proposed and implemented into the test controller, in order to enhance its performance and make its use more flexible to face many different situations in terms of required test strategies.

# 1 INTRODUÇÃO

#### 1.1 MOTIVAÇÃO

O uso de sistemas eletrônicos tornou-se imprescindível para a sustentação e evolução da sociedade moderna. A contínua busca pela modernização tem levado ao desenvolvimento de sistemas que se tornam cada dia menores e mais complexos. A competitividade entre os fabricantes de semicondutores, a necessidade tecnológica de alta velocidade, a diversidade de aplicações e o anseio da sociedade por novos produtos tem conduzido os fabricantes a buscarem formas alternativas de diminuir o tempo entre o projeto e a disponibilização dos seus produtos para os consumidores.

Os avanços em termos de aumento da capacidade de integração de *chips* levaram os fabricantes de circuitos integrados a solucionar parte de seus problemas através do reuso de módulos previamente projetados. Nos dias de hoje, diferentes tipos de módulos podem ser agrupados para juntos formarem um sistema completo em um único chip. Estes sistemas são chamados de SOCs (do inglês, *System-on-Chip*) e os módulos que os compõem recebem o nome de núcleos de hardware. Estes núcleos não são vendidos como ASICs manufaturados em uma pastilha de silício, mas sim, como uma descrição lógica sintetizável. A existência destes componentes permite ao projetista desenvolver um sistema complexo preocupando-se apenas com as questões de comunicação entre seus módulos, sem considerar detalhes de implementação de cada núcleo, assim, diminuindo consideravelmente o tempo de projeto do sistema.

Ao mesmo tempo em que os SOCs trouxeram um impressionante ganho na concepção de novos sistemas, também trouxeram um conjunto de novos problemas relativos ao teste. Este novo desafio inclui o teste de núcleos com diferentes funcionalidades, núcleos oriundos de diferentes fabricantes, restrições de acesso ao conteúdo dos núcleos por motivo de propriedade intelectual, acessibilidade limitada aos núcleos por intermédio das entradas e saídas primárias do sistema, controle do procedimento de teste de todo o sistema, etc.

Para resolver estes problemas são necessárias novas arquiteturas capazes de administrar o teste de mais de 100 milhões de transistores, ao mesmo tempo em que permitam atingir uma alta cobertura dos defeitos que podem se produzir no sistema. No intuito de facilitar a geração do teste, um grupo de trabalho IEEE está desenvolvendo um padrão chamado de P1500. Este grupo de trabalho tem enfocado seus esforços nos elementos que geram os estímulos e que comparam respostas de teste, no mecanismo que transporta os dados de teste entre fontes, núcleos e receptores, e principalmente na definição de uma lógica envoltória padrão para realizar o interfaceamento entre o núcleo e os mecanismos de teste. O padrão propõe, ainda, a definição de uma linguagem de descrição de teste para facilitar a comunicação entre os provedores dos núcleos de hardware e seus usuários.

Dois problemas importantes relativos ao teste de SOCs são: o acesso aos núcleos de hardware e a combinação da capacidade de teste e diagnóstico dos diferentes núcleos que integram o sistema. Além disso, as exigências de teste devem ser atendidas dada uma quantidade limitada de recursos (geradores de padrões, controladores de auto-teste, pinos extra no chip, área extra em silício, tempo de teste, etc). O uso dos tradicionais equipamentos automáticos de teste pode representar outra importante limitação, devido à largura dos mecanismos de acesso aos núcleos (TAM, do inglês, *Test Access Mechanism*) e da freqüência de relógio utilizada no teste. Normalmente, para TAMs com larguras grandes são utilizadas cadeias de varredura (*scan*), as quais limitam a velocidade e também impõem restrições adicionais quanto ao número de vetores de teste.

A solução clássica empregada para suprir a limitação dos recursos de teste é o reuso de hardware. Por exemplo, testar mais de um núcleo de hardware utilizando o mesmo gerador de padrões de teste, ou o mesmo barramento, são estratégias que foram propostas para reduzir área em silício. Controladores de teste também devem ser considerados por ocasião da definição da estratégia de teste do sistema. Normalmente, esta tarefa é executada por um ATE. Porém, o uso destes equipamentos pode encontrar algumas restrições para o controle de teste em SOCs.

A associação internacional de fabricantes de semicondutores Roadmap (ITRS) [ROA 01] prevê que o custo de testadores de alta velocidade vai exceder a casa dos 20 milhões de dólares em 2010. Outro dado importante que é fornecido por essa mesma associação é que a velocidade dos circuitos integrados possui um incremento de 30% ao ano, enquanto a precisão dos testadores tem aumentado a uma taxa de somente 12% ao ano [ROA

Introdução 3

01]. Por isso, modos alternativos que exigem menos dos testadores e mantenham a alta qualidade do teste devem ser buscados.

Alguns autores têm sugerido o uso de processadores e memórias disponíveis no próprio sistema para serem utilizados como testadores e elementos armazenadores de dados de teste. Em um ambiente SOC, esta é uma solução interessante, uma vez que, freqüentemente, estes circuitos possuem um ou mais processadores, além de núcleos de memória em abundância.

O uso de um processador dedicado para o teste é outra solução proposta para controladores integrados. Estes processadores podem ser muito eficientes em termos de área e desempenho, já que são dedicados e sintetizados com a mesma tecnologia do sistema sob teste. Assim, o controlador de teste é outro núcleo dentro do SOC e o reuso de hardware é conseguido através da utilização de memórias disponíveis no sistema para armazenar os padrões de teste.

Critérios para a tomada de decisão quanto ao uso ou não de controladores integrados ainda não foram objetivamente explorados na literatura. Alguns trabalhos sugerem a substituição quase total dos equipamentos externos de teste por um controlador interno. Outros trabalhos sugerem uma interação entre processadores internos e equipamentos externos de menor capacidade.

#### 1.2 OBJETIVOS DO TRABALHO

O objetivo deste trabalho é realizar um estudo sobre controladores de teste, mostrando sua complexidade e diferentes possibilidades de uso no contexto de sistemas construídos a partir de núcleos de hardware baseados em diferentes estratégias de teste (BIST, cadeias de varredura, etc). O enfoque principal é o uso de um controlador embutido e dedicado para o teste visando o padrão IEEE P1500.

A avaliação das diferentes estratégias de testes é realizada através da implementação na linguagem de descrição de hardware VHDL do controlador de teste descrito em [COT 01]. Mudanças são propostas e implementadas, sempre que possível, no intuito de melhorar o desempenho do controlador. Os resultados de síntese, simulação e exemplos de teste são apresentados e avaliados neste trabalho.

## 1.3 ORGANIZAÇÃO DA DISSERTAÇÃO

No próximo capítulo, busca-se fazer uma breve discussão sobre técnicas de teste voltadas para sistemas integrados em um único *chip*. Neste capítulo são apresentadas algumas definições sobre SOCs, definição e tipos de núcleos de hardware, sistemática de teste. A proposta de padrão IEEE P1500, para o teste de SOCs, e o norma IEEE std. 1149.1, conhecida como *boundary-scan*, também são enfocados neste capítulo. No capítulo 3 apresenta-se alguns dados sobre custo de equipamentos externos de teste, e busca-se fazer uma revisão dos principais trabalhos que apresentam controladores internos como sistemas gerenciadores de teste. A arquitetura de um controlador específico para o teste é apresentada no capítulo 4. Estudos de alguns tipos de teste e sugestões para a melhoria de desempenho do controlador de teste são apresentados no capítulo 5. Finalmente o capítulo 6 aborda as principais conclusões que puderam ser retiradas do trabalho realizado e apresenta perspectivas futuras de desenvolvimento.

#### 2 TESTES EM CIRCUITOS INTEGRADOS

## 2.1 SISTEMAS INTEGRADOS EM UM ÚNICO CHIP

Com o avanço nos métodos de projeto e manufatura de circuitos integrados (CIs), sistemas, que anteriormente eram construídos sobre placas de circuito impresso e que continham múltiplos CIs, agora podem ser integrados em um único substrato. Estes sistemas são chamados de SOCs (do inglês, *System-on-Chip*) e são formados por uma grande diversidade de sub-circuitos, chamados núcleos de hardware ou, do inglês, *cores*. Cada um destes sub-circuitos pode ser visto como um componente distinto, com projeto e verificação lógica independentes, mas que são passíveis de serem utilizados em conjunto com outros núcleos, formando assim, um circuito maior e mais complexo chamado de sistema integrado ou, do inglês, *core-based system*. A diferença entre um SOC e um sistema montado sobre uma placa de circuito impresso (PCB, do inglês, *Printed Circuit Board*), é que no primeiro todos os núcleos e a lógica responsável pela união entre os núcleos foram sintetizados em um único substrato, recebendo, ao final, um único encapsulamento. Em uma PCB, cada um dos núcleos é um circuito integrado distinto que foi produzido e encapsulado separadamente, mas montado sobre uma placa discreta que contém a lógica de comunicação entre os circuitos.

Sistemas integrados são tipicamente heterogêneos, uma vez que eles contêm tecnologias mistas, como circuitos digitais, memórias e circuitos analógicos [RAJ 97]. Tipicamente, núcleos de hardware apresentam funções que incluem CPUs e DSPs, interfaces seriais,

módulos para interconexão padrão como PCI, USB e IEEE 1394, funções de computação gráfica como MPEG e JPEG, e memórias [MAR 99]. Os sistemas embarcados, que são caracterizados pela diversidade de funções, e os sistemas de maior complexidade e/ou que possuem

um tempo de projeto restrito são as aplicações típicas dos SOCs.

Estes sistemas, por estarem integrados em um único substrato e por serem fabricados utilizando uma mesma tecnologia oferecem vantagens como: alto desempenho, baixo consumo de potência, menor tempo de projeto e grande volume de produção, quando comparados com sistemas tradicionais formados por múltiplos *chips* [MAR 99].

#### 2.2 NÚCLEOS DE HARDWARE

Um núcleo de hardware é um bloco funcional pré-verificado e pré-projetado, contendo pelo menos 5000 portas lógicas [ZOR 97], que pode ser utilizado na construção de sistemas maiores e mais complexos. A denominação original é, do inglês, *core*. Os núcleos de hardware também são chamados de componentes virtuais ou bibliotecas de hardware e são classificados como: *soft, firm* ou *hard* [ZOR 97].

- Um soft core é um código RTL sintetizável ou uma netlist genérica de parte de uma lógica.

- 2. Um firm core é também um código RTL sintetizável ou uma netlist genérica, porém, possui a sua estrutura e/ou topologia otimizadas para desempenho ou área. Um firm core não vem roteado e pode ser otimizado durante o posicionamento com o resto do sistema. Algumas vezes, está otimização ocorre durante o mapeamento para algumas tecnologias.

- 3. Um hard core existe em forma de leiaute implementado para uma determinada tecnologia. Ele é otimizado para um ou mais parâmetros chave, tais como velocidade, área ou potência. Um hard core está disponível como uma netlist com posicionamento e roteamento definidos ou como um arquivo de leiaute físico (em geral em formato GDSII) ou ainda como uma combinação dos dois.

Os três tipos de núcleos de hardware oferecem vantagens e desvantagens. Soft cores deixam uma boa parte da implementação para o projetista do sistema, mas são flexíveis e independentes do processo de fabricação. Hard cores são otimizados para um desempenho desejado, porém não apresentam maiores flexibilidades de projeto. Firm cores oferecem um compromisso entre os dois, sendo mais flexíveis que hard cores e menos genéricos que os soft cores.

Estes componentes são frequentemente produtos de tecnologias, software e *know-how* sujeitos a patentes e direitos autorais. Em outras palavras, um núcleo de hardware representa uma propriedade intelectual que o projetista do núcleo concede ao usuário deste bloco,

que é o projetista do sistema final. Por isso, questões como proteção da propriedade intelectual devem ser consideradas nas ações que utilizam esta nova tecnologia.

O número de blocos funcionais disponíveis como bibliotecas de hardware tem crescido continuamente. A Tabela 2.1 mostra alguns exemplos destes blocos existentes no mercado.

Tabela 2.1 - Exemplos de núcleos de hardware classificados por funcionalidade [GUP97].

| Categoria      | Exemplos de produtos           |

|----------------|--------------------------------|

| Processadores: |                                |

| RISC           | LSI Logic CW4K, ARM 7TDMI, PPC |

| CISC           | 680x0, x86                     |

|                | my my reason of the pion of    |

DSP TI TMS320C54X, DSP Group Pine BIST MenBIST-IC, PLL BIST, ADC BIST PkuP, DES Criptografia Controladores USB, PCI, UART Multimídia Compressão JPEG; Decodificados MPEG, DAC Redes ATM SAR, Ethernet Memórias Memórias especializadas; alta velocidade, de baixa potência

A diversidade de funcionalidade das bibliotecas virtuais tem aumentado com o surgimento de empresas de projeto especializadas e, a medida em que aumenta a disponibilidade destes componentes, as vantagens de sua aplicação se tornam mais evidentes. Novas tecnologias são incorporadas nos mais diversos produtos e o tempo entre projeto e produto final fica cada vez menor devido à possibilidade de reuso. Entretanto, existem ainda diversas questões não resolvidas neste meio [GUP 97]: métodos de projeto para construção de sistemas em um único circuito integrado, problemas na verificação e teste dos novos sistemas complexos, além das questões de licenciamento e proteção da propriedade intelectual dos blocos funcionais.

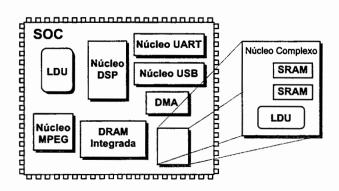

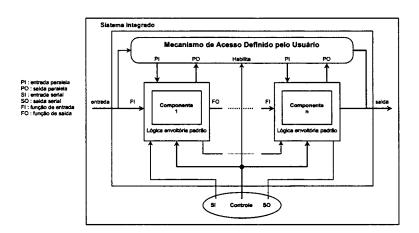

A Figura 2.1 apresenta um exemplo genérico de um sistema integrado que utiliza diversos núcleos de hardware, alguns deles hierárquicos. O sistema contém, ainda, uma Lógica Definida pelo Usuário (LDU) que acrescenta determinada funcionalidade ao conjunto. Esta lógica é definida pelo projetista responsável pela integração dos diversos componentes em um sistema maior.

Figura 2.1 - Sistema integrado que utiliza hierarquia de blocos funcionais e Lógica Definida pelo Usuário (LDU) [ZOR 97].

#### 2.3 EXIGÊNCIAS DO TESTE EM SISTEMAS INTEGRADOS

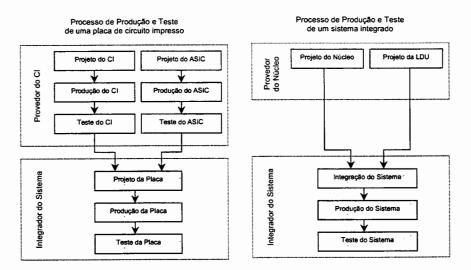

Sistemas integrados em um único chip e sistemas montados sobre placas de circuito impresso são conceitualmente análogos. Porém, as dificuldades de teste relacionadas com sistemas baseados em núcleos de hardware são bastante diferentes daquela relacionada ao teste de ASICs ou dos tradicionais circuitos integrados montados sobre placas. No caso convencional, a fabricação e o teste do circuito integrado ocorre antes da montagem da placa. Um projeto baseado em núcleos de hardware, por outro lado, tem apenas uma etapa de fabricação e teste de todo o sistema [GUP 97]. Neste caso, blocos individuais e sua lógica periférica definida pelo usuário são, primeiro, totalmente projetados e após integrados ao sistema. Somente após a etapa de integração, os passos de produção e teste do sistema final são executados.

Outra diferença importante entre as abordagens de teste para sistemas tradicionais e para sistemas baseados em bibliotecas de hardware é a questão do acesso à periferia do componente [ZOR 98], isto é, o acesso às entradas e saídas primárias dos blocos préprojetados. Para sistemas montados em uma placa, o acesso físico direto à periferia (pinos) do circuito integrado está tipicamente disponível para ser utilizado durante o teste de produção. Já para os núcleos de hardware, que estão, em geral, profundamente embutidos em um sistema integrado (uma vez que todo o sistema está contido em um único substrato), o acesso direto às suas periferias não está disponível originalmente. Assim, um mecanismo de acesso eletrônico é necessário. Este mecanismo necessita de uma lógica adicional em torno do bloco que pode conter, por exemplo, uma parte que permita o chaveamento entre modos de operação (normal e teste), outra que faz a ligação do bloco com o gerador e o receptor de dados de teste e uma terceira que permite o isolamento deste bloco em relação ao resto do sistema [ZOR 97].

Um dos maiores desafios relacionados à produção dos sistemas integrados é a união e coordenação das capacidades de teste e diagnóstico de todas as partes em um circuito integrado [ZOR 97]. Comparado a um sistema montado em uma placa, os requisitos de teste do sistema integrado são muitos complexos. O teste da placa consiste, simplesmente, no teste das conexões entre circuitos integrados e dos pinos de acesso, pois supõe-se que cada CI tenha sido previamente testado e esteja livre de falhas. O teste de um sistema integrado, por outro lado, é um único teste composto, que envolve a verificação dos núcleos de hardware e do sistema como um todo de forma integrada. A figura 2.2 mostra as diferenças entre estes dois tipos de teste [ZOR 97]. O teste de um sistema integrado é, na verdade, o teste individual de cada núcleo de hardware, o teste da lógica definida pelo usuário (LDU) e o teste de suas conexões. O teste de cada núcleo e LDU, por sua vez, pode envolver componentes periféricos. Certas restrições periféricas (por exemplo, modo de segurança, modo de baixa potência, modo de passagem) são requisitos comuns. Estas restrições necessitam de modos de acesso e isolamento específicos.

Figura 2.2 - Comparação entre os testes de uma placa e de um sistema integrado [ZOR 97].

Um projetista de núcleos de hardware deve preparar um esquema de teste interno que seja adequadamente descrito, portável e passível de ser facilmente integrado e utilizável, de forma automática se possível, para interagir com o teste do restante do sistema.

Além de problemas de integração e interdependência, o teste composto de sistemas integrados requer um sequenciamento adequado das tarefas de teste. Este escalonamento é necessário para atender determinados requisitos do sistema, como tempo de teste, potência dissipada, acréscimo de área, entre outros. O escalonamento do teste é necessário, ainda, para

executar o teste interno dos núcleos e a comunicação entre eles, em uma ordem tal que não influencie a inicialização e o conteúdo final dos blocos funcionais individualmente.

Sabendo que o teste do sistema integrado é composto pelo teste dos núcleos e do sistema, pode-se classificar os requisitos de teste do sistema integrado em três níveis distintos:

- 1. No primeiro nível estão os requisitos para a verificação dos núcleos que compõem o sistema. As soluções devem ser geradas pelos provedores dos componentes virtuais. O teste interno deve ser pensado pelo projetista do núcleo e transmitido para o integrador de alguma forma (vetores, sinais de controle necessários, etc.). Como o nível de preparação para o teste interno de um núcleo varia de um caso para outro, o teste individual dos núcleos deve ser adequadamente descrito e transportado para o processo de integração do sistema. A alternativa para estas descrições é o uso de uma linguagem padrão de teste, como é o caso da linguagem STIL [SOC 99].

- 2. No segundo nível, composto basicamente pelas interconexões entre os diversos núcleos, há um único requisito a ser atendido, porém de extrema importância para o desempenho e qualidade do teste final do sistema. Este requisito é o acesso a cada núcleo no momento de teste. Um núcleo, por exemplo, pode ser acessível apenas através das entradas e saídas de outro(s) componente(s). Neste caso, a inserção de vetores de teste externos e a verificação das respostas de teste deste núcleo podem não ser possíveis. No caso do acesso disponível pela funcionalidade normal do sistema não ser suficiente, é necessária a implementação de novos meios de acesso para o teste. Uma vez que, em geral, é o integrador quem define esta camada, ele deve também decidir sobre a melhor implementação dos caminhos de teste.

- 3. No terceiro nível estão os requisitos para o sistema final, que também devem ser resolvidos pelo integrador do sistema. Estes requisitos são: teste da lógica definida pelo usuário, teste do sistema como um todo, seqüenciamento do teste, e o controlador de teste.

Dentre as técnicas existentes para teste dos componentes virtuais tem-se observado uma forte tendência para o uso de estruturas BIST como parte importante do teste dos núcleos de um sistema integrado. Estruturas BIST são eficientes, pois podem ser embutidas nos núcleos permitindo a manutenção da propriedade intelectual associada ao bloco funcional; possuem uma arquitetura que permite a automatização de partes do projeto; apresentam alta cobertura de falhas; são técnicas bastante sedimentadas, tendo sido aplicadas a uma grande variedade de circuitos; e por fim, facilitam a definição do teste do sistema como um todo [WUN 98]. Espera-se que o esquema BIST, voltado para núcleos de hardware, garanta a proteção da propriedade intelectual, o baixo consumo no dispositivo, a integração simplificada em um sistema com BIST, a compatibilidade com o reuso de projeto e a capacidade de diagnóstico.

Embora um esquema BIST satisfaça a maioria dos requisitos de teste e torne possível a implementação de uma variedade de metodologias de projeto visando o teste, ele pode resultar em um acréscimo de área considerável e, muitas vezes, na repetição inútil de estruturas de teste como os geradores de vetores, ou analisadores de respostas, por exemplo. Técnicas baseadas em cadeias de varredura também podem atender os requisitos de teste de um núcleo de hardware, porém estas podem apresentar problemas devido ao tempo de teste necessário e à necessidade de geração externa de padrões de teste [WUN 98]. Por este motivo, técnicas que reduzam o acréscimo de área e o tempo de teste são de grande interesse. Estes objetivos podem ser alcançados com o uso de controladores de teste mais elaborados e projetados especialmente para serem utilizados em sistemas integrados constituídos por núcleos de hardware.

O conceito de projeto visando o teste (do inglês, *DFT – Design For Test*) visa uma metodologia onde o teste e a verificação do sistema são considerados desde as primeiras especificações do projeto. Nesta metodologia, junto com a lógica do sistema são inseridas estruturas que facilitam a verificação do circuito em diversos níveis, desde a verificação funcional até o teste de manutenção. Estas estruturas podem ser tanto pontos de acesso a modos internos a partir de suas entradas e saídas primárias, como subcircuitos capazes de realizar, independente do testador, o teste do sistema como um todo.

## 2.4 ARQUITETURA DE TESTE CONCEITUAL

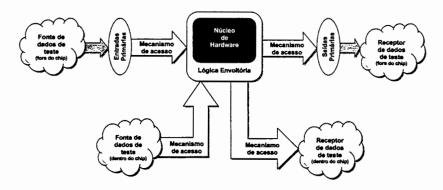

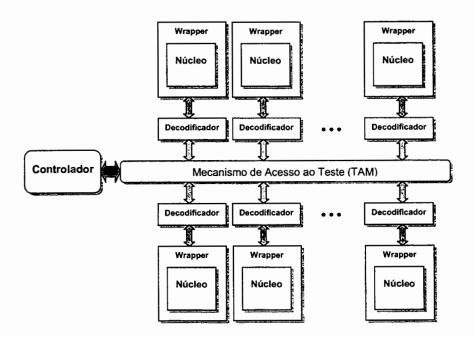

Baseada em alguns requisitos de teste, uma arquitetura conceitual e genérica para o teste foi introduzida em [ZOR 98]. Esta arquitetura, mostrada na figura 2.3, consiste em quatro elementos estruturais básicos:

- Uma fonte (dentro ou fora do chip) que gera estímulos de teste;

- Um receptor (dentro ou fora do *chip*) que avalia as respostas de teste;

- Mecanismos de acesso de teste que transportam os estímulos da fonte ao núcleo e deste ao receptor;

- Uma lógica de acesso periférica acoplada à periferia de um bloco interno ao sistema. Sua função é conectar os terminais deste bloco ao restante do circuito e aos mecanismos de acesso de teste.

Figura 2.3 - Arquitetura conceitual para o teste de sistemas integrados [ZOR 98].

Os elementos que compõem a arquitetural conceitual proposta por [ZOR 98] podem ser implementados de várias formas. As estruturas fonte e receptora de dados de teste podem ser implementadas externamente ao sistema, através de um equipamento de teste externo; dentro do sistema, através de estruturas BIST ou um controlador de teste embutido; ou como uma combinação entre o meio externo e os componentes internos.

#### 2.5 MECANISMO DE ACESSO AO TESTE

O mecanismo de acesso de teste cuida do transporte das informações de teste dentro do sistema, tanto da fonte de estímulos até o núcleo quanto deste até o receptor. Embora, para um núcleo, o mesmo tipo de mecanismo de acesso seja usado para transporte tanto de estímulos quanto de respostas de teste, isto não é estritamente necessário e várias combinações podem coexistir [ZOR 98]. O projeto de um mecanismo de acesso de teste procura o equilíbrio entre a capacidade de transporte do mecanismo e o custo de aplicação de teste que ele gera. A capacidade de transporte, por sua vez, é limitada pela capacidade da fonte e do receptor e pela área que pode ser utilizada para este fim [ZOR 98].

Segundo [ZOR 98], a implementação de um mecanismo de acesso tem as seguintes opções:

- Um mecanismo pode reutilizar barramentos e caminhos já existentes para o transporte das informações de teste ou ser formado por um caminho exclusivo;

- O mecanismo pode passar através de outros módulos dentro do sistema (utilizando ou não suas funções) ou passar em torno de outros núcleos, através de alguma lógica envoltória;

- Pode existir um mecanismo de acesso independente para cada núcleo ou pode-se ter o compartilhamento de caminhos entre diversos núcleos;

- O mecanismo de acesso pode ser apenas um transportador de sinais ou pode conter algumas funções para o controle do acesso.

[ZOR 98] apresenta, ainda, algumas abordagens já adotadas para implementação de mecanismos de acesso.

#### **2.6 PADRÃO IEEE P1500**

Em setembro de 1995, o *IEEE Test Technology Technical Committee (TTTC)* iniciou um Comitê de Atividade Técnica (do inglês, TAC, *Technical Activity Committee*) no campo de teste e DFT para sistemas integrados baseados em bibliotecas de hardware. Este Comitê evoluiu, mais tarde, para um Grupo de Trabalho de Padronização, aprovado em junho de 1997 como P1500, com o objetivo de desenvolver um padrão para o teste de blocos funcionais embutidos (núcleos de hardware).

A necessidade de padronização surgiu devido à existência de duas partes no processo de desenvolvimento e teste destas estruturas: de um lado, os provedores de núcleos de hardware e, de outro lado, o grupo usuário destes núcleos, projetistas ou integradores de sistemas. O grupo IEEE P1500 procura definir um padrão que facilite a interoperabilidade de blocos funcionais de diferentes origens a fim de melhorar a eficiência de ambos, provedores e usuários.

O grupo P1500 conta com a participação de diversas companhias de vários segmentos da indústria de semicondutores, incluindo-se ainda, o grupo de Trabalho em Teste relacionado à Manufatura da VSI Alliance [ALL 00].

Atualmente, o padrão ainda está em fase de elaboração. A versão atual da proposta de padronização considera núcleos como memórias e circuitos com lógica digital integrados ao sistema, mas vistos como blocos distintos dentro do mesmo, ou seja, não se pode modificar a lógica interna do componente durante a síntese. Uma versão preliminar do padrão foi finalizada em maio de 2000 (P1500/D0.2), alguns *drafts* foram apresentados em 2001 e uma versão final do padrão está prevista para 2002. Algumas definições do padrão têm sido divulgadas por meio de artigos em conferências recentes. Uma compilação destas informações é apresentada na seção seguinte.

O IEEE focaliza a padronização de partes do sistema relativas à interação entre o provedor e o usuário dos núcleos de hardware. Esta padronização envolve a transferência do conhecimento sobre o teste interno do núcleo, e o acesso de teste aos núcleos embutidos no sistema (bloco de acesso junto ao núcleo) [MAR 00a]. Tarefas como: métodos de teste ou DFT internos aos núcleos, integração do teste do sistema como um todo, otimização do teste do sistema, estímulos de teste e TAMs, não são cobertas pelo padrão P1500 [ZOR 2000]. Segundo [MAR 99], estas tarefas estão nas mãos dos provedores e dos usuários dos núcleos, e não estão sujeitas a padronização devido à grande diversidade de requisitos.

Os dois principais elementos do padrão P1500 são:

- 1. Uma linguagem, chamada Core Test Language (CTL), que servirá para transferência do conhecimento relativo ao teste interno do núcleo. CTL baseia-se na linguagem STIL (Padrão IEEE 1450.0) [ALL 2000] ou Standard Test Interface Language, que está sendo estendida para acomodar construções específicas do teste de núcleos de hardware.

- 2. Uma arquitetura escalonável (parametrizável) para teste de núcleos. Em relação ao acesso de teste aos núcleos embutidos no sistema, foi decidido padronizar-se apenas o bloco de acesso ao núcleo ou sua lógica envoltória (denominada Wrapper) e sua interface para um ou mais mecanismos de acesso de teste (ou, do inglês, TAM, Test Access Mechanisms) do sistema.

#### 2.6.1 Linguagem de Descrição do Teste de Núcleos de Hardware

A linguagem de Teste de Núcleos de hardware (do inglês, CTL, Core Test Language) definida no P1500 é uma linguagem capaz de capturar e expressar informações relativas ao teste de núcleos de hardware reutilizáveis [KAP 99]. Seu objetivo é complementar e co-existir com modos (orientados a estrutura) de representação de teste e atributos de testabilidade de uma entidade existente. Em particular, CTL procura prover um modelo de informação universal, explícito e conciso para controles específicos de núcleos de hardware, de forma a configurar um núcleo para seu próprio teste ou de suas funções anexas em um sistema. A-

lém disso, ela procura, ainda, prover as informações sobre requisitos e restrições para a implementação das interfaces entre o núcleo e o sistema no qual ele está inserido [ZOR 00].

CTL está sendo definida utilizando-se a sintaxe da Linguagem Padrão para Interface de Teste (do inglês, STIL, Standard Test Language Interface), definida pelo padrão IEEE 1450.0 [SOC 99]. STIL foi desenvolvida para ser uma linguagem comum, padronizada, para transferência de informações de testes digitais entre o ambiente de geração (domínio de ferramentas EDA) e o ambiente de aplicação (domínio dos equipamentos de teste). Então, STIL é capaz de descrever os dados relativos ao teste, tais como, estímulos de teste e formas de onda, para circuitos integrados. O P1500 utiliza, tanto quanto possível, a linguagem STIL original, mas dois elementos foram acrescentados a ela. Foram necessárias novas palavraschave para descrever aspectos específicos de núcleos de hardware e suas lógicas envoltórias. Além disso, um modelo de informação de teste está sendo criado, para permitir a definição das diversas configurações do núcleo, necessárias para torná-la parcial ou completamente compatível com o P1500. CTL descreve três tipos de informações:

- Aspectos dos dados de teste: trata das características básicas, tais como, tipo de dado, razão, estabilidade dos valores, e informações relativas à metodologia de teste.

- 2. Diferentes configurações do núcleo: informações sobre o modo de teste e sobre conectividade como atributos e protocolos.

- 3. Instruções para integração do sistema: informações sobre conectividade.

A partir de um código CTL o projetista tem acesso a informações suficientes da periferia do núcleo que permitam a instalação correta da lógica envoltória, o mapeamento dos terminais do núcleo para os terminais do *wrapper*, o reuso dos dados de teste do núcleo, o teste da lógica definida pelo usuário (LDU) e das conexões externas ao núcleo. Em [MAR 99] pode-se encontrar, com mais detalhes, as funções e os conteúdos da linguagem CTL definidas até este momento.

#### 2.6.2 Arquitetura Escalonável

O P1500 tenta definir uma interface uniforme e flexível entre o núcleo de hardware e seu ambiente de forma a facilitar sua integração. Um conjunto básico de requisitos de teste de núcleos de hardware foi estabelecido. Eles podem ser vistos como modos de operação que a arquitetura padrão deve suportar. São eles [ADH 99]:

- Modo Normal → Este modo permite que o sistema integrado e seus blocos embutidos funcionem em seu modo normal de operação.

- Modo de Teste Interno → Este modo habilita a aplicação de vetores prédefinidos em um núcleo do sistema.

- Modo de Teste de Interconexão → Este modo de teste habilita a lógica envoltória do núcleo de hardware a ser utilizada para o teste das conexões do sistema e da lógica entre blocos funcionais.

- Modo de Isolamento → Este modo permite que o núcleo de hardware seja isolado a fim de facilitar o teste de outros blocos ou da LDU no sistema integrado.

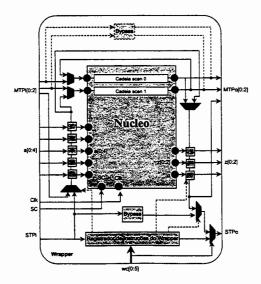

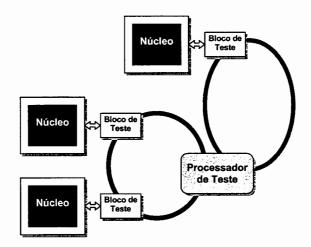

A figura 2.4 mostra um diagrama da arquitetura de teste proposta. Existem três componentes chave nesta arquitetura: a lógica envoltória do núcleo de hardware, o mecanismo de controle do teste e o mecanismo de acesso ao núcleo. Estes componentes são descritos detalhadamente em [AHD 99] e [IEE 15].

Figura 2.4 - Sistema integrado com núcleos utilizando o padrão P1500 [ADH 99].

A lógica envoltória do núcleo de hardware, também chamada de Wrapper, provê mecanismos para o acesso de dados de teste e o isolamento de um núcleo do resto do sistema. Esta lógica permite o controle das entradas e saídas através do mecanismo de acesso, de forma que os testes internos do núcleo possam ser reaplicados dentro do sistema. Esta lógica deve ser também capaz de prover o isolamento do bloco durante seu teste ou durante o teste de estruturas próximas, evitando dano ao sistema. O circuito envoltório pode ser visto como separado logicamente do bloco funcional e pode vir com o componente ou ser acrescido du-

rante a síntese do sistema. O padrão P1500 define apenas o comportamento funcional da lógica envoltória e não sua forma de implementação.

O modo de operação da lógica envoltória é determinado pela carga serial das instruções no Registrador de Instruções do *Wrapper*. O Grupo de Trabalho do P1500 pretende definir três categorias de instruções:

- Instruções obrigatórias: para que um wrapper seja compatível com o P1500, ele deve implementar este conjunto de instruções que resultam em um comportamento específico e pré-definido.

- 2. **Instruções Opcionais**: se implementadas, deve resultar em um comportamento pré-definido para que o *wrapper* seja compatível com o padrão P1500.

- 3. Instruções definidas pelo usuário: sem restrições ou regras.

O conteúdo de um wrapper é: um Registrador de Instruções do Wrapper (WRI) que serve para controlar a operação da lógica envoltória; múltiplas células capazes de prover controlabilidade e observabilidade nos terminais dos núcleos; um registrador de bypass de um bit que serve como passagem para o mecanismo de acesso de teste serial; e sinais de conexão para selecionar os vários modos de operação do wrapper. Observe que a lógica envoltória é muito semelhante a uma máquina da TAP definida pelo padrão IEEE std. 1149.1 [IEE 90] e resumida na seção 2.7. A principal diferença é que o wrapper permite um maior paralelismo, a fim de aumentar a dinâmica do teste provendo um maior controle e observabilidade durante o processo de teste. A figura 2.5 mostra a arquitetura conceitual do wrapper proposta pelo padrão IEEE P1500 [MAR 00b].

Figura 2.5 - Arquitetura conceitual do wrapper segundo IEEE P1500 [MAR 00b].

## 2.7 PADRÃO IEEE STD. 1149.1 (BOUNDARY-SCAN)

Nos meados dos anos 80, um grupo de engenheiros de teste de várias companhias européias de sistemas eletrônicos reuniu-se para examinar o problema crescente na dificuldade do teste de pontos de solda e das conexões entre CIs que eram montado sobre de placas de circuitos impressos. Conforme a tecnologia evoluía as placas de circuitos impressos eram construídas com trilhas mais finas e com quantidades maiores de camadas tornando o teste das interconexões praticamente impossível. Este grupo foi chamado de Joint European Test Action Group (JETAG).

A solução proposta por este grupo foi baseada no conceito de um caminho serial de registradores de deslocamentos colocado na periferia da lógica central que forma o CI, daí o consequente nome de *Boundary-scan*. Mais tarde este grupo uniu-se a engenheiros de testes de companhias da América do Norte e o grupo passou a ser chamado de Joint Test Action Group (JTAG). Esta organização converteu a idéia do *boundary-scan* em um padrão internacional chamado de IEEE std. 1149.1 [IEE 90].

Apesar do enfoque principal do padrão IEEE 1149.1 ser o teste de interconexões, o padrão também permite o uso das suas estruturas para testar a lógica central dos componentes. Na era SOC, o padrão *boundary-scan* passou a ser menos utilizado para o teste de interconexões e mais explorado para o teste da lógica central dos núcleos, provendo um importante mecanismo de acesso para a inserção de dados de teste do testador nos núcleos de hardware e destes de volta ao testador.

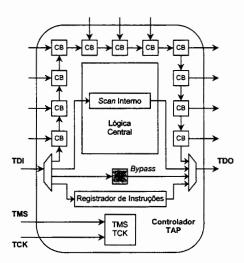

O padrão IEEE std. 1149.1 consiste basicamente na arquitetura da figura 2.6 e está dividido nos seguintes elementos:

- Quatro pinos de teste dedicados Test Data Input (TDI), Test Mode Select (TMS), Test Clock (TCK), Test Data Output (TDO). Estes pinos são coletivamente chamados de TAP (do inglês, Test Port Access).

- Células boundary-scan colocadas em todos os pinos de entradas e saídas, e unidas entre si para juntas formarem um registrador serial boundary-scan. O pino de TDI está na entrada desse registrador e o pino de TDO na saída.

- Uma máquina de estados com 16 estados (figura 2.7), para controlar a TAP através dos sinais de TCK e TMS.

- Um registrador de instruções.

#### • Um registrador de Bypass de 1-bit.

As células boundary-scan (CB) podem ser configuradas em modo de entrada paralela, saída paralela e modo deslocamento. Uma operação de carga paralela é chamada de operação de "CAPTURA". Esta operação faz com que os valores que foram introduzidos sejam carregados palas células de estrada e os valores que passaram pela lógica central do dispositivo sejam colocados nas células de saída. Uma operação de descarga em paralelo é chamada de operação de "ATUALIZAÇÃO". Esta operação faz com que os valores que estão nas células de entrada serem enviados para a lógica central. Isto causa a substituição de valores dos pinos de entrada do componente e dos valores presentes nas células boundary-scan de saída que são passados através dos pinos de saídas do componente, substituindo os valores de saídas gerados pela lógica central.

Figura 2.6 - Arquitetura IEEE std. 1149.1.

Para cada célula *boundary-scan* também é proporcionado um estado de registrador de deslocamento, onde todos as células são conectadas em série formando um caminho serial na periferia do CI. Os sinais são introduzidos a partir do pino de entrada TDI e são coletados a partir do pino de saída TDO.

No padrão IEEE std. 1149.1, todos os sinais são inseridos e retirados serialmente através dos pinos de TDI e TDO respectivamente. O controle de estados é feito através dos sinais de TMS e TCK. TCK é um sinal de relógio dedicado que serve para o deslocamento serial dos sinais nas células *boundary-scan*.

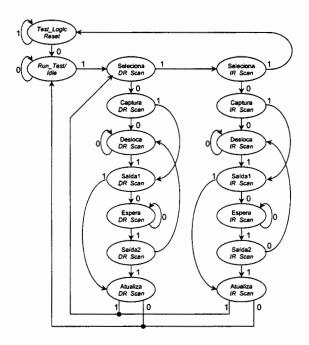

Figura 2.7 - Diagrama de estados do controlador de TAP.

O controlador de TAP (figura 2.7) inicializa no estado de *Test\_Logic\_Reset*. Enquanto TMS permanece em '1', o estado permanece inalterado. Quando TMS baixa, causa a transição para o estado inativo *Run\_Test*. Normalmente deseja-se chegar ao estado *Seleciona IR\_Scan* e assim ficar prontos para carregar e executar uma nova instrução. Uma seqüência adicional em TMS alcançará este estado. A partir deste estado, pode-se mover pelos estados de *Captura IR\_Scan*, *Desloca IR\_Scan e Atualiza IR\_Scan* conforme desejado. Uma instrução que esteja no registrador de instruções pode ser carregada diretamente a partir do estado de *Captura IR\_Scan*. Também pode-se carregar a instrução no registrador de instruções pelo deslocada serialmente através TDI no estado de *Desloca IR\_Scan*. No estado *Atualiza IR\_Scan*, a instrução é habilitada para tornar-se a instrução atual preparando o sistema para o teste, como por exemplo, selecionar uma cadeia *scan* interna.

A partir do estado Seleciona DR\_Scan os dados de teste são manipulados. No estado Desloca DR\_Scan os dados são deslocados serialmente através do pino de TDI, e no estado de Atualiza DR\_Scan o tipo de teste que foi selecionado pela instrução é executado, como por exemplo, a transferência dos dados das cadeias para o lógica central do núcleo.

Note que não existe nenhum sinal de *Reset* no controlador de TAP. Se houver uma necessidade para reinicializar o controle, isto pode ser feito mantendo TMS alto e ativando o sinal de TCK por no máximo cinco pulsos de relógio, ou seja, de qualquer estado, com no máximo cinco pulsos de relógio e TMS = '1' pode-se chegar no estado *Test\_Logic\_Reset*.

Controladores de Teste 21

#### 3 CONTROLADORES DE TESTE

À medida que aumenta a complexidade dos sistemas integrados e das estruturas de testes, surge a necessidade do uso de controladores de teste mais sofisticados e que atendam rapidamente a continua evolução tecnológica.

Um controlador de teste é o módulo responsável pelo gerenciamento do teste como um todo, enviando sinais de controle, estímulos de teste e analisando respostas para cada componente do sistema (núcleos de hardware, LDU e interconexões), de acordo com a seqüência definida e através dos caminhos de acesso e mecanismos de teste disponíveis.

O gerenciamento e envio dos sinais de teste pode ser realizado por equipamentos tradicionais chamados de ATEs (do inglês, *Automatic Test Equipments*), os quais realizam o controle do teste externamente, através das entradas e saídas primárias do circuito integrado, e de pinos extra, que são utilizados somente para o teste. Outra forma de fazer o controle é através de um módulo interno ao SOC. Fazendo uso da dinâmica re-configurável e escalonável da lógica envoltória e da flexibilidade das estruturas propostas pelo padrão IEEE P1500, dispositivos do tipo microprocessadores/microcontroladores podem ser transformadas em controladores de teste, transferindo, assim, a funcionalidade do controle para dentro do SOC [PAP99], [ABH99], [RAJ99], [COT 01].

O uso de um controlador interno tem, entre outras, a vantagem de ser dedicado, além de poder reutilizar módulos como, por exemplo, memórias existentes no sistema. Além disso, o controlador interno possui a vantagem de poder trabalhar na mesma freqüência do SOC, facilitando a execução de testes *at-speed* e contribuindo para a diminuir o tempo global de teste do sistema integrado. Outra característica importante no uso de um controlador interno, em relação aos ATEs, é a redução do número de pinos de entrada e saída do CI.

A transferência da funcionalidade do controle do teste para dentro do sistema é economicamente uma solução muito atrativa porque equipamentos de teste externos capazes de manipular uma grande quantidade de dados de teste e operar com altas velocidades possuem custos elevados. O acréscimo de pinos no encapsulamento para realizar a comunicação

Controladores de Teste 22

entre o controlador de teste externo e os núcleos que constituem o sistema é outro problema a se considerar.

Além do custo elevado para a inserção de pinos e caminhos extra no sistema integrado, existe o fato de que, em alguns sistemas, pode ser inviável a inserção de todos os pinos necessários para o teste, devido à limitação física do encapsulamento. O uso dos mecanismos de acesso ao teste pode reduzir o número de pinos extra para o teste, uma vez que os sinais podem ser roteados através de outros módulos até o núcleo que se deseja testar. Porém, o tempo total de teste do sistema pode aumentar significativamente e até mesmo tornar-se impraticável. Isto ocorre porque é necessário obedecer a uma seqüência de teste, já que o teste de um ou mais núcleos que utilizam um caminho específico deve ser concluído para que os caminhos de acesso possam ser reutilizados para testar outros elementos do sistema.

# 3.1 CUSTOS E PRECISÃO DE EQUIPAMENTOS AUTOMÁTICOS EXTERNOS DE TESTE (ATES).

Os custos dos ATEs são tradicionalmente medidos utilizando-se uma simples aproximação de "custo por pino digital". Embora este método seja conveniente, ele é incompleto, porque ignora os custos básicos do sistema associados com a infra-estrutura de equipamentos e instrumentos centrais como também ignora o escalonamento benéfico que ocorre com o incremento da quantidade de pinos. Por essa razão, foi sugerido o uso da equação 1 para o cálculo dos custos de ATEs de modo que os valores estejam mais próximo do real [ROA 01].

Custo do Testador =

$$b + \sum (m * x)_n$$

(1)

Na equação um (1), b representa o custo base de um sistema de teste com zero pinos, m representa o incremento do custo por pino, e x é o número de pinos. Note que b considera a capacidade, desempenho, e características do sistema básico, enquanto m depende da característica e capacidade analógica dos pinos. A tabela 3.1 mostra, como exemplo, alguns dados utilizados pelos fabricantes de semicondutores para o cálculo dos custos de equipamentos automáticos de testes [ROA 01].

Controladores de Teste 23

Tabela 3.1 - Parâmetros para o cálculo de custos de ATEs.

|                             | b          | m                               | X                   |                       |  |  |

|-----------------------------|------------|---------------------------------|---------------------|-----------------------|--|--|

| Segmentos de Testadores     | Custo Base | Incremento do<br>Custo por Pino | Quantidade de Pinos | Custo Total           |  |  |

|                             | KUS\$      | US\$                            | de i mos            | US\$                  |  |  |

| ASIC/MPU de alto desempenho | 250 - 400  | 2.700 - 6.000                   | 512                 | 1.632.400 - 3.472.000 |  |  |

| Sistemas Mistos             | 250 - 350  | 3.000 - 18.000                  | 128 - 192           | 634.000 - 3.806.000   |  |  |

| Testador DFT                | 100 - 350  | 150 - 650                       | 512 - 2500          | 176.800 - 1.975.000   |  |  |

| Microcontroladores / ASIC   | 200 - 350  | 1.200 - 2.500                   | 256 - 1024          | 507.200 -2.910.000    |  |  |

| Memória                     | 200+       | 800 - 1.000                     | 1024                | 1.019.200 -1.224.000  |  |  |

| RF                          | 200+       | ≈50.000                         | 32                  | ≈1.800.000            |  |  |

O incremento na velocidade de microprocessadores e pinos de E/S (entrada e saída) exige o aumento da precisão para uma resolução adequada dos tempos dos sinais medidos. Enquanto a velocidade fora do chip tem um incremento de 30% ao ano, a precisão dos testadores tem crescido a uma taxa de 12% ao ano. Se essa tendência atual continuar, erros do testador irão se aproximar do ciclo de tempo de dispositivos rápidos. Como mostra a tabela 3.2 [ROA 01] em 2001 às perdas de rendimento devido à imprecisão dos testadores tornaram-se um problema quando metodologias tradicionais de testes funcionais são utilizadas.

Tabela 3.2 - Rendimento versus precisão do testador.

| Anos                                                         |     | 2001 | 2002    | 2003  | 2004 | 2005 | 2006 | 2007 |

|--------------------------------------------------------------|-----|------|---------|-------|------|------|------|------|

| Freqüência do barramento do chip-placa – alto desempenho     | MHz | 1700 | - 1870. | :2057 | 2262 | 2488 | 2737 | 3014 |

| Período do dispositivo                                       | ps  | 588  | 535     | 486   | 442  | 402  | 365  | 332  |

| Precisão global do ATE (OTA)                                 | ps  | 200  | 176     | 155   | 136  | 120  | 106  | 93   |

| Exigência de precisão global do dispositivo (objetivo de 5%) | ps  | 29   | 27      | 24    | 22   | 20   | 18   | 17   |

- Soluções de fabricação são conhecidas

- Soluções de fabricação não são conhecidas

Este grave potencial de perda de rendimento deve ser reduzido pela introdução de métodos alternativos para testes funcionais *at-speed*. Novas metodologias devem ser buscadas

para aliviar o risco da perda de rendimento em projetos, devido a um testador impreciso. Devem também fornecer um beneficio adicional na redução da complexidade da interface entre o testador e o dispositivo sob teste, buscar a redução nas exigências das capacidades do equipamento e o aumento na ênfase de projetos baseados em DFT, incrementando o uso do teste paralelo e reduzindo o tempo de teste. Isto deve resultar na redução total do impacto no custo do equipamento de teste e, por conseqüência, no custo total do teste. O uso de testadores internos se insere perfeitamente neste desafio de fornecer uma alternativa de melhorar a relação da precisão necessária nos testadores externos e diminuir o impacto do custo dos ATEs e no teste como um todo.

#### 3.2 CONTROLADORES INTERNOS

Alguns trabalhos de pesquisa sobre o uso de controladores internos de teste têm sido apresentados nos últimos anos. Nestes trabalhos encontra-se uma grande variedade de implementações (processadores dedicados, reutilizados, etc.) e propostas de teste (BIST, cadeias de varredura scan, IDDq, etc.), que transferem parcial ou totalmente a funcionalidade do testador para dentro do *chip*. Nas seções seguintes deste capítulo, os principais trabalhos relacionados com controladores de teste internos serão apresentados.

## 3.2.1 Microprocessadores Reutilizados para Produzir Controladores de Teste

É fato conhecido que grande parte dos projetos de sistemas integrados possuem algum tipo de microprocessador (ou algum componente semelhante) embutido. Conseqüentemente, uma metodologia baseada no reuso de processadores para teste pode ser utilizada para a maioria dos sistemas baseados em núcleos de hardware. Em [PAP 99] é sugerido um esquema de teste baseado no uso de um microprocessador contido em um SOC para testar os demais núcleos do sistema. Neste caso, o tamanho do controlador externo de teste seria muito pequeno, uma vez que o microprocessador executaria a maioria das funções de controle do teste.

Os principais componentes exigidos pela estratégia sugerida seriam um microprocessador e memórias para serem utilizadas durante o teste. Um caminho deve estar disponível entre os pinos de entrada e saída primários do sistema, e a memória de teste requerida, de forma que os dados de teste possam ser carregados a partir de um equipamento externo. O

teste do microprocessador e da memória não é discutido em [PAP 99], assume-se apenas que estes componentes foram previamente testados.

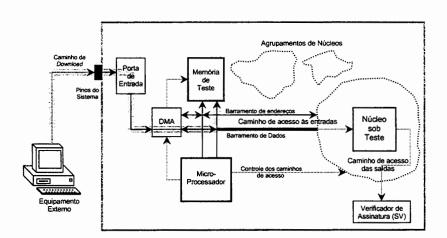

O conceito proposto em [PAP 99] é ilustrado na figura 3.1. Os dados de teste compactados que estão armazenados em um equipamento externo de teste, são carregados na memória de teste através de uma técnica de DMA (do inglês, *Direct Memory Access*). Após a carga dos dados, o microprocessador testa os núcleos. Os núcleos de hardware podem ser agrupados para o teste, sendo que núcleos pertencentes ao mesmo agrupamento não podem ser testados simultaneamente, enquanto que núcleos que fazem parte de agrupamentos diferentes podem ser testados em paralelo. Núcleos que pertencem ao mesmo agrupamento também podem ser diretamente conectados uns aos outros, enquanto, núcleos de diferentes grupos não podem ser diretamente conectados. A vantagem de fazer agrupamentos está em exercer um maior paralelismo do teste.

Figura 3.1 - Esquema de teste proposto em [PAP 99].

Para testar um núcleo de um agrupamento, é necessário prover um caminho de acesso do microprocessador até as entradas do núcleo e também, um caminho de acesso das saídas do núcleo até um bloco chamado de Verificador de Assinatura (SV, do inglês, Signature Verifier). Este bloco é um registrador de assinatura de múltiplas entradas, chamado de MISR (do inglês, Multiple Input Signature Register), capaz de compactar das respostas fornecidas pelo núcleo em uma assinatura que será analisada pelo microprocessador.

O microprocessador habilita os caminhos de acesso com a ajuda de um controlador de teste simplificado e envia os dados para o núcleo. Depois de aplicar os padrões de teste no núcleo, as saídas são levadas até o bloco verificador de assinaturas.

Na figura 3.1 observa-se a existência de três caminhos diferentes: um caminho de carga de dados (*download*), o caminho de acesso às entradas, e o caminho de acesso às saídas. O caminho de acesso às entradas inclui o caminho que faz a conexão da memória de teste com o microprocessador e deste com o núcleo.

Considerando que o tamanho da memória de teste é limitado deve-se assegurar que a carga dos dados de teste não exceda a capacidade da memória de teste. Isto é feito através do "empacotamento" dos vetores de teste, ou seja, uma certa quantidade de vetores é agrupada formando um pacote. A memória é carregada com estes pacotes e o tamanho de um pacote deve ser sempre menor que a capacidade da memória. Novas cargas de pacotes somente poderão ser feitas quando existir espaço na memória. O microprocessador deve esperar a carga total do pacote antes de começar a leitura deste.

O microprocessador deve executar as seguintes funções:

- Antes de ter acesso a cada pacote, o microprocessador deve conferir se o DMA já carregou todo o pacote exigido no teste;

- Controlar a carga do DMA, para que este não carregue um novo pacote sobre algum outro pacote que esteja sendo usado em um teste. Isto é feito através de interrupções;

- 3. Enquanto estiver testando um núcleo, o microprocessador deve configurar os caminhos, a fim de que os corretos acessos de entrada e saída dos núcleos sob teste sejam habilitados. Deve configurar ainda, o bloco verificador de assinaturas para compactar/verificar as saídas como exigido;

- 4. No caso de testes pseudo-aleatórios o microprocessador pode gerar os padrões de testes por si só. Neste caso, um controlador BIST não é necessário para testar qualquer núcleo com estrutura BIST, como, por exemplo, núcleos com testes pseudo-aleatórios. Esta seria uma forma de um software BIST e em alguns casos pode executar um teste mais rapidamente que um teste pseudo-aleatório externo.

Algumas informações não estão claras neste trabalho: o tempo de teste necessário e a definição da seqüência de teste. Além disto, o exemplo apresentado é bastante simples e o tempo de teste pode ser proibitivo para sistemas mais complexos. Outro problema refere-se a verificação do microprocessador e da memória utilizados no teste. O primeiro é, em geral, uma das partes mais complexas de um sistema (pode ser, inclusive, um núcleo hierárquico, com memória interna, unidade lógica e aritmética, máquina de controle, etc.), cujo teste deve

ser uma das tarefas mais complicadas. Desta forma, o problema principal do teste não é resolvido.

Em [RAJ 99] é proposta uma metodologia de teste para sistemas baseados em núcleos de hardware que contenham um núcleo microprocessador. Neste esquema, primeiro é testado o núcleo microprocessador. Em seguida, este é utilizado para testar memórias e outros núcleos do sistema. A metodologia proposta em [RAJ 99] pode ser dividida em:

- 1. Teste do microprocessador assegurando o seu correto funcionamento;

- 2. Uso do microprocessador para testar memórias;

- 3. Teste de outros núcleos;

Para o teste do microprocessador é utilizado um Registrador de Controle de teste (TCR, do inglês, *Test Control Register*), para prover os códigos operacionais das instruções do microprocessador durante o modo de teste. Também é utilizado um LFSR (do inglês, *Linear Feedback Shift Register*) e um MISR para gerar dados aleatoriamente e compactar as respostas, respectivamente. O controle deste esquema de teste é implementado através de um controlador TAP definido pelo padrão IEEE 1149.1 [IEE 90].

Para o teste das memórias, [RAJ 99] propõe o uso de um programa em uma linguagem de baixo nível (assembly) para gerar os padrões de teste de um algoritmo March [LAL 97]. O programa de teste deve ser convertido em um código binário que é armazenado em um equipamento externo. Durante o teste, este código passa diretamente do testador para o microprocessador que executa as operações e testa a memória. A saída final do microprocessador para o testador é um sinal indicando se a memória está livre de falhas ou possui algum defeito. Este conceito é utilizado para testar os outros núcleos do sistema. Um programa gerado a partir de uma linguagem de baixo nível é convertido em um código binário e armazenado em um testador, o microprocessador utiliza este código para testar os núcleos.

Este trabalho apresenta uma visão geral do processo de controle interno do teste através de alguns exemplos específicos. O controlador de teste é utilizado para o envio dos dados de teste, porém o autor não faz referência do controle ou do mecanismo de acesso utilizado para o teste de um sistema completo.

Usualmente, o teste funcional de sistemas complexos requer grandes quantidades de padrões de testes. Entretanto, espaço em memória nem sempre está disponível no sistema. Os vetores de teste podem ser de dois tipos: determinísticos ou pseudo-aleatórios. Padrões determinísticos são seqüências inteiras e específicas de estímulos gerados, normalmente, por simulação e que visam maior cobertura de falhas com menores quantidades de valores. Os padrões pseudo-aleatórios são valores gerados a partir de um polinômio. Para padrões de testes determinísticos, todos os vetores utilizados no teste devem ser armazenados em alguma memória e para padrões de testes pseudo-aleatórios, é suficiente armazenar o polinômio ou as sementes utilizadas para gerar os vetores.

A desvantagem dos padrões pseudo-aleatórios em relação aos determinísticos está na cobertura de falhas. Padrões pseudo-aleatórios têm, em geral, menor cobertura de falhas ou precisam de um maior número de vetores para a mesma cobertura oferecida por padrões determinísticos. Em geral, não se consegue gerar todos os vetores de teste necessários a partir de um, ou um conjunto, de polinômios. Outro fato importante é que os polinômios geram uma grande quantidade de padrões desnecessários, aumentando significativamente o tempo de teste em muitos sistemas complexos.

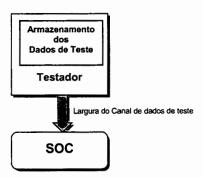

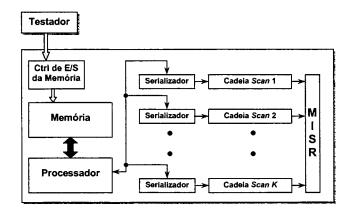

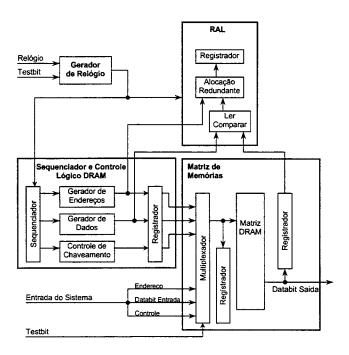

Em [HEL 96] é proposto um modelo que utiliza um modo misto para a geração de padrões de testes para circuitos com cadeias *scan*. Um processador embutido é utilizado para gerar padrões de testes pseudo-aleatórios, diminuindo a necessidade de grandes espaços em memória. Em complemento, serão armazenados somente os padrões determinísticos necessários para cobrir as falhas que os vetores gerados pelo processador não consigam detectar.