## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

### ROGER CAPUTO LLANOS

# Voltage Scaling Interfaces for Multi-Voltage Digital Systems

Thesis presented in partial fulfillment of the requirements for the degree of Master of Microeletronics

Advisor: Prof. Dr. Ricardo Reis Coadvisor: Prof. Dr. Marcelo Johann

Porto Alegre December 2015

### **CIP** — **CATALOGING-IN-PUBLICATION**

Llanos, Roger Caputo

Voltage Scaling Interfaces for Multi-Voltage Digital Systems / Roger Caputo Llanos. – Porto Alegre: PGMICRO da UFRGS, 2015.

119 f.: il.

Thesis (Master) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica, Porto Alegre, BR–RS, 2015. Advisor: Ricardo Reis; Coadvisor: Marcelo Johann.

1. Level Shifter. 2. Low Power. 3. Multiple Supply Voltage. 4. Power-Delay Product. 5. CMOS. 6. Dynamic Power. 7. Static Power. I. Reis, Ricardo. II. Johann, Marcelo. III. Título.

### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos Alexandre Netto

Vice-Reitor: Prof. Rui Vicente Oppermann

Pró-Reitor de Pós-Graduação: Prof. Vladimir Pinheiro do Nascimento

Diretor do Instituto de Informática: Prof. Luis da Cunha Lamb

Coordenador do PGMICRO: Prof. Gilson Inácio Wirth

Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

#### **ABSTRACT**

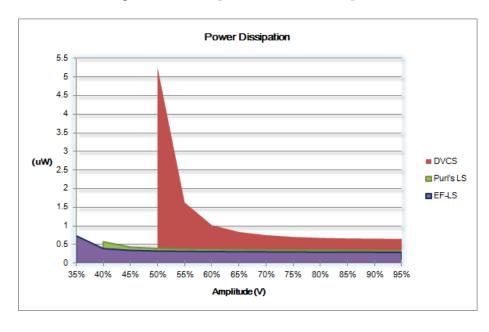

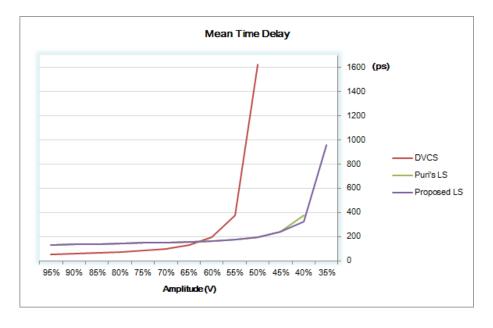

Multiple Voltage Digital Systems exploit the concept of voltage scaling by applying different supplies to particular regions of the chip. Each of those regions belongs to a power domain and may have two or more supply voltage configurations. Regardless of distinct energy levels on different power domains, the blocks shall process signals with coherent logic levels. In these systems, the Level Shifters (LS) are essential components that act as voltage scaling interfaces between power domains, guaranteeing the correct signal transmission. With the appropriate voltage scaling interface and its proper implementation, we can avoid excessive static and dynamic power consumption. Therefore, the design and implementation of level shifters should be a conscientious process and must guarantee the lowest overhead in size, energy consumption, and delay time. In this work, we study the main characteristics of voltage scaling interfaces and introduce an energy-efficient level shifter with reduced area, and suitable for low-to-high level conversion. We present the level shifters with the best performance that we found in the literature and categorize them into two main groups: Dual-rail and Single-rail, according to the number of power rails required. The proposed circuit was compared to the traditional topology of each group, Differential Cascode Voltage Switch (DCVS) and Puri's level shifter respectively. Simulations on an IBM<sup>TM</sup> 130nm CMOS technology show that the proposed topology requires up to 93.79% less energy under certain conditions. It presented 88.03% smaller delay and 39.6% less *Power-Delay Product* (PDP) when compared to the DCVS topology. In contrast with the Puri's level shifter, we obtained a reduction of 32.08% in power consumption, 13.26% smaller delay and 15.37% lower PDP. Besides, our level shifter was the only one capable of working at 35% of the nominal supply voltage.

**Keywords:** Level Shifter. Low Power. Multiple Supply Voltage. Power-Delay Product. CMOS. Dynamic Power. Static Power.

### Interfaces de escalonamento de tensão para Sistemas Digitais de Múltiplas Tensões

#### **RESUMO**

Os Sistemas Digitais de Múltiplas Tensões exploram o conceito de dimensionamento da tensão de alimentação através da aplicação de diferentes fontes para regiões específicas do chip. Cada uma destas regiões pertence a um domínio de energia e pode ter duas ou mais configurações de voltagens. Independentemente dos distintos níveis de energia em diferentes domínios de tensão, os blocos devem processar sinais com níveis lógicos coerentes. Nestes sistemas, os Conversores de Nível (LS do inglês Level Shifters) são componentes essenciais que atuam como interfaces de escalonamento da tensão entre domínios de energia, garantindo a correta transmissão dos sinais. Com a apropriada interface de escalonamento de tensão e sua correta implementação, pode-se evitar o consumo excessivo de potência dinâmica e estática. Portanto, a concepção e implementação de conversores de nível deve ser um processo consciente que garanta o menor sobrecusto no tamanho, consumo de energia, e tempo de atraso. Neste trabalho estudam-se as principais características das interfaces de escalonamento de tensão e se introduce um conversor de tensão com eficiência energética e área reduzida, adequado para a conversão de baixo a alto nível. Apresentam-se os conversores de nível com o melhor desempenho encontrados na literatura, os quais são categorizados em dois principais grupos: Dois trilhos (Dual-rail) e Único trilho (Single-rail), de acordo ao número de linhas de alimentação necessárias. O circuito proposto foi comparado com a topologia tradicional de cada grupo, o Differential Cascode Voltage Switch (DCVS) e o conversor de Puri respectivamente. Simulações na tecnologia CMOS 130nm da IBM<sup>TM</sup> mostram que a topologia proposta requer até 93,79% menos energia em determinadas condições. Esta apresentou 88,03% menor atraso e uma redução de 39,6% no Produto Potência-Atraso (PDP), quando comparada com a topologia DCVS. Em contraste com o conversor Puri, obteve-se uma redução de 32,08% no consumo de energia, 13,26% diminuição no atraso e 15,37% inferior PDP. Além disso, o conversor de nível proposto foi o único capaz de trabalhar a 35% da tensão nominal de alimentação.

**Palavras-chave:** Conversores de Nível. Baixo Consumo. Múltiplas Tensões. Produto Potência-Atraso. CMOS. Potência Dinâmica. Potência Estática.

### LIST OF ABBREVIATIONS AND ACRONYMS

ALC Asynchronous Level Converters

AVS Adaptive Voltage Scaling

CMOS Complementary Metal-Oxide Semiconductor

CPU Central Process Unit

CVS Clustered Voltage Supply

DIBL Drain Induced Barrier Lowering

DCVSL Differential Cascode Voltage Switch Logic

DLS Dual-rail Level Shifters

DVS Dynamic Voltage Supply

DVFS Dynamic Voltage and Frequency Scaling

ECVS Extended Clustered Voltage Scaling

EDA Electronic Design Automation

EM Electromigration

EOP Energy Per Operation

GECVS Greedy Extended - Clustered Voltage Scaling

HDL Hardware Description Language

IC Integrated Circuit

IP Intellectual Property

ITRS International Technology Roadmap for Semiconductors

LCFF Level Converting Flip-Flop

LS Level Shifters

MOS Metal-Oxide Semiconductor

MOSFET Metal-Oxide Semiconductor Field-Effect Transistor

MDSV Multiple Dynamic Supply Voltage

MVS Multi-level Voltage Scaling

PDP Power-Delay Product

ROI Return-on-Investment

RTL Register Transfer Level

SLS Single-rail Level Shifters

SoC System-On-Chip

STA Static Timing Analysis

SVS Static Voltage Scaling

VLSI Very Large Scale Integration

VRM Voltage Regulator Module

VTC Volta-transfer Characteristic

# LIST OF FIGURES

| Figure 1.1 Power Vs Energy                                        | 14  |

|-------------------------------------------------------------------|-----|

| Figure 1.2 Short-circuit current during transients                | 16  |

| Figure 1.3 Source of leakage currents in CMOS inverter            |     |

|                                                                   |     |

| Figure 2.1 CMOS inverter driving an external load                 |     |

| Figure 2.2 Sizing of a CMOS inverter for energy-minimization      |     |

| Figure 2.3 Progressive sizing of transistors of a n-input gate    |     |

| Figure 2.4 Example of transistor reordering                       |     |

| Figure 2.5 Propagation delay of a CMOS inverter                   |     |

| Figure 2.6 Subthreshold leakage                                   |     |

| Figure 2.7 Block diagram of a DVFS example                        |     |

| Figure 2.8 Voltage regulator module (VRM)                         |     |

| Figure 2.9 Global power gating topology                           |     |

| Figure 2.10 Local power gating topology                           |     |

| Figure 2.11 Switch-in-cell power gating topology                  |     |

| Figure 2.12 Clock Gating                                          |     |

| Figure 2.13 Energy-delay tradeoff                                 |     |

| Figure 2.14 Concurrency example design                            |     |

| Figure 2.15 Parallel Implementation                               |     |

| Figure 2.16 Pipelining Implementation                             | 42  |

| Figure 3.1 Typical back-end flow                                  | 4.4 |

| • • • • • • • • • • • • • • • • • • • •                           |     |

| Figure 3.2 Clustered Voltage Scaling                              |     |

| Figure 3.3 Extended Clustered Voltage Scaling                     |     |

| Tigute 3.4 MD3 v operation example                                |     |

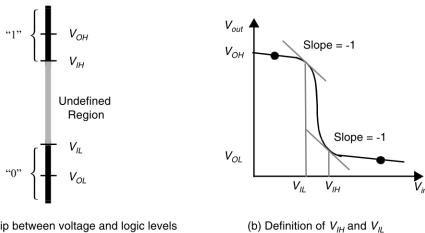

| Figure 4.1 Mapping logic levels to the voltage domain             | 58  |

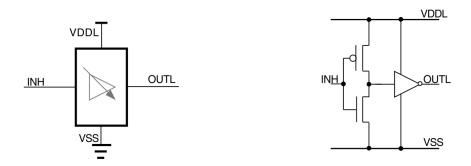

| Figure 4.2 High-to-Low Level Shifter                              |     |

| Figure 4.3 Low-to-High Level Shifter                              | 59  |

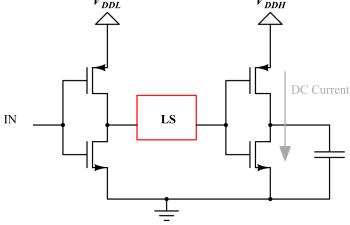

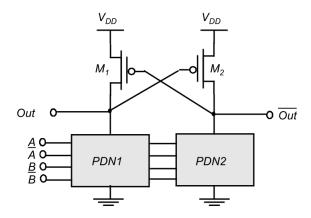

| Figure 4.4 DCVSL gate                                             |     |

| Figure 4.5 DCVS level shifter                                     | 62  |

| Figure 4.6 Constant-current mirror level shifter                  | 62  |

| Figure 4.7 Near-threshold level shifter                           | 63  |

| Figure 4.8 Bootstrapping level shifter                            | 65  |

| Figure 4.9 Pass gate level shifter                                |     |

| Figure 4.10 Half latch level shifter                              | 67  |

| Figure 4.11 Fedback-based level shifter                           | 68  |

| Figure 4.12 Puri's level shifter                                  |     |

| Figure 4.13 Comparison of DCVS converter and Puri's level shifter | 71  |

| Figure 4.14 Cross-coupled SLS                                     | 72  |

| Figure 4.15 DLS versus SLS on a multi-voltage design              |     |

|                                                                   |     |

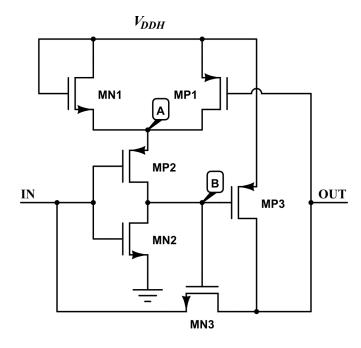

| Figure 5.1 Proposed level shifter <i>EF-LS</i>                    |     |

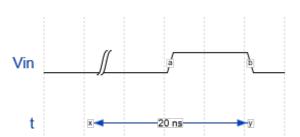

| Figure 5.2 Simulation Scheme of First Scenario                    |     |

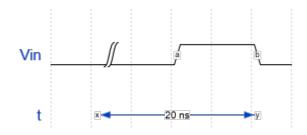

| Figure 5.3 Input Signal, slew rate of $0.03ns$                    |     |

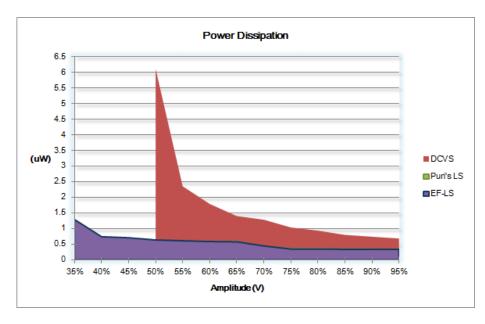

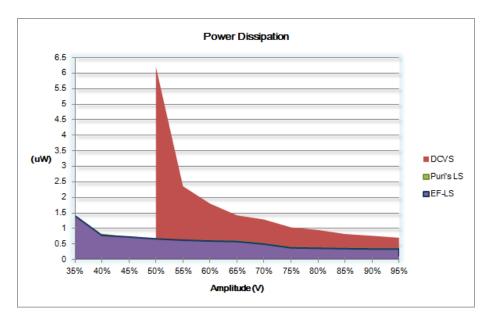

| Figure 5.4 Comparison of Power Dissipation                        |     |

| Figure 5.5 Mean Time Delay                                        |     |

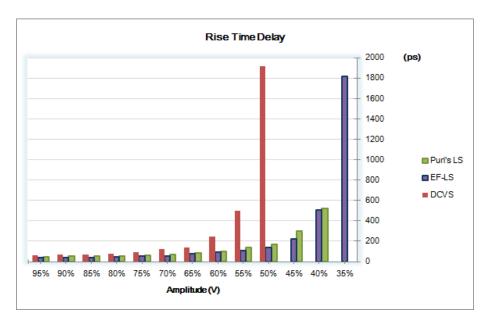

| Figure 5.6 Rise Time Delay                                        |     |

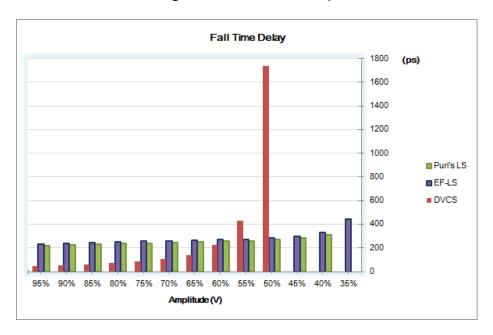

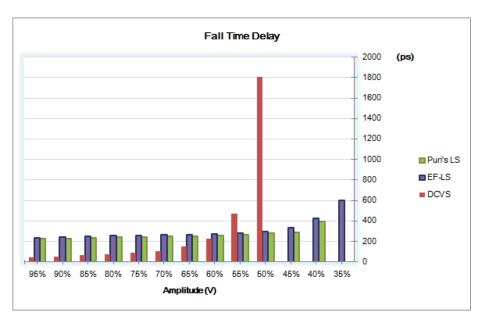

| Figure 5.7 Fall Time Delay                                        | 81  |

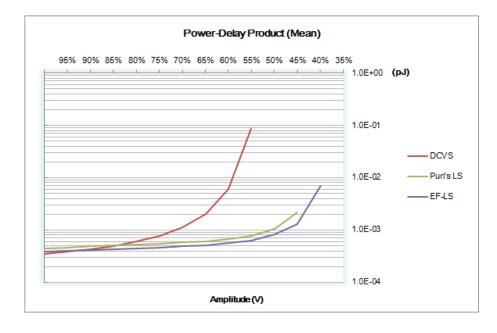

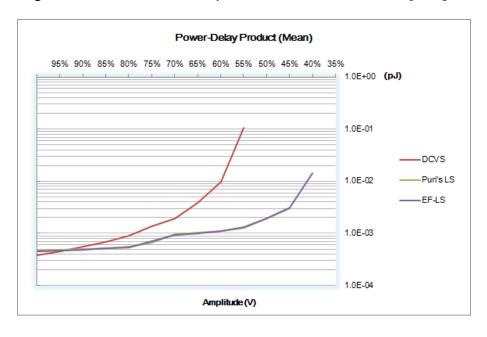

| Figure 5.8 1 | Mean Power-Delay Product                                     | 82   |

|--------------|--------------------------------------------------------------|------|

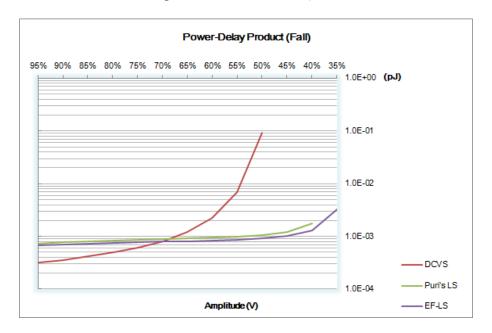

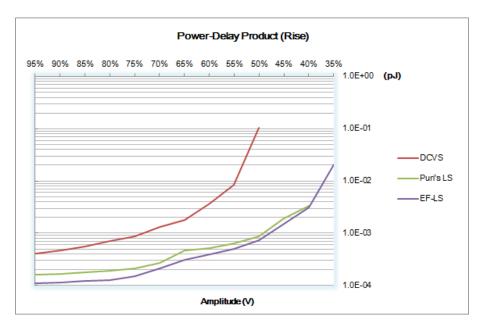

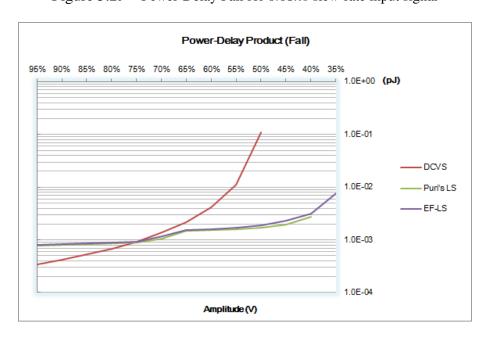

| Figure 5.9 I | Power-Delay Rise                                             | 83   |

| Figure 5.10  | Power-Delay Fall                                             | 83   |

| Figure 5.11  | DCVS's simulation scheme of Second Scenario                  | 84   |

| Figure 5.12  | Puri's simulation scheme of Second Scenario                  | 84   |

| Figure 5.13  | EF-LS's simulation scheme of Second Scenario                 | 85   |

| Figure 5.14  | Input Signal, slew rate of $0.3ns$                           | 85   |

| Figure 5.15  | Power Dissipation for 0.03ns slew-rate input signal          | . 86 |

| Figure 5.16  | Power Dissipation for $0.3ns$ slew-rate input signal         | 87   |

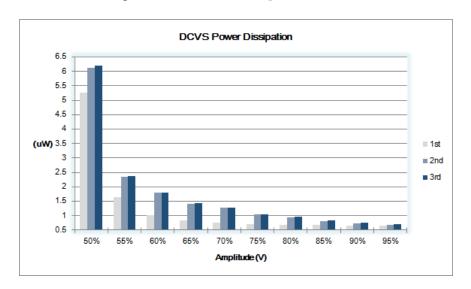

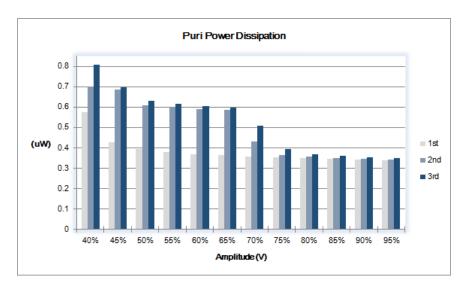

| Figure 5.17  | Power Dissipation of DCVS                                    | 87   |

| Figure 5.18  | Power Dissipation of Puri's level shifter                    | . 88 |

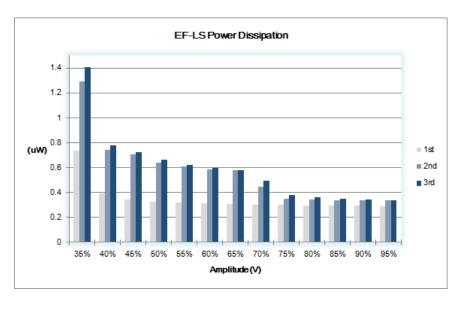

|              | Power Dissipation of proposed level shifter                  |      |

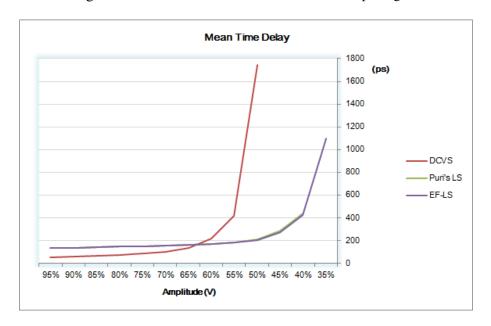

| Figure 5.20  | Mean time for 0.03ns slew-rate input signal                  | 89   |

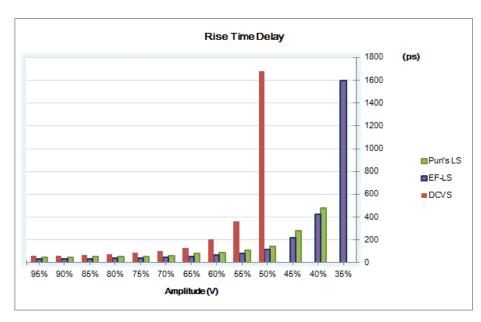

| Figure 5.21  | Rise Time Delay for 0.03ns slew-rate input signal            | 90   |

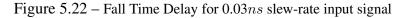

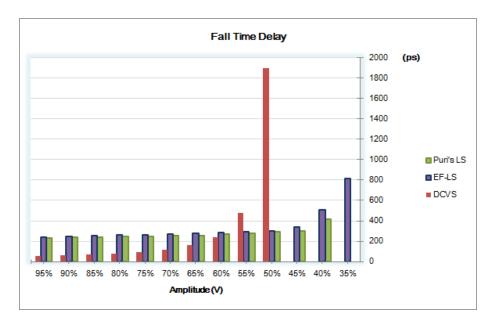

| Figure 5.22  | Fall Time Delay for 0.03ns slew-rate input signal            | . 90 |

| Figure 5.23  | Fall Time Delay for 0.3ns slew-rate input signal             | . 91 |

| _            | Rise Time Delay for 0.3ns slew-rate input signal             |      |

| Figure 5.25  | Mean Power-Delay Product for $0.03ns$ slew-rate input signal | 92   |

| Figure 5.26  | Mean Power-Delay Product for 0.3ns slew-rate input signal    | 93   |

| _            | Power-Delay Rise for $0.03ns$ slew-rate input signal         |      |

| Figure 5.28  | Power-Delay Rise for $0.3ns$ slew-rate input signal          | . 94 |

| _            | Power-Delay Fall for $0.03ns$ slew-rate input signal         |      |

| Figure 5.30  | Power-Delay Fall for 0.3ns slew-rate input signal            | 95   |

|              |                                                              |      |

# LIST OF TABLES

| Table 3.1 Comparison of power savings using CVS and GECVS versus the original de-           | 70    |

|---------------------------------------------------------------------------------------------|-------|

| sign with all gates being at $V_{DDH}$ and low $V_T$                                        | 50    |

| Table 3.2 Comparison of CVS, ECVS, and GECVS algorithms power savings. Backoff              |       |

| = 20%                                                                                       | 51    |

| Table 3.3 Comparison of CVS, ECVS, and GECVS algorithms power savings. Backoff              |       |

| = 10%                                                                                       | 52    |

| Table 4.1 Simulation results for the Half-latch level shifter under two operation condi-    |       |

| tions at 100MHz input.                                                                      | 67    |

| Table 4.2 Impact of DLS and SLS in the design of a multi-voltage system                     |       |

| rable 1.2 impact of DES and SES in the design of a mater votage system                      | 13    |

| Table A.1 Power dissipation of DCVS, Puri, and EF-LS level shifters for first simulation    |       |

| scenario                                                                                    |       |

| Table A.2 Time delays of DCVS, Puri, and EF-LS level shifters for first simulation scenario | o108  |

| Table A.3 Comparison chart of PDP for DCVS, Puri, and EF-LS level shifters in the first     |       |

| simulation scenario                                                                         | . 109 |

| Table A.4 Mean PDP of DCVS, Puri, and EF-LS level shifters for first simulation scenario    | o110  |

| Table A.5 Power dissipation of DCVS, Puri, and EF-LS level shifters for second simula-      |       |

| tion scenario                                                                               | . 111 |

| Table A.6 Time delays of DCVS, Puri, and EF-LS level shifters for second simulation         |       |

| scenario                                                                                    | . 112 |

| Table A.7 Comparison chart of PDP for DCVS, Puri, and EF-LS level shifters in the           |       |

| second simulation scenario                                                                  | . 113 |

| Table A.8 Mean PDP of DCVS, Puri, and EF-LS level shifters for second simulation            |       |

| scenario                                                                                    | . 114 |

| Table A.9 Power dissipation of DCVS, Puri, and EF-LS level shifters for second simula-      |       |

| tion scenario                                                                               | 115   |

| Table A.10 Time delays for DCVS, Puri, and EF-LS level shifters for second simulation       |       |

| scenario                                                                                    | 116   |

| Table A.11 Comparison chart of PDP for DCVS, Puri, and EF-LS level shifters in the          | , 110 |

| second simulation scenario                                                                  | 117   |

| Table A.12 Mean PDP of DCVS, Puri, and EF-LS level shifters for second simulation           | , 11/ |

| scenario                                                                                    | 110   |

| ochano                                                                                      | . 110 |

# **CONTENTS**

| 1 INTRODUCTION                                  | 13 |

|-------------------------------------------------|----|

| 1.1 Power, Energy, and Delay Basics             | 14 |

| 1.2 Dynamic Power Consumption                   | 15 |

| 1.3 Static Power Consumption                    | 17 |

| 1.4 Propagation Delay                           | 19 |

| 1.5 Main motivation                             | 20 |

| 2 LOW-POWER OPTIMIZATION STRATEGIES             | 22 |

| 2.1 Transistor-level Optimizations              | 22 |

| 2.1.1 Transistor Sizing                         | 22 |

| 2.1.2 Transistor Reorder                        | 27 |

| 2.2 Voltage Scaling                             | 28 |

| 2.2.1 Dynamic Voltage and Frequency Scaling     | 31 |

| 2.2.2 Adaptive Voltage Scaling                  | 33 |

| 2.3 Logic Optimizations                         | 34 |

| 2.3.1 Technology Mapping                        | 35 |

| 2.4 Power Gating                                | 35 |

| 2.5 Clock Gating                                | 38 |

| 2.6 Architecture-level Optimizations            | 39 |

| 2.6.1 Concurrency                               | 40 |

| 2.6.2 Pipelining                                | 41 |

| 3 MULTI-VOLTAGE DESIGNS                         | 43 |

| 3.1 Clustered Voltage Scaling                   | 45 |

| 3.2 Extended - Clustered Voltage Scaling        | 46 |

| 3.3 Greedy Extended - Clustered Voltage Scaling | 48 |

| 3.3.1 GECVS Optimization                        | 51 |

| 3.4 Multiple Dynamic Supply Voltage             | 54 |

| 3.4.1 Challenges in Multi-Voltage Designs       |    |

| 4 VOLTAGE SCALING INTERFACES - LEVEL SHIFTERS   |    |

| 4.1 High-to-Low Level Shifter                   | 58 |

| 4.2 Low-to-High Level Shifter                   | 59 |

| 4.3 Dual-rail Level Shifters                    | 60 |

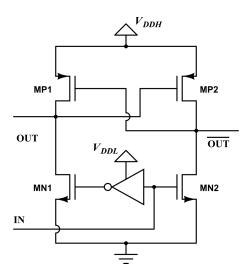

| 4.3.1 DCVS level shifter                        | 61 |

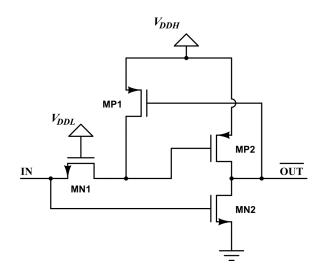

| 4.3.2 Bootstrapping level shifter               | 64 |

| 4.3.3 Feedback-based level shifters             | 66 |

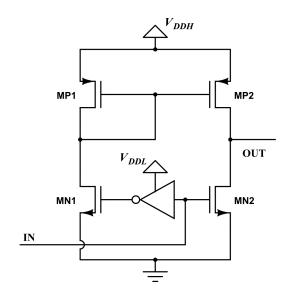

| 4.4 Single-rail Level Shifters                  | 69 |

| 4.4.1 Puri's level shifter                      |    |

| 4.4.2 Cross-coupled with single supply          | 71 |

| 4.5 DLS versus SLS                              |    |

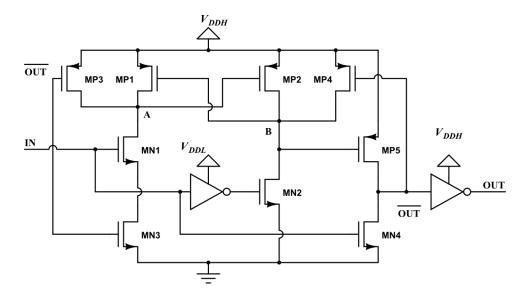

| 5 ENERGY-EFFICIENT LEVEL SHIFTER                | 75 |

| 5.1 Formal overview and characterization        | 76 |

| 5.1.1 Simulations and Results                   | 77 |

| 5.2 First Scenario                              | 77 |

| 5.2.1 Power Consumption                         |    |

| 5.2.2 Time Delays                               | 80 |

| 5.2.3 Power-Delay Product                       |    |

| 5.3 Second Scenario                             |    |

| 5.3.1 Power Consumption                         | 85 |

| 5.3.2 Time Delays                               |    |

| 5.3.3 Power-Delay Product | 92  |

|---------------------------|-----|

| 6 CONCLUSIONS             |     |

| REFERENCES.               |     |

| APPENDIX A — TABLES       |     |

| APPENDIX B — PUBLICATIONS | 119 |

#### 1 INTRODUCTION

The design of complex chips has undergone a series of revolutions. From the introduction of language-based design and synthesis to the adoption of design reuse and IP as a mainstream practice. Each of these revolutions was the response to the challenges posed by evolving semiconductor technology and by the need for more efficient Very-Large Scale Integration (VLSI) systems. In the past decade, energy and power consumption has become one of the primary concerns in sophisticated systems-on-chip (SoC) (RABAEY, 2009). For its impact and importance in VLSI designs, we can consider low power as the most recent design revolution.

As technology shrank to 90nm and below, the leakage current increased dramatically, to the point where, in some 65nm designs, leakage is nearly as large as dynamic current (KEAT-ING et al., 2007). These changes reflect on how we conceive the integrated circuits. For example, the power density of the highest performance chips grew to the point where it was no longer possible to increase clock speed as technology advanced. Subsequently, multi-processor chips emerged as an option instead of chips with a single, ultra-high speed processor (OLUKOTUN et al., 1996).

The continuous transistor downsizing has also empowered the development of portable devices. By using eight or more CPU cores, current smartphones match the computational capabilities of basic desktop computers and laptops. Despite its computing performance, a smartphone is a battery-powered system. Where, the available energy is fixed, and the rate of power consumption determines the lifetime of the battery or the time between recharges. It means that the energy supply is finite, and hence energy minimization is critical.

Rabaey (2009) showed that the battery capacity doubles approximately every ten years. Although this represents an improvement of 3 to 7% every year, the growth curve lags substantially behind Moore's law. This disparate evolution could be explained by the fact that the improvements in capacity are often related to new chemicals or electrode materials. Capacity and size limitations of batteries push further the energy savings of battery-powered devices.

Smartphones are just one example of devices with limited power supply, which require low energy consumption. For a vast number of designs, low power is the hardest constraint or the central objective. Wearable devices, bioengineering, sensor networks, among others, are application areas that may require conscious low-power design. The technology scaling may help to address some of the power issues. Nevertheless, design solutions will be the primary mechanisms for keeping energy consumption under control or within bounds.

In today's design environment, optimizing for only one parameter (delay or energy) rarely makes sense. The design with the minimum propagation delay in general takes an exorbitant amount of energy, and, vice versa, the design with the minimum energy is unacceptably slow. Both represent extremes in an optimization space, where many other optimal operational points and metrics exist. Typically, one metric receives greater weight; for instance, energy reduces for a given maximum delay or delay is minimized for a given maximum energy.

### 1.1 Power, Energy, and Delay Basics

Energy and Power terms are almost used indistinctly, but they have particular definitions despite the direct relation between each one. Energy is the product of power and time, in other words, it is power integrated over time. We can measure power at any point in time, whereas energy has to be measured during a period. Figure 1.1 illustrates better the difference between both. Energy is the area under the curve, and Power is the height of the graph (KEATING et al., 2007).

Power is height of the curve

Lower power could just be slower

Approach 1

Approach 2

time

Two approaches require the same Energy

Approach 1

Approach 2

time

Figure 1.1 – Power Vs Energy

Source: (KEATING et al., 2007)

The power consumption of a design determines how much energy it spends per operation, and how much heat the circuit dissipates. These factors influence a number of critical design decisions, such as the power-supply capacity, the battery lifetime, packaging and cooling requirements. Therefore, power dissipation is an important property of a VLSI design that affects the feasibility, cost, and reliability. With the increasing popularity of mobile and distributed computation, energy limitations put a firm restriction on the number of computations

at a given minimum time between battery recharges.

Power dissipation can be decomposed into static and dynamic components. The latter occurs only during transients when the gate is switching. It is attributed to the charging of capacitors and temporary current paths between the supply rails, and it is, therefore, proportional to the switching frequency. The higher the number of switching events, the higher the dynamic power consumption (RABAEY, 2009).

The charging and discharging of capacitances are the main sources of dynamic power dissipation. Other contributions are the parasitic effects of short-circuit currents and dynamic hazards or glitches. On the other hand, the static component is present even when no switching occurs. Static conductive paths between the supply rails or leakage currents are the main reasons for the static power consumption. It is always present, even when the circuit is in stand-by mode.

The propagation delay and the power consumption of a gate are related, the propagation delay is mostly determined by the speed at which a given amount of energy can be stored on the gate capacitors. The faster the energy transfer (or, the higher the power consumption), the faster the gate (RABAEY, 2009). The product of power consumption and propagation delay is generally constant. This product is the *Power-Delay Product* (PDP) and represents the energy consumed by the gate per switching event.

## **1.2 Dynamic Power Consumption**

Switching power consumption occurs when logic switches from *low-to-high* (and vice versa) and capacitances are charged and discharged. In summary, each switching cycle (consisting of a *low-to-high* and a *high-to-low* transition) takes a fixed amount of energy (RABAEY; CHANDRAKASAN; NIKOLIC, 2003). This being equal to  $C_L V_{DD}^2$ .

The switching power consumption can be described as a function of the energy spent per transition at a specific clock frequency. Equation (1.1) represents the dynamic power consumption when a gate is switched on and off  $f_{0\to 1}$  times.  $C_L$  is the load capacitance and  $V_{DD}$  the supply voltage.

$$P_{dyn} = C_L V_{DD}^2 f_{0 \to 1} \tag{1.1}$$

f represents the frequency of energy-consuming transitions for static Complementary

Metal-Oxide Semiconductor (CMOS)

Computing the dissipation of a complex circuit is complicated by the  $f_{0\to 1}$  factor. While

the switching activity is easily computed for an inverter, it turns out to be far more complex in the case of higher-order gates. From equation 1.1, we derive the expression 1.2, where f is the clock frequency, and  $\alpha$  is the switching activity.

$$P_{dyn} = \alpha C_L V_{DD}^2 f \tag{1.2}$$

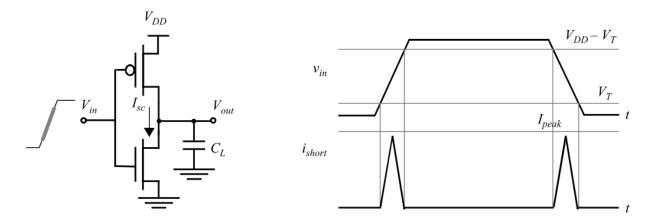

The switching activity is increased by glitches, which typically cause 15% to 20% of the activity in complementary static CMOS logic (CHINNERY; KEUTZER, 2007). In addition, short circuit power consists of the current that flows when both the NMOS and PMOS transistors of the CMOS inverter are on (Figure 1.2). As well as the current required to charge the internal capacitance (KEATING et al., 2007). This current creates temporary direct-path connecting  $V_{DD}$  and ground. Equation (1.3) estimates the short circuit current of an inverter without external load (CHINNERY; KEUTZER, 2007).

$$I_{sc} = c\mu \frac{\epsilon_{ox}}{t_{ox}} \frac{W}{L_{eff}} \frac{1}{V_{DD}} (V_{DD} - 2V_T)^3 s_{in}$$

(1.3)

c is a process-determined constant defined in (VEENDRICK, 1984);  $s_{in}$  is the input slew

Figure 1.2 – Short-circuit current during transients

Source: (RABAEY; CHANDRAKASAN; NIKOLIC, 2003)

If the rising and falling responses of the inverter are symmetric, the energy consumed per switching period due to direct-paths currents is (RABAEY; CHANDRAKASAN; NIKOLIC, 2003):

$$E_{dp} = V_{DD} \frac{I_{peak} t_{sc}}{2} + V_{DD} \frac{I_{peak} t_{sc}}{2} = t_{sc} V_{DD} I_{peak}$$

$$\tag{1.4}$$

Where  $t_{sc}$  is the duration of the short circuit current, and  $I_{peak}$  is the total internal switching current (short circuit current plus the current required to charge the internal capacitance) (KEATING et al., 2007). The peak current is also a function of the ratio between input and output slopes (RABAEY; CHANDRAKASAN; NIKOLIC, 2003). The direct-path power dissipation is proportional to the switching activity, similar to the capacitive power dissipation. From equation (1.4), we obtain the average power consumption during short-circuit events (RABAEY; CHANDRAKASAN; NIKOLIC, 2003):

$$P_{dp} = t_{sc} V_{DD} I_{neak} f = C_{sc} V_{DD}^2 f (1.5)$$

As long as the ramp time of the input signal is short, the short circuit current occurs for only a short time during each transition and the overall dynamic power is dominated by the switching power. Mainly because when the load capacitance is vast, the output fall time is significantly larger than the input rise time. Under those circumstances, the input moves through the transient region before the output starts to change. As the source-drain voltage of the PMOS device is approximately zero during that period, the device shuts off without ever delivering any current (RABAEY; CHANDRAKASAN; NIKOLIC, 2003). For this reason, the dynamic power is often reduced to the expression (1.2). Moreover, short-circuit power typically contributes less than 10% of the total dynamic power and increases with the escalation of  $V_{DD}$ , and with decreasing  $V_T$  (CHINNERY; KEUTZER, 2007).

### 1.3 Static Power Consumption

The current that flows between the supply rails in the absence of switching activity causes the Static power consumption. In equation (1.6),  $I_{stat}$  is ideally equal to zero, because PMOS and NMOS transistors of the CMOS inverter are never *on* simultaneously during static operation (RABAEY; CHANDRAKASAN; NIKOLIC, 2003).

$$P_{stat} = I_{stat} V_{DD} (1.6)$$

From a digital perspective, an ideal MOS transistor should not have any currents flowing into the bulk, should not conduct any current between drain and source when off, and should have an infinite gate resistance (RABAEY, 2009). Actually, there is a small leakage current that contribute to static power dissipation (Figure 1.3). According to (KEATING et al., 2007), the four main sources of leakage current are:

- Subthreshold Leakage  $(I_{SUB})$ : the current that flows from the drain to the source of a transistor operating in the weak inversion region.

- Gate Leakage ( $I_{GATE}$ ): it flows directly from the gate and occurs as a result of tunneling current through the gate oxide.

- Gate-Induced Drain Leakage ( $I_{GIDL}$ ): flows from the drain to the substrate induced by a high field effect in the MOSFET drain caused by a high  $V_{DG}$ .

- Reverse Bias Junction Leakage ( $I_{REV}$ ): caused by minority carrier drift and generation of electron/hole pairs in the depletion regions.

VDD

Vout = VDD

Vout = VDD

Drain Leakage Current

Subthreshold Current

Figure 1.3 – Source of leakage currents in CMOS inverter

Source: Author

In deep submicron process with low threshold voltages, the dominant sources of leakage power are subthreshold leakage and gate leakage. Expression (1.7) shows an analytical model for the subthreshold leakage current (KESHAVARZI; KAO, 2002).

$$I_{SUB} = e^{1.8} \mu \frac{\epsilon_{ox}}{t_{ox}} \frac{W}{L_{eff}} \left[ \frac{kT}{q} \right]^2 e^{q \frac{(V_{GS} - V_{TO} - \gamma V_b + \eta V_{DS})}{mkT}} (1 - e^{-\frac{qV_{DS}}{kT}})$$

(1.7)

Where k is the Boltzmann's constant; q is the charge of an electron; T is the temperature in Kelvins;  $V_{T0}$  is the zero-bias threshold voltage;  $V_b$  is the body bias voltage;  $\gamma$  is the linearized body effect coefficient; m is the subthreshold swing coefficient, and  $\eta$  is the Drain Induced Barrier Lowering (DIBL) coefficient. Keating (2007) shows a good approximation of (1.7):

$$I_{SUB} = \mu C_{ox} \frac{W}{L} \left[ \frac{kT}{q} \right]^2 e^{\left[ \frac{V_{GS} - V_T}{n \left( \frac{kT}{q} \right)} \right]}$$

(1.8)

Where (kT/q) is the thermal voltage (25.9mV) at room temperature and n is a function

of the device fabrication process with ranges from 1.0 to 2.5. Equation (1.8) shows that the subthreshold leakage increases exponentially as the threshold voltage reduces. Furthermore, it increases linearly with gate size (W) and with the supply voltage. Therefore, as  $V_{DD}$  and  $V_{T}$  scale down (to limit dynamic power), leakage power gets proportionally worse.

Gate leakage occurs because of the tunneling current through the gate oxide. A high electric field across the thin transistor gate oxide originates an electrons flow. The gate leakage can be modeled as shown in (1.9) (CHINNERY; KEUTZER, 2007), where a, b, and c are constants defined in the BSIM4 model.

$$I_{GATE} = aL_{eff}e^{\left(bV_{GS} - ct_{ox}^{-2.5}\right)} + aL_{eff}e^{\left(bV_{GD} - ct_{ox}^{-2.5}\right)}$$

(1.9)

In previous technology nodes, subthreshold leakage dominated leakage current. However, starting with 90nm, gate leakage can be nearly 1/3 as much as subthreshold leakage (KEATING et al., 2007). There are several approaches to minimizing leakage current. One technique, known as Multi- $V_T$ , uses high  $V_T$  cells wherever performance goals allow, and low  $V_T$  where necessary to meet timing constraints.

### 1.4 Propagation Delay

The propagation delay is defined by the time between the 50% transitions of the input and the output. For the CMOS inverter, the propagation delay is the time it takes to charge and discharge the load capacitor ( $C_L$ ) through the PMOS and NMOS transistors. A single inverter can theoretically drive an infinite number of gates (or have a vast fan-out); however, increasing the fan-out also increases the propagation delay. Therefore, a small load capacitor or reduced fan-out improves the propagation delay, enabling the realization of high-performance CMOS circuits.

One way to compute this delay is by integrating the capacitor current (RABAEY; CHAN-DRAKASAN; NIKOLIC, 2003). It results in the following expression, where i is the discharging current, v the voltage over the capacitor, and  $v_1$  and  $v_2$  the initial and final voltage:

$$t_p = \int_{v_1}^{v_2} \frac{C_L(v)}{i(v)} dv \tag{1.10}$$

An exact computation of this equation is impractical, as both  $C_L(v)$  and i(v) are non-linear functions of v. We rather use a simplified switch-model of the inverter to derive the propagation delay from the analysis of a first-order linear RC-network (RABAEY; CHAN-

DRAKASAN; NIKOLIC, 2003). Where the delay is proportional to the time-constant of the network, formed by a pull-down resistor and load capacitance. Hence, the propagation delay for the *high-to-low* transition becomes:

$$t_{pHL} = \ln(2)R_{ean}C_L = 0.69R_{ean}C_L \tag{1.11}$$

Similarly, we can obtain the propagation delay for the *low-to-high* transition,

$$t_{pLH} = 0.69 R_{eqp} C_L (1.12)$$

On (1.11) and (1.12),  $R_{eqn}$  and  $R_{eqp}$  are the equivalent on-resistance of the MOS transistor over the interval of interest. This analysis assumes that the equivalent load-capacitance is identical for both the high-to-low and low-to-high transitions. Then, the overall propagation delay of the inverter becomes the average of the two values.

$$t_p = \frac{t_{pHL} + t_{pLH}}{2} = 0.69C_L \left(\frac{R_{eqn} + R_{eqp}}{2}\right)$$

(1.13)

#### 1.5 Main motivation

The total power consumption of a SoC consists of dynamic power and static power. As explained before, dynamic power is mainly present when the device is active or in switching activity, and the static power represents the energy consumed when the device is inactive or in standby mode. There is a broad range of approaches for optimizing both components of power consumption. From systems with multiple voltages to power-awareness designs, and, at a lower abstraction level, transistor sizing and supply voltage scaling enable a grainy control of the circuit's consumption.

Optimizations at the architecture or system level can enable more effective power minimization and maintain performance at the same time. While circuit techniques may yield improvements in the 10-50% range, architecture and algorithm optimizations have reported greatest power reduction (RABAEY, 2009). Among the latter, we can mention designs that employ multiple voltages to optimize the power consumption.

Those multi-voltage designs exploit the concept of voltage scaling by applying different supplies to specific regions of the chip. Each region belongs to a power domain and may have two or more supply voltage configurations. Regardless of distinct energy levels on differ-

ent power domains, the blocks shall process signals with coherent logic levels. When driving signals between power domains with radically different power rails, the need for level converters is essential. These voltage scaling interfaces (also referred as *Level Shifters*) are located at the power domain boundaries, and they must ensure the correct communication between two regions. Therefore, the design and implementation of level shifters should be a conscientious process and must guarantee the lowest overhead in size, energy consumption, and delay time. Thus, the main motivation of this research is to study and to identify the best level shifter topologies for low power consumption and reduced area, as well as to propose a novel approach.

The following chapter describes some of the most common techniques to reduce the power consumption of SoC designs. Among them, Multi-Voltage approaches are versatile solutions that present considerable energy savings and are widely used in modern designs. Chapter 3 presents the basic Multi-Voltage techniques we found in the literature and explains some of their challenges, including the need for Level Shifters (LS). The reader can find more information about these voltage scaling interfaces in Chapter 4 of this document, which also summarizes the *state-of-the-art* Level Shifters. After analyzing the approaches with the best results, we introduce a novel topology of Level Shifter with low power consumption. The proposed circuit and its effects can be observed in Chapter 5 and subsequent section. Finally, our final considerations and future prospects conclude this work.

#### 2 LOW-POWER OPTIMIZATION STRATEGIES

Designers dispose of several approaches to minimize the impact of the switching activity or leakage current of CMOS digital circuits. In a custom VLSI project, they can implement low-power optimizations almost at every step of the design process. From a *bottom-up* view, the most common techniques for optimizing power are: transistor-level optimizations; voltage scaling; clock gating; power-gating; logical optimizations; and architecture-level optimizations. An ideal design methodology employs low power techniques in all abstraction levels to obtain better results. The gain at each level contributes to greater energy savings.

### 2.1 Transistor-level Optimizations

Custom techniques used to achieve high-speed on designs may also be employed to reach low power constraints (THOMPSON et al., 2001). Designers can optimize the individual logic cells, the layout, the wiring between cells, and other aspects of the design as the number of transistors, their size and positions. A reduction in the number of transistors can impact both, static and dynamic power consumption. In (SCARTEZZINI; REIS, 2011), authors achieved better results in terms of power and delay, when using networks with reduced number of transistors instead of commercial standard cells.

## 2.1.1 Transistor Sizing

In some custom designs, engineers have the option to enlarge or reduce the width of the transistors channel to target the short-circuit power. Transistor Sizing is a useful technique to lessen the delay of a CMOS circuit. When the width of the channel enlarges, the current drive capability of the transistor increases, which reduces the signal rise/fall times at the gate output.

Transistor sizing technique becomes a trade-off between speed and power dissipation because varying the channel width affects both power and delay. On equation (2.1), if we increase the width (W), the resistance decreases allowing more current to flow through the transistor. This may reduce the delay of the transistor but augments the energy consumption instead.

$$R_n = \frac{1}{\mu C_{ox} \left( V_{GS} - V_T \right) 2} \left( \frac{L}{W} \right) \tag{2.1}$$

By changing W, we can control the gain factor of a CMOS inverter. Equation (2.2) represents the maximum short-circuit dissipation under *no-load* condition at the output of the inverter (VEENDRICK, 1984). Where  $\tau$  is the input transition time and  $\beta$  is the gain factor of the transistor.

$$P_{sc} = \frac{\tau \beta}{12} (V_{DD} - 2V_T)^3 f \tag{2.2}$$

On equation (2.2), the gain factor of the gate  $(\beta)$  is determined by the width of the transistor (W) and the mobility of the carriers responsible for the transition  $(\mu_p)$  for a low-to-high transition and  $\mu_n$  for a high-to-low transition). Expression (2.2) further reduces to (2.3), where k is a process and voltage dependent constant of proportionality. It clearly shows that the short-circuit power  $(P_{sc})$  consumption is directly proportional to both width of the transistor and the input transition time.

$$P_{sc} = k\mu W \tau f \tag{2.3}$$

Borah, Owens, and Irwin (1996) presented an analytical derivation of the optimum value of W under high fan-out condition. They also showed a nonlinear (U-shape) curve representing transistor size versus average power dissipation. The U-shape curve indicates that there is an optimum point to design the channel width. A large channel width may increase the driving current but reduce the transition time, thus reducing the short-circuit power. Over-sizing the transistors beyond the optimal value comes at a hefty price in energy. On the other hand, a small channel width could decrease the driving current but result in a longer transition time, thus increasing the short-circuit power (YUAN; DI, 2005).

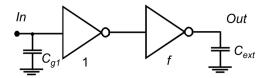

Figure 2.1 shows a static CMOS inverter driving an external capacitance ( $C_{ext}$ ) and a minimum-sized device drives the inverter. The goal here is to minimize the energy dissipation of the complete circuit while maintaining the performance (RABAEY; CHANDRAKASAN; NIKOLIC, 2003). The propagation delay of the optimized circuit should be smaller or equal to the delay of a reference circuit, with size factor f = 1 and supply voltage  $V_{DD} = V_{ref}$ .

Figure 2.1 – CMOS inverter driving an external load

Source: (RABAEY; CHANDRAKASAN; NIKOLIC, 2003)

Expression (2.4) represents the propagation delay of the circuit. With (effective fan-out)  $F = (C_{ext}C_{g1})$ , the intrinsic delay of the inverter is the overall effective fan-out of the circuit  $t_{p0}$ .

$$t_p = t_{p0} \left[ \left( 1 + \frac{f}{\gamma} \right) + \left( 1 + \frac{F}{f\gamma} \right) \right] \tag{2.4}$$

The energy dissipation for a single transition at the input of the circuit can be determined by:

$$E = V_{DD}^{2} C_{a1} \left[ (1 + \gamma) (1 + f) + F \right]$$

(2.5)

If the intrinsic output capacitance of the gate equals its gate capacitance ( $\gamma=1$ ), we have the following relation:

$$\frac{t_p}{t_{p_{ref}}} = \frac{t_{p0} \left(2 + f + \frac{F}{f}\right)}{t_{p0_{ref}} \left(3 + F\right)} = \left(\frac{V_{DD}}{V_{ref}}\right) \left(\frac{V_{ref} - V_{TE}}{V_{DD} - V_{TE}}\right) \left[\frac{2 + f + \frac{F}{f}}{3 + F}\right]$$

(2.6)

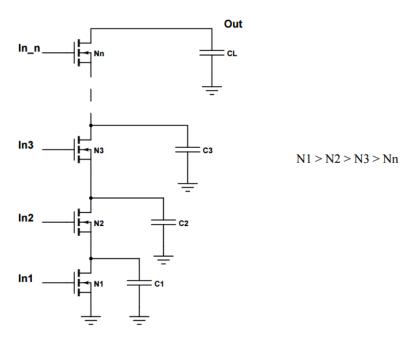

The previous equation establishes a relationship between the sizing factor f and the supply voltage. Figure 2.2 plots this correlation for different values of f. It shows that increasing the size of the inverter rises the performance until the sizing factor of  $f = \sqrt{F}$  is reached. Further increases in the device size only intensify the self-loading factor, deteriorate the performance, and require an escalation in supply voltage. Therefore, over-sizing the transistors beyond the optimal value comes at a hefty price in energy.

Earlier approaches for transistor sizing concentrated on minimizing the area of the circuit subject to a particular delay constraint. Those methods were based on the assumption that the power consumption of a circuit was proportional to the active area (HOPPE et al., 1990; SAPATNEKAR et al., 1993). Later studies revealed that the power consumption of a CMOS circuit does not always reduce by minimizing the active area; but it can be improved by enlarging some of the transistors that drive large active loads (BORAH; IRWIN; OWENS, 1995; KO; BALSARA, 1995). In contrast to the existing assumption at the time; Borah, Owens, and Irwin (1996) showed that the power consumption of a circuit is a convex function of the area. They presented an analytical model based on the analysis of short-circuit power consumption by Veendrick (1984) and the gate delay model of Hedenstierna and Jeppson (1987). In which,

Figure 2.2 – Sizing of a CMOS inverter for energy-minimization

Supply voltage as a function of the sizing factor f for different values of the overall effective fan-out F

Source: (RABAEY; CHANDRAKASAN; NIKOLIC, 2003)

the curve of average power consumption versus transistors size attains a minimum when:

$$W_1^* = \frac{\sqrt{\phi \frac{\mu'}{\mu} C_L \left(\sum_{i=2}^n W_i f_i\right)}}{\sqrt{\left(\frac{k_1}{k} + \mu \tau\right) f_1}}$$

(2.7)

In (2.7),  $W_1^*$  is the *power optimal size* for the transistor driving various gates (first inverter on Figure 2.1). By substituting  $\mu_p$  for  $\mu$  and  $\mu_n$  for  $\mu'$ , we obtain the optimal size of the *p-channel* transistor. The optimal *n-channel* transistor size can be obtained by substituting  $\mu_n$  and  $\mu_p$ , respectively. This approach can be used in the situation where each transistor is scaled up uniformly.

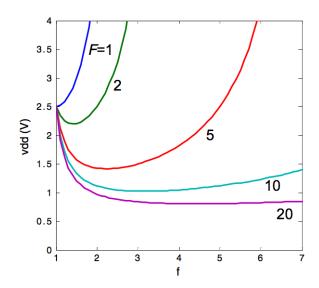

In complex CMOS gates, the best method to scale the transistors is by progressive upsizing them. Basically, progressive transistor sizing approach reduces the transistor resistance while reducing capacitance (RABAEY; CHANDRAKASAN; NIKOLIC, 2003). Figure 2.3 shows an example of progressive sizing of transistors in a large transistor chains, each one driving a corresponding external load.

The delay of a chain of N transistors of width W is less than n times the delay of a single inverter of width W is given by (2.8) (BORAH; OWENS; IRWIN, 1996).

$$\frac{t_p N_{transistors}}{t_p inverter} = 1 + \varsigma (n - 1)$$

(2.8)

Taking into account the fact that the total gate capacitance of the driver is proportional

to N \* W, we have in (2.9) the power-optimal size of a transistor in a gate with N serially connected transistors (BORAH; OWENS; IRWIN, 1996).

$$W_N^* = \frac{\sqrt{\phi \frac{\mu'}{\mu} \left[1 + \varsigma \left(n - 1\right)\right] C_L \left(\sum_{i=2}^n W_i f_i\right)}}{\sqrt{\left[\frac{k_1 N}{k} + \frac{\mu \tau}{1 + \varsigma (n - 1)}\right] f_1}}$$

(2.9)

Figure 2.3 – Progressive sizing of transistors of a n-input gate

Source: Author

After the recents *International Symposium on Physical Design* (ISPD) contests, power-driven gate sizing has aroused lot of interest. Since then, plenty of research papers have been published and new algorithms were proposed based on the ISPD 2013 contest formulation. (REIMANN; SZE; REIS, 2015) presented an approach to integrate a state-of-the-art *Lagrangian Relaxation*-based gate sizing method (FLACH et al., 2014) into a physical synthesis framework. Their sizing method achieved the first place in the *ISPD 2013 Discrete Gate Sizing Contest* with, on average, 8.78% better power results than the second place tool. This flow was also the first gate sizing method to report violation-free solutions for all benchmarks of the ISPD 2013 Contest.

#### 2.1.2 Transistor Reorder

Often implemented together with Transistor Sizing, Transistor Reorder mainly targets on the capacitive switching power  $(P_{dyn})$  of the transistors. "The fundamental idea of transistor reordering is to achieve lower switching power by adjusting the order of the transistors in a serial-connected CMOS chain, based on the behaviors of different inputs." (YUAN; DI, 2005).

Serially connected transistors are widely used to implement NAND/NOR gates, various complex gates, and PLA's in VLSI logic design. The preponderance of these structures in CMOS circuits produces a significant source of power dissipation. Mainly because the transition times at internal nodes are strongly dependent on the input signal characteristics and input positions. Therefore, a misguided transistor placement may increase the spurious transitions at internal nodes and result in extra power consumption. The goal of transistor reordering is to reduce the propagation delay as well as the charging and discharging of internal capacitances to achieve low power consumption.

The same input sequence could cause different power dissipation while applied to different orders of transistor chains. To determine the appropriate transistor order, we must have some information about inputs. First, one must determine the percentage of time that the specific input stays in a logic high and then determine how often this input makes a transition. Since the exact data of actual inputs is unknown beforehand, only probabilistic information is available (YUAN; DI, 2005). We can use signal probability and transition density to decide the order of transistors (SHEN; LIN; WANG, 1995; VEENDRICK, 1984). Expression (2.10) defines the signal probability; where  $p_i$  is the signal probability of input  $x_i$ , S is the total number of time slots during one clock cycle, and  $x_i(k)$  is the value of  $x_i$  during the interval of time instances k and k+1.

$$p_i = \lim_{n \to \infty} \frac{\sum_{k=1}^{n \times S} x_i(k)}{n \times S}$$

(2.10)

Equation (2.11) shows the transition density  $D_i$  for an input  $x_i$ .

$$D_{i} = \lim_{n \to \infty} \frac{\sum_{k=1}^{n \times S} \left[ x_{i}(k) \overline{x_{i}(k+1)} + \overline{x_{i}(k)} x_{i}(k+1) \right]}{n \times S}$$

(2.11)

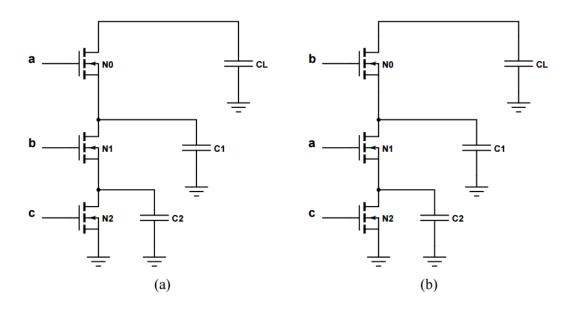

Figure 2.4 shows two alternate implementations of a three-input NAND gate. In both cases, node  $N_0$  is the output of the gate, with two other internal nodes  $N_1$  and  $N_2$ . On Figure 2.4 (a), if a vector "110" followed by "011" is applied to the inputs in alphabetic order, and all three inputs arrive simultaneously. The sequence causes the capacitances  $C_L$ ,  $C_1$  and  $C_2$  to be

initially charged and then the capacitances  $C_1$ , and  $C_2$  are discharged; whereas only capacitance  $C_2$  in Figure 2.4 (b) discharges.

Figure 2.4 – Example of transistor reordering

Original three-input NAND gate (a). Gate with transistors reordered (b).

Source: Author

## 2.2 Voltage Scaling

Up to the mid-1990s, the standard supply voltage for all digital components was five volts, and a fixed-voltage scaling model was the norm. Back then, fixed-voltage scaling was an attractive proposition because it simplified the interfacing between different components (RABAEY, 2009). Around 1995, supply voltages dropped for the first time to 3.3V with the advent of  $0.35\mu$ m technology. It dates the beginning of supply voltage scaling in correspondence with successive process nodes. On equation (1.2) is clear that the dynamic power is quadratically proportional to the supply voltage. Thus, despite the intrinsic increase in the delay, the supply voltage reduction is one of the most efficient ways to reduce power dissipation. Therefore, the scaling-down of the supply voltages has been kept until recent technology nodes. The *International Roadmap for Semiconductors* (low-power scenario) (ITRS, 2013) projects that the voltage will be reduced to 0.5V and then saturates. This may occur in the forthcoming years, when the transistors downscaling surpasses the 7nm of gate length.

Scaling down the supply voltage requires a commensurate reduction in clock frequency

because signal propagation delays increase when the supply voltage reduces. The maximum clock frequency at which a transistor can operate is proportional to  $[(V_{DD} - V_T)^{\alpha}]/(V_{DD})$ , where  $V_T$  is the transistor threshold voltage and  $\alpha$  is strongly dependent on the mobility degradation of the electrons (LI et al., 2005).

In Figure 2.5, if we move the curve to the left, the performance penalty for lowering voltage reduces. One way to address the delay problem of reduced supply voltage is by using low  $V_T$  cells or by combining cells with different  $V_{DD}$ . Moreover, dual  $V_{DD}$  (BENINI; DEMICHELI, 1998; CHANDRAKASAN; SHENG; BRODERSEN, 1992) and dual  $V_T$  (ATHAS, 1999; MERMET, 1997) techniques have been proposed. Thus, it is possible to reduce power while meeting delay constraints by using high  $V_{DD}$  with low  $V_T$  on delay critical paths, and low  $V_{DD}$  with high  $V_T$  where there is sufficient timing slack.

As supply voltage scales down, the subthreshold leakage and the leakage due to Drain Induced Barrier Lowering (DIBL) also decreases (RABAEY, 2009). The main reason for these undesired effects is the scaling of the supply voltage while keeping the threshold voltage constant. One way to address this performance issue is to scale the device threshold as well.

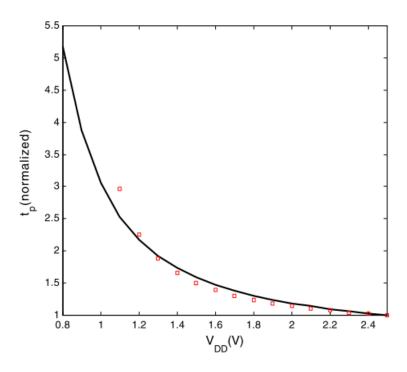

Figure 2.5 – Propagation delay of a CMOS inverter

Propagation delay as a function of supply voltage (normalized with respect to the delay at 2.5 V).

Source: (RABAEY; CHANDRAKASAN; NIKOLIC, 2003)

In a CMOS inverter, the propagation delay also reduces with the decrement of the threshold voltage. Gonzalez, Gordon, and Horowitz (1997) showed that this propagation delay is

inversely proportional to  $(V_{DD} - V_T)$ . The dominant sources of leakage in deep-submicron process technologies with low threshold voltages are subthreshold leakage (Figure 2.6) and gate leakage. This additional leakage power dissipation reduced the benefits of supply voltage scaling.

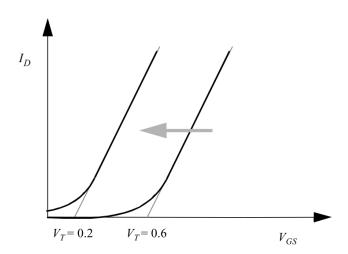

Figure 2.6 – Subthreshold leakage

Decreasing the threshold voltage increases the subthreshold current at  $V_{GS} = 0$ .

Source: (RABAEY; CHANDRAKASAN; NIKOLIC, 2003)

The issue with lowering  $V_{DD}$  is that it tends to reduce  $I_{DS}$  as well, resulting in slower speeds. If we ignore velocity saturation and some of the other subtle effects that occur below 90nm, the  $I_{DS}$  for a MOSFET can be approximated by expression (2.12).

$$I_{DS} = \mu C_{ox} \frac{W}{L} \frac{(V_{GS} - V_T)^2}{2}$$

(2.12)

Several practical approaches have been proposed to minimize the effect of leakage current (ABDOLLAHI; FALLAH; PEDRAM, 2004; NARENDRA; CHANDRAKASAN, 2006; ROY; MUKHOPADHYAY; MAHMOODI-MEIMAND, 2003). On custom VLSI chip design, for example, high- $V_T$  (slow) transistors are used to minimize the leakage current, they must be located on logical paths with enough positive slack. While low- $V_T$  (fast) transistors increase the driving current and speed on critical paths. By combining supply voltage scaling optimizations and cells with different threshold voltages, we can control leakage, reduce delay and achieve significant power savings. From a design perspective, on (KEATING et al., 2007), the authors cite four different approaches for voltage scaling:

• Static Voltage Scaling (SVS): where different blocks or subsystems receive fixed supply

voltages.

- Multi-level Voltage Scaling (MVS): an extension of the static voltage scaling case where a block or subsystem is switched between two or more voltage levels. Only a few, fixed, discrete levels are supported for different operating modes.

- Dynamic Voltage and Frequency Scaling (DVFS): is considered as an extension of MVS where a larger number of voltage levels dynamically switches to follow changing workloads.

- Adaptive Voltage Scaling (AVS): an extension of DVFS where a control loop is used to adjust the voltage.

DVFS and AVS are two of the most commonly used approaches for dynamic power optimization we found in literature (BURD; BRODERSEN, 2000; BURD et al., 2000; POUWELSE; LANGENDOEN; SIPS, 2001; ZHAI et al., 2004; ELGEBALY; SACHDEV, 2007; DHAR; MAKSIRNOVI; KRANZEN, 2002; GUPTA et al., 2008). These techniques obtain the best results for voltage-frequency tradeoff.

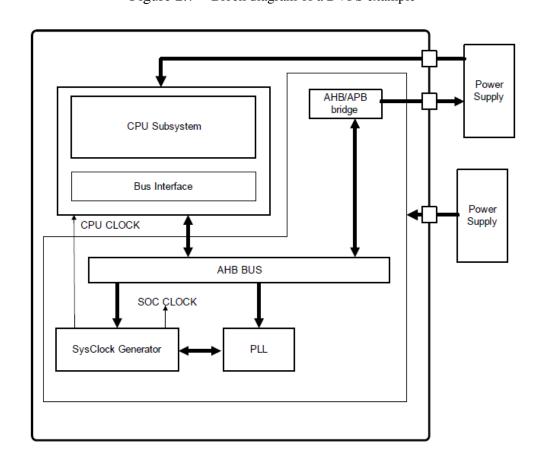

### 2.2.1 Dynamic Voltage and Frequency Scaling

Varying clocks and voltages during operation is a relatively new paradigm in design that demands determining which voltage and clock values to support, modeling timing and dealing with the settling time of clock generators, and power supplies (KEATING et al., 2007). Usually, the Dynamic Voltage and Frequency Scaling requires the circuit to be partitioned focusing on performance. Each area or part of the system have specific power constraints and target clock frequency. Figure 2.7 shows an example of a DVFS design. A programmable power supply drives the CPU sub-system. A fixed supply voltage powers the rest of the chip. Also, a Phase-locked Loop (PLL) provides a high-speed clock to the *SysClock Generator*, which uses dividers to generate the *CPU CLOCK* and the *SOC CLOCK*. For voltage and frequency scaling, a software must decide the minimum CPU clock speed that meets the workload requirements. It then determines the lowest supply voltage that will support that clock speed (KEATING et al., 2007).

During its operation, the system may face two possible situations: a high workload that requires an increase in frequency and other where a lower frequency could be used. If the target clock frequency is higher than the current frequency, the CPU programs the power supply to the new voltage and continues operating at the current clock frequency until the new voltage settles. The CPU can program either the SysClock Generator or the PLL to adjust the clock

frequency when required. On the other case, if the target clock frequency is lower than the current frequency, the CPU programs the new clock frequency and changes the configurations for the SysClock Generator, and the PLL if required. The CPU then selects the power supply to the new voltage and continues operating at the new clock frequency while the voltage settles to the new value.

Figure 2.7 – Block diagram of a DVFS example

Source: (KEATING et al., 2007)

Most DVFS systems use a set of discrete voltage/frequency pairs. Determining which values to support is a crucial design decision, and it is highly application dependent. (YAO; DEMERS; SHENKER, 1995) presented an algorithm for voltage selection that takes into account the delay, the execution time limit and the number of CPU cycles required to perform a task. The technique they proposed, computes the speed of execution, determining the start and end times of each task. Another way to solve the problem of choosing the better voltage level was proposed in (SHIN; KIM; LEE, 2001); where the voltage is set during the execution of the task and the number of CPU cycles required to perform the task may change during execution.

### 2.2.2 Adaptive Voltage Scaling

At lower supply and threshold voltages, the delay and the energy become more sensitive to variations in  $V_{DD}$  and  $V_{T}$ . Thus, the control of both voltage levels is critical. A tough task because, on real circuits, there is always a small uncertainty in the value of the supply and threshold voltage. The main sources of uncertainty are the operation conditions of the circuit and the variability of the manufacturing process. These variations cause the delay and energy to be spread out over a range, reducing the overall efficiency of the circuit. One way to minimize the effect of uncertainty is by using adaptive techniques to regulate the supply and threshold voltages. That is, dynamically adjust the supply and/or threshold voltage such that the circuit meets the required specifications (DHAR; MAKSIRNOVI; KRANZEN, 2002; ELGEBALY; SACHDEV, 2007; GONZALEZ; GORDON; HOROWITZ, 1997; USAMI; HOROWITZ, 1995; VIERI et al., 1995).

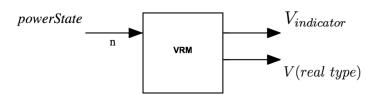

Chinnery and Keutzer (2007) shows an example of adaptive voltage scaling. Figure 2.8 depicts a diagram of a simple Voltage Regulator Module (VRM) with the ability to control the voltage rails in an analog-like fashion. The output voltage  $V(real\ type)$  is controlled by the input powerState. A binary voltage indicator ( $V_{indicator}$ ) signals when the requested voltage is stable at the output. This model enables a continuous change in the voltage in real time. A new voltage level is sought by powerState, and then the VRM will set the indicator to "0" and move the output voltage to the required level. Once the VRM reaches the new voltage level, the indicator is set to "1". With this signal we can control other aspects of the design; for instance, it may assist with the control of clock frequencies. Under higher performance demands, the voltage raises followed by an increment in frequency. The voltage indicator can be used to signalize that is safe to increase the clock frequency once the requested voltage has been achieved and is stable.

Figure 2.8 – Voltage regulator module (VRM)

Source: (CHINNERY; KEUTZER, 2007)

## 2.3 Logic Optimizations

The EDA tools provide the designers with a variety of tweaking options to improve the performance of a system for low power scenarios. The technology-independent part of the logic synthesis process consists of a sequence of optimizations that manipulate the network topology to minimize delay, power, or area. On the physical phase, the object of technology mapping is to transform a technology-independent logic description into an implementation in a specific technology.

At the logic level, the EDA tools automatically choose the network topology to implement a particular function. Several optimizations can be carried out during the logic synthesis, most of them contribute to reducing the power consumption. For example, from a performance perspective, it is a good idea to connect the most critical signal to the input pin closest to the output node; on the NAND gate of Figure 2.4, it is the N0 transistor. This is just one example of the multiple modifications that the RTL code suffers during the logical synthesis phase. These optimizations include: factoring; restructuring to minimize spurious transitions; buffer insertion/removal for path balancing and timing constraints; and *don't-care* optimization.

It seems obvious that a simpler logical expression would require less power as well. For instance, translating the function f=a.b+a.c into its equivalent f=a(b+c) seems a no-brainer, as it requires one less gate. However, this factorization may also introduce an internal node with substantially higher transition probabilities. Actually, this may increase the net power. Hence, power-aware logical synthesis must not only be aware of network topology and timing, but also should incorporate parameters such as capacitance and activity. In the end, the goal is to derive the *pareto-optimal* energy-delay curves (RABAEY, 2009). It is, we need to choose the network that minimizes power for a given maximum delay or reduces the delay for maximum power.

The algorithms for logic synthesis manipulate the logic equations to reduce the fan-in requirements and hence reduce the gate delay. For example, the quadratic dependency of the gate delay on fan-in makes a six-input NOR gate extremely slow. Partitioning the NOR-gate into two three-input gates results in a significant speed-up (RABAEY; CHANDRAKASAN; NIKOLIC, 2003). However, this new topology could increase total power consumption. Restructuring the logic network to have paths with similar lengths can reduce timing problems, power consumption, and spurious logic transitions. Also, dynamic hazards could be minimized by balancing the system in terms of timing (LAVAGNO; KEUTZER; SANGICIVANNI-VINCENTELLI, 1991).

Following the same approach, the network can also be balanced by the insertion or re-

moval of buffers. The buffers themselves add extra switching capacitance. Hence, as always, buffer insertion is a careful trade-off process. Analysis of state-of-the-art synthesis tools have shown that simple buffers handle a considerable part of the overall power budget of the combinatorial modules (RABAEY, 2009).

## 2.3.1 Technology Mapping

Technology mapping makes the link between logic synthesis and physical design. The object of technology mapping is to transform a technology-independent logic description into an implementation in a target technology. During this phase, the EDA tools select the gates and choose the appropriate size for them based on the design constraints. One of the key operations during technology mapping is to recognize logic equivalence between a portion of the initial logic description and an element of the target technology.

Different combinations of cells can implement a gate with distinctive switching activities, capacitance, power and delay (OZDAL; BURNS; HU, 2012). To implement an XOR2, an AO22 with inverters may be smaller and more energy-efficient, but slower. Refactoring to eliminate common subexpressions reduces the number of operations, therefore, the switching activity. Balancing path delays can decrease the glitch activity. Hence, the technology mapping for low power can take advantage of other approaches, as the ones cited previously, to improve the results. Also, during technology mapping, a gate sizing process chooses the best cells for meet timing constraints and minimize power consumption. To reduce delay, gates on critical paths are upsized, increasing their capacitance. In turn, the gates fan-in must be incremented to drive the larger capacitance. This result in oversized gates and buffer insertion on the critical paths (CHINNERY; KEUTZER, 2007).

### 2.4 Power Gating

Leakage power dissipation grows with every generation of CMOS process technology due to the scaling transistor threshold voltages. This leakage power is not only a serious challenge for battery-powered devices, but also an issue in tethered equipment such as servers, routers, and set-top boxes. To reduce the overall leakage power of the chip, it is desirable to add mechanisms to turn off blocks that are not required. In consequence, Power Gating provides two power modes: a low power (or inactive mode) and an active mode (KEATING et al., 2007).

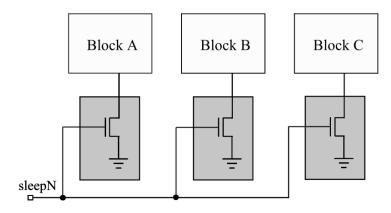

Block A Block B Block C

Figure 2.9 – Global power gating topology

Source: (CHINNERY; KEUTZER, 2007)

Power gating consists of selectively powering down certain blocks in the chip while keeping other blocks powered up. The goal of power gating is to minimize leakage current by temporarily switching power off to blocks that are not required in the current operating mode. The use of this power optimization strategy is justified by the fact that on real systems, periods of activity are followed by relatively lengthy periods of inactivity. Moreover, while the power consumption during the active period is mostly due to the dynamic power, leakage power represents the major energy consumption during inactive or standby periods.

The most basic form of power gating control is an externally switched power supply. For example, on a CPU that has a dedicated *off-chip* power supply which provides power only to the CPU, we can shut down this power supply and reduce the leakage current in the CPU. This approach, though, takes the longest time and requires the most energy to restore power to a gated block. A better approach could be power gating internally, where internal switches control the power of selected blocks. Hence, a critical decision in power gating is how to switch power. In general, there are two approaches: fine grain power gating and coarse grain power gating (KEATING et al., 2007). In fine grain power gating the switch that controls the power is inside each standard cell in the library. In coarse grain power gating, a block of gates has its power switched by a collection of switch cells.

Based on these approaches, Power Gating can be implemented using several different topologies, such as: *global power gating*, *local power gating*, and *switch-in-cell power gating*. *Global power gating* refers to a logical topology in which multiple switches connect to one or more blocks of logic, and all the power-gated logic blocks share a single virtual ground. Figure 2.9 shows an example of this approach, where the three logic blocks share a virtual ground, and each sleep domain is controlled by a particular sleep enable signal. This topology is only effective for large logic blocks, and when a single sleep signal is enough to control all of them.

Figure 2.10 – Local power gating topology

Source: (CHINNERY; KEUTZER, 2007)

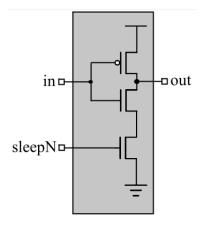

Figure 2.11 – Switch-in-cell power gating topology

Source: (CHINNERY; KEUTZER, 2007)

Local power gating specifies a logical topology in which each switch singularly gates its virtual ground connected to its own group of logic, as illustrated in Figure 2.10. Here, each logic block uses its particular switch, sharing the sleep signal.

Switch-in-cell may be thought of as an extreme form of local power gating implementation. In this topology, each logic cell contains a specific switch transistor (as Figure 2.11 depicts). This approach has several notable advantages and disadvantages. As primary advantages, delay calculation is very straightforward since each cell is timing characterized with its dedicated internal switch. However, the additional transistor in the pulldown stack and the need to size up the previously existing logic transistors to compensate for the additional device in the stack, can increase the chip's area.

# 2.5 Clock Gating

In CMOS digital circuits, the sequential part is the major contributor of the total power dissipation. A significant fraction of the dynamic power is due to the distribution network of the clock. The clock is the only signal that switches all the time. It is also mostly likely to drive a heavy load. Clock buffers spend up to 50% or even more of the dynamic power (CHINNERY; KEUTZER, 2007). In addition, the flops receiving the clock dissipate some dynamic power even if the input and output remain the same. Thus, reducing the clock power is an efficient way to minimize the total power dissipation. The most common way to do this is by turning clocks off when they are not required. This approach is known as clock gating (YUAN; DI, 2005).

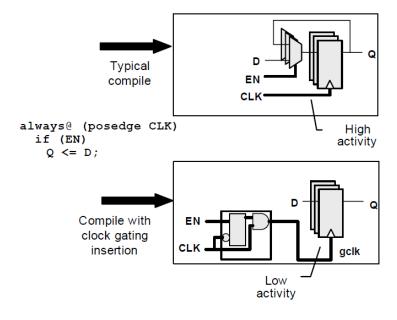

Modern design tools support automatic clock gating, they can identify circuits where clock-gating circuitry may be inserted without changing the function of the logic. Figure 2.12 exemplifies the insertion of clock gating. In the original RTL, the register updates independently of the variable (EN); when applied clock gating, this signal controls the state of the register.

Figure 2.12 – Clock Gating

Source: (KEATING et al., 2007)

This power optimization technique is transparent to the RTL designer. However, in the early days of RTL design, engineers would code clock-gating circuits explicitly in the RTL. This approach was error prone because it is very easy to create a clock gating circuit which glitches during gating (KEATING et al., 2007). Today, most libraries include specific clock

gating cells that the synthesis tool recognizes. The combination of explicit clock gating cells and automatic insertion makes clock gating a simple and reliable way of reducing power (WU; PEDRAM; WU, 2000).

### 2.6 Architecture-level Optimizations

Optimizations at the architecture or system level can enable more efficient power minimization while maintaining performance. At higher abstraction levels, design modifications tend to have a greater potential impact, allowing circuit level techniques such as voltage scaling (ZHAI et al., 2004) or gate sizing (FLACH et al., 2013) to be more effective. Moreover, it is well known that the *Return-on-Investment* (ROI) increases at higher levels of the design process. While circuit techniques may yield improvements in the 10-50% range, architecture and algorithm optimizations have reported power reduction by orders of magnitude (RABAEY, 2009).

At the circuit level, the optimization parameters are mostly continuous. We have to decide the optimum gate/transistor size or the best supply and threshold voltage levels for low power scenarios. At the architecture-level, the choices are rather discrete. For instance, we dispose of several adder topologies to choose the one that best fit the design constraints. These discrete choices contribute to expanding the energy-delay space.

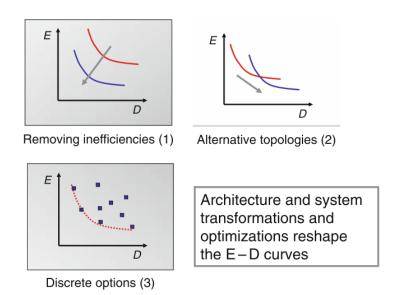

Figure 2.13 – Energy-delay tradeoff

Source: (RABAEY, 2009)

Figure 2.13 plots three scenarios for *energy-delay* tradeoff. Following the previous example, if two adder topologies are available, each of them comes with its optimal energy-delay curve (Figure 2.13, plot 2). When one topology is superior, offering the best energy-delay tradeoff, the selection process is quite straightforward (plot 1). Finally, a third scenario consists of many discrete options such as the sizes and the number of register files (plot 3).

### 2.6.1 Concurrency

Concurrency is a property of systems in which several operations are executing simultaneously, and potentially interacting with each other. A system that exploits parallel approaches, may have different clock domains and particular energy demands. Depending on the requirements of the system and its topology, we can enable aggressive supply voltage scaling. It also improves performance at a fixed *energy per operation* (EOP) (CHANDRAKASAN; SHENG; BRODERSEN, 1992).

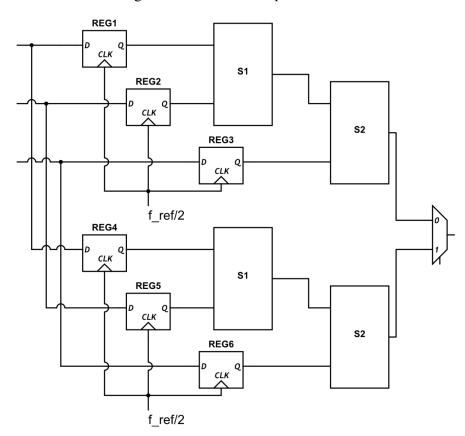

To better understand the advantages of concurrency, consider the design of Figure 2.14, which operates at a nominal supply voltage  $(V_{DD_{ref}})$  and a specific frequency  $f_{ref}$ . S1 and S2 are combinational logic blocks, and  $C_{ref}$  is the average switched capacitance. A parallel implementation of the same design, as the one on Figure 2.15, replicates the design such that parallel branches process interleaved input samples; then a multiplexer recombines the outputs.

REG1

P CLK

REG2

P CLK

REG3

P CLK

S1

F\_ref

Figure 2.14 – Concurrency example design

S1 and S2 contain adders, ALUs, etc. The total power is  $P_{ref} = C_{ref} (V_{DD_{ref}})^2 f_{ref}$

Source: (CHANDRAKASAN; SHENG; BRODERSEN, 1992)

Thanks to the parallelism, the new design can operate at half the speed; hence the fre-

quency becomes  $f_{par} = f_{ref}/2$ . Loosen the delay constraint enables a reduction of the supply voltage by a  $\epsilon_{par}$  factor, and the total power is now  $P_{par} = C_{ref}(V_{DD_{ref}}/\epsilon_{par})^2 f_{par}$ . With this implementation, the overhead of switching capacitance is minimal but the increase in area is substantial. The impact of introducing concurrency to reduce EOP for a fixed performance hinges on the relationship between the supply voltage and delay as explained before.

Figure 2.15 – Parallel Implementation

Source: (CHANDRAKASAN; SHENG; BRODERSEN, 1992)

## 2.6.2 Pipelining

Another form to introduce concurrency in a design is with pipelining; it can be equally effective in reducing the supply voltage, and hence reducing power dissipation. Pipelining improves throughput at the cost of latency by inserting extra registers between logic gates. It employs the registers to break up a datapath into multiple stages, each stage storing the intermediate results.

Figure 2.16. depicts a possible pipelining implementation of the previous example. The area overhead of pipelining is much smaller than that of parallelism, the only cost being the

extra registers, compared to replicating the design and adding multiplexers (RABAEY, 2009). The switching power in registers is the major part of power dissipation and pipelined implementations typically come with a higher switched capacitance than parallel designs.

REG1

P CLK

REG2

REG3

P CLK

REG3

P CLK

REG4

S2

F\_ref

f\_ref

f\_ref

Figure 2.16 – Pipelining Implementation

Source: (CHANDRAKASAN; SHENG; BRODERSEN, 1992)

An ideal low-power design methodology employs some or all previously presented techniques, with the objective to reduce power in all abstraction levels and obtain greater energy savings.

With pipelining and parallelism, digital systems can achieve the same performance at lower clock frequencies. The timing slack is useful to reduce the power with the aid of a lower supply voltage, a higher threshold voltage, and reduced gate sizes. Some parts of the chip may operate at lower supply voltage, and those that require high-performance will maintain a higher voltage level. In consequence, concurrency also enables the possibility to use multiple voltages for controlling the power of each region independently. Systems with multiple supplies require a special design methodology and considerations as we can see in the next chapter.

#### 3 MULTI-VOLTAGE DESIGNS

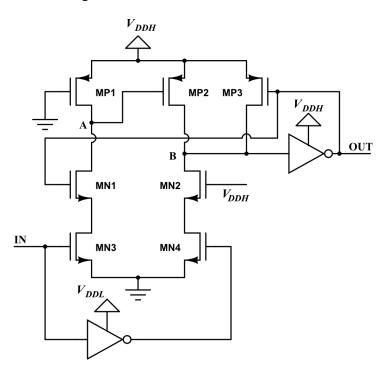

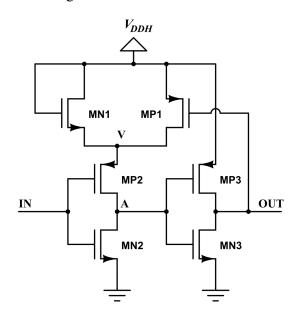

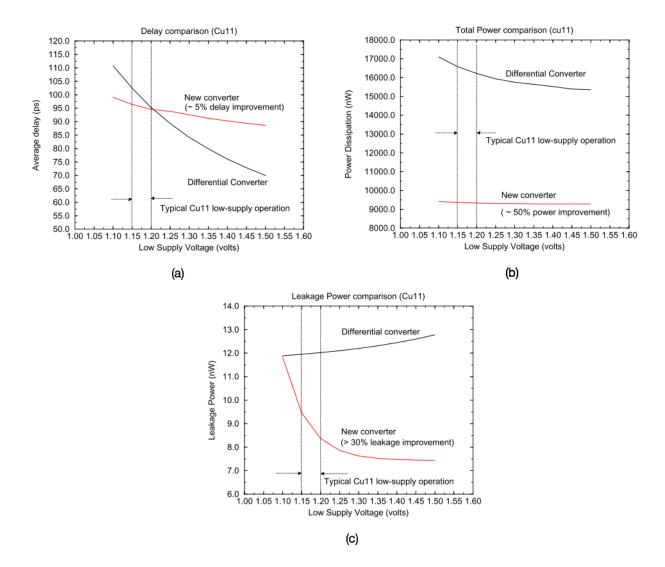

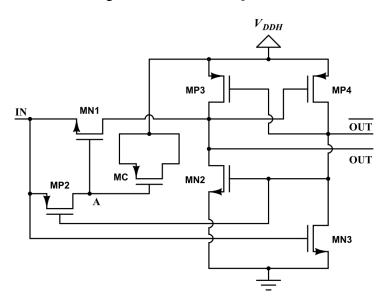

On systems that exploit concurrency, the logic blocks can operate at different frequencies. Each one having peculiar energy demands to fulfill the clock speed requirements. In addition, some of those blocks do not operate at all when the system is in standby mode. Several approaches take advantage of these characteristics to implement distinct voltage level regions (KULKARNI; SRIVASTAVA; SYLVESTER, 2004; LI et al., 2005; TERRES et al., 2014).