# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA - PGMICRO

#### DALTON MARTINI COLOMBO

# Bandgap Voltage References in submicrometer CMOS technology

Thesis presented in partial fulfillment of the requirements for the degree of Master in Microelectronics

Prof. Dr. Gilson Wirth Advisor

Prof. Dr. Sergio Bampi Co-Advisor

# CIP – CATALOGAÇÃO NA PUBLICAÇÃO

#### Colombo, Dalton Martini

Bandgap Voltage References in submicrometer CMOS tecnology / Dalton Martini Colombo – Porto Alegre: Programa de Pós-Graduação em Microeletrônica, 2008.

92 f.:il.

Thesis (Master) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica. Porto Alegre, BR – RS, 2008. Advisor: Gilson Wirth; Co-Advisor: Sergio Bampi.

1. Projeto Analógico CMOS. 2. Referências de tensão 3. Referências de tensão Bandgap. I. Wirth, Gilson, II. Bampi, Sergio.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos Alexandre Netto Vice-reitor: Prof. Rui Vicente Oppermann

Pró-Reitor de Pós-Graduação: Aldo Bolten Lucion

Diretor do Instituto de Informática: Prof. Flávio Rech Wagner Coordenador do PGMICRO: Prof. Henri Ivanov Boudinov

Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

## **ACKNOWLEDGMENTS**

First I would like to thank my family (Decio Colombo, Maria Ap. Martini Colombo and Allan Colombo) for all support they always give to me. It was only through their help that I had opportunity to study and invest in my career.

I'm very grateful to my supervisors Gilson Wirth and Sergio Bampi for the great opportunity to work with them. They always give me valuable guidance and support.

I would like to thank for all members of the UFRGS microelectronics group (and Informatics Institute), professors and technical members. In specially, I'm would like to express my gratitude for the friends of 100 laboratory – all helpful discussions were of great value to me.

I'm grateful to the reviewers of this work: Profs. Altamiro Susin, Eric Fabris and Robson Moreno. I also thank the professors of UNIFEI for the first opportunity to work with academic research: Paulo César Crepaldi and Ótavio Agusto Carpinteiro.

At the end, I would to thank the CNPq for the financial support that makes this work possible.

# **TABLE OF CONTENTS**

| LIST           | OF SYMBOLS                                        | 6  |

|----------------|---------------------------------------------------|----|

| LIST           | OF ABREVIATIONS AND ACRONYMS                      | 8  |

| LIST           | OF FIGURES                                        | 9  |

| LIST           | OF TABLES                                         | 11 |

| ABST           | TRACT                                             | 12 |

| RESU           | JMO                                               | 13 |

| 1 IN           | ITRODUCTION                                       | 15 |

| 2 B            | ANDGAP VOLTAGE REFERENCES                         | 18 |

| 2.1            | Generation of $\mathbf{V}_1$ and $\mathbf{V}_2$   | 19 |

|                | Output voltage                                    |    |

| 2.3            | Historical View                                   | 24 |

| 3 B            | ANDGAP VOLTAGE REFERENCES DESIGNED                | 28 |

| <b>3.1</b> 1   | BGR1                                              |    |

| 3.1.1          | Implementation Details                            | 30 |

| 3.1.2          | Startup-Circuit                                   |    |

| 3.1.3          | Layout of BGR1                                    |    |

| 3.1.4          | Post-Layout Simulation results                    |    |

|                | BGR2                                              |    |

| 3.2.1          | Implementation Details                            |    |

| 3.2.2          | Start-up Circuit                                  |    |

| 3.2.3          | Layout of BGR2                                    |    |

| 3.2.4          | Post-Layout Simulation Results                    |    |

|                | BGR3                                              |    |

| 3.3.1<br>3.3.2 | Implementation Details                            |    |

| 3.3.2<br>3.3.3 | Start-up circuit                                  |    |

| 3.3.4          | Layout of BGR3  Post-Layout Simulation Results    |    |

|                | OW-VOLTAGE LOW-POWER, NOISE AND VARABILITY ISSUES |    |

|                |                                                   |    |

|                | Low-Voltage and Low-power                         |    |

| 4.1.1          | Resistive Subdivision                             | 55 |

| 4.1.2                    | Low-Bandgap Material                                                   | . 56                 |

|--------------------------|------------------------------------------------------------------------|----------------------|

| 4.1.3                    | Virtual Low-Bandgap Device                                             | . 56                 |

| 4.2                      | Variability caused by Fabrication Process                              | 57                   |

| 4.3                      | Output Noise                                                           |                      |

| 4.4                      | Trim range limited by Noise                                            |                      |

| 4.4.1                    | Trim circuits                                                          | 65                   |

| 4.4.2                    | $\mathcal{C}$                                                          |                      |

| 4.4.3                    |                                                                        |                      |

| 4.4.4                    | New trim range for BGR1, BGR2 and BGR3                                 | 68                   |

| 5 C                      | CONCLUSIONS                                                            | 70                   |

| REF                      | ERENCES                                                                | 72                   |

|                          |                                                                        |                      |

| PUB                      | LICATIONS BY THE AUTHOR OF THIS MASTER THESIS                          | 77                   |

| ANN                      | LICATIONS BY THE AUTHOR OF THIS MASTER THESIS                          |                      |

| ANN<br>PER               | IEX A EXAMPLES OF COMMERCIAL BGR'S CHIPS AND THEIR                     | 78                   |

| ANN<br>PER<br>ANN<br>APP | IEX A EXAMPLES OF COMMERCIAL BGR'S CHIPS AND THEIR FORMANCE PARAMETERS | 78<br>79<br>))       |

| ANN<br>PER<br>ANN<br>APP | IEX A EXAMPLES OF COMMERCIAL BGR'S CHIPS AND THEIR FORMANCE PARAMETERS | 78<br>79<br>0)<br>82 |

# LIST OF SYMBOLS

V<sub>REF</sub> Voltage Reference

V<sub>G0</sub> Bandgap energy of silicon extrapolated for zero Kelvin

V<sub>BE</sub> Base-emitter voltage

$\Delta V_{BE}$  The difference between the emitter-base voltages of two

BJT's

$\Delta V_{REF\ TEMP}$  Variation of the  $V_{REF}$  over the operation temperature range

V<sub>LSB</sub> Voltage that corresponds to 1 bit variation in Data

Converter

$V_{TH}$  Thermal voltage

J<sub>C</sub> Collector current density

A Geometric and fabrication process parameter

γ Temperature coefficient

α Temperature coefficient of the current source supplying

the diodes

k Boltzmann's constant

q Charge of electron

T Absolute temperature

T<sub>0</sub> Room Temperature

β<sub>F</sub> Common-emitter current gain

I<sub>C</sub> Collector Current

I<sub>B</sub> Base Current

I<sub>S</sub> Saturation Current

n Ratio of emitter areas

C Temperature-independent constant

D Temperature-independent constant

N Temperature-independent constant

x Arbitrary number defined by the temperature dependence

of the current forced through the collector

V<sub>GS</sub> Gate-source voltage

I<sub>D0</sub> Process constant

n' Subthreshold slope factor

W Channel Width

L Channel Length

V<sub>OV</sub> Overdrive Voltage

V<sub>OS</sub> Offset Voltage

V<sub>T</sub> Threshold Voltage

$\beta_N$  Negative feedback factor  $\beta_P$  Positive feedback factor

V<sub>PTAT</sub><sup>2</sup> Square proportional to the temperature voltage

I<sub>Supply</sub> Supply Current

VDD<sub>MIN</sub> Minimum supply voltage for one traditional BGR

$\Delta V_{REF}$  Variation in  $V_{REF}$

$\Delta V_{REF\_TOTAL}$  Total Variation in  $V_{REF}$

$\Delta V_{REF\_i} \hspace{1.5cm} Variation \ in \ V_{REF} \ due \ to \ each \ error \ source$

V<sub>REF\_MONTE\_CARLO</sub> Output voltage from Monte Carlo Analysis

$\Delta V_{REF\_TEMP\_MONTE\_CARLO}$  Variation in  $V_{REF}$  over TEMP range from Monte Carlo

**Analysis**

V<sub>OS MONTE CARLO</sub> Offset voltage from Monte Carlo Analysis

$\begin{array}{ll} V_{REF\_UPPER} & 3\sigma \text{ behavior for the damaged output voltage} \\ V_{REF\_DOWN} & 3\sigma \text{ behavior for the damaged output voltage} \end{array}$

$\Delta V_{REF NOISE}$  Variation of output voltage due the noise

V<sub>PEAK-TO-PEAK</sub> 3σ value of noise behavior

$V_{RMS}$  RMS noise

gm Transconductance

Number of bits needed to trim the circuit

$V_{FS}$  Initial full-scale tolerance expected  $V_{LSB}$  Value of the least significant bit

202

V<sub>Accuracy</sub> The target accuracy (after trimming)

$K_C$  "Safety Factor" used to reduce the value of  $V_{LSB}$

K<sub>F</sub> Device-specific noise constant

## LIST OF ABREVIATIONS AND ACRONYMS

BGR Bandgap voltage reference

BiCMOS Bipolar Junction Transistor and CMOS technology

TC Temperature coefficient

DTMOST Dynamic-threshold voltage MOS transistor

PTAT Proportional to absolute Temperature

PTAT<sup>2</sup> Square PTAT

CTAT Complementary to Absolute Temperature

OA Operational amplifier

VLSI Very Large Scale Integration

CMOS Complementary Metal Oxide Semiconductor

BJT Bipolar junction transistor

IC Integrated Circuit

PSR Power Supply Rejection

PSRR Power Supply Rejection Ratio

BW Bandwidth

DRAM Dynamic Random Access Memory

PLL Phase Locked Loop

TSMC Taiwan Semiconductor Manufacturing Company

DAC Digital to Analog Converter

ADC Analog to Digital Converter

VLSB Least Significant Bit

VR Voltage Reference

PLL Phase Look Loop

TC Temperature Coefficient

SNR Signal-to-noise ratio

RMS Root-mean-square

TEMP Temperature

# **LIST OF FIGURES**

| Figure 1.1: Voltage-Scale 3-bit DAC (Allen, 2004).                                    | 15 |

|---------------------------------------------------------------------------------------|----|

| Figure 2.2: Generation of V <sub>TH</sub> using two BJT's with different areas        | 22 |

| Figure 2.3: Typical Curvature of first-order V <sub>REF</sub> over temperature range  |    |

| Figure 2.4: Integrated voltage reference proposed by (Widlar, 1971)                   |    |

| Figure 3.1: BGR1                                                                      |    |

| Figure 3.2: $V_{REF}$ as a function of temperature and different value of $T_0$       |    |

| Figure 3.3: Start-up Circuit of BGR1                                                  |    |

| Figure 3.4: Start-up Time of BGR1 with and without (Dotted Line) start circuit        |    |

| Figure 3.5: Layout of BGR1                                                            |    |

| Figure 3.6: V <sub>REF</sub> as a function of temperature of BGR1                     |    |

| Figure 3.7: Line Regulation for BGR1 (1.7 – 1.9V)                                     |    |

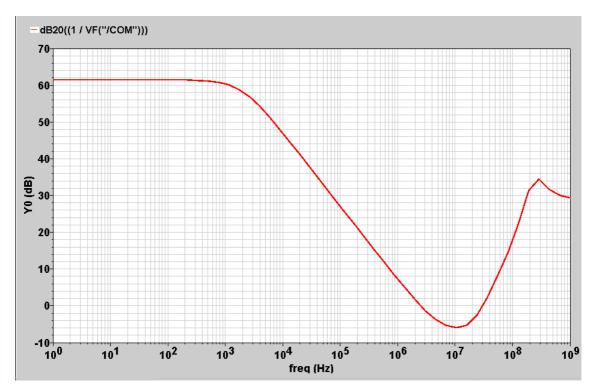

| Figure 3.8: PSR of BGR1                                                               |    |

| Figure 3.9: BGR2 using error-amplifier-base current mirror                            |    |

| Figure 3.10: OTA with 2-stages and its bias circuit                                   |    |

| Figure 3.11: Start-up circuit used in BGR2                                            |    |

| Figure 3.12: Start-up time of BGR2 with and without (dot line) start-circuit          |    |

| Figure 3.13: BGR2 layout                                                              |    |

| Figure 3.14: Layout of error-amplifier and its bias circuit                           | 43 |

| Figure 3.15: V <sub>REF</sub> as a function of temperature for BGR2                   |    |

| Figure 3.16: Line Regulation for BGR2 (1.7 – 1.9 V)                                   | 44 |

| Figure 3.17: PSR for BGR2                                                             | 45 |

| Figure 3.18: Typical Curvature of second-order compensated BGR                        | 46 |

| Figure 3.20: Layout of BGR3                                                           |    |

| Figure 3.21: V <sub>REF</sub> as a function of temperature for BGR3                   | 50 |

| Figure 3.22: Line Regulation of BGR3 (1.7 – 1.9V)                                     |    |

| Figure 3.23: PSR for BGR3                                                             |    |

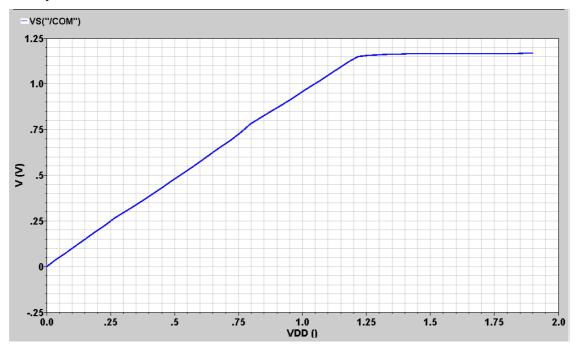

| Figure 4.1: V <sub>REF</sub> as a function of Supply Voltage for BGR2                 | 54 |

| Figure 4.3: Cross Section of DTMOST (Annema, 1999)                                    | 56 |

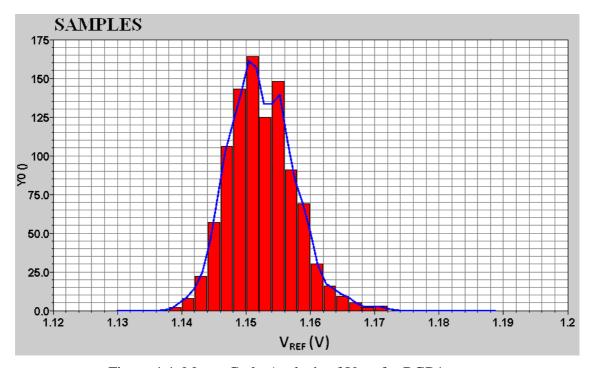

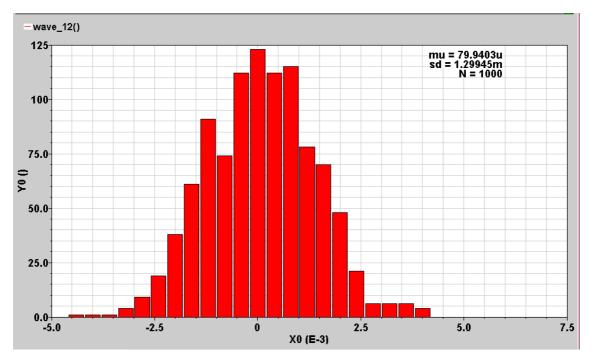

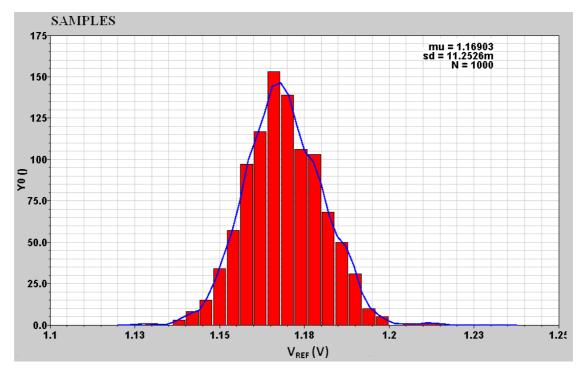

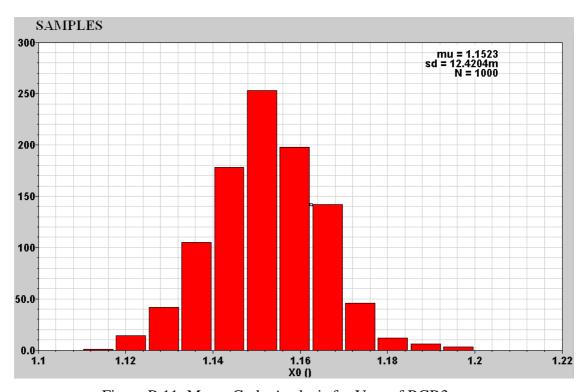

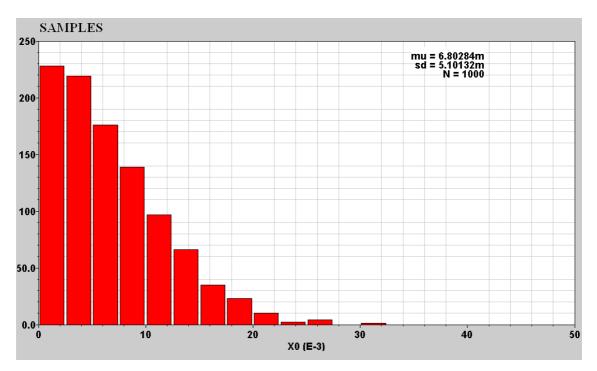

| Figure 4.4: Monte Carlo Analysis of V <sub>REF</sub> for BGR1                         | 59 |

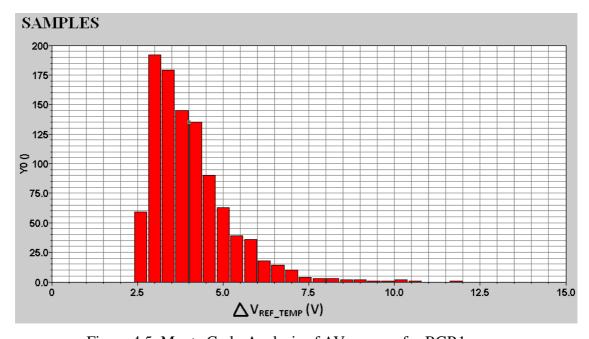

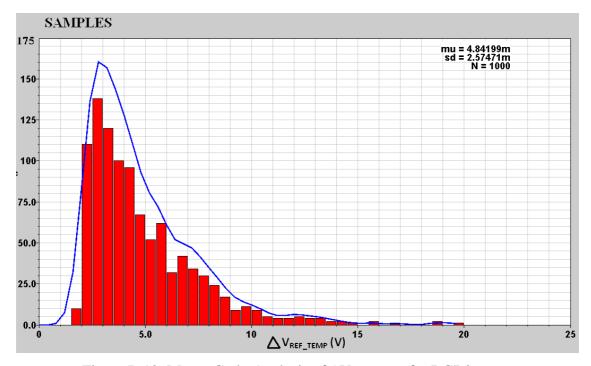

| Figure 4.5: Monte Carlo Analysis of ΔV <sub>REF TEMP</sub> for BGR1                   |    |

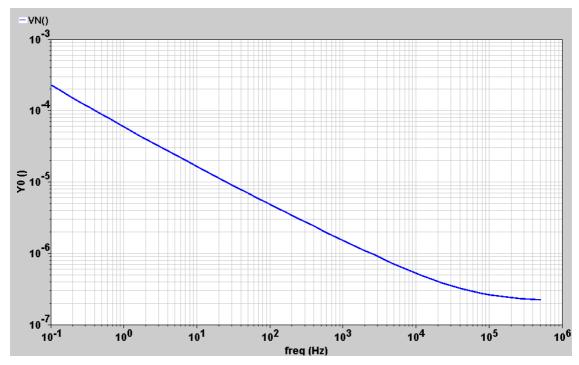

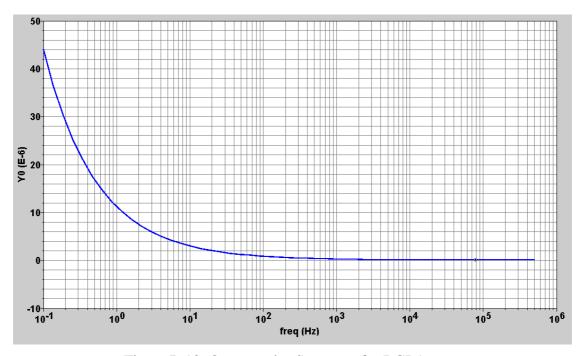

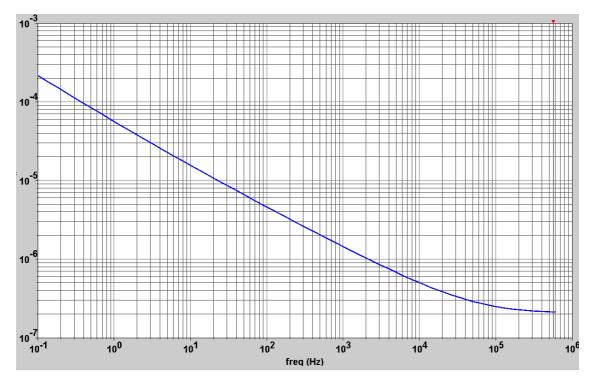

| Figure 4.6: Output noise Spectrum of BGR2 - (Noise Axis in logarithm)                 |    |

| Figure B.3: M <sub>1</sub> and M <sub>2</sub> in common centroid configuration – BGR1 |    |

| Figure B.4: 8x1 BJT's in common centroid configuration – BGR1, BGR2 and BGR3          |    |

| Figure B.5: Matched Resistors in common centroid configuration of BGR1                |    |

| Figure B.6: Bode Diagram of Operational Amplifier used in BGR2 and BGR3               |    |

| Figure B.7: V <sub>REF</sub> as a function of supply voltage of BGR1                  |    |

| Figure B.8: V <sub>REF</sub> as a function of Supply Voltage for BGR3                 |    |

| Figure B.9: Monte Carlo Analysis of V <sub>OS</sub> for opamp used in BGR2 and BGR3   |    |

| Figure B.10: Monte Carlo Analysis of $\Delta V_{REF\ TEMP}$ for BGR2 | 90 |

|----------------------------------------------------------------------|----|

| Figure B.10: Monte Carlo Analysis for V <sub>REF</sub> of BGR2       | 91 |

| Figure B.11: Monte Carlo Analysis for V <sub>REF</sub> of BGR3       | 91 |

| Figure B.12: Monte Carlo Analysis of ΔV <sub>REF TEMP</sub> for BGR3 | 92 |

| Figure B.13: Output noise Spectrum for BGR1                          |    |

| Figure B.14: Output noise Spectrum for BGR3 (Noise axis in log)      | 93 |

# **LIST OF TABLES**

| Table 2.1: Parameters of equations 2.4 and 2.5 (Allen, 2004)               | 20 |

|----------------------------------------------------------------------------|----|

| Table 2.2: Parameters of equations 2.7 and 2.8                             | 21 |

| Table 2.3: Parameters of equations 2.12 and 2.13                           | 22 |

| Table 2.4: Parameters of equation 2.15                                     | 25 |

| Table 2.5: Summary of the BGR's discussed in this section                  | 26 |

| Table 3.1: Size of transistors and value of the resistor of BGR1           | 31 |

| Table 3.2: Size of devices in Start-up circuit of BGR1                     | 33 |

| Table 3.4: Simulated results for the error-amplifier                       | 38 |

| Table 3.5: Size of transistors and value of the resistor of BGR2           | 39 |

| Table 3.7: Parameters of equations 3.10 and 3.11                           | 47 |

| Table 3.8: Sizes of transistors and values of the resistors in BGR3        | 48 |

| Table 4.3: Temperature dependence of error sources (Gupta, 2002)           | 58 |

| Table 4.4: Monte Carlo Analysis for BGR1, BGR2 and BGR3                    | 60 |

| Table 4.5: Output noise and $\Delta V_{REF NOISE}$ for BGR1, BGR2 and BGR3 | 63 |

| Table 4.7: Parameters of equations 4.10 and 4.11                           | 67 |

| Table 4.8: Number of bit for each BGR                                      | 68 |

| Table 4.9: Number of bit for each BGR considering the output noise         | 69 |

| Table A.1: Examples of Commercial BGR chips                                |    |

| Table B.1: Model Parameters of IBM 0.18 Micron 7RF technology              |    |

## **ABSTRACT**

A Voltage Reference is a pivotal block in several mixed-signal and radio-frequency applications, for instance, data converters, PLL's and power converters. The most used CMOS implementation for voltage references is the Bandgap circuit due to its high-predictability, and low dependence of the supply voltage and temperature of operation.

This work studies the Bandgap Voltage References (BGR). The most relevant and the traditional topologies usually employed to implement Bandgap Voltage References are investigated, and the limitations of these architectures are discussed. A survey is also presented, discussing the most relevant issues and performance metrics for BGR, including, high-accuracy, low-voltage and low-power operation, as well as the output noise of Bandgap References fabricated in submicrometer technologies.

Moreover, a comprehensive investigation on the impact of fabrication process effects and noise on the reference voltage is presented. It is shown that output noise can limit the accuracy of the BGR and trim circuits.

To support and develop our work, three BGR's were designed using the IBM 0.18 Micron 7RF process with a supply voltage of 1.8 V. The layouts of these circuits were also designed to provide post-extracted layout information and electrical simulation results. This work provides a comprehensive discussion on the structure and design practices for Bandgap References.

Keyworkds: Analog Design, CMOS, Voltage References, Bandgap References.

## Referências de Tensão Bandgap em Tecnologias CMOS Submicrométricas

#### **RESUMO**

Referências de tensão são blocos fundamentais em uma série de aplicações de sinais mistos e de rádio frequência, como por exemplo, conversores de dados, PLL's e conversores de potência. A implementação CMOS mais usada para referências de tensão é o circuito Bandgap devido sua alta previbilidade, e baixa dependência em relação à temperatura e tensão de alimentação.

Este trabalho estuda aplicação de Referência de Tensão Bandgap. O princípio, as topologias tradicionalmente usadas para implementar este método e as limitações que essas arquiteturas sofrem são investigadas. Será também apresentada uma pesquisa das questões recentes envolvendo alta precisão, operação com baixa tensão de alimentação e baixa potência, e ruído de saída para as referências Bandgap fabricadas em tecnologias submicrométricas.

Além disso, uma investigação abrangente do impacto causado pelo o processo da fabricação e do ruído no desempenho da referência é apresentada. Será mostrado que o ruído de saída pode limitar a precisão dos circuitos Bandgap e seus circuitos de ajuste.

Para desenvolver nosso trabalho, três Referências Bandgap foram projetadas utilizando o processo IBM 7RF 0.18 micra com uma tensão de alimentação de 1.8V. Também foram projetados os leiautes desses circuitos para prover informações pósleiaute extraídos e resultados de simulação elétrica. Este trabalho provê uma discussão de algumas topologias e das práticas de projeto para referências Bandgap.

**Palavras Chave:** Projeto Analógico, CMOS, Referência de Tensão, Referência Bandgap

#### 1 INTRODUCTION

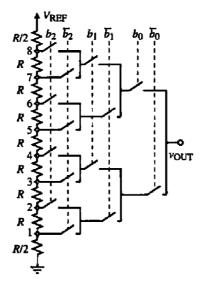

A Voltage Reference (VR) is a circuit that provides stable and accurate output voltage. The term "Reference" is used to distinguish from "source", since a source has less stability and accuracy. The stable voltage provided is used to bias others subcircuits to generate predictable and repeatable results. References are therefore an essential building block in the design of several applications; for example, voltage regulators, analog to digital (ADC), digital to analog converters (DAC), AC-DC converters, phase-locked Loop (PLL) and power converters. Figure 1 shows a typical example of one voltage-scaling DAC. Depending on the value of digital input word, the switches are configured in such way that a proper fraction of the voltage reference is connected to the output (Allen, 2004).

Figure 1.1: Voltage-Scale 3-bit DAC (Allen, 2004).

To illustrate the importance of a good voltage reference, consider the following example. A 10-bit ADC has a voltage reference ( $V_{REF}$ ) tuned to 3.072 V at 25 °C. Once this reference is allowed to cause a maximum error of  $\pm \frac{1}{2}$  V<sub>LSB</sub> (voltage that corresponds to 1 least-significant-bit variation) over the temperature range of 0 to 50 °C, which is the maximum allowable temperature coefficient (TC) for the VR?

$$V_{LSB} \equiv \frac{V_{ref}}{2^N} = \frac{3.072}{2^{10}} = 0.003 V$$

$$\frac{\Delta V_{REF}}{\Delta T} = \frac{V_{LSB}/2}{25^\circ} = \frac{0.0015}{25^\circ} = 60 \mu V / ^\circ C$$

Accordingly, the VR for this application should vary at maximum  $60\mu V/^{\circ}C$ , otherwise the target DAC accuracy can not be met. A reference voltage variation of only  $60\mu V/^{\circ}C$  frequently can not be achieved by circuits without techniques of temperature compensation.

A reference circuit is designed to be independent of: supply voltage (VDD), temperature range of operation and fabrication process effects. Moreover, this circuit should have high accuracy, low output noise and present a long-term stability. The long-term stability is the capacity of the reference to present the same output voltage and performance over a long period of time. Finally, since today there is a large demand for battery-powered products and embedded systems, the recent voltage references also are required to present low-voltage and low-power operation (Ker, 2005).

In respect of the connected load, the voltage references usually are able to drive up to  $100~\mu A$  (Rincon-Mora, 2002), more often less than this value. In case the load demands a higher current, it is necessary to use a buffer amplifier to isolate the reference from the load, and in this way, the high performance is guaranteed even if larger loads have to be driven.

In the past, many voltage references were designed to be off-chip. However, external circuits influence the signal integrity and increase the pin count of the system, what is a large disadvantage in the current scenario requiring high integration and low cost, where many times whole systems are fully integrated inside a single chip (Freitas, 2007). Thus, voltage references should present the features listed above and be compatible with integrated CMOS technology.

As some desired characteristics impose design decisions that are conflicting with other features, usually two important system trends can be distinguished when designing a voltage reference: i) targeting at low-power, or ii) targeting at high-performance (Annema, 1999).

Bandgap references (BGR) are one of the most popular implementation for voltage references. The origin of this technique was the work by Hilbiber (Hilbiber, 1964) and seven years later, Robert Widlar (Widlar, 1971) proposed the first integrated circuit implementation of the Bandgap concept.

This work presents a study of BGR design in CMOS technology. The Bandgap principle, the traditional topologies usually employed to implement this idea and the limitations of such architectures, especially if new fabrication processes are used, are addressed herein. The state of the art of the research underway in this area is also presented. Constraints and performance metrics including high-accuracy, low-voltage and low-power operation are discussed, and noise issues related to the Bandgap performance are also treated.

Special investigation on the impact of fabrication process effects on the Bandgap performance is presented. In addition, it is shown that the output noise can limit the performance of the BGR and the trim circuits.

To support and to develop our work, three BGR's were designed using a submicrometer technology. The layouts of these circuits were also designed to provide post-extracted information. The fabrication process to be used is the IBM 0.18 Micron 7RF (accessible through the MOSIS service). This technology was chosen because it is

a standard CMOS fabrication process which has also capabilities for RF and mixed signal applications, and, moreover, the design kit for it was licensed by UFRGS University through the MOSIS silicon brokerage service. It has 6 metal layers and supports a nominal supply voltage of 1.8 volts. The Cadence CAD tools, including the SPECTRE simulator were used to design and simulate all circuits.

The text is organized as follows. Chapter 2 presents the BGR principle, an historical view of this voltage reference method and some usual definitions related to it.

In the Chapter 3, the three Bandgap voltage references designed are described in detail. The layout techniques applied to reduce the impact of fabrication process variations is also presented.

Chapter 4 presents some limitations inherent to the traditional topologies, mainly in designs requiring low-voltage and low-power operation. The state-of-art design techniques presented in the literature to overcome these restrictions are also presented. Moreover, variability caused by the fabrication process and the output noise are investigated.

The conclusions are presented in chapter 6. Appendix A presents the summary of this Master thesis in Portuguese. Appendix B and C show figures and the deduction of output voltage for the designed BGR3 circuit, respectively. In Annex A, examples of commercial Bandgap reference voltages and their performance parameters are presented. Annex B shows the model parameters of the technology used to design the circuits.

#### 2 BANDGAP VOLTAGE REFERENCES

The Bandgap voltage reference is a technique that allows the generation of an output voltage with little dependence upon temperature and power supply. This reference was named "Bandgap" because its output voltage is close to 1.166 volts, which is the Bandgap energy per elementary electron charge in silicon, extrapolated to zero Kelvin  $(V_{G0})$  (Allen, 2004).

Before to start explaining how this reference works, it is important to define the usual metrics used to characterize the performance of voltage references.

• Temperature drift: it is the variation of the reference voltage over the operation temperature range of the application. The typical metric used for these variations is the temperature coefficient (TC), and it is frequently expressed in parts-per-million per degree Celsius (ppm/°C). The TC is calculated by means of equation 2.1 (Rincon-Mora, 2002).

$$TC_{REF} = \frac{1}{V_{REF}} \cdot \frac{\partial V_{REF}}{\partial Temperature}$$

(2.1)

- $\bullet$  Line regulation: it is the variation in  $V_{REF}$  caused by power supply variations. It is usually expressed in percentage.

- $\bullet$  Load regulation: it is the variation in  $V_{REF}$  caused by the effects of loading the reference supply.

BGRs with different temperature coefficients can be implemented. Very different TC values are reported in the literature, as for instance 70 ppm/°C (Tzanateas, 1979) down to 3 ppm/°C (Yao, 2005) over a wide temperature range. There are many possible implementations for the BGR concept, where each one achieves a different accuracy. Often trade offs have to be met, as for instance, more accurate BGR's often demand larger silicon area. Thus, it is the application who defines which BGR architecture should be used in each design. For many applications, such as an operational amplifier, a simple low-precision reference is fully adequated.

The small dependence of  $V_{REF}$  upon temperature is achieved through a balanced adding of two voltages with opposite temperature coefficient, as described by equation (2.2). If the constants  $\alpha 1$  and  $\alpha 2$  – both temperature-independent – are chosen in such way that equation (2.3) is satisfied,  $V_{REF}$  with zero TC at room temperature is achieved at some given temperature T where the equation 2.3 below applies.

$$V_{REF} = \alpha 1 \cdot V_1 + \alpha 2 \cdot V_2 \tag{2.2}$$

$$0 = \alpha 1 \cdot \frac{\partial V_1}{\partial T} + \alpha 2 \cdot \frac{\partial V_2}{\partial T}$$

(2.3)

Considering that  $V_1$  increases with temperature, it is usually called Proportional to Absolute Temperature (PTAT) voltage. Then,  $V_2$  decreases with temperature and is frequently called Complementary to Absolute Temperature (CTAT) voltage (Razavi, 2001). There are different ways to generate  $V_1$  and  $V_2$ , and in the section 2.1 one of the most widespread methods is presented.

#### 2.1 Generation of $V_1$ and $V_2$

The most prevalent technique in the literature to provide  $V_1$  and  $V_2$  is through the built-in voltage of a diode or the base-emitter voltage ( $V_{BE}$ ) of a bipolar junction transistor (BJT). The widespread use of this technique is due to:

- High-stability against fabrication process effects (Widlar, 1971) with a predictability of about  $\pm 2$  to 5% (Rincon-Mora, 2002).

- Well characterized temperature dependence.

Equation 2.4 describes  $V_{BE}$  voltage and equation 2.5 describes its temperature drift. Table 2.1 presents all the parameters of equations 2.4 and 2.5. Assuming room temperature  $T_0 = 300$  K and typical values for other parameters, TC calculated by equation 2.5 is about -1.5 mV/°C. Since  $V_{BE}$  voltage decreases with temperature, it is a CTAT voltage.

$$V_{BE} = V_{TH} \cdot \ln \left( \frac{J_C}{A \cdot T^{\gamma}} \right) + V_{G0}$$

(2.4)

$$\frac{\partial V_{BE}}{\partial T}\Big|_{T=T0} = \frac{V_{BE} - V_{G0}}{T_0} + (\alpha - \gamma) \cdot \left(\frac{k}{q}\right)$$

(2.5)

The thermal voltage (V<sub>TH</sub>), in table 2.1, is described by equation 2.6 (Razavi, 2001).

$$V_{TH} = \frac{k \cdot T}{q} \tag{2.6}$$

| Parameter | Description                                                        | Typical<br>value       | Unit             |

|-----------|--------------------------------------------------------------------|------------------------|------------------|

| $V_{BE}$  | Base-emitter voltage                                               | 0.7                    | V                |

| $V_{G0}$  | Bandgap energy of silicon extrapolated to zero Kelvin              | 1.166                  | V                |

| $V_{TH}$  | Thermal voltage                                                    | -                      | V                |

| $J_{C}$   | Collector current density                                          | -                      | A/m <sup>2</sup> |

| A         | Geometric and fabrication process parameter                        |                        |                  |

| γ         | Temperature coefficient                                            | 3.2                    | -                |

| α         | Temperature coefficient of the current source supplying the diodes | 1                      | -                |

| k         | Boltzmann's constant                                               | 1.38x10 <sup>-23</sup> | J/K              |

| q         | Charge of electron                                                 | 1.6x10 <sup>-19</sup>  | С                |

| T         | Absolute temperature                                               | -                      | K                |

| $T_0$     | Room temperature                                                   |                        | K                |

Table 2.1: Parameters of equations 2.4 and 2.5 (Allen, 2004)

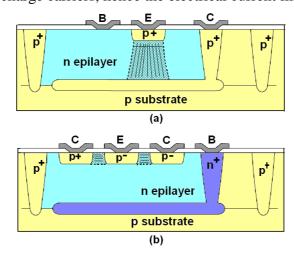

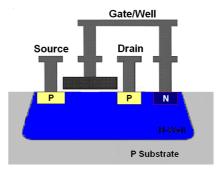

Unfortunately typical BJTs with optimized device structure are not available in standard CMOS processes and therefore these transistors must be built through parasitic devices. In general, there are two parasitic BJTs in CMOS process: vertical and lateral BJTs. The cross-section of (a) vertical PNP transistor and (b) lateral PNP transistor in CMOS p-substrate process can be seen in figure 2.1. The shaded area in the figure represents the flow of charge carriers, hence the electrical current lines.

Figure 2.1: Cross-section of (a) vertical (b) lateral PNP BJT in CMOS technology

As can be seen in figure 2.1 (a), the vertical BJT is built with a drain diffusion, n-well and p-substrate, that act respectively as emitter, base and collector. Once the substrate (collector) is always connected to the most negative supply voltage, the use of vertical devices is limited for certain applications where the grounded collector is

admissible. For circuits where it is necessary to control the voltage at the collector terminal, lateral PNP BJT is recommended.

However, parasitic devices present some disadvantages if compared to standard transistors. Due to the large base size, parasitic BJTs present a large base resistance and a high rate of recombination – which leads to a small value for the common-emitter current gain ( $\beta_F$ ). Such effects lead to a more difficult matching and a large possibility of latchup. But, if good layout techniques are applied in the design, these disadvantages can be significally reduced - what explains the large use of parasitic BJTs in BGR designs (Vermaas, 1998), (Cajueiro, 2002) and (Leung, 2004). Equation 2.7 describes beta gain and table 2.2 shows its parameters.

$$\beta_F = \frac{I_C}{I_B} \tag{2.7}$$

| Parameter                  | Description                 | Unit    |

|----------------------------|-----------------------------|---------|

| $oldsymbol{eta_{	ext{F}}}$ | Common-emitter current gain | -       |

| $I_{\rm C}$                | Collector Current           | A       |

| $I_{\mathrm{B}}$           | Base Current                | A       |

| $I_{S}$                    | Saturation current          | A       |

| $J_{\rm C}$                | Collector current density   | $A/m^2$ |

| n                          | Ratio of emitter areas      | -       |

Table 2.2: Parameters of equations 2.7 and 2.8

Up to this point, the reasons why the  $V_{BE}$  voltage has been vastly used as CTAT voltage have been discussed. But, how will the PTAT voltage needed to achieve the compensation proposed by equation 2.3 be generated?

The PTAT voltage can be obtained through the Thermal voltage. Equation 2.8 describes the temperature dependence of  $V_{TH}$  voltage, and its value is +0.087 mV/°C. (Razavi, 2001).

$$\frac{\partial V_{TH}}{\partial T} = \frac{V_{TH}}{T} \tag{2.8}$$

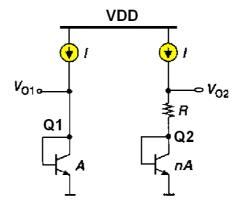

One way to generate the thermal voltage is from the difference between the emitter-base voltages ( $\Delta V_{BE}$ ) of two bipolar transistors. If these two devices differ only by their emitter area and are operated at the same  $I_C$  and temperature, the  $\Delta V_{BE}$  is given by equation 2.9 (Razavi, 2001). The parameters of 2.9 are also given by table 2.2.

$$\Delta V_{BE} = V_{BE1} - V_{BE2} = V_{TH} \cdot \ln \frac{J_{C1}}{J_{C2}} = V_{TH} \cdot \ln \left( \frac{I_{C1} \cdot I_{S2}}{I_{S1} \cdot I_{C2}} \right) = V_{TH} \cdot \ln(n)$$

(2.9)

Figure 2.2 shows one possible scheme to generate the  $\Delta V_{BE}$  voltage. If the voltages  $V_{O1}$  and  $V_{O2}$  are forced to be equal, using for example cascode devices,  $\Delta V_{BE}$  voltage appears across the resistor R.

Figure 2.2: Generation of V<sub>TH</sub> using two BJT's with different areas

In summary, following the concept expressed by equation 2.2, it is possible to generate a PTAT voltage ( $V_1$ ) and a CTAT voltage ( $V_2$ ) by means of  $V_{TH}$  and  $V_{BE}$  voltage using standard CMOS processes with parasitic BJTs. Section 2.2 presents the achieved output voltage when  $V_1$  and  $V_2$  are summed to produce the reference.

#### 2.2 Output voltage

Substituting  $V_{BE}$  and  $V_{TH}$  voltages in equation 2.2 and making  $\alpha 2$  equal to 1, the output voltage obtained is described by equation 2.10. Then, it is possible to design  $\alpha 1$  in such way that the output voltage shows zero temperature drift at room temperature.

$$V_{REF} = V_{RE} + \alpha 1 \cdot V_{TH} \tag{2.10}$$

After choosing a proper value for  $\alpha 1$ , one can prove that the value of  $V_{REF}$  at room temperature is given by 2.11, where  $V_{T0}$  is the thermal voltage at room temperature and the parameters  $\alpha$  and  $\gamma$  are given by table 2.1. Details of this deduction are presented in (Allen, 2004). Considering  $T_0 = 300$  K and typical values for other constants,  $V_{REF}$  has a value around 1.262 V, what is few milivolts higher than  $V_{G0}$  - explaining the reason for the name "Bandgap voltage reference".

$$V_{REF}|_{T=T0} = V_{GO} + V_{T0}(\gamma - \alpha)$$

(2.11)

Althought the negative TC of  $V_{BE}$  is cancelled by the positive TC of  $V_{TH}$  near the room temperature; the obtained  $V_{REF}$  still has temperature dependence of the order of 20 to 100 ppm/°C. One of the major reasons for this behavior is better explained through equations 2.12 and 2.13, which describe the temperature dependence of  $V_{BE}$  voltage (Tsividis, 1980). Equation 2.13 is the Taylor series expansion of equation 2.12. Table 2.3 explains all parameters of these equations.

$$V_{BE} = V_{G0} + V_{TH} \cdot \ln\left(\frac{D}{C}\right) - \left[\left(4 - N\right) - x\right] \cdot V_{TH} \cdot \ln T$$

(2.12)

$$V_{BE} = a_0 + a_1 T + a_2 T^2 + \dots + a_n T^n$$

(2.13)

Table 2.3: Parameters of equations 2.12 and 2.13

| Parameter       | Description                                                                                                                         |   |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------|---|--|

| $V_{BE}$        | Base-emitter voltage                                                                                                                | V |  |

| $V_{G0}$        | Bandgap energy of silicon extrapolated to zero Kelvin                                                                               |   |  |

| $V_{TH}$        | Thermal voltage                                                                                                                     | V |  |

| С               | Temperature-independent constant – comes from the saturation current.                                                               | - |  |

| D               | Temperature-independent constant – comes from the collector current.                                                                | - |  |

| N               | Temperature-independent constant – comes from average mobility for minority carriers in the base                                    | - |  |

| X               | Arbitrary number defined by the temperature dependence of the current forced through the collector, i.e., x is 1 to a PTAT current. | - |  |

| T               | Absolute Temperature                                                                                                                | K |  |

| $a_0, a_1, a_n$ | Constants of the Taylor series expansion                                                                                            | - |  |

As can be verified through equation 2.12, the  $V_{BE}$  voltage is not exactly complementary to the absolute temperature; it has a non-linearity described by the multiplication of the temperature by the logarithm of temperature. Equation 2.13 provides another way to see this non-linearity through the Taylor expansion of 2.12.

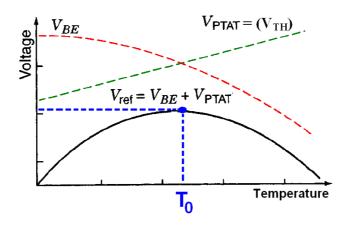

When the sum of  $V_{BE}$  and  $V_{TH}$  (Linear term) is evaluated, only the linear part of  $V_{BE}$  voltage is offset. The term T\*ln(T) is not compensated, what explains the remaining temperature-dependence of the output voltage even after the sum. Figure 2.3 represents graphically the topics discussed in the last two paragraphs.

Figure 2.3: Typical Curvature of first-order  $V_{REF}$  over temperature range From figure 2.3, it is possible to add some observations:

$\bullet$  The maximum value of  $V_{REF}$  is at room temperature, that is, the point where the derivation of the output voltage in relation to temperature assumes the value described by equation 2.11. At room temperature, the term  $V_{BE}$  is exactly equal to the  $V_{TH}$ .

- $\bullet$  For temperatures below  $T_0$ , the non-linear term of  $V_{BE}$  is small and therefore, it is the  $V_{TH}$  term that dominates the behavior  $V_{REF}$  increases with temperature.

- $\bullet$  For temperatures above  $T_0$ , the non-linear term of  $V_{BE}$  increases faster, in such a way that it dominates the behavior  $V_{REF}$  decreases with temperature.

In this section, the output voltage generated through the Bandgap concept and the performance achieved were discussed. For many applications the achieved performance of 20 to 100 ppm/°C is fully enough, and because of this reason, BGR circuits became maybe the most widespread technique to provide voltage references. Section 2.3 shows a historical view about this technique.

#### 2.3 Historical View

In the 60's, one of the most used voltage references was the Zener diode. The extensive use of this technique was due to its good performance, such as 10 to 50 ppm/°C over moderate temperature ranges. However, the high value of the breakdown voltage, the noise performance, the poor long-term stability and its variability due the fabrication process of this device, lead to a search for alternative solutions for voltage references.

The Bandgap principle was proposed by Hilbeber (1964), but was only in Widlar (1971) that the first integrated regulator using a Bandgap Voltage Reference was presented. Figure 2.4 presents the simple form of this reference.

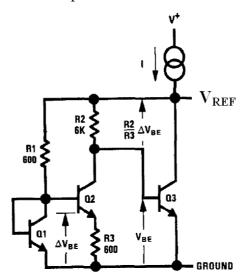

Figure 2.4: Integrated voltage reference proposed by (Widlar, 1971)

The proposed Bandgap reference using bipolar technology works as explained in sections 2.1 and 2.2, generating an output voltage of 1.205 V. In this circuit, Q1 is operated with a current density 10 times larger than Q2 and consequently, the  $\Delta V_{BE}$  voltage appears across R3. Using transistors with high-gain, the voltage across R2 will also be proportional to the  $\Delta V_{BE}$  voltage. Thus, using transistor Q3, the output voltage is forced to be equal to  $V_{BE3}$  plus a constant multiplied by the  $\Delta V_{BE}$  voltage, as suggested by equation 2.10. More specifically, the output voltage is given by 2.14, where the aspect ratio of resistors R2 and R3 will define the temperature compensation.

$$V_{REF} = V_{BE_{Q3}} + \frac{R2}{R3} \cdot V_{TH} \cdot \ln(10)$$

(2.14)

The good performance and the viability offered by the BGR technique resulted in a large use of this method and the emergence of different implementations, each one suitable for a different application.

In Tzanateas (1979) one of first implementations of CMOS Bandgap reference is proposed. Using a standard process with MOS transistors operating in the weak inversion region and one parasitic BJT, a BGR that achieved 70 ppm/ $^{\circ}$ C of temperature performance was designed. The MOS transistors operating in weak inversion were used to build the thermal voltage, instead of using the  $\Delta V_{BE}$  of two BJTs. Please note that the behavior of MOS transistors operating in weak inversion (subthreshold) is similar to the behavior of BJT's, where the current has an exponential relationship with the control voltage. The drain current of the MOSFET in subthreshold operation is roughly described by equation 2.15 (Allen, 2004). Table 2.4 explains the parameters of this equation.

$$I_D \cong \frac{W}{L} \cdot I_{D0} \cdot \exp\left(\frac{V_{GS}}{nV_{TH}}\right)$$

(2.15)

|                     |                                                               | TT 1. |

|---------------------|---------------------------------------------------------------|-------|

| Parameter           | Description                                                   | Unit  |

| $V_{GS}$            | Gate-source voltage                                           | V     |

| $\overline{I_{D0}}$ | Process Constant. It also depends of V <sub>SB</sub> (Source- | A     |

|                     | Bulk voltage) and V <sub>T</sub> (threshold voltage)          |       |

| n′                  | Subthreshold slope factor                                     | -     |

| W                   | Channel Width                                                 | μm    |

| L                   | Channel Length                                                | μm    |

Table 2.4: Parameters of equation 2.15

Due to the need of more precise voltage references, in the years 1980's works emerged that investigated techniques to reduce the non-linearity of Bandgap reference and thus, achieve greater temperature-performance.

In Tsividis (1980) a carefully investigation about the temperature effects in  $I_C$ - $V_{BE}$  characteristics with application to BGR's was presented. It was shown that the main cause of disagreement between the theoretical equation for  $V_{BE}(T)$  (base-emitter voltage in function of temperature) and the measured data, is due to the wrong assumption that the silicon Bandgap voltage varies linearly with the temperature. This wrong supposition led to errors in predicting the output voltage of BGRs. The temperature-dependence of  $V_{BE}$  was discussed in detail, and some suggestions to improve the accuracy achieved by the Bandgap references were presented. The equation for  $V_{BE}(T)$  presented in that work is equation 2.13, presented in section 2.2.

As already discussed in section 2.2, Tsividis clarified the need to thermally cancel not only the first term, but also the high-order terms of equation 2.13 to allow a better temperature performance. This work was the base for high-accuracy Bandgap designs.

One of the suggestions of Tsividis was implemented by (PALMER, 1981). This work proposed a Curvature-Corrected Bandgap reference that implements the thermal compensation of the nonlinearity of  $V_{BE}$  by means of the inclusion of another non-linear with opposite temperature coefficient. For one output voltage of 5 V, it was possible to achieve only  $\pm 0.02\%$  of variation over temperature range from -55 to 125°C.

Nicollini (1991) proposed a switched-capacitor fully differential Bandgap reference suitable for applications that require good PSRR, for instance, telephony and audio processing systems. Making use of standard CMOS process, a fully differential approach and without the need of any trimming in mass production, it was possible to achieve a typical performance of 15.2 ppm/°C and about 90 dB up to 500 kHz of power supply rejection.

Nowadays, the traditional high-accuracy BGR's is not enough anymore to satisfy the requirement of the current electronic applications. Due the increasing demand for low-power portable equipments, low-voltage and low-power operation becomes essential for any analog block. In Malcovati (2001), a Curvature-Compensated BiCMOS Bandgap with 1-V Supply voltage was proposed. This circuit has an output voltage of 0.54 V, 7.5 ppm/°C of temperature performance and only 92µW of power consumption at room temperature. One disadvantage of this technique is the need of a 0.8-µm BiCMOS process to permit low-voltage operation of the operational amplifier used in this design – what increases the cost of fabrication.

Another method to reduce the supply voltage was present in Kim (2008). With a hybrid design, discrete Ge (Germanium) diodes - whose Bandgap voltage is only 0.6 V - and a silicon chip connected through one printed circuit board, it was possible to achieve an output voltage reference of 310 mV with a 302 ppm/°C TC at 1V of supply voltage. Nevertheless the use of discrete diodes is not compatible with the need for fully integration demanded by recent applications.

In summary, more than forty years have passed since the Bandgap technique was first proposed, and today it is a commercial reference used in the design of a large number of applications. Moreover, this technique is still the subject of many research works, where the current focus is to adapt the BGR method to design in submicrometer technologies. We finish this section with table 2.5 showing a comparison of the BGRs discussed. In Colombo (2008) is also presented a wide comparison between different Bandgap Circuits. Annex A presents a table with a few examples of commercial BGR chips and its performance parameters.

| Work            | Temp.<br>Performance | VDD<br>(V) | Power<br>Consumption | Process |

|-----------------|----------------------|------------|----------------------|---------|

|                 | (ppm/°C)             | ` '        | $(\mu W)$            |         |

| WIDLAR, 1971    | ≈ 30                 | 5          | -                    | Bipolar |

| TZANATEAS, 1979 | 70                   | 3.5        | 10                   | CMOS    |

| PALMER, 1981    | ≈ 3                  | 10         | 2000                 | Bipolar |

| NICOLLINI, 1991 | 15.2                 | ± 5        | 4800                 | CMOS    |

| MALCOVATI, 2001 | 7.5                  | 1          | 92                   | BiCMOS  |

| KIM, 2008       | 302                  | 1          | -                    | Hybrid  |

## 3 BANDGAP VOLTAGE REFERENCES DESIGNED

After understanding the Bandgap idea and its origins, this chapter supports and develops our study presenting three BGR's designed using IBM 0.18 Micron 7RF technology. The IBM technology is a standard CMOS process that presents a vertical BJT's and its parameters are shown in Annex B

The types of the implemented BGRs were chosen because their topologies are the basis for the more complex Bandgap architectures, and then, comprehending its principles it is possible to understand the issues involving any BGR. Furthermore, to have a more comprehensive study of the impact of noise and the variability, we have opted to choose three circuits with different performance.

All Voltage References were designed to operate in the temperature range of -55 to 125°C, and with a supply voltage variation of 1.7 to 1.9 V. The order which these circuits are here presented is related to their achieved performance.

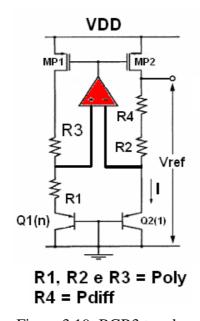

#### 3.1 BGR1

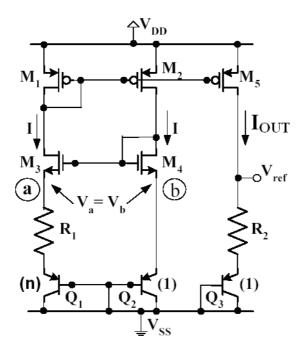

Every BGR presents a balanced sum of two voltages with opposite temperature coefficient to achieve a good temperature performance. As already explained, the most common voltages used in this addition are the  $V_{BE}$  and  $V_{TH}$  produced by means of parasitic BJT's. The first Bandgap Reference (BGR1) implements this concept through the architecture depicted in figure 3.1.

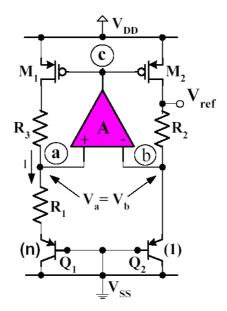

Figure 3.1: BGR1

This circuit is a well-know BGR topology (Gray, 2001) that achieves good performance with a very simple structure. The reference uses a "bootstrapped" current mirror to reduce the power supply dependency. The transistors  $M_3$  and  $M_4$  force nodes A and B to be of equal voltage, and once the  $Q_1$  area is n times bigger than  $Q_2$ , a PTAT voltage appears across  $R_1$ . Equation 3.1 describes the current flowing through  $R_1$ .

$$I = \frac{\Delta V_{BE}}{R_1} = \frac{V_{TH} \cdot \ln(n)}{R_1} \tag{3.1}$$

The bulk of the NMOS and PMOS devices are respectively connected to VSS and VDD. Transistors  $M_1$  and  $M_2$  have the same dimensions and the output current  $I_{OUT}$  is given by equation (3.2).

$$I_{OUT} = \left(\frac{(W/L)_5}{(W/L)_1}\right) \cdot I \tag{3.2}$$

Thus, the output voltage is described by equation (3.3). Observe that 3.3 has the same form of equation 2.10, where  $\alpha 1$  (adjust factor) is given by (3.4). Remember now that the TC of  $V_{BE}$  voltage and the  $V_{TH}$  are respectively, roughly -1.5 mV/°C and exactly +0.087 mV/°C. Accordingly, the adequate value for  $\alpha 1$  is about 17, for the voltage reference to achieve the temperature compensation. The exact value of  $\alpha 1$  depends on several variables, but mainly on the bias point, the type of the BJT (typical, vertical or lateral), the TC of the resistors and the room temperature  $T_0$ .

$$V_{REF} = V_{BE3} + \left(\frac{(W/L)_5}{(W/L)_2}\right) \cdot \frac{R2}{R1} \cdot \ln(n) \cdot V_T$$

(3.3)

$$\alpha 1 = \left(\frac{(W/L)_5}{(W/L)_2}\right) \cdot \frac{R2}{R1} \cdot \ln(n) \tag{3.4}$$

In general, the curve of  $V_{REF}$  is designed to flatten to a zero-derivative at the room temperature, but this is not a requirement. However, considering that this assumption is true, there will be different values of  $\alpha 1$  for each specific  $T_0$ . Figure 3.2 shows each curve (for different  $\alpha 1$  values) for three different room temperatures. Note that the point where each curve flattens to zero is labeled as  $T_0$ .

Figure 3.2: V<sub>REF</sub> as a function of temperature and different value of T<sub>0</sub>

Section 3.1.1 presents details about the implementation, such as transistors size and design decisions focusing on good performance. Section 3.1.2 shows the startup circuit. The layout of this circuit is presented in section 3.1.3 and we finish with the post-layout simulation results in section 3.1.4.

#### 3.1.1 Implementation Details

Here a series of decisions taken into account in our design are presented:

- (a) The channel length modulation negatively impacts the output performance, and hence should be reduced. Thus large transistor channel lengths were used in the design.

- (b) The overdrive voltage  $(V_{OV})$  was assumed to be between 150 and 200 mV, and consequently, the weak inversion operation was avoided and more voltage headroom was provided.

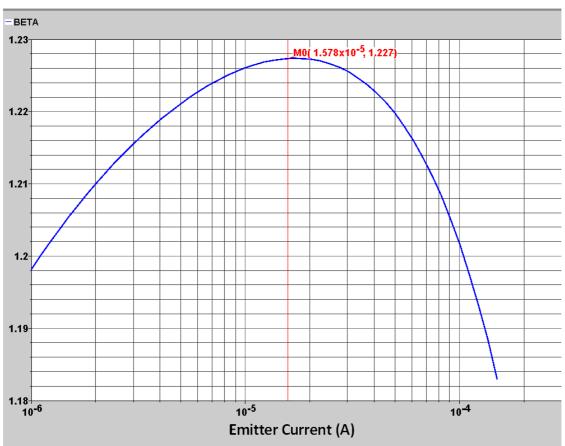

- (c) Current I described by equation 3.1 was defined based on the tradeoff between minimization of resistors area, minimization of consumed power and the matching between the bipolar transistors. Figure C.1, in Appendix C, shows that the  $\beta_F$  of the vertical BJT is very small and depends on the bias collector current which is not good for matching. However, it is reported in Vermaas (1998) that the best choice for matching is to bias the bipolar device in such way that the  $\beta_F$  is large and constant. Hence, in our design, the emitter current was chosen to achieve a large and constant value for  $\beta_F$ .

- (d) The room temperature was defined to be in the middle of the temperature range (35°C). This helps to reduce the output variation over the whole temperature range.

- (e) To reduce the mismatching due the fabrication process and the flicker noise generated by MOSFET's, these devices were designed to have a large area. Chapter 4 discusses the variability and the output noise of BGR's.

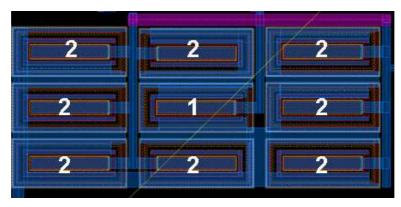

- (f) To allow a good layout matching between the bipolar transistors,  $Q_1$  was designed to be 8 times larger than  $Q_2$ . Values larger that 8 are not adequate, as the separation of the devices increases and more errors are introduced. Moreover, a large area will be spend with a little increment in the ln(n) function equation 3.1

- (g) To allow a good layout matching between the resistors, they were designed to have the same size, then enabling a common centroid configuration.

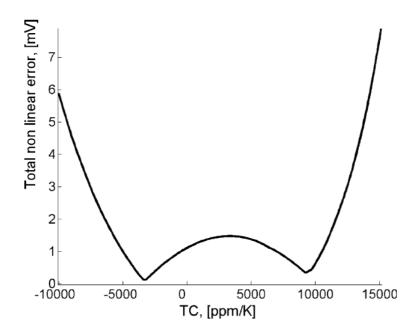

- (h) The type of resistors was chosen based on their TC's, resistivity and the matching properties. The temperature dependence of the resistor influences the reference performance. More specifically, it was shown in Falconi (2005) that appropriate choice of the resistor material can significally reduces the non-linearity of the output reference and then, achieves a better temperature performance. For the task of choosing the resistor material, analog simulation is fundamental. Figure C.2, in Appendix C, shows an illustration of the output curvature for different resistors with different TC's. In our case, P<sup>+</sup> Poly silicon resistor presents the best tradeoff between resistivity, matching properties and non-linearity reduction. This resistor presents a TC equal to 160 ppm/°C (IBM, 2005).

Following all decisions listed above, the transistors in the circuit were sized. Table 3.1 shows the final size of transistors, the value of the resistors and the aspect area ratio of the BJT's. The dimensions used in the layout are also shown.

| Device            | Design<br>Dimensions            | Layout<br>Dimensions                    | Units           |

|-------------------|---------------------------------|-----------------------------------------|-----------------|

| M <sub>1,2</sub>  | $\frac{W}{L} = \frac{97.52}{5}$ | $8 \times \left(\frac{12.19}{5}\right)$ | <u>μm</u><br>μm |

| M <sub>3,4</sub>  | $\frac{W}{L} = \frac{70}{7}$    | $4 \times \left(\frac{17.5}{7}\right)$  | <u>μm</u><br>μm |

| M <sub>5</sub>    | $\frac{W}{L} = \frac{354}{3}$   | $40 \times \left(\frac{8.85}{3}\right)$ | <u>μm</u><br>μm |

| R <sub>1, 2</sub> | 3                               | 3×1                                     | $K\Omega$       |

| Q <sub>1</sub>    | 8×A2                            | 8×A2                                    | -               |

| $Q_2$             | A2                              | A2                                      | -               |

Table 3.1: Size of transistors and value of the resistor of BGR1

#### 3.1.2 Startup-Circuit

One point that should be carefully analyzed in the BGR design is the operation point stability. The BGR1 circuit presents two possible points of operation: the first one

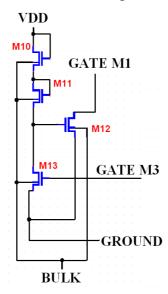

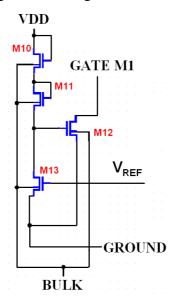

showing the biasing current equal to zero, and the second one showing the current equal to the value described by equation 3.1. Therefore, it is necessary to use a start-up circuit to force the correct operation point. Figure 3.3 shows the start-up circuit inserted in the BGR circuit – this circuit is very similar to the one present in Brito (2007).

Figure 3.3: Start-up Circuit of BGR1

The Start-up circuit works as follows. Suppose the circuit with the biasing current equal to zero even if the VDD voltage is applied – the wrong operation point. Thus, it is possible that the gate of transistor  $M_1$  is at a high voltage that causes a  $V_{SG\_M1}$  less than  $V_T$  (Threshold Voltage), making current conduction impossible. Without current, the BJT's are not in forward operation and probably the gate of  $M_3$  has low value in such way that  $V_{GS\_M3}$  is less than  $V_T$ . In such a situation, device  $M_{13}$  of the start-up circuit is cut-off and  $M_{12}$  enters in conduction, since its gate is connected to VDD – Devices  $M_{10}$  and  $M_{11}$  are always in conduction. Thus, the gate of  $M_1$  is connected to ground, forcing  $V_{SG\_M1}$  to be greater than  $V_T$  and putting the BGR circuit to its corrected operating point.

With the reference in operation, the gate  $M_3$  is above threshold, which makes  $M_{13}$  to enter in conduction. Accordingly, the gate of  $M_{12}$  is connected to ground, which leads to its cut-off – disconnecting the start-up circuit from the Bandgap Reference. This disconnection is important to avoid that the start-up circuit affects the performance of the voltage reference.

Two observations about the size of start-up devices are done here. Since the transistors  $M_{10}$  and  $M_{11}$  are always conducting, they were design with larger channel lengths to increase the resistance – what leads to less power consumption of this auxiliary circuit. Devices  $M_{12}$  and  $M_{12}$  were designed with the minimum channel length to provide a low-resistance path to the ground and make the start-up procedure faster. Table 3.2 shows the devices sizes and start-up time of this auxiliary circuit.

| Devices | Design                            | Layout                            | Units           |

|---------|-----------------------------------|-----------------------------------|-----------------|

|         | Dimensions                        | Dimensions                        |                 |

| M10, 11 | $\frac{W}{L} = \frac{1}{15}$      | $\frac{W}{L} = \frac{1}{15}$      | <u>µт</u><br>µт |

| M12, 13 | $\frac{W}{L} = \frac{0.40}{0.18}$ | $\frac{W}{L} = \frac{0.40}{0.18}$ | μm<br>μm        |

Table 3.2: Size of devices in Start-up circuit of BGR1

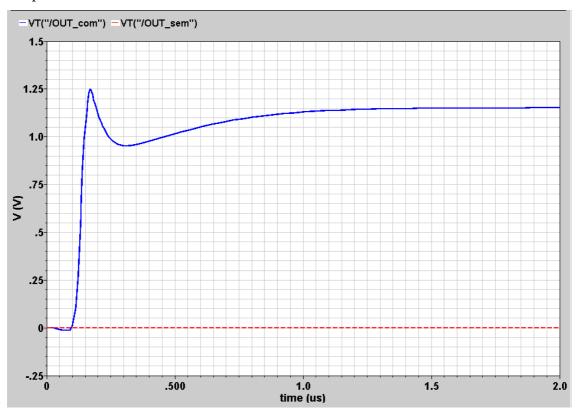

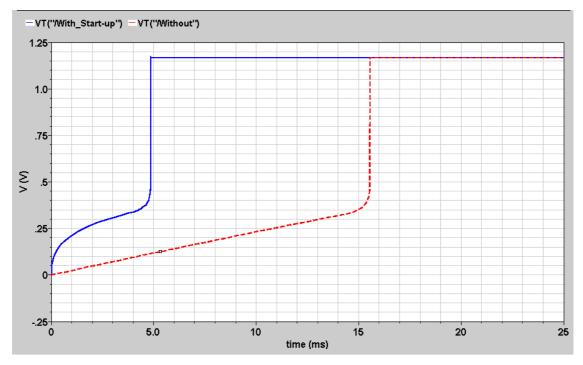

Figure 3.4 shows the importance of this auxiliary circuit in case of operation at the wrong point. Two BGR's circuits were simulated, one with and another one without the startup circuit in a forced wrong operation point. The circuit with start-up enters in stable conduction after about 2.7  $\mu$ s while the other circuit remains in cut-off. In fact, it is well known that fabricated circuits will hardly remain in the wrong operation point, due the noise and the existing fabrication mismatches. However, the time of the start-up procedure can be large for many applications and then, the auxiliary circuit provides a faster operation.

Figure 3.4: Start-up Time of BGR1 with and without (Dotted Line) start circuit

#### 3.1.3 Layout of BGR1

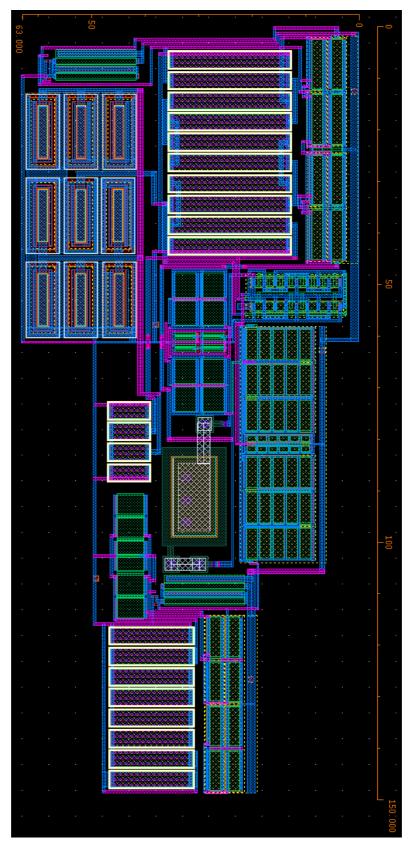

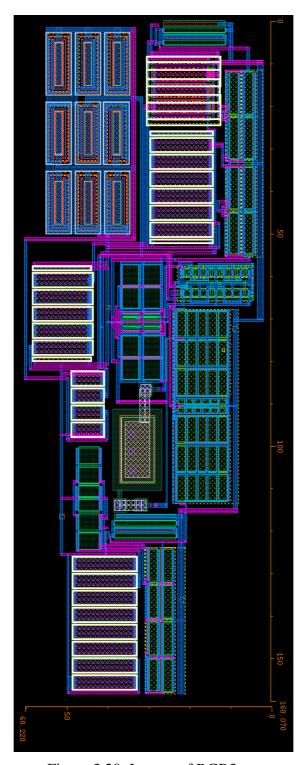

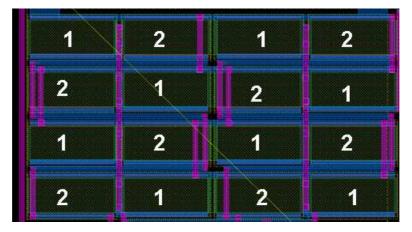

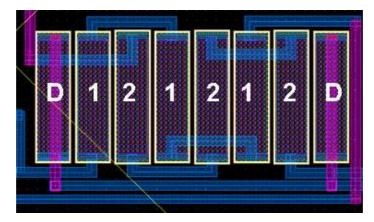

Figure 3.5 shows the layout of the BGR1. The total used area is less than 123 x 89  $\mu m^2$ . The layout of the PNP vertical BJT is provided by the foundry and it can not be changed. Good layout techniques such as common centroid configuration and dummy

devices were used to allow a good matching between the MOSFET's, BJT's and resistors. Appendix B shows more details about the applied layout techniques.

Figure 3.5: Layout of BGR1

#### 3.1.4 Post-Layout Simulation results

After concluding the layout, the extraction of the circuit parasitics was performed. Afterwards, the circuits were simulated to verify the temperature performance, line regulation, power consumption and the power supply rejection. Table 3.3 shows the results obtained.

| Parameter                | Value        | Unit |

|--------------------------|--------------|------|

| V <sub>REF</sub> @ 27 °C | 1.152        | V    |

| $\Delta V_{REF\_TEMP}$   | 3            | mV   |

|                          | (26 ppm/ °C) |      |

| Temp. Range              | -55 to 125   | °C   |

| Line Regulation          | 7            | mV   |

| (VDD: 1.7 – 1.9)         | (35 mV/V)    |      |

| VDD                      | 1.8          | V    |

| $I_{ m Supply}$          | 147.4        | μΑ   |

| PSR @ 1 kHz              | 29           | dB   |

Table 3.3: Post-Layout Simulation Results of BGR1

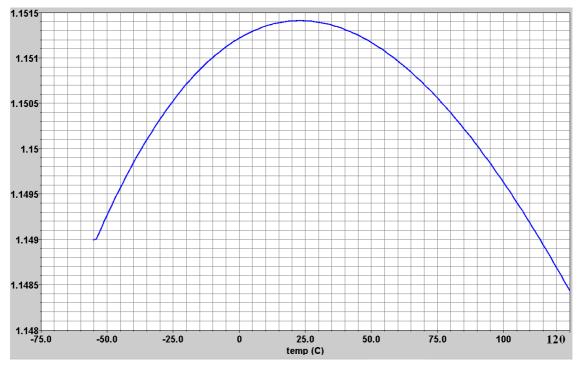

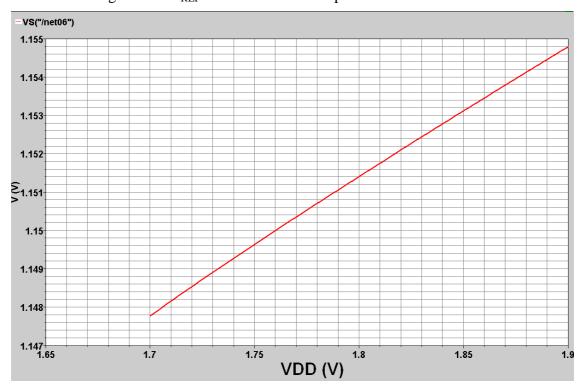

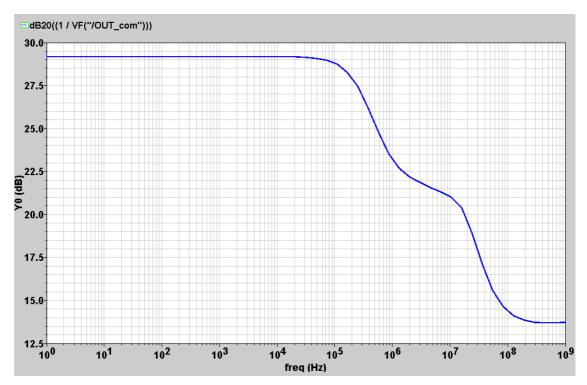

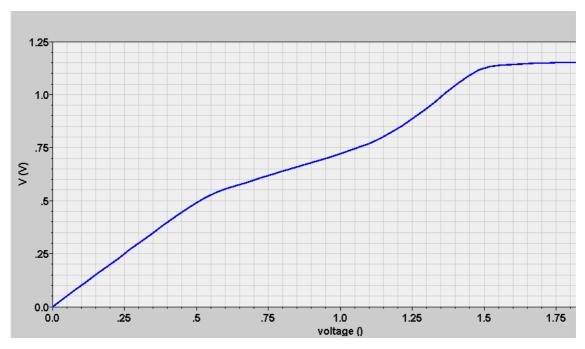

Figures 3.6-3.8 show respectively, the  $V_{\text{REF}}$  as a function of temperature, the line regulation performance and the power supply rejection.

Figure 3.6:  $V_{REF}$  as a function of temperature of BGR1

Figure 3.7: Line Regulation for BGR1 (1.7 – 1.9V)

Figure 3.8: PSR of BGR1

The obtained TC of 25 ppm/°C is in close agreement to the first order Bandgap voltage references; in Annema (1999) it is reported that output voltage variation in the temperature range of - 40 to 120 °C is around 4 mV.

As can be seen in table 3.3 the worst performance parameter is the line regulation, with a value equal to 7 mV for a variation of the supply voltage equal to  $\pm$  100mV. This data shows that the current mirror and the voltage-clamping composed by M1-M5 are not effective at different supply voltages. One reason for the large output variation is the channel length modulation. The values of channel length used in the current source transistors are already big, and then increasing these values will not contribute in a significant way to reduce the channel length modulation. One way to reduce the supply voltage dependence would be the insertion of cascode devices in the current mirror, increasing the output resistance. However, the low-supply voltage of 1.8 V makes device cascoding impossible. One alternative to favour the insertion of cascode devices is to use triple-well NMOS devices (IBM, 2005). Through these devices, it is possible to reduce the bulk-effects and provide a better use of the voltage headroom. This solution frequently requires extra-fabrication steps, which would lead to increased cost.

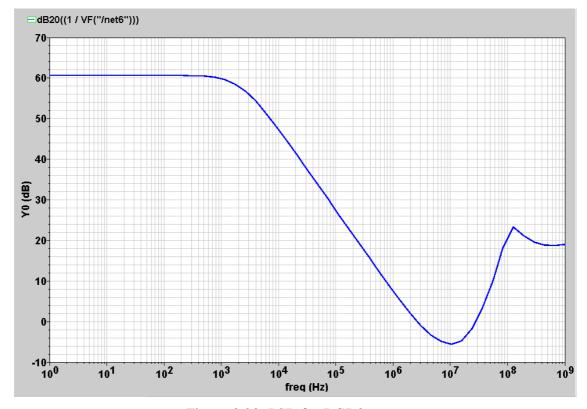

Besides the high-VDD dependence, this architecture achieves a poor power supply rejection rate of 29 dB at low-frequency. The next topology to be studied, BGR2, is less sensitive to VDD and presents a better PSR.

#### 3.2 BGR2

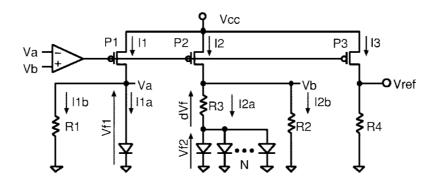

The second implemented Bandgap Voltage Reference (BGR2) was proposed initially in Gregorian (1981). This popular topology achieves the same temperature coefficient as BGR1, however, using an error-amplifier-based current mirror it is possible to obtain a better line regulation performance. Figure 3.9 shows the BGR2 architecture.

Figure 3.9: BGR2 using error-amplifier-base current mirror

Using an error-amplifier with a high voltage gain A, it is possible to get equal voltages at the nodes A and B, since the negative feedback is provided. The negative feedback is guaranteed because the negative feedback factor  $\beta_N$  is greater than the positive feed factor  $\beta_P$ .

The resistors  $R_2$  and  $R_3$  are designed to be matched, what leads to  $V_{DS1} = V_{DS2}$  for the matched devices  $M_1$  and  $M_2$ . As a consequence, the BJT's are supplied by equal currents given by equation 3.5

$$I = \frac{\Delta V_{BE}}{R_1} = \frac{V_{TH} \cdot \ln(n)}{R_1} \tag{3.5}$$

If we consider that the Offset voltage  $(V_{OS})$  of the amplifier is zero,  $V_{REF}$  is described by equation (3.6). Observe again that 3.6 also has the form of equation 2.10, where the adjust factor  $(\alpha 1)$  is given by (3.7). Therefore, the resistor aspect ratio and the bipolar areas should be designed to achieve  $\alpha 1$  roughly equal to 17.

$$V_{REF} = V_{BE2} + \left(\frac{R_2}{R_1}\right) \cdot \ln(n) \cdot V_T \tag{3.6}$$

$$\alpha 1 = \left(\frac{R2}{R1}\right) \cdot \ln(n) \tag{3.7}$$

Section 3.2.1 shows details about the implementation such as, transistors size and design decisions focusing in good performance. Section 3.2.2 shows the startup circuit. The layout of this circuit is presented in section 3.2.3 and we finish with the post-layout simulation results in section 3.2.4.

#### 3.2.1 Implementation Details

Alls decisions taken into account in the design of BGR1 were also considered in the design of BGR2. Moreover, other issues were investigated, for instance, the architecture of the error-amplifiers.

In the literature, several types of topologies are used to implement the "error amplifier". In Kourdounas (2007) and Xing (2007) Operational Transconductance Amplifier (OTA) with 2-stages were used. In Leung (2004) and Tom (2004) a simple differential pair is used to implement this function. In addition, Mok (2004) defends the use of the simplest architecture due to its reduced offset and the easy matching that this topology achieves. In summary, the architecture choice depends on the constrains of the system for which the reference is intended, such as area occupied, accuracy, low-voltage and low-power operation. However, regardless of the architecture used, it must provide high gain. The errors in the PTAT voltage generation are inversely proportional to the gain. Frequently, open loop gains higher than 60 dB are used in this design. Another issue that must be carefully analyzed is the stability of the error-amplifier, and in this case, it is often necessary to use compensation to avoid instability.

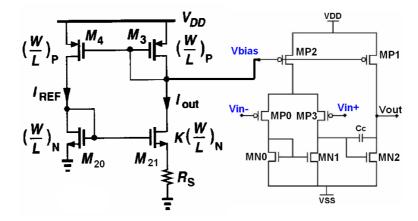

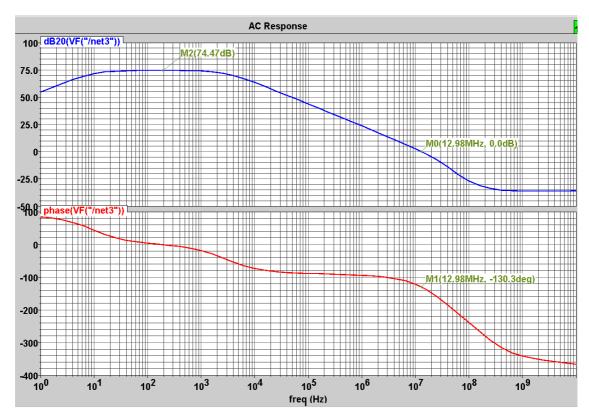

In our case, considering that the gain can be reduced after fabrication, we decided to design an amplifier with more than 70 dB of gain and a phase margin greater than 45°. A Compensated OTA with two stages was chosen to implement the error amplifier. Figure 3.10 illustrates the op-amp circuit and the supply independent current source used to bias it. Figure C.3, in appendix C, shows the Bode diagram of the OP-AMP. To ensure that the bias circuit does not become instable, transistor  $M_{21}$  is designed with a width 3 times larger than that of  $M_{20}$  (Sedra, 1997).

Figure 3.10: OTA with 2-stages and its bias circuit

Table 3.4 shows the simulation results for the amplifier and table 3.5 shows the final size of transistors, the value of the resistors and the aspect area ratio of the BJT's. The dimensions used in the layout are also shown.

|                | Value | Unit |

|----------------|-------|------|

| Open-loop gain | 74    | dB   |

| Phase Margin   | 50    | 0    |

| Bandwidth      | 13    | MHz  |

Table 3.4: Simulated results for the error-amplifier

Table 3.5: Size of transistors and value of the resistor of BGR2

| Device              | Design<br>Dimensions              | Layout<br>Dimensions                     | Units              |

|---------------------|-----------------------------------|------------------------------------------|--------------------|

|                     |                                   | OP-AMP                                   |                    |

| $M_{P2}$            | $\frac{W}{L} = \frac{11.25}{1.5}$ | $5 \times \left(\frac{2.25}{1.5}\right)$ | <u>μm</u><br>μm    |

| $M_{P1}$            | $\frac{W}{L} = \frac{174.2}{2}$   | $20 \times \left(\frac{8.71}{2}\right)$  | μm<br>μm           |

| M <sub>P0, P3</sub> | $\frac{W}{L} = \frac{11.6}{1.5}$  | $8 \times \left(\frac{1.45}{1.5}\right)$ | μm<br>μm           |

| M <sub>NO,N1</sub>  | $\frac{W}{L} = \frac{1.6}{4}$     | $4 \times \left(\frac{0.4}{1.5}\right)$  | μm<br>μm           |

| $M_{\rm N2}$        | $\frac{W}{L} = \frac{37.4}{4}$    | 37.4<br>4                                | <u>μ</u> т<br>μт   |

| $C_{\rm C}$         | 500f                              | 500f                                     | F                  |

|                     | Independent-Sup                   | ply Voltage Current                      | Source             |

| M <sub>3,4</sub>    | $\frac{W}{L} = \frac{30}{2}$      | $4 \times \left(\frac{7.5}{2}\right)$    | μm<br>μm           |

| $M_{20}$            | $\frac{W}{L} = \frac{5}{5}$       | $\frac{5}{5}$                            | <u>μm</u><br>μm    |

| M <sub>21</sub>     | $\frac{W}{L} = \frac{15}{5}$      | $\frac{15}{5}$                           | <u>μm</u><br>μm    |

| $R_S$               | 7.4                               | 6×1.2332                                 | $K\Omega$          |

|                     | 0.                                | ther Devices                             | <u> </u>           |

| Q1                  | 8×A2                              | 8×A2                                     | -                  |

| Q2                  | A2                                | A2                                       | -                  |

| R <sub>2,3</sub>    | 7.5                               | 4×1.875                                  | $K\Omega$          |

| $R_1$               | 1.1                               | 2×0.550                                  | $K\Omega$          |

| M <sub>1,2</sub>    | $\frac{W}{L} = \frac{38}{2}$      | $4 \times \left(\frac{9.5}{2}\right)$    | <u>μ</u> ιπ<br>μιπ |

## 3.2.2 Start-up Circuit

The BGR2 also requires a start-up circuit to avoid the wrong operation point. This auxiliary circuit is the same used in BGR2 and the connections are shown in figure 3.11.

The analysis is similar to that presented for BGR1 and the start-up procedure was simulated, as shown in figure 3.12, The reference with the start-up circuit entered in operation after 5 miliseconds, while the circuit without start-up started conduction after 15 milisenconds. The large time of start-up indicates that the size of  $M_{12}$  transistor should be increased to permit a greater driving current.

Figure 3.11: Start-up circuit used in BGR2

Figure 3.12: Start-up time of BGR2 with and without (dot line) start-circuit

#### 3.2.3 Layout of BGR2

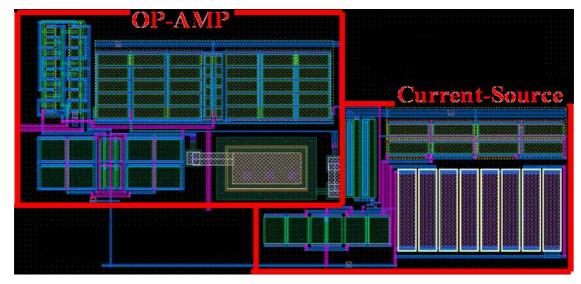

Figure 3.13 shows the layout of BGR2. The layout was done manually and the total area used is less than 63 x 150  $\mu$ m<sup>2</sup>, which is almost the same size of BGR1. Good layout techniques were also applied in this design. Figure 3.14 shows the layout of the

operational amplifier and its current source in detail. One can see that the bias circuit has approximately the same size of the error-amplifier due to the large size of the resistors. The compensation capacitor is implemented with Metal-Insulator-Metal (MIM) material.

Figure 3.13: BGR2 layout

Figure 3.14: Layout of error-amplifier and its bias circuit

#### 3.2.4 Post-Layout Simulation Results

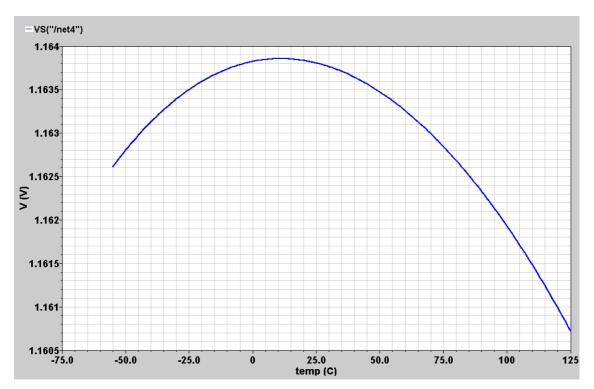

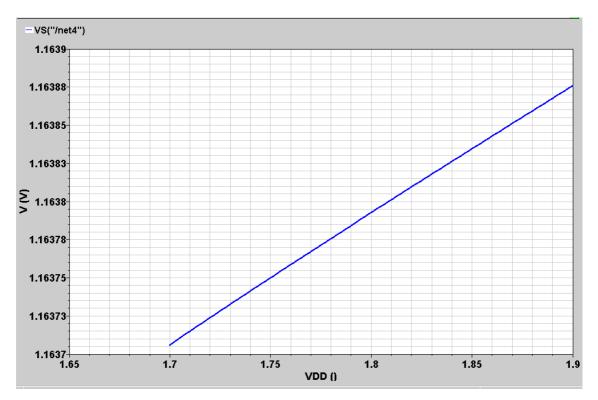

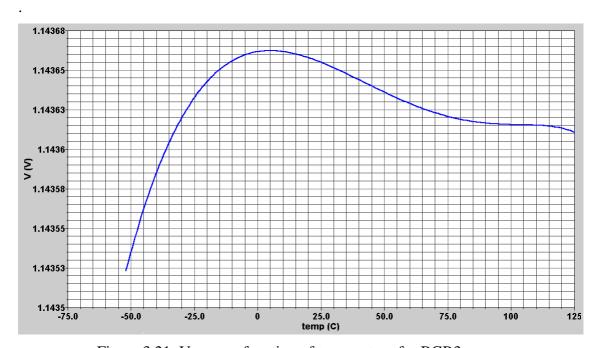

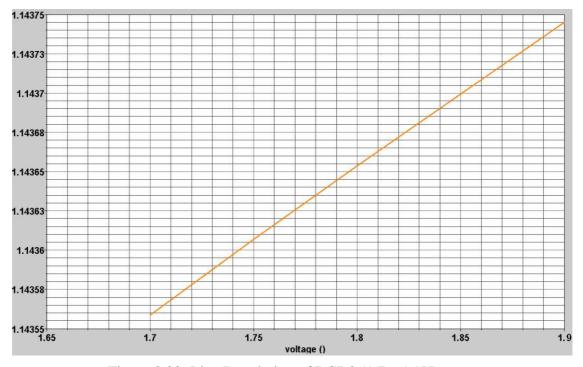

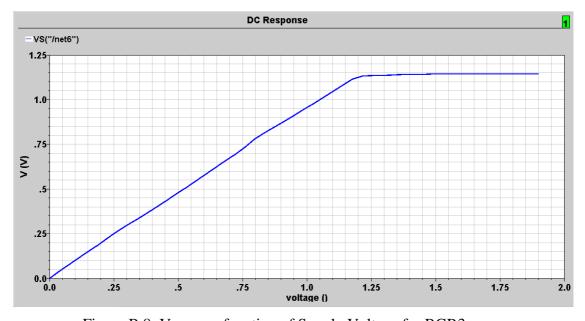

In a similar way as for BGR1, post layout simulation, after parasitics extraction, as run to verify the temperature performance, the line regulation and the PSR. Table 3.6 shows post-layout simulation results. Figures 3.15-3.17 show respectively, the  $V_{REF}$  as a function of temperature, the line regulation performance and the power supply rejection.

| Parameter                | Value        | Unit |

|--------------------------|--------------|------|

| V <sub>REF</sub> @ 27 °C | 1.166        | V    |

| $\Delta V_{REF\_TEMP}$   | 3.12         | mV   |

|                          | (24 ppm/ °C) |      |

| Temp. Range              | -55 to 125   | °C   |

| Line Regulation          | 170          | μV   |

| (VDD: 1.7 – 1.9)         | (0.85  mV/V) |      |

| VDD                      | 1.8          | V    |

| I <sub>Supply</sub>      | 262          | μΑ   |

| PSR @ 1 kHz              | 60           | dB   |

Table 3.6: Post-Layout Simulation Results of BGR2

As can be seen on table 3.6, BGR2 presents the same temperature performance as BGR1. However, it presents an improvement of 40 times in terms of line regulation. With almost the same area used, and 1.7 times more power consumption, it was possible to achieve an improvement of more than 15 dB in the power supply rejection. However, the temperature drift of 24 ppm/ °C may be not enough to achieve the performance requirements of many applications, for instance, for high-resolution data-converters. Hence, Bandgap architectures that correct the curvature of the output voltage should be used. Section 3.3 shows the design of a second-order BGR.

Figure 3.15:  $V_{\text{REF}}$  as a function of temperature for BGR2

Figure 3.16: Line Regulation for BGR2 (1.7 - 1.9 V)

Figure 3.17: PSR for BGR2

#### 3.3 BGR3

As already introduced in section 2.2, one of the main contributors for the output voltage curvature is the non-linear dependency of  $V_{BE}$  voltage – described by equation 2.12. Thus, to correct this temperature curvature and achieve an improved accuracy over the whole operation range, the non-linear terms of the CTAT voltage should be also temperature offseted. In fact, compensating the second term of equation 2.13 is enough to achieve the high-accuracy output voltage required by the most of applications. The non-linear terms of order higher than the second are important only for very high-accuracy application and/or for very large temperature ranges (Falconi, 2005).

The first BGR's to use techniques to provide a high-order correction were proposed in Palmer (1981) and Meijer (1982). The first one implements the thermal compensation of the nonlinearity of  $V_{BE}$  by means of the inclusion of another non-linear term with opposite temperature coefficient; and achieves a temperature performance better than 3 ppm/ $^{\circ}$ C. In the second work, a compensated BGR without introduction of extra non-linear terms was presented. By the control of the collector current it was possible to generate a  $V_{BE}$  voltage that is totally linear with temperature, and accordingly, a temperature coefficient of 0.5 ppm/ $^{\circ}$ C is obtained.

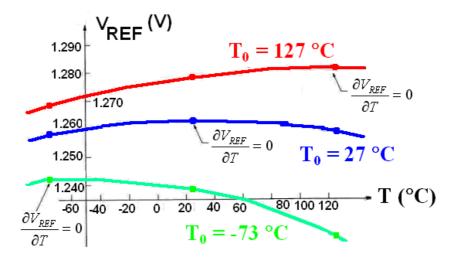

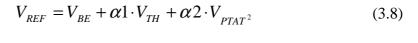

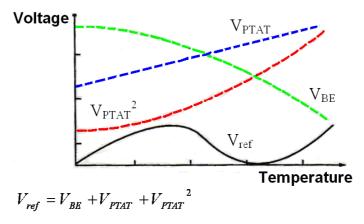

Several methods are found in the literature to design second-order BGR's (Rinconmora, 2002). One of the most diffused techniques is to use the ratio of resistors of different materials to generate a squared PTAT voltage (PTAT<sup>2</sup>). The widespread use of this technique is due to this simplicity and low-cost of implementation. Through only one extra-resistor it is possible to achieve second-order compensation. This parabolic term is added to equation 2.2 to compensate the non-linearity of the V<sub>BE</sub> voltage, what leads to a temperature coefficient of 1 to 20 ppm/°C. Equation 3.8 describes the output voltage in this case and figure 3.18 shows temperature dependency graphically.

Figure 3.18: Typical Curvature of second-order compensated BGR

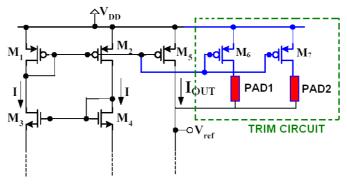

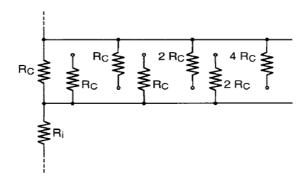

Through figure 3.18 it is possible to see that at low temperatures the term  $V_{PTAT}^2$  is small and can not compensate the non-linearity of  $V_{BE}$  voltage – what leads to an output curvature similar to the one presented by the first-order BGR's. In the middle of the temperature range, this term already compensates part of the non-linearity of the base-emitter voltage and consequently reduces the temperature dependency of the output voltage. At higher temperatures, due to the exponential relationship with temperature,  $V_{PTAT}^2$  assumes large values and dominates the behavior of the reference voltage.