# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

#### MAYLER GAMA ALVARENGA MARTINS

# **Functional Composition and Applications**

Thesis presented in partial fulfillment of the requirements for the degree of Master in Microelectronics

Prof. Dr. André Inácio Reis Advisor

Prof. Dr. Renato Perez Ribas Co-advisor

# CIP - CATALOGAÇÃO NA PUBLICAÇÃO

Gama Alvarenga Martins, Mayler

Functional Composition and Applications / Mayler Gama

Alvarenga Martins. – Porto Alegre: PGMICRO da UFRGS, 2012.

97f.: il.

Thesis (Master) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica, Porto Alegre, BR–RS, 2012. Advisor: André Inácio Reis; Coadvisor: Renato Perez Ribas.

1. Boolean function. 2. Logic synthesis. 3. Functional composition. 4. Minimum decision chain. 5. Boolean factoring. 6. Exclusive-OR. 7. Majority gate. I. Reis, André Inácio. II. Ribas, Renato Perez. III. Functional Composition and Applications.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos Alexandre Netto

Pró-Reitor de Coordenação Acadêmica: Prof. Pedro Cezar Dutra Fonseca

Pró-Reitor Adjunto de Pós-Graduação: Prof. Aldo Bolten Lucion Diretor do Instituto de Informática: Prof. Flavio Rech Wagner Coordenador do PGMICRO: Prof. Ricardo Augusto da Luz Reis Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

## ACKNOWLEDGMENTS

There are some people I wish to say "thank you".

I would like to thank my advisor, André I. Reis, for his vast knowledge in logic synthesis and by often pointing out the path to be followed, even with my uncertainty about where this path would lead. Now I see that these paths led in the right direction.

I would like to thank my co-advisor, Renato P. Ribas, for its ability to organize ideas and texts, and his enthusiasm to talk about any subject. Thanks for all the barbecues held at his home

I would like to thank the rest of my thesis committee: Prof. Sérgio Bampi, Prof. Fabrizio Ferrandi, and Prof. Francesc Echeto for their insightful comments.

To all labmates, by the intense discussions, that helped me in the development of this thesis. I want to thank (in order of reviews): Felipe Marranghelo, Lucas Machado, Vinicius Dal Bem and Vinicius Callegaro for all thesis' reviews. These reviews improved a lot this text. I would like to thank in particular Vinicius Callegaro for your patience in helping me with the code issues, and by random discussions, ranging from brewing to poker strategies.

I owe my gratitude to my parents, Luiz C. P. Martins and Maruza G. Alvarenga, and my godmother Ediméa C. Gama, through the encouragement and support. I am grateful to my girlfriend Francine B. Puchalski for all the love and unconditional patience.

And finally, I would like to thank all Nangate A/S for financing my trip to Copenhagen in 2010 and given me the opportunity to show my work. I want to thank also CAPES funding agency and the European Community's Seventh Framework Programme under grant 248538 – Synaptic. Without their investment, this work would not be possible.

To all that collaborated in this work directly or indirectly, my sincere thanks!

# **CONTENTS**

| 1 INTRODUCTION                                                      | 15 |

|---------------------------------------------------------------------|----|

| 1.1 Logic Synthesis                                                 |    |

| 1.2 Motivation and Challenges                                       |    |

| 1.3 Objectives                                                      |    |

| 1.4 Thesis Organization                                             |    |

| 2 BOOLEAN LOGIC CONCEPTS                                            |    |

| 2.1 Boolean Functions                                               |    |

| 2.2 Canonical Representations of Boolean Functions                  |    |

| 2.2.1 Truth Table                                                   |    |

| 2.2.2 Binary Decision Diagrams                                      |    |

| 2.3 Boolean Operations                                              |    |

| 2.4 Properties of Boolean Functions                                 |    |

| 2.4.1 Shannon Expansion and Cofactors                               |    |

| 2.4.2 Unateness                                                     |    |

| 2.4.3 Order                                                         |    |

| 2.4.4 Symmetry                                                      |    |

| 2.4.5 Davio Expansion                                               |    |

| 2.4.6 Self-Dual Functions                                           |    |

| 2.5 Boolean Equations                                               |    |

| 2.5.1 Literals                                                      |    |

| 2.5.2 Two level expressions                                         |    |

| 2.5.2.1 Minterms and Maxterms                                       |    |

| 2.5.2.2 Implicants, Prime Implicants and Essential Prime Implicants |    |

| 2.5.3 Factored Expressions                                          |    |

| 2.5.3.1 Read-Once Functions                                         | 32 |

| 2.6 Comparison Between Boolean Functions Representations            | 33 |

| 2.7 Two Level AND-XOR Expressions                                   | 33 |

| 3 GENERAL PRINCIPLES OF FUNCTIONAL COMPOSITION                      |    |

| 3.1 Functional Decomposition                                        |    |

| 3.2 General Principles of Functional Composition                    |    |

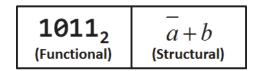

| 3.2.1 Bonded-Pair Representation                                    | 39 |

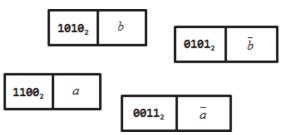

| 3.2.2 Initial Functions                                             | 40 |

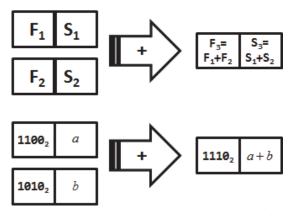

| 3.2.3 Bonded-Pair Association                                       |    |

| 3.2.4 Partial Order and Dynamic Programming                         |    |

| 3.2.5 Allowed Functions                                             |    |

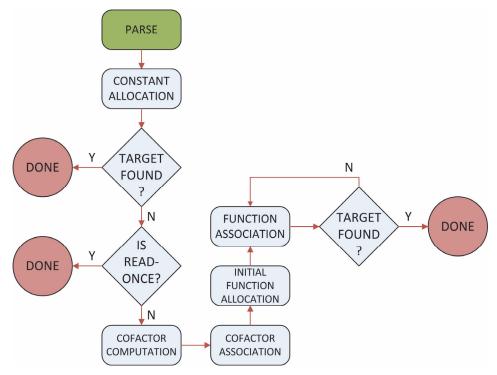

| 3.3 General Flow                                                    |    |

| 3.4 Related Work                                                    |    |

| 3.5 Conclusions                                                     | 43 |

| 4 M                 | IINIMUM DECISION CHAIN COMPUTATION                                 |      |

|---------------------|--------------------------------------------------------------------|------|

| 4.1                 | Introduction                                                       |      |

| 4.2                 | Minimum Decision Chains                                            |      |

| 4.3                 | QMC-MDC Procedure                                                  |      |

| 4.4                 | FC-MDC Procedure                                                   |      |

| 4.4.1               | Functional Composition Setup for MDC Computation                   |      |

| 4.4.2               | FC- MDC Computation                                                |      |

| 4.5                 | FC-MDC Application Example                                         | . 50 |

| 4.6                 | Sum of Products Synthesis Using FC-MDC                             |      |

| 4.7                 | Experimental Results                                               |      |

| 4.8                 | Conclusions                                                        |      |

|                     | OOLEAN FACTORING                                                   |      |

| 5.1                 | Basic Concepts about Factorization                                 |      |

| 5.2                 | Related Work                                                       |      |

| 5.3                 | FC Factoring Baseline Algorithm                                    |      |

| 5.4                 | Functional Composition Setup for Boolean Factoring                 |      |

| 5.5                 | Boolean Operations Considering Order                               |      |

| 5.6                 | Read-Once Factoring                                                |      |

| <b>5.7</b> 5.7.1    | Exact Approach                                                     |      |

| 5.7.1<br><b>5.8</b> | Allowed Combinations                                               |      |

| 5.8.1               | Allowed Functions                                                  |      |

| 5.8.1<br>5.9        | Other Optimizations                                                |      |

| 5.10                | General Flow                                                       |      |

| 5.11                | Examples                                                           |      |

|                     | Read-Once Algorithm.                                               |      |

|                     | FC-HEURISTIC Algorithm                                             |      |

|                     | Experimental Results                                               |      |

| 5.13                | Conclusions                                                        |      |

| 6 B                 | OOLEAN FACTORING USING XOR                                         |      |

| 6.1                 | Related Work                                                       |      |

| 6.2                 | Functional Composition Setup for Boolean Factoring considering XOF |      |

| 6.3                 | Exact Factoring with XOR                                           | . 73 |

| 6.3.1               | Boolean Operations Considering Order                               |      |

| 6.3.2               | Allowed Combinations                                               | . 74 |

| 6.3.3               | Condition to enable XOR factorization                              |      |

| 6.3.4               | Technology Mapping Based Optimizations                             |      |

| 6.4                 | Example                                                            |      |

| 6.5                 | Experimental Results                                               |      |

| 6.6                 | Conclusions                                                        |      |

|                     | IAJORITY-BASED CIRCUIT SYNTHESIS                                   |      |

| 7.1                 | Related Work                                                       | . 79 |

| 7.2                 | Functional Composition Setup for Majority Gate Circuit Synthesis   |      |

| 7.3                 | Partial Order Criterion                                            |      |

| 7.3.1               | Number of Majority Gates Approach                                  |      |

| 7.3.2               | Logic Depth Approach                                               |      |

| 7.4                 | Inverter Cost                                                      |      |

| 7.5                 | Synthesizing a Library                                             |      |

| 7.6                 | Experimental Results                                               | . 80 |

| 7.7 | Conclusions                 | 88 |

|-----|-----------------------------|----|

| 8   | CONCLUSIONS AND FUTURE WORK | 89 |

| RE  | FERENCES                    | 91 |

# LIST OF ACRONYMS AND ABBREVIATIONS

AIG And-Inverter Graph

BDD Binary Decision Diagram

CMOS Complementary Metal Oxide Semiconductor

DFT Design for Testability

DSD Disjoint Support Decomposition

EDA Electronic Design Automation

ESOP Exclusive-OR Sum Of Products

FC Functional Composition

FD Functional Decomposition

FPRM Fixed Polarity Reed-Muller Expression

GF Good Factor

GRM Generalized Reed-Muller Expression

IC Integrated Circuit

ISOP Irredundant Sum-Of-Products

KRO Kronecker Expression

MDC Minimum Decision Chain

MF Majority Function

NSP Non Series-Parallel

OBDD Ordered Binary Decision Diagram

PKDD Pseudo-Kronecker Decision Diagram

PLA Programmable Logic Array

POS Product-Of-Sums

PPRM Positive Polarity Reed-Muller Expression

PSDKRO Pseudo Kronecker Expression PSDRM Pseudo Reed-Muller Expression

QBF Quantified Boolean Formula

QF Quick Factor

ROBDD Reduced and Ordered Binary Decision Diagram

RTL Register-Transfer Level

SET Single Electron Tunneling

SPFD Sets of Pairs of Functions to be Distinguished

SOP Sum-Of-Products

TPL Tunneling Phase Logic

VHDL VHSIC Hardware Description Language

XF X-Factor

# LIST OF FIGURES

| Figure 1.1: Logic synthesis flow.                                                                                                                                            | . 17 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 2.1: Karnaugh map representation of the function shown in Table 2.1                                                                                                   |      |

| Figure 2.2: Vertex representation for a BDD node.                                                                                                                            |      |

| Figure 2.3: BDD representation from the function in Table 2.1.                                                                                                               |      |

| Figure 2.4: ROBDD from the OBDD in Figure 2.3.                                                                                                                               |      |

| Figure 2.5: ROBDD with the same function from Table 2.1, but with different variable                                                                                         |      |

| $\epsilon$                                                                                                                                                                   | . 24 |

| Figure 2.6: Boolean operations: the blue area represents the result of each operation                                                                                        |      |

| Figure 2.7: Order visualized in the Karnaugh map.                                                                                                                            |      |

| Figure 2.8: Karnaugh map of function f.                                                                                                                                      |      |

| Figure 2.9: Covering table of function f.                                                                                                                                    | . 31 |

| Figure 2.10: Logic tree of the two level expression representation of the expression $b \cdot d \cdot e \cdot f + b \cdot c + a \cdot d \cdot e \cdot f + a \cdot c$ .       | . 32 |

| Figure 2.11: Logic tree of the factored expression representation of the expression $(a+b)\cdot(c+d\cdot(e\cdot f))$ .                                                       | 32   |

| Figure 2.12: Relationship between various classes of AND-EXOR expressions                                                                                                    |      |

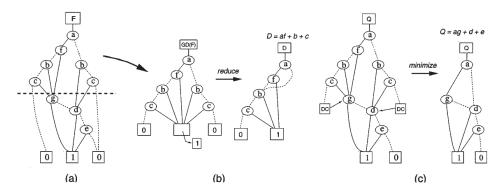

| Figure 3.1: A disjoint support decomposition for <i>F</i> . Source: (PLAZA; BERTACCO,                                                                                        |      |

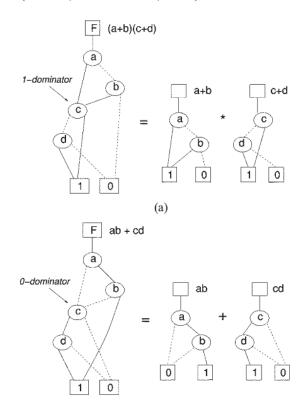

| 2005.)Figure 3.2: Algebraic decompositions of Karplus: (a) conjunction decomposition,                                                                                        | . 38 |

| F=(a+b)(c+d), based on 1-dominator and (b) disjunctive decomposition, $F=ab+cd$ ,                                                                                            | 20   |

| , , ,                                                                                                                                                                        |      |

| Figure 3.3: Conjunctive BDD decomposition: (a) original function $F$ , (b) generalized dominator and Boolean divisor $D$ , and (c) computing quotient $Q$ from $F$ . Source: |      |

| YANG; CIESIELSKI, 2002.                                                                                                                                                      | 39   |

| Figure 3.4: Bonded-Pair representation example.                                                                                                                              |      |

| Figure 3.5: Example of initial bonded-pairs.                                                                                                                                 |      |

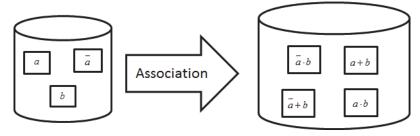

| Figure 3.6: Bonded-pair association example.                                                                                                                                 |      |

| Figure 3.7: When combining the elements of a bucket, a new element is generated and                                                                                          |      |

| stored in a new bucket.                                                                                                                                                      | 41   |

| Figure 3.8: Some elements of Figure 3.7 can be removed to reduce the number of                                                                                               |      |

| elements in a bucket, improving memory and execution time.                                                                                                                   | 42   |

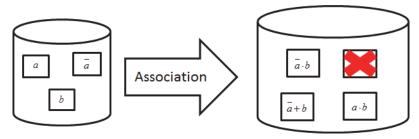

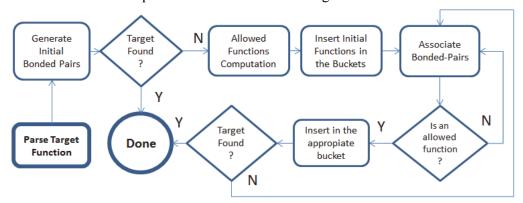

| Figure 3.9: General Flow for FC.                                                                                                                                             | 42   |

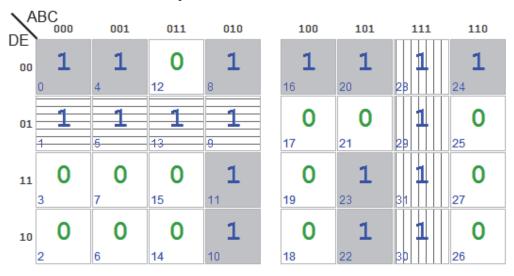

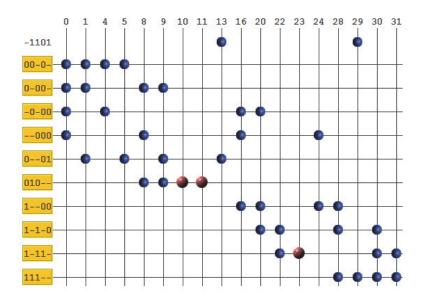

| Figure 4.1: K-map for the Eq. 4.1.                                                                                                                                           |      |

| Figure 4.2: Karnaugh map for Equation 4.2.                                                                                                                                   |      |

| Figure 4.3: Covering table related Equation 4.2.                                                                                                                             |      |

| Figure 4.4: MDC computation example.                                                                                                                                         | 50   |

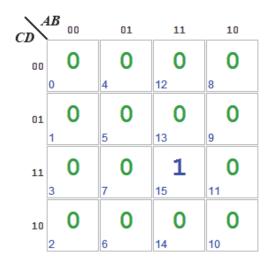

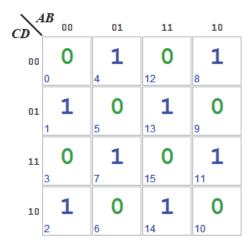

| Figure 4.5: Karnaugh map of AND4 function                                                                                                                                    |      |

| Figure 4.6: Karnaugh map of XOR4 function.                                                                                                                                   | . 53 |

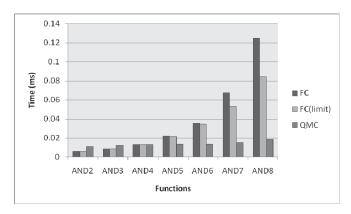

| Figure 4.7: MDC computation of AND with 2 to 8 inputs.                                  | . 54 |

|-----------------------------------------------------------------------------------------|------|

| Figure 4.8: MDC computation of XOR, with 2 to 8 inputs                                  | . 54 |

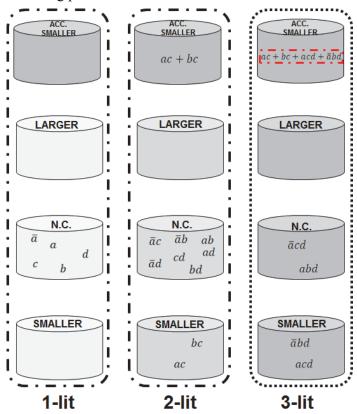

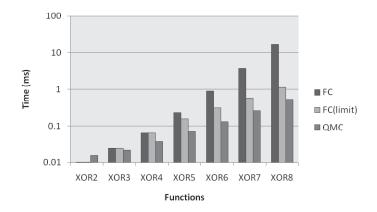

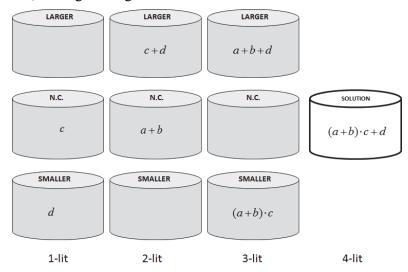

| Figure 5.1: Generation of functions contained in the 5-literal bucket                   | . 58 |

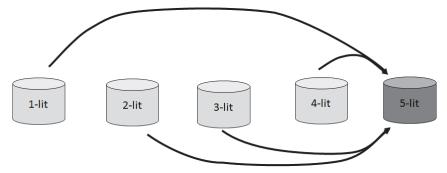

| Figure 5.2: Bucket divided in smaller, larger and not comparable sets.                  | 60   |

| Figure 5.3: Allowed Functions generation.                                               |      |

| Figure 5.4: Heuristic approach flow.                                                    | . 64 |

| Figure 5.5: Combination step of factorization with simplified bucket content            | . 65 |

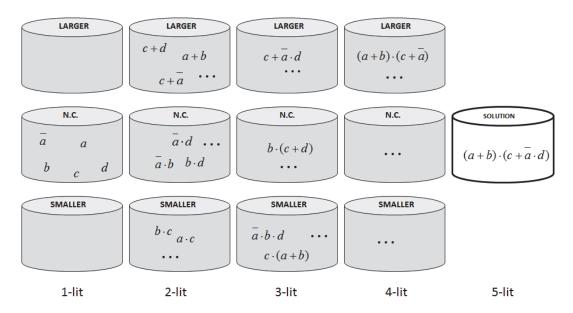

| Figure 5.6: Combination step of factorization with simplified bucket content            | . 67 |

| Figure 6.1: PKDD representation for a Boolean function                                  | . 72 |

| Figure 6.2: Combination step to find solutions for f using FC-EXACTXOR                  | . 76 |

| Figure 6.3: XOR4 function distribution between buckets                                  | . 77 |

| Figure 7.1: A n-input threshold logic gate                                              | . 79 |

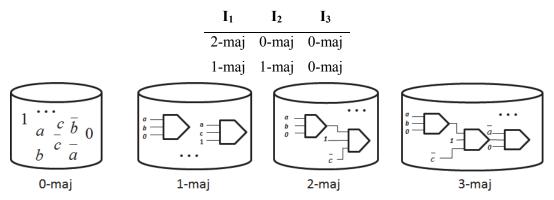

| Figure 7.2: Self-dual property in majority gates.                                       | . 81 |

| Figure 7.3: Number of majority gate approach example                                    | . 83 |

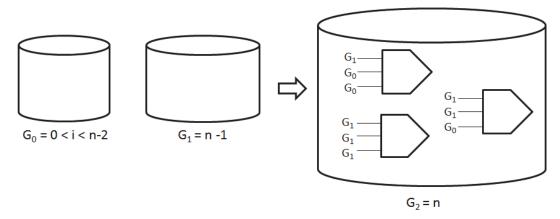

| Figure 7.4: Generating an n-depth bucket.                                               | . 84 |

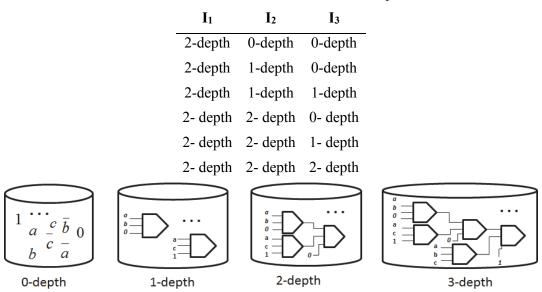

| Figure 7.5: Logic depth approach                                                        | . 84 |

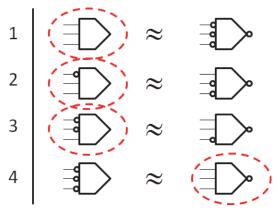

| Figure 7.6: Exploring the self-dual property to reduce the number of inverters          | . 85 |

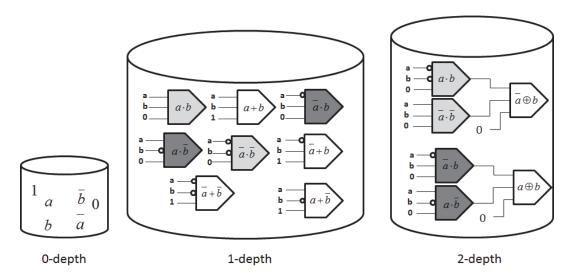

| Figure 7.7: Generation of all functions up to 2 variables.                              | . 86 |

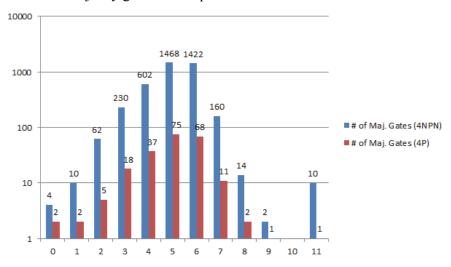

| Figure 7.8: Histogram for 4-input library, considering the number of majority gates to  |      |

| implement the functions.                                                                | . 87 |

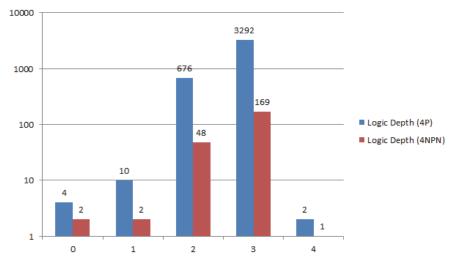

| Figure 7.9: Histogram for 4-input library, considering the logic depth of the functions | 3.   |

|                                                                                         | . 87 |

# LIST DE TABLES

| Table 2.2: Truth tables for the following operations: negation, product, sum, and |     |

|-----------------------------------------------------------------------------------|-----|

| exclusive product operations, respectively                                        | 25  |

| Table 2.3: Truth table of self-dual function f.                                   | 29  |

| Table 2.4: Characteristics of the representations forms of Boolean functions      | 33  |

| Table 4.1: Total execution time of on-set MDC computation                         | 52  |

| Table 4.2: MDC computation of 5-NPN through FC-MDC method, using a limit va       | lue |

| pre-defined by the user                                                           | 52  |

| Table 5.2: AND/OR operations considering function order                           | 60  |

| Table 5.3: Description of Table 5.2 operations results                            | 60  |

| Table 5.4: Cofactors and cube cofactors of r, simplified by symmetry information  |     |

| Table 5.5: Cofactors and cube cofactors of f                                      | 66  |

| Table 5.6: Results of multi-objective goal factorization.                         | 68  |

| Table 5.7: Results regarding number of literals and area after mapping            | 68  |

| Table 5.8: Number of literals after factorization in some benchmarks.             | 69  |

| Table 6.1: Comparison between factorization using XOR algorithms                  | 73  |

| Table 6.2: XOR operation considering function order.                              | 73  |

| Table 6.3: Result of the operations in Table 6.2                                  | 74  |

| Table 6.4: Results comparing FC-EXACTXOR with other methods.                      | 76  |

| Table 7.1: Comparison between majority-based synthesis algorithms                 | 81  |

| Table 7.2: Possible combinations to create a 5-maj bucket.                        | 82  |

| Table 7.3: Possible combinations to create a 3-maj bucket.                        | 83  |

| Table 7.4: Possible combinations to create a 3-depth bucket                       | 84  |

| Table 7.5: Results (in number of majority gates) of FC-MAJ for 3-input functions. | 86  |

## **ABSTRACT**

This work presents functional composition (FC) as a new paradigm for combinational logic synthesis. FC is a bottom-up approach to synthesize Boolean functions, being able to evaluate the cost of intermediate sub-functions, exploring a larger number of different candidate combinations. These are interesting advantages when compared to the top-down behavior of functional decomposition. FC presents great flexibility to implement algorithms with optimal or suboptimal results for different applications. The proposed strategy presents good results for the synthesis of Boolean functions targeting different technologies. FC is based on the following principles: (1) the representation of logic functions is done by a bonded pair of functional and structural representations; (2) the algorithm starts from a set of initial functions; (3) simpler functions are associated to create more complex ones; (4) there is a partial order, enabling dynamic programming; (5) a set of allowed functions can be used in order to reduce execution time/memory consumption. This work presents functional composition algorithms for Boolean factoring, including optimal factoring, Boolean factoring considering the exclusive-OR operator, minimum decision chain computation and synthesis of functions considering only majority and inverter logic gates.

**Keywords:** Boolean functions, logic synthesis, functional composition, minimum decision chain, Boolean factoring, exclusive-OR, majority gate.

#### Composição Funcional e Aplicações

# **RESUMO**

Este trabalho apresenta a composição funcional (CF) como um novo paradigma para realização da síntese lógica de blocos combinacionais. CF usa uma abordagem ascendente para sintetizar funções Booleanas, sendo capaz de avaliar os custos das funções intermediárias e explorando dessa forma um grande número de combinações diferentes de funções candidatas. Há vantagens interessantes quando comparado à abordagem descendente da decomposição funcional. CF apresenta grande flexibilidade para criar algoritmos com resultados ótimos ou subótimos para diferentes aplicações. A estratégia proposta apresenta bons resultados para síntese de funções Booleanas visando diferentes tecnologias. CF é baseado nos seguintes princípios: (1) representação de funções lógicas como um par ligado com representações funcional e estrutural; (2) o algoritmo começa de um conjunto de funções iniciais; (3) funções mais simples são associadas para criar funções mais complexas; (4) existe uma ordem parcial que permite o uso da programação dinâmica; (5) um conjunto de funções permitidas pode ser mantido para reduzir o tempo de execução/consumo de memória. Este trabalho apresenta algoritmos de composição funcional para fatoração Booleana, incluindo fatoração ótima, fatoração considerando o operador OU-exclusivo, computação de cadeias mínimas de decisão e síntese de funções considerando somente portas lógicas majoritárias e inversores.

**Palavras-Chave:** Função Booleana, síntese lógica, composição funcional, cadeia mínima de decisão, fatoração Booleana, OU-exclusivo, porta majoritária.

## 1 INTRODUCTION

The increasing availability of digital technologies is adding new possibilities for investigative research and the way researchers work. Advances in many (if not most) areas of study depend now on the generation and manipulation of digital data, often in huge quantities.

Since Jack Kilby's invention of the first integrated circuit (IC), in 1958 (KILBY, 1959), unprecedented technological advances occurred, mainly in the electronic industry. In 1965, Intel Corp. co-founder, Gordon E. Moore, predicted a major miniaturization trend for the semiconductor industry, known as Moore's Law (MOORE, 1965). Moore's Law predicts that the number of available transistors being packed into a single IC would grow exponentially, doubling approximately every two years. This trend has been observed for more than four decades, and perhaps will continue for another decade or even longer, mainly for digital systems.

A digital system can often be divided into two portions: datapath and control logic. The datapath logic concerns with data computation and storage, and often comprises of structures such arithmetic logic units, buses, registers, regular memories (WAGNER; REIS; RIBAS, 2006). Datapath circuits are often composed of regular structures. Control logic is concerned with the control of these data processing units. Datapath and control logic can be very different in nature and the design of datapath and control logic uses different algorithms. It is common to have synthesis algorithms dedicated either to control logic or to datapath. Algorithms can also vary according to target implementation. The goal of this work is to provide an algorithm for logic synthesis that has enough flexibility to be adapted to control logic or datapath logic designed for different target implementations. The proposed approach is focused mainly on logic synthesis step, which will be described in the following.

# 1.1 Logic Synthesis

Logic synthesis is the process of transforming an abstract form of desired circuit behavior into a design implementation regarding logic components. The circuit behavior is usually expressed using a Register Transfer Level (RTL) description, where the design implementation regarding logic components is a logic gate netlist. Logic synthesis can be viewed as an essential step bridging high-level synthesis (which outputs an RTL description) and physical design (which takes as input a logic gate netlist). Logic synthesis involves the abstraction, representation, manipulation, transformation, analysis, and optimization of logic circuits. All these operations take place in the transformation from the RTL description to the gate level description. Logic synthesis performs automatic generation of logic gates netlists, such that timing

constraints imposed by the designer are respected, and the final logic gate netlist has minimum area and minimum power.

The main mathematical foundation of logic synthesis is the intersection of logic and algebra. The "algebra of logic" created by George Boole, in 1847, also known as Boolean algebra, is the core of logic synthesis. One of the most significant contributions connecting Boolean algebra and circuit design is Claude E. Shannon's M.Sc. thesis, "A Symbolic Analysis of Relay and Switching Circuits", completed at the Massachusetts Institute of Technology (MIT), in 1937 (SHANNON, 1938). Shannon showed that the design and analysis of switching circuits could be formalized using Boolean algebra and switching circuits can be used to solve Boolean algebra problems.

The synthesis of digital circuits involves different views and levels of abstractions. Views can be associated with domains, as it is for the Y-chart proposed by Gajsky (GAJSKI; KHUN, 1983). Gajski divides circuit views into three types or domains: behavioral, structural and physical. Behavioral views express the expected behavior of a given circuit. Structural views express circuits as a list of interconnected subcomponents. Physical views express how structural views are implemented physically. Generally speaking, the goal of any synthesis process is to add detail to existing design views. Synthesis is made to translate designs from the behavioral domain (views) to the structural domain, or from structural domain to physical domain. High-level synthesis does a translation from behavioral to the structural domain, where functional algorithms are mapped to structural representations composed of blocks such as arithmetic logics units, processors and read-only memories (ROMs). Logic synthesis starts from an abstract behavioral description, possibly at the register-transfer level (RTL), which is transformed into a structural netlist of logic gate networks. Logic synthesis is known to perform well to minimize and simplify control logic, which is irregular by nature. Consequently, logic synthesis is particularly useful for control-dominating applications like protocol processing. However, for more regular logic, like arithmetic-intensive applications, signal processing special techniques are used (SONG; PERKOSWI, 1998; SASAO, 2005; SASAO ET AL, 1995).

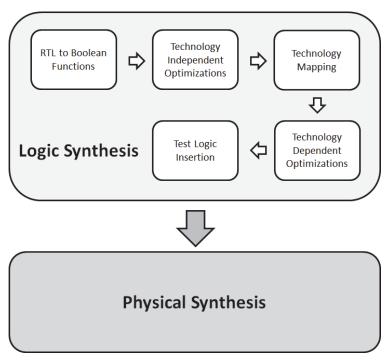

Logic synthesis is composed of technology independent and technology dependent steps, as shown in Figure 1.1. The initial RTL description is parsed into a technologyindependent description. The initial parsing can include a control/data flow analysis that treats arithmetic/datapath independently of control flow. The arithmetic part can be synthesized by choice of possible pre-defined structures. The control flow logic is then treated with technology independent logic optimization algorithms. The initial gatelevel implementation of the control flow portion is composed of generic logic gates (e.g. AND, OR and NOT gates), with no relationship to any specific technology. As a result, the structure at this point is a technology independent netlist (i.e., a list of gates connected by nets), and can be implemented in any technology using technology mapping. However, before the technology mapping process, a number of technology independent optimizations can be done to the technology independent netlist by logic restructuring techniques (MISHCHENKO, 2006). Once the technology mapping has been performed, it is followed by technology dependent optimizations and the insertion of logic to support design for testability (DFT). The physical synthesis begins after these steps (MICHELLI, 1994). A logic synthesis flow is illustrated in Figure 1.1.

Figure 1.1: Logic synthesis flow.

# 1.2 Motivation and Challenges

Observing the logic synthesis field of study, it is easy to see many difficulties and problems with no definitive solution from a research point-of-view. There are many discussions on: "library based (LIU, 2011) versus library free (MARQUES ET AL, 2007)" approaches in mapping; which data structure to use for a given problem (SWORDS; HUNT, 2010; MISHCHENKO; CHATTERJEE; BRAYTON, 2006); and when to use complex gates (KONG; HUSSAIN; OVERHAUSER, 1997) or simple gates (MARKOV; SYLVESTER; BLAAUW, 2008). There are many objectives comprising minimum area, minimum power, maximum performance or any combination of these. Most logic synthesis algorithms are computationally hard problems, and solutions demonstrate approaches based on theoretical studies but also empirical solutions.

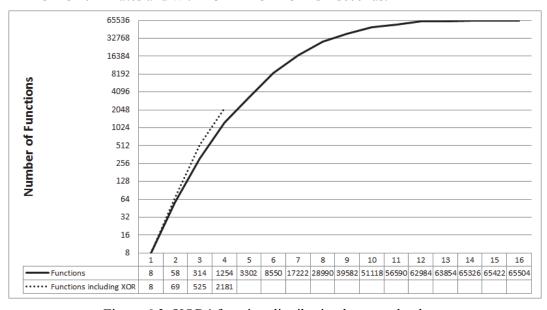

There are many subareas in logic synthesis. Some examples are factoring algorithms, majority based circuit synthesis and functional decomposition. Many of logic synthesis methods (if not all) may rely on the exploitation of Boolean functions properties. As a consequence, fast methods to compute Boolean function properties are needed to allow the use of these properties in the logic synthesis flow. One of these properties is the minimum decision chain (MDC) (MARTINS ET AL, 2011a), (MARTINS ET AL, 2011b). The MDC of a function f is related to the minimum worst case number of series switches required to implement a switch network for the function f in a single stage. The top-down algorithm for MDC computation (SCHNEIDER ET AL, 2005) is slow in some cases of interest (up to 5 transistors in series), so limiting the MDC use in practice.

Factoring is another important procedure for logic synthesis tools. It consists in the conversion of a logic function into a logically equivalent parenthesized expression or

factored form (BRAYTON, 1987). This factored form in general presents a reduced implementation cost. There are other costs associated with a factored form, but the state-of-art algorithms only concern to obtain a minimal factored form, not exploring other costs. Besides that, the state-of-art algorithms do not synthesize expressions with the exclusive-OR operator, which is interesting for arithmetic and testing circuits.

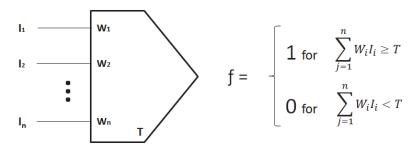

On the other hand, the research in majority logic synthesis dates back to 1960s, when majority logic circuits were called threshold circuits (MUROGA, 1971). A threshold circuit uses majority gates with weighted inputs, having applications mainly in analog circuits. With the CMOS technology achieving the scaling limits, there are many candidate technologies to replace the CMOS, such as tunneling phase logic (TPL), single electron tunneling (SET) and quantum cellular automata (QCA). All these mentioned technologies use majority or minority gates as primitive elements in the circuit (ZHANG; GUPTA; JHA, 2005). Unfortunately, there are no algorithms capable of generating optimal synthesis (considering the number of majority gates as costs) for functions with more than 3 inputs.

Functional decomposition (FD) is a method for combinational logic synthesis in which a Boolean function is decomposed into a set of smaller functions that implement the Boolean function. FD has been introduced by the pioneering works of (ASHENHURST, 1959) and (CURTIS, 1962). The results of functional decomposition are in the functional domain, meaning that it can produce non-trivial logic rewritings that are very suitable to overcome the structural bias. A logic synthesis algorithm with structural bias has the results strongly dependent on the algorithm input data, and this is not a desired characteristic. FD has been extensively used for FPGA mapping, as it is simple to control the number of inputs of each sub-function. However, FD has two critical drawbacks in this context. Firstly, it is a top-down approach, which breaks the original function to be decomposed into smaller ones, so the implementation cost of these functions is not necessarily known. Secondly, FD involves costly operations for one possible decomposition, relying on complex operations as counting the number of distinct subfunctions, test inversions, and so on.

All these drawbacks discussed in FD, factorization, MDC computation, and majority gate circuit synthesis can be overcome if a bottom-up approach is used since the costs of initial functions are known, the logic operations are simple, the subfunctions have suboptimal and optimal implementations, and a control cost can be easily set.

# 1.3 Objectives

This thesis proposes a novel technique based on functional composition (FC) to overcome the drawbacks of functional decomposition applied to local function rewriting. It is a novel synthesis paradigm that performs a bottom-up association of Boolean functions as opposed to the top-down functional decomposition strategy. By performing a bottom-up process, FC has a better control of the implementation cost of the final function.

Functional composition is based on the following principles: (1) representation of logic functions as a bonded pair of functional/structural representations; (2) it starts from a set of initial functions; (3) simpler functions are associated to create more complex functions; (4) a partial order that enables dynamic programming is respected; (5) a set of allowed functions is maintained to reduce execution time/memory consumption.

The functional composition approach is flexible; i.e., it can be configured to provide new alternatives to already known logic synthesis algorithms. FC can provide reduced costs due to the use of a bottom-up approach, where the implementation costs of all subfunctions generated during the synthesis process are known. In this thesis, three different FC algorithms are exemplified. All three algorithms are obtained by configuring FC for various purposes.

The first application is an approach to efficiently compute MDC, especially from the cases of interest. The second application is a Boolean factoring algorithm that is capable of factorizing expressions considering one or more costs besides the expression size. A second Boolean factoring algorithm has the capability to factorize expressions using the exclusive-OR operator. The third application is a majority gate circuit synthesis algorithm superior to the existing ones.

# 1.4 Thesis Organization

This thesis is organized as follows. Chapter 2 provides some basic concepts useful for a better understanding of the reader. Chapter 3 explains the paradigm of FC, describing the general principles, which are used in all the applications proposed herein. Chapter 4 explains the MDC computation using FC. Chapter 5 and Chapter 6 propose two novel FC-based Boolean factoring algorithms which provide important improvements over previously available factoring procedures. Chapter 7 explores the characteristics of FC to synthesize circuits containing majority gates and inverters. The last chapter presents the conclusion of the thesis, summarizes the contributions of this work, summarizes the major contributions, and outlines some possible future works.

## 2 BOOLEAN LOGIC CONCEPTS

In this chapter, important concepts of logic synthesis that are necessary for the complete understanding of this thesis are reviewed. The concepts described are Boolean algebra; Boolean equations representation forms; representation of Boolean functions in a data structure format; the computing properties of Boolean functions and the logic design using only AND-eXclusive-OR (AND-XOR) expressions. Readers with knowledge in this field can skip this chapter without compromising the understanding of the contents discussed in the next chapters.

#### 2.1 Boolean Functions

Let  $B = \{0,1\}$ . A Boolean logic function f with n input variables  $[x_1,...,x_n]$  and one output variable is a function:

$$f: B^n \mapsto B$$

where  $x = [x_1, ..., x_n] \in B^n$  is the input of f. This is a representation of a completely specified Boolean function (CSF) taking values from B, i.e., all the values of the input map into 0 or 1 for all components of f.

For each function f, it can be defined as follows: the on-set  $(X^{ON} \subseteq B^n)$  is the set of input values x such that f(x) = 1, and the off-set  $(X^{OFF} \subseteq B^n)$  is the set of input values x such that f(x) = 0.

#### 2.2 Canonical Representations of Boolean Functions

A canonical representation of a Boolean function means that for each possible function f, there is only a unique representation, considering a given representation type. In this section, two canonical representations are presented: truth tables and binary decision diagrams (BDD).

#### 2.2.1 Truth Table

A truth table is one possible representation of a logic function. In this form, the value of the function is specified for each possible combination of inputs. For instance, let  $f: x \mapsto y \mid y \in B$ , where the values of  $x = [x_1, x_2, x_3]$  is indicated in Table 2.1.

Table 2.1: Truth table for a logic function with 3 variables

| $x_1$ | $x_2$ | $x_3$ | У |

|-------|-------|-------|---|

| 0     | 0     | 0     | 1 |

| 0     | 0     | 1     | 1 |

| 0     | 1     | 0     | 0 |

| 0     | 1     | 1     | 0 |

| 1     | 0     | 0     | 1 |

| 1     | 0     | 1     | 1 |

| 1     | 1     | 0     | 1 |

| 1     | 1     | 1     | 0 |

|       |       |       | ı |

For this function,  $X^{ON} = \{\{[0,0,0], [0,0,1], [1,0,0], [1,0,1], [1,1,0]\}$  and  $X^{OFF} = \{[0,1,0], [0,1,1], [1,1,1]\}.$

The assignment of a Boolean function can be exhaustively enumerated with a truth table, where every truth assignment has a corresponding *y* value.

Truth tables are canonical representations of Boolean functions. That is, two Boolean functions are equivalent if and only if they have the same truth table. The canonicity of Boolean data structures is an important property because is simple to check the equality between two Boolean functions.

Because of exhaustive enumeration, it is not feasible to represent a Boolean function through a truth table containing many input variables, e.g. a number of inputs greater than 20. The truth table has space complexity of  $O(2^n)$  since this is the number of lines in a truth table. Hence, it is not memory feasible to represent many functions with  $2^{20}$  bits per function, for instance.

By storing the truth table data as a computer word or an array of words, basic Boolean operations can be done in constant time by parallel operation over their truth tables. For example, the y output of the truth table shown in Table 2.1 can be represented as  $01110011_2$  (in binary format) or  $73_{16}$  (in hexadecimal format), where the most significant bit is the leftmost digit.

| $\chi_3^{\chi}$ | 1,X2<br>00 | U1 | 11 | 10 |

|-----------------|------------|----|----|----|

|                 | 1          | 0  | 1  | 1  |

| 0               | 0          | 2  | 6  | 4  |

| 1               | 1          | 0  | 0  | 1  |

| _               | 1          | 3  | 7  | 5  |

Figure 2.1: Karnaugh map representation of the function shown in Table 2.1.

The Karnaugh map is another way of representing the information of a function (KARNAUGH, 1953). In a Karnaugh map, the Boolean variables are ordered according to the principles of Gray code in which only one variable changes in between adjacent

neighboring values (GRAY, 1947). It is designed to present the information in a bidimensional way that allows easy grouping of neighboring terms. A Karnaugh map representation for the function seen in Table 2.1 is shown in Figure 2.1.

#### 2.2.2 Binary Decision Diagrams

A Boolean function can be represented as a rooted, directed, acyclic graph which consists of decision nodes and two terminal nodes called 0-terminal and 1-terminal, also known as BDDs. BDDs were first proposed by (LEE,1959), and further developed by Akers (AKERS, 1978). To reduce the number of decision nodes in the representation, (BRYANT, 1986) proposed several reduction rules, leading to the well-known Reduced Ordered BDDs (ROBDDs).

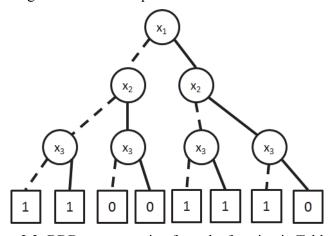

The BDD from Akers is a directed graph G(V, E). All vertices  $v \in V$ , except for the root and the leaf vertices, have one edge ingoing to them and two outgoing edges from them, where an edge  $e \in E$ . The two outgoing edges from a vertex point to the children vertices are called low and high vertices, and are denoted by  $\eta(v)$  and  $\lambda(v)$ , respectively. Moreover, each vertex has an attribute called variable and is denoted by  $\phi(v)$ . When  $\phi(v) = 0$ , the vertex  $\eta(v)$  is chosen and when  $\phi(v) = 1$  the vertex  $\lambda(v)$  is chosen. The root vertex does not have an edge incident to it. The leaf vertices do not have any edges leaving from them. The vertex is shown in Figure 2.2. A BDD example is illustrated in Figure 2.3, where the dashed line is the  $\eta(v)$  and the full line is  $\lambda(v)$ .

Figure 2.2: Vertex representation for a BDD node.

Figure 2.3: BDD representation from the function in Table 2.1.

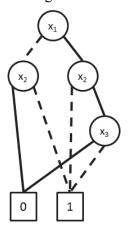

An Ordered BDD (OBDD) is a BDD with the nodes on every path from the root node to a terminal node of the BDD follow the same variable ordering. An OBDD can be reduced to an ROBDD. The derived ROBDD has the smallest number of nodes under a given variable ordering.

ROBDDs are structurally (and also functionally) isomorphic, this means that two functional equivalent ROBDDs have the same graph structure, considering the same

variable ordering for two ROBDDs. Every function has only one ROBDD for a given variable ordering, being a canonical representation of its respective Boolean function. The ROBDD obtained from OBDD of Figure 2.3 is shown in Figure 2.4.

Figure 2.4: ROBDD from the OBDD in Figure 2.3.

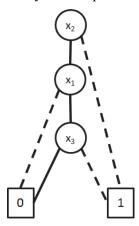

The size of the ROBDD is determined both by the function being represented and the chosen ordering of the variables. There exist Boolean functions that depend on the ordering of the variables, these functions would end up being represented by a graph whose number of nodes would be linear on the number of Boolean variables in the best case and exponential at the worst case. The variable ordering chosen in the BDD of Figure 2.3 was  $[x_1,x_2,x_3]$ . Choosing the variable ordering  $[x_2,x_1,x_3]$  results in the ROBDD shown in Figure 2.5. This ROBDD has one node less than the ROBDD from Figure 2.4, hence decreasing the memory consumption.

Figure 2.5: ROBDD with the same function from Table 2.1, but with different variable ordering.

The advantage of ROBDD is the possibility to perform Boolean operations directly on the compressed representation, i.e., without decompressing an ROBDD to an OBDD to do the operation.

# 2.3 Boolean Operations

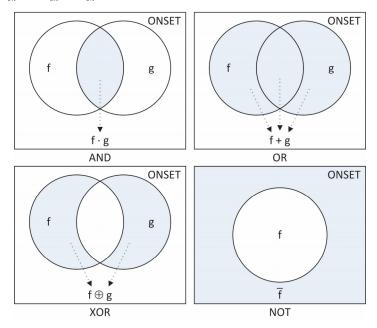

Four basic Boolean operations are discussed in this section. These operations are illustrated in Figure 2.6, and the truth tables are representing the operations are shown in Table 2.2.

The complement or negation (NOT,  $\bar{f}$ ) of a logic function  $\bar{f}$  is the logic function  $\bar{f}$ , where  $\bar{f}_{on} = f_{off}$  and  $\bar{f}_{off} = f_{on}$ .

The intersection or product (AND,  $\cdot$ ) of two logic functions f and g,  $h = g \cdot f$  is defined to be the logic function h, where  $h_{on} = f_{on} \cap g_{on}$ .

The union or sum (OR, +) of two logic functions f and g, i = g + f is defined to be the logic function i, where  $i_{on} = f_{on} \cup g_{on}$ .

The symmetric difference or exclusive product (XOR,  $\oplus$ ) of two logic functions f and g,  $j = g \oplus f$  is defined to be the logic function j, where  $j_{on} = (f_{on} \cup g_{on}) - (f_{on} \cap g_{on})$ .

Figure 2.6: Boolean operations: the blue area represents the result of each operation.

Table 2.2: Truth tables for the following operations: negation, product, sum, and exclusive product operations, respectively.

| NOT(f)           | AND(f,g) | OR(f,g) | XOR(f,g) |

|------------------|----------|---------|----------|

| c =              | f g h    | f g i   | f g j    |

| $f \overline{f}$ | 0 0 0    | 0 0 0   | 0 0 0    |

| 0 1              | 0 1 0    | 0 1 1   | 0 1 1    |

| 1 0              | 1 0 0    | 1 0 1   | 1 0 1    |

|                  | 1 1 1    | 1 1 1   | 1 1 0    |

# 2.4 Properties of Boolean Functions

There are some important Boolean properties, described in the following subsections.

#### 2.4.1 Shannon Expansion and Cofactors

The Shannon expansion (or Shannon decomposition) is defined as (SHANNON, 1949):

$$f(x_1, ..., x_i, ... x_n) = x_i \cdot f(x_1, ..., 1, ... x_n) + \overline{x_i} \cdot f(x_1, ..., 0, ... x_n)$$

(2.1)

The cofactor is a sub-element of a Shannon expansion. The Shannon expansion is a way to express a Boolean function by the sum of two subfunctions of the original. Considering a function f with the input variables  $\{x_1, ..., x_i, ..., x_n\}$ , the cofactor  $f_{x_i}$  is defined as:

$$f_{x_i} = \{ f(x_1, \dots, x_i, \dots x_n) \mid x_i = k, k \in B \}$$

(2.2)

The positive cofactor is defined when k=1 and the negative cofactor is defined when k=0. For simplicity, let  $f_{x_i=1}$  and  $f_{x_i=0}$  represent positive and negative cofactors, respectively, in the variable  $x_i$  of the function f. A **cube cofactor** is obtained by setting more than one input variable to specific values that can be zero or one (e.g.  $f_{x_i=0,x_2=1}$ ). The cube cofactors are commutative operations.

There is also a Shannon expansion representation using the exclusive-OR operator:

$$x_i \cdot f(x_1, \dots, 1, \dots, x_n) \oplus \overline{x_i} \cdot f(x_1, \dots, 0, \dots, x_n)$$

$$(2.3)$$

This expansion is used to generate expressions using only AND-XOR operators.

## 2.4.2 Unateness

Let f be a Boolean function. The variable  $x_k$  in the function f is "don't care" if  $f_{x_k=0}=f_{x_k=1}$ . The variable  $x_k$  in the function f is positive unate if  $f_{x_k=0}+f_{x_k=1}=f_{x_k=1}$ . The function f is negative unate in the variable  $x_k$  if  $f_{x_k=0}+f_{x_k=1}=f_{x_k=0}$ . Otherwise, the variable  $x_k$  in the function f is binate.

Let  $U(f,x_k)$  denote the unateness detection function of a variable  $x_k$  in the function f, and auxiliary function  $i = f_{x_k=1} + f_{x_k=0}$ , we have:

$$U(f, x_{k}) = \begin{cases} positive & (f_{x_{k}=1} \equiv i) \land (f_{x_{k}=1} \neq f_{x_{k}=0}) \\ negative & (f_{x_{k}=0} \equiv i) \land (f_{x_{k}=1} \neq f_{x_{k}=0}) \\ don't care & f_{x_{k}=1} \equiv f_{x_{k}=0} \\ binate & (f_{x_{k}=1} \neq f_{x_{k}=0}) \land (f_{x_{k}=1} \neq i) \land (f_{x_{k}=0} \neq i) \end{cases}$$

For instance, consider the function f as:

$$f = (x_1 + \overline{x_2}) \cdot (x_3 + \overline{x_1} \cdot x_4)$$

#### 2.4.3 Order

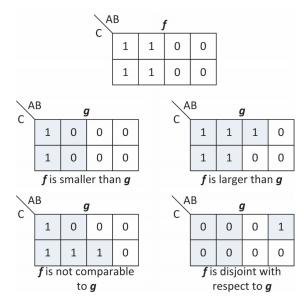

Two Boolean functions can be compared and classified according to their relative ordering, which can be equal, larger, smaller, not-comparable or disjoint. Let O(f,g) denote the order of f against g, and h be the auxiliary function h = f + g, we have:

Figure 2.7: Order visualized in the Karnaugh map.

$$O(f,g) = \begin{cases} \text{equal} & f = g \\ \text{smaller} & (h = g) \land (f \neq g) \\ \text{larger} & (h = f) \land (f \neq g) \\ \text{not comparable} & (f \neq g) \land (f \neq h) \land (g \neq h) \land (f \cdot g \neq 0) \\ \text{disjoint} & (f \neq g) \land (f \neq h) \land (g \neq h) \land (f \cdot g = 0) \end{cases}$$

The order of two functions can be easily observed in a Karnaugh map, shown in Figure 2.7. The hachured area represents the auxiliary function h for each function g.

#### 2.4.4 Symmetry

Two or more variables are symmetric when they can be interchanged without modifying the logic function. Two or more variables are antisymmetric if they can be inverted and exchanged to each other without changing the logic function.

For a function  $f(x_1,...x_n)$  with  $n \ge 2$ , symmetry and antisymmetry of two variables  $x_i$  and  $x_j$  can be detected comparing the cube cofactors of  $x_i$  and  $x_j$ . Let  $S(f,x_i,x_j)$  denote the symmetry check of variables  $x_i$  and  $x_j$  in the function f, g and h auxiliary functions, we have:

$$g = f_{x_i=1,x_j=0}$$

$$h = f_{x_i=0,x_j=1}$$

$$S(f,x_i,x_j) = \begin{cases} symmetric & g = h \\ not \ symmetric & otherwise \end{cases}$$

The antisymmetric property is similar, changing only the cube cofactors to be checked. Let  $AS(f, x_i, x_j)$  denote the antisymmetry check of variables  $x_i$  and  $x_j$  in the function f, and k and m auxiliary functions, we have:

$$k = f_{x_i=0,x_j=0}$$

$$m = f_{x_i=1,x_j=1}$$

$$AS(x_i,x_j) = \begin{cases} antisymmetric & k=m\\ not \text{ antisymmetric} & otherwise \end{cases}$$

Example: Consider the function f as:

$$f = x_1 \cdot x_2 + x_1 \cdot x_3 + x_2 \cdot x_3$$

$x_1, x_2, x_3$  are symmetric.

Example 2: Consider the function g as:

$$g = x_1 \cdot \overline{x_2} + \overline{x_1} \cdot x_2$$

$x_1, x_2$  are symmetric and antisymmetric.

#### 2.4.5 Davio Expansion

There are other ways to expand a Boolean expression with the exclusive-OR operator. The Reed-Muller or Davio expansion is one of the most used expansions with this objective (THAYSE, 1973). Consider the Boolean derivation of f as follows:

$$\frac{\partial f}{\partial x_i} = f_{x_i=1} \oplus f_{x_i=0} \tag{2.3}$$

The positive Davio expansion is:

$$f = f_{x_i=0} \oplus x_i \frac{\partial f}{\partial x_i}$$

(2.4)

The negative Davio expansion is:

$$f = f_{x_i=1} \oplus \overline{x_i} \frac{\partial f}{\partial x_i}$$

(2.5)

For instance, consider the function  $f = x_1 \cdot x_2 + x_3$ . Applying the positive Davio expansion in the variable  $x_1$ , the result is indicated in Equation 2.6.

$$f = x_3 \oplus \overline{x_1} \cdot (x_2 \cdot x_3 \oplus x_3)$$

$$x_3 \oplus \overline{x_1} \cdot x_2 \cdot x_3 \oplus \overline{x_1} \cdot x_3$$

$$(2.6)$$

#### 2.4.6 Self-Dual Functions

The dual of a function  $f(x_1, x_2, ..., x_n)$  is the function  $f^d = \overline{f(\overline{x_1}, \overline{x_2}, ..., \overline{x_n})}$ . Notice that the function  $f^d$  is obtained first by replacing each  $x_i$  with  $\overline{x_i}$  and then complementing the function f. A self-dual function is a function such that  $f = f^d$ .

For instance, in Table 2.3 is presented a self-dual function, called f.

Table 2.3: Truth table of self-dual function *f*.

| $x_1$ | $x_2$                      | $x_3$                                         | f                                                                                                                                                                             |

|-------|----------------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | 0                          | 0                                             | 0                                                                                                                                                                             |

| 0     | 0                          | 1                                             | 0                                                                                                                                                                             |

| 0     | 1                          | 0                                             | 0                                                                                                                                                                             |

| 0     | 1                          | 1                                             | 1                                                                                                                                                                             |

| 1     | 0                          | 0                                             | 0                                                                                                                                                                             |

| 1     | 0                          | 1                                             | 1                                                                                                                                                                             |

| 1     | 1                          | 0                                             | 1                                                                                                                                                                             |

| 1     | 1                          | 1                                             | 1                                                                                                                                                                             |

|       | 0<br>0<br>0<br>0<br>1<br>1 | 0 0<br>0 0<br>0 1<br>0 1<br>1 0<br>1 0<br>1 1 | 0       0       0         0       0       1         0       1       0         0       1       1         1       0       0         1       0       1         1       1       0 |

The values in the line 0, 1, 2 and 3 have complemented values of the lines 7, 6, 5 and 4; respectively it characterizes a self-dual function.

# 2.5 Boolean Equations

An algebraic representation of f is a Boolean expression that evaluates to 1 for all inputs in  $X^{\mathit{ON}}$ , and evaluates to 0 for all inputs in  $X^{\mathit{OFF}}$ . An algebraic representation of f can be built by inspection from the truth table of f. For instance, the algebraic representation of f can be constructed as follows. Consider every row of the truth table that has a 1 in the output value. Create a Boolean product (logical "and", represented by the operator  $\cdot$ ) of the f input variables f [f input variable in the variable f input variable is 0 and uncomplemented if it is 1. This product evaluates to 1 for the input combinations corresponding to the row of the truth table and 0 for all other input combinations. Joining all products using a Boolean sum (OR) of all the product terms created, an algebraic representation of f is found. Using the example given in Table 2.3, and applying the rules above, the Equation 2.7 is obtained.

$$f = \overline{x_1} \cdot x_2 \cdot x_3 + x_1 \cdot \overline{x_2} \cdot x_3 + x_1 \cdot x_2 \cdot \overline{x_3} + x_1 \cdot x_2 \cdot x_3$$

(2.7)

#### 2.5.1 Literals

A literal is either a variable or the negation of a variable within a Boolean logic expression. For example, the expression represented by function  $f = (x_1 + \overline{x_2}) \cdot (x_3 + \overline{x_1} \cdot x_4)$  has 5 literals and the variable set is  $[x_1, x_2, x_3, x_4]$ , being  $x_1$  a positive literal and  $\overline{x_2}$  a negative literal.

#### 2.5.2 Two level expressions

There are two ways to represent two level expressions. An expression called sum-of-products (SOP) is an expression that uses product terms joined by a sum. Another way is using expressions composed of sum terms joined by product, being called product-of-sum (POS).

#### 2.5.2.1Minterms and Maxterms

For a Boolean function of n variables, a product term in which each of the n variables appears once (in its complemented or uncomplemented form) is called a minterm. Thus, a minterm is a logical expression of n variables that employs only the complement operator and the Boolean sum operator.

There are up to  $2^n$  minterms for n variables since a variable in the minterm expression can be either in its complemented form or uncomplemented form.

Maxterms are similar to minterms. For a Boolean function of n variables, a sum term in which each of the n variables appears once (in its complemented or uncomplemented form) is called a maxterm.

For example, consider a function with 3 variables with input assignment  $[x_1,x_2,x_3]$ . The indexes are the decimal representation of the binary value. Index 6 is the minterm  $x_1 \cdot x_2 \cdot \overline{x_3}$  (maxterm  $x_1 + x_2 + \overline{x_3}$ ), the input assignment is [1,1,0], and the minterm is denoted as  $m_6$  (maxterm as  $M_6$ ). Similarly,  $m_5$  is  $x_1 \cdot \overline{x_2} \cdot x_3$  ( $M_5$  is  $x_1 + \overline{x_2} + x_3$ ) with input assignment [1,0,1], and  $m_7$  is  $x_1 \cdot x_2 \cdot x_3$  ( $M_7$  is  $x_1 + x_2 + x_3$ ) with input assignment [1,1,1].

#### 2.5.2.2Implicants, Prime Implicants and Essential Prime Implicants

In Boolean logic, an implicant is a covering (sum terms or product terms) of one or more terms in a SOP (or maxterms in a POS) of a Boolean function. Implicants are also known as cubes. Considering a SOP, a product term p is an implicant of the Boolean function f if p implies f. The product term p implies f (and thus is an implicant of f) if f is equal one whenever p is equal one at the output. This concept can be extended to a POS.

A prime implicant pi of a function f is an implicant that cannot be covered by a more reduced (meaning with fewer literals) implicant. A prime implicant of f is a minimal implicant. The removal of any literal from pi results in a non-implicant for f. Essential prime implicants are prime implicants that cover an output of the function that no combination of other prime implicants can cover.

The process of removing literals from a term is called expanding the term. Expanding by one literal doubles the number of input combinations for which the term

is true (in Boolean algebra). The sum of all prime implicants of a Boolean function is called the complete sum of that function.

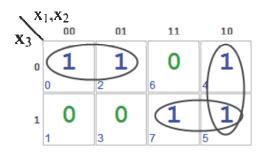

For instance, in the function  $f = \overline{x_1} \cdot \overline{x_3} + x_1 \cdot x_3 + \overline{x_2} \cdot \overline{x_3}$ , the Karnaugh map is shown in Figure 2.8, and the covering table of f is shown in Figure 2.9.

Figure 2.8: Karnaugh map of function *f*.

Figure 2.9: Covering table of function *f*.

The columns in Figure 2.9 represent the minterms, and the lines represent the implicants. The following symbols represent each prime implicant: '0' – the respective variable is complemented; '1' – the respective variable is uncomplemented, and '-' (dash) – the respective variable is absent (does not care). A *don't care* variable can assume the value 0 or 1. For example, the prime implicant [0-0] represents the implicants [000] and [010].

The two gray spheres represent implicants that are only covered by one prime implicant, and the black spheres represent the minterms covered by the respective cube. The [0-0] and [1-1] are essential prime implicants. The [-00] and the [10-] are prime implicants, but not essential prime implicants, since the minterm 4 is covered by both. An **irredundant sum-of-products** (ISOP) is a SOP where no product can be deleted without changing the function. The **irredundant product-of-sums** (IPOS) is a POS where no sum can be deleted without changing the function.

#### 2.5.3 Factored Expressions

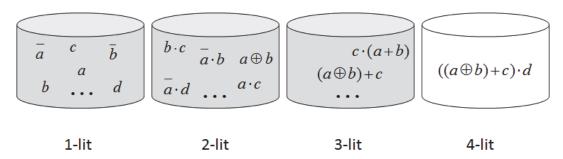

Factoring is the process of deriving a parenthesized algebraic equation, multilevel expressions, or factored form, representing a given logic function (BRAYTON, 1987).

An argument for factored forms is that they are a natural multilevel representation. A factored form is isomorphic to a tree structure, where each internal node is an AND

or OR operator, each leaf is a literal, and the root node is the function output. This leads to a simple and relatively efficient multilevel implementation of the function of the output node. For instance, a function f can be expressed in a two level expression, represented by Equation 2.8. The Equation 2.8 can be factored in a more compact, parenthesized representation represented by Equation 2.9.

$$f = b \cdot d \cdot e \cdot f + b \cdot c + a \cdot d \cdot e \cdot f + a \cdot c \tag{2.8}$$

$$f = (a+b) \cdot (c+d \cdot (e \cdot f)) \tag{2.9}$$

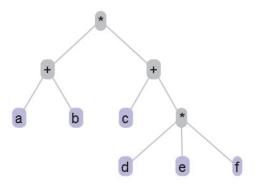

The logic tree of the two level expressions and the factored expressions are shown in Figure 2.10 and Figure 2.11, respectively. Note that the logic tree of the factored expression has three levels of Boolean operations. The number of literals is also reduced, from 12 literals in the SOP expression to 6 literals in the factored expression.

Figure 2.10: Logic tree of the two level expression representation of the expression  $b \cdot d \cdot e \cdot f + b \cdot c + a \cdot d \cdot e \cdot f + a \cdot c$ .

Figure 2.11: Logic tree of the factored expression representation of the expression  $(a+b)\cdot(c+d\cdot(e\cdot f))$ .

#### 2.5.3.1Read-Once Functions

A function f is called read-once if it can be represented by an expression where each variable appears no more than once. For instance, the factored expression  $(a+b)\cdot(c+d\cdot(e\cdot f))$  is read-once.

# 2.6 Comparison Between Boolean Functions Representations

This chapter presented three ways of describing Boolean functions. Table 2.4 summarizes the essential characteristics of each kind of representation.

Table 2.4: Characteristics of the representations forms of Boolean functions.

|               |      | Truth Table | BDD (ROBDD)              | Expression  |

|---------------|------|-------------|--------------------------|-------------|

| Size          |      | Exponential | Linear to<br>Exponential | Linear      |

| Boolean Opera | tion | Linear      | Linear to Exponential    | Constant    |

| Equality      |      | Linear      | Constant                 | Exponential |

| Canonicity    | ,    | Yes         | Yes                      | No          |

# 2.7 Two Level AND-XOR Expressions

Most of the logic design methods are based on AND-OR-NOT expressions. However, the use of XOR has particular interest in arithmetic and telecommunication circuits, reducing the complexity of switching networks. There are many forms of expression representation, generated by using Davio expansion, as discussed below.

# • Positive Polarity Reed-Muller Expression (PPRM)

PPRM is obtained by expanding an expression recursively using the positive Davio expansion. Negative polarity variables can be represented as  $\bar{x} = x \oplus 1$ . The resulting expression is canonical.

**Example**: The Equation 2.10 is a representation of  $\overline{x_1} \cdot \overline{x_2}$  as a PPRM.

$$\overline{x_1} \cdot \overline{x_2} = (x_1 \oplus 1) \cdot (x_2 \oplus 1) = x_1 \cdot x_2 \oplus x_1 \oplus x_2 \oplus 1$$

(2.10)

#### • Fixed Polarity Reed-Muller Expression (FPRM)

FPRM representation is a generalization of PPRM. Each variable can be expanded using the positive or negative Davio expansion, but not both at the same time.

**Example**: Representation of  $x_1 \cdot x_2 \cdot x_3 + x_1 \cdot x_2 \cdot x_3$  as an FPRM, using a negative Davio expansion in  $x_1$  and a positive Davio expansion in  $x_2$  and  $x_3$ .

Using the property  $x \cdot y = 0 \Leftrightarrow x + y = x \oplus y$ :

$$x_{1} \cdot x_{2} \cdot x_{3} + \overline{x_{1}} \cdot \overline{x_{2}} \cdot \overline{x_{3}} = x_{1} \cdot x_{2} \cdot x_{3} \oplus \overline{x_{1}} \cdot \overline{x_{2}} \cdot \overline{x_{3}}$$

$$x_{1} \cdot \overline{x_{2}} \cdot \overline{x_{3}} \oplus \overline{x_{1}} \cdot x_{2} \cdot x_{3} = x_{1} \cdot (x_{2} \oplus 1) \overline{x_{3}} \oplus (x_{1} \oplus 1) \cdot x_{2} \cdot (\overline{x_{3}} \oplus 1)$$

$$x_{1} \cdot \overline{x_{3}} \oplus x_{1} \cdot x_{2} \oplus x_{2} \cdot \overline{x_{3}} \oplus x_{2}$$

#### • Kronecker Expression (KRO)

KRO representation is a generalization of FPRM. Each function can be expanded using the positive or negative Davio expansion or the Shannon expansion for all variables.

**Example**: Representation of  $x_1 \cdot x_2 \cdot x_3 + \overline{x_1} \cdot \overline{x_2} \cdot \overline{x_3}$  as a KRO, using a Shannon expansion in  $x_1$ ,  $x_2$  and  $x_3$ :

$$x_{1} \cdot x_{2} \cdot x_{3} + \overline{x_{1}} \cdot \overline{x_{2}} \cdot \overline{x_{3}} = x_{1}(x_{2} \cdot x_{3}) \oplus \overline{x_{1}}(\overline{x_{2}} \cdot \overline{x_{3}})$$

$$x_{1} \cdot x_{2} \cdot (x_{1} \cdot x_{3}) \oplus \overline{x_{1}} \cdot \overline{x_{2}} \cdot (\overline{x_{1}} \cdot \overline{x_{3}})$$

$$x_{1} \cdot x_{2} \cdot x_{3} \cdot (x_{1} \cdot x_{2}) \oplus \overline{x_{1}} \cdot \overline{x_{2}} \cdot \overline{x_{3}}(\overline{x_{1}} \cdot \overline{x_{2}})$$

$$x_{1} \cdot x_{2} \cdot x_{3} \oplus \overline{x_{1}} \cdot \overline{x_{2}} \cdot \overline{x_{3}}$$

# • Pseudo Reed-Muller Expression (PSDRM)

PSDRM representation is another generalization of an FPRM. For each expansion using positive or negative Davio expansion in an expression, there are two resulting subfunctions. For each of the two subfunctions, they can be expanded using positive or negative Davio expansions, using different expansions for each subfunction.

**Example**: Representation of  $x_1 \cdot x_2 \cdot x_3 + \overline{x_1} \cdot \overline{x_2} \cdot \overline{x_3}$  as a PSDRM, using a positive Davio expansion in  $x_1$ .

$$x_1 \cdot x_2 \cdot x_3 + \overline{x_1} \cdot \overline{x_2} \cdot \overline{x_3} = \overline{x_2} \cdot \overline{x_3} \oplus x_1(x_2 \cdot x_3 \oplus \overline{x_2} \cdot \overline{x_3})$$

The subexpression  $\overline{x_2} \cdot \overline{x_3}$  is a PSDRM since all variables are expanded with the negative Davio expansion. Expanding  $x_2 \cdot x_3 \oplus \overline{x_2} \cdot \overline{x_3}$ :

$$x_2 \cdot x_3 \oplus \overline{x_2} \cdot \overline{x_3} = \overline{x_3} \oplus x_2 \cdot (x_3 \oplus \overline{x_3})$$

$$\overline{x_3} \oplus x_2$$

The final expression is:

$$x_1 \cdot x_2 \cdot x_3 + \overline{x_1} \cdot \overline{x_2} \cdot \overline{x_3} = \overline{x_2} \cdot \overline{x_3} \oplus x_1 \cdot (\overline{x_3} \oplus x_2)$$

$$\overline{x_2} \cdot \overline{x_3} \oplus x_1 \cdot \overline{x_3} \oplus x_1 \cdot x_2$$

#### • Pseudo Kronecker Expression (PSDKRO)

PSDKRO representation is the generalization of KRO representation. For each expansion using positive or negative Davio expansion or the Shannon expansion in an expression, there are new subfunctions. For each of the new subfunctions, they can be expanded using positive or negative Davio expansions or the Shannon expansion, using different expansions for each subfunction.

**Example**: Representation of  $x_1 + x_2 \cdot x_3$  as a PSDKRO, using a Shannon expansion in  $x_1$ ,  $x_1 \oplus \overline{x_1} \cdot x_2 \cdot x_3$  is obtained:

Decomposing  $x_2 \cdot x_3$  using the negative Davio expansion in  $x_2$ , is obtained  $x_3 \oplus \overline{x_2} \cdot x_3$ .

Decomposing  $x_3 \oplus \overline{x_2} \cdot x_3$  using the positive Davio expansion in  $x_3$ , is obtained  $x_3 \oplus \overline{x_2} \cdot x_3$ .

Applying all the expansions:

$$x_1 + x_2 \cdot x_3 = x_1 \oplus \overline{x_1} \cdot x_2 \cdot x_3$$

$$x_1 \oplus \overline{x_1} \cdot (x_3 \oplus \overline{x_2} \cdot x_3)$$

$$x_1 \oplus \overline{x_1} \cdot x_3 \oplus \overline{x_1} \cdot \overline{x_2} \cdot x_3$$

# • Generalized Reed-Muller Expression (GRM)

GRM representation is the generalization of a PPRM expression. Each literal at each product can have arbitrary polarity.

**Example**: The expression of  $x_1 \oplus x_2 \oplus \overline{x_1} \cdot \overline{x_2}$  is a GRM but not a PSDKRO since this expression cannot be achieved using positive/negative Davio or Shannon expression.

#### • Exclusive-OR Sum-of-Products Expression (ESOP)

ESOP representation is a generalization of any AND-EXOR expression. An ESOP is a logic expression that combines arbitrary product terms using XORs.

**Example**: The expression of  $x_1 \oplus x_2 \oplus x_1 \cdot x_2 \oplus \overline{x_1} \cdot \overline{x_2}$  is an ESOP. This representation cannot be achieved by a PSDKRO or GRM.

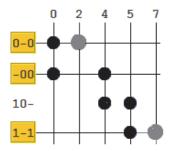

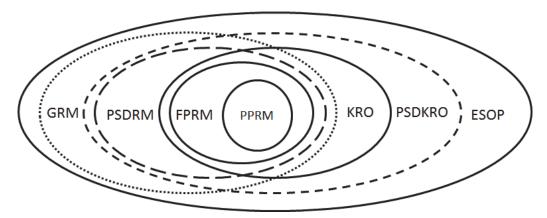

Figure 2.12 summarizes all classes of AND-EXOR expressions in sets, and the characteristics of all classes are compiled in Table 2.5.

Table 2.5: Characteristics of the AND-XOR expressions.

|        | Positive<br>Davio<br>expansion | Negative<br>Davio<br>expansion | Shannon expansion | Different expansions | Arbitrary polarity | Arbitrary products |

|--------|--------------------------------|--------------------------------|-------------------|----------------------|--------------------|--------------------|

| PPRM   | ✓                              |                                |                   |                      |                    |                    |

| FPRM   | ✓                              | ✓                              |                   |                      |                    |                    |

| KRO    | ✓                              | ✓                              | ✓                 |                      |                    |                    |

| PSDRM  | ✓                              | ✓                              |                   | ✓                    |                    |                    |

| PSDKRO | ✓                              | ✓                              | ✓                 | ✓                    |                    |                    |

| GRM    | ✓                              | ✓                              |                   | ✓                    | ✓                  |                    |

| ESOP   | ✓                              | ✓                              | ✓                 | ✓                    | ✓                  | ✓                  |

Figure 2.12: Relationship between various classes of AND-EXOR expressions.

# 3 GENERAL PRINCIPLES OF FUNCTIONAL COMPOSITION

This thesis proposes the functional composition aiming at overcoming the drawbacks of functional decomposition applied to local function rewriting. FC is a novel synthesis paradigm that performs bottom-up association of Boolean functions as opposed to the top-down functional decomposition approach. By performing a bottom-up approach, the costs of initial functions are necessarily known, the logic operations are simple, the subfunctions have sub-optimal and optimal implementations, and a control cost can be easily set.

In this chapter, the functional composition (FC) paradigm is described, and the novelty of FC is introduced by comparing with functional decomposition (FD). The principles of functional composition are discussed.

# 3.1 Functional Decomposition

Functional decomposition (FD) is a method for combinational logic synthesis in which a Boolean function is decomposed into a set of subfunctions. FD has been introduced by the pioneering works of (ASHENHURST, 1959) and (CURTIS, 1962). The results of FD are in the functional domain, meaning that it can produce non-trivial logic rewritings that are very suitable to overcome the structural bias (CHATTERJEE ET AL, 2005). FD has been extensively used in FPGA mapping since it is easy to control the number of inputs at each subfunction (STANION; SECHEN, 1995). There are many related works on functional decomposition, such as disjoint support decomposition (DSD) (BERTACCO; DAMIANI, 1997) and bidecomposition (YANG; CIESIELSKI, 2002).

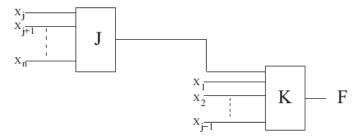

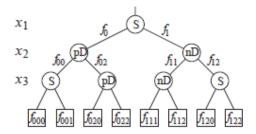

The disjoint support decomposition of a Boolean function  $F(x_1,...,x_n)$  consists in representing f using simpler component functions J and K, such that the inputs of J and K do not share any input variable, and  $F = K(x_1,...,x_{j-1},J(x_j,...,x_n))$ . This DSD is shown in Figure 3.1.

In general, a function has several disjoint support decompositions, which can be superimposed to obtain decompositions with finer granularity. Moreover, it is possible to recursively search for DSDs for functions J and K to produce even smaller components. At the limit, f can be represented as a tree of functions, with the inputs  $x_i$  being the leaves of the tree.

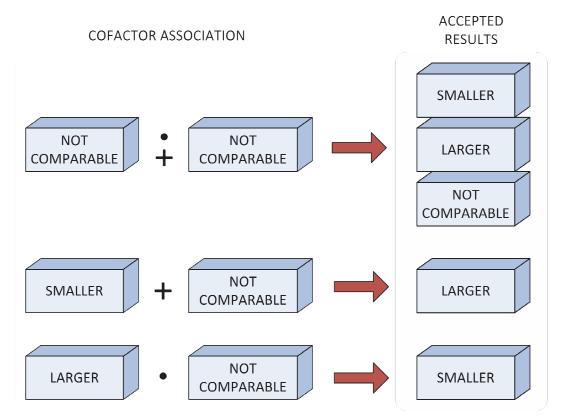

Figure 3.1: A disjoint support decomposition for *F*. Source: (PLAZA; BERTACCO, 2005.)