## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

#### LUCAS ANTUNES TAMBARA

# Analyzing the Impact of Radiation-induced Failures in All Programmable System-on-Chip Devices

Thesis presented in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Microelectronics

Advisor: Dr. Fernanda Lima Kastensmidt

## CIP - CATALOGAÇÃO NA PUBLICAÇÃO

Antunes Tambara, Lucas

Analyzing the Impact of Radiation-induced Failures in All Programmable System-on-Chip Devices / Lucas Antunes Tambara. – 2017.

192 f.

Orientadora: Fernanda Lima Kastensmidt.

Tese (Doutorado) -- Universidade Federal do Rio Grande do Sul, Instituto de Informática, Programa de Pós-Graduação em Microeletrônica. Porto Alegre, BR-RS, 2017.

1. APSoC. 2. SRAM-based FPGA. 3. Radiation effects. I. Lima Kastensmidt, Fernanda, orient. II. Analyzing the Impact of Radiation-induced Failures in All Programmable System-on-Chip Devices.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Rui Vicente Oppermann Vice-Reitor: Prof. Jane Fraga Tutikian

Pró-Reitor de Pós-Graduação: Prof. Celso Giannetti Loureiro Chaves

Diretor do Instituto de Informática: Prof. Luís da Cunha Lamb Coordenador do PGMICRO: Prof. Fernanda Lima Kastensmidt

Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

#### **ACKNOWLEDGMENTS**

I would like to start by thanking my wife, Renata Borella Venturini, for always supporting me unconditionally and for always walking along by my side, no matter the country.

To my parents, Lúcia Regina Antunes Tambara and Pedro Jorge Tadiello Tambara, for my existence, unconditional support, and everything else that involve the relation between parents and sons.

To UFRGS, Institute of Informatics, PGMICRO, and the Brazilian research agencies CAPES, CNPq, and FAPERGS, for the financial support and for putting their facilities at my disposal so I could develop my research.

To my advisor, Fernanda Lima Kastensmidt, for the confidence, lessons, and patience. Thank you for pushing me forward and encouraging me in my academic and personal decisions.

To Matteo Sonza Reorda, from Politecnico di Torino, and Salvatore Danzeca, from CERN, for having accepted me as a visiting researcher in their research institutes during my Ph.D.

To Paolo Rech, Nilberto Medina, Nemitala Added, Marcilei Guazzelli, and several other professors and researchers that contributed to this thesis.

To all my colleagues from laboratories 230/232 from UFRGS and others that are already in other rooms, cities, or countries.

To all of you, my sincere thanks.

#### **ABSTRACT**

The recent advance of the semiconductor industry has allowed the integration of complex components and systems' architectures into a single silicon die. Nowadays, state-ofthe-art FPGAs include not only the programmable logic fabric but also hard-core parts, such as hard-core general-purpose processors, dedicated processing blocks, interfaces to various peripherals, on-chip bus structures, and analog blocks. These new devices are commonly called of All Programmable System-on-Chip (APSoC) devices. One of the major concerns about radiation effects on APSoCs is that radiation-induced errors may have different probability and criticality in their heterogeneous hardware parts at both device and design levels. For this reason, this work performs a deep investigation about the radiation effects on APSoCs and the correlation between hardware and software resources sensitivity in the overall system performance. Several static and dynamic experiments were performed on different hardware parts of an APSoC to better understand the trade-offs between reliability and performance of each part separately. Results show that there is a trade-off between design cross section and performance to be analyzed when developing a system on an APSoC. Therefore, today it is mandatory to take into account each design option available and all the parameters of the system involved, such as the execution time and the workload of the system, and not only its cross section. As an example, results show that it is possible to increase the performance of a system up to 5,000 times by changing its architecture with a small impact in cross section (increase up to 8 times), significantly increasing the operational reliability of the system. This work also proposes a reliability analysis flow based on fault injection for estimating the reliability trend of hardware-only designs, software-only designs, and hardware and software co-designs. It aims to accelerate the search for the design scheme with the best trade-off between performance and reliability among the possible ones. The methodology takes into account four groups of parameters, which are the following: area resources and performance; the number of output errors and critical bits; radiation measurements, such as static and dynamic cross sections; and, Mean Workload Between Failures. The obtained results show that the proposed flow is a suitable method for estimating the reliability trend of system designs on APSoCs before radiation experiments.

**Keywords**: APSoC, SRAM-based FPGA, Processor, Reliability, Radiation effects, Radiation experiment, Fault injection, SEE, SEU, Execution time, Trade-off.

# Avaliação do Impacto de Falhas Induzidas pela Radiação em Dispositivos Sistemas-em-Chip Totalmente Programáveis

#### **RESUMO**

O recente avanço da indústria de semicondutores tem possibilitado a integração de componentes complexos e arquiteturas de sistemas dentro de um único chip de silício. Atualmente, FPGAs do estado da arte incluem, não apenas a matriz de lógica programável, mas também outros blocos de hardware, como processadores de propósito geral, blocos de processamento dedicado, interfaces para vários periféricos, estruturas de barramento internas ao chip, e blocos analógicos. Estes novos dispositivos são comumente chamados de Sistemasem-Chip Totalmente Programáveis (APSoCs). Uma das maiores preocupações acerca dos efeitos da radiação em APSoCs é o fato de que erros induzidos pela radiação podem ter diferente probabilidade e criticalidade em seus blocos de hardware heterogêneos, em ambos os níveis de dispositivo e projeto. Por esta razão, este trabalho realiza uma investigação profunda acerca dos efeitos da radiação em APSoCs e da correlação entre a sensibilidade de recursos de hardware e software na performance geral do sistema. Diversos experimentos estáticos e dinâmicos inéditos foram realizados nos blocos de hardware de um APSoC a fim de melhor entender as relações entre confiabilidade e performance de cada parte separadamente. Os resultados mostram que há um comprometimento a ser analisado entre o desempenho e a área de choque de um projeto durante o desenvolvimento de um sistema em um APSoC. Desse modo, é fundamental levar em consideração cada opção de projeto disponível e todos os parâmetros do sistema envolvidos, como o tempo de execução e a carga de trabalho, e não apenas a sua seção de choque. Exemplificativamente, os resultados mostram que é possível aumentar o desempenho de um sistema em até 5.000 vezes com um pequeno aumento na sua seção de choque de até 8 vezes, aumentando assim a confiabilidade operacional do sistema. Este trabalho também propõe um fluxo de análise de confiabilidade baseado em injeções de falhas para estimar a tendência de confiabilidade de projetos somente de hardware, de software, ou de hardware e software. O fluxo objetiva acelerar a procura pelo esquema de projeto com a melhor relação entre performance e confiabilidade dentre as opções possíveis. A metodologia leva em consideração quatro grupos de parâmetros, os quais são: recursos e performance; erros e bits críticos; medidas de radiação, tais como seções de choque estáticas e dinâmicas; e, carga de trabalho média entre falhas. Os resultados obtidos mostram que o fluxo proposto é um método apropriado para estimar tendências de confiabilidade de projeto de sistemas em APSoCs antes de experimentos com radiação.

**Palavras-chave**: APSoC, FPGA baseado em SRAM, Processador, Confiabilidade, Efeitos da radiação, Experimentos com radiação, Injeção de falhas, SEE, SEU, Tempo de execução, Correlação.

# LIST OF FIGURES

| Figure 2.1 – Bock diagram of a processor with a SIMD engine embedded (a) and a simplified block       |      |  |  |  |

|-------------------------------------------------------------------------------------------------------|------|--|--|--|

| diagram of a SIMD engine (b).                                                                         |      |  |  |  |

| Figure 2.2 - Processor models: (a) Symmetric, (b) Asymmetric, and (c) Heterogeneous                   | 24   |  |  |  |

| Figure 2.3 – Generic architecture of an APSoC.                                                        |      |  |  |  |

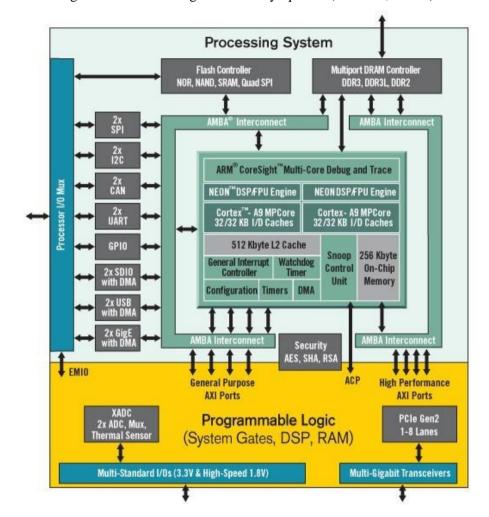

| Figure 2.4 – Block diagram of the Zynq-7000 (XILINX, 2015d)                                           | 28   |  |  |  |

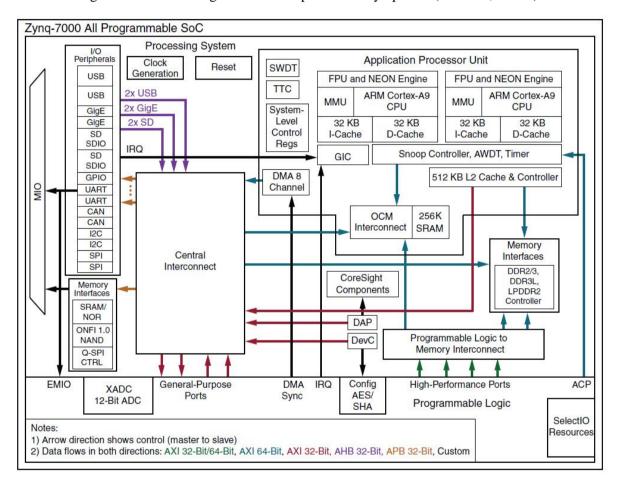

| Figure 2.5 – Block diagram of the PS part of the Zynq-7000 (XILINX, 2015d)                            |      |  |  |  |

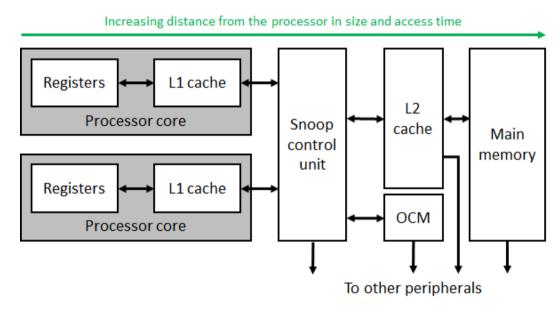

| Figure 2.6 – Zynq-7000's memory hierarchy.                                                            |      |  |  |  |

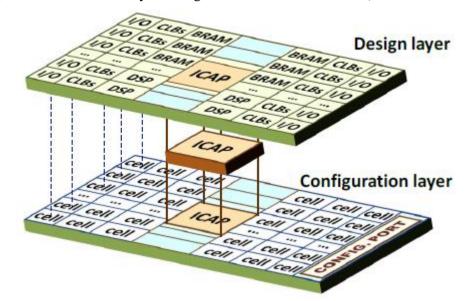

| Figure 2.7 – Abstraction layers of a generic SRAM-based FPGA (TARRILLO, 2014)                         | 34   |  |  |  |

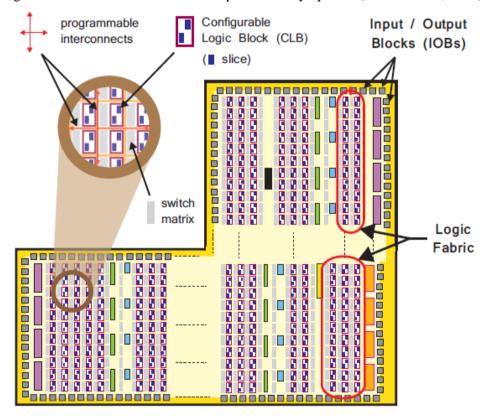

| Figure 2.8 – Basic structure of the PL part of the Zynq-7000 (CROCKETT, 2014)                         | 34   |  |  |  |

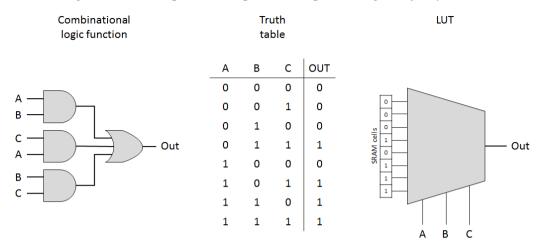

| Figure 2.9 – Example of a 3-input LUT implementing a majority voter.                                  |      |  |  |  |

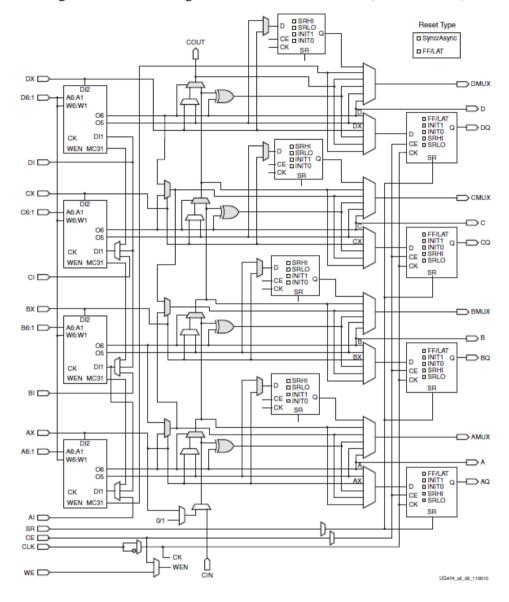

| Figure 2.10 – Block diagram of a Xilinx 7-Series slice (XILINX, 2014)                                 |      |  |  |  |

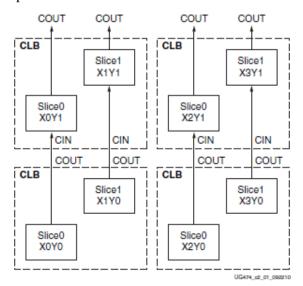

| Figure 2.11 - Relationship between CLBs and Slices in Xilinx 7-Series FPGAs (XILINX, 2014)            |      |  |  |  |

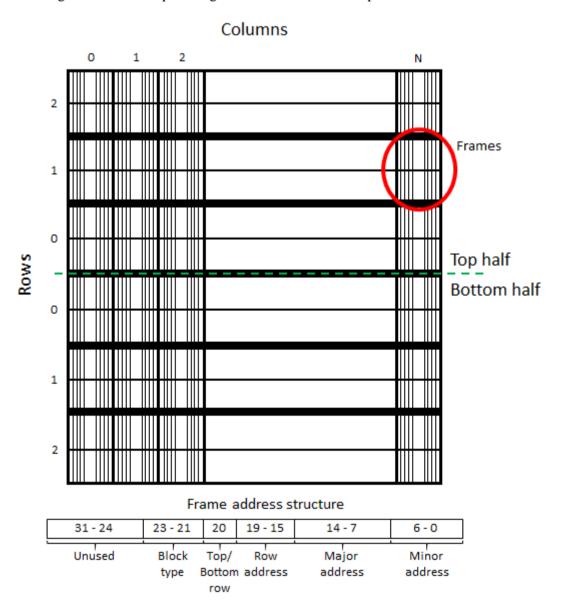

| Figure 2.12 – Example of a generic Xilinx FPGA floorplan and frame structure.                         |      |  |  |  |

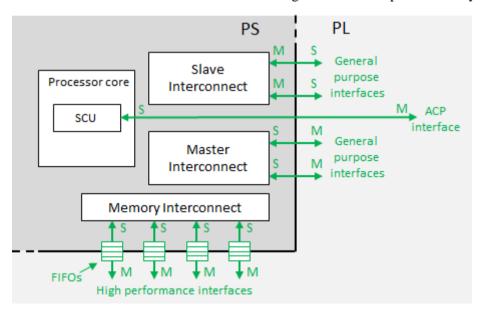

| Figure 2.13 – AXI interconnects and interfaces connecting the PS and PL parts of the Zynq-7000        | 39   |  |  |  |

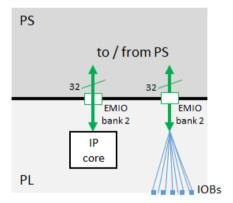

| Figure 2.14 – EMIO interface between the PS and PL parts of the Zynq-7000                             | 40   |  |  |  |

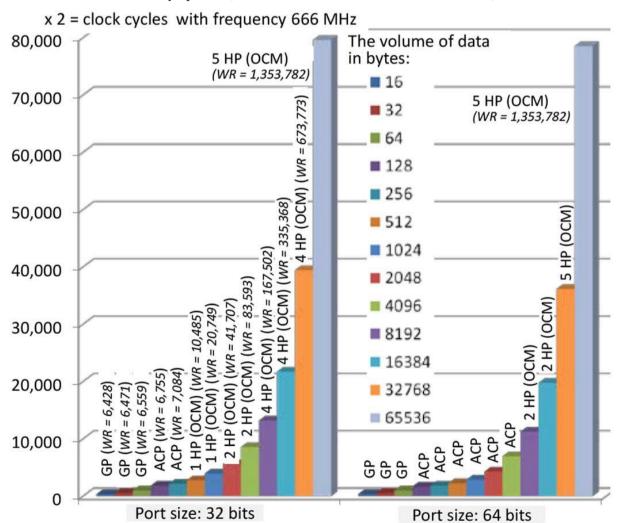

| Figure 2.15 – Obtained best methods for transferring different numbers of data items between PS an    | ıd   |  |  |  |

| PL in Zynq-7000 (SILVA, SKLYAROV, SKLIAROVA, 2015)                                                    | 41   |  |  |  |

| Figure 2.15 – Example of parallel versus sequential execution.                                        | 43   |  |  |  |

| Figure 2.16 – Estimated overall system speed-up provided by the addition of different numbers of      |      |  |  |  |

| hardware accelerators.                                                                                | 44   |  |  |  |

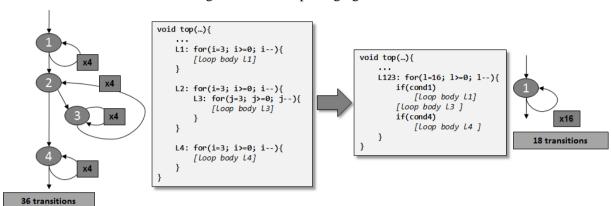

| Figure 2.17 – Example of a control and data flow extraction during the HLS process.                   | 45   |  |  |  |

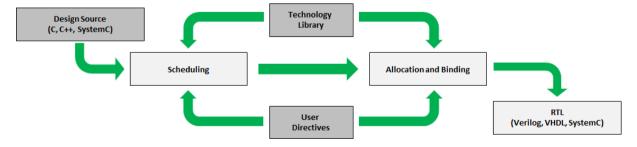

| Figure 2.18 – The essential three HLS phases and their relations                                      | 45   |  |  |  |

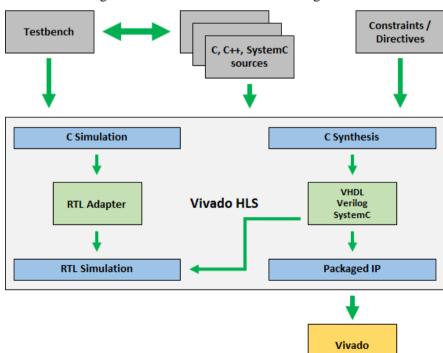

| Figure 2.19 – Xilinx Vivado HLS design flow.                                                          | 46   |  |  |  |

| Figure 2.20 – Function pipelining behavior.                                                           | 48   |  |  |  |

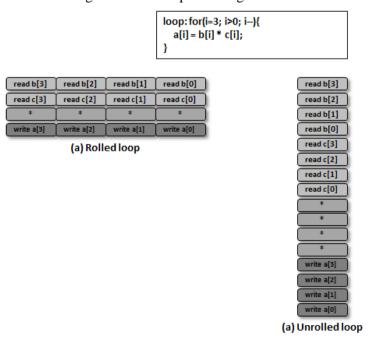

| Figure 2.21 – Loop unrolling behavior.                                                                | 48   |  |  |  |

| Figure 2.22 – Loop merging behavior                                                                   | 49   |  |  |  |

| Figure 2.23 – Influence of the hardware accelerator granularity on the execution time of a system     |      |  |  |  |

| (LAFOND, LILIUS, 2008).                                                                               |      |  |  |  |

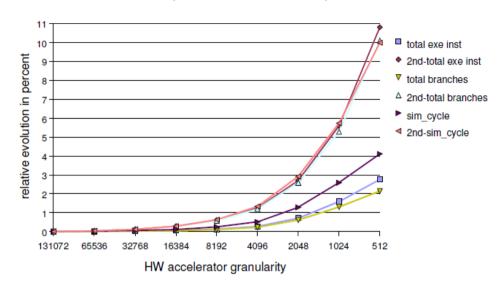

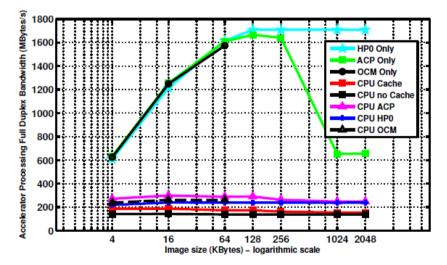

| Figure 2.24 – Impact of the cache architecture on the average execution time (speed-up) relative to a | a    |  |  |  |

| baseline system, which employs a single accelerator running sequentially using a 1-way (direct-       |      |  |  |  |

| mapped) 2KB cache with a 32-byte line size (CHOI et al., 2012)                                        |      |  |  |  |

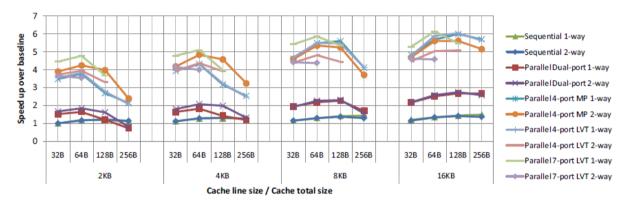

| Figure 2.25 – Processing bandwidth comparison of different acceleration methods in Zynq-7000. Da      |      |  |  |  |

| size sweeps from 4 KB to 2048 KB (SADRI et al., 2013)                                                 |      |  |  |  |

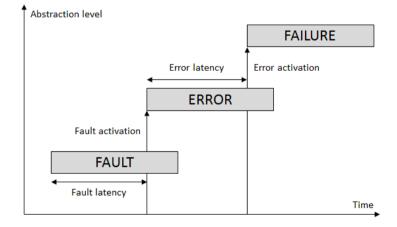

| Figure 3.1 – Fault, error, and failure propagation.                                                   |      |  |  |  |

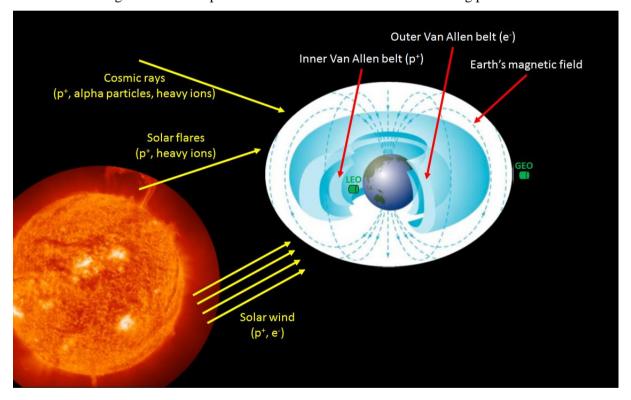

| Figure 3.2 – The space environment and its sources of ionizing particles.                             | 58   |  |  |  |

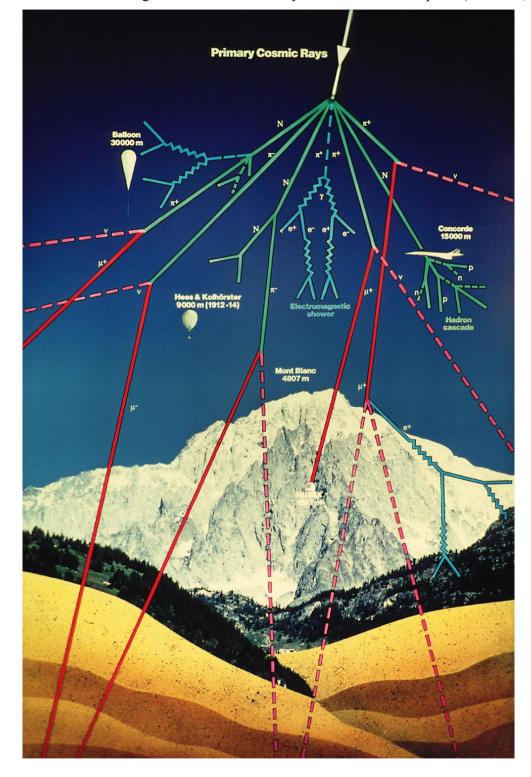

| Figure 3.3 – Particle cascade generated from cosmic rays in the Earth's atmosphere (STEFAN, 2001)     | 1).  |  |  |  |

|                                                                                                       | 61   |  |  |  |

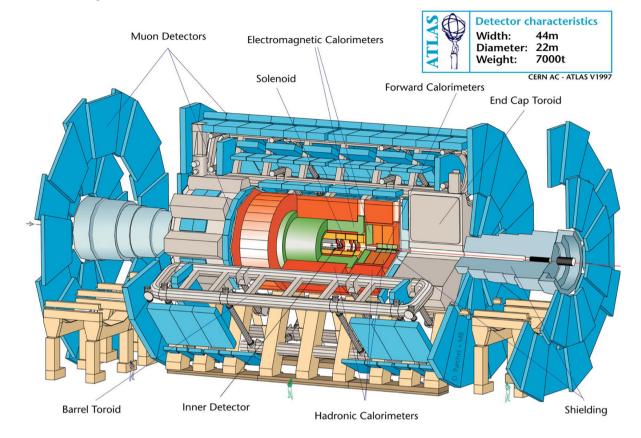

| Figure 3.4 – General view of the CERN/LHC/ATLAS detector (ATLAS, 2016)                                |      |  |  |  |

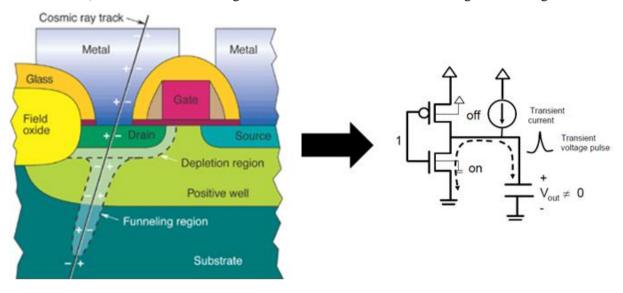

| Figure 3.5 – Electron-hole pairs track generated by an ionized particle in a CMOS transistor (SOOS    |      |  |  |  |

| 2009) on the left and the charge collection mechanism in an inverter gate on the right                |      |  |  |  |

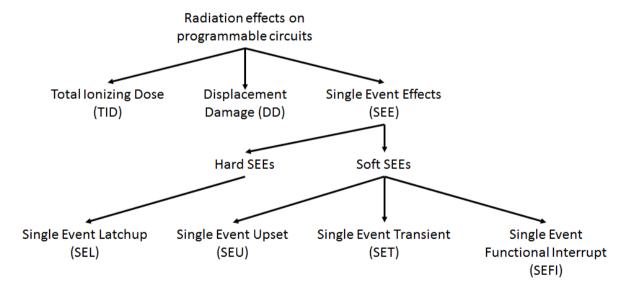

| Figure 3.6 – Main radiation effects on programmable circuits. Adapted from (QUINN et al., 2015a).     |      |  |  |  |

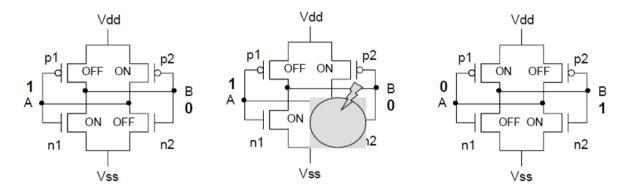

| Figure 3.7 – Example of Single Event Upset (KASTENSMIDT, CARRO, REIS, 2006)                           | 66   |  |  |  |

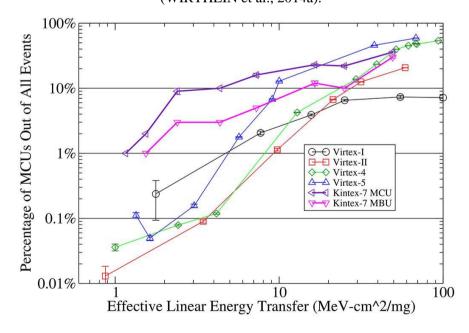

| Figure 3.8 – MCU events as a percentage of SEUs for different families of Xilinx FPGAs                |      |  |  |  |

| (WIRTHLIN et al., 2014a).                                                                             | 66   |  |  |  |

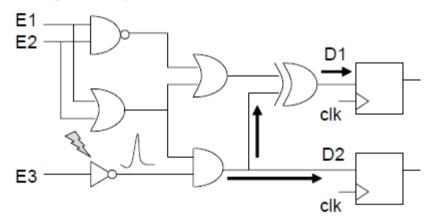

| Figure 3.9 – Example of a Single Event Transient (KASTENSMIDT, CARRO, REIS, 2006)                     |      |  |  |  |

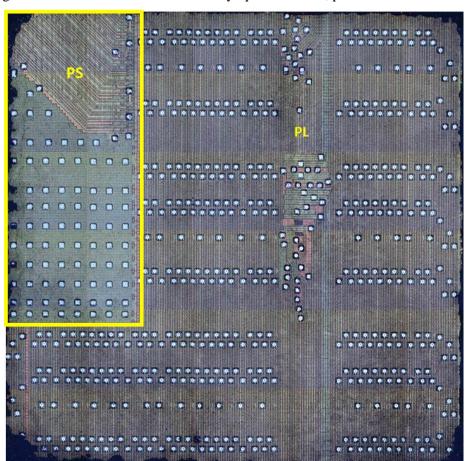

| Figure 3.10 – View of the surface of a Zynq-7000 device, part XC7Z020-CLG484                          |      |  |  |  |

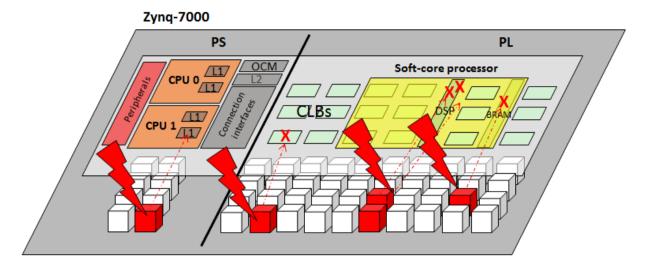

| Figure 3.11 – Possible effects of SEEs in Zynq-7000 and similar APSoCs.                               |      |  |  |  |

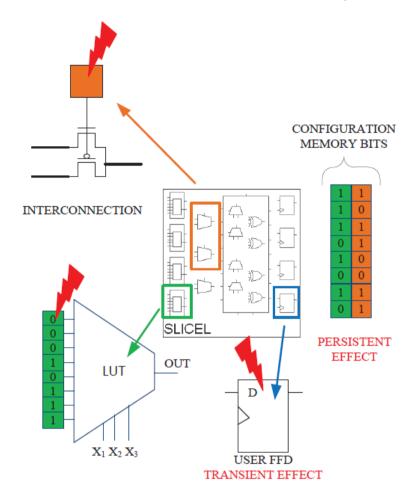

| Figure 3.12 – Possible effects of SEUs in SRAM-based FPGAs (TONFAT, 2015).                            |      |  |  |  |

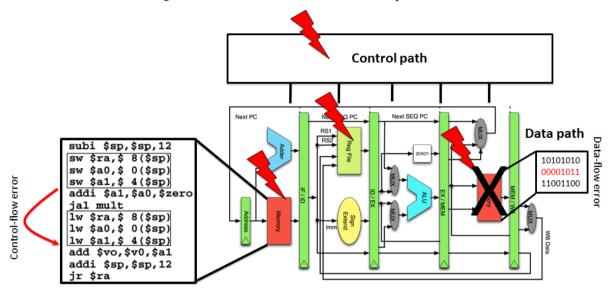

| Figure 3.13 – Possible effects of SEEs in processors                                                  |      |  |  |  |

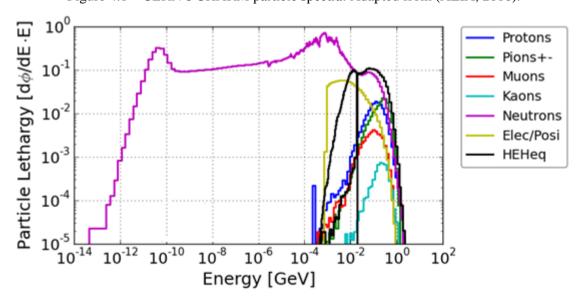

| Figure 4.1 – CERN's CHARM particle spectra. Adapted from (ALÍA, 2016)                                 | . 75 |  |  |  |

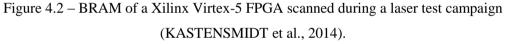

| Figure 4.2 – BRAM of a Xilinx Virtex-5 FPGA scanned during a laser test campaign                        |

|---------------------------------------------------------------------------------------------------------|

| (KASTENSMIDT et al., 2014)                                                                              |

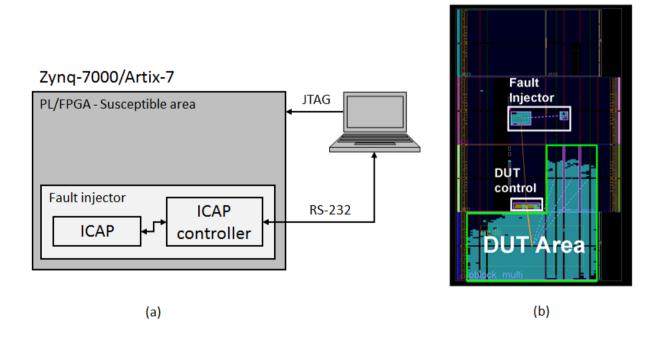

| Figure 4.3 – Block diagram of the fault injection platform used in this thesis in (a) and an example of |

| the FPGA floorplanning with the fault injector and the DUT placed in (b)                                |

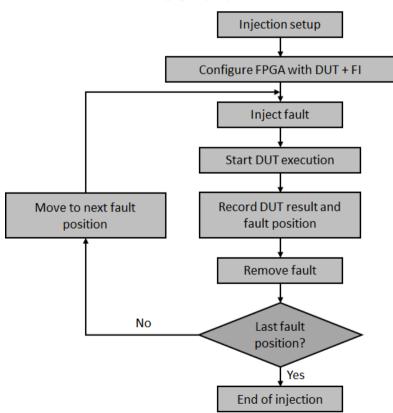

| Figure 4.4 – Flow diagram illustrating the hardware fault injection procedure in the Zynq-7000's PL     |

| and Artix-780                                                                                           |

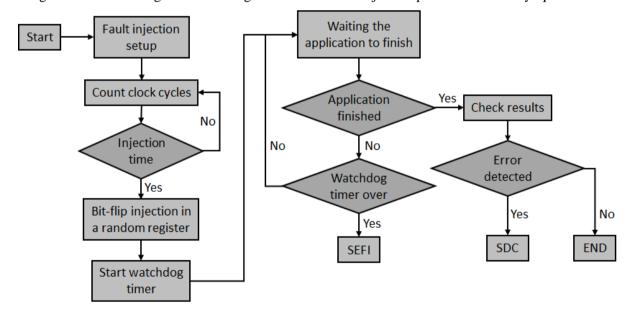

| Figure 4.5 – Platform setup of the software fault injector                                              |

| Figure 4.6 – Flow diagram illustrating the software fault injection procedure in the Zynq-7000's PS.82  |

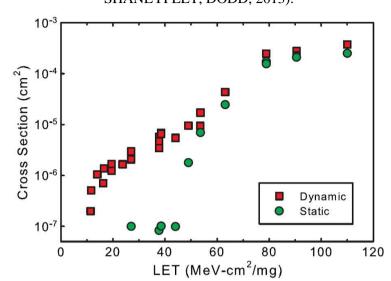

| Figure 4.7 – SEU cross section for static and dynamic tests in a memory (SCHWANK,                       |

| SHANEYFELT, DODD, 2013) 84                                                                              |

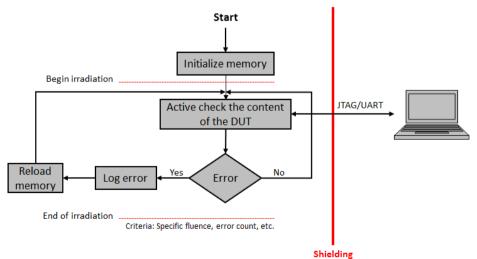

| Figure 4.8 – Static test flow diagram. Adapted from (IROM, 2008)                                        |

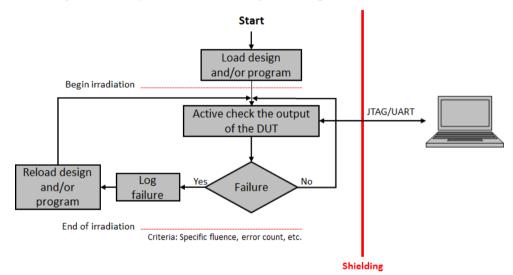

| Figure 4.9 – Dynamic test flow diagram. Adapted from (IROM, 2008)                                       |

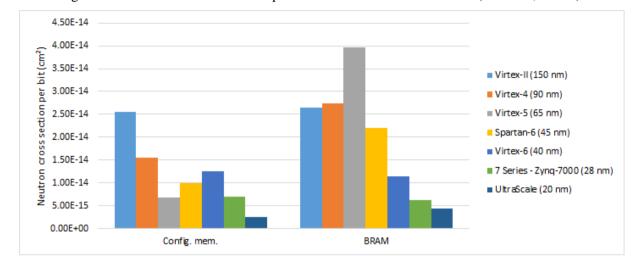

| Figure 4.10 – Neutron cross section per bit for different Xilinx devices (XILINX, 2016c)                |

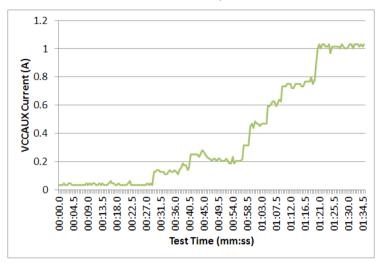

| Figure 4.11 – SEL occurrence in the PL part of Zynq-7000 during heavy ion experiments (AMRBAR           |

| et al., 2015)                                                                                           |

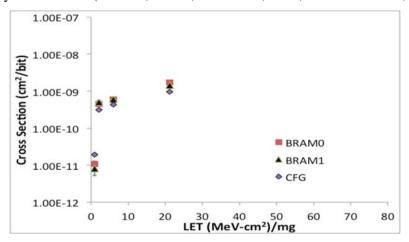

| Figure 4.12 – Heavy ion SEU static cross section for the PL part of the Zynq-7000 configuration         |

| memory and BRAMs (ALLEN, IROM, AMRBAR, 2015; AMRBAR et al., 2015)                                       |

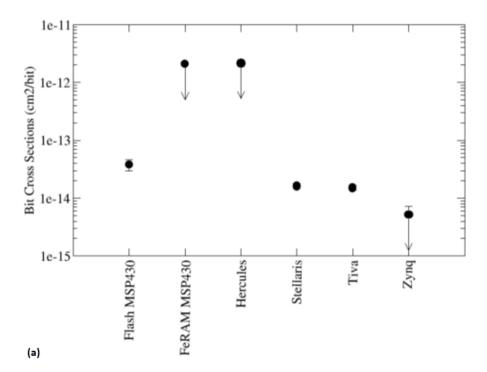

| Figure 4.13 – (a) SEU cross section and (b) SET and SEFI cross section in neutrons for different SoCs   |

| (QUINN et al., 2014b)                                                                                   |

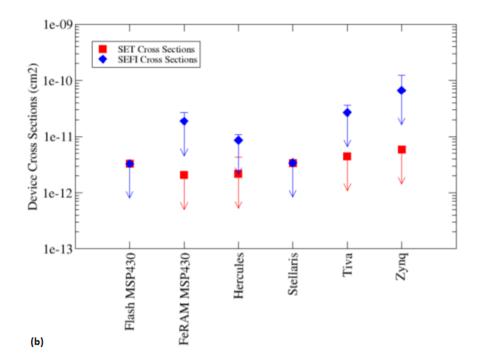

| Figure 4.14 – Measured Zynq-7000 SDC and SEFI cross sections of applications running bare to the        |

| metal (Bare SDC and Bare SEFI) and on the top of Linux (Linux SDC and Linux SEFI) compared to           |

| the expected standalone Linux SEFI cross section (dashed line). (SANTINI et al., 2016)                  |

| Figure 4.15 – Heavy ion SEFI cross sections for the MSS, GPIO, and FIC blocks of the SmartFusion2       |

| (REZZAK et al., 2015)                                                                                   |

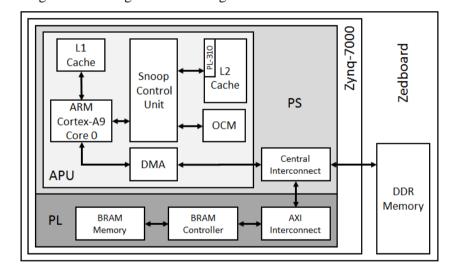

| Figure 5.1 – Integrated block diagram of the static tests architectures                                 |

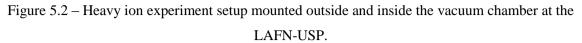

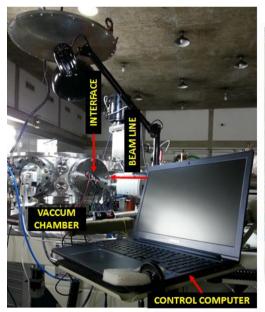

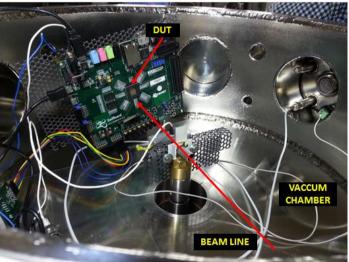

| Figure 5.2 – Heavy ion experiment setup mounted outside and inside the vacuum chamber at the            |

| LAFN-USP                                                                                                |

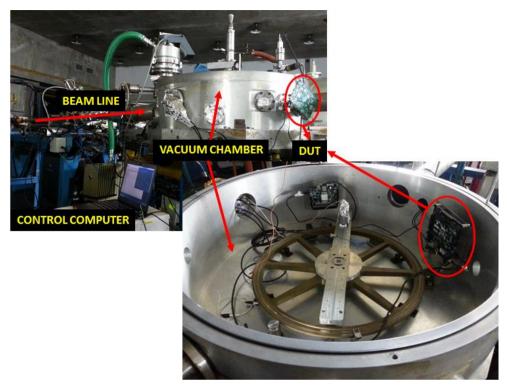

| Figure 5.3 – Microscopic section of a Zynq-7000 device, part XC7Z020-CLG484 102                         |

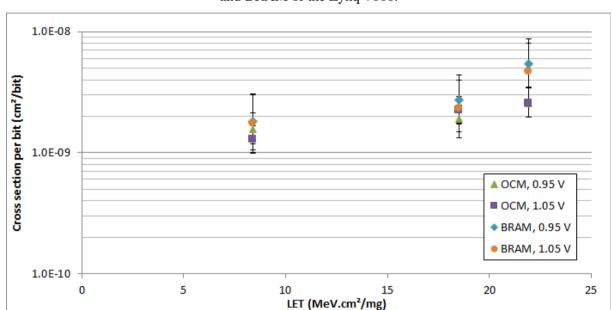

| Figure 4.4 – Cross section results from the heavy ion irradiations in the embedded memories OCM         |

| and BRAM of the Zynq-7000.                                                                              |

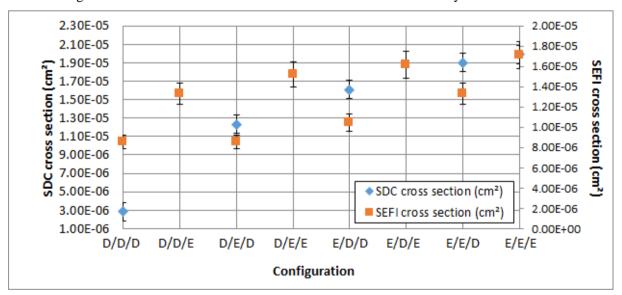

| Figure 5.5 – Obtained SDC and SEFI cross sections from the heavy ion irradiations                       |

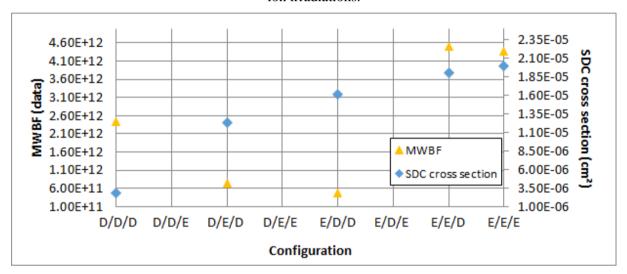

| Figure 5.6 – Comparison between the obtained SDC cross section and MWBF values from the heavy           |

| ion irradiations                                                                                        |

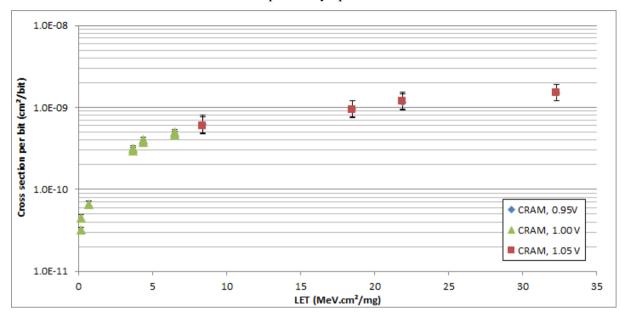

| Figure 6.1 – Cross section results from the heavy ion irradiations in the configuration memory of the   |

| PL part of Zynq-7000.                                                                                   |

| Figure 6.2 – Cross section results from the proton irradiations in the configuration memory of the PL   |

| part of Zynq-7000.                                                                                      |

| Figure 6.3 – Proposed reliability analysis flow for hardware-only designs                               |

| Figure 6.4 – Architecture of the (a) processor-based design and the (b) HLS-based design                |

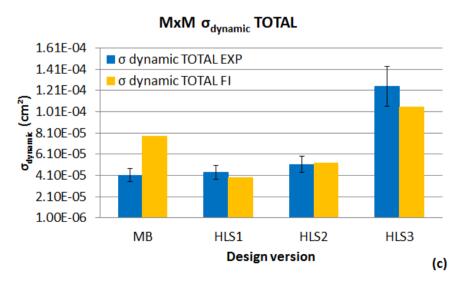

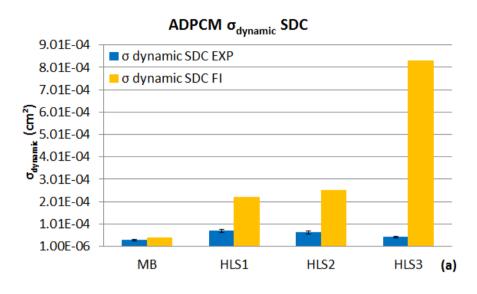

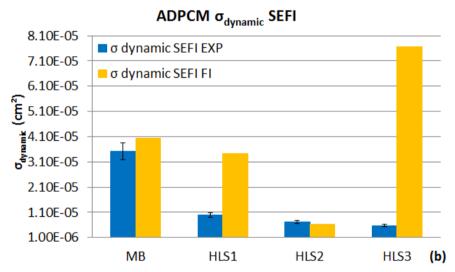

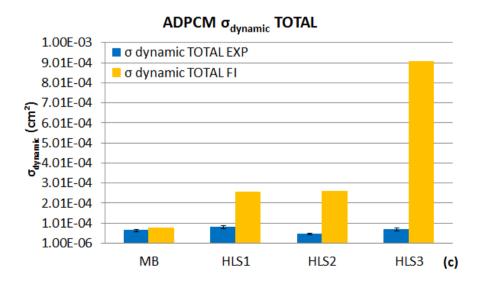

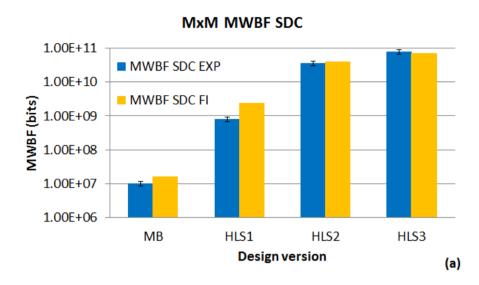

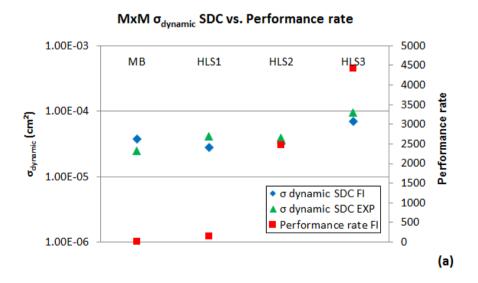

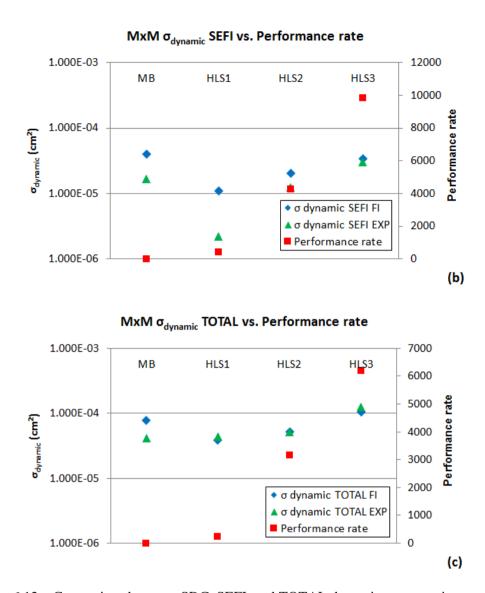

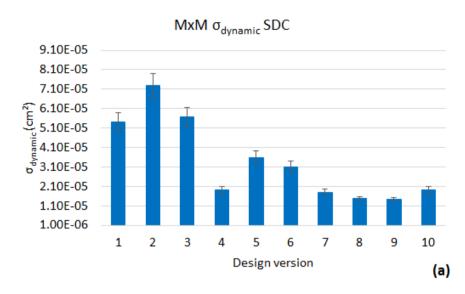

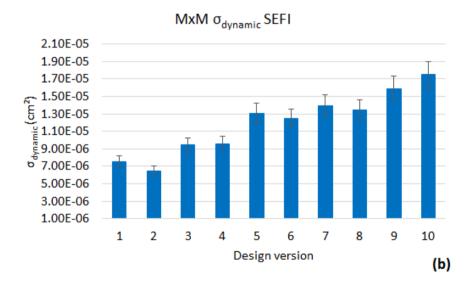

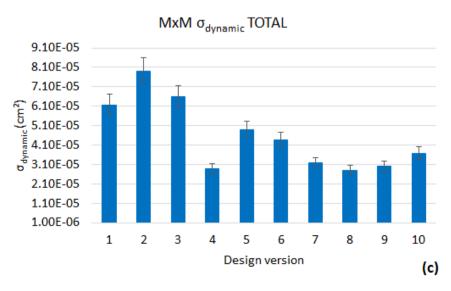

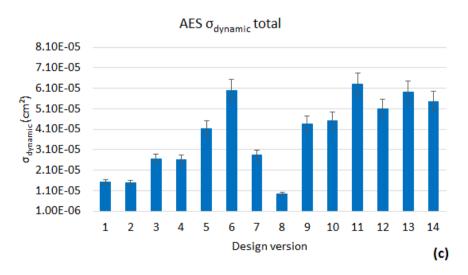

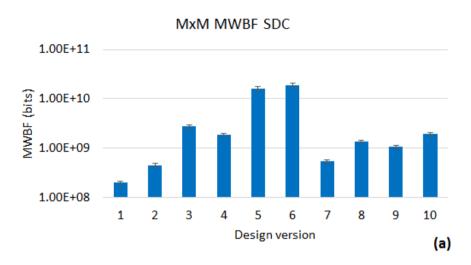

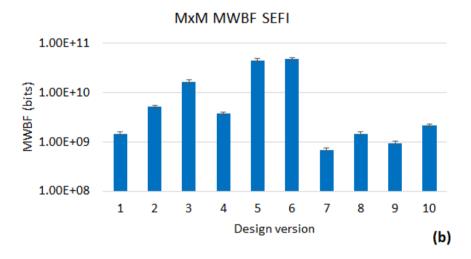

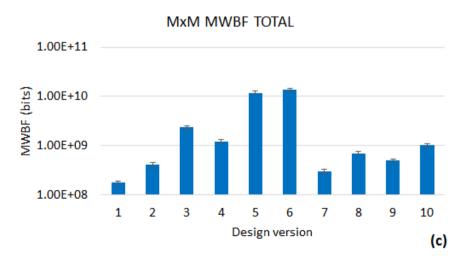

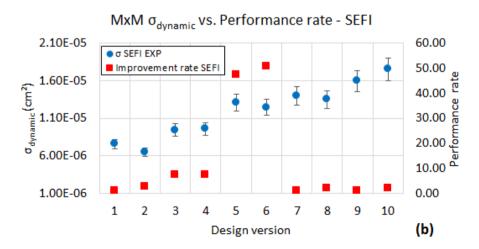

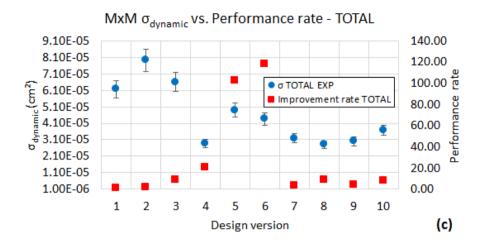

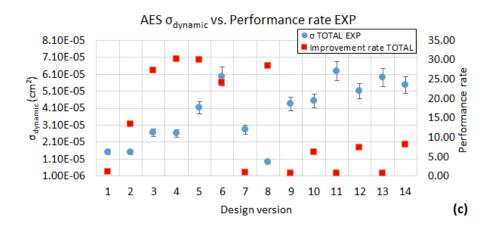

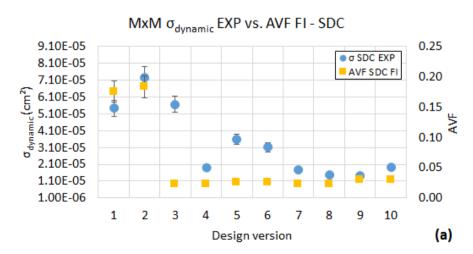

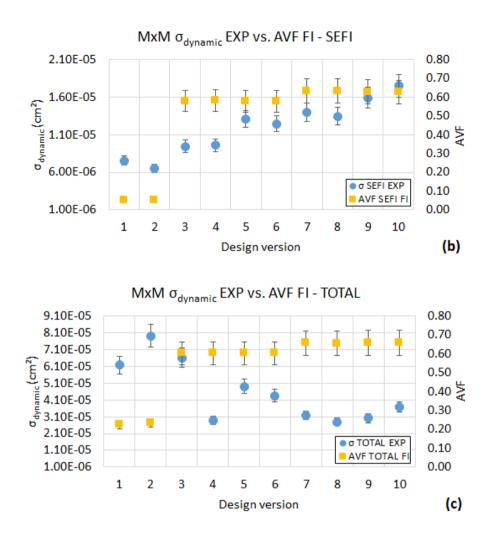

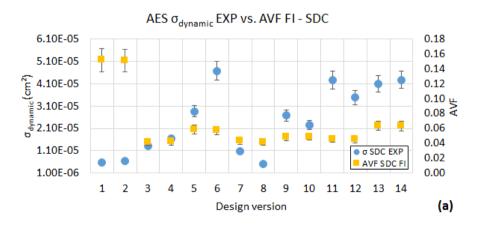

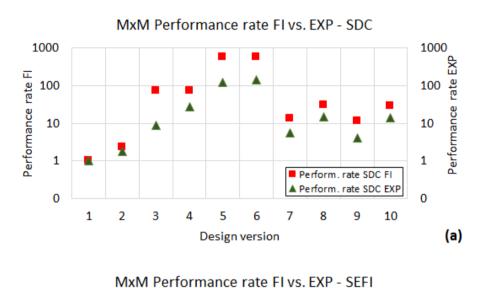

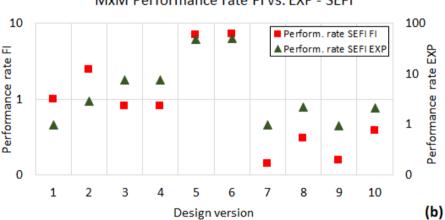

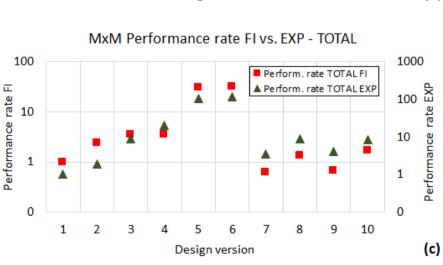

| Figure 6.5 – SDC, SEFI, and TOTAL dynamic cross section results obtained for the MxM designs            |

| from both fault injections and radiation experiments                                                    |

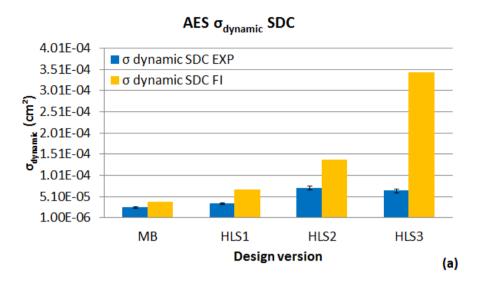

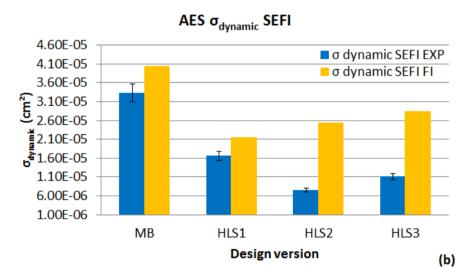

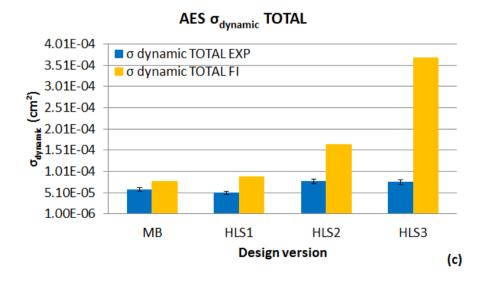

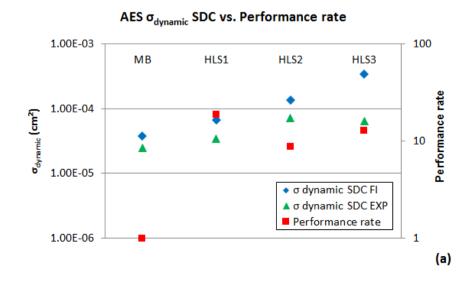

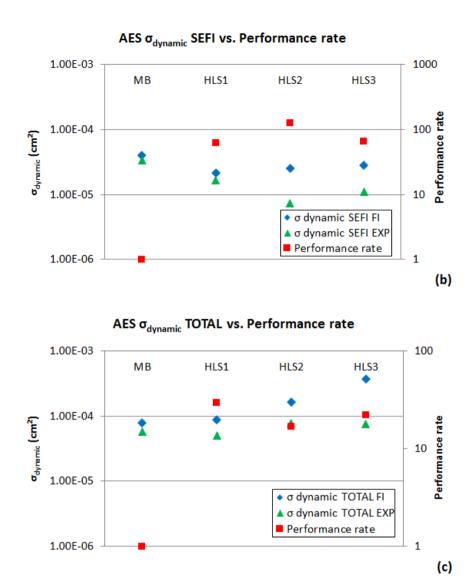

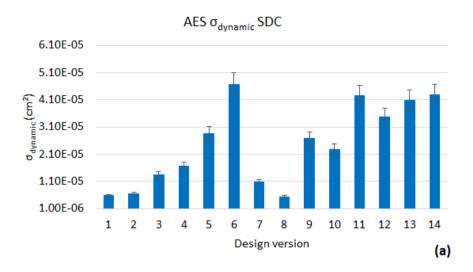

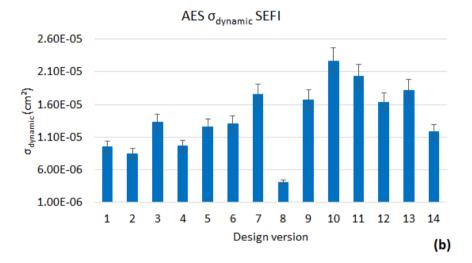

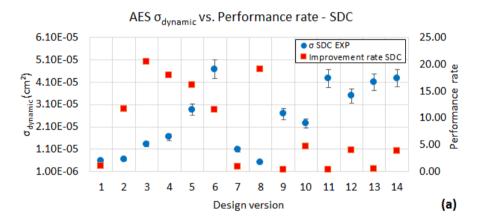

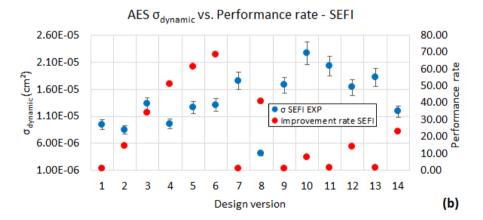

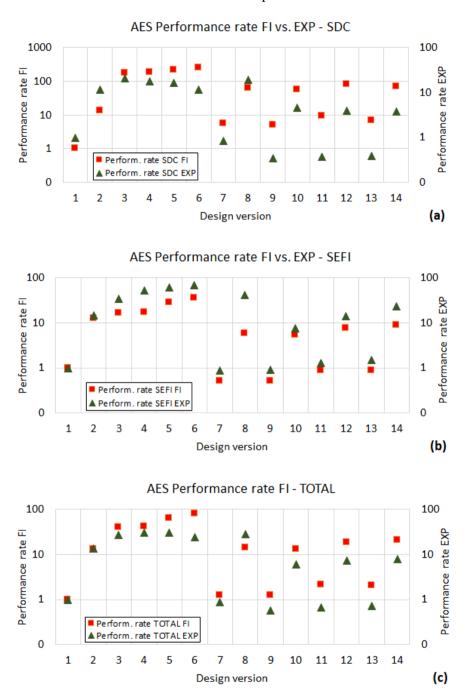

| Figure 6.6 – SDC, SEFI, and TOTAL dynamic cross section results obtained for the AES designs both       |

| fault injections and radiation experiments                                                              |

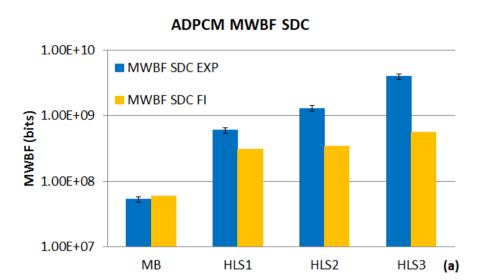

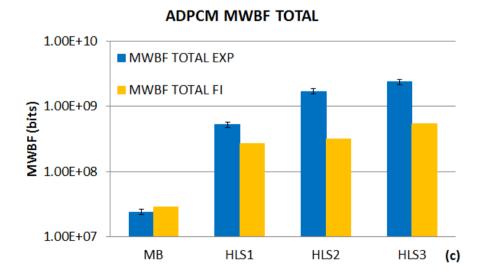

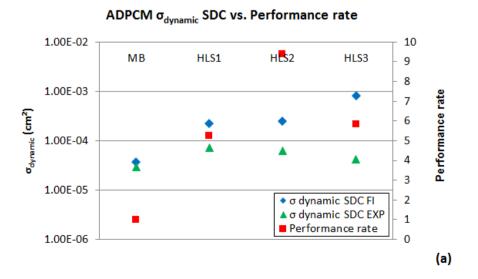

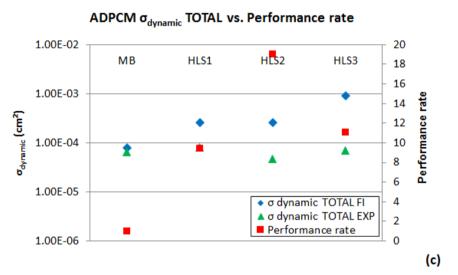

| Figure 6.7 – SDC, SEFI, and TOTAL dynamic cross section results obtained for the ADPCM designs          |

| both fault injections and radiation experiments                                                         |

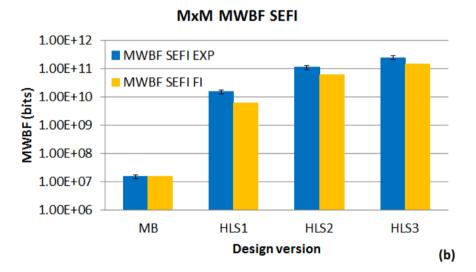

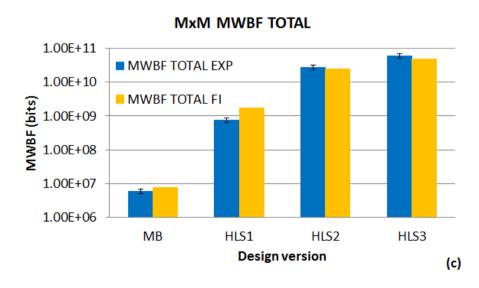

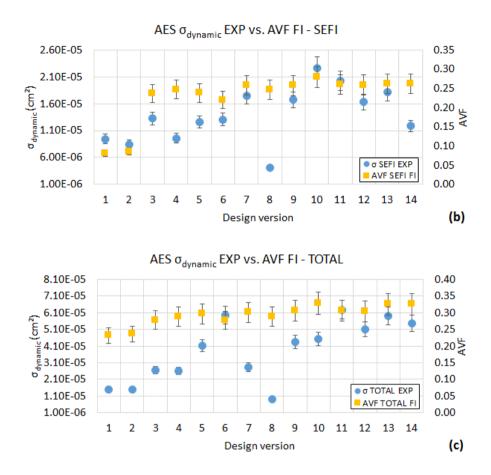

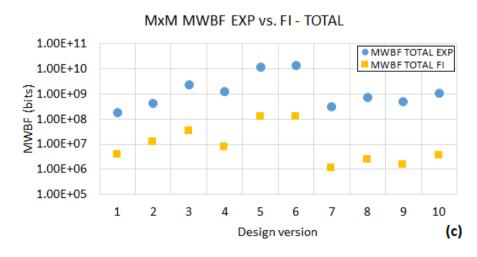

| Figure 6.8 – SDC, SEFI, and TOTAL MWBF results obtained for the MxM designs both fault                  |

| injections and radiation experiments                                                                    |

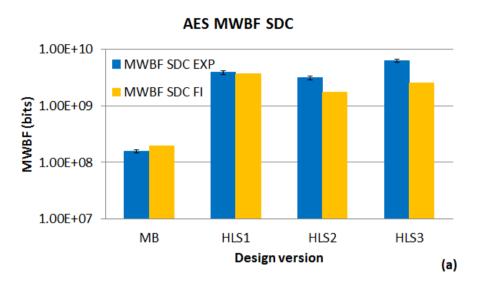

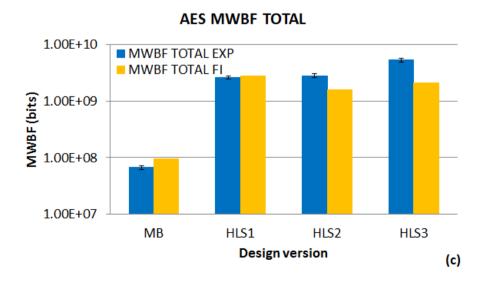

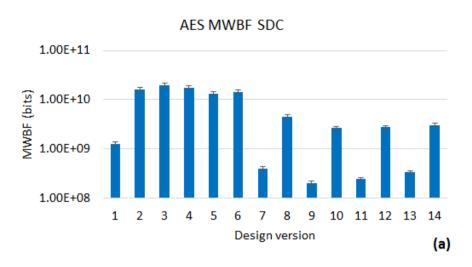

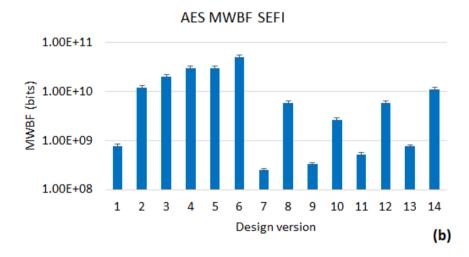

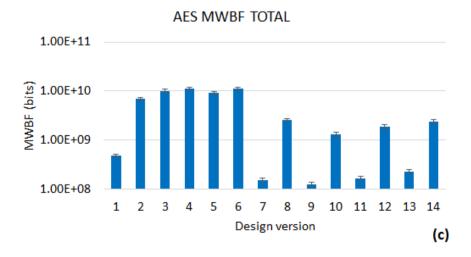

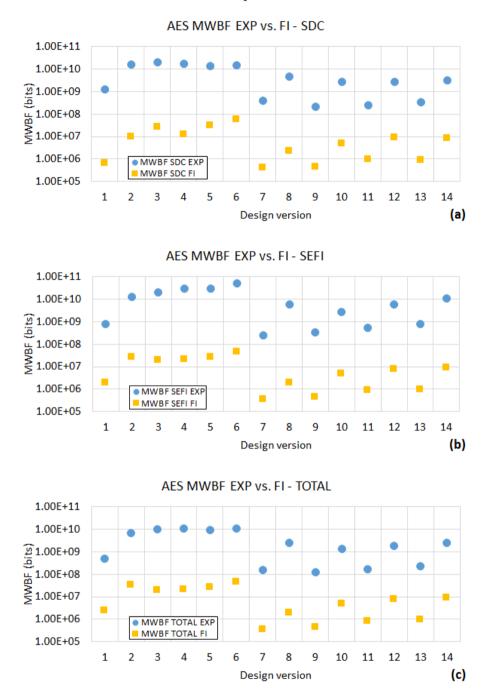

| Figure 6.9 – SDC, SEFI, and TOTAL MWBF results obtained for the AES designs both fault                  |

| injections and radiation experiments                                                                    |

| Figure 6.10 – SDC, SEFI, and TOTAL MWBF results obtained for the ADPCM designs both fault               |

|                                                                                                         |

| injections and radiation experiments                                                                    |

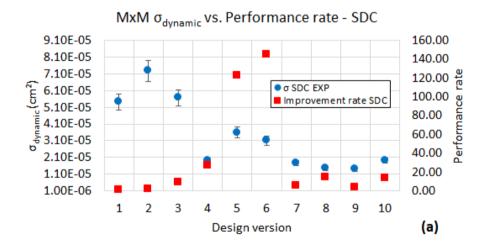

| respective performance rates for the MxM designs from fault injection and radiation experiment          |

| results                                                                                                 |

| 10ourio 13U                                                                                             |

| Figure 6.12 – Comparison between SDC, SEFI, and TOTAL dynamic cross sections and their respective performance rates for the AES designs from fault injection and radiation experiment results    |   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Figure 6.13 – Comparison between SDC, SEFI, and TOTAL dynamic cross sections and their respective performance rates for the ADPCM designs from fault injection and radiation experiment results. |   |

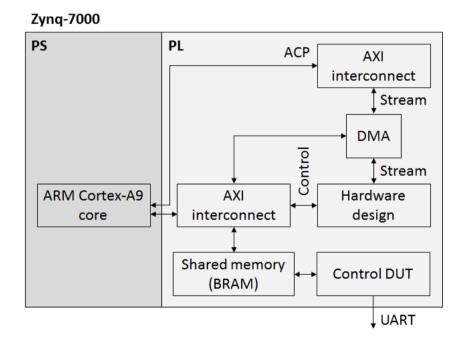

| Figure 7.1 – Block diagram of the case-study multiprocessor-based heterogeneous system                                                                                                           |   |

| Figure 7.2 – Matrix multiplication algorithm                                                                                                                                                     |   |

| Figure 7.3 – Generic representation of the case-study benchmark algorithms                                                                                                                       |   |

| Figure 7.4 – Block diagram of the architecture developed for evaluating the case-study hardware and                                                                                              | _ |

| software co-designs in Zynq-7000.                                                                                                                                                                | , |

| Figure 7.5 - Heavy ion experiment setup mounted at the new beam line of the LAFN-USP                                                                                                             |   |

| Figure 7.6 – SDC, SEFI, and TOTAL dynamic cross section results obtained for the MxM designs                                                                                                     | , |

| from radiation experiments.                                                                                                                                                                      | 7 |

| Figure 7.7 – SDC, SEFI, and TOTAL dynamic cross section results obtained for the AES designs from                                                                                                |   |

| radiation experiments                                                                                                                                                                            |   |

| Figure 7.8 – SDC, SEFI, and TOTAL MWBF results obtained for the MxM designs from radiation                                                                                                       | , |

| experiments                                                                                                                                                                                      | ) |

| Figure 7.9 – SDC, SEFI, and TOTAL MWBF results obtained for the AES designs from radiation                                                                                                       |   |

| experiments                                                                                                                                                                                      | ) |

| Figure 7.10 – Comparison between SDC, SEFI, and TOTAL dynamic cross sections and their                                                                                                           | • |

| respective performance rates for the MxM designs from radiation experiment results                                                                                                               | ı |

| Figure 7.11 – Comparison between SDC, SEFI, and TOTAL dynamic cross sections and their                                                                                                           | - |

| respective performance rates for the AES designs from radiation experiment results                                                                                                               | 2 |

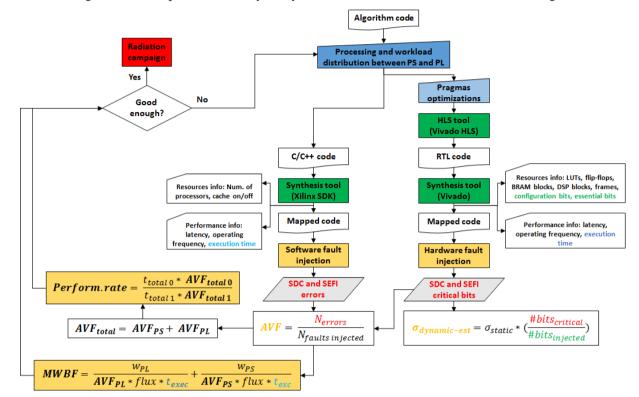

| Figure 8.1 – Proposed reliability analysis flow for hardware and software co-designs                                                                                                             |   |

| Figure 8.1 – Block diagrams of the architectures developed with the hardware (a) and software (b)                                                                                                |   |

| fault injectors embedded.                                                                                                                                                                        | 3 |

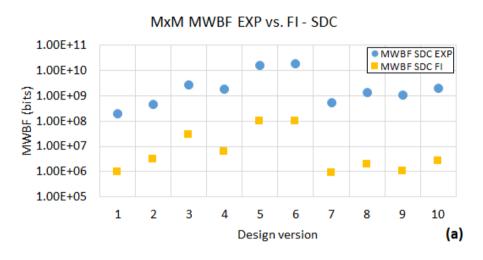

| Figure 8.2 – Comparison between the total SDC, SEFI, and TOTAL (SDC + SEFI) AVF values                                                                                                           |   |

| obtained from both hardware and software fault injection campaigns with the respective dynamic cross                                                                                             | 3 |

| sections obtained from radiation experiments for the MxM benchmark                                                                                                                               |   |

| Figure 8.3 – Comparison between the total SDC, SEFI, and TOTAL (SDC + SEFI) AVF values                                                                                                           |   |

| obtained from both hardware and software fault injection campaigns with the respective dynamic cross                                                                                             | 3 |

| sections obtained from radiation experiments for the AES benchmark                                                                                                                               | 2 |

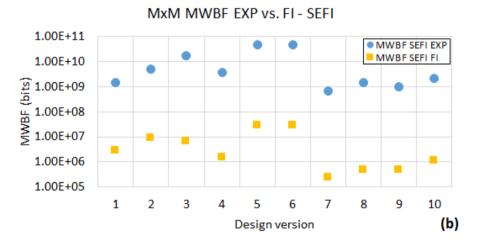

| Figure 8.4 – Comparison between the total SDC, SEFI, and TOTAL (SDC + SEFI) MWBF values                                                                                                          |   |

| obtained from both hardware and software fault injection campaigns with the respective MWBF                                                                                                      |   |

| values obtained from radiation experiments for the MxM benchmark                                                                                                                                 | ļ |

| Figure 8.5 – Comparison between the total SDC, SEFI, and TOTAL (SDC + SEFI) MWBF values                                                                                                          |   |

| obtained from both hardware and software fault injection campaigns with the respective MWBF                                                                                                      |   |

| values obtained from radiation experiments for the AES benchmark                                                                                                                                 | 5 |

| Figure 8.6 – Comparison between the total SDC, SEFI, and TOTAL (SDC + SEFI) Performance rate                                                                                                     |   |

| values obtained from both hardware and software fault injection campaigns with the respective                                                                                                    |   |

| MWBF values obtained from radiation experiments for the MxM benchmark                                                                                                                            | 5 |

| Figure 8.7 – Comparison between the total SDC, SEFI, and TOTAL (SDC + SEFI) Performance rate                                                                                                     |   |

| values obtained from both hardware and software fault injection campaigns with the respective                                                                                                    |   |

| MWBF values obtained from radiation experiments for the AES benchmark                                                                                                                            | 1 |

|                                                                                                                                                                                                  |   |

# LIST OF TABLES

| Table 2.1 – Commercially-available APSoCs characteristics                                          | 26     |

|----------------------------------------------------------------------------------------------------|--------|

| Table 5.1 – Characteristics if the heavy ion beams used at LAFN-USP                                | 100    |

| Table 5.2 – Characteristics of the ROSCOSMOS heavy ion facility                                    |        |

| Table 5.3 – Characteristics if the heavy ion beams used at ROSCOSMOS                               | 102    |

| Table 5.4 – Characteristics of the Russian proton facility.                                        | 103    |

| Table 5.5 – Heavy ion and proton test schemes performed in the embedded memories of the PS p       | art of |

| Zynq-7000                                                                                          |        |

| Table 5.6 – Application information running on Zynq-7000's ARM Cortex-A9 Core 0 with differ        | rent   |

| cache schemes (D = Disabled, E = Enabled).                                                         | 106    |

| Table 5.7 – Obtained SDC and SEFI cross sections from the heavy ion irradiations                   | 107    |

| Table 5.8 – Obtained MTBF, MEBF, and MWBF from the heavy ion irradiations                          | 108    |

| Table 6.1 – Heavy ion and proton test schemes performed in the configuration memory of the PL      | part   |

| of Zynq-7000                                                                                       |        |

| Table 6.2 – Optimization strategies applied in each HLS-based design for each benchmark progra     | ım.    |

|                                                                                                    |        |

| Table 6.3 – Resource usage and performance results of each case-study design                       | 120    |

| Table 7.1 – Resource usage and performance of each case-study architecture implemented             |        |

| Table 7.2 – Experimental results from the neutron radiation tests for the four case-studied system | in     |

| Zynq-7000                                                                                          |        |

| Table 7.3 - Case-study hardware and software co-designs and their respective configurations, res   | ource  |

| usage, and performance results.                                                                    | 144    |

| Table 8.1 – Number of critical bits and AVF of the hardware part of each hardware and software     | co-    |

| design obtained from the hardware fault injection campaigns.                                       | 159    |

| Table 8.2 – AVF of the software part of each hardware and software co-design obtained from the     |        |

| software fault injection campaigns                                                                 | 160    |

#### LIST OF ABBREVIATIONS AND ACRONYMS

ABFT Algorithm-Based Fault Tolerance

ACP Accelerator Coherency Port

ADAS Advanced Driver Assistance Systems

ADPCM Adaptive Differential Pulse-Code Modulation

AES Advanced Encryption Standard

ALICE A Large Ion Collider Experiment

AMBA Advanced Microcontroller Bus Architecture

AMP Asymmetric Multi-Processing

APSoC All Programmable System-on-Chip

APU Application Processing Unit

ARM ARM Cortex-A9

ASIC Application Specific Integrated Circuit

ATLAS A Toroidal LHC Apparatus

AXI Advanced Extensible Interface

AXI-S Advanced Extensible Interface Stream

AVF Architectural Vulnerability Factor

BCE Base-Core Equivalent

BRAM Block Random Access Memory

CERN European Organization for Nuclear Research

CHARM CERN High Energy Accelerator Mixed-Field

CLB Configurable Logic Block

CMOS Complementary Metal Oxide Semiconductor

CMS Compact Muon Solenoid

COTS Commercial Off-The-Shelf

CPU Central Processing Unit

CRAM Configuration Memory

CRC Cyclic Redundancy Check

D Disabled

DD Displacement Damage

DDR Double Data Rate

DFT Discrete Fourier Transform

DMA Direct Memory Access

DRAM Dynamic Random Access Memory

DSP Digital Signal Processing

DUT Design Under TestDUT Device Under Test

E Enabled

ECC Error Correcting Code

EMIO Extended Multiplexed Input/Output

ESA European Space Agency

EXP Radiation Experiment

FF Flip-Flop

FFT Fast Fourier Transform

FI Fault Injector

FIC Fabric Interface Controller

FIFO First In, First Out

FIT Failure in Time

FPGA Field Programmable Gate Array

FPU Floating Point Unit

FSM Finite State Machine

GEO Geostationary Orbit

GIC General Interrupt Controller

GP General Purpose

GPGPU General Purpose Graphics Processing Unit

GPIO General Purpose I/O

GPR General-Purpose Register

GPU Graphics Processing Unit

HDL Hardware Description Language

HEP High-Energy Physics

HLS High-Level Synthesis

HP High Performance

I/O Input/Output

ICAP Internal Configuration Access Port

IOB Input/Output Block

ISA Instruction Set Architecture

ITRS International Technology Roadmap for Semiconductors

JPEG Joint Photographics Experts Group

JTAG Joint Test Action Group

L1 Level 1

L1D Level 1 Data

L1I Level 1 Instruction

L2 Level 2

LAFN Laboratório Aberto de Física Nuclear

LANL Los Alamos National Laboratory

LANSCE Los Alamos National Science Center

LEO Low Earth Orbit

LET Linear Energy Transfer

LHC Large Hadron Collider

LHCb LHC-Beauty

LLVM Low Level Virtual Machine

LUT Look-Up Table

MB Microblaze

MBU Multiple Bit Upset

MCU Multiple Cell Upset

MEBF Mean Execution Between Failures

MEPhI Moscow Engineering Physics Institute

MIO Multiplexed Input/Output

MIPS Microprocessor without Interlocked Pipeline Stages

MMU Memory Management Unit

MSR Millimeter Square Radian

MSS Microcontroller Subsystem

MTBF Mean Time Between Failures

MxM Matrix Multiplication

MWBF Mean Workload Between Failures

NASA National Aeronautics and Space Administration

NSREC Nuclear and Space Radiation Effects Conference

OCM On-Chip Memory

OS Operating System

PC Program Counter

PCR Primary Cosmic Radiation

PL Programmable Logic

PLL Phase-Locked Loop

PoR Power-on Reset

PS Processing System

PSI Paul Scherrer Institut

RAL Rutherford Appleton Laboratory

RAM Random Access Memory

RISC Reduced Instruction Set Computer

ROM Read-Only Memory

ROSCOSMOS Russian Federal Space Agency

RTL Register Transfer Level

RTOS Real-Time Operating System

SAA South Atlantic Anomaly

SCU Snoop Control Unit

SDC Silent Data Corruption

SECDED Single-Error Correct/Double-Error Detect

SEE Single Event Effect

SEFI Single Event Functional Interrupt

SEL Single Event Latchup

SEM Soft Error Mitigation

SER Soft Error Rate

SET Single Event Transient

SEU Single Event Upset

SIHFT Software Implemented Hardware Fault Tolerance

SIMD Single Instruction Multiple Data

SMP Symmetric Multi-Processing

SoC System-on-Chip

SRAM Static Random Access Memory

TID Total Ionizing Dose

TMR Triple Modular Redundancy

TSMC Taiwan Semiconductor Manufacturing Company

UART Universal Asynchronous Receiver/Transmitter

USA United States of America

USP Universidade de São Paulo

WR Worst Result

## **CONTENTS**

| 1 INTRODUCTION                                              | 16       |

|-------------------------------------------------------------|----------|

| 1.1 Objectives and contributions                            | 18       |

| 1.2 Thesis organization                                     | 20       |

| 2 HETEROGENEOUS PROGRAMMABLE HARDWARE                       | 22       |

| 2.1 All Programmable System-on-Chip devices                 | 25       |

| 2.1.1 Xilinx Zynq-7000 APSoC                                |          |

| 2.1.1.1 The Processing System (PS)                          |          |

| 2.1.1.2 The Programmable Logic (PL)                         |          |

| 2.1.1.3 The interfaces between PS and PL                    |          |

| 2.2 Hardware/Software co-design                             | 42       |

| 2.2.1 High-Level Synthesis                                  | 44       |

| 2.2.2 Xilinx Vivado High-Level Synthesis                    |          |

| 2.2.3 Related works about HLS                               | 49       |

| 2.3 Implementation metrics                                  | 51       |

| 2.4 Related works about APSoCs                              | 52       |

| 2.5 Summary                                                 | 54       |

| 3 RADIATION EFFECTS ON APSOCS                               | 56       |

| 3.1 Fault, error, and failure                               |          |

|                                                             |          |

| 3.2 Radiation environments                                  |          |

| 3.2.1 Space environment                                     |          |

| 3.2.2 Terrestrial environment                               |          |

| 3.2.3 Particle accelerators environment                     | 61       |

| 3.3 Radiation effects on integrated circuits                | 63       |

| 3.4 Radiation effects on APSoCs                             | 68       |

| 3.5 Summary                                                 | 73       |

| 4 METHODS AND METRICS FOR EVALUATING APSOCS UNDER RADIATION | 74       |

| 4.1 Accelerated radiation tests                             | 74       |

| 4.2 Fault injection by emulation                            | 77       |

| 4.2.1 Hardware fault injection platform used.               | 77<br>78 |

| 4.2.1 Hardware fault injection platform used                |          |

| 4.3 Test methods and metrics                                | 82       |

| 4.3.1 Static test method and metrics                        |          |

| 4.3.2 Dynamic test method and metrics                       |          |

| = j                                                         |          |

| 4.4 Deleted works shout ADSoCs under rediction              | 00       |

| 4.5 Summary                                                                             | 90          |

|-----------------------------------------------------------------------------------------|-------------|

| 5 ANALYSING SINGLE EVENT EFFECTS ON THE PS PART OF ZYNQ-7000                            | 9           |

| 5.1 Static tests                                                                        | 9′          |

| 5.1.1 Tests procedures                                                                  |             |

| 5.1.2 Tests setups                                                                      |             |

| 5.1.3 Tests results.                                                                    |             |

| 5.2 Dynamic tests                                                                       | 104         |

| 5.2.1 Tests procedures                                                                  |             |

| 5.2.2 Tests setup                                                                       | 106         |

| 5.2.3 Tests results                                                                     | 106         |

| 6 ANALYSING SINGLE EVENT EFFECTS ON THE PL PART OF ZYNQ-7000                            | 110         |

| 6.1 Static tests                                                                        | 11          |

| 6.1.1 Tests procedures                                                                  | 113         |

| 6.1.2 Tests setups                                                                      | 111         |

| 6.1.3 Tests results                                                                     | 112         |

| 6.2 Dynamic tests and proposed reliability analysis for hardware-only designs           | 113         |

| 6.2.1 Proposed reliability analysis for hardware-only designs                           |             |

| 6.2.1.1 Resources and performance                                                       |             |

| 6.2.1.2 Errors and critical bits                                                        |             |

| 6.2.1.3 Radiation measurements                                                          |             |

| 6.2.1.4 Mean Workload Between Failures                                                  |             |

| 6.2.1.5 Xilinx analysis tools                                                           |             |

| 6.2.1.6 Fault injection method and analysis                                             |             |

| 6.2.2 Case-study designs and resources and performance results                          |             |

| 6.2.3 Cross section and MWBF results                                                    |             |

| 6.3 Summary                                                                             | 133         |

| 7 EXPLORING BOTH PS AND PL PARTS OF ZYNQ-7000 UNDER SINGLE EVENT                        |             |

|                                                                                         | 135         |

| 7.1 Reliability of hard- and soft-cores heterogeneous processing in the Zynq-7000       | 135         |

| 7.2 Reliability of heterogeneous processing through hardware and software co-designs in |             |

| 7.2.1 Case-study designs and resources and performance evaluations                      |             |

| 7.2.2 Cross section, MWBF, and performance evaluation                                   |             |

| 7.3 Summary                                                                             | 153         |

| 8 PROPOSED RELIABILITY ANALYSIS FOR HARDWARE AND SOFTWARE CO-                           | DESIGNS 154 |

| 8.1 Analysis flow                                                                       | 154         |

| 8.2 Case-study designs                                                                  |             |

| 8.3 Obtained results                                                                    |             |

| 8.4 Summary                                                                             |             |

| 9 CONCLUDING REMARKS                                                                    |             |

|                                                                                         |             |

| 9.1 Main contributions                                                                  | 169         |

| 9.1.1 Extensive review about APSoCs, possible radiation effects on them, and the methods and met   |     |

|----------------------------------------------------------------------------------------------------|-----|

| for evaluating them under radiation                                                                | 169 |

| 9.1.2 Original static data about Xilinx Zynq-7000 under radiation                                  | 170 |

| 9.1.3 Original dynamic analysis and data about Xilinx Zynq-7000 under radiation                    | 170 |

| 9.1.4 Reliability analysis flow for hardware-only designs, software-only designs, and hardware and |     |

| software co-designs                                                                                |     |

| č                                                                                                  |     |

| 9.2 Future works                                                                                   | 171 |

| 9.2.1 Completing the static measurements of Zynq-7000                                              | 171 |

| 9.2.2 Improving the reliability analysis flow                                                      | 172 |

| 9.2.3 Analyzing the use of fault-tolerant techniques in APSoCs                                     | 172 |

| 9.2.4 Evaluation of other APSoCs                                                                   |     |

| 9.3 Publications                                                                                   | 173 |

| 9.3.1 Book chapters                                                                                |     |

| 9.3.2 Journals                                                                                     |     |

| 9.3.3 Conferences and workshops                                                                    |     |

| DEFEDENCES                                                                                         | 180 |

#### 1 INTRODUCTION

The recent advances in silicon technology have allowed the integration of complex components and systems' architectures into a single silicon die. Today, state-of-the-art complex embedded systems include Field Programmable Gate Array (FPGA) together with hard-core parts, such as general-purpose embedded processors (hereafter shortened to only "processors"), dedicated processing blocks, interfaces to various peripherals, on-chip bus structures, and analog blocks. These new devices are commonly called All Programmable Systems-on-Chip (APSoCs) or, more generically, Heterogeneous Hardware.

APSoCs are designed to provide higher system performances and programmable flexibility at lower costs compared to standard FPGAs and processors. According to ITRS (2013), heterogeneous architectures such as APSoCs will dominate the next generation of computing systems. In general, APSoCs are composed of two main parts: the Programmable Logic (PL), which is basically an embedded FPGA, and the Processing System (PS), which is formed around of a hard-core processor. The PL is adopted to implement high-speed logic, arithmetic, data processing subsystems, etc. The PS supports software routines and operating systems. The overall functionality and workload of any system design can then be appropriately distributed between hardware and software. Some recent examples of commercially available APSoCs are Zynq-7000 (XILINX, 2015d) from Xilinx, SmartFusion (MICROSEMI, 2015a) and SmartFusion2 (MICROSEMI, 2015b) from Microsemi, and Cyclone V (ALTERA, 2015) from Altera.

The mentioned characteristics of being programmable, flexible, and extremely efficient, make APSoCs very suitable and attractive for safety-critical markets such as space, avionics, automotive, biomedical, and high-energy physics experiments. Moreover, Commercial Off-The-Shelf (COTS) products have been widely employed in these safety-critical areas in recent years. The Large Hadron Collider (LHC) at the European Organization for Nuclear Research (CERN) is a clear example. There are several areas of LHC in which commercial programmable devices not specifically designed to be radiation-tolerant are used (MUSA, 2008). As an example, ALICE (A Large Ion Collider Experiment), which is one of the LHC experiments, makes use of hundreds of SmartFusion2 devices in its Time Projection Chamber (TPC). The TPC is the main particle tracking detector in the central barrel of ALICE. The CHREC Space Processor (CSPv1) is an example of APSoC employment in space applications (RUDOLPH et al., 2014). CSPv1 is a small computer designed to operate

in low-cost space missions powered by a Zynq-7000. CSPv1 relies on the use of a combination of commercial and radiation-hardened components, in which commercial components perform critical computations but are supervised by the radiation-hardened components. Another example is the APEX-SoC proposed in (ITURBE et al., 2015), which is a generic platform based on a Zynq-7000 device and intended to control science instruments in future NASA missions. At terrestrial level, for example, APSoCs are very suitable to implement the Advanced Driver Assistance Systems (ADAS), aimed at increasing vehicles safety (XILINX, 2016b). In ADAS, the hardware and software combined programmability eases the performance and efficiency optimization distributing between hardware and software operations like sensing, environmental characterization, and feature implementation.

Unfortunately, although APSoCs offers a plethora of advantages, their high complexity and density increase the system's susceptibility to transient errors that are present in the environment, such as the ones caused by radiation. Radiation effects known as Single Event Effects (SEEs) are a well-known issue at device level in standard FPGA (DODD et al., 2010; WIRTHLIN, 2015) and processor-based (DODD et al., 2010) devices. SEEs result from the interaction of high-energy particles with circuit elements in integrated circuits. When a high-energy particle passes through the silicon substrate of a device, charged particles are created as the result of sub-atomic particle collisions. These particles are generated by an ionization trail along the path of the incoming particle. As an example, if a charged particle impacts at or near a transistor junction, the collected charge can temporally charge or discharge the stroke node inducing a transient pulse, known as Single Event Transient (SET). If the SET width of is wide enough, the pulse can propagate through the circuit and be latched by a memory cell. If the SET occurs inside a memory cell such as a latch or a flip-flop, the transient pulse can change the state of that memory cell. This effect is known as bit-flip or Single Event Upset (SEU). With the dimensions of the transistors shrinking to below 28 nm, the operating voltages and the element capacitance decreasing to very low levels, and the clock speed increasing, the concerns about SET and SEU in FPGAs, processors, and APSoCs, have increased in the last years.

One of the most challenging concerns about radiation effects on APSoCs is that radiation-induced errors may have different probability and criticality in the PL and PS parts at both device and design levels. APSoCs are programmed by configuring a large set of SRAM memory cells and, consequently, they are very susceptible to bit-flips. SEUs in the configuration memory bits of the PL part have a persistent effect and reconfiguration is needed to correct them. When an application is executed on the PS, it may mask eventual

SEUs according to the application Architectural Vulnerability Factor (AVF) (MUKHERJEE et al., 2003) and the sensitivity of the resources in use. Memories of the PS part such as L1 and L2 caches, embedded SRAM and Block RAM memories are also very sensitive to SEU, and each one has a distinct sensitivity, which may contribute differently to the overall system failure rate and performance overhead.

At design level, APSoCs enable many possibilities for implementing a system due to their heterogeneous architectures. However, each implementation will impose a different amount of resources usage and a different resource utilization efficiency, which may impact the vulnerability of the system. Therefore, the correlation between hardware and software resources sensitivity and the overall benefits brought to the system is essential to evaluate its efficiency.

#### 1.1 Objectives and contributions

This thesis aims at performing a deep investigation about the radiation effects on APSoCs and the correlation between hardware and software resources sensitivity in the overall system reliability and performance. Therefore, the main two topics addressed in this thesis are:

- 1. Which is the behavior of an APSoC device under radiation? Moreover, considering a hardware and software co-design implementing a high-performance system that runs on both PS and PL parts of an APSoC like Xilinx Zynq-7000, how much is it necessary to accelerate it to compensate the sensitivity increase and improve the Mean Workload Between Failures (MWBF)?

- 2. Is it possible to estimate the reliability trend of APSoC-based systems like Velazco, Foucard, and Peronnard (2010) did for FPGAs in the past?

As this thesis shows, state-of-the-art complex devices and technologies such as APSoCs and hardware and software co-designs have created many challenges for the radiation effects field. That is because radiation-induced failures in such devices and architectures may result in a complex chain of effects due to their heterogeneous nature. Additionally, the components testing methodologies have not changed over the years for taking into account such heterogeneity.

Another important critical point is the cross section metric. Today, the growing computational need, whether in a spacecraft or high-energy physics experiments, for example, has pushed the need to deploy high-performance computing in harsh environments, such as satellites and the LHC detectors. Thus, adopting only the cross section metric for estimating the reliability of a device, system, or design, is no longer enough. Besides the sensitivity of a resource, it is also essential to evaluate the benefit that this resource brings to the system. Therefore, to compare the reliability of heterogeneous and high-performance systems such as APSoCs, it is essential to take into account not only the cross section but also at least the execution time and workload of the system. Consequently, one of the main metrics adopted in this thesis is the Mean Workload Between Failures (MWBF), previously introduced in (RECH et al., 2014), but not in the APSoC context. The capability of a system to provide correct data depends on several factors, as sensitive area and the time required to complete computations. The MWBF metric identifies the workload that can be correctly computed by the system before experiencing a failure. Moreover, the MWBF considers all these aspects and is of particular interest in safety-critical applications as it provides the realistic impact of a given APSoC configuration on the system reliability.

The first objective of this thesis is to try to answer the following questions: Which is the behavior of an APSoC device under radiation? Moreover, considering a hardware and software co-design implementing a high-performance system that runs on both PS and PL parts of an APSoC like Zynq-7000, how much is it necessary to accelerate it to compensate the dynamic cross section increase and improve the MWBF? One of the main issues concerning radiation effects in an APSoC is that radiation-induced failures have different probability and criticality in its heterogeneous parts. In addition, at design level, the heterogeneous architecture of an APSoC enables a plethora of possibilities for implementing a project. Each implementation imposes a different amount of resources usage and a different resource utilization efficiency, which impact the vulnerability of the system. Therefore, the correlation between hardware and software resources sensitivity and the overall benefits brought to the system are essential to evaluate the system efficiency.

The second objective of this thesis is to develop a methodology to estimate the reliability trend of APSoC-based systems like Velazco, Foucard, and Peronnard (2010) did in the past for FPGA-based designs. Accelerated radiation tests are mandatory to obtain the sensitivity of the target device by determining its static cross section. However, static cross section significantly overestimates the sensitivity of the final application, as the next chapters show, and accelerated radiation tests are scarce, making prohibitive the test of any design

developed. In the case of FPGAs, in (VELAZCO, FOUCARD, PERONNARD, 2010), authors demonstrated that the dynamic cross section of a design can be predicted combining the static cross section with the results of fault injection campaigns, in which SEUs are emulated by a suitable approach, such as hardware/software fault injection. Base on this context, and together with the fact that APSoC devices have been increasingly used in safety-critical markets, a methodology aiming to estimate the APSoC-based design with the best trade-off between performance and reliability among the ones available becomes fundamental.

#### 1.2 Thesis organization

This thesis is organized as follows:

- Chapter 2 Heterogeneous programmable hardware: introduces heterogeneous programmable hardwares, Xilinx Zynq-7000 as an example of APSoC and the case-study device of this thesis, hardware/software co-design concepts, implementation metrics, and related works about Zynq-7000 and similar APSoCs;

- Chapter 3 Radiation effects on APSoCs: introduces the concepts of fault, error, and failure; the main radiation environments; and the radiation effects on integrated circuits and APSoCs;

- Chapter 4 Methods and metrics for evaluating APSoCs under radiation: presents the main methods and metrics for evaluating APSoCs under radiation and related works about APSoCs under radiation;

- Chapter 5 Analyzing single event effects on the PS part of the Zynq-7000: presents static and dynamic tests procedures, setups, and results for the Zynq-7000's PS part;

- Chapter 6 Analyzing single event effects on the PL part of the Zynq-7000: presents static and dynamic tests procedures, setups, and results for the Zynq-7000's PL part. This chapter also proposes a reliability analysis flow for estimating the reliability of hardware-only designs based on fault injections;

- Chapter 7 Exploring both PS and PL parts of Zynq-7000 under single event effects: presents an analysis of the impact of using both PS and PL parts of Xilinx Zynq-7000 in the overall failure rate of a system;

- Chapter 8 Proposed reliability analysis for hardware and software co-designs:

presents the proposed reliability analysis flow for estimating the reliability

trend of hardware and software co-designs, the case-study designs, and the

obtained results;

- Chapter 9 Concluding remarks: presents the concluding remarks of this thesis, such as its main contributions and future works.

#### 2 HETEROGENEOUS PROGRAMMABLE HARDWARE

Following Moore's law (MOORE, 1965), the processors' frequency doubled at each every 18 to 24 months until the middle of 2000's decade. However, due to the ever increasing core design complexity of the high performance processors and the power consumption caused by the high frequencies, researches started to look at other strategies to continue increasing systems performance. According to Shen and Pétrot (2011), three possible solutions were proposed until that year. More important, we already can see all of them being commercialized today.

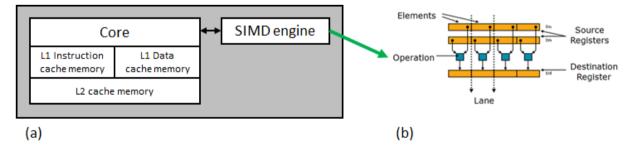

The first solution was to optimize the instruction set for certain application classes. The generalization of the Single Instruction Multiple Data (SIMD) extensions (Fig. 2.1), which first appeared in the general purpose high-performance processors in the early of 90's decade to all processors including the embedded ones (GOODACRE, SLOSS, 2005) after the 2000's decade is an evidence of this trend. The SIMD technique allows multiple data to be processed in one or a few CPU cycles by assuming that registers are considered as vectors of elements of the same data type. A today's example is the NEON engine (ARM, 2015b), which is the SIMD implementation present in ARMv7-A processors (Cortex-A9 family). The drawback of this solution is that these resources can accelerate only part of the application, which make them useless for other parts of the execution.

Figure 2.1 – Bock diagram of a processor with a SIMD engine embedded (a) and a simplified block diagram of a SIMD engine (b).

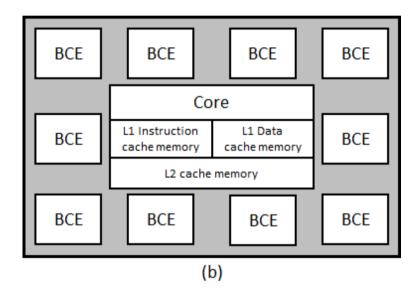

The second solution, straightforward from the point of view of the hardware designer, was to integrate several symmetric cores, based on the first solution, into the same silicon die, as Fig. 2.2(a) shows. Due to power dissipation issues, the integrated cores should feature a high performance per watt ratio and an overall current consumption acceptable for the

application. The drawback of this solution is that all cores are symmetric in both performance and function, which limits the speed-up that can be obtained by the parallel execution of the cores, since all applications intrinsically have sequential phases.

In the general and high-performance computing fields, there is a clear trend towards to chips with multiprocessor architectures. In 1967, G. M. Amdahl stated that the performance improvement (*S*) to be gained from using some faster mode of execution is limited by the fraction of the time (*f*) the faster mode can be used (Eq. 2.1) (AMDAHL, 1967).

(Equation 2.1)

$$Speedup_{enhanced} = \frac{1}{(1-f) + \frac{f}{S}}$$

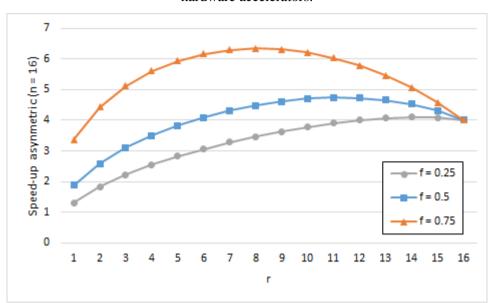

Based on Amdahl's law, during the last decade, the semiconductor industry has defined high-performance asymmetric architectures which accelerate the sequential execution by using fast cores and the parallel execution by a massive usage of small cores (Base-Core Equivalent – BCE) having lower performance but better high performance per watt ratio than the fast ones. This was the third solution and it is shown in Fig. 2.2(b). This kind of architecture can improve the overall system performance by accelerating some critical parts of a parallel application while still providing very good flexibility. Based on this concept, Hill and Marty (2008) extended the Amdahl's law for symmetric (Eq. 2.2) and asymmetric (Eq. 2.3) multicore devices by introducing two additional parameters, n and r, to represent the total number of resources available and those dedicated to sequential processing (BCE), respectively. Hill and Marty used the Pollack's Law (POLLACK, 1999) as input to their model, which observes that the sequential processing performance from a microarchitecture alone grows roughly with the square root of transistors used ( $perf_{seq}(r) = \sqrt{r}$ ).

(Equation 2.2)

$$Speedup_{symmetric}(f, n, r) = \frac{1}{\frac{1-f}{perf_{seq}(r)} + \frac{f}{\frac{n}{r} x \ perf_{seq}(r)}}$$

(Equation 2.3)

$$Speedup_{asymmetric}(f, n, r) = \frac{1}{\frac{1-f}{perf_{seq(r)} + \frac{f}{perf_{seq(r) + n - r}}}}$$

However, today the semiconductor industry already went a step further in the asymmetric architectures solution by using heterogeneous architectures to achieve greater energy efficiency. Thus, the present metrics are no longer totally applied to such devices. Heterogeneous architectures (Fig. 2.2(c)) combine traditional processors with other hardware

Core Core L1 Instruction L1 Instruction L1 Data cache memory cache memory cache memory cache memory L2 cache memory L2 cache memory Core Core L1 Instruction L1 Data L1 Instruction L1 Data cache memory cache memory cache memory cache memory L2 cache memory L2 cache memory

Figure 2.2 - Processor models: (a) Symmetric, (b) Asymmetric, and (c) Heterogeneous.

(a)

(c)

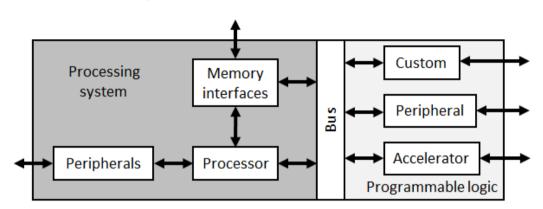

categories, such as custom logic, General Purpose Graphics Processing Units (GPGPUs), or FPGAs. Custom logic can provide the most energy-efficient form of computation (100-1000x improvement in either efficiency or performance) through ASICs customized to a specific task (DALLY et al., 2008). However, it is costly to develop and cannot be easily re-used for new applications. GPGPUs have also been shown to significantly outperform conventional microprocessors in target applications (LEE et al., 2010). GPGPUs derive their capabilities through SIMD vectorization and through multithreading to hide long memory latencies. GPGPUs are very suitable for homogeneous data parallel tasks. Finally, the third option of heterogeneous architecture is the FPGAs. Unlike custom logic and GPGPUs, FPGAs enable flexibility through programmable Look-Up Tables (LUTs) cells that can be used to implement arbitrary logic circuits. In exchange for this flexibility, a typical 10-100x gap in area and power exists between custom logic and FPGAs (KUON, ROSE, 2007). Heterogeneous FPGAs, which are the focus of this thesis, are the most suitable devices to perform pipeline irregular data flows as well as data parallel tasks.

#### 2.1 All Programmable System-on-Chip devices

Although traditional processors have been coupled with FPGAs before, it has never been quite the same proportion as now. Today, heterogeneous FPGAs, called of APSoC devices hereafter, have embedded hard-core processors capable of running full operating systems.

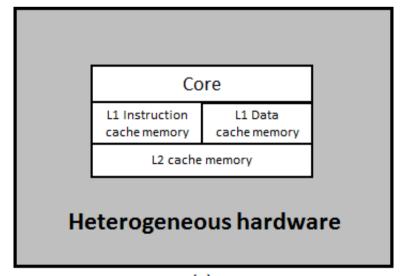

In general, APSoCs are composed of two main parts (Fig. 2.3): the Programmable Logic (PL), which is FPGA-based, and the Processing System (PS), which is formed around of a hard-core processor. The architecture is usually completed by embedding several peripherals and industry bus interfaces, which provide high bandwidth and low latency between PS and PL. The PL section is ideal for implementing high-speed logic, arithmetic, and data processing subsystems, while the PS supports software routines and/or operating systems. Thus, the overall functionality of any designed system can be appropriately partitioned between hardware and software. Finally, it is worth mentioning that in APSoCs, the processor embedded into the PS part can be regarded as the central element of the hardware system. The software system running on the processor comprises applications that run or in bare-metal mode with a lower level of software functionality for interfacing with the hardware system, or on the top of an Operating System (OS).

There are several APSoCs currently available on the market. Some recent examples are Zynq-7000 (XILINX, 2015d) from Xilinx, SmartFusion (MICROSEMI, 2015a) and SmartFusion2 (MICROSEMI, 2015b) from Microsemi, and Cyclone V (ALTERA, 2015) from Altera.

Figure 2.3 – Generic architecture of an APSoC.

Zynq-7000 and the Cyclone V devices use a dual-core ARM Cortex-A9 application processor. SmartFusion2 devices are based around the ARM Cortex-M3 embedded processor, primarily targeting microcontroller applications. The main characteristics of the three devices are summarized in Table 2.1. Further information about the architecture of the devices can be found in their respective datasheets, which were referred in the previous paragraph. This thesis uses the Xilinx Zynq-7000 APSoC as case-study platform. Nevertheless, the methodologies and the achieved results are capable to be extendable to other APSoCs.

Table 2.1 – Commercially-available APSoCs characteristics.

| Table 2.1 – Commercially-available At Soes characteristics. |                                   |                                   |                                    |

|-------------------------------------------------------------|-----------------------------------|-----------------------------------|------------------------------------|

| Functional unit                                             | Xilinx Zynq-7000                  | Altera Cyclone V                  | Microsemi<br>SmartFusion2          |

| Processor                                                   | ARM Cortex-A9                     | ARM Cortex-A9                     | ARM Cortex-M3                      |

| Processor class                                             | Application processor             | Application processor             | Microcontroller                    |

| Single or dual core                                         | Dual                              | Dual                              | Single                             |

| Processor max. freq.                                        | 1.0 GHz                           | 1.0 GHz                           | 166 MHz                            |

| L1 cache                                                    | Data: 32 KB<br>Instruction: 32 KB | Data: 32 KB<br>Instruction: 32 KB | No data cache<br>Instruction: 8 KB |

| L2 cache                                                    | Unified: 512 KB                   | Unified: 512 KB                   | Not available                      |

| Memory Management<br>Unit (MMU)                             | Yes                               | Yes                               | Yes                                |

| Floating-Point Unit (FPU)                                   | Yes                               | Yes                               | Not available                      |

| A1                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                 | <u> </u>                                                                                                                                                                                                |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Accelerator Coherency Port (ACP)    | Yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Yes                                                                                                                                                                                                                                                                                                                                                                             | Not available                                                                                                                                                                                           |

| Interrupt controller                | Generic                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Generic                                                                                                                                                                                                                                                                                                                                                                         | Nested, Vectored                                                                                                                                                                                        |

| On-Chip Memory<br>(SRAM)            | 256 KB                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 64 KB                                                                                                                                                                                                                                                                                                                                                                           | 64 KB                                                                                                                                                                                                   |

| Direct Memory                       | 8-channel                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8-channel                                                                                                                                                                                                                                                                                                                                                                       | 1-channel HPDMA                                                                                                                                                                                         |

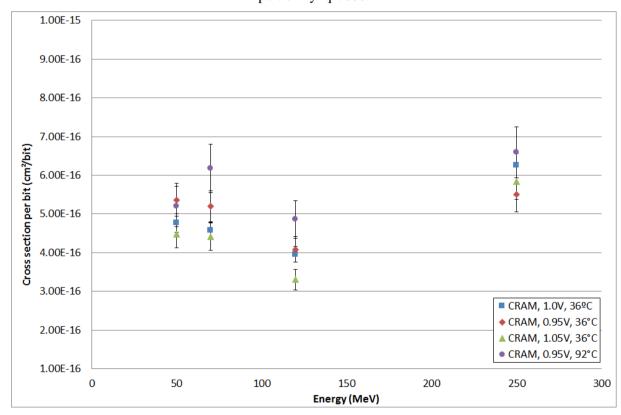

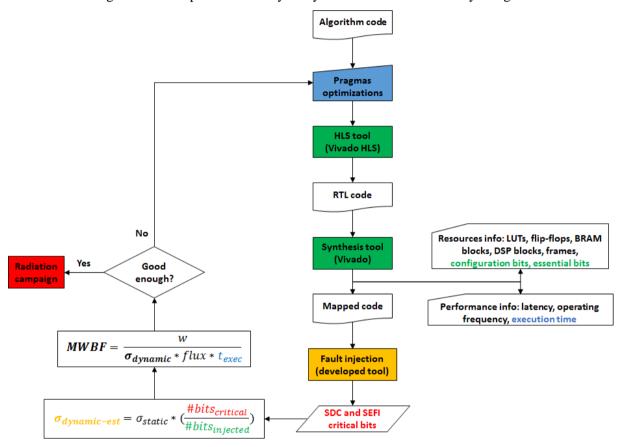

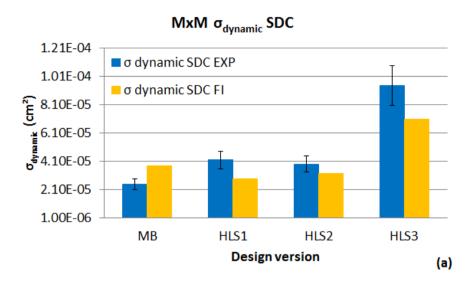

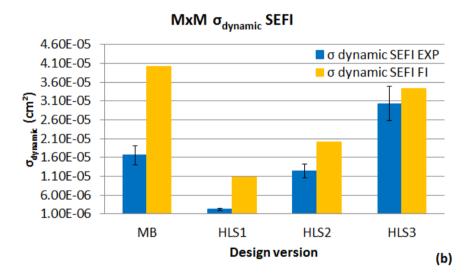

| Access (DMA)                        | 4 requests                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 32 requests                                                                                                                                                                                                                                                                                                                                                                     | 4 requests                                                                                                                                                                                              |