# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA CURSO DE ENGENHARIA DE COMPUTAÇÃO

# RENNÊ SILVA DA SILVA

# Using Software Optimization Techniques and Exploiting Hardware Capabilities to Speed-Up BLSTM Neural Network on CPUs

Work presented in partial fulfillment of the requirements for the degree of Bachelor in Computer Engeneering

Advisor: Prof. Dr. Bruno Castro da Silva Coadvisor: M. Sc. Vladimir Rybalkin

# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Rui Vicente Oppermann Vice-Reitora: Prof<sup>a</sup>. Jane Fraga Tutikian Pró-Reitor de Graduação: Prof. Vladimir Pinheiro do Nascimento

Diretora do Instituto de Informática: Prof<sup>a</sup>. Carla Maria Dal Sasso Freitas

Coordenador do Curso de Engenharia de Computação: Prof. Renato Ventura Bayan Hen-

Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

"There is no path to happiness.

Happiness is the path."

— ABRAHAM JOHANNES MUSTE

#### ACKNOWLEDGMENTS

First of all, I need to thank my family, especially my mother Ema Rosa, my father Carlos Renato and my sister Renata. They are the strongest pillar of my structure and without them, I would probably never get here. They support me on all my way, giving me everything I've needed and always encouraging me to move forward. The most important thing I've learned from them is education; not a scholar or academic education, but the most important one: moral education. My family always taught me valuable lessons and thanks to them all the care, affection and love they give to me will be passed on to the people who I will meet on my way.

Second, I would like to express my enormous gratitude to M.Sc. Vladimir Rybalkin for guidance, patience and lots of useful insights provided during this work, besides for sharing his vast knowledge. I would like to thank Prof. Dr.-Ing. Norbert Wehn and Taisy Weber by the opportunity of the exchange program in Kaiserslautern, Germany. They allowed me to live one of the most important experiences of all my life. My gratitude to all the staff of the Microelectronic Systems Design Research Group from TU Kaiserslautern for receiving me in an environment where I could feel at home.

I would like to thank all professors of Universidade Federal do Rio Grande do Sul (UFRGS) and structure provided by this university. Besides the UFRGS professors, my gratitude to all my teachers/professors during my way, especially the good ones. They are at some point, part of my personality.

Another important acknowledgment is to all my friends, especially for those who have lived with me for longer periods of time: my colleagues at ADP and colleagues of the exchange program in Germany.

During this year, Prof. Dr. Bruno Castro da Silva helped me a lot as advisor. He really took part in this work. His knowledge, guidance, interest, participation, concern, meaningful insights and support made this graduation work possible and less stressful. My enormous gratitude to him!

Finally, thanks to my girlfriend Bruna Pinzon that with all her dedication, affection and love helped me and encouraged me to move forward.

#### **ABSTRACT**

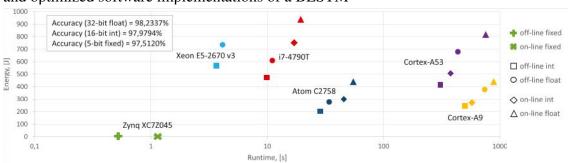

Many current applications benefit from using neural networks to solve machine learning problems, since they often outperform other conventional approaches both in terms of accuracy and robustness. However, training and deploying high accuracy networks sometimes requires using complex neural networks with many weights. This has a direct impact on the time needed to train and run such networks since these procedures involve intensive computations and many memory accesses. Such high processing costs may be a challenging burden even to modern computational platforms such as multi-cores and vector units. Although GPUs can be used in order to improve runtime, they are not always the best option—small networks, for instance, may not benefit from GPUs, and GPUs may not always be available in simpler devices. This graduation work introduces and demonstrates the efficacy of many software optimization techniques that allow for neural networks to fully benefit from the capabilities of CPUs without compromising their accuracy. We evaluate the proposed optimization techniques using a Bidirectional Long Short-Term Memory (BLSTM) neural network to solve an Optical Character Recognition (OCR) problem. Different architectures (Intel and ARM CPUs), memory access patterns, parallelization schemes, linear algebra high-performance libraries, numerical representations, lookup tables and vectorization (SSE, AVX and NEON) were taken into account to specify optimization strategies that allow for improvements in the runtime of the network. Finally, we present performance comparisons between different implementations of a BLSTM, both in terms of runtime and energy consumption, and show that the implemented optimizations improve runtime by a factor of 9 (when compared to an optimized floating-point baseline) while undergoing negligible loss of accuracy.

**Keywords:** Recurrent Neural Networks. BLSTM. Software Optimization Techniques. Improving Runtime. Energy Consumption Reduction. Parallel and High-Performance Computing. SSE, AVX, NEON Intrinsics.

# Usando Técnicas de Otimização de Software e Explorando Capacidades de Hardware para Acelerar Redes Neurais BLSTM em CPUs

#### **RESUMO**

Muitas aplicações atuais se beneficiam ao usar redes neurais para solucionar problemas de aprendizado de máquina, visto que elas frequentemente superam outras abordagens convencionais tanto em termos de acurácia e robustez dos resultados. Contudo, algumas vezes, treinar e executar redes com alta acurácia requer o uso de redes neurais complexas com muitos pesos. Isto tem um impacto direto no tempo necessário para treinar e executar uma rede neural, visto que estes procedimentos envolvem computação intensa e muitos acessos à memória. Tais altos custos de processamento podem ser uma carga computacional desafiadora até mesmo para plataformas computacionais modernas tais como as que possuem vários núcleos e unidades vetoriais. Apesar de GPUs poderem ser usadas a fim de melhorar tempo de execução, elas nem sempre são a melhor opção—redes pequenas, por exemplo, podem não se beneficiar do uso de GPUs além de nem sempre elas estarem disponíveis em dispositivos mais simples. Este trabalho de graduação introduz e demonstra a eficácia de várias técnicas de otimização de software que permitem que redes neurais se beneficiem totalmente das capacidades de CPUs sem comprometer sua acurácia. Nós avaliamos as técnicas de otimização propostas ao usar uma rede neural BLSTM para resolver um problema de Reconhecimento Ótico de Caracteres. Arquiteturas diferentes (CPUs Intel e ARM), padrões de acesso a memória, esquemas de paralelização, bibliotecas de alta performance para álgebra linear, representações numéricas, lookup tables e vetorização (SSE, AVX e NEON) foram levadas em consideração neste trabalho para especificar estratégias que permitem melhorias no tempo de execução da rede. Finalmente, nós apresentamos uma comparação entre diferentes implementações de uma BLSTM tanto em termos de tempo de execução quanto de consumo de energia e mostramos que as otimizações implementadas melhoram o tempo de execução por um fator de 9 com perda insignificante de acurácia.

**Palavras-chave:** Redes Neurais Recorrentes. BLSTM. Técnicas de Otimização de Software. Otimização de Tempo de Execução. Redução de Consumo de Energia. Computação Paralela e de Alta Performance. Funções Intrínsecas SSE, AVX e NEON..

# LIST OF ABBREVIATIONS AND ACRONYMS

CPU Central Processing Unit

GPU Graphics Processing Unit

ARM Advanced RISC Machine

LSTM Long Short-Term Memory

**BLSTM Bidirectional Long Short-Term Memory**

NN Neural Network

ANN Artificial Neural Network

RNN Recurrent Neural Network

BRNN Bidirectional Recurrent Neural Network

CNN Convolutional Neural Network

OCR Optical Character Recognition

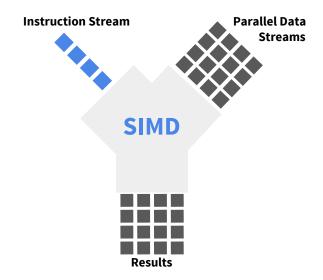

SIMD Single Instruction Multiple Data

SSE Streaming SIMD Extensions

AVX Advanced Vector Extensions

NEON Advanced SIMD Extension for ARM CPUs

BLAS Basic Linear Algebra Subprogram

ALU Arithmetic Logic Unit

CTC Connectionist Temporal Classification

TDP Thermal Design Power

# LIST OF FIGURES

| Figure 2.1  | Artificial Neural Network                                                 | 18         |

|-------------|---------------------------------------------------------------------------|------------|

| Figure 2.2  | A recurrent neural network and its unrolling over time                    | 19         |

| Figure 2.3  | LSTM Cell Structure                                                       | 22         |

| Figure 2.4  | Single instruction, multiple data                                         | 26         |

| Figure 2.5  | Size of the new registers added by SSE and AVX instruction set extension  | ıs27       |

|             | Runtime and energy consumption comparison between a dedicated-hardwa      |            |

| and o       | optimized software implementations of a BLSTM                             | 31         |

| Figure 4.1  | BLSTM implementation                                                      | 36         |

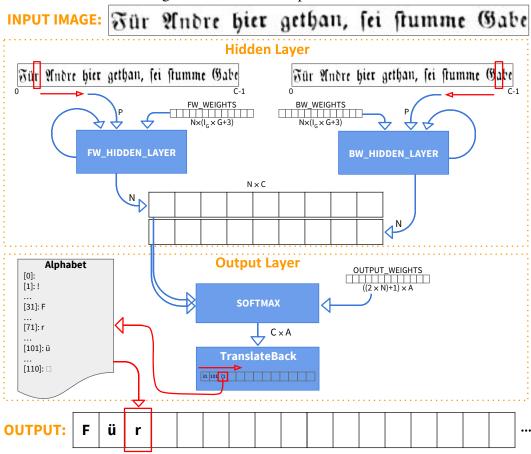

| Figure 4.2  | Example of the BLSTM execution and output                                 | 37         |

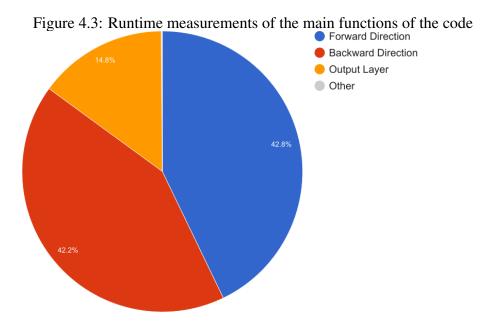

| Figure 4.3  | Runtime measurements of the main functions of the code                    | 38         |

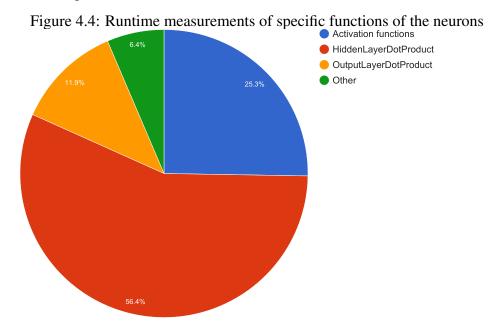

| Figure 4.4  | Runtime measurements of specific functions of the neurons                 | 39         |

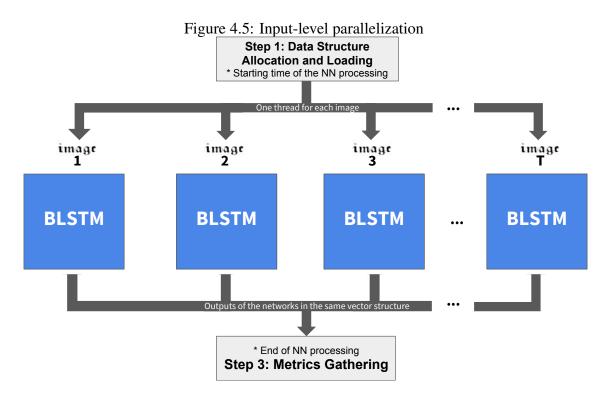

| Figure 4.5  | Input-level parallelization                                               | 41         |

| Figure 4.6  | Threads creation example with OpenMP                                      | 41         |

|             | Neuron-level parallelization                                              |            |

|             | Allocation of the weights used by the LSTM cells dot products before      |            |

|             | ht aggregation                                                            | 44         |

|             | Weights aggregation in a single vector, instead of using four different   |            |

|             | hts for each hidden layer                                                 |            |

| Figure 4.10 | Coop unrolling example                                                    | 46         |

| _           | Eigen dot product example                                                 |            |

| _           | 2 Scaling the weights and images                                          |            |

|             | 3 Initializing lookup table operations                                    |            |

| -           | Example of 16-byte alignment of a memory block                            |            |

| _           | 5 Vector addition example with SSE intrinsic function                     |            |

|             | 5 Dot product with SSE2 intrinsic functions                               |            |

| _           | 7 Integer implementation of dot product function with SSE intrinsics      |            |

| _           | Integer implementation of dot product function with AVX intrinsics        |            |

| _           | Integer implementation of dot product function with NEON intrinsics       |            |

| E' (1       | D C C C C C C C C C C C C C C C C C C C                                   |            |

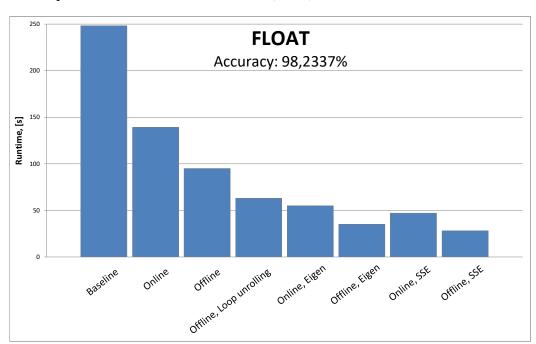

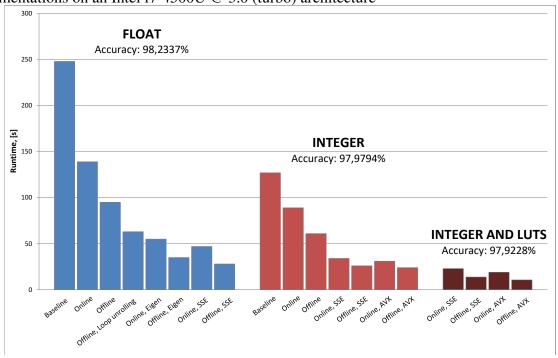

| _           | Runtime of a floating-point BLSTM implementation under different op-      | 64         |

|             | ation techniques on the Intel i7-4500U @ 3.0 (turbo) architecture         | 04         |

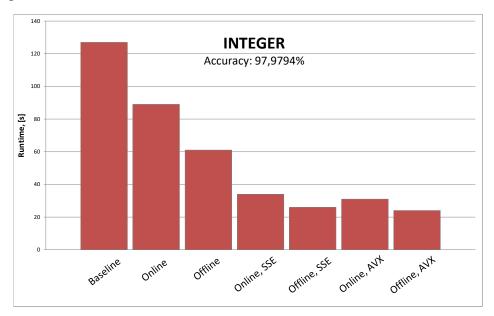

|             | Runtime of an integer BLSTM implementation under different opti-          | 66         |

|             | tion techniques on the Intel i7-4500U @ 3.0 (turbo) architecture          | 00         |

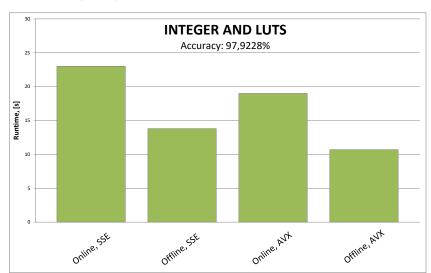

| _           | Runtime of an integer BLSTM implementation using lookup tables on         | 67         |

|             | ntel i7-4500U @ 3.0 (turbo) architecture                                  | 07         |

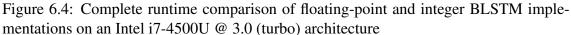

|             | Complete runtime comparison of floating-point and integer BLSTM im-       | 67         |

| -           | entations on an Intel i7-4500U @ 3.0 (turbo) architecture                 | 07         |

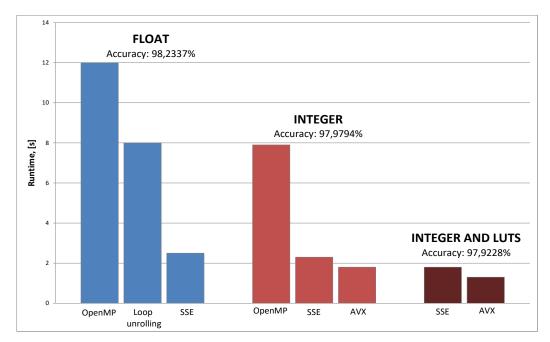

| _           | Runtime comparison of floating-point and integer-based BLSTM im-          |            |

| -           | entations under the main optimization techniques, using just offline par- | <b>6</b> 0 |

|             | zation on a Xeon E5-2670 v3 @ 3.1 GHz (turbo) architecture                | 68         |

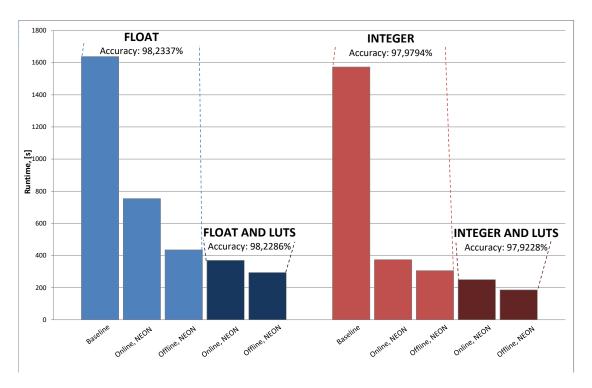

| -           | Runtime of floating-point and integer BLSTM implementations under         |            |

|             | nain configurations of software optimization techniques on an ARM Cortex- |            |

|             | @ 1.2 GHz architecture                                                    | 09         |

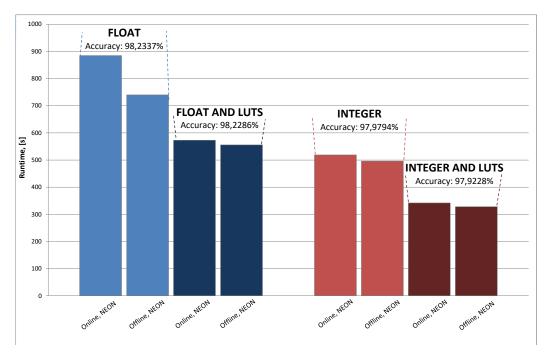

|             | Runtime of floating-point and integer BLSTM implementations under         |            |

|             | nain configurations of software optimization techniques on an ARM Cortex- |            |

| A9 (        | 9 800MHz                                                                  | /U         |

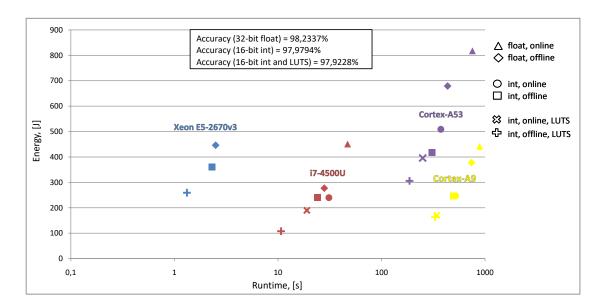

| Figure 6.8 Runtime vs energy consumption of the main optimized configurations     |    |

|-----------------------------------------------------------------------------------|----|

| of the BLSTM, on all architectures                                                | 71 |

|                                                                                   | 70 |

| Figure A.1 Header file to use lookup tables for the neuron activation functions   | /8 |

| Figure A.2 C++ source file implementing functions to use lookup tables instead of |    |

| regular neuron activation functions                                               | 79 |

# LIST OF TABLES

| Table 2.1 | The reference CPU architectures used in this work            | 5 |

|-----------|--------------------------------------------------------------|---|

| Table 4.1 | General information about the baseline BLSTM implementation3 | 5 |

# **CONTENTS**

| 1 INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 13                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 1.1 General Objective                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 16                                                                   |

| 1.2 Outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                      |

| 2 THEORETICAL BACKGROUND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                      |

| 2.1 Neural Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                      |

| 2.1.1 Recurrent Neural Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                      |

| 2.1.2 LSTM and BLSTM Neural Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                      |

| 2.2 Optical Character Recognition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                      |

| 2.3 String Comparison Algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                      |

| 2.3.1 Levenshtein Distance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                      |

| 2.4 CPU Architectures and Instruction Set Extensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                      |

| 2.4.1 Streaming SIMD Extensions (SSE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                      |

| 2.4.2 Advanced Vector Extensions (AVX)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                      |

| 2.4.3 NEON Advanced SIMD Architecture Extension                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                      |

| 3 RELATED WORK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                      |

| 3.1 Accelerating Neural Networks via Dedicated Hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                      |

| 3.2 Accelerating Neural Networks via Software-Only Optimizations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 31                                                                   |

| 3.3 Accelerating Neural Networks via Software Optimizations and Hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 22                                                                   |

| Capabilities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                      |

| 4 OPTIMIZATION TECHNIQUES FOR NEURAL NETWORKS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                      |

| 4.1 Baseline BLSTM Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                      |

| 4.1.1 Step 1: Data Structure Allocation and Loading                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                      |

| 4.1.2 Step 2: Computing Neural Network Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                      |

| 4.1.5 Step 5. Metrics Gathering/Performance Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3 /                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 20                                                                   |

| 4.2 Identifying Bottlenecks in the Baseline BLSTM Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                      |

| <ul><li>4.2 Identifying Bottlenecks in the Baseline BLSTM Implementation</li><li>4.3 Software Optimization Techniques</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 39                                                                   |

| <ul><li>4.2 Identifying Bottlenecks in the Baseline BLSTM Implementation.</li><li>4.3 Software Optimization Techniques</li><li>4.3.1 Parallelization Scenarios</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>39</b><br>40                                                      |

| <ul> <li>4.2 Identifying Bottlenecks in the Baseline BLSTM Implementation</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 40<br>40                                                             |

| <ul> <li>4.2 Identifying Bottlenecks in the Baseline BLSTM Implementation.</li> <li>4.3 Software Optimization Techniques.</li> <li>4.3.1 Parallelization Scenarios.</li> <li>4.3.1.1 Input-level Parallelization (Offline).</li> <li>4.3.1.2 Neuron-level Parallelization (Online).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                            | 40<br>40<br>42                                                       |

| 4.2 Identifying Bottlenecks in the Baseline BLSTM Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 40<br>40<br>42<br>42                                                 |

| 4.2 Identifying Bottlenecks in the Baseline BLSTM Implementation. 4.3 Software Optimization Techniques. 4.3.1 Parallelization Scenarios. 4.3.1.1 Input-level Parallelization (Offline). 4.3.1.2 Neuron-level Parallelization (Online). 4.3.2 Hidden Layers Aggregation. 4.3.3 Memory Allocation and Access.                                                                                                                                                                                                                                                                                                                                                               | 40<br>40<br>42<br>42<br>43                                           |

| 4.2 Identifying Bottlenecks in the Baseline BLSTM Implementation. 4.3 Software Optimization Techniques. 4.3.1 Parallelization Scenarios. 4.3.1.1 Input-level Parallelization (Offline). 4.3.1.2 Neuron-level Parallelization (Online). 4.3.2 Hidden Layers Aggregation. 4.3.3 Memory Allocation and Access. 4.3.4 Loop Unrolling.                                                                                                                                                                                                                                                                                                                                         | 40<br>42<br>42<br>43<br>45                                           |

| 4.2 Identifying Bottlenecks in the Baseline BLSTM Implementation. 4.3 Software Optimization Techniques. 4.3.1 Parallelization Scenarios. 4.3.1.1 Input-level Parallelization (Offline). 4.3.1.2 Neuron-level Parallelization (Online). 4.3.2 Hidden Layers Aggregation. 4.3.3 Memory Allocation and Access. 4.3.4 Loop Unrolling. 4.3.5 Use of High-Performance Libraries.                                                                                                                                                                                                                                                                                                | 39<br>40<br>42<br>42<br>43<br>45                                     |

| 4.2 Identifying Bottlenecks in the Baseline BLSTM Implementation. 4.3 Software Optimization Techniques. 4.3.1 Parallelization Scenarios. 4.3.1.1 Input-level Parallelization (Offline). 4.3.1.2 Neuron-level Parallelization (Online). 4.3.2 Hidden Layers Aggregation. 4.3.3 Memory Allocation and Access. 4.3.4 Loop Unrolling. 4.3.5 Use of High-Performance Libraries. 4.3.6 Precision Reduction.                                                                                                                                                                                                                                                                     | 39<br>40<br>42<br>42<br>43<br>45<br>45                               |

| 4.2 Identifying Bottlenecks in the Baseline BLSTM Implementation. 4.3 Software Optimization Techniques 4.3.1 Parallelization Scenarios 4.3.1.1 Input-level Parallelization (Offline) 4.3.1.2 Neuron-level Parallelization (Online) 4.3.2 Hidden Layers Aggregation 4.3.3 Memory Allocation and Access 4.3.4 Loop Unrolling. 4.3.5 Use of High-Performance Libraries 4.3.6 Precision Reduction 4.3.7 Lookup Tables for Activation Functions                                                                                                                                                                                                                                | 39<br>40<br>42<br>43<br>45<br>45<br>47<br>48                         |

| 4.2 Identifying Bottlenecks in the Baseline BLSTM Implementation 4.3 Software Optimization Techniques 4.3.1 Parallelization Scenarios 4.3.1.1 Input-level Parallelization (Offline) 4.3.2 Neuron-level Parallelization (Online) 4.3.3 Memory Allocation and Access 4.3.4 Loop Unrolling 4.3.5 Use of High-Performance Libraries 4.3.6 Precision Reduction 4.3.7 Lookup Tables for Activation Functions 4.4 Hardware Dependent Optimization Techniques                                                                                                                                                                                                                     | 39<br>40<br>42<br>43<br>45<br>46<br>47<br>48                         |

| 4.2 Identifying Bottlenecks in the Baseline BLSTM Implementation. 4.3 Software Optimization Techniques 4.3.1 Parallelization Scenarios 4.3.1.1 Input-level Parallelization (Offline) 4.3.1.2 Neuron-level Parallelization (Online) 4.3.2 Hidden Layers Aggregation 4.3.3 Memory Allocation and Access 4.3.4 Loop Unrolling. 4.3.5 Use of High-Performance Libraries 4.3.6 Precision Reduction 4.3.7 Lookup Tables for Activation Functions                                                                                                                                                                                                                                | 39<br>40<br>42<br>43<br>45<br>46<br>47<br>48<br>51                   |

| 4.2 Identifying Bottlenecks in the Baseline BLSTM Implementation. 4.3 Software Optimization Techniques. 4.3.1 Parallelization Scenarios. 4.3.1.1 Input-level Parallelization (Offline). 4.3.2 Neuron-level Parallelization (Online). 4.3.3 Hidden Layers Aggregation. 4.3.4 Loop Unrolling. 4.3.5 Use of High-Performance Libraries. 4.3.6 Precision Reduction. 4.3.7 Lookup Tables for Activation Functions. 4.4 Hardware Dependent Optimization Techniques. 4.4.1 SSE Intrinsic Functions. 4.4.2 AVX Intrinsic Functions.                                                                                                                                               | 39<br>40<br>42<br>43<br>45<br>46<br>47<br>48<br>51<br>52             |

| 4.2 Identifying Bottlenecks in the Baseline BLSTM Implementation. 4.3 Software Optimization Techniques 4.3.1 Parallelization Scenarios 4.3.1.1 Input-level Parallelization (Offline) 4.3.2 Neuron-level Parallelization (Online) 4.3.3 Memory Allocation and Access 4.3.4 Loop Unrolling. 4.3.5 Use of High-Performance Libraries 4.3.6 Precision Reduction 4.3.7 Lookup Tables for Activation Functions 4.4 Hardware Dependent Optimization Techniques 4.4.1 SSE Intrinsic Functions 4.4.2 AVX Intrinsic Functions 4.4.3 NEON Intrinsic Functions                                                                                                                        | 39<br>40<br>42<br>43<br>45<br>46<br>47<br>48<br>51<br>52             |

| 4.2 Identifying Bottlenecks in the Baseline BLSTM Implementation. 4.3 Software Optimization Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 39<br>40<br>42<br>43<br>45<br>46<br>47<br>48<br>51<br>52<br>54<br>57 |

| 4.2 Identifying Bottlenecks in the Baseline BLSTM Implementation. 4.3 Software Optimization Techniques 4.3.1 Parallelization Scenarios 4.3.1.1 Input-level Parallelization (Offline) 4.3.2 Neuron-level Parallelization (Online) 4.3.3 Memory Allocation and Access 4.3.4 Loop Unrolling. 4.3.5 Use of High-Performance Libraries 4.3.6 Precision Reduction 4.3.7 Lookup Tables for Activation Functions 4.4 Hardware Dependent Optimization Techniques 4.4.1 SSE Intrinsic Functions 4.4.2 AVX Intrinsic Functions 4.4.3 NEON Intrinsic Functions                                                                                                                        | 39404243454647485152545759                                           |

| 4.2 Identifying Bottlenecks in the Baseline BLSTM Implementation 4.3 Software Optimization Techniques 4.3.1 Parallelization Scenarios 4.3.1.1 Input-level Parallelization (Offline) 4.3.2 Neuron-level Parallelization (Online) 4.3.3 Memory Allocation and Access 4.3.4 Loop Unrolling 4.3.5 Use of High-Performance Libraries 4.3.6 Precision Reduction 4.3.7 Lookup Tables for Activation Functions 4.4 Hardware Dependent Optimization Techniques 4.4.1 SSE Intrinsic Functions 4.4.2 AVX Intrinsic Functions 4.4.3 NEON Intrinsic Functions 5 EXPERIMENTAL METHODOLOGY 5.1 Evaluation Problem                                                                        | 394042434546474851525959                                             |

| 4.2 Identifying Bottlenecks in the Baseline BLSTM Implementation. 4.3 Software Optimization Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 394042434546475254575959                                             |

| 4.2 Identifying Bottlenecks in the Baseline BLSTM Implementation. 4.3 Software Optimization Techniques. 4.3.1 Parallelization Scenarios. 4.3.1.1 Input-level Parallelization (Offline). 4.3.2 Neuron-level Parallelization (Online). 4.3.3 Memory Allocation and Access. 4.3.4 Loop Unrolling 4.3.5 Use of High-Performance Libraries. 4.3.6 Precision Reduction. 4.3.7 Lookup Tables for Activation Functions. 4.4 Hardware Dependent Optimization Techniques. 4.4.1 SSE Intrinsic Functions 4.4.2 AVX Intrinsic Functions 4.4.3 NEON Intrinsic Functions 5 EXPERIMENTAL METHODOLOGY 5.1 Evaluation Problem 5.2 Comparisons 5.3 Evaluation Metrics.                      | 39404243454647515257595960                                           |

| 4.2 Identifying Bottlenecks in the Baseline BLSTM Implementation. 4.3 Software Optimization Techniques. 4.3.1 Parallelization Scenarios. 4.3.1.1 Input-level Parallelization (Offline). 4.3.1.2 Neuron-level Parallelization (Online). 4.3.3 Hidden Layers Aggregation. 4.3.4 Loop Unrolling 4.3.5 Use of High-Performance Libraries. 4.3.6 Precision Reduction. 4.3.7 Lookup Tables for Activation Functions. 4.4 Hardware Dependent Optimization Techniques. 4.4.1 SSE Intrinsic Functions. 4.4.2 AVX Intrinsic Functions. 4.4.3 NEON Intrinsic Functions. 5 EXPERIMENTAL METHODOLOGY. 5.1 Evaluation Problem. 5.2 Comparisons. 5.3 Evaluation Metrics. 5.3.1 Accuracy. | 3940424345464751525759596060                                         |

| 6 RESULTS                                                         | 63 |

|-------------------------------------------------------------------|----|

| 6.1 BLSTM runtime on Intel architectures                          | 63 |

| 6.2 BLSTM runtime on ARM architectures                            | 68 |

| 6.3 Runtime and energy consumption on Intel and ARM architectures | 70 |

| 7 CONCLUSION                                                      | 73 |

| 7.1 Future Work                                                   | 75 |

| REFERENCES                                                        | 76 |

| APPENDIX A — C++ IMPLEMENTATION OF LOOKUP TABLE                   | 78 |

#### 1 INTRODUCTION

Large-scale neural networks, with thousands or millions of weights, are currently being deployed in applications to achieve super-human accuracy. However, training and running such networks is computationally and memory expensive since these procedures involve costly mathematical operations and many memory accesses. Such operations could be run in parallel, in GPUs, thereby achieving a considerable computation speedup; this is possible since GPUs usually have more resources and faster memory bandwidth, besides providing a better architecture to manipulate vectors. However, affordable and powerful GPUs are not always available for deployment, due to a variety of reasons including cost, component reliability, and programming complexity (VANHOUCKE; SE-NIOR; MAO, 2011). The overhead of launching GPU kernels and transferring data between the CPU and GPU, for instance, cannot always be amortized over the execution time of some workloads, according to the size of the data (batch size) that must be offloaded. With this in mind, we show that software optimization techniques and hardware capabilities of traditional CPUs can be used and result in significant scalability and performance improvements. Some of the techniques applied in this work are not new to researchers working in high-performance computing, but when they are combined as presented in this work, result in new neural network development methods that provide considerable runtime and energy consumption improvements. We also show that using specific hardware capabilities of a target architecture results in expressive runtime improvements even compared to the use of optimized high-performance BLAS libraries.

To develop and evaluate the contributions presented in this work, we will consider the use and optimization of a Bidirectional Long Short Term-Memory (BLSTM) neural network designed for high-accuracy Optical Character Recognition (OCR), when applied to old German text (Fraktur). Optical Character Recognition is the conversion of printed or handwritten text images into machine encoded text. It is a building block of many important visual recognition processes such as data mining, machine translation and text-to-speech translations. BLSTM neural networks are a variant of the Long Short-Term Memory (LSTM) architecture, which is known to often outperform other types of approaches in terms of accuracy and robustness of the results on the task of character recognition (RYBALKIN et al., 2017), (BREUEL et al., 2013), (AFZAL et al., 2015), (GRAVES, 2008), (HAYKIN, 1999) and many other tasks.

BLSTM neural networks are Recurrent Neural Networks (RNNs) that are known

to perform well when processing data with a sequential or temporal characteristic, such as sequences of letters in an image for OCR and sequences of wave forms for speech recognition, where the identification of a given word is made easier by taking into account the words and sounds that preceded it. BLSTMs achieve this capability by implementing a memory-like functionality, capable of preserving information from previous outputs of an input signal to the network as part of an internal state. In the context of OCR applications, BLSTMs are an appropriate machine learning algorithm since they allow for the network to consider both preceding and following characters in an image, when performing the transcription of a specific part of a text.

There are many challenges involved in developing an efficient software implementation of a BLSTM. A first challenge is the high memory bandwidth needed to transfer network weights from memory to computational units (e.g. ALU). Some characteristics of BLSTMs make it difficult to efficiently implement them in terms of better memory usage: first, they have recurrent connections, which makes it harder to parallelize the computation of their outputs; secondly, BLSTMs differ from RNNs in that they have four additional gates to control the data flow within a neuron, which has an impact in the amount of data that needs to be loaded and processed by each individual neuron; thirdly, BLSTMs, unlike classic neural network architectures, read input data in two directions: forward and backward. This means that the hidden layer of the network needs to be duplicated, which has a direct impact on the amount of memory needed to compute the output of the network. In this work we propose to deploy a series of optimization techniques over a baseline BLSTM implementation in order to overcome these difficulties; the techniques are: 1) rearrange weighs in memory and use new access patterns that allow us to avoid a duplication of the hidden layer; 2) rearrange weights in memory to have full data vectors in contiguous memory, making better use of cache locality; 3) reduce the memory required for intermediate results, which can be high due to the fact that BLSTMs have recurrent connections; and 4) tolerate a small reduction in the accuracy of the network by reducing the numerical precision of the weights that compose it.

A second challenge in efficiently implementing BLSTMs is the high complexity of each LSTM cell structure, which includes activation functions and multiple multiplicative units making use, in particular, of expensive dot product algebraic operations. In order to speed up the baseline implementation of BLSTM that we consider in this work, we suggest to explore runtime improvements by 1) making use of sequential data vectors for processing high-dimensional inputs; 2) performing loop unrolling of dot product

operations; 3) using BLAS library for more efficient dot product operations. Although these standard optimization techniques allow us to accelerate the relevant algebra operations and result in better performance, we aim to further accelerate the implementation of dot products by modifying a baseline BLSTM implementation by also exploiting specific hardware capabilities. We propose, for instance, to do so by allowing more data to be processed by a same instruction, using: 4) SSE and AVX intrinsic functions (for Intel architectures); and 5) NEON intrinsic functions (for ARM architectures). And finally, we intend to accelerate BLSTMs by 6) applying lookup tables to the neuron activation functions, in order to replace runtime-intensive mathematical functions with simpler arrays indexing operations while tolerating a small decrease in accuracy.

To parallelize the neural network, we take into consideration two common scenarios of visual recognition mobile applications: one where the tasks are offloaded to the cloud to be run in high-performance machines, and another where the tasks run locally on an embedded processor. The second scenario has an important concern: energy consumption. In order to reduce this requirement in mobile applications, we also take into consideration the need to reduce the amount of allocated resources. With these two aspects in mind we propose two different parallelization scenarios: one that is better suited for batch processing (where all inputs are loaded in memory), which we call *Input-level parallelization* or *Offline*, and another one that is better suited to process one high-dimensional input or a sequence of inputs at a time, but using fewer CPU resources; we call this the *Neuron-level parallelization* or *Online* scenario.

As previously mentioned, we demonstrate the performance improvements obtained by our proposed techniques in an image recognition application. In our experiments, we use a network composed of one hidden layer with 200 neurons, divided equally into forward and backward direction functions. The test set of our application is composed of 3401 text images. We evaluate the accuracy of the outputs computed by the network, as well as its runtime. The reference recognition accuracy of the baseline BLSTM implementation is 98.2337% using single-precision floating-point format. We consider applying optimizations over two Intel architectures: the Intel I7-4500U, a power-optimized CPU designed for laptops, and the Intel Xeon E5-2670 v3, a high-performance CPU. We also consider two ARM low-power CPUs for embedded devices: the ARM Cortex-A53 (e.g. used by Zynq FPGA board) and the ARM Cortex-A9 (e.g. used by Raspberry pi 3 board). We show that by using our proposed optimizations, it is possible to produce a BLSTM that is 9x faster than a baseline implementation with parallelization. We also

show a significant decrease in energy consumption, while undergoing a negligible loss in accuracy.

# 1.1 General Objective

In this work, we present contributions to improve performance and energy consumption of neural network software implementations in CPUs without compromising their accuracy. We aim to achieve this objective by applying software optimization techniques, and using hardware capabilities of modern computational platforms, to speed-up the most intensive calculation parts of the code of a BLSTM neural network for Optical Character Recognition.

#### 1.2 Outline

The thesis is structured as follows. In Section 2 we review the theoretical basis that underlies this work and present the different architectures used to evaluate our implementations. In Section 3, we review previous publications that also aim at speeding up neural networks. The software optimization techniques and hardware capabilities explored in this work are described in Section 4. In Section 5, we show the way that we intend to conduct the experimental analysis. Finally, Section 6 presents the results obtained via the proposed techniques and compares different configurations of the implementations. Section 7 concludes this work by outlining its main results and discussing future work.

#### 2 THEORETICAL BACKGROUND

In this chapter we will review the main neural networks concepts that are relevant to the implementation of BLSTM neural networks. We will also introduce the Optical Character Recognition problem, used in this work to evaluate the performance of our optimized neural network, as well and a string comparison algorithm that is used to measure the accuracy of our neural networks. Finally, we present the main computer architectures that are relevant to this work, giving special attention to some particular features of each one of them.

#### 2.1 Neural Networks

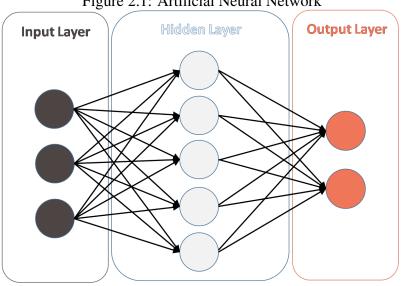

Artificial Neural Networks (ANNs or just NNs) are interconnected groups of nodes that computationally model the functionality of the human brain. The goal of NNs is to solve problems in the same way humans would do. Each node of an NN can be identified as a neural unit, and they are connected with many others within a same layer or among layers (see Figure 2.1). The input signals presented to a network travel from the first (input) to the last (output) layer, passing through intermediate layers—either just one (single-layer) or more hidden layers (multi-layer). The activation function of a neuron determine its output, given inputs; they typically compute this by taking a weighted sum of the inputs (weighted by their respective weights) and limiting it to a pre-defined range, before propagating this output to other neurons. Typical activation functions used in neurons include the functions  $1/(1+\exp^{-x})$  and  $\tanh(x)$ . The connections/weights between neurons can enforce or inhibit the effect on the activation state of connected neural units.

NNs need to be trained from examples, rather than explicitly programmed. The training process aims at finding weights that result in the NN correctly mapping given inputs to the most appropriated outputs. There are many algorithms to train a NN and estimate the optimal weights of each neuron. One of the most popular algorithms is called Backpropagation.

The Backpropagation algorithm ((BRYSON; DENHAM; DREYFUS, 1963)) consists in measuring the error of the network when applied to a given input (specifically, by comparing its output with the desired/ground truth output), and then using this information to modify the network weights in order to minimize the error. The Backpropagation algorithm is a supervised learning technique that receives as input a training set (con-

Figure 2.1: Artificial Neural Network

Representation of a feed forward artificial neural network with ten neurons. Each neuron is represented by a circular node. The arrows represent the connections/weights between neurons. In this example, the neurons are split into three layers. Three neurons compose the input layer, five neurons the hidden layer and two neurons compose the output layer.

sisting of sample pairs of input and corresponding desired output) and iterates over its elements in order to optimize the weights of the neurons. At first, all weights are initialized randomly. Following, input samples are propagated forward through the network and its output is compared with the expected one (i.e. ground truth) using a given loss function; if the difference/error is not satisfactory, the error is propagated back to the previous layers of the network and used to adjust their internal weights. After that, another iteration starts, where the next example is presented and weights are adjusted, and the process is repeated until a stop criterion is met.

A simplified version of the method used to determine the output of a neuron is presented in Equation 2.1. The weighted sum of the inputs is represented here by the dot product between an input vector X and the weight vector W of the neuron. This sum is processed by a  $\sigma$  activation function resulting in h, the neuron output (MCCULLOCH; PITTS, 1943):

$$h = \sigma(W \cdot X). \tag{2.1}$$

Among the many different existing ANNs architectures we can highlight those purely built with acyclic connections, also known as feed-forward neural networks (see Figure 2.1), and those with cyclic connections, referred to as Recurrent Neural Networks (RNNs).

#### 2.1.1 Recurrent Neural Networks

RNNs are able to look at recent information (i.e. previous outputs) to perform the present task. The cyclic connections of an RNN architecture allow for a memory-like functionality, preserving the previous activation outputs of the network as a type of internal state (see Figure 2.2). This is helpful for sequence processing tasks that need access to past network outputs in order to improve accuracy at a current input.

Figure adapted from: (OLAH, 2015). On the left of the equality, an RNN with its cyclic connection. It receives a given input  $X_t$  and outputs a value  $h_t$  at time t. The loop/cyclic connection allows for information about previous activations to be taken into account at future timesteps, when processing subsequent inputs. On the right of the equality, we see the same RNN but with its loop unrolled in time. The network can be thought of as multiple copies of a same network, repeated over time, each one passing its output as a message to a successor network. The loop unrolled RNN makes it explicit how this architecture keeps track of input sequences, by clarifying how context information about previous inputs/outputs is passed ahead when processing subsequent inputs.

Bidirectional Recurrent Neural Networks (BRNNs) were proposed to take into account previous outputs from both sides of an input signal (e.g. past and future letters of an input image). The input signal is processed both in the forward and backward directions by passing it through two separate hidden layers. The outputs of these layers are added by a common output layer that has access to past and future context of the given input.

Despite being extremely important, RNNs present a problem of long term dependencies. Olah (2015) explains this problem by considering the difficulties of building a language model capable of correctly predicting which words may follow other words:

"If we are trying to predict the last word in "the clouds are in the sky", we do not need any further context—it is pretty obvious the next word is going to be sky. In such cases, where the gap between the relevant information and the place that it is needed is small, RNNs can learn to use the past information (...) There are cases where we need more context. Consider trying to predict the last word in the text "I grew up in France... I speak fluent French". Recent information suggests that the next word is probably the name of a language, but if we want to narrow down which language, we need the context of France, from further back. It is entirely possible for the gap between the relevant information and the point where it is needed to become very large. Unfortunately, as that gap grows, RNNs become unable to learn to connect the information" (OLAH, 2015)

Due to this limited range of accessible context (i.e. the network can keep information just from the recent outputs and not of long-term dependencies) with RNNs, Long Short-Term Memory (LSTM) architecture was proposed in (HOCHREITER; SCHMIDHUBER, 1997) to overcome this problem.

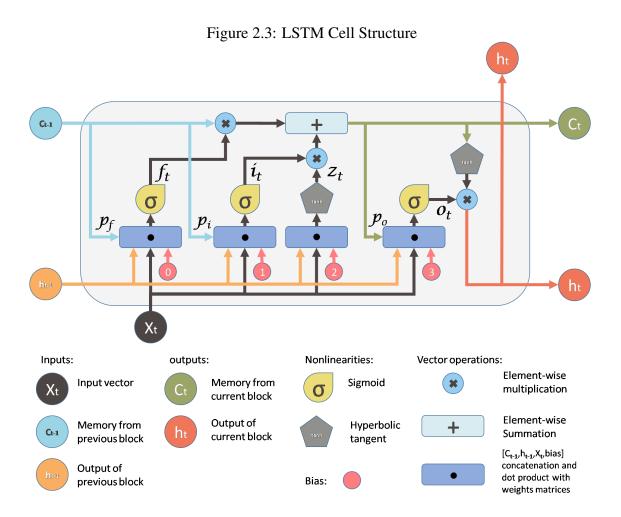

#### 2.1.2 LSTM and BLSTM Neural Networks

LSTM networks are a special type of RNN architecture, capable of storing and encoding long-term dependencies between its inputs. The LSTM architecture replaces the simple nodes (i.e. neurons) of an RNN (such as a *hyperbolic tangent* function) with memory blocks, or "memory cells". Each memory cell (i.e. neuron) has three different internal *gates* that control the flow of the input data and determine in which way the internal state (or memory) of the cell will be updated, as it processes new input signals. The LSTM cells that compose the overall LSTM neural network can be thought as repetitive connections of one LSTM cell with the next one, similarly to the repetitive connections previously shown in Figure 2.2.

The three control gates that compose an LSTM cell are called *forget*, *input*, *and* output gates: (f, i and o), respectively. These gating functions can be interpreted as reset, write and read operations, respectively. They are applied to the cell internal state (C) and are responsible for preserving the internal state of the memory cell over longer periods of time. The cell state signal C is propagated through the entire chain of memory cells, undergoing changes and updates determined by the above-mentioned gates. Each gate regulates the way in which state information must be removed or added to the cell state. Each control gate is implemented as a sigmoid neural net layer and a pointwise

multiplication operation; the outputs of this layer are numbers between zero and one, specifying how much of each component of the memory/state should be preserved.

In the case of a *forget gate*, an output of zero can be interpreted as a signal ordering the network to remove information from the current memory state. In an OCR application, for instance, this might happen when we reach the end of a sentence, in which case we can forget the last word that was processed since it may be irrelevant, e.g., to predict if the next word will be a verb or a noun. An output of one, on the other hand, can be interpreted as a signal ordering the network to completely preserve (not forget) a given part of the state, since it may be very relevant to determine the class of upcoming words. A similar intuition applies also to *input gates* (which determine how strongly information about new words should be included in the current state/memory), and to *output gates* (which determines how strongly the current state/memory values will be used in determining the present output or prediction being made by the network). In Figure 2.3, the output of the forget, input, and output gates are depicted, respectively, as the control gates of the cell state.

A complete description of an LSTM cell structure is presented in Figure 2.3. Equation 2.2 presents formulas that compute the forward activation (or output) of an LSTM network (GREFF et al., 2015). In Equation 2.2, t denotes the current time, t-1 refers to the previous timestep/input, (X) is an input vector; and (h) refers to the cell's output. These equations specify, in particular, (I) how the current state/memory, (I) is updated based on the previous state, (I) and on the outputs of the control gates; and (I) how its outputs are updated, (I) given the current input, (I) in these equations, (I) is a bias vector, (I) is a rectangular input weight matrix for each gate, and (I) is a square recurrent weight matrix. The so-called *peephole connections* (I) are responsible for allowing the gates to access the cell's internal state. Since the goal of this work is not to provide an in-depth derivation for these equations, we refer the interested reader to (GREFF et al., 2015) and (OLAH, 2015) for more technical details.

$$f_{t} = \sigma(W_{f}X_{t} + R_{f}h_{t-1} + p_{f} \odot C_{t-1} + b_{f}) \qquad \text{forget gate}$$

$$i_{t} = \sigma(W_{i}X_{t} + R_{i}h_{t-1} + p_{i} \odot C_{t-1} + b_{i}) \qquad \text{input gate}$$

$$z_{t} = \tanh(W_{z}X_{t} + R_{z}h_{t-1} + b_{z}) \qquad \text{block input}$$

$$o_{t} = \sigma(W_{o}X_{t} + R_{o}h_{t-1} + p_{o} \odot C_{t} + b_{o}) \qquad \text{output gate}$$

$$C_{t} = i_{t} \odot z_{t} + f_{t} \odot C_{t-1} \qquad \text{cell state}$$

$$h_{t} = o_{t} \odot \tanh(C_{t}) \qquad \text{block output.}$$

Figure adapted from: (YAN, 2016)

In Figure 2.3, the output of each control gate is processed through an activation function, which is a non-linear function that bounds the output's range to a known numerical interval. Activation functions are point-wise non-linear functions and typically implemented as a *logistic sigmoid* function  $(1/1 + \exp^{-x})$ , denoted by  $\sigma$ , and a *hyperbolic tangent* function, denoted by tanh. The *hyperbolic tangent* is usually used to implement the block input  $z_t$  and the output gate  $o_t$ . Computing the output of activation functions can be computationally expensive, and one of the contributions of this work will be to show how it can be accelerated.

Another important feature of the LSTM architecture is the presence of a forward-backward algorithm, known as Connectionist Temporal Classification (CTC) (GRAVES et al., 2006). It is used to process the numeric outputs generated by the network in order to associate them with a discrete label or class. In particular, CTC runs the real-valued outputs of the network through a softmax function, which scales to the range [0,1] so that they can be interpreted as probabilities; then, CTC uses the resulting information about class probabilities (given the input that was presented) to identify/generate the particular

class that will be used as the predicted output of the network. In the OCR setting, the CTC algorithm is responsible for allowing an LSTM to generate outputs that are directly associated with indices in an alphabet containing all possible characters that may be present in a given input image. In this way, LSTM networks are capable of recognizing entire input sequences without any pre-segmentation or post-processing of their corresponding inputs. They can directly transform the outputs of the network into label sequences because they are trained to predict the conditional probabilities of the possible output labels, given input sequences. The last step is performed by a Translate Back function, which is responsible for identifying, in the alphabet data structure, the target character by an index, and outputs it, one by one, to the output vector of the network creating the predicted string for the given input image.

Even though LSTMs achieve good performance in tasks where a type of memory is necessary, in this work we consider a variant of the LSTM architecture, known as BLSTM. BLSTMs consist of a bi-directional recurrent neural network (as previously defined in Section 2.1.1) composed of many LSTM memory cells. This type of network is composed of two hidden layers: a Forward Hidden Layer (FHL) and a Backward Hidden Layer (BHL), both of which are connected to a common output layer. The FHL is a layer composed of N LSTM cells that take as input, e.g., an image, and processes its pixel columns from left to right. The BHL, on the other hand, uses a different set of N LSTM cells for processing the same input, e.g., the same image presented to the FHL, and processes its pixels columns from right to left. Each such hidden layer has its own distinct set of weights. The capability of analyzing an image from different perspectives (e.g., by processing its pixels in different orders) results in better accuracy, since it allows the network to take into account information about preceding and following letters when determining which particular character corresponds to the current image location being processed. BLSTMs inherit many of the advantages of LSTMs, such as the capability of preserving the long-term dependencies of its inputs for a longer period of time). In Section 4.1 we will describe characteristics of the particular BLSTM used in this work.

# 2.2 Optical Character Recognition

As mentioned in Chapter 1, LSTM neural networks often outperform other types of neural networks in terms of accuracy and robustness, when applied to the task of character recognition. For this reason, we choose evaluate the performance of our proposed

optimization techniques (when applied to a baseline BLSTM neural network) in this problem.

The Optical Character Recognition (OCR) problem consists in recognizing printed or handwritten text images; that is, converting printed or handwritten image characters (stored as an image) into machine encoded characters. A text image is usually scanned or taken by a camera from a printed paper data record, such as a passport, receipt, card, book, or other types of documents. The OCR conversion process consists of an analysis of the image, character by character, translating its alphabetic letters, symbols, or numeric digits, into computer character codes that can represent them, such as ASCII codes. This process is an important step of digitizing printed texts in order to make them electronically available, and is widely used in machine processes such as cognitive computing, machine translation, text-to-speech conversion, and text mining.

#### 2.3 String Comparison Algorithms

When evaluating the accuracy of a network tasked with recognizing characters, we need to choose a metric to compare the output produced by the network (a string) and the desired/ground truth output. One possible way of comparing strings is by using string distance algorithms which compute the dissimilarity between two words of arbitrary length.

#### 2.3.1 Levenshtein Distance

The Levenshtein Distance is a metric used to measure the difference between two sequences of characters, or strings. The Levenshtein Distance algorithm measures the difference between two sequences of characters by calculating the minimum number of character additions, deletions, and substitutions required to transform one sequence into the other (Levenshtein, 1966).

The Levenshtein distance between two strings a and b with length |a| and |b|, respectively, is denoted by  $\text{lev}_{a,b}(|a|,|b|)$  and defined in Equation 2.3. Here, the term  $1_{(a_i \neq b_j)}$  is the indicator function, equal to 0 when  $a_i = b_j$  and equal to 1 otherwise, and  $\text{lev}_{a,b}(i,j)$  is the distance between the first i characters of a and the first j characters of b. The first element in the "min" clause of the equation represents the possibility of deletion

(from a to b); the second clause corresponds to the possibility of character insertion, and the third one to the match or mismatch, depending on whether the respective characters are the same.

$$\operatorname{lev}_{a,b}(i,j) = \begin{cases} \max(i,j) & \text{if } \min(i,j) = 0, \\ \operatorname{lev}_{a,b}(i-1,j) + 1 & \\ \operatorname{lev}_{a,b}(i,j-1) + 1 & \text{otherwise.} \end{cases}$$

$$\operatorname{lev}_{a,b}(i-1,j-1) + 1_{(a_i \neq b_j)}$$

(2.3)

#### 2.4 CPU Architectures and Instruction Set Extensions

In our work, we consider using many CPU-specific optimizations, which depend on the particular architecture a neural network is implemented on. In this section we present the CPU architectures used in this work to conduct our experiments and tests. Table 2.1 shows four selected architectures. Xeon E5-2670 is a high-performance CPU targeted at non-consumer workstation/server/embedded systems markets. Core i7-4500U is a power-optimized CPU designed for laptops. The ARM Cortex-A53 and Cortex-A9 architectures are low-power CPUs for embedded devices. They are used by the Raspberry Pi 3 Model B and by Xilinx Zynq-7000 XC7Z045 SoC, respectively. The maximum working frequency of each processor above mentioned is shown in the first column of Table 2.1. The second column of Table 2.1 presents the thermal design power (TDP) in watts of the corresponding processors. TDP is defined as the maximum amount of heat generated by the processor when in typical operation. The number of cores and threads of each processor is presented in the third column of the table; the last column enumerates the extensions to the instruction set of each architecture—which will be exploited in this work when introducing and proposing possible hardware-specific optimizations.

| Table 2.1: The reference CPU:  Processor | architecture<br>TDP | es used in thi<br>Cores | s work  Instruction Set |

|------------------------------------------|---------------------|-------------------------|-------------------------|

|                                          | [ <b>W</b> ]        | (Threads)               | Extension               |

| Intel Xeon E5-2670 v3 @ 3.1 GHz (turbo)  | 90                  | 16(32)                  | SSE4.2 / AVX2.0         |

| Intel Core i7-4500U @ 3.0 GHz (turbo)    | 15                  | 2(4)                    | SSE4.2 / AVX2.0         |