### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

#### ROGER LUIS BRITO ZAMPARETTE

# High Efficiency MPPT Switched Capacitor DC - DC Converter for Photovoltaic Energy Harvesting Aiming for IoT Applications

Thesis presented in partial fulfillment of the requirements for the degree of Master of Microeletronics

Advisor: Prof. Dr. Hamilton Klimach

#### CIP - CATALOGING-IN-PUBLICATION

Luis Brito Zamparette, Roger

High Efficiency MPPT Switched Capacitor DC - DC Converter for Photovoltaic Energy Harvesting Aiming for IoT Applications / Roger Luis Brito Zamparette. – Porto Alegre: PGMI-CRO da UFRGS, 2017.

123 f.: il.

Thesis (Master) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica, Porto Alegre, BR–RS, 2017. Advisor: Hamilton Klimach.

1. Switched Capacitor. 2. DC-DC converter. 3. Photovoltaic Energy Harvesting. 4. IoT. 5. MPPT. 6. CMOS. I. Klimach, Hamilton. II. Título.

#### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Rui Vicente Oppermann Vice-Reitor: Profa. Jane Fraga Tutikian

Pró-Reitor de Pós-Graduação: Prof. Celso Giannetti Loureiro Chaves Diretor do Instituto de Informática: Profa. Carla Maria Dal Sasso Freitas Coordenadora do PGMICRO: Prof. Fernanda Gusmão de Lima Kastensmidt Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

#### ACKNOWLEDGEMENTS

It is hard to thank everyone who deserves, especially when many of them will never read this work. But, I will give a shot.

Naturally, I thank my parents Jacira da Purificação Brito and Rogério de Souza Zamparette, that are there for me in the good and the bad moments, and my sister Angel Gabriela Brito Zamparette, that is my confidant and is the person that knows me better in all this world.

Technically speaking, I thank Professor and my Advisor Dr. Hamilton Klimach. He is the person that taught me practically everything I know about the basis of microelectronics.

I can not forget about the guys of CS Lab 110: Gabriel, Diogo, Carlos, Israel, Jhon, and Arthur. They made my time in the Master be fun and joyful. Especially, a thank Arthur Campos for the friendship, discussions, and parties. Finally, to all the people that somehow contributed to my growth, like Professor Dr. Sérgio Bampi, MSc. Pedro Toledo and all the guys that participate of the GME - AMS.

Also, this work could not be done without the financial support of CAPES, CNPQ and HP Company, the access to silicon provided by MOSIS and all the EDA and TI support given by NSCAD.

#### **ABSTRACT**

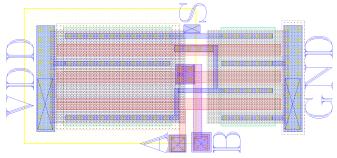

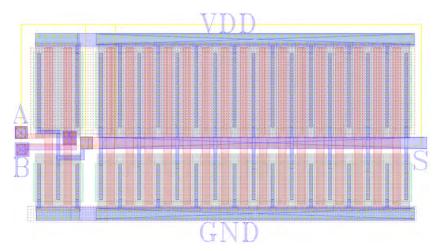

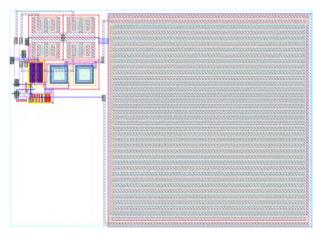

This work presents a six phase Switched Capacitor (SC) DC - DC converter for photovoltaic Energy Harvesting designed in a 130 nm CMOS process for commercial motes application and Internet of Things (IoT). It tracks the Maximum Power Point (MPP) of a commercial 3 cm x 3 cm 60 mW polycrystalline photoelectric panel through switching frequency modulation aiming battery recharge. Open-circuit voltage ratio was the chosen Maximum Power Point Tracking (MPPT) strategy. The converter achieves a maximum power conversion efficiency of 90 % for input power higher than 30 mW and is designed to operate with input voltages from 1.25 V to 1.8 V, resulting output voltages from 2.5 V to 3.6 V, respectively. Peripheral circuitry also includes an output over-voltage protection of 3.6 V and the control circuits, that consumes a total of 850  $\mu$ A at 3.3 V of static power. Complete layout consumes 300 x 700  $\mu$ m $^2$  of silicon area. The only external components are 6x100 nF capacitors.

**Keywords:** Switched Capacitor. DC-DC converter. Photovoltaic Energy Harvesting. IoT. MPPT. CMOS.

# Conversor DC - DC de Alta Eficiência baseado em Capacitores Chaveados usando MPPT com o Objetivo de Coletar Energia Fotovoltaica com Foco em Aplicações IoT

#### **RESUMO**

Este trabalho apresenta um conversor CC - CC baseado em Capacitores Chaveados de 6 fases e tempos intercalados com o objetivo de coletar energia fotovoltaica projetado em tecnologia CMOS de 130 nm para ser usado em aplicações em Internet das Coisas e Nós Sensores. Ele rastreia o máximo ponto de entrega de energia de um painel fotovoltaico policristalino de 3 cm x 3 cm através de modulação da frequência de chaveamento com o objetivo de carregar baterias. A razão da tensão de circuito aberto foi a estratégia de rastreio escolhida. O conversor foi projetado em uma tecnologia CMOS de 130 nm e alcança uma eficiência de 90 % para potencias de entrada maiores do que 30 mW e pode operar com tensões que vão de 1.25 até 1.8 V, resultando em saídas que vão de 2.5 até 3.6, respectivamente. Os circuitos periféricos também incluem uma proteção contra sobre tensão na saída de 3.6 V e circuitos para controle, que consomem um total máximo de potência estática de 850  $\mu$ A em 3.3 V de alimentação. O layout completo ocupa uma área de 300 x 700  $\mu m^2$  de silício. Os únicos componentes não integrados são 6x100 nF capacitores.

**Palavras-chave:** Capacitor Chaveado, Conversor CC - CC, Coleta de Energia Fotovoltaica, IoT, MPPT, CMOS.

# LIST OF FIGURES

| Figure 1.1 Wireless Sensor Network: Generic Scheme.                                    | 15 |

|----------------------------------------------------------------------------------------|----|

| Figure 1.2 MICA2.                                                                      |    |

| Figure 1.3 Generic scheme of a Energy Harvesting DC-DC Conversion                      | 16 |

| Figure 2.1 10 cm x 10 cm PV cell                                                       | 21 |

| Figure 2.2 PV cell construction                                                        | 21 |

| Figure 2.3 Crystal structure of monocrystalline and polycrystalline Photovoltaic cells | 22 |

| Figure 2.4 Electrical model of a PV cell.                                              | 22 |

| Figure 2.5 I-V and P-V PV cell characteristic.                                         |    |

| Figure 2.6 I-V PV cell characteristic for various S.                                   |    |

| Figure 2.7 P-V PV cell characteristic for various S.                                   | 25 |

| Figure 2.8 I-V PV cell characteristic for various T.                                   | 25 |

| Figure 2.9 P-V PV cell characteristic for various T.                                   |    |

| Figure 2.10 Selected PV panel.                                                         |    |

| Figure 2.11 Schematic of the setup test for PV panel characterization.                 |    |

| Figure 2.12 Characterization PV panel board.                                           |    |

| Figure 2.13 Measurements for $S_1 = 1000 \text{ W/m}_2$ (a) I-V (b) P-V.               |    |

| Figure 2.14 Measurements for $S_2 = 200 \text{ W/m}_2$ (a) I-V (b) P-V.                |    |

| Figure 2.15 Measurements for $S_3 = 50 \text{ W/m}_2$ (a) I-V (b) P-V.                 |    |

| Figure 2.16 Spreadsheet for parameters extraction PV panel.                            |    |

| Figure 2.17 Measured and estimated: initial kick.                                      |    |

| Figure 2.18 Measured and estimated: 1 iteration                                        |    |

| Figure 2.19 Measured and estimated: 32 iterations                                      |    |

| Figure 2.20 Flowchart of P and O MPPT algorithm                                        |    |

| Figure 2.21 Flowchart of Incremental Conductance MPPT algorithm                        |    |

| Figure 2.22 MPPT complete scheme.                                                      | 36 |

| Figure 3.1 PV energy conversion. (a) Wrong way to connect (b) Right way to connect     | 37 |

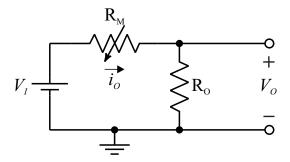

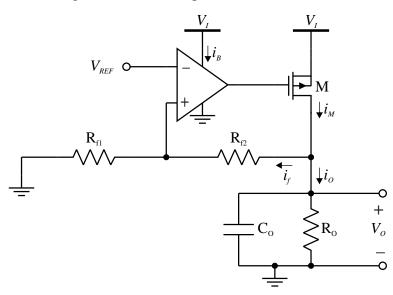

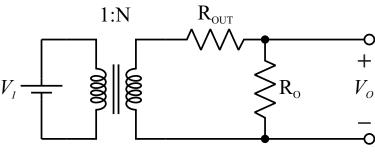

| Figure 3.2 Linear DC-DC converter conceptual schematic.                                | 38 |

| Figure 3.3 Low-Dropout DC-DC converter.                                                | 39 |

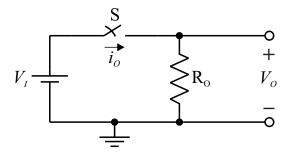

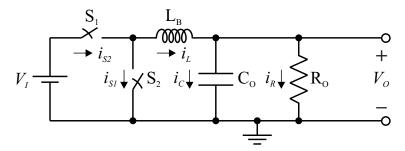

| Figure 3.4 Switched DC-DC converter conceptual schematic                               | 40 |

| Figure 3.5 Buck converter.                                                             | 41 |

| Figure 3.6 Boost converter.                                                            |    |

| Figure 3.7 Boost converter operation steps.                                            | 43 |

| Figure 3.8 Current waveforms.                                                          |    |

| Figure 3.9 Voltage waveforms.                                                          |    |

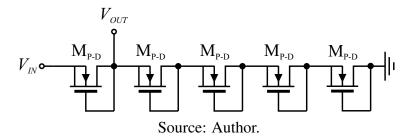

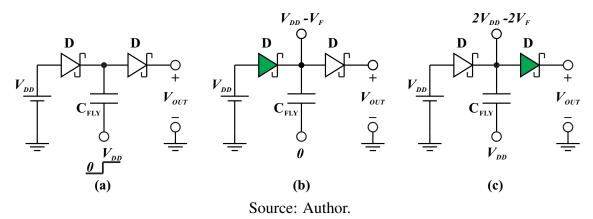

| Figure 3.10 1-to-3 SC DC - DC Converter.                                               |    |

| Figure 3.11 1-to-3 SC DC - DC Converter operation steps.                               |    |

| Figure 3.12 Boost converter operation steps.                                           |    |

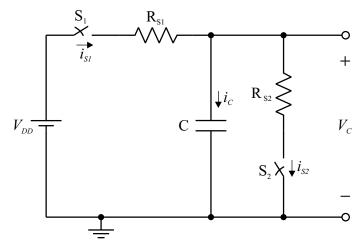

| Figure 3.13 Didactic circuit to explain SSL and FSL losses                             | 48 |

| Figure 4.1 Application's block diagram.                                                | 54 |

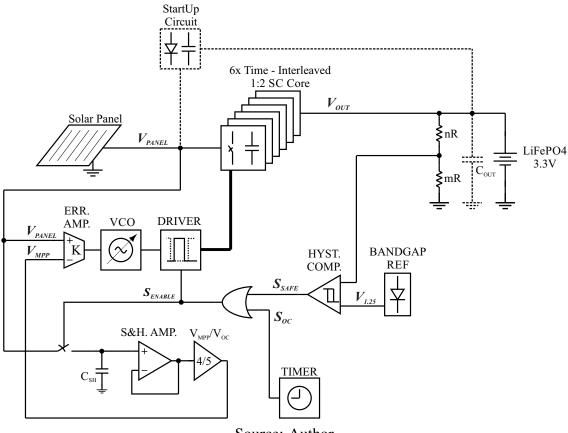

| Figure 4.2 Proposed architecture.                                                      | 56 |

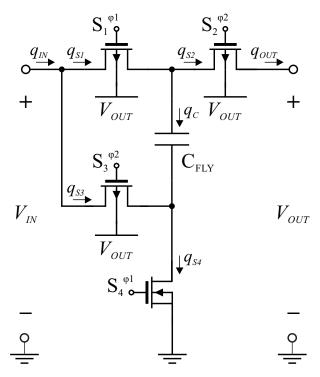

| Figure 4.3 1-to-2 SC Topology                                                          | 57 |

| Figure 4.4 1-to-2 SC operation.                                                        | 57 |

| Figure 4.5 Optimum switching frequencies for different input powers                    | 60 |

| Figure 4.6 Optimum W curves                                                            |    |

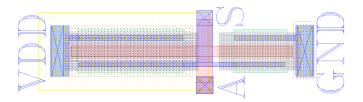

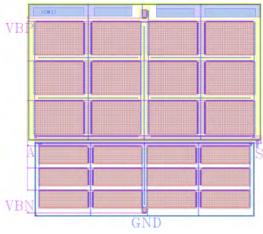

| Figure 4.7 Layout of the converter core (105 $\mu$ m x 105 $\mu$ m).                   | 61 |

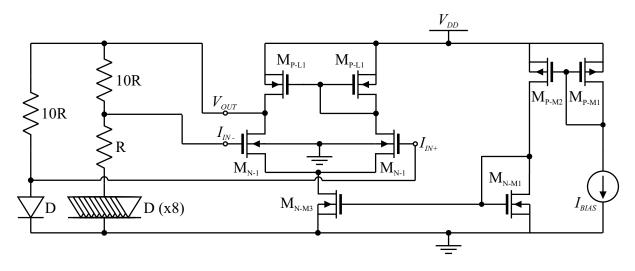

| Figure 4.8 Sample & Hold circuit topology.                                                              | 62 |

|---------------------------------------------------------------------------------------------------------|----|

| Figure 4.9 Timer topology                                                                               | 63 |

| Figure 4.10 Timer bias.                                                                                 | 64 |

| Figure 4.11 Telescopic op-amp topology.                                                                 | 65 |

| Figure 4.12 PMOS divider.                                                                               | 65 |

| Figure 4.13 Circuit of protection                                                                       | 67 |

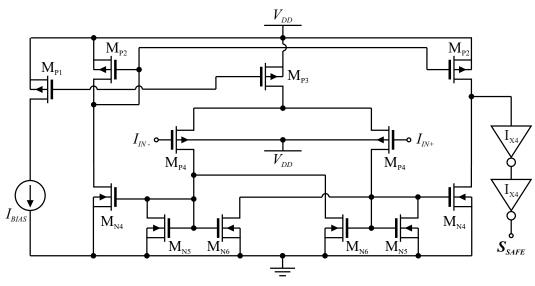

| Figure 4.14 Comparator topology.                                                                        |    |

| Figure 4.15 Bandgap voltage reference topology                                                          | 68 |

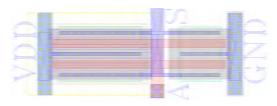

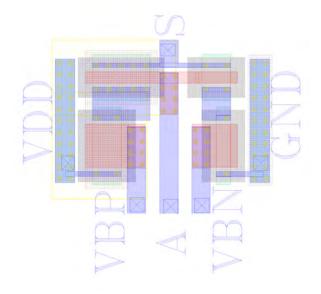

| Figure 4.16 MPP Reference Generator & Protection (150 $\mu$ m x 260 $\mu$ m)                            | 69 |

| Figure 4.17 Control & Drive scheme.                                                                     |    |

| Figure 4.18 Differential amplifier.                                                                     | 70 |

| Figure 4.19 VCO schematic.                                                                              | 71 |

| Figure 4.20 Non-overlapping driver schematic                                                            | 71 |

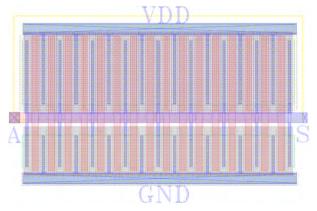

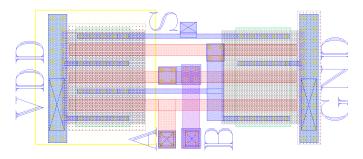

| Figure 4.21 Control & Driver layout (150 $\mu$ m x 140 $\mu$ m)                                         |    |

| Figure 4.22 Current Bias topology.                                                                      |    |

| Figure 4.23 Current Bias layout (35 $\mu$ m x 42 $\mu$ m).                                              |    |

| Figure 4.24 Digital blocks designed.                                                                    |    |

| Figure 4.25 Inverter DC Sweep Simulation for different Aspect Ratios                                    |    |

| Figure 4.26 INX1 (2.9 μm x 10.4 μm)                                                                     |    |

| Figure 4.27 INX2 (2.9 \( \mu \) x 10.4 \( \mu \))                                                       |    |

| Figure 4.28 INX4 (2.9 \(\mu m\) x 10.4 \(\mu m\)                                                        |    |

| Figure 4.29 INX8 (3.9 \( \mu \) x 10.4 \( \mu \))                                                       |    |

| Figure 4.30 INX64 (17.6 μm x 10.4 μm).                                                                  |    |

| Figure 4.31 ID (11.0 μm x 20.0 μm).                                                                     |    |

| Figure 4.32 IS (73.6 \(\mu\)m x 67.5 \(\mu\)m).                                                         |    |

| Figure 4.33 IC (36.5 \( \mu \) x 37.0 \( \mu \) m).                                                     |    |

| Figure 4.34 IC2 (5.5 \(\mu\)m x 7.6 \(\mu\)m)                                                           |    |

| Figure 4.35 ANX2 (4.9 $\mu m \times 10.4 \mu m$ ).                                                      |    |

| Figure 4.36 ORX4 (4.9 \(\mu m\) x 10.4 \(\mu m\)                                                        |    |

| Figure 4.37 ORX64 (20.9 μm x 10.4 μm)                                                                   |    |

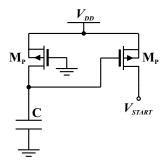

| Figure 4.38 Start-up topology.                                                                          |    |

| Figure 4.39 Start-up operation phases                                                                   |    |

| Figure 4.40 Start-up created by the PMOS transistors of the main converter                              | 81 |

| Figure 4.41 Start-up using the PMOS current path                                                        |    |

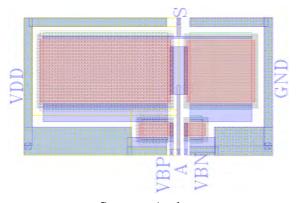

| Figure 4.42 Start-up layout (225.0 $\mu m$ x 320.0 $\mu m$ ).                                           |    |

| Figure 4.43 Start-up for the self-biased blocks.                                                        |    |

| Figure 4.44 Layout of the starting circuit (7.0 $\mu m \times 10.0 \mu m$ ).                            |    |

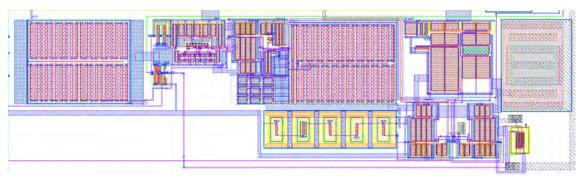

| Figure 4.45 Complete layout of the SC DC - DC Converter (300 $\mu$ m x 700 $\mu$ m)                     |    |

|                                                                                                         |    |

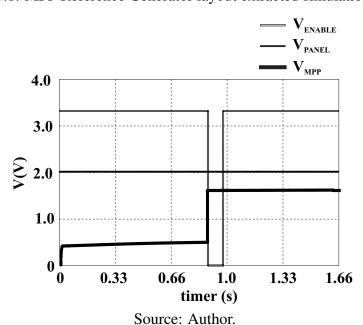

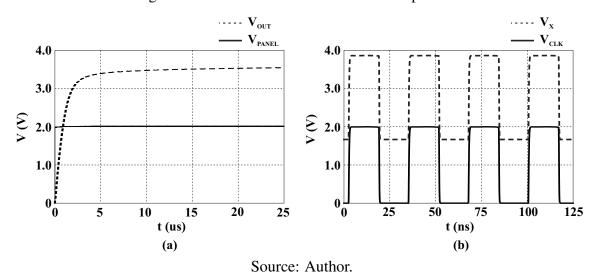

| Figure 5.1 MPP Reference Generator layout extracted simulation results.                                 |    |

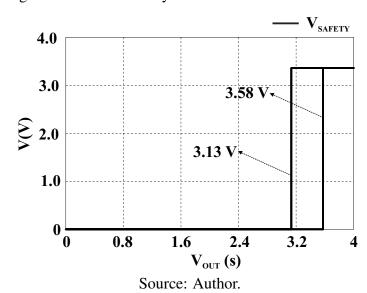

| Figure 5.2 Protection layout extracted simulation results.                                              |    |

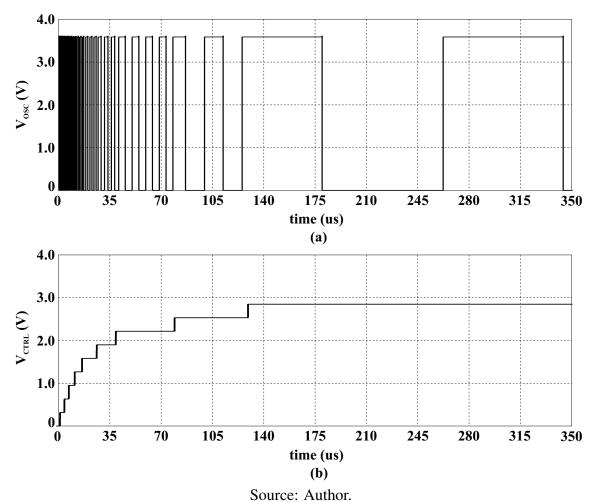

| Figure 5.3 Driver signal with respect to the error signal in time domain (a) Pulses (b) $V_{CTR}$       |    |

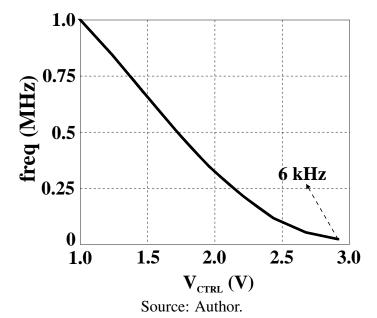

| Figure 5.4 Driver signal frequency with respect to the error voltage                                    |    |

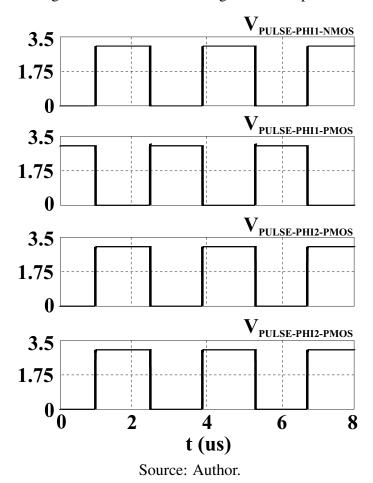

| Figure 5.5 Time-interleaved signals.                                                                    |    |

| Figure 5.6 The four drive signals of one phase.                                                         |    |

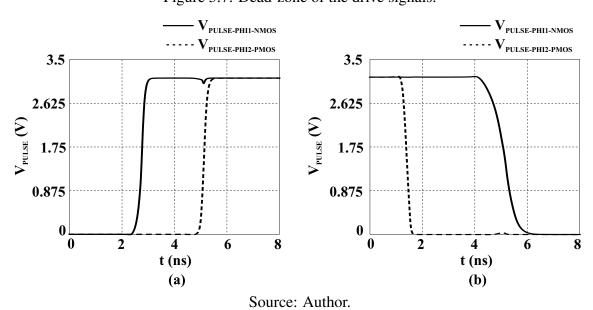

| Figure 5.7 Dead-zone of the drive signals                                                               |    |

| Figure 5.8 Simulation results of the start-up circuit                                                   | 90 |

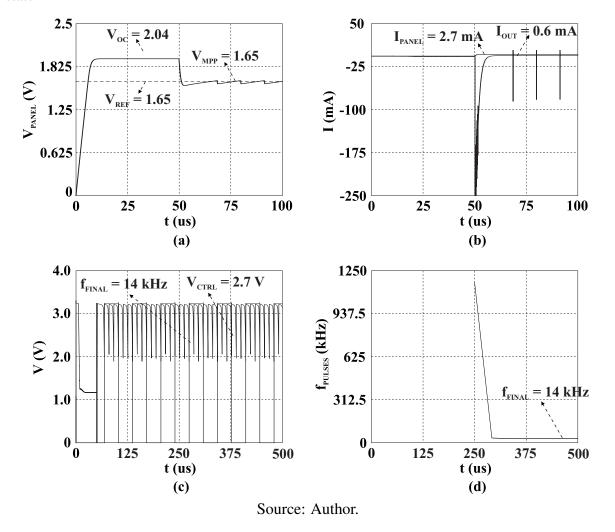

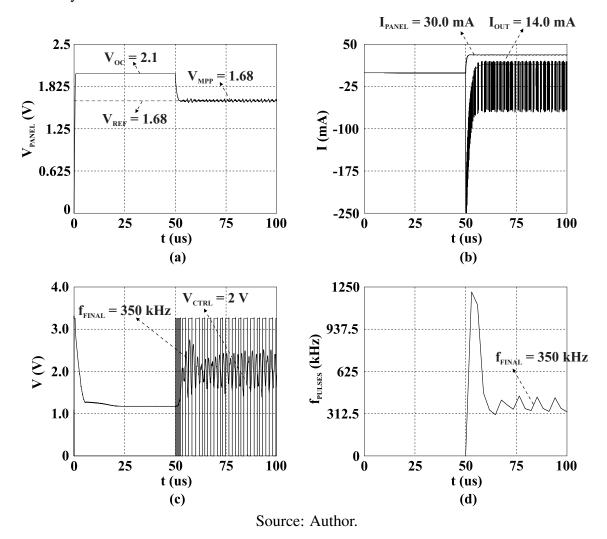

| Figure 5.9 Simulation Results, $I_{SC} = 3$ mA. (a) $V_{PANEL}$ response, (b) $I_{PANEL}$ and $I_{OUT}$ |    |

| responses, (c) $V_{CTRL}$ and $V_{PULSES}$ responses and (d) $I_{PANEL}$ and switching frequency        |    |

| response until steady-state                                                                             | 91 |

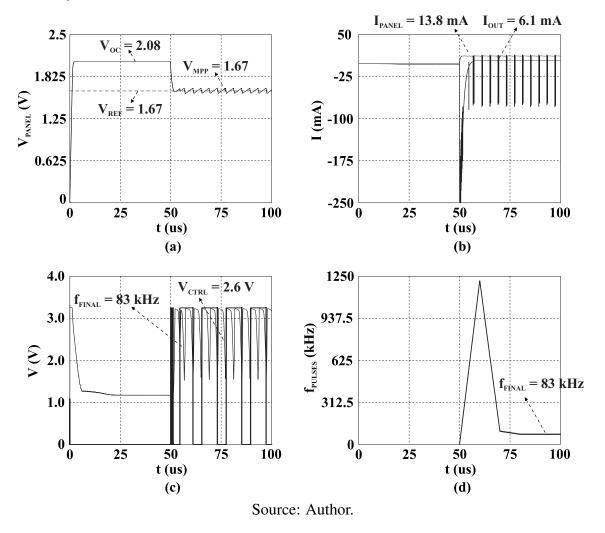

| respon     | Simulation Results, $I_{SC}$ = 15 mA. (a) $V_{PANEL}$ response, (b) $I_{PANEL}$ and $I_{OUT}$ ares, (c) $V_{CTRL}$ and $V_{PULSES}$ responses and (d) $I_{PANEL}$ and switching frequency                        | 02    |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| -          | nse until steady-state                                                                                                                                                                                           | 92    |

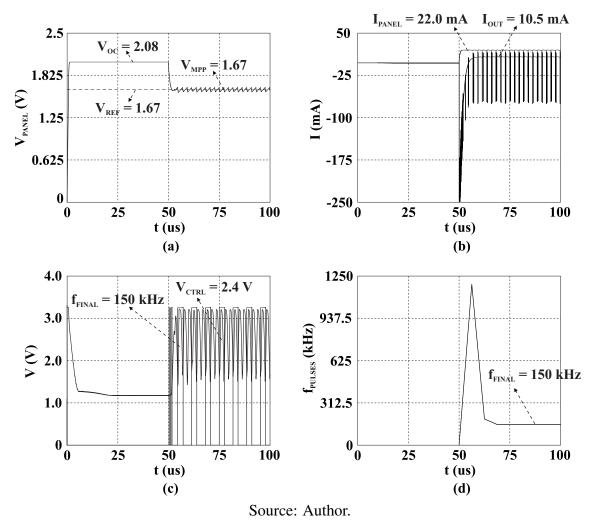

| respon     | Simulation Results, $I_{SC} = 25$ mA. (a) $V_{PANEL}$ response, (b) $I_{PANEL}$ and $I_{OUT}$ nses, (c) $V_{CTRL}$ and $V_{PULSES}$ responses and (d) $I_{PANEL}$ and switching frequency nse until steady-state | 93    |

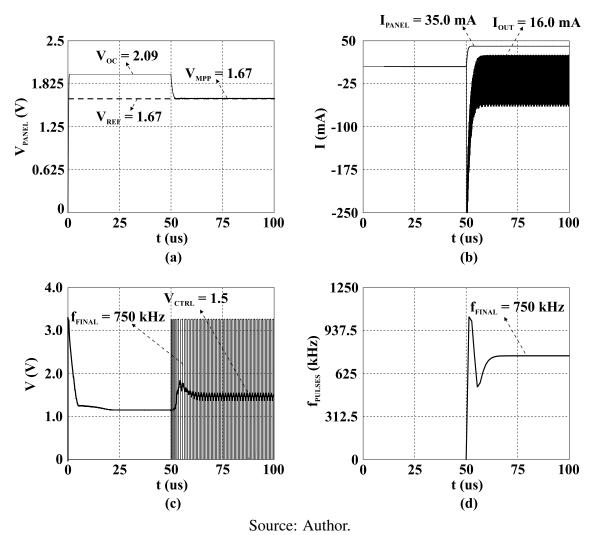

|            | Simulation Results, $I_{SC} = 35$ mA. (a) $V_{PANEL}$ response, (b) $I_{PANEL}$ and $I_{OUT}$                                                                                                                    | 93    |

| respon     | uses, (c) $V_{CTRL}$ and $V_{PULSES}$ responses and (d) $I_{PANEL}$ and switching frequency                                                                                                                      | 0.4   |

| 1          | nse until steady-state                                                                                                                                                                                           | 94    |

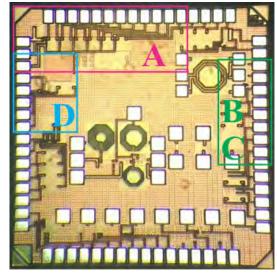

|            | Fabricated chip (2mm x 2mm).                                                                                                                                                                                     | 93    |

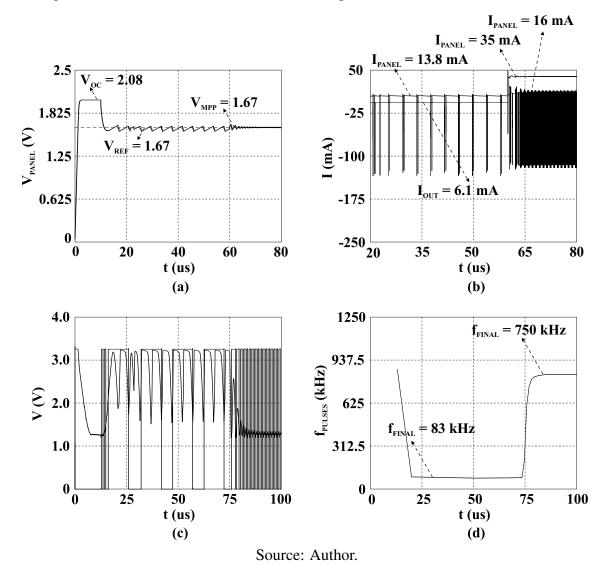

| _          | Simulation Results, $I_{SC} = 45$ mA. (a) $V_{PANEL}$ response, (b) $I_{PANEL}$ and $I_{OUT}$                                                                                                                    |       |

| _          | uses, (c) $V_{CTRL}$ and $V_{PULSES}$ responses and (d) $I_{PANEL}$ and switching frequency                                                                                                                      | 07    |

|            | nse until steady-state                                                                                                                                                                                           | 97    |

| _          | Simulation Results, irradiation step, from $I_{SC} = 45$ mA to $I_{SC} = 15$ mA                                                                                                                                  | 98    |

| _          | Simulation Results, signal of enable, due to timer and high output voltage                                                                                                                                       | 00    |

| 1          | tion.                                                                                                                                                                                                            |       |

|            | Efficiency vs. Input Power.                                                                                                                                                                                      |       |

| •          | ATP scheme.                                                                                                                                                                                                      |       |

| _          | PCB for tests.                                                                                                                                                                                                   |       |

| _          | PV panel, board and battery structure.                                                                                                                                                                           |       |

| _          | Current sense and signal terminal board.                                                                                                                                                                         | . 102 |

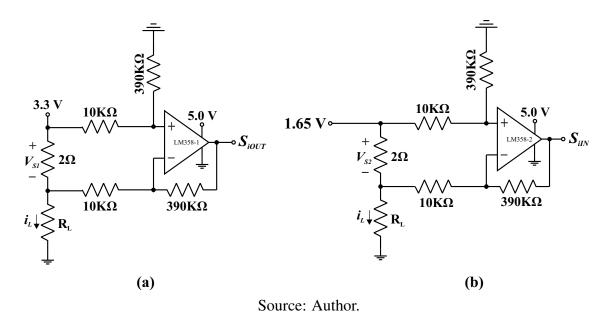

| _          | Schematic of the output (a) and input (b) sense amplifiers with the calibration                                                                                                                                  | 103   |

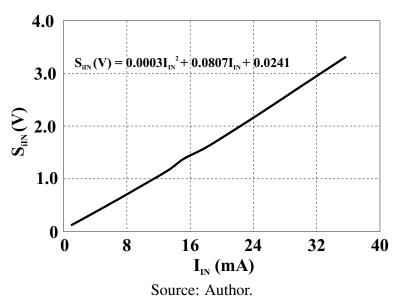

|            | Input current sense characteristic.                                                                                                                                                                              |       |

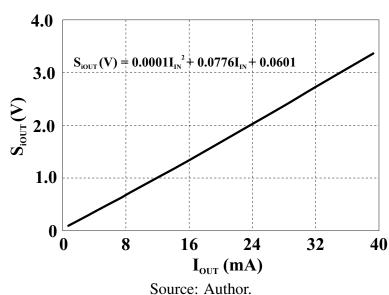

| _          | Output current sense characteristic.                                                                                                                                                                             |       |

| •          | Illuminance meter 510 01 of Yokogawa.                                                                                                                                                                            |       |

| •          | Arduino UNO.                                                                                                                                                                                                     |       |

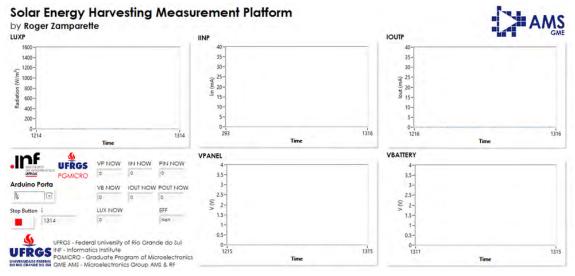

| _          | LabVIEW Interface.                                                                                                                                                                                               |       |

| _          | Complete ATP.                                                                                                                                                                                                    |       |

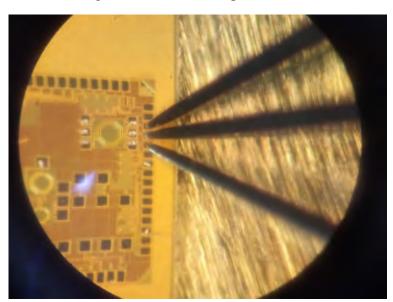

| _          | Die in the probe station.                                                                                                                                                                                        |       |

| _          | Probe station.                                                                                                                                                                                                   |       |

| •          | Complete setup test.                                                                                                                                                                                             |       |

| _          | Timer measurement result (a) Enable Pulse (b) Enable Pulse Inverted                                                                                                                                              |       |

|            | Bandgap measurement result.                                                                                                                                                                                      |       |

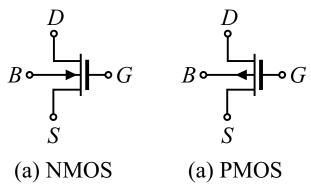

|            | NMOS transistor structure.                                                                                                                                                                                       |       |

|            | NMOS and PMOS transistors schematic symbol.                                                                                                                                                                      |       |

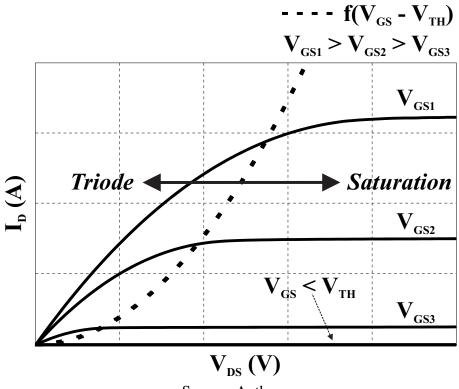

| -          | Current Behavior of MOS transistor.                                                                                                                                                                              |       |

| Figure A.4 | Capacitance across the MOS terminals.                                                                                                                                                                            | 118   |

| _          | $\mu_{n(p)}C_{OX}.$                                                                                                                                                                                              |       |

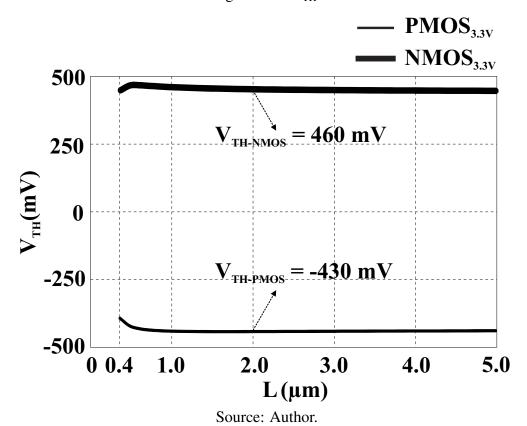

| Figure A.6 | V <sub>TH</sub>                                                                                                                                                                                                  | 120   |

| Figure C.1 | LabVIEW "code"                                                                                                                                                                                                   | . 123 |

# LIST OF TABLES

| Table 2.1 | Comparison of the energy harvesting sources                                     | 19  |

|-----------|---------------------------------------------------------------------------------|-----|

| Table 2.2 | Error and estimated parameters for each iteration for $S_2 = 200 \text{ W/m}^2$ | 33  |

|           | Comparison among MPPT Techniques                                                |     |

| Table 4.1 | Power Limits of the PV panel.                                                   | 59  |

|           | Timer sizing                                                                    |     |

|           | Op-amp sizing.                                                                  |     |

|           | S&H sizing and Divider.                                                         |     |

|           | Comparator sizing                                                               |     |

|           | Bandgap sizing.                                                                 |     |

|           | Ibias sizing                                                                    |     |

|           | Digital blocks sizes                                                            |     |

|           | Start-up sizing.                                                                |     |

|           | Starting block.                                                                 |     |

| Table 5.1 | List of Components.                                                             | 101 |

| Table 6.1 | Comparison among works                                                          | 112 |

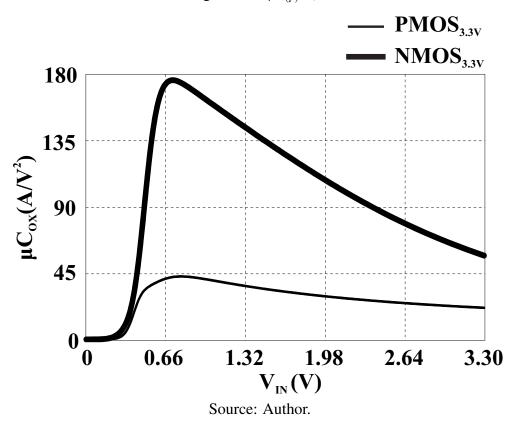

| Table A.1 | Conductivity of the Thick Oxide Transistors                                     | 118 |

|           | Channel-Length Modulation Parameter - $\Lambda_{NMOS3,3V}(V^{-1})$              |     |

|           | Channel-Length Modulation Parameter - $\Lambda_{PMOS3.3V}(V^{-1})$              |     |

#### LIST OF ABBREVIATIONS AND ACRONYMS

AC Alternate Current

CMOS Complementary Metal-Oxide-Silicon

CP Charge-Pump

CCM Continuous Conduction Mode

DC Direct Current

DCM Discontinuous Conduction Mode

EH Energy Harvesting

ESR Equivalent Series Resistance

FSL Fast-Switching Limit

IoT Internet of Things

MOS Metal-Oxide-Silicon

MOSFET Metal-Oxide-Silicon Field-Effect Transistor

MPP Maximum Power Point

MPPT Maximum Power Point Tracking

NMOS N-type Metal-Oxide-Silicon Field-Effect Transistor

PCB Printed Circuit Board

PMOS P-type Metal-Oxide-Silicon Field-Effect Transistor

PV Photovoltaic

RF Radio Frequency

SC Switched Capacitor

SSL Slow-Switching Limit

TEG Thermoelectric Generator

ULP Ultra-Low Power

VCO Voltage - Controlled Oscillator

WSN Wireless Sensor Network

# **CONTENTS**

| 1 INTRODUCTION                                     | 14  |

|----------------------------------------------------|-----|

| 1.1 Objectives                                     | 17  |

| 1.2 Organization                                   |     |

| 2 ENERGY HARVESTING                                | 19  |

| 2.1 Photovoltaic Energy                            | 20  |

| 2.2 PV Cell Electrical Model                       | 22  |

| 2.3 Selected PV Panel                              |     |

| 2.4 PV Panel Electrical Characterization           |     |

| 2.5 PV Panel Parameters Extraction                 |     |

| 2.5.1 PV Parameters Extraction Tool                |     |

| 2.6 Maximum Power Point Tracking - MPPT Techniques |     |

| 3 DC-DC CONVERTERS                                 |     |

| 3.1 Linear DC-DC Conversion                        |     |

| 3.2 Switched DC-DC Conversion                      |     |

| 3.3 Inductor Based DC-DC Conversion                |     |

| 3.3.1 The Boost Converter                          | 42  |

| 3.4 Capacitor Based DC-DC Conversion               |     |

| 3.4.1 Switched Capacitor Losses                    |     |

| 3.4.2 R <sub>SSL</sub> and R <sub>FSL</sub>        |     |

| 4 ARCHITECTURE AND DESIGN METHODOLOGY              |     |

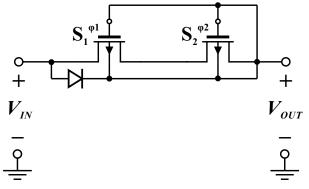

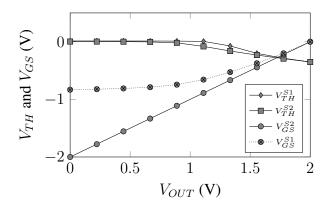

| 4.1 1-to-2 Switched - Capacitor Core               |     |

| 4.2 MPP Reference Generator & Protection           |     |

| 4.2.1 MPP Reference Generator                      |     |

| 4.2.2 Protection                                   |     |

| 4.3 Control & Driver                               |     |

| 4.4 Digital Blocks & Current Bias                  |     |

| 4.4.1 Current Bias                                 |     |

| 4.4.2 Digital Blocks                               |     |

| 4.5 Start-up                                       |     |

| 4.6 Starting the Blocks                            |     |

| 4.7 Complete Layout                                |     |

| 5 RESULTS                                          |     |

| 5.1 Simulation Results                             |     |

| 5.1.1 MPP Reference Generator                      |     |

| 5.1.2 Protection                                   |     |

| 5.1.3 Driver                                       |     |

| 5.1.4 Start-up                                     |     |

| 5.1.5 Complete SC DC - DC Converter                |     |

| 5.2 Circuit Fabrication                            |     |

| 5.3 Experimental Results                           |     |

| 5.3.1 Test Setup                                   |     |

| 5.3.2 Automatic Test Platform                      |     |

| 5.3.2.1 Test Board, PV panel and Battery           |     |

| 5.3.2.2 Current Sense Amplifiers                   |     |

| 5.3.2.3 Illuminance meter 510 01 of Yokogawa       |     |

| 5.3.2.4 Arduino UNO                                |     |

| 5.3.2.5 LabVIEW Interface                          |     |

| 5.3.2.6 Complete ATP                               | 106 |

| 5.3.3 Bare Die Setup Test                             | 106                      |

|-------------------------------------------------------|--------------------------|

| 5.3.4 Measurement Results                             | 107                      |

| 5.3.5 Timer, Bias and Bandgap                         | 108                      |

| 5.4 Other Results                                     | 110                      |

| 6 CONCLUSIONS                                         | 111                      |

| REFERENCES                                            | 113                      |

| APPENDIX A — MOSFET TRANSISTOR & PARAMETER EXTRACTION | 115                      |

| APPENDIX A — MOSFET TRANSISTOR & PARAMETER EXTRACTION | 115                      |

| A.1 Quadratic Model                                   |                          |

|                                                       | 116                      |

| A.1 Quadratic Model                                   | 116<br>117               |

| A.1 Quadratic Model                                   | 116<br>117<br>118        |

| A.1 Quadratic Model                                   | 116<br>117<br>118<br>121 |

#### 1 INTRODUCTION

Internet is one of the most important and powerful tools developed by the human race. It molded our society, education, business and connected the world. In 2010, there were 12.5 billion devices connected to the internet, what is a number higher than the global population. This absurd amount is responsible for letting the Internet in continual evolution and the Internet of Things (IoT) is the next step in this path. (EVANS, 2011)

Internet of Things is the concept of connecting all possible devices to the Internet. Cisco IBSG of 2011 predicts that will be 50 billion of connected devices by 2020. This huge amount and variety of devices will generate an amount of data traffic never seen before. This "Big Data" is a challenge to be faced together by academy, governments, business, and industry. (EVANS, 2011)

Wearables, implantables, medical devices and local sensors are part of the IoT world. These kind of devices face their own challenges, the main one is Autonomy. The desirable is that the gadgets could last as much as possible without the need of a battery recharge. It brought the necessity of Ultra-Low Power (ULP) devices that can sense, process data and communicate consuming the minimum possible.

These two challenges: Big Data and Autonomy are trend topics in academy and industry. The most important international conferences and journals receive a significant amount of works focused on those problems. They face these problems at different levels: applications, systems, architectures, blocks and circuits.

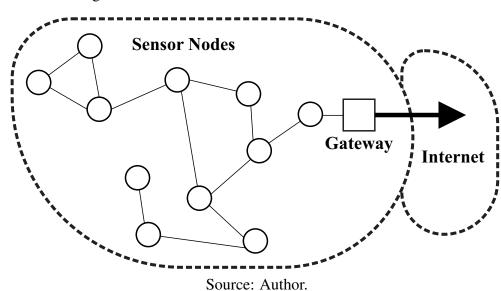

Internet of Things and Wireless Sensor Networks (WSN) were born together. Also called motes or smart dust, WSN is the concept of building networks with smart autonomous compact-device sensor units to obtain different kinds of information. Fig. 1.1 shows a generic scheme of a WSN. The sensor nodes must be capable of collect, receive and transmit information consuming the minimum possible of energy. They create a communication path to the network Gateway that deliveries the collected information to the internet. (ASHTON, 2009)

There are countless challenges and trade-offs in the design of a smart node but, two of the critical ones are the operation lifetime and device compactness. An important object that impacts in those aspects, lifetime x compactness, is the battery. Battery density have been increasing and the trade-off limit between sensor nodes operation time and devices size have been pushed towards together, but this is still an object of investigation. (NOORDEN, 2014)

Not only the reducing of consumption is a way to increase autonomy. It is possible, also, to use some Energy Harvesting (EH) strategy. There exists a considerable amount of potential

sources of energy that can be collected by a compact transducer, *e.g.* Thermoelectric Generators (TEGs), Photovoltaic (PV) cells, Ambient RF Signals and Piezoelectric Materials. (SOYATA; COPELAND; HEINZELMAN, 2016)

The MICA2, Fig. 1.2, is an example of a commercial sensor node that has a large variety of integrated sensors in one platform with a multi-channel radio transceiver. This platform includes an Atmel ATmega 128L low power microcontroller and its energy is supplied by two standard alkaline AA batteries that deliver from 2.7 to 3.3 V and supply enough energy for one year of operation using sleep mode. (CROSSBOW TECHNOLOGY, 2010)

Figure 1.1: Wireless Sensor Network: Generic Scheme.

Alkaline AA battery capacity is in the range of 1800 to 2600 mAh of charge or 2700 to 3900 mWh of energy, meaning that one year of active sensor operation with two batteries results in a circuit consumption around 0.6 to 0.9 mW. So if an energy harvesting power source could supply an average power around 0.3 to 0.5 mW every day the sensor node autonomy of MICA2 would be doubled.

The extra power could be harvested from many kinds of environmental sources but usually available high density energy sources are 'light' (using PV cells) and 'heat' (using TEGs). Among the available environmental sources of energy, 'light' is the one that offers higher power density (output electrical power per area or volume) with relatively high output voltage levels, especially for outdoor applications where sunlight can reach PV panels all over the day.

PV cells and TEGs are non-ideal sources of energy, so, the maximum power transfer theorem must be taken into account if one wants to collect the maximum available energy.

Although, it is not possible to achieve the MPP by a direct connection between source and load. A DC-DC converter between the power supply and an energy storage element (battery, capacitor or super-capacitor) overcome this problem and a post DC-DC converter is used to regulate the output voltage. Fig. 1.3 shows a generic scheme described for a PV panel source.

Figure 1.2: MICA2.

Source: (CROSSBOW TECHNOLOGY, 2010)

Usually boost step-up converters based on inductors are employed for this job, like the works (IM et al., 2012) and (BANDYOPADHYAY; CHANDRAKASAN, 2012). But, some newly proposed topologies are based on Switched-Capacitor (SC) strategy for this purpose, like in (LIU et al., 2016) and (LIU; SáNCHEZ-SINENCIO, 2015), due to the lower intrinsic losses of these kinds of converters. (SANDERS et al., 2013)

PV Panel

Harvester

Storage

Element

Source: Author.

Figure 1.3: Generic scheme of a Energy Harvesting DC-DC Conversion.

#### 1.1 Objectives

In this context, this work proposes an integrated CMOS Switched-Capacitor (SC) DC-DC Converter for Photovoltaic (PV) Energy Harvesting (EH) using a Maximum Power Point Tracking (MPPT) strategy aiming to be employed in Sensor Nodes (SN) at outdoor applications to increase its autonomy. Specifically, the main objectives of this work are to:

#### 1. Energy Harvesting

- Make a review about Energy Harvesting sources;

- Make a review about PV cells;

- Choose and characterize a small PV panel;

#### 2. DC - DC Conversion

- Make a review about DC DC conversion:

- Make a review about SC DC DC converters;

- Propose a SC DC DC converter architecture suitable for the chosen PV panel and battery;

- Design and send for fabrication the proposed converter;

#### 3. Simulation & Measurements

- Obtain and analyze simulation results of the complete DC DC converter and internal blocks;

- Design, fabricate and montage of the Printed Circuit Board (PCB) for the chip tests;

- Design of an automatic measurement setup;

- Perform and analyze measurements results of the complete DC DC converter and internal blocks:

#### 1.2 Organization

The work is organized as follows: Chapter 2 presents a review of EH sources like TEGs, RF, piezoelectric and a broad look at PV cells. Chapter 3 gives the basis about DC - DC conversion with a focus on the modeling and behavior of the SC DC - DC ones. The proposed architecture and the design methodology are in Chapter 4. Simulation and some measurement results are presented in Chapter 5. Conclusions and considerations are the focus of Chapter 6.

Finally, the parameters extraction of the used CMOS technology and some tools used in the work are in the Appendix.

#### 2 ENERGY HARVESTING

Energy harvesting happens when a transducer intercepts a "force" carried by a wave or matter and converts into electricity. These waves can be classified in mechanical or electromagnetic, depending on its nature. Wind, sound, and vibration are examples of mechanical waves. Light, microwave, and X-rays are examples of electromagnetic. (SOYATA; COPELAND; HEINZELMAN, 2016)

Each form of energy has its transducer capable of converting it into electricity. Wind turbines convert energy transported by the wind, Thermoelectric generators (TEGs) the heat, Photovoltaic (PV) cells the energy present in photons and piezoelectric materials the energy from vibration. (SOYATA; COPELAND; HEINZELMAN, 2016)

An engineer may want to choose one of these kinds of energies to harvest and use it in an application. The availability of the power source and the transducer characteristics defines if the energy can be collected efficiently or not, this outlines the pros and cons that must be taken into account for the intended application.

The most common energy harvesting sources are ambient RF, piezoelectric, that can be by vibration or push buttons, thermal and solar. Each of these energies has their characteristics and particularities. Tab. 2.1 presents a comparison among them. (KIM et al., 2014)

Table 2.1: Comparison of the energy harvesting sources.

|                   | PV Energy                                          | Thermal Energy           | Ambient RF Energy                    | Piezoelec                | tric Energy                                              |

|-------------------|----------------------------------------------------|--------------------------|--------------------------------------|--------------------------|----------------------------------------------------------|

|                   | 1 v Energy                                         | Thermal Energy           | Ambient Kr Energy                    | Vibration                | Push Button                                              |

| Power<br>Density  | $100 \text{ mW/cm}^2$                              | $60 \ \mu \text{W/cm}^2$ | $0.0002$ - 1 $\mu$ W/cm <sup>2</sup> | $200  \mu \text{W/cm}^3$ | 50 μJ/N                                                  |

| Output            | 0.5 V (single Si cell)<br>1.0 V (single a-Si vell) | -                        | 3 - 4 V (Open circuit)               | 10 - 25 V                | 100 - 10000 V                                            |

| Available<br>Time | Day time (4 - 8 Hrs)                               | Continuous               | Continuous                           | Activity dependent       | Activity dependent                                       |

| Weight            | 5 to 10 g                                          | 10 to 20 g               | 2 to 3 g                             | 2 to 10 g                | 1 to 2 g                                                 |

| Pros              | - Large energy                                     | - Always available       | - Ant. integrated                    | - Well developed tech    | - Well developed tech                                    |

| Pros              | - Well developed tech                              |                          | - Widely available                   | - Light weight           | <ul><li>Light weight</li><li>Small volume</li></ul>      |

| Cons              | - Need large area                                  | - Need large area        | - Distance dependent                 | - Need large area        | - Highly variable output                                 |

| Colls             | - Non-continuous                                   | - Low power              | - Available source                   | - Variable output        | - Low conversion<br>efficiency (high<br>volt./low amps.) |

|                   | - Orientation issue                                | - Rigid and brittle      |                                      |                          |                                                          |

Source: (KIM et al., 2014).

The ambient RF energy is still a technology in development. It presumes a considerable distance between the transmitter and the receiver, >5 m, so a small amount of energy can be

collected and, alone, it is not capable of supplying the most of the applications. Like the TEGs, it is possible to harvest ambient RF energy all day.

Piezoelectric energy is a well-developed technology, but depends on the activity of the application, since, mechanical force must be applied continuously. Also, a little amount of energy can be harvest due to power density and critical electrical characteristics, high voltage and low current, what is not suitable for a high-efficiency voltage conversion. (KIM et al., 2014)

Thermoelectric Generators (TEGs) is a well-developed technology. In wearable applications, where the temperature gradient is small, <2 K, the power density, and the delivered voltage are small, at dozens of  $\mu$ W and mV respectively. A good point is that is possible to harvest the energy all day.

Photovoltaic energy is one of the most well-developed technologies of all the energy harvesters. At outdoor applications, where a high intensity of light reaches the panel, it can achieve a power density of dozens of  $mW/cm^2$ . At indoor applications, this density reduces to  $\mu W/cm^2$ . But, in both, outdoor and indoor application, the output voltage are suitable to be converted, at least hundreds of mV. The drawback is that the energy is not available always and intensities vary along the time.

The high power density, dozens of mW, and relatively high output voltage, hundreds of millivolts, are excellent characteristics that make the solar energy to be elected as the best option for outdoor applications and a good one for indoor applications. A better insight in this technology will be presented in the next section.

#### 2.1 Photovoltaic Energy

PV cell is the current technology responsible for converting the energy of photons into electricity. They can be arranged in different ways to construct panels or modules to obtain more output current or voltage and, consequently, more power. Fig 2.1 shows a image of a 10 cm x 10 cm PV cell. (BOXWELL, 2017)

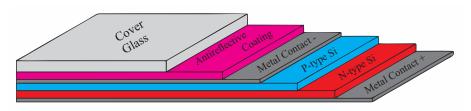

The construction of a PV cell is based on a p-n semiconductor junction. It transforms energy through, first, absorption of light, generating either electron-hole pairs, two, separation of charge carriers of opposite types and, three, separate extraction of those carriers to an external circuit. Fig 2.2 shows the construction structure of a PV cell.

There are plenty of ways to construct the semiconductor part of the PV cell. But, the technologies that dominate, due to the cost of manufacturing, are the polycrystalline and monocrystalline silicon. The difference of construction is illustrated in the Fig.2.3. The monocrys-

talline technology creates a homogeneous silicon crystal, that achieves a conversion efficiency in the range of 14 to 21%. The polycrystalline is a fusion of different silicon crystals and achieves a conversion efficiency in the range of 13 to 16.5%. Polycrystalline PV cell is cheaper to be made, due to the simplest process of fabrication, so, the trade-off between cost and efficiency depends on the application. (SOLAR, 2017)

Figure 2.1: 10 cm x 10 cm PV cell.

Source: http://www.sunlinkpv.com.

Figure 2.2: PV cell construction.

Source: Author.

Independent of the technology used in the construction, the p-n junction is intrinsic, and it firmly commands the electrical behavior of the PV cell. The next section will treat about the power response of a PV cell.

Figure 2.3: Crystal structure of monocrystalline and polycrystalline Photovoltaic cells.

#### 2.2 PV Cell Electrical Model

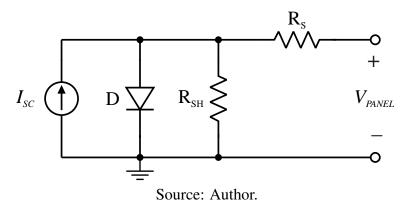

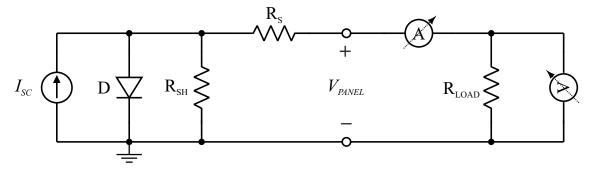

The Fig. 2.2 shows the structure of a PV cell. It consists of a p-n junction with metal contacts to access the semiconductors and some dielectrics to enhance the performance. This structure is translated to a electric model as a diode with a injection of electrons due to light incidence and some ohmic losses due to construction and contacts. Fig 2.4 shows the electrical model of a PV cell.

Figure 2.4: Electrical model of a PV cell.

In Fig. 2.4, D is the intrinsic diode,  $I_{SC}$  is the injected current due to the incidence of photons,  $R_{SH}$  represents the ohmic losses due to construction of the PV cell and the  $R_{S}$  is the equivalent series resistance of the contacts to external connection.

It is possible to write the relationship between the output current,  $I_{PANEL}$ , and the internal currents of the PV cell, Eq. 2.1.

$$I_{PH} = I_D + I_{SH} + I_{PANEL}$$

(2.1)

The current behavior of a diode is well known, and it is described by Eq. 2.2.  $I_D$  is the current in the diode,  $I_{SAT}$  is the current in the diode when it is reverse biased,  $V_D$  is the voltage across the diode, n is the ideality factor, and  $V_T$  is the thermal voltage.

$$I_D = I_{SAT} \left( e^{\frac{V_D}{nV_T}} - 1 \right) \tag{2.2}$$

It is possible to relate  $V_D$  and  $V_{PANEL}$  with  $I_{PANEL}$  through Eq. 2.3 and use it to relate  $V_{PANEL}$  and  $I_{PANEL}$  with  $I_{SH}$ , Eq. 2.4

$$V_D = V_{PANEL} + R_S I_{PANEL} \tag{2.3}$$

$$I_{SH} = \frac{V_{PANEL} + R_S I_{PANEL}}{R_{SH}} \tag{2.4}$$

Replacing Eq. 2.2 and Eq. 2.4 into Eq. 2.1, an equation that represents the behavior of the PV cell is achieved, Eq. 2.5.

$$I_{PANEL} = I_{PH} - I_{SAT} \left( e^{\frac{V_{PANEL} + R_S I_{PANEL}}{nV_T}} - 1 \right) - \frac{V_{PANEL} + R_S I_{PANEL}}{R_{SH}}$$

(2.5)

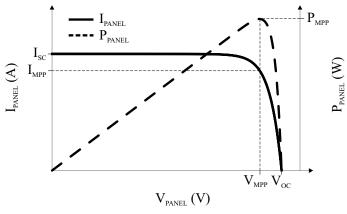

The relationships  $I_{PANEL}$  vs.  $V_{PANEL}$  and  $P_{PANEL}$  vs.  $V_{PANEL}$  are presented in Fig. 2.5, based on Eq. 2.5.

Fig. 2.5 shows that the current  $I_{PANEL}$  behaves as a current source for low voltage levels of  $V_{PANEL}$ . For  $V_{PANEL}$  equals zero (short circuit), the current is maximum,  $I_{SC}$ , and the current drops quickly as the  $V_{PANEL}$  increases until the current goes to zero at  $V_{OC}$  (open circuit). The power of the panel has a point of maximum power delivery (MPP),  $V_{MPP}$  and  $I_{MPP}$ , what is natural for a non-ideal source of energy.

The injected current depends strongly on the intensity of light, S [W/m²], and slightly of the temperature T [K]. Eq. 2.6 shows this relationship, where  $I_{SC}(T_O)$  is the injected current measured at a temperature  $T_O$  and at a irradiation  $S_O$ ,  $\alpha$  is a second order temperature coefficient, T is the temperature and S is the irradiation.

Figure 2.5: I-V and P-V PV cell characteristic.

$$I_{PH}(S,T) = [I_{PH}(S_O, T_O) + \alpha T(T - T_O)] \frac{S}{S_O}$$

(2.6)

The saturation current strongly depends on the temperature and, because of it, the  $V_{OC}$ . The dependence of the  $I_{SAT}$  with temperature is given by Eq. 2.7.

$$I_{SAT} = I_S \left(\frac{T}{T_O}\right)^3 e^{\left[\frac{qEg}{nk}\left(\frac{1}{T_O} - \frac{1}{T}\right)\right]}$$

(2.7)

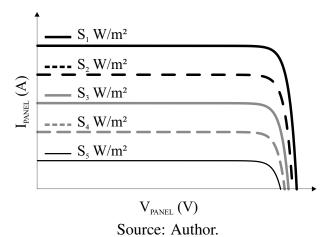

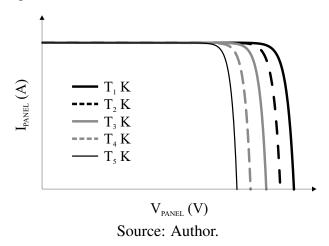

Eq. 2.6 and Eq. 2.7 relate the behavior of the PV cell with irradiation and temperature. Fig. 2.6, Fig. 2.7, Fig. 2.8 and Fig. 2.9 present these relationships reflected on the  $I_{SC}$  and  $V_{OC}$ , where  $S_1 > S_2 > S_3 > S_4$  and  $T_1 < T_2 < T_3 < T_4$ .

Fig. 2.6 shows that the injected current,  $I_{SC}$ , increases linearly with the irradiation, but the open-circuit voltage,  $V_{OC}$ , change slightly it.

Figure 2.6: I-V PV cell characteristic for various S.

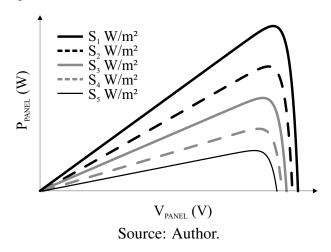

The overall delivered power,  $P_{PANEL}$ , also increases with irradiation, as presented in Fig. 2.7.

Fig. 2.8 shows that the injected current,  $I_{SC}$ , increases slightly with the temperature, but the open-circuit voltage,  $V_{OC}$ , changes inversely and strongly with it.

The maximum delivered power,  $P_{MPP}$ , increases linearly inversely with temperature, as presented in Fig. 2.10.

Figure 2.7: P-V PV cell characteristic for various S.

Figure 2.8: I-V PV cell characteristic for various T.

Eq. 2.5 describes the behavior of voltage and current of a PV cell. It is an equation non-linear and transcendental, so, to fully characterize a PV panel, diode behavior, shunt and series resistance values, it is necessary to make some simplifications or to use a computational method. In this work, a computational method was used to this task. But, first, a PV cell was

chosen in the market and measurements in different irradiation situations were performed. The next section will treat about it.

$\underbrace{\sum_{\substack{T_1 \\ K}\\ T_2 \\ K}}_{T_3 \\ K} \underbrace{-\cdots \\ T_4 \\ K}_{T_5 \\ K}$   $\underbrace{V_{PANEL}(V)}_{Source: Author.}$

Figure 2.9: P-V PV cell characteristic for various T.

#### 2.3 Selected PV Panel

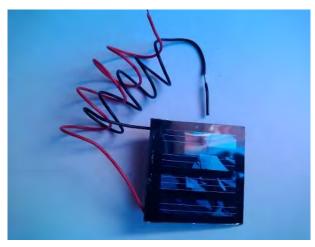

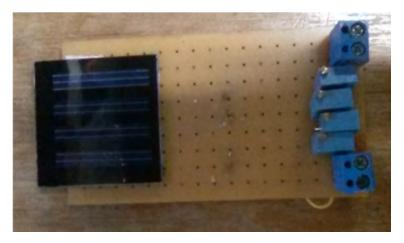

A designer of a Wireless Sensor Node aims to increase the autonomy of the node while keeping the device compactness and small price. So, it is natural to look for a small size PV panel. Fig. 2.10 shows the KS-M4030, a small dimension and light weight polycrystalline solar panel, 3.0 x 3.0 cm<sup>2</sup> and 3.7g respectively, that can deliver up to 60 mW of power at outdoor applications. It is manufactured by China Solar LTD.

The presented PV panel is cheap, small and easy to find in Brazil, so it was the chosen for the application. It is necessary to obtain its electrical characteristics to design the DC - DC harvester properly.

Figure 2.10: Selected PV panel.

Figure 2.11: Schematic of the setup test for PV panel characterization.

Source: Author.

#### 2.4 PV Panel Electrical Characterization

The setup test presented in Fig. 2.11 was implemented to characterize the PV panel. The measurements were performed at three irradiation levels,  $S_1$  = 1000 W/m<sub>2</sub>,  $S_2$  = 200 W/m<sub>2</sub> and  $S_3$  = 50 W/m<sub>2</sub>. These irradiation levels were measured using the illuminance meter 510 01 of Yokogawa. For each irradiation level,  $V_{PANEL}$  and  $I_{PANEL}$  was measured at different loads,  $R_{LOAD}$ .

Fig. 2.12 shows the implemented board to perform the measurements.

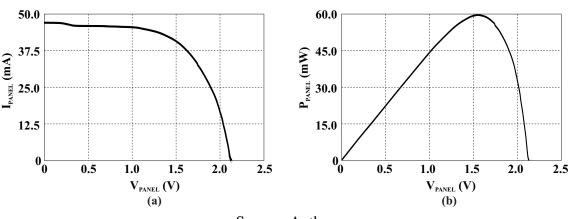

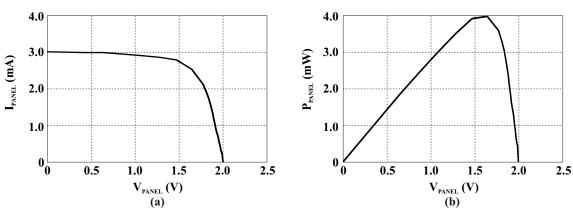

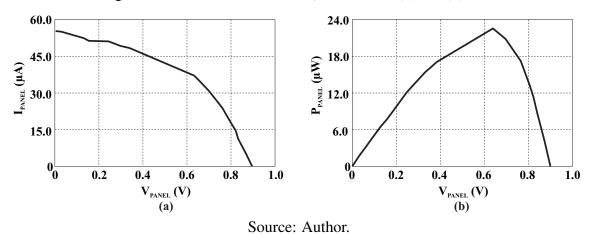

The Fig. 2.13 presents the measurements for  $S_1 = 1000 \text{ W/m}_2$  performed at the midday of a summer day. Fig. 2.14 presents the measurements for  $S_2 = 200 \text{ W/m}_2$  performed at the late afternoon of a summer day and Fig. 2.15 presents the measurements for  $S_3 = 50 \text{ W/m}_2$  performed at a closed room artificially illuminated.

Figure 2.12: Characterization PV panel board.

An analysis of the results shown a high dynamic range of PV panel power with respect to the irradiation. At the midday of a summer day, with the maximum possible irradiation intensity, the maximum power delivered by the PV panel is 60 mW, while the same PV cell delivers a maximum power of 22  $\mu$ W at indoor. Also, at late afternoon, almost night, the PV cell delivers a maximum power of 4 mW.

Figure 2.13: Measurements for  $S_1 = 1000 \text{ W/m}_2$  (a) I-V (b) P-V.

Source: Author.

The focus of this work are in outdoor applications, so the power limits considered were from 4 to 60 mW.

Once the measurements were performed, the behavior of the intrinsic diode D and the values of  $R_{SH}$  and  $R_{S}$  can be obtained through a computational method, that will be presented in the next section.

Figure 2.14: Measurements for  $S_2 = 200 \text{ W/m}_2$  (a) I-V (b) P-V.

Figure 2.15: Measurements for  $S_3 = 50 \text{ W/m}_2$  (a) I-V (b) P-V.

#### 2.5 PV Panel Parameters Extraction

The Fig. 2.4 shows the schematic model of a PV Panel. It shows the parameters to be extracted. They are  $R_{SH}$ ,  $R_{S}$  and the parameters of the diode D, n and  $I_{SAT}$ . So, it is necessary to extract parameters that makes Eq. 2.5 true for each measured pair  $V_{PANEL}$  and  $I_{PANEL}$ . From Eq. 2.5, it is possible to write the error equation Eq. 2.8.

$$Error(i) = I_{PH} - I_{SAT} \left( e^{\frac{V_{PANEL}(i) + R_{S}I_{PANEL}(i)}{nV_{T}}} - 1 \right) - \frac{V_{PANEL}(i) + R_{S}I_{PANEL}(i)}{R_{SH}} - I_{PANEL}(i)$$

(2.8)

The objective is to estimate the parameters that minimize the error of all the measured points to the expected curve. For it, the Error(i) is calculated for each measured pair  $V_{PANEL}(i)$

and I<sub>PANEL</sub>(i). Then, the sum of the absolute value of each error is minimized, Eq. 2.9.

$$S_{Errors} = \sum_{i=1}^{N} |Error(i)|$$

(2.9)

With the equation to be minimized defined, the second step is to use or create a tool to minimize it.

#### 2.5.1 PV Parameters Extraction Tool

Excel © was the tool chosen for this task. The supplement Solver was used to minimize Eq. 2.9. It can minimize a specific spreadsheet cell varying other defined cells by the user. It is possible choose among three algorithms of optimization, Evolutionary, LP Simplex and GRG Non-Linear. LP Simplex is better to optimize linear problems, Evolutionary to high derivative curves and GRG Non Linear to non-linear low derivative curves. The behavior of a PV panel is non-linear and the curves are soft, so the GRG Non-Linear was the algorithm chosen to the task. Fig. 2.16 presents the spreadsheet designed to perform the parameters extraction.

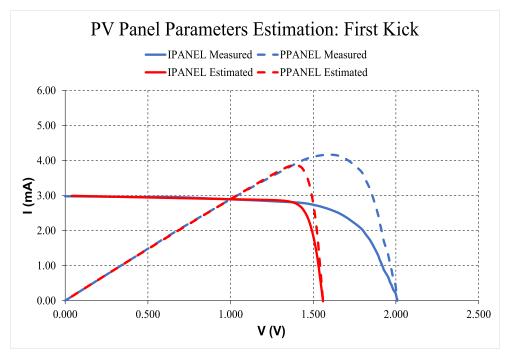

To present the functionality of the tool, Fig. 2.17 compares the measured curve for  $S_2$  and the estimated curve based on a first kick for the parameters. Once the  $I_{SC}$  is a parameter measured, the error for small values of  $V_{PANEL}$  is little. But, the error gets higher as the value of  $V_{PANEL}$  increases.

Then, One iteration was performed using the designed spreadsheet, and the error reduced for higher values of  $V_{PANEL}$ , but it is still far from the measured points, Fig. 2.18.

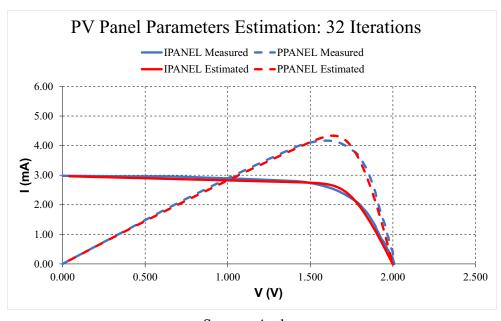

Finally, a target of  $S_{Errors}$  of less than 0.005 was set and after 32 iterations, the error got small enough and the estimated curve got closer of the measurements, Fig. 2.19.

Tab. 2.2 shows the errors and the parameters calculated for the three presented cases. With the parameters extracted, it is possible to generate a accurate model o the selected PV panel to be used in simulations of the converter.

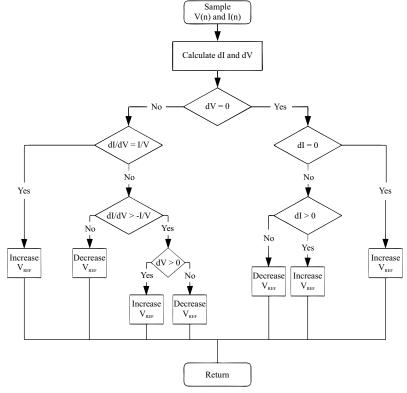

The measurements shown that the PV panel presents a Maximum Point of Power (MPP) delivery. It is desirable to extract the maximum power available in the PV panel, so a strategy of MPPT must be employed. The next section will talk about this subject.

Figure 2.16: Spreadsheet for parameters extraction PV panel.

| Rown   Residence   Residence | <u>.</u>                                                                                                                       | Fitting Spreadsheet |          |               |          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|---------------------|----------|---------------|----------|

| T   303   Unknown   T   305   Unknown   T    |                                                                                                                                |                     |          |               |          |

| T   303   Unknown   T   305   Unknown   T    | UFRGS " III AMS                                                                                                                | k                   | 1.38E-23 | Isc           | 0.00298  |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | HAMIVEDGIDADE EEDEDAL                                                                                                          | a                   | 1.60E-19 |               |          |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                |                     | 303      |               |          |

| Sum of Errors   986.036                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                |                     |          | Unknown       |          |

| Sum of Errors   986.036                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ( B I IV )                                                                                                                     | Isat (10^-20)       | 1.00     | Rsн           | 10000.00 |

| Sum of Errors   986.036                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Erro = $I_{CC} - I_{CAT} \left( \frac{R_{SIPANEL} + V_{PANEL}}{nV_{T}} - 1 \right) - \frac{V_{PANEL}}{nV_{PANEL}} - I_{PANEL}$ | 'n                  | 1.50     |               |          |

| Measured   Fire   Panel   Pa | R <sub>SH</sub>                                                                                                                | Rs                  | 10.00    |               |          |

| Measured   Fire   VPAMEL (V)   IPAMEL (A)   Erro   ABS Erro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                |                     |          | Sum of Errors |          |

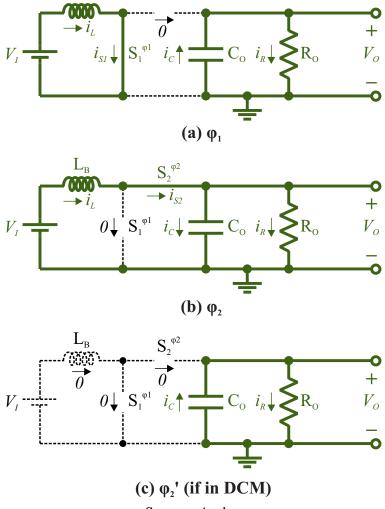

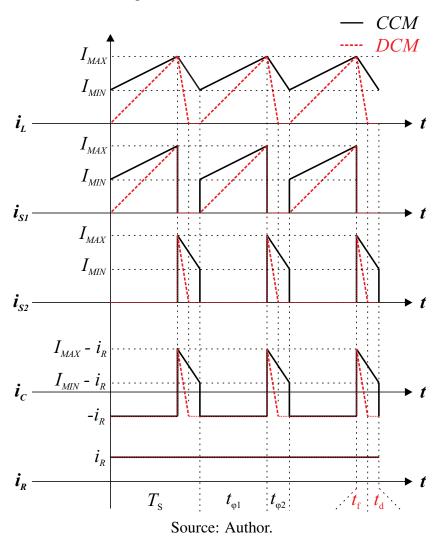

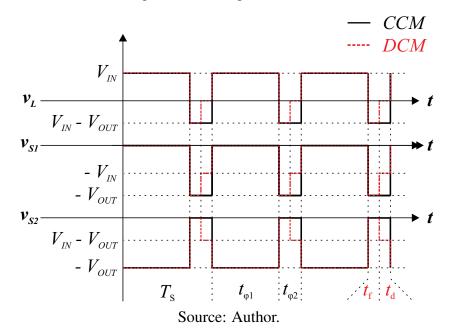

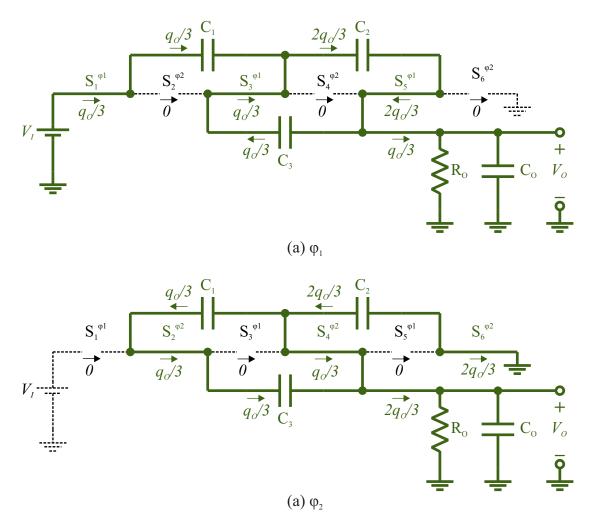

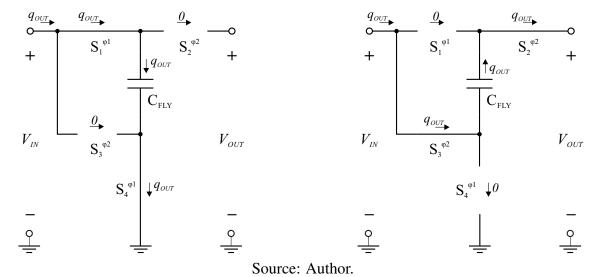

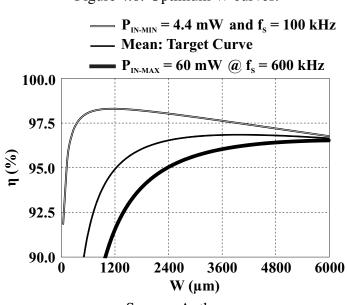

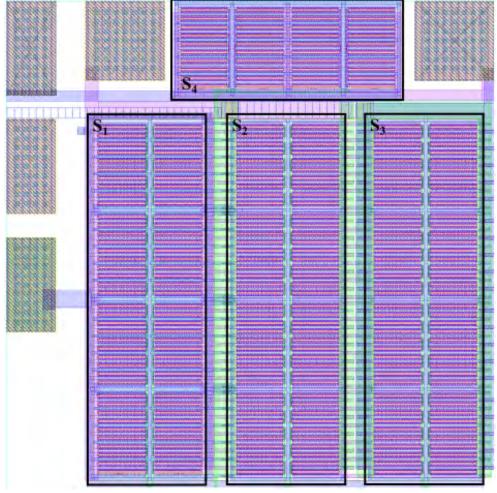

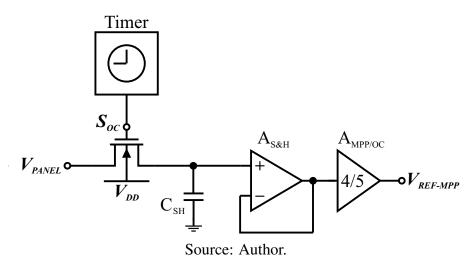

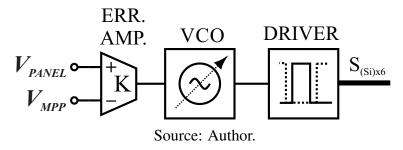

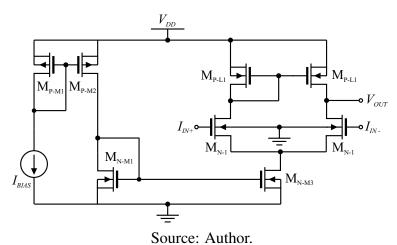

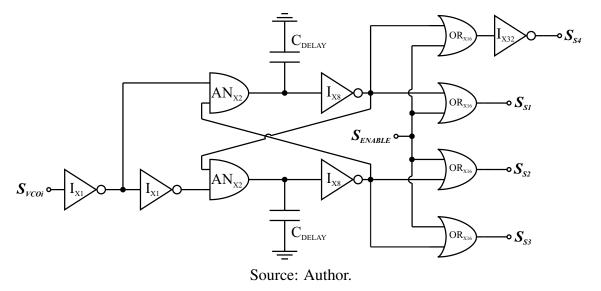

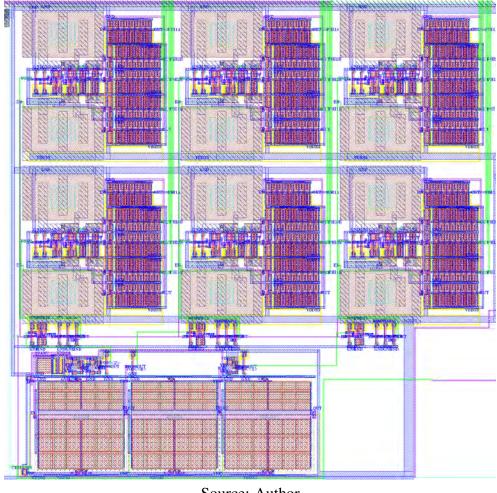

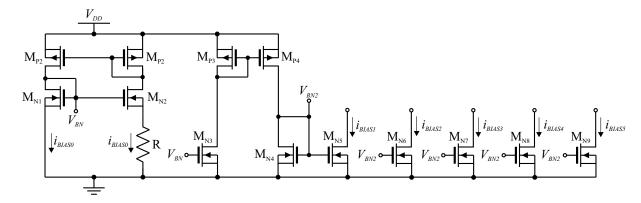

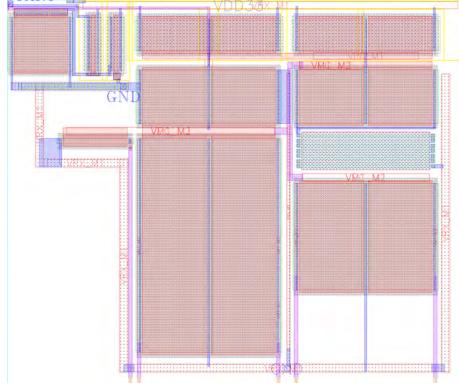

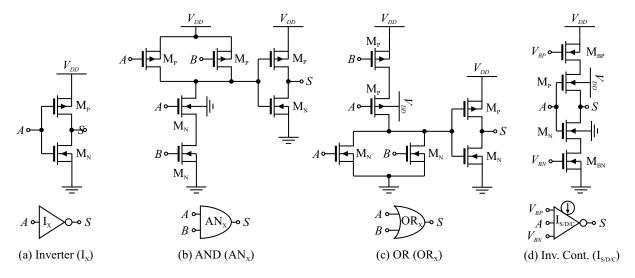

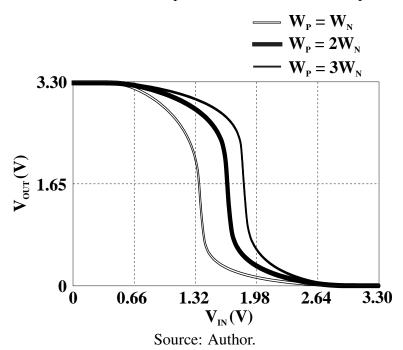

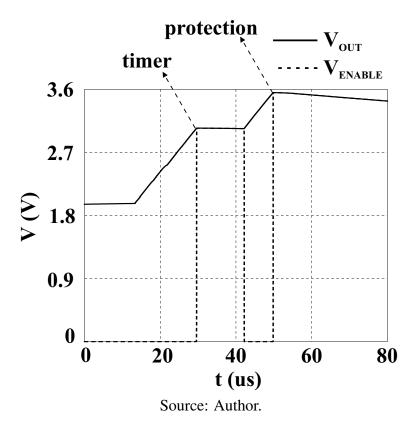

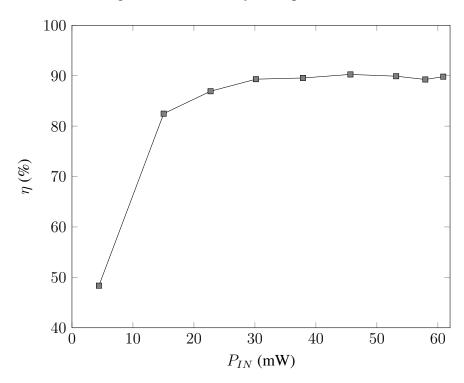

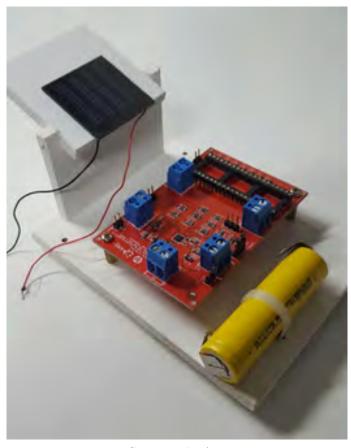

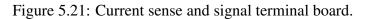

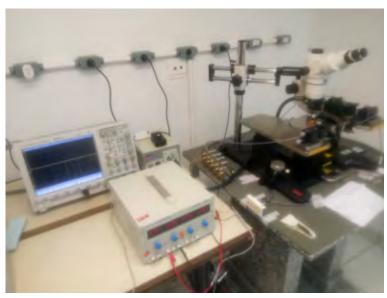

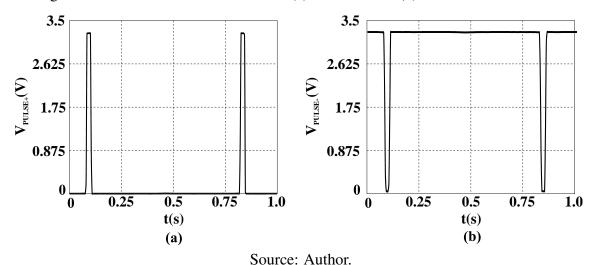

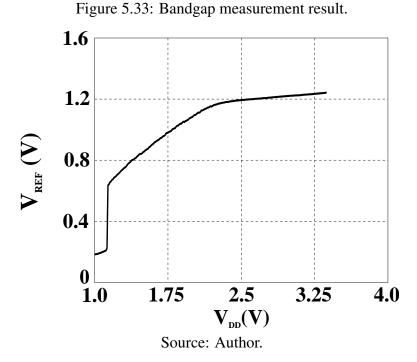

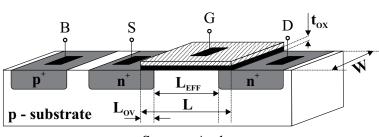

| VPANEL (V)         IPANEL(A)         Erro         ABS Erro           0.000         0.0030         0.000000         0.000000           0.218         0.0030         -0.000012         0.000012           0.421         0.0030         -0.000022         0.000022           0.635         0.0030         -0.000026         0.000026           1.064         0.0029         -0.00006         0.000006           1.288         0.0028         0.000017         0.000017           1.477         0.0028         -0.00049         0.000409           1.850         0.0025         -0.037064         0.037064           1.821         0.0001         -0.929145         0.929145           1.846         0.0017         -4.537695         4.537695           1.867         0.0015         -7.408720         7.408720           1.893         0.0013         -13.534175         13.534175           1.991         0.0012         -16.141344         16.141344           1.927         0.0009         -29.037869         29.037869           1.956         0.0005         -71.491412         71.491412           1.966         0.0005         -74.491412         71.491412                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                |                     |          |               |          |