# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

## ANDERSON LUIZ SARTOR

# Adaptive and Polymorphic VLIW Processor to Dynamically Balance Performance, Energy Consumption, and Fault Tolerance

Thesis presented in partial fulfillment of the requirements for the degree of Doctor of Computer Science

Advisor: Prof. Dr. Antonio Carlos Schneider Beck

#### CIP — CATALOGING-IN-PUBLICATION

Sartor, Anderson Luiz

Adaptive and Polymorphic VLIW Processor to Dynamically Balance Performance, Energy Consumption, and Fault Tolerance / Anderson Luiz Sartor. – Porto Alegre: PPGC da UFRGS, 2018.

167 f.: il.

Thesis (Ph.D.) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação, Porto Alegre, BR–RS, 2018. Advisor: Antonio Carlos Schneider Beck.

1. Adaptive processor. 2. Fault tolerance. 3. Energy consumption. 4. Performance. 5. VLIW. I. Beck, Antonio Carlos Schneider. II. Título.

# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Rui Vicente Oppermann Vice-Reitora: Prof<sup>a</sup>. Jane Fraga Tutikian

Pró-Reitor de Pós-Graduação: Prof. Celso Giannetti Loureiro Chaves Diretora do Instituto de Informática: Prof<sup>a</sup>. Carla Maria Dal Sasso Freitas

Coordenador do PPGC: Prof. João Luiz Dihl Comba

Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

#### **ABSTRACT**

Performance is no longer the only optimization goal when designing a new processor. Reducing energy consumption is also mandatory: while most of the embedded devices are heavily dependent on battery power, General-Purpose Processors (GPPs) are being pulled back by the limits of Thermal Design Power (TDP). Moreover, due to technology scaling, soft error rate (i.e., transient faults) has been increasing in modern processors, which affects the reliability of both space and ground-level systems. In addition, most traditional homogeneous and heterogeneous processors have a fixed design, which limits its runtime adaptability. Therefore, they are not able to cope with the changing application behavior when one considers the axes of fault tolerance, performance, and energy consumption altogether.

In this context, we propose two processor designs that are able to trade-off these three axes according to the application at hand and system requirements. Both designs rely on an instruction duplication with rollback mechanism that can detect and correct errors and a power gating module to reduce the energy consumption of the functional units. The former design, called *adaptive processor*, uses thresholds defined at design time to allow runtime adaptation of the application's execution and controls the application's Instruction-Level Parallelism (ILP) to create more slots for duplication or power gating. The latter design (*polymorphic processor*) takes the former one step further by dynamically reconfiguring the hardware and evaluating different processor configurations for each application, and it also exploits the available pipelanes to maximize the number of applications that are executed concurrently.

For the adaptive processor using an energy-oriented configuration, it is possible, on average, to reduce energy consumption by 37.2% with an overhead of only 8.2% in performance, while maintaining low levels of failure rate, when compared to a fault-tolerant design. For the polymorphic processor, results show that the dynamic reconfiguration of the processor is able to efficiently match the hardware to the behavior of the application, according to the requirements of the designer, achieving 94.88% of the result of an oracle processor when the trade-off between the three axes is considered. On the other hand, the best static configuration only achieves 28.24% of the oracle's result.

**Keywords:** Adaptive processor. fault tolerance. energy consumption. performance. VLIW.

# Processador VLIW adaptativo e polimórfico para equilibrar de forma dinâmica o desempenho, o consumo de energia e a tolerância a falhas

## **RESUMO**

Ao se projetar um novo processador, o desempenho não é mais o único objetivo de otimização. Reduzir o consumo de energia também é essencial, pois, enquanto a maior parte dos dispositivos embarcados depende fortemente de bateria, os processadores de propósito geral (GPPs) são restringidos pelos limites da energia térmica de projeto (TDP - thermal design power). Além disso, devido à evolução da tecnologia, a taxa de falhas transientes tem aumentado nos processadores modernos, o que afeta a confiabilidade de sistemas tanto no espaço quanto no nível do mar. Adicionalmente, a maioria dos processadores homogêneos e heterogêneos tem um design fixo, o que limita a adaptação em tempo de execução. Nesse cenário, nós propomos dois designs de processadores que são capazes de realizar o trade-off entre esses eixos de acordo com a aplicação alvo e os requisitos do sistema. Ambos designs baseiam-se em um mecanismo de duplicação de instruções com rollback que detecta e corrige falhas, um módulo de power gating para reduzir o consumo de energia das unidades funcionais. O primeiro é chamado de processador adaptativo e usa thresholds, definidos em tempo de projeto, para adaptar a execução da aplicação. Adicionalmente, ele controla o ILP da aplicação para criar mais oportunidade de duplicação e de power gating. O segundo design é chamado processador polimórfico e ele avalia (em tempo de execução) a melhor configuração de hardware a ser usada para cada aplicação. Ele também explora o hardware disponível para maximizar o número de aplicações que são executadas em paralelo. Para a versão adaptativa usando uma configuração orientada a otimização de energia, é possível, em média, economizar 37,2% de energia com um overhead de apenas 8,2% em performance, mantendo baixos níveis de defeito, quando comparado a um design tolerante a falhas. Para a versão polimórfica, os resultados mostram que a reconfiguração dinâmica do processador é capaz de adaptar eficientemente o hardware ao comportamento da aplicação, de acordo com os requisitos especificados pelo designer, chegando a 94.88% do resultado de um processador oráculo quando o trade-off entre os três eixos é considerado. Por outro lado, a melhor configuração estática apenas atinge 28.24% do resultado do oráculo.

**Palavras-chave:** processador adaptativo, tolerância a falhas, consumo de energia, desempenho, VLIW.

#### LIST OF ABBREVIATIONS AND ACRONYMS

**ABFT** Algorithm-Based Fault Tolerance.

**ACE** Architecturally Correct Execution.

**ADPCM** Adaptive Differential Pulse-Code Modulation.

**AFRV** Acceptable Failure Rate Variation.

**ALU** Arithmetic Logic Unit.

**ASIC** Application-Specific Integrated Circuit.

**AVF** Architectural Vulnerability Factor.

BB Basic Block.

**BBHT** Basic Block History Table.

CFG Control Flow Graph.

**CMOS** Complementary Metal–Oxide–Semiconductor.

**CPU** Central Processing Unit.

**DCT** Discrete Cosine Transform.

**DFT** Discrete Fourier Transform.

**DMR** Dual Modular Redundancy.

**DVFS** Dynamic Voltage and Frequency Scaling.

**DVS** Dynamic Voltage Scaling.

**DWC** Duplication With Comparison.

**ECC** Error Correction Code.

**EDFP** Energy-Delay-Failure Product.

**EDP** Energy-Delay Product.

FIFO First-In-First-Out.

**FPGA** Field-Programmable Gate Array.

FU Functional Unit.

GCC GNU Compiler Collection.

**GPP** General-Purpose Processor.

**HPC** High-Performance Computing.

ILP Instruction-Level Parallelism.

**IPC** Instructions Per Cycle.

**ISA** Instruction Set Architecture.

LANSCE Los Alamos Neutron Science Center.

**LUDCMP** LU Decomposition.

**LUT** Look-Up Table.

**MCCP** Multiple Clustered Core Processor.

**MITF** Mean Instructions to Failure.

MPI Message Passing Interface.

**MWPUETF** Mean Work Per Unit of Energy to Failure.

**MWTF** Mean Work to Failure.

NASA National Aeronautics and Space Administration.

NMR N-modular Redundancy.

NOP No-Operation.

OoO Out-of-Order.

**OpenMP** Open Multi Processing.

**PC** Program Counter.

**PG** Power Gating.

PID Process ID.

**PPI** Parallel Programming Interface.

Pthreads POSIX threads.

**RAW** Read After Write.

**RMT** Redundant Multithreading.

**ROB** Re-order Buffer.

RTL Register-Transfer Level.

**SEE** Single-event effect.

**SET** Single-Event Transient.

**SEU** Single-Event Upset.

**SRAM** Static Random Access Memory.

TCL Tool Command Language.

**TDP** Thermal Design Power.

**TID** Total Ionizing Dose.

TLP Thread-Level Paralellism.

TMR Triple Modular Redundancy.

**TSH** Tricriteria Scheduling Heuristics.

**VHDL** VHSIC Hardware Description Language.

VLIW Very Long Instruction Word.

# LIST OF FIGURES

| Figure 1.1 High-level Overview of Common Optimization Techniques                     | 20    |

|--------------------------------------------------------------------------------------|-------|

| Figure 2.1 Hardware-based Replication with Rollback for Superscalar Processors       | 25    |

| Figure 2.2 Triplication of the Combinational Logic with a Stand-by Module            | 26    |

| Figure 2.3 Traditional Out-of-order Compared to the DIVA Approach                    |       |

| Figure 2.4 Aaron Scheduling Example                                                  |       |

| Figure 2.5 Power Gating Header Transistor                                            |       |

| Figure 2.6 Key Intervals for the Power Gating Technique                              |       |

| Figure 2.7 Methodology Flow of the Compiler-directed Power Gating                    |       |

| Figure 2.8 Example of Control Flow Graph for a Given Functional Unit                 |       |

| Figure 2.9 Multithreaded Application Behavior Regarding Communication                |       |

| Figure 2.10 Evaluated Cluster Configurations                                         |       |

| 11gaie 2.10 Evaluated Cluster Configurations                                         | 15    |

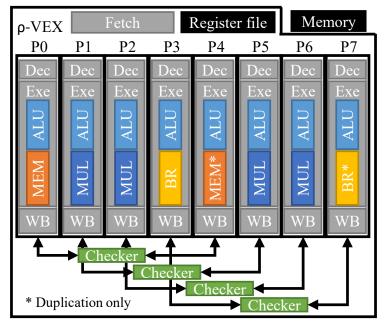

| Figure 3.1 Fault Tolerance Implementation of the $\rho$ -VEX Processor               | 48    |

| Figure 3.2 Full Duplication Configuration for the 4-issue $\rho$ -VEX Processor      |       |

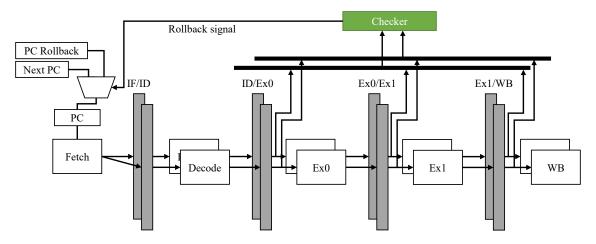

| Figure 3.3 Rollback Mechanism                                                        | 49    |

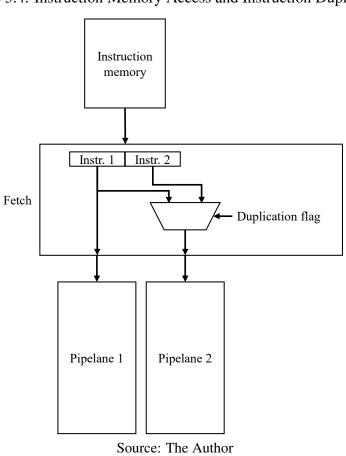

| Figure 3.4 Instruction Memory Access and Instruction Duplication                     | 51    |

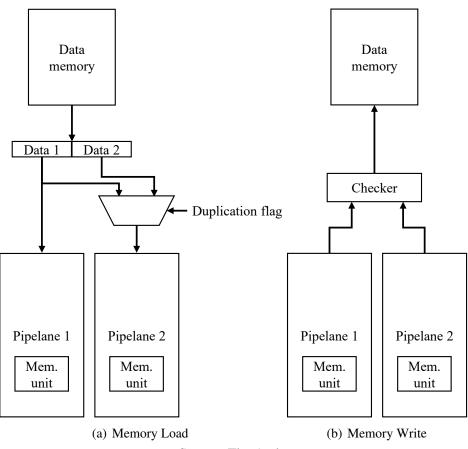

| Figure 3.5 Data Memory Access and Instruction Duplication                            |       |

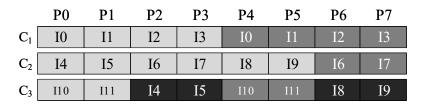

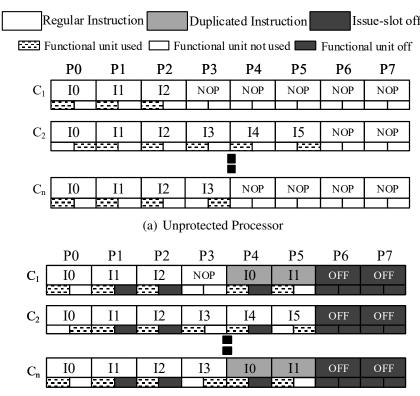

| Figure 3.6 Code Execution Example                                                    |       |

| Figure 3.7 Temporal and Spatial Duplication Execution Example                        |       |

| Figure 3.8 Temporal and Spatial Duplication Core Overview                            |       |

| Figure 3.9 Basic Block Execution Example                                             |       |

| Figure 3.10 Spatial Duplication with PG and ILP Control                              |       |

|                                                                                      |       |

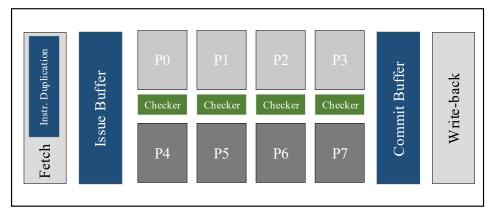

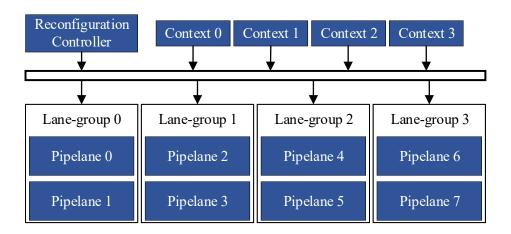

| Figure 4.1 Static $\rho$ -VEX organization (4-issue)                                 |       |

| Figure 4.2 Interconnection Between Register Contexts and Processor Pipelanes Con-    |       |

| trolled by the Reconfiguration Controller                                            |       |

| Figure 4.3 Dynamic $\rho$ -VEX Schematic                                             |       |

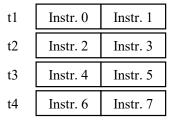

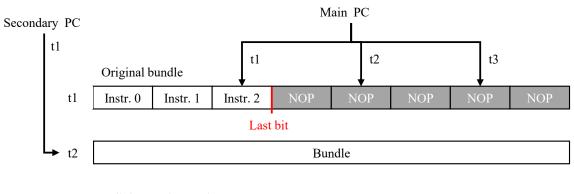

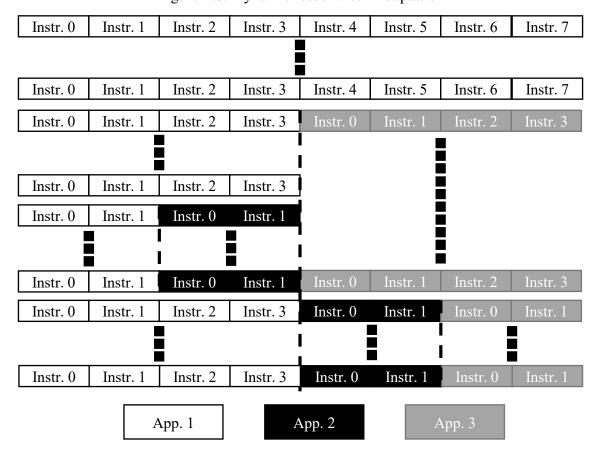

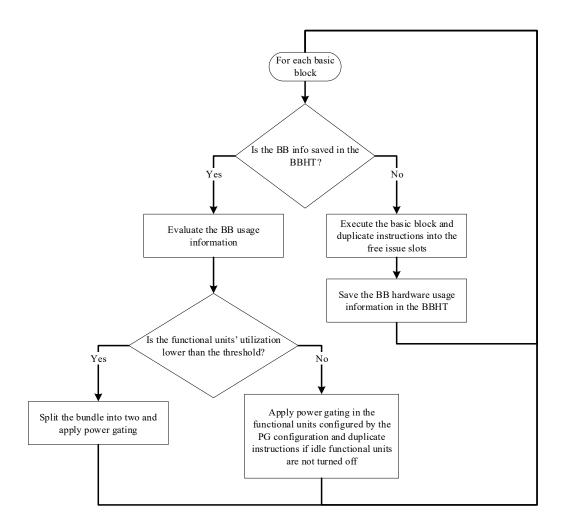

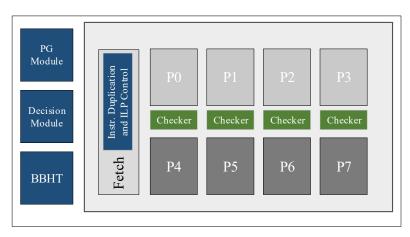

| Figure 4.4 Example of Bundle that Cannot be Split Using the Generic Binary Scheme    |       |

| Figure 4.5 Instruction Split Example                                                 |       |

| Figure 4.6 Dynamic Issue-width Adaptation                                            | 65    |

| Figure 4.7 Adaptive Processor Overview                                               |       |

| Figure 4.8 Spatial Duplication with ILP Control                                      | 67    |

| Figure 4.9 Adaptive Processor's Execution Flow                                       | 68    |

| Figure 4.10 Overview of the Processor with Fault Tolerance, Energy Optimization,     |       |

| and Performance Management Mechanisms                                                | 69    |

| Figure 4.11 Polymorphic Processor Overview                                           | 71    |

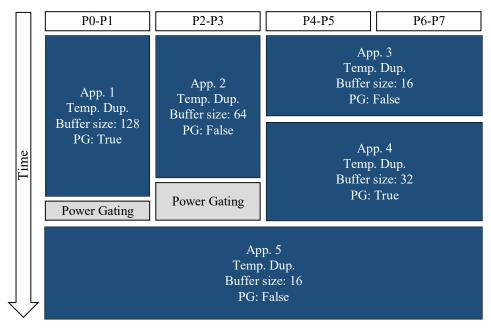

| Figure 4.12 Application Scheduling Example                                           |       |

| Figure 5.1 Fault Injection Flow                                                      | 84    |

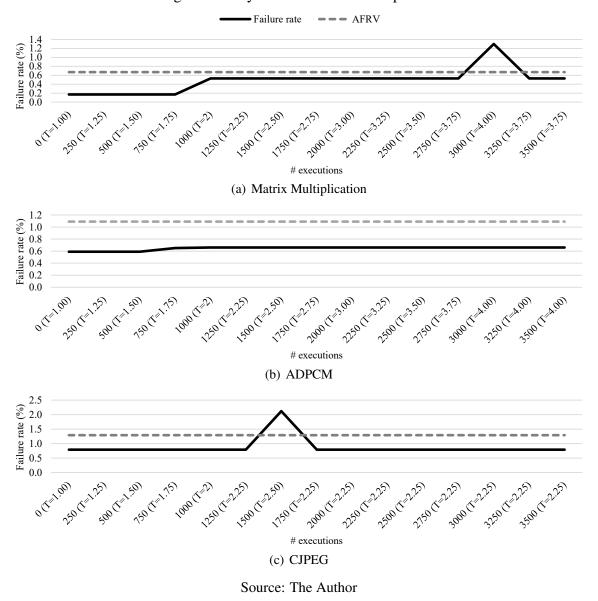

| Figure 5.2 Failure Rate Behavior as more Faults are Injected (Unprotected Processor) |       |

| rigure 3.2 Tundre Rute Benavior as more rutats are injected (emprotected ricessor)   | , 0 , |

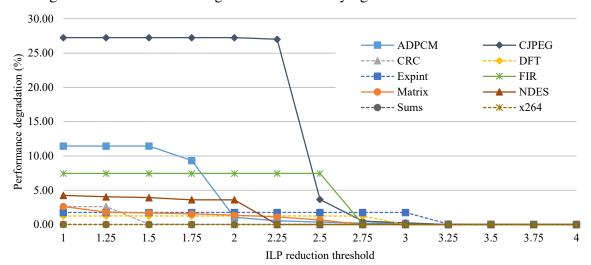

| Figure 6.1 Performance Degradation when Varying the ILP Reduction Threshold          | 99    |

| Figure 6.2 Spatial Duplication with ILP Control Normalized to the Unprotected        |       |

| Version                                                                              | 100   |

| Figure 6.3 Dynamic Threshold Adaptation                                              |       |

| Figure 6.4 Performance Improvement and Failure Rate Variation for the Dynamic        |       |

| Threshold Approach when Compared to the Threshold=1                                  | 103   |

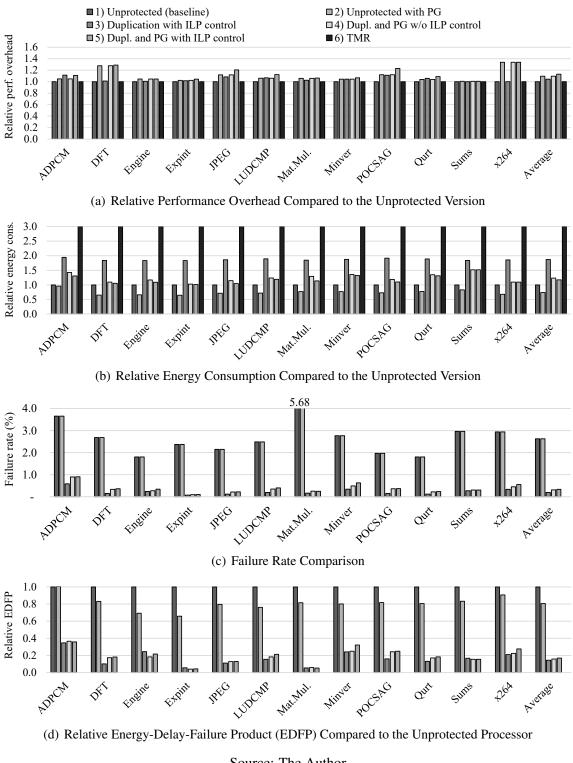

| Figure 6.5 Performance, Energy Overhead, Failure Rate, and Energy-Delay-Failu | re  |

|-------------------------------------------------------------------------------|-----|

| Product (EDFP) Comparison                                                     | 108 |

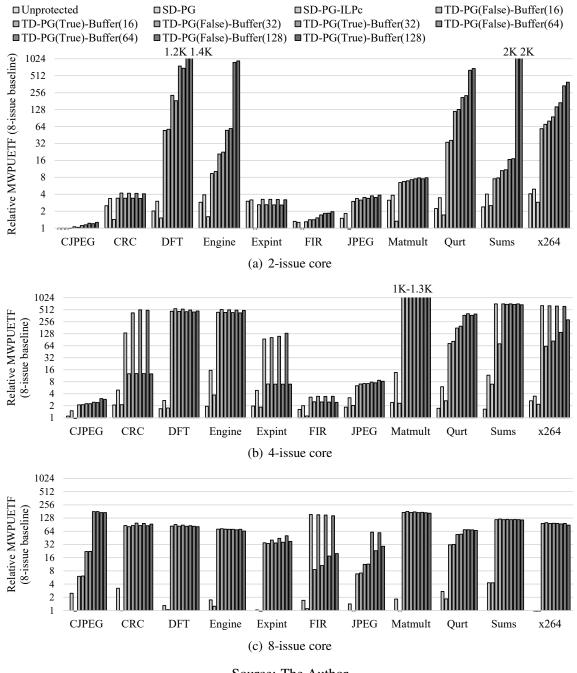

| Figure 6.6 MWPUETF Comparison                                                 | 111 |

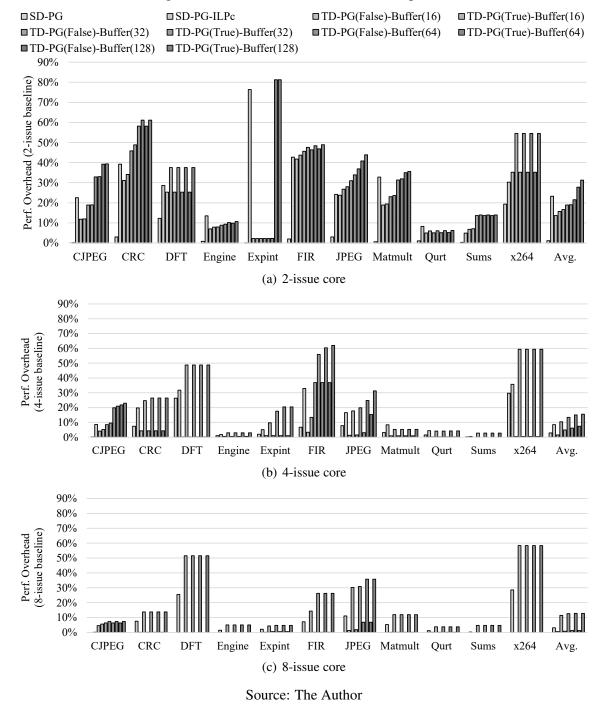

| Figure 6.7 Performance Overhead Comparison                                    | 115 |

| Figure 6.8 Relative Energy Consumption Comparison                             | 117 |

| Figure 6.9 MWPUETF Comparison - Polymorphic Processor                         | 120 |

| Figure 6.10 System Performance and Energy Consumption Comparison              | 126 |

| Figure A.1 Issue Utilization and Phase-configurable Duplication               | 150 |

| Figure A.2 Phase-configurable Duplication for the ADPCM Benchmark             | 151 |

# LIST OF TABLES

| Table 2.1 Core Parameters                                                         | 42     |

|-----------------------------------------------------------------------------------|--------|

| Table 6.1 Accuracy Comparison between RTL and Gate-level Fault Injection          | 94     |

| Table 6.2 Number of Cycles and Simulation Time Comparison                         |        |

| Table 6.3 Number of Transitions and Switching Activity from Gate-level Simulation |        |

| Table 6.4 Failure Rate and Performance Degradation Comparison                     |        |

| Table 6.5 Area and Power Dissipation Comparison                                   |        |

| Table 6.6 Fault Tolerance Techniques Comparison                                   |        |

| Table 6.7 Evaluated Designs and Their Techniques for Fault Tolerance and PG on    | , 10 1 |

| the Static Processor                                                              | .105   |

| Table 6.8 Performance, Energy Consumption, and Fault Tolerance Comparison         |        |

| Table 6.9 Best Configuration for Each Benchmark                                   |        |

| Table 6.10 Duplication Ratio - 2-issue Processor                                  |        |

| Table 6.11 Duplication Ratio - 4-issue Processor                                  |        |

| Table 6.12 Duplication Ratio - 8-issue Processor                                  |        |

| Table 6.13 Area Comparison - Temporal Duplication Mechanism                       |        |

| Table 6.14 Number of Kernel Executions and Number of Steps to Find the Best       |        |

| Configuration                                                                     | .118   |

| Table 6.15 MWPUETF Normalized to the Oracle Processor                             |        |

| Table 6.16 Best Static Configuration When Prioritizing Each of the Axes           |        |

| Table 6.17 Best Configuration - Priority: Energy (0.8)                            |        |

| Table 6.18 MWPUETF Normalized to the Oracle Processor - Priority: Energy          |        |

| Consumption                                                                       | .123   |

| Table 6.19 Best Configuration - Priority: Performance (0.8)                       | .124   |

| Table 6.20 MWPUETF Normalized to the Oracle Processor - Priority: Performance     | .124   |

| Table 6.21 Best Configuration - Priority: Fault tolerance (0.8)                   | .125   |

| Table 6.22 MWPUETF Normalized to the Oracle Processor - Priority: Fault Tol-      |        |

| erance                                                                            | .125   |

| Table A.1. Feilers Determined Desferment Describes Commission                     | 150    |

| Table A.1 Failure Rate and Performance Degradation Comparison                     |        |

| Table A.2 Area and Power Dissipation Comparison                                   | .133   |

| Table B.1 Best Configuration - Priority: Energy (0.5)                             | .155   |

| Table B.2 Best Configuration - Priority: Energy (0.6)                             |        |

| Table B.3 Best Configuration - Priority: Energy (0.7)                             |        |

| Table B.4 Best Configuration - Priority: Energy (0.8)                             |        |

| Table B.5 Best Configuration - Priority: Energy (0.9)                             |        |

| Table B.6 Best Configuration - Priority: Performance (0.5)                        |        |

| Table B.7 Best Configuration - Priority: Performance (0.6)                        |        |

| Table B.8 Best Configuration - Priority: Performance (0.7)                        |        |

| Table B.9 Best Configuration - Priority: Performance (0.8)                        |        |

| Table B.10 Best Configuration - Priority: Performance (0.9)                       |        |

| Table B.11 Best Configuration - Priority: Fault tolerance (0.5)                   |        |

| Table B.12 Best Configuration - Priority: Fault tolerance (0.6)                   |        |

| Table B.13 Best Configuration - Priority: Fault tolerance (0.7)                   |        |

| Table B.14 Best Configuration - Priority: Fault tolerance (0.8)                   |        |

| Table B.15 Best Configuration - Priority: Fault tolerance (0.9)                   |        |

# **CONTENTS**

| 1 INTRODUCTION                                                       |    |

|----------------------------------------------------------------------|----|

| 2 BACKGROUND AND RELATED WORK                                        | 23 |

| 2.1 Fault Tolerance                                                  | 23 |

| 2.1.1 Transient Faults                                               | 23 |

| 2.1.1.1 Dual Modular Redundancy (DMR) with Rollback                  | 24 |

| 2.1.1.2 Duplication with Comparison (DWC)                            | 25 |

| 2.1.1.3 Triple Modular Redundancy (TMR)                              | 26 |

| 2.1.1.4 Watchdog Processors                                          | 27 |

| 2.1.1.5 Adaptive Fault Tolerance Approaches                          | 29 |

| 2.1.2 Permanent Faults                                               |    |

| 2.2 Energy Consumption                                               | 31 |

| 2.2.1 Power Dissipation                                              | 31 |

| 2.2.1.1 Dynamic Power Dissipation                                    | 31 |

| 2.2.1.2 Static Power Dissipation                                     | 32 |

| 2.2.2 Energy Optimization Techniques                                 | 32 |

| 2.2.2.1 Clock Gating                                                 | 32 |

| 2.2.2.2 Power Gating                                                 | 33 |

| 2.2.2.3 Dynamic Voltage and Frequency Scaling (DVFS)                 | 34 |

| 2.2.3 Energy Optimization on the $\rho$ -VEX Processor               |    |

| 2.2.4 Energy-aware Fault Tolerance                                   | 37 |

| 2.3 Performance                                                      | 37 |

| 2.3.1 ILP and TLP exploitation                                       | 37 |

| 2.3.1.1 Instruction-Level Parallelism (ILP)                          |    |

| 2.3.1.2 Multiple Applications and Thread-Level Parallelism (TLP)     | 39 |

| 2.3.2 Adaptive Multi-core Architectures                              |    |

| 2.4 Fault Tolerance, Energy Consumption, and Performance Trade-off   | 41 |

| 2.5 Contributions of this Thesis                                     |    |

| 2.5.1 Fault Tolerance                                                | 44 |

| 2.5.2 Energy Consumption                                             | 44 |

| 2.5.3 Performance and Learning                                       | 45 |

| 2.5.4 Fault Tolerance, Energy Consumption, and Performance Trade-off | 45 |

| 3 IMPLEMENTED TECHNIQUES                                             | 47 |

| 3.1 Fault Tolerance                                                  | 47 |

| 3.1.1 Basic Duplication with Rollback                                |    |

| 3.1.1.1 Spatial duplication                                          |    |

| 3.1.1.2 Temporal and Spatial Duplication                             |    |

| 3.2 Energy Optimization                                              |    |

| 3.3 Performance                                                      |    |

| 3.3.1 ILP Control                                                    |    |

| 3.3.1.1 ILP Control for Fault Tolerance                              |    |

| 3.3.1.2 ILP Control for Energy Optimization                          | 57 |

| 4 PROPOSED ADAPTIVE AND POLYMORPHIC PROCESSORS                       |    |

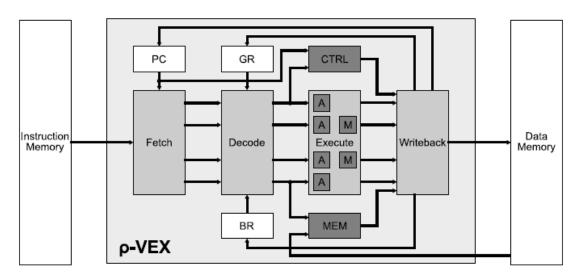

| <b>4.1</b> ρ-VEX Processor Background                                |    |

| 4.1.1 Static <i>ρ</i> -VEX Processor                                 |    |

| 4.1.2 Dynamic $\rho$ -VEX Processor                                  |    |

| 4.2 Proposed Adaptive Processor                                      |    |

| 4.2.1 Reliability-oriented Configuration                             |    |

| 4.2.2 Energy-oriented Configuration                                  | 68 |

|        | Final Remarks Regarding the Threshold Configuration        |     |

|--------|------------------------------------------------------------|-----|

| 4.3 I  | Proposed Polymorphic Processor                             | 71  |

| 4.3.1  | Learning Phase                                             | 72  |

| 4.3.2  | Runtime Phase                                              | 76  |

| 5 PR   | OPOSED HYBRID FAULT INJECTOR                               | 79  |

|        | Motivation                                                 |     |

| 5.2 H  | Fault Injectors - Related Work                             | 81  |

|        | Fault Injection Framework                                  |     |

|        | Implementation                                             |     |

|        | Fault Model                                                |     |

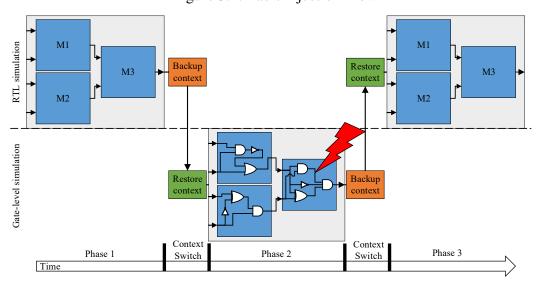

| 5.3.3  | Hybrid Mechanism                                           | 84  |

|        | Fault Injection Accuracy                                   |     |

|        | SULTS                                                      |     |

| 6.1 N  | Methodology                                                | 89  |

|        | Benchmarks                                                 |     |

| 6.1.2  | Temporal Duplication and Optimization Module Simulators    | 92  |

|        | Hybrid Fault Injector Results                              |     |

|        | RTL vs Gate-level: Accuracy Comparison                     |     |

|        | Fault Injection Performance                                |     |

|        | Adaptive $\rho$ -VEX Processor                             |     |

|        | Spatial Duplication Without Power Gating                   |     |

|        | .1 Failure Rate and Performance                            |     |

| 6.3.1. | .2 Dynamic Threshold Adaptation                            | 101 |

|        | .3 Area, Power Dissipation, and Energy Consumption         |     |

|        | .4 Comparison With Other Fault Tolerance Techniques        |     |

|        | Spatial Duplication With Power Gating                      |     |

| 6.3.2  | .1 Performance                                             | 106 |

| 6.3.2  | .2 Energy and Area                                         | 107 |

| 6.3.2  | .3 Failure Rate                                            | 107 |

| 6.3.2  | .4 EDFP - Energy-Delay-Failure Product                     | 109 |

| 6.4 I  | Polymorphic ρ-VEX Processor                                | 110 |

| 6.4.1  | Temporal and Spatial Duplication Mechanism                 | 110 |

| 6.4.1  | .1 Mean Work Per Unit of Energy to Failure - MWPUETF       | 110 |

| 6.4.1  | .2 Duplication ratio                                       | 112 |

| 6.4.1  | .3 Performance                                             | 114 |

| 6.4.1  | .4 Energy and Area                                         | 116 |

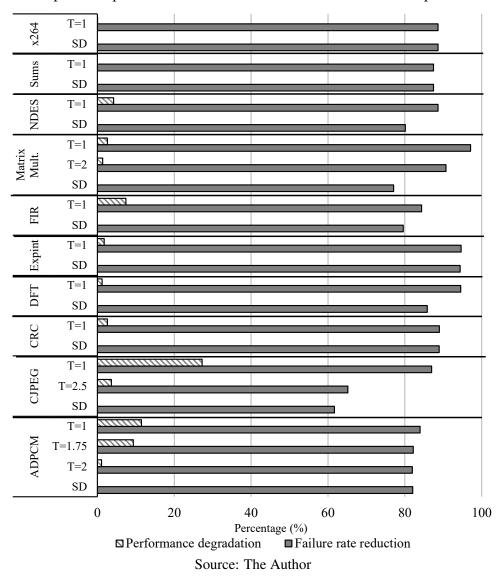

| 6.4.2  | Optimization Algorithm                                     | 117 |

| 6.4.2  | .1 Number of Steps to Find the Best Configuration          | 117 |

| 6.4.2  | .2 MWPUETF Comparison with the Same Weight for All Axes    | 119 |

| 6.4.2  | .3 MWPUETF Comparison with Different Weights for Each Axis | 121 |

|        | .4 System Performance and Energy Consumption               |     |

| 7 CO   | ONCLUSION AND FUTURE WORK                                  | 129 |

| 7.1 S  | Summary of Contributions                                   | 129 |

|        | Future Work                                                |     |

|        | Additional Techniques for Energy Optimization              |     |

|        | Support for Multithreaded Applications                     |     |

|        | Criticality-aware Duplication                              |     |

|        | ILP Control for the Polymorphic Processor                  |     |

|        | Improved Application Dispatcher                            |     |

| 7.3 I  | Publications                                               | 131 |

| 7.3.1  | Journals                                                   | 131 |

| 7.3.2 Conferences and Workshops                          | 132 |

|----------------------------------------------------------|-----|

| REFERENCES                                               |     |

| APPENDIX A — PHASE-CONFIGURABLE DUPLICATION              | 149 |

| A.1 Results                                              | 151 |

| APPENDIX B — EVALUATION OF DIFFERENT PRIORITIES FOR THE  | C   |

| MWPUETF                                                  | 155 |

| B.1 Priority: Energy Consumption                         |     |

| B.2 Priority: Performance                                | 157 |

| B.3 Priority: Fault Tolerance                            | 159 |

| APPENDIX C — RESUMO EM PORTUGUÊS                         | 163 |

| C.1 Introdução                                           | 163 |

| C.2 Técnicas propostas                                   |     |

| C.2.1 Tolerância a falhas                                |     |

| C.2.1.1 Duplicação com rollback                          | 164 |

| C.2.1.2 Duplicação baseada em fases                      |     |

| C.2.1.3 Duplicação espacial - duplicação quando possível | 164 |

| C.2.1.4 Duplicação temporal e espacial                   | 164 |

| C.2.2 Consumo de energia                                 |     |

| C.2.3 Performance                                        | 165 |

| C.3 Processador adaptativo                               | 165 |

| C.4 Processador polimórfico                              | 165 |

| C.5 Injetor de falhas híbrido                            | 166 |

| C.6 Metodologia                                          |     |

| C.7 Resumo dos resultados                                |     |

| C.8 Conclusões                                           | 167 |

#### 1 INTRODUCTION

As technology continues to evolve, more attention is paid to energy consumption and fault tolerance when designing new processors. While most of the embedded devices are heavily dependent on battery power, General-Purpose Processors (GPPs) are being held back by the limits of Thermal Design Power (TDP), highlighting the importance of reducing energy consumption. In addition, the need for fault tolerance on both space and ground-level systems is increasingly present in current processor designs. As the feature size of transistors decreases, their reliability is getting compromised as they become more susceptible to soft errors (SHIVAKUMAR et al., 2002). Therefore, energy consumption and fault tolerance, together with performance, should be considered and balanced to address the aforementioned issues according to given design constraints.

On the other hand, current processors are designed to focus on one or, at most, two of these axes. Achieving the ideal balance among them is challenging, due to their conflicting nature. For instance, reducing energy consumption will likely reduce performance; increasing fault tolerance will increase energy consumption and possibly reduce performance; and improving performance will affect the energy consumption and possibly reduce fault tolerance.

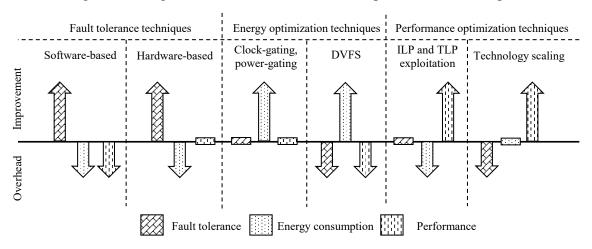

Figure 1.1 depicts a high-level overview, comparing the improvement and overhead of applying common optimization techniques to the axes of fault tolerance, energy consumption, and performance (further details about each of these techniques will be discussed in Chapter 3). Let us consider fault tolerance: replication techniques are widely used to detect or mask faults during the execution: while hardware-based techniques increase the power dissipation, software-based ones increase execution time; and both increase the total energy consumption.

Energy optimization techniques usually save energy by shutting down idle hard-ware or by reducing the supply voltage and frequency, which will very likely reduce performance; and when operating in very low voltage states, the reliability may also be reduced. Performance improvements may be achieved from several different techniques, from core optimizations to better exploit the Instruction-Level Parallelism (ILP); to system-level techniques, which comprise several cores and caches hierarchy to exploit the Thread-Level Paralellism (TLP) from applications. All these techniques focus on a single axis, and the incurred overhead in the other two axes varies depending on the chosen technique.

Figure 1.1: High-level Overview of Common Optimization Techniques

Source: The Author

In this scenario, we propose two processor designs to trade-off fault tolerance, energy consumption, and performance, named *adaptive* and *polymorphic* processors. The adaptive balances these three axes based on design time parameters, while the polymorphic dynamically evaluates different configurations and reconfigures the processor, adapting the hardware to the current application. The proposed processor relies on a set of optimization techniques that work together to provide improvements in each of the aforementioned axes with a low overhead in the other ones.

The  $\rho$ -VEX Very Long Instruction Word (VLIW) processor (WONG; Van As; BROWN, 2008) was used as target architecture for this study. VLIW processors are representative examples of current VLIW multiple-issue architectures (e.g., Intel Itanium (SHARANGPANI; ARORA, 2000), Trimedia CPU64 (EIJNDHOVEN et al., 1999), and TMS320C6745 (INSTRUMENTS, 2011)). Notably, a VLIW multi-core was recently used by the National Aeronautics and Space Administration (NASA) in its Mars rover for image processing (BORNSTEIN et al., 2011). These processors are able to deliver high-performance at a low energy consumption cost, as they do not rely on runtime dependency-checking mechanisms for scheduling the instructions that will be executed in parallel (HUCK et al., 2000). Therefore, VLIW processors are suitable options for safety-critical systems in several fields, such as automotive, space, and avionics.

Next, all mechanisms and tools that were developed and evaluated to get to the proposed processors are introduced. Note that several techniques were evaluated, and the ones with the best outcome were chosen to be integrated into each version of the processor (therefore some of them were not included into the final version of the processor).

# 1. Fault Tolerance Techniques:

- Spatial redundancy: a modified dual modular redundancy approach with roll-back that exploits idle issue-slots (i.e., functional units that execute No-Operations (NOPs)) and dynamically duplicates instructions to improve the reliability of the system by detecting and correcting errors.

- Temporal and spatial redundancy: takes the former mechanism one step further by also exploiting idle issue-slots in different bundles, that is, in different cycles, and not only within the same bundle.

- Hybrid fault injection tool that improves fault injection speed when compared

to other simulation fault injection approaches, while maintaining the accuracy

of gate-level fault injection.

# 2. Energy Optimization Techniques:

• A power gating mechanism that can be applied to the datapath to reduce both static and dynamic power. As idle issue-slots are completely turned off, they are not able to execute duplicated instructions, but they also reduce the sensitive area of the processor, influencing fault tolerance.

## 3. Performance Optimization Techniques:

- A dynamic ILP controller that can reduce the parallelism (and therefore performance) at runtime. In this case, issue-slots are artificially freed by automatically moving operations to the next cycle, offering opportunities to duplicate more instructions or maximize the power gating phases (as it will be explained, power gating demands that an issue-slot must be turned off for a minimum period, so the gains in power overcome its costs).

- Application dispatcher that takes into account the issue-width requirements

of each application and the ability of the processor to change its configuration during runtime to maximize the number of applications that are executed

concurrently.

- Optimization algorithm that evaluates and chooses the best configuration for each application that is being executed, considering the trade-off between the three axes.

- The dynamic version of the ρ-VEX, which is able to change the issue-width

of the processor during runtime, was used and extended so the optimization

modules could also resize their resources or enable/disable certain features

during runtime to exploit the trade-off between the aforementioned axes.

Each version of the proposed processor uses a set of these techniques in addition to a decision module, which controls these techniques during runtime. The adaptive processor uses thresholds to cope with different application behaviors, while the polymorphic processor can dynamically test and choose the best configuration for each benchmark considering fault tolerance, performance, and energy consumption. The polymorphic's learning is done by executing each iteration of a given kernel with a different configuration and evaluating its outcome (a metric that considers the trade-off between the three axes). The learning stops when the best configuration (the one that delivers the best trade-off) is found, resulting in a reduced number of tests. In addition, an application dispatcher module was implemented to dynamically schedule multiple applications concurrently, according to the available hardware. Therefore, it is possible to dynamically and efficiently adapt the processor configuration to the behavior of the application.

The remainder of this work is organized as follows. Background and related work comprising the aforementioned axes are discussed in Chapter 2. Chapter 3 describes the proposed techniques for each of the axes and their implementation. Next, in Chapter 4, the adaptive and polymorphic processor implementations are discussed, and Chapter 5 presents a hybrid simulation-based fault injector that is able to speed up the fault injection campaign while maintaining the accuracy of gate-level fault injection. In Chapter 6 the results are discussed in terms of fault tolerance, energy consumption, performance, area, and the trade-off between these axes. Finally, Chapter 7 concludes this work and discusses future directions.

#### 2 BACKGROUND AND RELATED WORK

In this chapter, the background and related work comprising the axes of fault tolerance, energy consumption, and performance will be discussed. First, the faults will be classified and related work regarding fault tolerance will be discussed. Second, energy optimization and energy-aware fault tolerance techniques will be presented. Third, the axis of performance will be assessed. Finally, the trade-off among these axes will be discussed and related work will be compared to the proposed methodology.

#### 2.1 Fault Tolerance

A fault may be classified into one of the two large groups: transient or permanent. Next, each of these groups is discussed in detail and fault tolerance techniques are presented.

#### 2.1.1 Transient Faults

Single-event effects (SEEs) are caused by numerous energetic particles such as protons and heavy ions from space or neutron and alpha particles at ground-level. They are created from the deposition of energy from a single ionizing particle in either sequential or combinational logic in the silicon. The former is called Single-Event Upset (SEU) and characterizes that a stored value in a memory cell had its value inverted (bit flip). The latter is called Single-Event Transient (SET) and it generates a transient current pulse in the combinational circuit, which also may affect memory elements if the inverted signal is captured by a clock edge. SETs may not be captured in a memory element by one of the following reasons (SHIVAKUMAR et al., 2002):

- Logical masking: occurs when the particle strike affects a signal that does not affect the output of a subsequent gate, which is determined by its other inputs.

- *Electrical masking:* happens when the pulse from a particle strike is attenuated by subsequent gates, not affecting the result of the circuit.

- Latching-window masking: due to a pulse that reaches a latch in a clock transition in which it does not capture its input value, consequently not affecting the result.

For Application-Specific Integrated Circuits (ASICs) and antifuse-based Field-Programmable Gate Arrays (FPGAs), these effects are transient, and only last until the next time a value is loaded to that same element. For Static Random Access Memory (SRAM)-based FPGAs, in addition to the same vulnerabilities of ASICs, the configuration bits are also sensitive, which means that the configuration of the programmed design may change and lead to wrong computation. A fault in the configuration bits is permanent in the sense that it needs reconfiguration in order to restore correct behavior (de Lima Kastensmidt et al., 2004). Approaches have been proposed to perform the reconfiguration: scrubbing (BERG et al., 2008), readback and partial reconfiguration of the faulty parts (CARMICHAEL; CAFFREY; SALAZAR, 2000), etc.

Several works have been proposed for the detection and correction of transient faults in multiple-issue processors (e.g., VLIW and superscalar). These works aim to improve the fault tolerance of the target system, typically based on redundancy, which may be implemented in software, hardware, or both. Next, some of these techniques will be discussed.

## 2.1.1.1 Dual Modular Redundancy (DMR) with Rollback

Dual Modular Redundancy (DMR) based on checkpoints with rollback was used by Xiaoguang et al. (2015) and Yang and Kwak (2010) to detect and correct errors. Whenever an error is detected, the state in which the execution was correct is recovered. Therefore, the latency to detect the error on these approaches will vary according to the periodicity of the checkpoints (i.e., when a new checkpoint must be made). These approaches were implemented in software.

In order to reduce the energy consumption of rollback and recovery protocols for High-Performance Computing (HPC), Ibtesham et al. (2014) propose to apply a check-point compression scheme. This approach reduces data volume and traffic, incurring higher computational overhead to process the compressed packages. Even though there is a computational cost to compress and decompress the checkpoint information, the energy consumption is reduced due to the reduction in the execution time.

A hardware-based replication with rollback mechanism for superscalar processors is proposed by Ray, Hoe and Falsafi (2001). In this approach, the application is replicated into two or more threads and the computed results are checked before commit. If any inconsistency is found, the rollback is activated, the re-order buffer is flushed, and the execution restarts by fetching once more the next-PC from the last committed instruction.

Figure 2.1: Hardware-based Replication with Rollback for Superscalar Processors

Source: (RAY; HOE; FALSAFI, 2001)

Figure 2.1 depicts this approach: (1) the register renaming capabilities were adapted so the instructions fetched from a single stream can be issued redundantly into two or more data-independent threads; (2) the multiple threads are checked against each other before the committing the instruction; (3) any inconsistency in the redundant results rewinds the execution. These threads have tightly coupled executions (both must execute at the same time) and, consequently, each type of functional unit used by the main thread must be duplicated so that the replicated thread may execute concurrently.

## 2.1.1.2 Duplication with Comparison (DWC)

Bolchini (2003) and Hu et al. (2009) propose software-based redundancy based on Duplication With Comparison (DWC) for VLIW data paths aiming to reduce the performance overhead by using the idle functional units. However, these techniques still present huge performance degradation and increase code size, as they are implemented in software. Mitropoulou, Porpodas and Cintra (2014) propose an optimization to the DWC's generated code by reducing the impact of the basic block fragmentation caused by the check instructions, having lower, but still not negligible, performance degradation than the previous two techniques.

Instruction Decode (ID) Execution (EXE) Stage Memory (MEM) Stage Write-Back (WB) Stage Instruction Fetch (IF) Stage Stage Write-back Signals Pipeline Registers with Shadow Latch Synchronous Dual-read-port Register File Data Forwarding Signal Asynchronous Instruction Memory 6 Dual-port Asynchronous Data Memory Demultiplexers Next Instruction Address Signal = Pseudo-dynamic Comparator Branch Address Signal Multiplexers

Figure 2.2: Triplication of the Combinational Logic with a Stand-by Module

Source: (WALI et al., 2015)

# 2.1.1.3 Triple Modular Redundancy (TMR)

Another common approach is to triplicate hardware components and use a majority voter to mask the faults, Triple Modular Redundancy (TMR), as implemented by Schölzel (2007) and Chen and Leu (2010). In these cases, they only triplicate the functional units of a VLIW processor rather than the entire processor; therefore, it is possible to reduce area and power dissipation costs. Schölzel (2007) proposed the Reduced TMR, in which both hardware and software needed to be changed. If the two instructions (main and duplicated) compute different results, the instruction is executed a third time. Hu et al. (2005) propose a similar approach to Schölzel (2007). However, instruction replication is done in software, so the binary code is changed, even though there is no area overhead. In the same way, replication is done partially to some instructions to amortize the costs in performance.

Wali et al. (2015) propose to triplicate the combinational logic parts of a MIPS processor. However, only two copies run in parallel, while the third one uses time-redundancy in case of an error to vote the correct result. This approach is depicted in Figure 2.2. A state-machine controls which two combinational logic modules will be active, and a control module manages the comparator, pipeline register, demultiplexer and multiplexer. In order to re-compute the operation in case of an error (third execution), shadow latches are used to hold the last fault-free state of the pipeline. Then, the comparator votes the three computed results. Anjam and Wong (2013) propose a TMR approach to be applied on the synchronous flip-flops of a VLIW processor.

Psiakis, Kritikakou and Sentieys (2017) propose to exploit temporal and spatial duplication for the VEX Instruction Set Architecture (ISA) in order to provide more flex-

ibility in the instruction replication, as instructions that cannot be replicated in a given bundle are stored in a buffer so they can be executed in a subsequent cycle. The authors evaluate the duplication (for fault detection only) and the triplication of instructions in order to provide fault tolerance. However, no reliability, area, power, and energy results are presented, only performance ones. In addition, the memory latency is not exploited to execute duplicated instructions (i.e., execute instructions while the processor is waiting for the memory), as the VEX simulator does not provide a cache and memory model.

# 2.1.1.4 Watchdog Processors

Watchdog processors (MAHMOOD; MCCLUSKEY, 1988) execute concurrently to the main processor, and they compare the outputs from the main processor with their own (pre-computed or concurrently computed). Examples of watchdog processors are discussed next. DIVA (AUSTIN, 1999) proposes to increase the reliability of a superscalar processor by augmenting the commit phase of the pipeline with a checker unit (watchdog processor). This checker is a simple in-order processor that does not have any mechanism to speed up computation (e.g., predictors, renamers and dynamic schedulers). The checker will verify and commit the results if the computation is correct, and flush the computation and restart the processor in case of an error, as presented in Figure 2.3. The checker is considered to be more robust than the other parts of the circuit and the verification cost of the checker is lower than verifying traditional processor design due to its simplicity. In addition, the authors discuss the buffering of results in order to deeply pipeline the checker unit, which permits implementations with large time margins and large transistors (more resistant to transient faults and radiation interference).

Other approaches use redundant threads as watchdog processors (ROTENBERG, 1999; REINHARDT; MUKHERJEE, 2000). SHREC (SMOLENS et al., 2004) proposes an approach for asymmetric re-execution, similar to DIVA. In addition, it allows threads to be replicated and staggered. Hence, the difference in the execution progress between the leading and trailing (replicated) thread hides cache-miss latencies and allows the leading thread to provide branch prediction information to the trailing thread. The trailing thread instructions are only checked using input operands produced by the leading thread, avoiding bottlenecks in the issue queue and reorder buffer. In addition, the functional units are shared, unlike DIVA.

Rashid et al. (2005) propose a thread-level redundant execution that consumes less energy than replicating the whole program and running it on identical hardware. This is

Traditional Out-of-Order Core out-of-order execute nonspec results В ID REN in-order in-order issue retirement DIVA Core DIVA Checker out-of-order execute instructions with inputs and outputs IF REN В ID 0 in-order in-order verify and commit issue

Figure 2.3: Traditional Out-of-order Compared to the DIVA Approach

Source: (AUSTIN, 1999)

done by parallelizing the trailing thread and running it in several small cores (i.e., simple cores with reduced frequency). Moreover, the leading thread provides the trailing thread with branch information and L1 cache prefetch hints. Periodic checkpoints are performed by the leading thread to allow the rollback to a fault-free state when an error is detected. Madan and Balasubramonian (2007) propose a similar approach to Rashid et al. (2005), using Dynamic Voltage and Frequency Scaling (DVFS) instead of only Dynamic Voltage Scaling (DVS), and in-order execution on the trailing thread instead of an out-of-order processor.

RECVF (SUBRAMANYAN et al., 2010) proposes to forward critical instruction results from the leading to the trailing thread, so the latter may execute faster and the energy consumption can be reduced by executing the trailing core at a lower voltage and frequency. The results to be forwarded are chosen based on heuristics proposed by Tune et al. (2001). For instance, one approach is to forward instructions on the head of the Re-order Buffer (ROB), as these instructions are likely to be on the critical path (other instructions have to wait for the execution of these ones, so they can be committed); forward instructions in the head of the instruction queue; forward every Nth instruction; forward mispredicted branches/jumps; forward all possible values (oracle heuristic given infinite storage and bandwidth); among other heuristics. In order to recover from an error, the cores are reset to the instruction following the last verified instruction when an error is detected.

#### 2.1.1.5 Adaptive Fault Tolerance Approaches

Some works exploit the previous techniques in order to provide an adaptive fault tolerance mechanism. Jacobs et al. (2012) propose an adaptive framework that switches between different fault tolerance techniques depending on a priori knowledge of the environment, external events, or application-triggered events. The supported fault-tolerance modes are triple modular redundancy, duplication with comparison, Algorithm-Based Fault Tolerance (ABFT), internal TMR, and high-performance (no fault tolerance). This approach is for FPGAs only, as the hardware needs to be reconfigured.

An adaptive checkpoint mechanism was proposed by Zhang and Chakrabarty (2004), in which the checkpointing interval is adjusted during the execution based on the occurrence of faults and the available slack. An offline preprocessing based on linear programming is used to determine the parameters that are provided to the online checkpointing procedure. That is, the preprocessing step obtains the slack time for each job according to the deadline constraints and the threshold for the minimum number of checkpoints. Even though the checkpointing is adaptively made, the detection latency is still greater than zero, besides the need for preprocessing.

Works that aim to minimize the performance cost of the software-based fault tolerance mechanisms were also proposed. Nakka, Pattabiraman and Iyer (2007) propose to replicate only critical instructions of the application. This is done by first identifying which are the critical variables, extracting the critical code sections and finally instrumenting the code with check instructions. This approach is only able to detect faults, not to correct them. It detects 87% of instruction errors and 97% of data errors.

Aaron (BRÜNINK et al., 2011) tackles software and hardware errors by using diversified software components in the Central Processing Unit (CPU) spare cycles. Eight methods are used in this diversification, including SWIFT (REIS et al., 2005b), a software-based fault tolerance approach that duplicates instructions and registers. The system load is estimated, and the scheduler chooses the best variant to use the spare cycles (e.g., executing a reliability-oriented variant, which takes longer to execute, but is able to provide fault tolerance), as presented in Figure 2.4. Therefore, whenever load permits, more fault coverage is achieved; even though it is only able to detect errors, not correct them. Gomaa

C Client Variant

T Thread Task

Figure 2.4: Aaron Scheduling Example

Source: (BRÜNINK et al., 2011)

and Vijaykumar (2005) propose two mechanisms to exploit unused resources on low ILP phases: the first replicates the main thread and compares the results to detect faults; the second applies a reuse technique to detect and compare the results of implicit redundant operations within the main thread. The previous four works discussed in this subsection are implemented in software, having lower performance when compared to a hardware-based mechanism. Most of these approaches are only able to detect, and not to correct, a fault.

#### 2.1.2 Permanent Faults

Single event effects can also be destructive, damaging the device permanently. In this case, reconfiguration of FPGAs will not correct the error and ASICs are also affected. Permanent damage may occur due to several factors, for instance, the energy from a charged particle may lead to excessive supply power. Also, the Total Ionizing Dose (TID), which is a cumulative long-term ionizing damage due to protons and electrons, has the potential to damage the device permanently. Aging effects are also critical, especially for space missions, where system maintenance or replacement is difficult (BOLCHINI; SANDIONIGI, 2010).

As the detection of permanent faults is not in the scope of this thesis, only a few works will be briefly discussed next. One technique is to relocate the affected design to a

part of the FPGA in which there are no errors, via reconfiguration. Fay et al. (2007) use relocation to recover the system in case of a hard fault, whereas Srinivasan et al. (2008) also use this approach to recover from performance degradation due to aging effects.

Other approaches for hardware relocation in order to avoid faulty parts of the circuit are proposed by Bolchini, Miele and Sandionigi (2012), Noji et al. (2010), Mitra et al. (2004). Techniques as TMR or N-modular Redundancy (NMR) naturally mask permanent faults as long as the majority of the results is still correct.

# 2.2 Energy Consumption

As the energy consumption is defined by the integral of power dissipation over time, next, we discuss the classification of power, which can be divided into two large groups: dynamic or static power. Then, we will discuss optimization mechanisms to reduce the energy consumption of the circuit.

# **2.2.1 Power Dissipation**

#### 2.2.1.1 Dynamic Power Dissipation

Dynamic power  $(P = C * V^2 * A * f)$  varies according to the load capacitance (C), supply voltage (V), activity factor (A), and operating frequency (f), next each of these terms is discussed (KAXIRAS; MARTONOSI, 2008).

- *Capacitance*: mainly depends on the technology of the transistors and wire length of the chip.

- *Supply Voltage:* due to its quadratic influence on power dissipation, when the voltage is reduced, the power is reduced proportionally to the square of that factor.

- Activity Factor: refers to how often the transistors transition from '0' to '1' or '1' to '0', which is represented by a fraction that varies between zero and one (i.e., 0% to 100%).

- Clock Frequency: frequency affects not only the power dissipation, but also the supply voltage. For instance, for higher clock frequencies, higher supply voltage is required, and vice-versa. Thus, the pair  $V^2*f$  offers the potential of cubic reduction in the power dissipation, which is exploited by energy optimization techniques and will be discussed in detail in the next subsections.

# 2.2.1.2 Static Power Dissipation

Reducing the feature size of transistors as well as supply and threshold voltages cause an increase in the leakage current, which increase the static power dissipation (leakage) of the circuit (DE; BORKAR, 1999; RAO et al., 2003). Leakage represents 20% to 30% of the total power dissipation of modern processors (BORKAR, 1999; MAIR et al., 2007; RUSU et al., 2007).

Leakage energy can come from sub-threshold leakage and gate leakage, among other sources (KAXIRAS; MARTONOSI, 2008). Sub-threshold leakage represents the power that is dissipated by a gate that is supposed to be off. That is, until the current reaches the threshold voltage (voltage in which the transistor switches on), the transistor charge is leaked to the ground. In addition to the threshold voltage, another important parameter that determines the sub-threshold leakage power is the temperature (it depends exponentially on the temperature), increasing the temperature, increases the leakage. Gate leakage occurs due to the tunneling of electrons through the gate insulator, which separates the gate terminal from the transistor channel. It is also dependent on the temperature, and strongly dependent on the insulator thickness, gate-to-source bias, and gate-to-drain bias.

## 2.2.2 Energy Optimization Techniques

Several techniques may be applied in order to reduce the power dissipation of the circuit and, in most cases, the energy consumption of the applications. These techniques are applied at several and different granularities: from flip-flops to whole functional units or subsystems (e.g., memory and processor). Some of them are discussed next.

#### 2.2.2.1 Clock Gating

Clock gating consists in disabling the clock signal to idle units, therefore, saving dynamic but not static power. For small circuits or individual flip-flops, clock gating reduces the power dissipation by eliminating the switching activity of these units. At this granularity, such transformations are routinely applied by the Register-Transfer Level (RTL) compiler. On the other hand, for coarser granularities, high-level control policies are needed (KAXIRAS; MARTONOSI, 2008).

Figure 2.5: Power Gating Header Transistor

Source: (HU et al., 2004)

Due to its simplicity, this approach may be applied on a cycle-by-cycle basis with limited penalty in area and timing. This technique is used in both low-power designs (Intel XScale (CLARK et al., 2001)) and high-performance processors (IBM's Power5 (CLABES et al., 2004)).

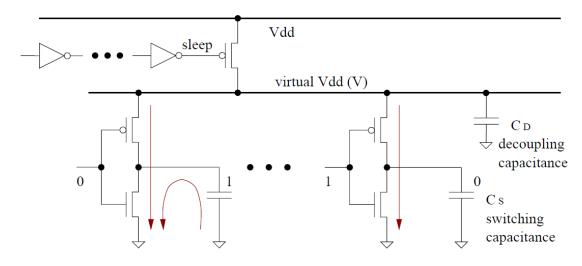

#### 2.2.2.2 Power Gating

Power gating is used to address leakage power dissipation by shutting off idle blocks of the circuit, thus, reducing both static and dynamic power dissipation. A suitably sized header transistor is used to turn off the supply voltage to the circuit block, which creates a virtual Vdd, as presented in Figure 2.5. A sleep signal controls this transistor so the Vdd can pass through when the circuit is active (virtual Vdd = Vdd) and gate the Vdd when idle (virtual Vdd = 0). The sleep signal is controlled via a global policy that varies according to the implementation. As one more transistor is used, this comes at the cost of performance penalty and power overhead as the power lines are not able to be charged and discharged in one clock cycle. In order to cope with this additional cost of the mechanism, the break-even point must be considered, which is the point when the leakage energy savings equals the energy overhead of switching the circuit on and off (which will be explained in detail next). After reaching this point, the energy consumption of the system is reduced (HU et al., 2004).

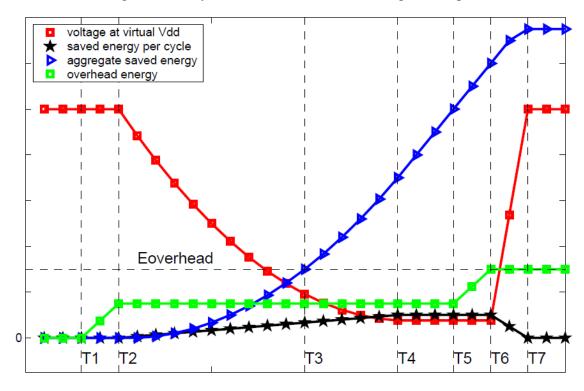

Figure 2.6 (HU et al., 2004) depicts the key intervals that must be considered for power gating. The inactivity interval starts at t = 0 and goes until  $t = T_1$ , when the control

Figure 2.6: Key Intervals for the Power Gating Technique

Source: (HU et al., 2004)

circuit makes the decision of power gating the unit. At  $t = T_2$ , the header device receives the sleep signal and the virtual Vdd starts going down. As the voltage decreases, the amount of leakage energy saved per cycle increases. The break-even point is achieved when the execution reaches  $t = T_3$ , at this point the aggregate leakage energy savings equals the energy overhead of switching ON  $(T_1 \text{ to } T_2)$  and OFF  $(T_5 \text{ to } T_6)$  the header device.

At  $t=T_4$  the reduction in voltage at the virtual Vdd saturates (not necessarily at zero due to the leakage of the header device). The control logic detects the next busy interval at  $t=T_5$  and the sleep signal is de-asserted, and in  $t=T_6$ , the header device is turned on. From  $t=T_6$  to  $t=T_7$ , the virtual Vdd is charged up to the Vdd level. As the Vdd increases, the energy savings per cycle is gradually reduced, reaching zero at  $t=T_7$  (when the unit is completely active). Therefore, the energy savings are proportional to the idle time that can be exploited by this mechanism while executing an application.

# 2.2.2.3 Dynamic Voltage and Frequency Scaling (DVFS)

The dynamic power dissipation equation (previously discussed) clearly shows the significant leverage that voltage and frequency adjustment may provide (potential cubic

influence in the dynamic power dissipation). However, this comes at the cost of performance and reliability: by reducing voltage and frequency, the performance is reduced as well, not achieving a cubic reduction in the energy consumption due to the longer execution time. That is, even though the dynamic power dissipation may be reduced by a cubic factor, the longer execution time (which implies in more static power dissipation) prevents a cubic reduction in the total energy consumption (KAXIRAS; MARTONOSI, 2008). Reliability is also reduced when reducing the voltage, because it allows low energy particles to create a critical charge that leads to a transient fault (ZHU; MELHEM; MOSSÉ, 2004).

# 2.2.3 Energy Optimization on the $\rho$ -VEX Processor

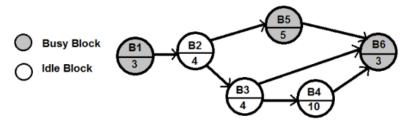

Giraldo, Wong and Beck (2016) propose to insert customized instructions at compile time (static) to power-gate functional units and parts of the register file, based on the profiling of the application, on the  $\rho$ -VEX processor. Their methodology follows the flow depicted in Figure 2.7. First, the application is compiled, then it is profiled to obtain information about the basic blocks that were executed. With this information, the Control Flow Graph (CFG) (explained in detail next) of the application is generated, then it is analyzed in order to determine which are the best spots to insert power gating instructions (always placed at the beginning of the basic block). Finally, the application is executed once more with the power gating instructions in order to evaluate the energy savings and the incurred performance overhead.

The CFG that is built based on the application profiling (i.e., considering conditional branch and loop information) is a data structure that comprises the transitions probabilities to the other basic blocks and the number of idle cycles of each basic block. This is done for each functional unit. An example of CFG is depicted in Figure 2.8, in which the transition probability from basic block  $B_2$  to  $B_3$  is of 70%, and  $B_3$  to  $B_4$  is 90%. Therefore, the expected number of idle cycles starting at a given basic block is defined by the weighted sum considering the number of idle cycles and the transition probability. In the example, equation (2.1) is obtained for such functional unit.

$$T = 4 + (0.7 * 4) + (0.7 * 0.9 * 10) = 13.1$$

(2.1)

Data Memory 2. Compilation 1. Source Code and Instruction Memory Insertion of 4. Dynamic 5. CFG Power Gating Profiling instructions 9. Results of Power Savings 7. Code Modified 8. Simulation and Performance Impact

Figure 2.7: Methodology Flow of the Compiler-directed Power Gating

Source: (GIRALDO; WONG; BECK, 2016)

Figure 2.8: Example of Control Flow Graph for a Given Functional Unit

Source: (GIRALDO; WONG; BECK, 2016)

This value represents the expected number of idle cycles that a power gating instruction could exploit if it was to be inserted in the given basic block. The authors consider the break-even point to be of 10 cycles (HU et al., 2004). Hence, in this example, a power gating instruction would be added at the beginning of the basic block  $B_2$ , as the estimated number of idle cycles is 13.

In addition, the wake-up time is of 3 cycles for this technology. This means that after starting a basic block in which a functional unit must be turned on, this unit will take three cycles to be completely active, which implies that an instruction at the beginning of the basic block that needs this functional unit will have to wait it become ready. On the other hand, if the instructions at the beginning of the basic block do not use the functional unit that is being activated, the execution may continue normally (i.e., there is no need to stall the processor if all functional units that will be used are already activated).

For the register file power gating, the application is profiled and the register file is divided into eight groups of 8 registers each. Based on the profiling, portions of the

register file are shut down at the beginning of the application, turning off the blocks that are never used.

## 2.2.4 Energy-aware Fault Tolerance

In this subsection, works that combine energy optimization mechanisms with fault tolerance to reduce the energy consumption of the protected circuit will be discussed. Fault tolerance techniques usually increase the energy consumption of the application by increasing the power dissipation of the circuit (spatial redundancy) or the execution time (time redundancy). In addition, when using DVS or DVFS to reduce the energy consumption, the circuit becomes less reliable as the voltage is reduced. Therefore, the number of SEUs is increased exponentially as voltage decreases (HAZUCHA; SVENSSON; WENDER, 2000; HAZUCHA; SVENSSON, 2000; ZHU; MELHEM; MOSSÉ, 2004).

Pop et al. (2007) propose to increase fault tolerance and minimize the energy consumption in a no-fault scenario by scheduling and applying voltage scaling on a heterogeneous distributed time-triggered system, in which the processes are statically scheduled. The transient faults are tolerated by re-executing the process.

Oh and McCluskey (2002) combine procedure call duplication with statement duplication to reduce the energy consumption overhead when compared to the duplication of every program instruction. This approach is only able to detect errors and it reduces the energy consumption, on average, by 25% depending on the required detection latency when compared to the full instruction duplication.

## 2.3 Performance

Performance may be exploited at different levels: the most common are at instruction (ILP) or thread (TLP) level. Next, we will discuss in detail these two parallelism exploitation granularities (for both VLIW and superscalar processors).

# 2.3.1 ILP and TLP exploitation

## 2.3.1.1 Instruction-Level Parallelism (ILP)

ILP is exploited by analyzing the instructions that have to be executed, the ones that are independent of each other (i.e., a given instruction that does not depend on the

result from the other) can be executed concurrently if there are available functional units. The identification of such instructions can be performed during run-time or compile time. The former is adopted by superscalar processors and the latter by VLIW ones.

Superscalar processors use dependency-checking mechanisms, instruction queue, reorder buffer and other hardware components to exploit ILP during run-time. Two execution paradigms may be applied to the instructions: in-order and out-of-order (HENNESSY; PATTERSON, 2017).

- In-order processors will exploit ILP by executing instructions in parallel, however, if a given instruction depends on an instruction that is currently being executed, the following instructions in the instruction queue must wait the former instruction start its execution so they can be issued to the available functional units.

- Out-of-order processors allow the instructions in the instruction queue to be issued as soon as their operands are available and there is an available functional unit to execute the given operation. Therefore, they are not executed in the compiled order. Out-of-order execution allows the performance to be improved (when compared to in-order execution) as more instructions are considered to be executed at a given time, exploiting the functional units more efficiently. However, the cost of this flexibility comes with increased power dissipation and area overhead for control mechanisms.

On the other hand, VLIW processors exploit ILP by means of a compiler, executing several operations (instructions) per cycle depending on the processor's issue-width and the intrinsic ILP available in the application. These instructions are organized into words (bundles), and all instructions in a bundle are executed in parallel. VLIW processors occupy less area and dissipate less power when compared to traditional superscalar processors, since the process of scheduling instructions is statically done by a compiler. Therefore, the hardware of a VLIW processor is much simpler: the instruction queue, reorder buffer, dependency-checking and many other hardware components are not needed. However, in several cases, it is not able to fill all slots of the bundle with independent instructions (ADITYA; MAHLKE; RAU, 2000). The solution is filling the unused slots with NOPs. These NOPs require memory bandwidth to be fetched, potentially increasing cache misses, which would result in performance degradation and extra energy consumption.

In order to amortize such costs, several techniques have been proposed to remove these NOPs: compressed encoding for VLIW instruction (TREMBLAY et al., 2000;

COLWELL et al., 1991; CONTE et al., 1996; JEE; PALANIAPPAN, 2002); instruction template bits (SHARANGPANI; ARORA, 2000; WAERDT et al., 2005); and stop-bits (FISHER; FARABOSCHI; YOUNG, 2005; RAJE; SIU, 1999; SUGA; MATSUNAMI, 2000; HUBENER et al., 2014). Even so, the functional units of the issue slot responsible for executing the NOP (whether it was removed from code or not) will still be idle, which potentially allows this idle hardware to be exploited in a more efficient way: executing duplicated instructions for fault tolerance, shutting down these functional units to save energy, or executing another thread to improve performance.

# 2.3.1.2 Multiple Applications and Thread-Level Parallelism (TLP)

Multicore architectures exploit parallelism by executing several applications or several threads from the same application concurrently. Therefore, improving the performance of the system or application. In order to speed up the development of parallel applications, Parallel Programming Interfaces (PPIs) are used, such as, Open Multi Processing (OpenMP) (CHAPMAN; JOST; Van Der Pas, 2008), POSIX threads (Pthreads) (BUTENHOF, 1997), or Message Passing Interface (MPI) (SNIR, 1998). Each of these PPIs have different characteristics regarding the management of the threads, distribution of the workload and synchronization. For instance, OpenMP and Pthreads use shared variables in memory for data exchange, and MPI uses message passing. OpenMP offers a set of compiler directives, library functions, and environment variables for the development of multithreaded programs. Pthreads offers functions that allow a fine-grain adjustment of the workload, and the creation/termination of the threads, distribution of the workload and control of the execution are entirely defined by the programmer (BUTENHOF, 1997).

OpenMP synchronizes the threads using busy-waiting (i.e., the threads access the shared memory repeatedly until the end of synchronization). On the other hand, Pthreads synchronizes the threads by blocking them with mutexes, therefore, waiting on standby until the end of the synchronization (TANENBAUM; WOODHULL, 1987). MPI offers communication primitives (e.g., send and receive) to exchange data. The creation and termination of the processes may be dynamic or static at the beginning and end of the execution, depending on the MPI version that is used. In multicore environments, MPI communications are implemented using shared memory regions to store First-In-First-Out (FIFO) queues of each MPI process (CHANDRAMOWLISHWARAN; KNOBE; VUDUC, 2010). Therefore, TLP exploitation is not transparent for the developer and

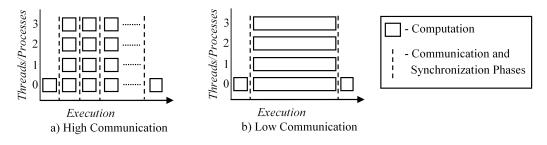

Figure 2.9: Multithreaded Application Behavior Regarding Communication

Source: (LORENZON; CERA; BECK, 2016)

the performance improvements greatly depend on the characteristics of the application, target architecture, and chosen PPI.

Figure 2.9 depicts different communication behaviors that multithreaded applications may present: applications with low communication requirements (i.e., CPU-intensive applications that distribute the workload at the beginning of the execution and in the end join the results of the threads) present a speedup close to the ideal (Figure 2.9(a)), which is the reduction of the execution time by a factor close to the number of available cores. On the other hand, high communication applications constantly exchange data between the threads during the execution (Figure 2.9(b)), which implies in several synchronization points, consequently reducing the speedup of the parallel application (LORENZON; CERA; BECK, 2016). In order to quantify the amount of concurrency that an application has, the TLP metric proposed by Gao et al. (2014) is presented in (2.2).

$$TLP = \frac{\sum_{i=1}^{n} c_i i}{1 - c_0} \tag{2.2}$$

In which,  $c_i$  represents the fraction of time that i cores are concurrently running different threads, n is the number of cores, and  $1 - c_0$  is the non-idle time fraction. The closer this value is to the total number of threads, the more TLP is available.

## 2.3.2 Adaptive Multi-core Architectures

Traditional core micro-architectures are not able to efficiently exploit the TLP available in the applications. Most commercial processors have large out-of-order cores (Intel Core i7) or small cores (ARM A15/A7). Large Out-of-Order (OoO) cores provide

high performance for single threaded programs by exploiting ILP, however, they are extremely power-inefficient for TLP exploitation due to the complex OoO cores. On the other hand, small cores are able to exploit the TLP without wasting energy and area at the cost of reduced single-thread performance.

In order to cope with high ILP and TLP programs, heterogeneous chip multiprocessors have been proposed (HILL; MARTY, 2008; MORAD et al., 2006; SULEMAN et al., 2009). These processors provide a few large cores for single-thread performance and many small cores for multithreaded applications. However, the number of cores of each type must be chosen during design time, which restricts the ability of the core to adapt itself for different applications that do not fit the pre-determined number of cores, resulting in sub-optimal performance and energy consumption.

Processor architectures with the objective of overcoming the drawbacks of heterogeneous cores were also proposed (BOYER; TARJAN; SKADRON, 2010; GIBSON; WOOD, 2010; GUPTA et al., 2010; IPEK et al., 2007; KIM et al., 2007; PRICOPI; MITRA, 2012; PUTNAM; SMITH; BURGER, 2011; WATANABE; DAVIS; WOOD, 2010). In these approaches, several small cores are used to provide high throughput to multi-threaded programs and these cores are "fused" into a large core when single thread performance is needed.

MorphCore (KHUBAIB et al., 2012) follows the same idea of adjusting the number of cores during run-time, but instead of fusing small cores, it uses a large out-of-order core that is able to "morph" into several small cores for multi-thread performance. This project choice was made in order to avoid additional latencies in the pipeline stages and to avoid the data migration among the caches when switching modes. The application starts running in the large OoO core and the mode switching is based on the number of active threads. Hence, when the number of active threads increases, the core switches to in-order mode (switching back to OoO mode if the number of active threads is reduced). As the mode switching mechanism is implemented in hardware, the operating system does not require any modification.

## 2.4 Fault Tolerance, Energy Consumption, and Performance Trade-off

A few works have proposed to target all three axes: Tricriteria Scheduling Heuristics (TSH) (ASSAYAD; GIRAULT; KALLA, 2011) proposes an offline scheduling heuristic that produces a static multiprocessor schedule, based on a given application graph and

Table 2.1: Core Parameters

| Core Configuration<br>Mode | F(GHz) / V(Volt) | Buffer Size<br>(IQ, LSQ, ROB) | Width<br>(Fetch, Issue) |  |

|----------------------------|------------------|-------------------------------|-------------------------|--|

| CCMA (Avg. core)           | 1.6/0.8          | 36,128,128                    | 4,4                     |  |

| CCMN (Narrow)              | 2/1              | 24,64,64                      | 2,2                     |  |

| CCML (Large)               | 1.4/0.8          | 48,128,256                    | 4,4                     |  |

| CCMS (Small)               | 1.2/0.7          | 12,16,16                      | 1,1                     |  |

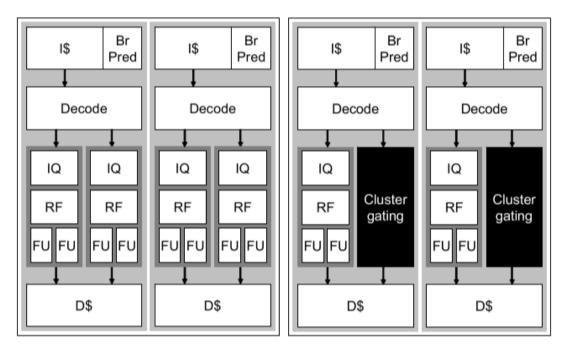

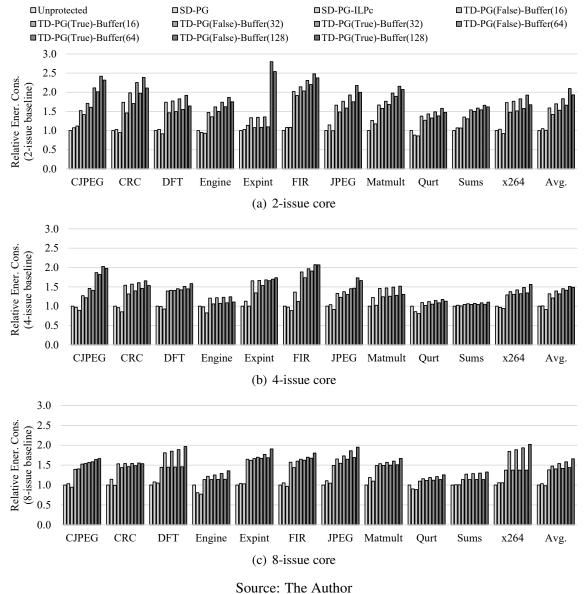

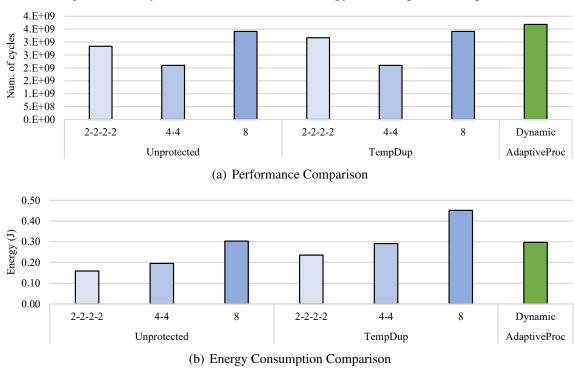

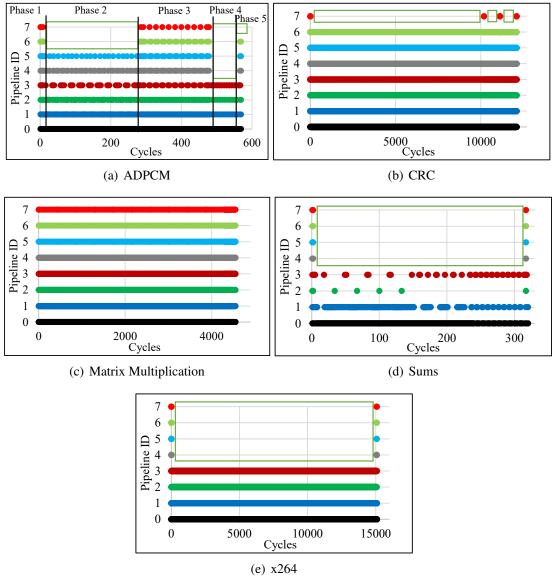

Source: (SRINIVASAN; KOREN; KUNDU, 2015)