## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

#### LUIS ALBERTO CONTRERAS BENITES

# Automated Design Flow for Applying Triple Modular Redundancy in Complex Semi-Custom Digital Integrated Circuits

Thesis presented in partial fulfillment of the requirements for the degree of Master of Microeletronics

Advisor: Prof. Dr. Fernanda Lima Kastensmidt

#### CIP — CATALOGING-IN-PUBLICATION

Contreras Benites, Luis Alberto

Automated Design Flow for Applying Triple Modular Redundancy in Complex Semi-Custom Digital Integrated Circuits / Luis Alberto Contreras Benites. – Porto Alegre: PGMI-CRO da UFRGS, 2018.

139 f.: il.

Thesis (Master) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica, Porto Alegre, BR-RS, 2018. Advisor: Fernanda Lima Kastensmidt.

1. Fault tolerance. 2. Radiation effects. 3. TMR. 4. Equivalence checking. 5. Semi-custom design flow. 6. ASIC. 7. FPGA. I. Lima Kastensmidt, Fernanda. II. Título.

#### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Rui Vicente Oppermann Vice-Reitora: Prof<sup>a</sup>. Jane Fraga Tutikian

Pró-Reitor de Pós-Graduação: Prof. Celso Giannetti Loureiro Chaves Diretora do Instituto de Informática: Prof<sup>a</sup>. Carla Maria Dal Sasso Freitas Coordenadora do PGMICRO: Prof. Fernanda Gusmão de Lima Kastensmidt Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

#### **ACKNOWLEDGMENTS**

This work is one way to thank my parents William and Yuni for their guidance and love. Also, to my siblings Williams and Melany for being always along with me although the distance.

I want to express my gratitude to my girlfriend Thaiane for being supportive, understanding and a wonderful companion.

I would like to sincerely thank my adviser professor Fernanda Lima for her constant support, patience, motivation, and sharing her expertise and knowledge with me.

Thank CEITEC for providing facilities to allow me to attend the master's subjects during work hours. I am particularly grateful with Janaina Costa for her several advice and help.

I am also thankful for the financial aid provided by CAPES and CNPq during the development of my master course in microelectronics and my training in the CI Brasil Program.

Finally, to the persons that I met in Porto Alegre, Mauricio, Sebastian, Nolberto and Jorge for their invaluable friendship.

#### **ABSTRACT**

Radiation effects have been one of the most serious issues in military and space applications. But they are also an increasing concern in modern technologies, even for commercial applications at the ground level. Protection or hardening of integrated circuits against radiation effects can be obtained through the use of enhanced fabrication processes and strategies at different stages of the circuit design. The triple modular redundancy (TMR) technique is a widely and well-known technique employed to mask single faults without detecting them. However, the design of TMR circuits is not automated by commercial electronic design automation (EDA) tools and even they can remove partially or totally the redundant logic. On the other hand, there are several tools that can be used to implement the TMR technique in integrated circuits, although most of them are licensed commercial tools, convenient only for specific devices, or with restricted use because of the International Traffic in Arms Regulations (ITAR) regimen. The present work intends to overcome these issues so a methodology is proposed to automate the design of TMR circuits using a commercial design flow. The proposed approach uses a structured netlist to implement automatically TMR circuits at different granularity levels of redundancy for cell-based and field-programmable gate array (FPGA) designs. Optimization of the resulting TMR circuit is also applied based on the gate sizing approach. Moreover, verification of the implemented TMR circuit is based on equivalence checking, and guarantee its correct functionality and its fault-tolerant capability against soft errors. Experiments with an high-level synthesis (HLS)-derived circuit and an obfuscated description of the ARM Cortex-M0 soft-core are performed to show the use and the advantages of the proposed design flow. Several issues related to the removal of the implemented redundant logic were found as well as the impact in the increment of area caused by the majority voters. Furthermore, the reliability of different TMR implementations of the ARM soft-core synthesized in FPGA was evaluated using emulated-simulation fault injection campaigns. As a result, it was reinforced the high-reliability level of the finest granularity implementation even in the presence of up to 10 accumulated faults and the poorest mitigation capacity corresponding to the replication of flip-flops solely.

**Keywords:** Fault tolerance. Radiation effects. TMR. Equivalence checking. Semicustom design flow. ASIC. FPGA.

# Fluxo de projeto automatizado para aplicar redundância modular tripla em circuitos digitais semicustomizados complexos

#### **RESUMO**

Os efeitos de radiação têm sido um dos problemas mais sérios em aplicações militares e espaciais. Mas eles também são uma preocupação crescente em tecnologias modernas, mesmo para aplicações comerciais no nível do solo. A proteção dos circuitos integrados contra os efeitos da radiação podem ser obtidos através do uso de processos de fabricação aprimorados e de estratégias em diferentes estágios do projeto do circuito. A técnica de TMR é bem conhecida e amplamente empregada para mascarar falhas únicas sem detectálas. No entanto, o projeto de circuitos TMR não é automatizado por ferramentas EDA comerciais e até mesmo eles podem remover parcial ou totalmente a lógica redundante. Por outro lado, existem várias ferramentas que podem ser usadas para implementar a técnica de TMR em circuitos integrados, embora a maioria delas sejam ferramentas comerciais licenciadas, convenientes apenas para dispositivos específicos, ou com uso restrito por causa do regime ITAR. O presente trabalho pretende superar esses incovenientes, para isso uma metodologia é proposta para automatizar o projeto de circuitos TMR utilizando um fluxo de projeto comercial. A abordagem proposta utiliza um netlist estruturado para implementar automaticamente os circuitos TMR em diferentes níveis de granularidade de redundância para projetos baseados em células e FPGA. A otimização do circuito TMR resultante também é aplicada com base na abordagem do dimensionamento de portas lógicas. Além disso, a verificação do circuito TMR implementado é baseada na verificação de equivalência e garante sua funcionalidade correta e sua capacidade de tolerancia a falhas simples. Experimentos com um circuito derivado de HLS e uma descrição ofuscada do soft-core ARM Cortex-M0 foram realizados para mostrar o uso e as vantagens do fluxo de projeto proposto. Diversas questões relacionadas à remoção da lógica redundante implementada foram encontradas, bem como o impacto no incremento de área causado pelos votadores de maioria. Além disso, a confiabilidade de diferentes implementações de TMR do soft core ARM sintetizado em FPGA foi avaliada usando campanhas de injeção de falhas emuladas. Como resultado, foi reforçado o nível de alta confiabilidade da implemntação com mais fina granularidade, mesmo na presença de até 10 falhas acumuladas, e a menor capacidade de mitigação correspondente à replicação de flip-flops apenas. **Palavras-chave:** Tolerância a falhas. Efeitos da radiação. TMR. Comprovação de equivalência. Fluxo de projeto semicustomizado. ASIC. FPGA.

## LIST OF ABBREVIATIONS AND ACRONYMS

ALPEN Alpha-particle source/drain penetration

ASIC Application specific integrated circuit

ASTEP Altitude Single Event Effects Test European Platform

CERN Conseil Européen pour la Recherche Nucléaire

CGTMR Coarse grain TMR

DD Displace damage

DICE Dual interlocked storage cell

DSP Digital signal processing

EDA Electronic design automation

ELT Enclosed layout transistor

FGLTMR Fine grain local TMR

FGDTMR Fine grain distributed TMR

FGTMR Fine grain TMR

FI Fault injection

FPGA Field-programmable gate array

HDL Hardware description language

HKMG High-k metal gate

HLS High-level synthesis

LHC Large Hadron Collider

LSM Laboratory of Modane

IC Integrated circuit

IP Intellectual property

ITAR International Traffic in Arms Regulations

LEO Low Earth orbit

LET Linear energy transfer

MBU Multiple-bit upset

NIEL Non-ionizing energy loss

PKA Primary knock-on atom

RHBD Radiation Hardening by Design

RHBP Radiation Hardening by Process

RTL Register-transfer level

TMR Triple modular redundancy

SAA South Atlantic Anomaly

SDC Silent data corruption

SEE Single-event effect

SEL Single-event latch-up

SET Single-event transient

SEU Single-event upset

SKA Secondary knock-on atom

SoC System-on-a-chip

SOI Silicon-on-insulator

SRAM Static random-access memory

STI Sallow trench isolation

TID Total-ionizing dose

# LIST OF FIGURES

| Figure 2.1 Two doughnut-shaped regions of trapped radiation with maximum inte-                                                                            | 20    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| sity (inner and outter radiation belts)                                                                                                                   |       |

| Figure 2.2 Inner belt is closer to the ground over South America and the South Atlant                                                                     |       |

| Figure 2.3 Map of radiation dosage over South Atlantic Anomaly (SAA)                                                                                      |       |

| Figure 2.4 Representation of cosmic rays cascade through the earth's atmosphere                                                                           | 22    |

| Figure 2.5 Defect types and sub-cascade formation related to primary knock-on                                                                             | 24    |

| atom energy in Silicon                                                                                                                                    | 24    |

| Figure 2.6 Cross section representation and positive trapped charge of a) LOCOS and b) STI isolated transistors. c) Leakage paths (1 and 2 arrows) in STI |       |

| transistors                                                                                                                                               | 25    |

| Figure 2.7 Charge deposition and drift and diffusion collection processes. Pulse                                                                          | 20    |

| current duration                                                                                                                                          | 27    |

| Figure 2.8 Pulse quenching mechanism                                                                                                                      | 28    |

| Figure 2.9 Real-time soft-error rate measurements from three technological gener-                                                                         |       |

| ations of single-port SRAMs: CMOS 130, 65 and 40 nm                                                                                                       | 29    |

| Figure 2.10 Measurements of SBU and MCU events as a function of technology nod                                                                            | le 30 |

|                                                                                                                                                           |       |

| Figure 3.1 Fault, failure and error events                                                                                                                |       |

| Figure 3.2 Triple Well process                                                                                                                            |       |

| Figure 3.3 Epitaxial bulk CMOS                                                                                                                            | 34    |

| Figure 3.4 Cross sections of a) Partially Depleted and b) Fully Depleted SOI MOS-                                                                         |       |

| FETs                                                                                                                                                      |       |

| Figure 3.5 SOI parasitic a)PBJT and b) MOS                                                                                                                |       |

| Figure 3.6 Annular transistor with a) 90o angle, b) 45o angle and large W/L case                                                                          | 37    |

| Figure 3.7 Enclosed layout transistors with a) just source enclosed and b) both                                                                           | 2=    |

| drain and source enclosed                                                                                                                                 | 37    |

| Figure 3.8 Cross section of two adjacent NMOS transistor with guard band be-                                                                              | 20    |

| tween them                                                                                                                                                |       |

| Figure 3.9 Resistor memory cell schematic                                                                                                                 |       |

| Figure 3.10 DICE memory cell schematic                                                                                                                    |       |

| Figure 3.11 HIT memory cell schematic                                                                                                                     |       |

| Figure 3.12 Immune Latch diagram.                                                                                                                         | 41    |

| Figure 3.13 a) SEILA memory cell schematic, b) and c) shows the same area uti-                                                                            | 11    |

| lization for single and double height cell schemes respectively                                                                                           |       |

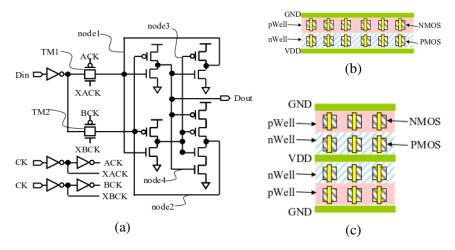

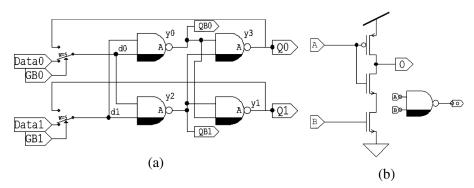

| Figure 3.14 a) BISER latch diagram and b) C-element diagram and truth table                                                                               |       |

| Figure 3.15 a) SERT diagram and b) half transition NAND gate                                                                                              |       |

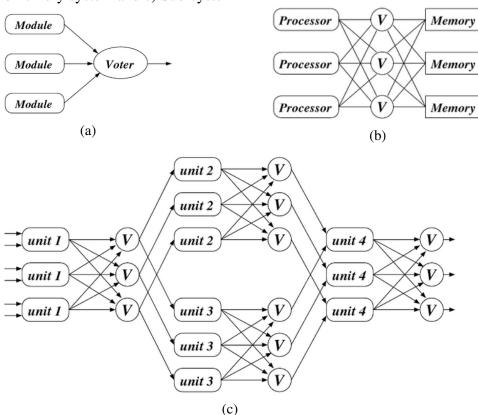

| Figure 3.16 Dual Modular Redundancy (DMR)                                                                                                                 | 44    |

| Figure 3.17 a) Triple Modular Redundant (TMR) structure, b) Triplicated TMR of                                                                            | 15    |

| a processor/memory system and c) Sub-system TMR                                                                                                           |       |

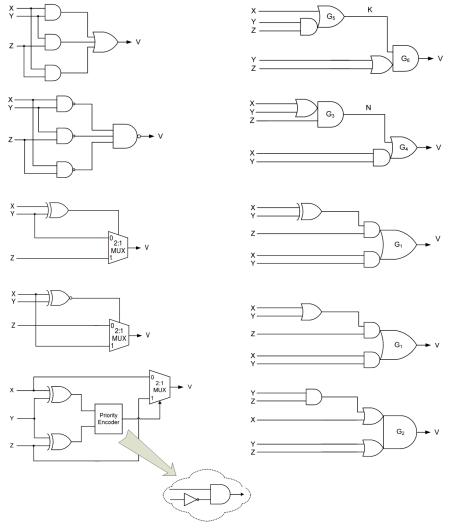

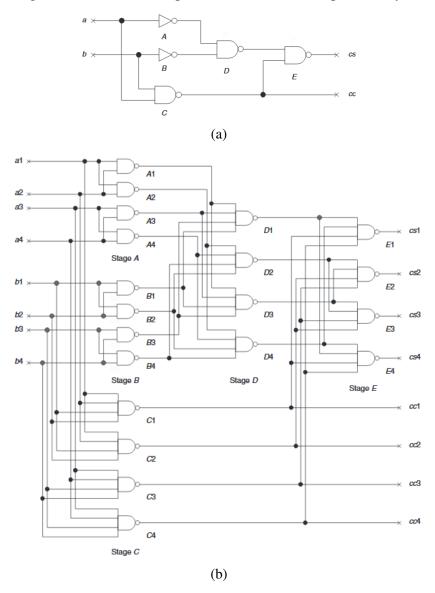

| Figure 3.18 Different implementations of majority voters for TMR systems                                                                                  | 40    |

| mented with NAND logic and b) Quadded implementation of the comple-                                                                                       |       |

| mentary half adder                                                                                                                                        | 47    |

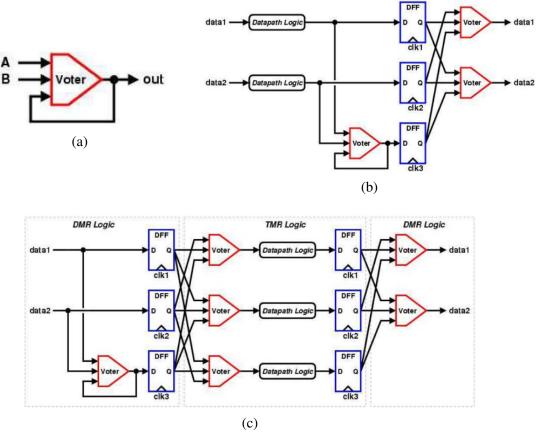

| Figure 3.20 a) Self-voting dual modular redundancy circuit, b) Self-voting major-                                                                         | ,     |

| ity circuit and c) DMR-to-TMR and TMR-to-DRM mixed circuits                                                                                               | 48    |

| •                                                                                                                                                         |       |

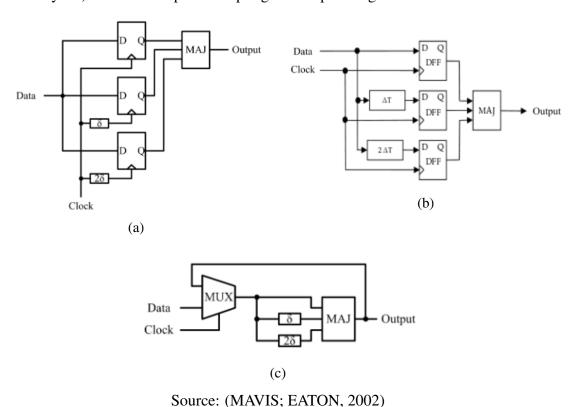

| Figure 3.21 Temporal sampling in TMR latch with a) internal clock delays and b) internal data delays. c) Minimal temporal sampling latch replicating itself in time | 19         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

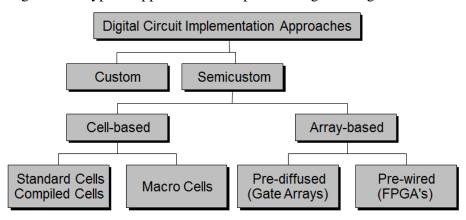

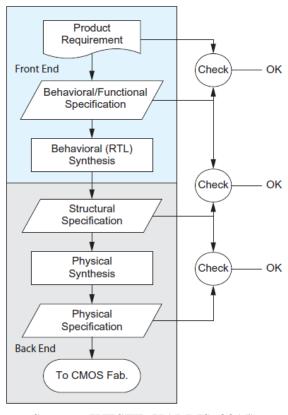

| Figure 4.1 Typical approaches to implement digital integrated circuits                                                                                              | 52         |

| Figure 4.2 Generalized semi-custom design flow5                                                                                                                     | 54         |

| Figure 4.3 Proposed fault tolerant design flow to automate the implementation, optimization and verification steps of TMR circuits                                  | 56         |

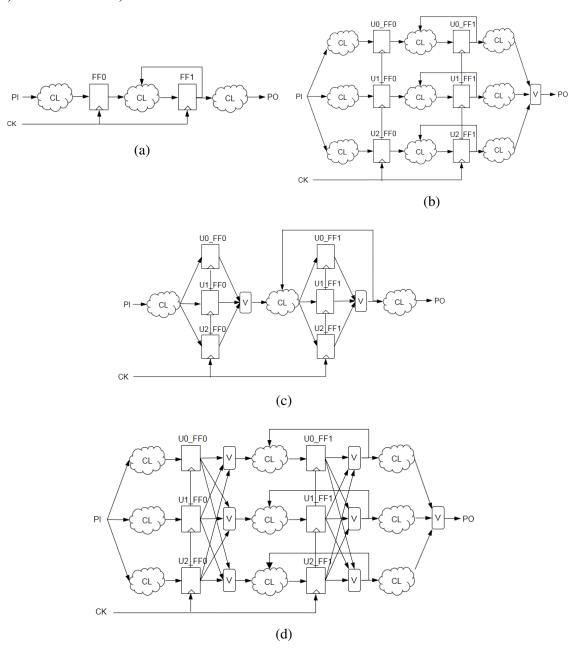

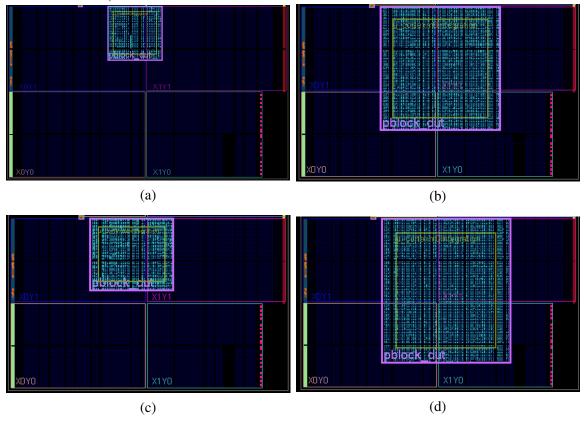

| Figure 4.4 Illustration of a a) simple circuit and its TMR implementations: b)  CGTMR, c) FGLTMR and d) FGDTMR                                                      |            |

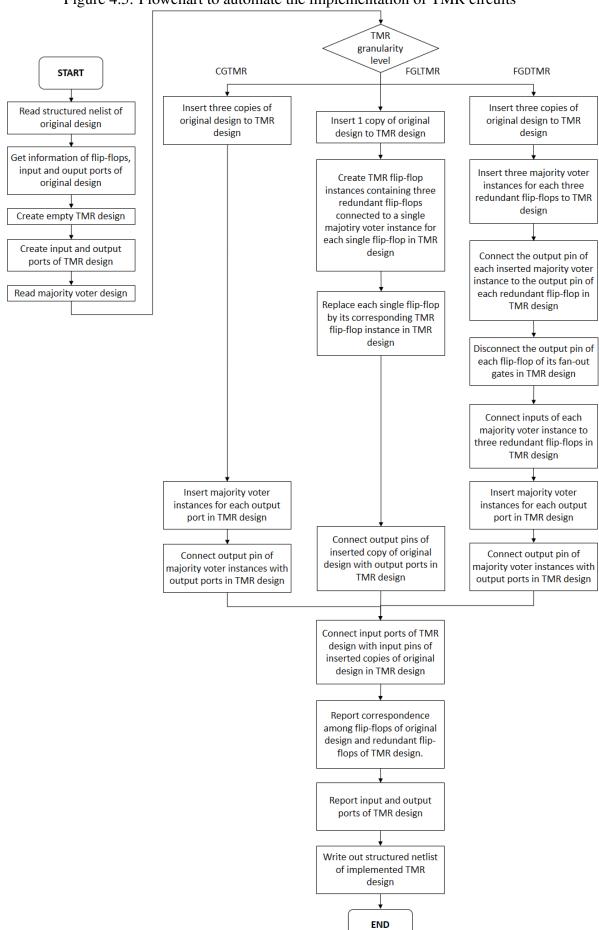

| Figure 4.5 Flowchart to automate the implementation of TMR circuits                                                                                                 |            |

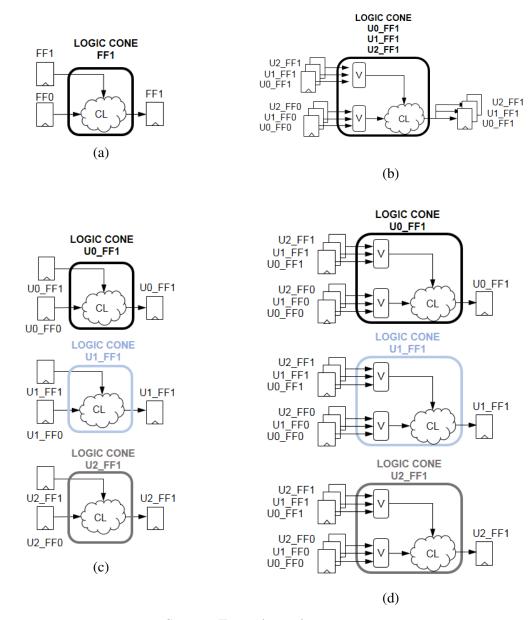

| Figure 4.6 Logic cones of a) unmitigated flip-flop and the resulting TMR logic cones: b) FGLTMR, c) CGTMR and d) FGDTMR                                             |            |

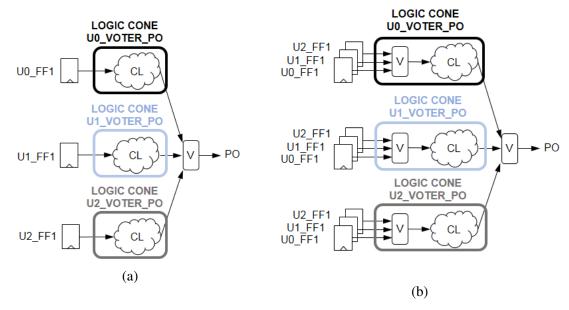

| Figure 4.7 Triplicated combinational logic paths of primary output in a) CGTMR and b) FGDTMR implementations respectively                                           | <b>5</b> 5 |

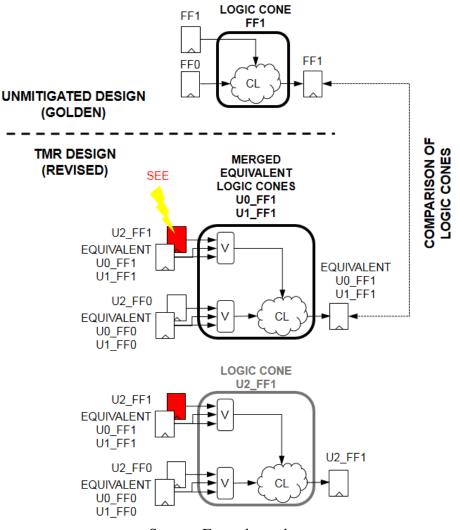

| Figure 4.8 Comparing process and fault injection for the FGDTMR implementation6                                                                                     | 57         |

| Figure 4.9 Flowchart to get elements of logic cone of a selected flip-flop                                                                                          | 58         |

| Figure 4.10 Flowchart to find shared elements in logic cones of three redundant flip-flops                                                                          | <b>59</b>  |

| Figure 4.11 Flowchart to find shared elements in logic cones of a selected primary output                                                                           | 70         |

| Figure 4.12 Flowchart to verify the correct functionality and masking capability of the implemented TMR design                                                      |            |

| Figure 5.1 Matrix multiplication algorithm                                                                                                                          | 74         |

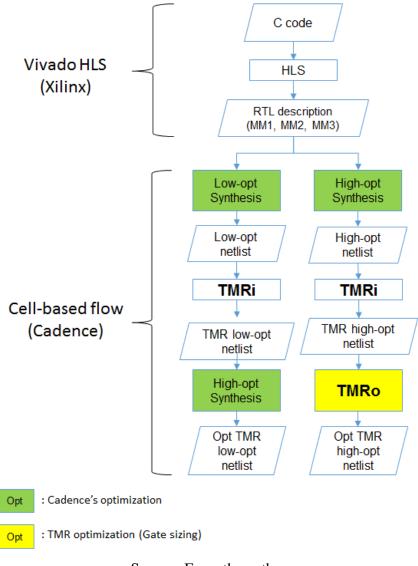

| Figure 5.2 Procedure to evaluate the proposed cell-based flow to design TMR circuits 7                                                                              |            |

| Figure 5.3 Extract from flip-flop's searching report in optimized TMR circuit derived from low-optimized implementation                                             |            |

| Figure 5.4 Extract from logic cones' report of optimized TMR circuit derived from low-optimized implementation                                                      |            |

| Figure 5.5 Extract from voter's searching report in optimized TMR circuit derived from low-optimized implementation                                                 |            |

| Figure 5.6 Extract from flip-flop's searching report in optimized TMR circuit (gate sizing) derived from high-optimized implementation                              |            |

| Figure 5.7 Extract from logic cones' report of optimized TMR circuit (gate sizing)  derived from high-optimized implementation                                      |            |

| Figure 5.8 Extract from voter's searching report in optimized TMR circuit (gate                                                                                     |            |

| sizing) derived from high-optimized implementation                                                                                                                  | )1         |

| circuit (gate sizing) derived from high-optimized implementation                                                                                                    | 32         |

| Figure 5.10 Verification report shows the correct implementation of the TMR versions of MM1                                                                         | 32         |

| Figure 5.11 Verification report shows the correct implementation of the TMR versions of MM2                                                                         | 33         |

| Figure 5.12 Verification report shows the correct implementation of the TMR versions of MM3                                                                         | 33         |

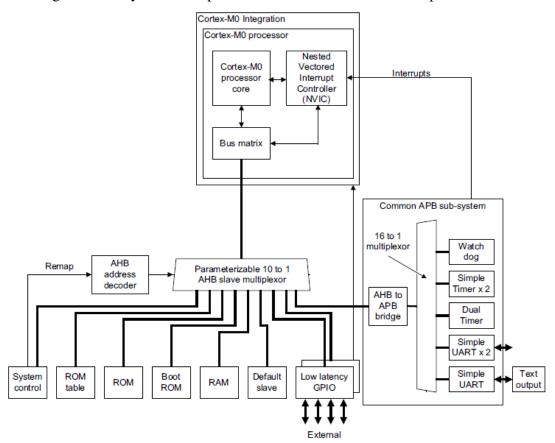

| Figure 5.13 System example based on the ARM Cortex-M0 processor                                                                                                     |            |

| Figure 5.14 Procedure to evaluate the proposed FPGA flow to design TMR circuits                                                                                     |            |

| Figure 5.15 Verification report shows the correct implementation of the TMR ver-                                                                                    |            |

| sions of the ARM Cortex-M0 processor                                                                                                                                | 37         |

| Figure 5.16 Microcontroller system provided into the ARM Cortex-M0 Design-       | 00  |

|----------------------------------------------------------------------------------|-----|

| Start Eval package                                                               | 89  |

| Figure 5.17 Placement of a) unmitigated and its TMR implementations: b) CGTMR,   |     |

| c) FGLTMR and d) FGDTMR                                                          | 89  |

| Figure 5.18 Placement of the reference and the implementations under test of the |     |

| ARM Cortex-M0 processor                                                          | 90  |

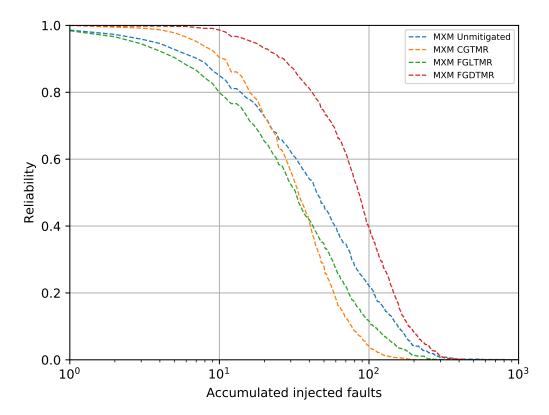

| Figure 5.19 Reliability curve from accumulated fault injection campaigns         |     |

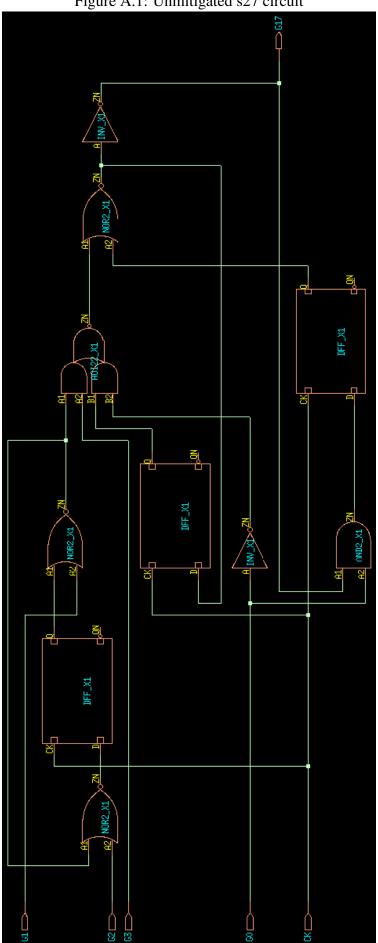

| Figure A.1 Unmitigated s27 circuit.                                              | 111 |

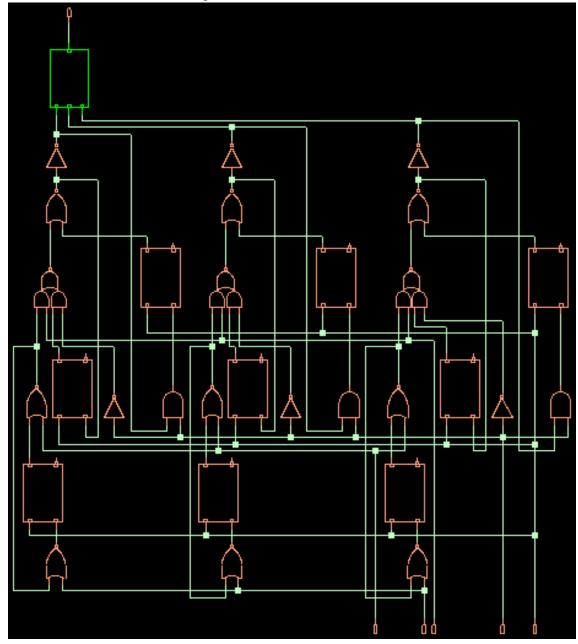

| Figure A.2 CGTMR s27 circuit                                                     |     |

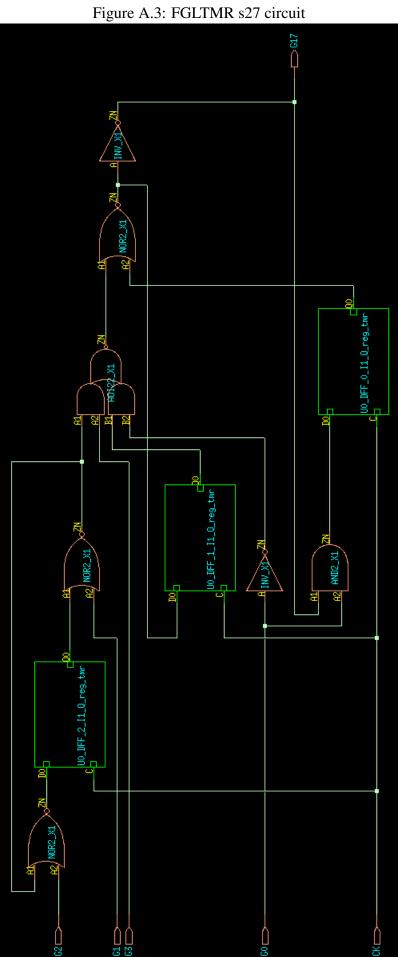

| Figure A.3 FGLTMR s27 circuit                                                    |     |

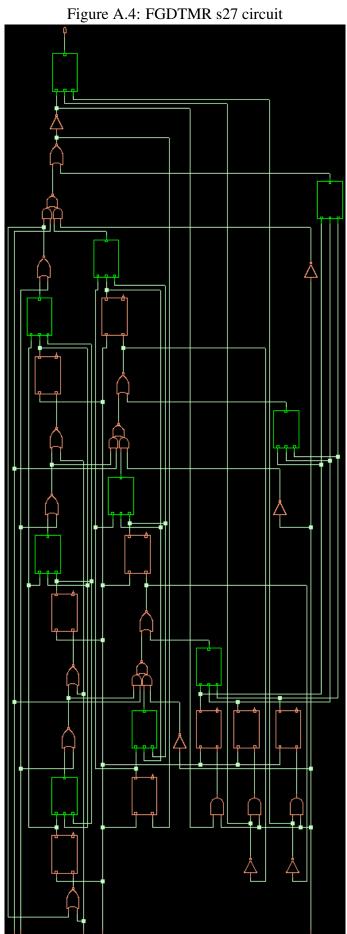

| Figure A.4 FGDTMR s27 circuit                                                    |     |

|                                                                                  |     |

# LIST OF TABLES

| Table 1.1 Dedicated tools to implement TMR circuits                             | 17 |

|---------------------------------------------------------------------------------|----|

| Table 2.1 Alpha emissivities of various materials                               | 23 |

| Table 2.2 SEE classification                                                    | 28 |

| Table 3.1 Radhard standard cell libraries                                       | 43 |

| Table 3.2 Summary of techniques, the effects that they mitigate and the need of |    |

| logic gates customization                                                       | 50 |

| Table 5.1 Summary of low and high effort synthesis results of circuit versions  | 76 |

| Table 5.2 Summary of TMR implementation results from low-optimized netlist      |    |

| (left section) and further aggressive optimization (right section)              | 77 |

| Table 5.3 Summary of TMR implementation results from high-optimized netlist     |    |

| (left section) and further gate sizing optimization (right section)             | 78 |

| Table 5.4 Summary of TMR synthesis results of generic cell-based and FPGA im-   |    |

| plementations                                                                   | 86 |

| Table 5.5 Classification of errors from the fault injection campaigns           |    |

| · · · · · · · · · · · · · · · · · · ·                                           |    |

# **CONTENTS**

| 1 INTRODUCTION                                                               | 16 |

|------------------------------------------------------------------------------|----|

| 1.1 Motivation                                                               | 16 |

| 1.2 Related work                                                             | 17 |

| 1.3 Objective                                                                | 17 |

| 1.4 Outline                                                                  | 18 |

| 2 RADIATION EFFECTS IN INTEGRATED CIRCUITS                                   | 19 |

| 2.1 Introduction                                                             |    |

| 2.2 Radiation environments                                                   |    |

| 2.2.1 Space environment                                                      |    |

| 2.2.2 Terrestrial environment                                                |    |

| 2.2.3 Artificial Man-made radiation.                                         |    |

| 2.3 Classification of radiation effects                                      |    |

| 2.3.1 Displacement Damage (DD)                                               |    |

| 2.3.2 Total Ionization Dose (TID) damage                                     |    |

| 2.3.3 Single-Event Effect (SEE)                                              | 26 |

| 2.3.3.1 Basic mechanisms of SEE                                              | 26 |

| 2.3.3.2 Types of SEEs                                                        |    |

| 2.4 Radiation effects in modern world                                        |    |

| 2.5 Conclusion                                                               |    |

| 3 FAULT-TOLERANCE TECHNIQUES FOR DIGITAL CIRCUITS                            |    |

| 3.1 Introduction                                                             |    |

| 3.2 Fault classification                                                     |    |

| 3.3 Enhanced Process                                                         |    |

|                                                                              |    |

| 3.4 Radiation Hardening by Design                                            |    |

| 3.4.1 Layout                                                                 |    |

|                                                                              |    |

| 3.4.1.2 Guard rings                                                          |    |

| 3.4.2 Circuit Level                                                          |    |

| 3.4.2.1 Hardened Memory cells                                                |    |

| 3.4.2.2 Rad-hard library of digital cells                                    |    |

| 3.4.2.3 Filtering                                                            |    |

| 3.4.2.4 Redundancy                                                           |    |

| 3.5 Conclusion                                                               | 50 |

| 4 AUTOMATED TMR DESIGN                                                       |    |

| 4.1 Introduction                                                             |    |

| 4.2 Implementation of digital Integrated Circuits                            |    |

| 4.3 Semi-custom design flow                                                  |    |

| 4.4 Proposed fault-tolerant design flow                                      |    |

| 4.4.1 TMR implementation process (TMRi)                                      |    |

| 4.4.2 TMR optimization Process (TMRo)                                        |    |

| 4.4.3 TMR verification process (TMRv)                                        |    |

| 4.5 Conclusion                                                               |    |

| 5 EXPERIMENTS                                                                | 73 |

| 5.1 Introduction                                                             |    |

| 5.2 Fault-tolerant cell-based design flow                                    |    |

| 5.2.1 Analyzing the impact of logic optimization in the designs              |    |

| 5.2.2 Analyzing the impact of adding TMR in area and performance             | 76 |

| 5.2.3 Analyzing the impact of performing logic optimization after adding TMR |    |

| 84  |

|-----|

| 85  |

| 87  |

| 91  |

| 93  |

| 94  |

| 96  |

| 98  |

| 106 |

|     |

#### 1 INTRODUCTION

#### 1.1 Motivation

Radiation effects have been one of the most serious issues in military and space applications but currently, they are an increasing concern even for commercial applications at the ground level. The radiation effects in semiconductor devices can vary from data corruption to permanent damage such as parametric shifts and complete device failure. For terrestrial applications, the transient faults or single-event effects (SEEs) caused by ionizing radiation are predominant (BAUMANN, 2005; DODD; MASSENGILL, 2003).

The main factors that affect the sensitivity of electronic devices to radiation are the reduction in the transistor's dimensions and the operating voltages in order to satisfy the demand for higher density, functionality and lower power. Whereas technology scaling enables the design of whole systems into a single die, also known as system-on-a-chip (SoC), they also increase design complexity and encounter reliability issues. Thus, ensuring the correct functionality of SoC designs becomes a challenging task.

In order to deal with the effects of radiation, fault-tolerant techniques are employed to prevent malfunctions of electronic systems. Protection or hardening of integrated circuits (ICs) against radiation effects can be done by the use of enhanced fabrication processes and strategies at different stages of the circuit design such as layout, circuit, system and embedded software levels (HUGHES; BENEDETTO, 2003; NICO-LAIDIS, 2005). The last approach is not based on a specific technology node, so it can be employed in commercial design flows. However, the implementation of fault-tolerant techniques is not automated by commercial electronic design automation (EDA) tools. The main issue of considering commercial tools to design radiation hardening circuits is that those techniques are based on some type of redundancy. Unfortunately, one typical optimization performed by the EDA tools is to remove redundant logic structures. As a consequence, the designer must restrict the features of the tool to preserve the inserted redundancies. Specialized tools to harden electronics systems are available as well but they affect the design cost because of the extra cost due to license purchase. Moreover, some country regulatory regimes restrict the export of technology related to spatial and military applications. The ITAR regimen imposed by the United States is a clear example of this limitation (BLOUNT, 2008; MONTENEGRO; PETROVIC; SCHOOF, 2010).

**Tool** Vendor/Institution License **Design level** Device **XTMR** Xilinx Commercial **Synthesis FPGA** Sinplify Premier Commercial **Synthesis** Synopsys **FPGA** Precision Hi-Rel Mentor Commercial Synthesis **FPGA FTMR** Cobham Gaisler Commercial RTL **FPGA TMRG CERN** Internal use **RTL ASIC** TLegUp Macquarie University Academic **HLS FPGA BL-TMR Brigham Young University** Academic Netlist **FPGA** IHP Academic Netlist **ASIC**

Table 1.1: Dedicated tools to implement TMR circuits

Source: From the author

#### 1.2 Related work

There are several dedicated tools that are able to implement the TMR technique in ASIC and FPGA designs (XILINX, 2017; SYNOPSYS, 2012; MENTOR, 2018; PRATT et al., 2005; KULIS, 2017; HABINC, 2002; LEE et al., 2017; STAMENKOVIC; PETROVIC; SCHOOF, 2013). Table 1.1 lists some of them and also indicates the step in the design where it is applied the replication of the circuit.

In spite of the features of the aforementioned tools to implement TMR design, none of them automates the verification of the resulting TMR circuit. Fault injection (FI) campaigns are usually employed to observe the behavior of a system in presence of faults. According to the complexity of the system and the design stage where is performed the FI, it can incur in large simulation times and even discover the TMR implemented was removed partially or completely after fabrication of the circuit. An interesting approach is the use of equivalence checking to speed up the verification process in an early design stage. Authors in (MELANY; LABEL; PELLISH, 2016; BELTRAME, 2015; BURLYAEV, 2015; SESHIA; LI; MITRA, 2007) details the challenges of using formal verification for design verification against soft errors.

#### 1.3 Objective

This work intends to overcome the issues encountered in the use of commercial EDA tools to design fault-tolerant circuits. The well known TMR technique is employed for that purpose. It was developed a methodology to automate the implementation, optimization, and verification of the TMR technique for complex circuits.

The main features of the devised approach in this work are:

- Reuse of any behavioral description such as HLS, RTL, and structured netlist.

- No dependence in the code-style of the behavioral description.

- Selection of the desired granularity of the TMR technique.

- Selectivity to protect an entire system or only its critical blocks.

- Use of customized voter elements.

- Insertion of voters to protect finite state machines.

- Redundancy of designs with undefined blocks (black boxes).

- Implementation of TMR circuit for ASIC and FPGA designs.

- Verification of the functionality and fault tolerant against soft errors.

- Further optimization of the resulting TMR circuit.

#### 1.4 Outline

This document is compound of 6 chapters. In Chapter 2 are described the radiation environments and their operating conditions that affect electronic systems. Moreover, the mechanisms of the radiation effects are explained in order to understand its interaction with electronics. Chapter 3 brings a compilation of several techniques to mitigate the effects of radiation in digital ICs. Chapter 4 shows the additional steps of the proposed fault-tolerant design flow to automate the design of TMR circuits. Chapter 5 shows the use of the proposed methodology through experimentation in two study-case circuits. Eventually, the conclusion of the present work and future works are exposed in Chapter 6.

#### 2 RADIATION EFFECTS IN INTEGRATED CIRCUITS

#### 2.1 Introduction

Development of man-made technology is highly driven by the use of microelectronics. Furthermore, the technological development of these miniaturized devices is powered by the advance of the semiconductor industry. The transistor, which is compound of complex semiconductor structures, becomes smaller, faster, dissipates less power and is cheaper to fabricate in each new technology generation. Despite these advantages, the constant shrink of the transistor's dimensions along with the shortcomings of the lithographic techniques employed in the fabrication process cause that characteristics of manufactured devices to be unpredictable. Moreover, devices become more susceptible to failures induced by radiation.

The levels of radiation that semiconductor devices encounter during their life cycle depend on the radiation environment and their operating conditions. In general, it is possible to identify three main environments where man-made technology is deployed and exposed to the effects of radiation: space, terrestrial and artificial-made environments. In the following sections, these environments and also the main effects of radiation are detailed.

#### 2.2 Radiation environments

#### 2.2.1 Space environment

The space environment is governed by three main sources of radiation: galactic cosmic rays, particles emitted by the Sun and particles trapped into earth's magnetic field.

Galactic cosmic rays are particles originated outside our solar system. Protons are the predominant particles in this environment (about 85%). These particles can reach very high energies of up to hundreds of GeV. As a consequence, the associated high power penetration makes unpractical to shield using reasonable amounts of material. Fluxes of these particles are in order of a few particles per cm<sup>2</sup> per second (CLAEYS; SIMOEN, 2002)

Solar activity generates solar particles that includes all types of elements, from protons to uranium and their flux depends on the solar cycle. The flux of solar particles

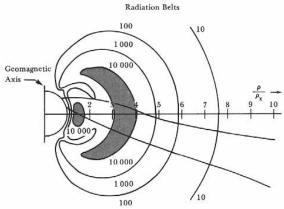

Figure 2.1: Two doughnut-shaped regions of trapped radiation with maximum intesity (inner and outter radiation belts)

Source: (Van Allen; FRANK, 1959)

can reach 10<sup>5</sup> particles/cm<sup>2</sup>/s with energies higher than 10 MeV (MOOR; DE, 2011). The solar activity consists of a cycle of 7 years of high activity and 4 years of low activity. Solar cycle influences galactic cosmic ray flux. During the high solar activity, the flux of cosmic rays is reduced due to the shielding effects of solar particles.

Charged particles can be trapped by the Earth's magnetic field. These trapped particles form two permanent doughnut-shaped regions knows as van Allen Belts (Van Allen; FRANK, 1959). The Inner belt is located from about 500 Km from the earth's surface and it extends to 13000 Km. Protons and low-energy electrons (from 1 up to 5 MeV) compose the inner belt. The Outer belt, located further out the Inner belt, contains high energy electrons with energies in the range from 10 to 100 MeV. Figure 2.1 depicts these charge trapped regions.

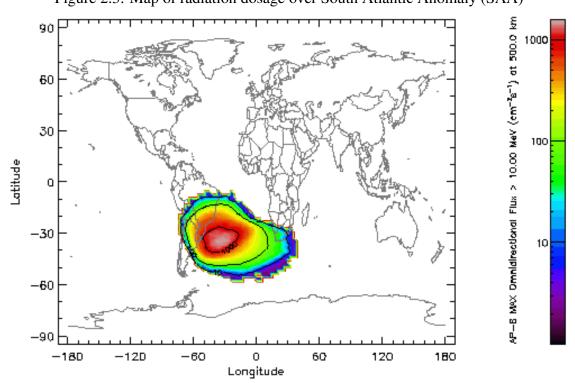

The earth's magnetic field is tiled 11° with respect to the geographic axis. In consequence, van Allen belts come closer to the earth surface over South America and South Atlantic (Figure 2.2). This region is called as South Atlantic Anomaly (SAA), where spacecrafts traveling inside the low Earth orbit (LEO) encounters the Inner belt (Figure 2.3).

#### 2.2.2 Terrestrial environment

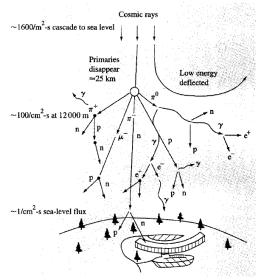

Particles in the wind solar are not able to penetrate Earth's atmosphere. Only cosmic ray particles with energies of more than 2 GeV go through the atmosphere layers and interact with Nitrogen and Oxygen atoms to produce a cascade of secondary particles (Figure 2.4). These high-energy cosmic rays, mainly protons and helium nuclei, are

500km alt.

Earth's Surface

SAA

SAA

Solution 1005

Solution 100

Figure 2.2: Inner belt is closer to the ground over South America and the South Atlantic

Source: (NASA, 2018)

Figure 2.3: Map of radiation dosage over South Atlantic Anomaly (SAA)

Source: (NASA, 2018)

Figure 2.4: Representation of cosmic rays cascade through the earth's atmosphere

Source: (ZIEGLER et al., 1996)

called primary cosmic rays. The interaction of primary cosmic rays with the atmosphere produces secondary cosmic rays (protons, muons, pions, neutrons) and an electromagnetic component. These particles have enough energy to create further particle cascades. However, the amount of secondary particles decreases when the shielding effect of the atmosphere overcomes the production of particles.

High-energy neutrons (> 10 MeV) or atmospheric neutrons, which are originated in the atmosphere's outer layers, are among the most abundant ionizing particle at the sea level. Despite neutrons are not charged particles, they can trigger nuclear reactions with chip materials, giving rise to charged secondary products. Atmospheric neutron flux depends on altitude, solar activity, latitude, and atmospheric pressure. The neutron flux of New York City, which is 14 n/cm2/hour with energy above 10MeV, is taking as a reference (GORDON et al., 2004). Tables are available in order to calculate neutron flux in other locations (JEDEC, 2006; WILKINSON, 2006). The neutron flux increases with altitude but around 15 km of altitude, neutron flux shows a peak. That is the reason why avionics is an application where neutrons are a serious concern for electronics. The energy spectrum in aircraft altitudes and on the ground is essentially identical (NORMAND; BAKER, 1993). On the other side, thermal neutrons exhibit short lifetime of around 0.1 s and energy levels about 25 meV. Their effects can be considerable because of the high probability of interacting with the boron isotope  ${}^{10}B$ . often found in inter-metal layers of integrated circuits or as a dopant. The reaction produces an alpha particle and  ${}^{7}Li$ , with a combined energy of 2.3 MeV. The flux of terrestrial thermal neutron presents an average value of 4 cm<sup>-2</sup>h<sup>-1</sup> at the sea level (DIRK et al., 2003).

Table 2.1: Alpha emissivities of various materials

| Material                  | Emissivity (cm <sup>-2</sup> h <sup>-1</sup> ) |

|---------------------------|------------------------------------------------|

| Fully Processed Wafers    | < 0.0004                                       |

| 30um thick Cu Metal       | < 0.0003                                       |

| 20um thick AlCu Metal     | < 0.0003                                       |

| Mold compound             | < 0.024 - < 0.0005                             |

| Flip Chip Underfill       | < 0.004 - < 0.0007                             |

| Eutectic Pb-based Solders | < 7.2 - < 0.0009                               |

Source: (JEDEC, 2006)

The second source of radiation-induced effects in electronics at terrestrial level is alpha particles. They are produced from the decay of radioactive elements intentionally used in integrated circuit fabrication or unexpected impurities. Table 2.1 shows alpha particle surface emissions from some key production materials used during the fabrication process.

#### 2.2.3 Artificial Man-made radiation

Some man-made radiation environments such as high-energy physics experiments and nuclear plants are very harsh in terms of ionizing radiation. For instance, Conseil Européen pour la Recherche Nucléaire (CERN) plans to use doses above 100 Mrad(Si) in the High-Luminosity Large Hadron Collider (HL-LHC), which is the planned upgrade of the current Large Hadron Collider (LHC) (BAGATIN; GERARDIN, 2015).

Ionizing radiation is also a concern in nuclear fission plants and future fusion plants under development. In the ITER project, which is a magnetic fusion reactor, large fluxes of neutrons with a maximum energy of 14.1 MeV are expected to hit electronic systems (BAGATIN et al., 2012).

#### 2.3 Classification of radiation effects

Exposition of electronic components to radiation can lead to displacement of atoms from their lattice sites and generation of electron-hole pairs (ionization). The former effect is known as displacement damage (DD) meanwhile, the last can be divided into total ionizing dose (TID) and single-event effects (SEE) according to the place where electron-hole pairs are deposited.

Recoil energy

1-2 keV

12-20 keV

Free defects

Single cascade subcascades

6-10 MeV

Proton energy

Figure 2.5: Defect types and sub-cascade formation related to primary knock-on atom energy in Silicon

Source: (BAGATIN; GERARDIN, 2015)

### 2.3.1 Displacement Damage (DD)

High-energy particles (neutrons, protons, heavy ions, electrons and indirectly photons) can transmit enough energy to a lattice atom of the target material to dislodge it from its original location. The capacity of an energetic particle to trigger a DD is established by its non-ionizing energy loss (NIEL) coefficient. NIEL measures the amount of energy lost per unit of length of the striking particle due to non-ionizing processes. It is directly related to the linear energy transfer (LET) or stopping power for ionizing events. Atomic displacement leads to the creation of a vacancy in the lattice and an interstitial defect in a non-lattice position (Frenkel pair). The first displaced atom, also known as primary knock-on atom (PKA), can induce further displacements of secondary knock-on atoms (SKA), which are able to generate additional defects. Resulting groups of defects close to each other are denominated clusters (SROUR; MARSHALL; MARSHALL, 2003). Figure 2.5 illustrates the defect types related to DD.

Vacancies travel across the lattice until they become stable because of the high probability of recombination of the Frenkel pair soon after its generation or due to the creation of other types of defects. More stable defects can be the result of the combination of two close vacancies (divacancies) or a vacancy and an impurity close to ones another (defect-impurity complexes).

DD causes alteration of electrical properties of the semiconductor crystal and can lead to degradation or failure of the device.

## 2.3.2 Total Ionization Dose (TID) damage

TID represents the accumulated amount of energy deposited by ionization process in the target material. In electronic devices, radiation-induced currents in insulators are generally not a problem because of lower mobility and lower amount of electron-hole pairs are created. However, charges can be trapped for long period of time. The trapped charges generate internal space-charge electric fields that can lead to a shift in the threshold voltage, reduction in transconductance and leakage current in MOS devices. In modern low-voltage MOSFETs, radiation-induced charge trapping in thin gate oxides is negligible.

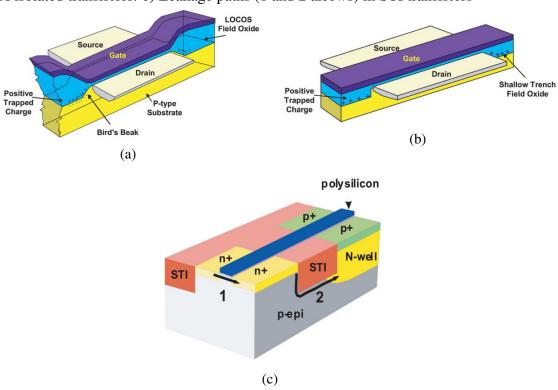

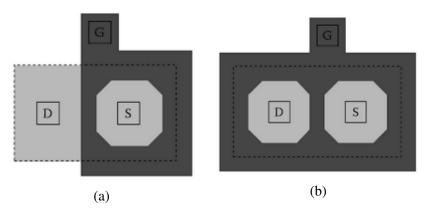

TID issues are associated with thick lateral isolation and oxide spacers. Unlike gates oxides that are thermally grown, insulation layers like field oxides and shallow trench isolation (STI), used in older and state-of-the-art devices respectively, are generally deposited (Figure 2.6. So, these oxides exhibit lower quality than gate oxides that becomes them more susceptible to TID effects (SCHWANK et al., 2008).

Figure 2.6: Cross section representation and positive trapped charge of a) LOCOS and b) STI isolated transistors. c) Leakage paths (1 and 2 arrows) in STI transistors

Source: (SCHWANK et al., 2008)

## 2.3.3 Single-Event Effect (SEE)

An SEE is caused when a single high-energy particle goes through sensitive regions of a microelectronic device. According to the consequences of an SEE over the device, it may be classified as soft effects and hard effects. The former leads to no permanent damage (nondestructive), meanwhile the last causes irreversible physical damage (destructive).

Unlike TID and DD effects that are cumulative and build up over time, an SEE is a stochastic event.

#### 2.3.3.1 Basic mechanisms of SEE

An ionizing particle deposits charge along its path in the target material. In consequence, electron-hole pairs are generated until the striking particle loses all of its energy. The energy loss per unit path length is described by the linear energy transfer (LET). The LET depends on the mass and energy of the incident particle and the target material. In Silicon, a charge deposition of 1 pC/um correspond to a LET of 97 MeV-cm2/mg.

The most sensitive regions under particle strikes are usually reversed-biased p-n junctions. There is a high-electric field into the depletion region of a reversed-biased junction. Thus, electron-hole pairs can efficiently be collected through drift process and it generates a transient current at the junction contact. Charge generated along the particle track can distortion temporarily the electrostatic potential of the junction into a funnel shape (field funnel). This funneling effect can enhance charge collection by extending the junction's electric field away from the junction and deep into the substrate.

Carriers generated beyond the depletion region may diffuse back toward the junction where they can be efficiently collected. However, diffusion occurs on a longer timescale. Figure 2.7 illustrates the resulting current pulse induced by a single radiation event.

In deep sub-micron MOS transistor, charge collection mechanism may be triggered when an alpha-particle at grazing strike passes through both drain and source of the transistor. In consequence, a disturbance in the channel potential can induce a short-lived current that mimics the on-state of the transistor. This charge collection effect is denominated as the alpha-particle source/drain penetration effect (ALPEN) (TAKEDA; HISAMOTO; TOYABE, 1988).

Furthermore, an ionizing particle can generate electron-hole pairs inside the well

Ion track n+ (b) Prompt Current (arbitrary unit) charge (c) Diffusion collection charge collection (a) Onset of event (a) (b) (c) 10<sup>-13</sup> 10-12 10-11 10<sup>-10</sup> 10<sup>-9</sup> Time (seconds)

Figure 2.7: Charge deposition and drift and diffusion collection processes. Pulse current duration

Source: (BAUMANN, 2005)

or body region of the transistor. The potential of the well is altered as well. For instance, in an NMOSFET, the generated carriers can be collected at the drain/well junction. Hole diffusion raises the potential of the p-well and the source/well junction becomes forward-biased. The source injects electrons into the channel and can be collected at the drain, strengthen the effect of the original particle-induce current. A parasitic bipolar effect is evidenced in this mechanism where the well, the source, and the drain represents the base, emitter and the collector respectively.

#### *2.3.3.2 Types of SEEs*

According to the effect of the SEE over the performance of a circuit, they can be classified as permanent or hard and soft for recovery faults. Table 2.2 gives a short description of the types of SEE.

#### 2.4 Radiation effects in modern world

Technology feature size of semiconductor devices has scaled from sub-micron to deep sub-micron, and in the last years to sub-100 nm. TID hardness of modern CMOS microelectronics components is high and the dominated radiation effects are related to single-event effects. Consequences of the rapidly shrinking geometry are the increasing of density integration, high operation frequencies, reduction of nodal capacities, and the use of lower power voltages. These factors contribute to SEEs are one of the key reliability issues in advanced integrated circuits.

Table 2.2: SEE classification

| SEE                            | Description                                                   |

|--------------------------------|---------------------------------------------------------------|

| Single-event upset (SEU)       | Corruption of electric state of a storage cell such as memory |

|                                | cell, latches, and flip-flops. SEU is often called as a soft  |

|                                | error.                                                        |

| Multiple-bit upset (MBU)       | A single particle strike changes the state of more than one   |

|                                | adjacent storage cells.                                       |

| Single-event transient (SET)   | Current/voltage transient pulse that can propagate and be     |

|                                | latched by a storage element leads to soft error.             |

| Single-event functional inter- | Perturbation of control registers or clock signal induces     |

| rupt (SEFI)                    | temporal loss of device functionality                         |

| Single-event latch-up (SEL)    | A strong and sudden increase of power supply current due to   |

|                                | radiation-induced activation of parasitic bipolar structures. |

| Single-event snapback (SES)    | A sustained high-current condition in SOI devices. The        |

|                                | bipolar amplification effect is similar to SEL                |

| Single-event burnout (SEB)     | Activation of parasitic bipolar structures causes burnout of  |

|                                | power devices (e.g. power MOSFETs and IGBTs).                 |

| Single-event gate rupture      | Irreversible rupture of transistor's gate oxide observed es-  |

| (SEGR)                         | pecially in power MOSFETs.                                    |

Source: From the author

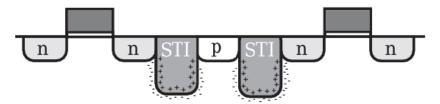

Pulse quenching consists in the SET width pulse reduction due to the delayed charge collection as a direct result of charge sharing. Figure 2.8 illustrates the pulse quenching mechanism (AHLBIN et al., 2009).

Quenched SET that Ion Strike propagates Adj. PMOS Hit PMOS Out3 Out1 Out2 **SET Pulse** at **Hit Node**  $V_{DD}$ G G D STI D S **Charge Diffuses** Well Ion strike deposits **Once adjacent PMOS** contact charge and injects turns off, drain SET pulse at Out2 collects charge and N-Well injects another SET P\* Deep-Well P Sub

Figure 2.8: Pulse quenching mechanism

Source: (AHLBIN et al., 2009)

Figure 2.9: Real-time soft-error rate measurements from three technological generations of single-port SRAMs: CMOS 130, 65 and 40 nm

Source: (AUTRAN et al., 2014)

The high density of transistors in the same die enables that multiple transistors can be vulnerable to a single ion strike. Multiple-cell upsets (MCU) events in planar devices can be caused by bipolar amplification (OSADA et al., 2004) and charge sharing (AMUSAN et al., 2008). Authors in (AUTRAN et al., 2014) present real-time soft-error rate measurements of advanced static random-access memory (SRAM) technologies conducted during the last decade on the Altitude Single Event Effects Test European Platform (ASTEP) and at the Underground Laboratory of Modane (LSM). They found experimentally up to 21, 8 and only 2 MCUs for the CMOS 40, 65 and 130 nm single-port SRAM technologies respectively. The MCU multiplicity (i.e. number of bit flips per MCU event) for the different technologies is depicted in Figure 2.9.

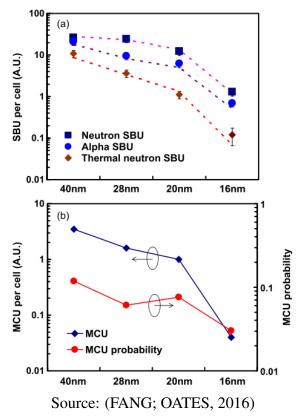

Authors in (FANG; OATES, 2016) characterize single-bit upset (SBU) and MCU events for 40, 28, and 20 nm planar SRAMs and 16nm FinFET SRAM. Figure 2.10 shows how both SBUs and MCUs per cell decrease with technology scaling. Moreover, FinFET SRAMs reach a significant reduction in both SBUs and MCUs with regard to planar devices.

Figure 2.10: Measurements of SBU and MCU events as a function of technology node

The use of new materials has decreased considerably the soft error rate. It is the case of strained silicon devices that achieve a higher ON current due to the boost of carrier mobility. Thereby, the use of strain transistors increases the driven current as well as the necessary critical charge to induce a current transient. Authors in (MAHATME et al., 2012) show a reduction of around 50% in the total SER and most importantly, the lower SER is achieved without any area penalty.

However, the presence of high-Z materials (like tungsten) can increase the SEU and MCU cross sections of high critical charge devices exposed to terrestrial neutrons (CLEMENS et al., 2011). Besides, even though the BPSG is not utilized in modern semiconductor processes,  $^{10}B$  can subsist within the back-end-of-line (BEOL) structure as a coating over tungsten plugs, for instance (AUTRAN et al., 2014).

Evaluation of HKMG (high-k metal gate) SRAM devices in (ZHANG, 2011) shows a negligible soft error rate induced by thermal neutrons comparing to the effect of terrestrial high-energy neutrons. Also, they conclude that thermal neutrons do not provoke MBU/SEFI/SEL in 32 nm HKMG SRAMs.

#### 2.5 Conclusion

This section brought a survey of the main concepts related to the effects of radiation in electronic devices. In summary, electronic systems are affected by radiation according to the environment where is deployed, and their operating conditions. The radiation environments can be classified in space, terrestrial and artificial environments. Each one of these environments is characterized by its own spectrum of particles and energy distribution. Radiation exposure of electronic components can lead to the displacement of atoms from their lattice sites (displace damage) and generation of electron-hole pairs (ionization). Accordingly, to the regions where electron-hole pairs are deposited into the structure of the transistor, ionization can affects insulators (TID) or reverse-biased p-n junctions (SEE). In modern devices at the sub-100nm node, microelectronic devices are more resilient to TID and SEEs become the key concern in the design of advanced integrated circuits.

## 3 FAULT-TOLERANCE TECHNIQUES FOR DIGITAL CIRCUITS

#### 3.1 Introduction

The effects of radiation on electronics devices represent an increasing concern for reliability even in terrestrial applications. Furthermore, the use of commercial technologies is not enough to ensure the correct functionality. Hence, strategies that deal with these issues becomes mandatory, especially in deep submicron technologies.

Protection or hardening of circuits against radiation effects can be taken into account in different categories. The employment of enhanced fabrication process is denominated as Radiation Hardening by Process (RHBP). On the other hand, the use of strategies at different stages of the circuit design is known as Radiation Hardening by Design (RHBD). This approach is not based on a technology process so, it can be considered in commercial applications.

The following sections will give a revision about the most popular RHBD techniques. Knowing these mitigation techniques is useful for planning strategies to accomplish the desired fault tolerance for the circuit. Moreover, the employment of these techniques must be accompanied by a trade-off between the improvement in soft error tolerance and the unavoidable penalties of area, power or performance that implicates their use.

#### 3.2 Fault classification

Any system is far away from being totally free of faults during their operational life. A fault is a physical defect or a flaw in hardware component or software. An error is the manifestation of a fault and represents the deviation from correctness or accuracy in the behavior of a component. Furthermore, the presence of an error in the system can propagate to its final output and cause malfunction. This deviation from the specified functionality of a system is known as a failure. Figure 3.1 depicts the hierarchy of fault, error and failure events.

Faults can be caused by several issues at the specification, implementation and fabrication stages of the design process. Also, external factors such as inappropriate operator's use or environmental disturbances can generate faults. On the other hand, according to the duration of the faults, they can be classified into permanent, intermittent or tran-

Malfunction of electronic system (Shut-down, abnormal operation, miscalculation)

Final output of PCB/product

- Recover is not possible without physical or economic damage in system (Reboot, reconfiguration, etc)

- SEU (Single Event Upset)

Figure 3.1: Fault, failure and error events

- Data is flipped in more than 1 memory elements

- · Impact is not deterministic on circuit, system

- · Detection and recover are possible

- · Nondestructive device level errors

(Single Event) Fault

Hazard/Failure

Error

- · Local transient (including SET)

- Noise

- Impact is not deterministic on device, circuit and system

- · Generally difficult to monitor/detect

- · Source is limited to single well

Source: (IBE, 2015)

sient. A permanent fault remains continue and stable until a corrective action is taken. An intermittent fault never disappears entirely, it oscillates between being quiescent and active. A transient fault goes away after some time and the functionality of the system is fully recovered. The origin of transient faults is mostly due to environmental conditions as electrical power drops, overheating, mechanical shock, electrostatic discharge, electromagnetic interference or ionizing radiation. This master thesis is focused on the radiation interference.

#### 3.3 Enhanced Process

Commercial CMOS fabrication process is not addressed to deal with the radiation effects. Thus, dedicated processes are used to avoid these undesired effects. The use of enhanced processes to mitigate these effects is called Radiation Hardening by Process (RHBP). The main drawback of using dedicated fabrication processes is its expensive production cost.

For instance, triple-well technology is typically used in deep submicron CMOS technology. This process consists of independent P-well and N-well regions. Thus, an NMOS transistor is electrically isolated in a p-type substrate. Figure 3.2 shows the iso-

Complementary Polysilicon Gates

(M3, M4 not shown)

SiO<sub>2</sub> W Plug

N - Well

Isolated P - Well

P - Substrate

Figure 3.2: Triple Well process

Source: (WILSON et al., 2011)

lated P-well embedded into N-well in a P-substrate. The triple-well process reduces substrate noise currents improving transistor performance, limiting the charge deposition by heavy ions and avoiding the latch-up effect (WILSON et al., 2011).

Another well-known approach to reducing the risk of latch-up is the addition of a thin epitaxial layer to increase the bulk resistance as depicted in Figure 3.3. Initially used to mitigate the latch-up effect, however, in scaled technologies epitaxial substrates showed to be affected by latch-up (SHELDON, 2005).

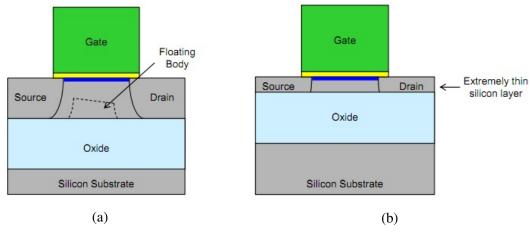

Silicon-on-insulator (SOI) CMOS technology historically was developed for radhard and power applications. This once niche market has now reached maturity and is challenging traditional bulk CMOS in all sectors of the market (KONONCHUK; NGUYEN, 2014).

An SOI structure is composed of an insulating layer that separates a top single-crystal silicon layer from the bulk substrate. In microelectronics, it is widely employed as a buried oxide (BOX) layer SiO2 as the insulator. Based on the thickness of the top

p+ n+ n+ n+ p+ p+

p-well NMOS n-well PMOS

p epitaxial layer

p+-substrate

Figure 3.3: Epitaxial bulk CMOS

Source: (SECRETARY, 2016)

Figure 3.4: Cross sections of a) Partially Depleted and b) Fully Depleted SOI MOSFETs

Source: (BOHR; MISTRY, 2011)

silicon layers, two types of SOI transistor structures can be identified: Fully and Partially Depleted Transistors.

Fully depleted (FD) SOI transistor has a very thin film silicon to form the channel (typically less than 50 nm). Hence, the whole body area is underneath the depletion region and there is no need to dope the channel. On the other side, the partially depleted (PD) SOI transistor uses a thicker silicon film (normally greater than 100 nm). This structure exhibits a no depleted area at the bottom of the body, forming a neutral region called floating body. Figure 3.4a and 3.4b illustrates the PD SOI and the FD SOI transistors respectively.

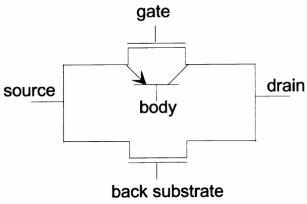

In presence of radiation, parasitic structures illustrated in Figure 3.5 are activated in the SOI structure (SCHWANK et al., 2003). The floating body can behave as the base of a parasitic bipolar transistor. In order to avoid the activation of this undesired element,

Figure 3.5: SOI parasitic a)PBJT and b) MOS

Source: (SCHWANK et al., 2003)

the body region can be tied to the source potential or ground. So, the radiation generated charge can be removed through the body tie. On the other hand, the bulk substrate and the thick BOX can act as the gate and the gate insulator of the parasitic back gate transistor.

SOI devices are completely immune to latch-up, although they can be affected by single-event snapback originated by the parasitic bipolar transistor.

## 3.4 Radiation Hardening by Design

As an alternative to the use of enhanced CMOS fabrication processes, Radiation Hardening by Design (RHBD) consists of designing integrated circuits using available commercial fabrication processes. In order to accomplish with the desired fault tolerance level, RHBD techniques may be applied at different levels of design. RHBD takes advantage of process maturity, high levels of die yield, availability of many silicon foundries, low cost and quick prototyping, low volume of production and the portability to modern technologies.

#### **3.4.1 Layout**

RHBD layout techniques have been demonstrated to be very effective in eliminating single event latch-up and preventing radiation-induced leakage currents related with Total Ionizing Dose (TID) (CAO PAUL LEROUX, 2015). Furthermore SET and SEU are also mitigated (SECRETARY, 2016). Additionally, standard layout techniques also can improve radiation tolerance. For instance, folded MOSFET transistors are drawn as interconnected fingers with reduced drain and source areas. Thus, the folding technique reduces the sensitive p-n cross-section areas (SCHRIMPF; FLEETWOOD, 2004).

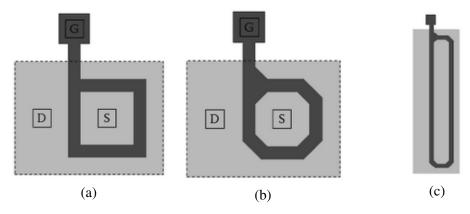

#### 3.4.1.1 Edgeless transistor

A very effective RHBD practice is to avoid the edge leakage. The layout draws a closed gate shape separating the drain and source region of the CMOS transistor. The transistor's edge is designed to connect common implant areas such as source-source or drain-drain or to eliminate completely all the edges, where only the drain or source touch the edge (Figure 3.6). The former receives the name of annular transistor and the last is denoted as the Enclosed Layout Transistor (ELT) (Figure 3.7).

Figure 3.6: Annular transistor with a) 90o angle, b) 45o angle and large W/L case

Source: (CRESSLER; MANTOOTH, 2012)

The main drawbacks of the ELT transistor are its relatively large area and its in-accurate modeling (CAO PAUL LEROUX, 2015). The minimum typical width of the annular transistor is around four to five times the standard transistor's minimum width. On the other side, it is possible to draw a small width ELT (CRESSLER; MANTOOTH, 2012).

Reduction of the drain's area diminishes the cross-section of the device and consequently the sensitivity to SET and SEU. Thus, the drain is generally located on the internal side of the ring-shaped transistor (CAMPLANI et al., 2014). This approach is applied typically on NMOS transistors. PMOS transistors can be designed conventionally because is not prone to current leakage, reducing the area overhead.

Figure 3.7: Enclosed layout transistors with a) just source enclosed and b) both drain and source enclosed

Source: (CRESSLER; MANTOOTH, 2012)

Figure 3.8: Cross section of two adjacent NMOS transistor with guard band between them

Source: (CAMPLANI et al., 2014)

## 3.4.1.2 Guard rings

Guard rings consist of p-well or n-well diffusions that are inserted around NMOS or PMOS transistors respectively. In Figure 3.8, the use of guard rings allows reducing the leakage current through thick field oxides between N-type diffusions of adjacent NMOS transistors. Moreover, guard rings are used to prevent the latch-up effect by reducing the gain of the parasitic thyristor structure.

The main drawback is also the increase of the area of RHBD circuits by the use of additional p-well diffusions. This structure is available in conventional CMOS process. Thus, this approach is commonly employed along with the edgeless layout technique.

### 3.4.2 Circuit Level

Design of RHBD circuits takes advantage of concepts with regard to circuit topologies, electrical properties, and redundancy. Circuits can contain interconnecting transistors, in order to create logic cells, or use a set of logic cells to design a more complex circuit. Thus, two views of design are defined: cell view and block view respectively.

### 3.4.2.1 Hardened Memory cells

The most representative case of RHBD circuit at the cell view is the design of hardened memory cells. In the literature can be found a great diversity of storage elements designed to be insensitive to radiation-induced single event upsets. However, most of them are derived from well-known designs. The importance of understanding the operation of this cells is due to they can be found in commercial Rad-Hard libraries of standard cells for ASICs.

The use of decoupling or feedback resistors in SRAM cells is an effective hardening approach to reduce the SEU tolerance (WEAVER et al., 1987). Decoupling resistors

Figure 3.9: Resistor memory cell schematic

delays the propagation of the current transient through the regenerative feedback of the SRAM cell. Thus, increasing the resistors' values leads to the reduction of SEU susceptibility of the SRAM cell. Figure 3.9 illustrates the schematic of an SRAM cell with the decoupling resistors.

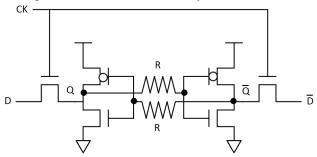

The Dual Interlocked Storage Cell (DICE) was proposed as a hardened storage element insensitive to single-event effects. It does not require special constraints on transistor sizes (CALIN; NICOLAIDIS; VELAZCO, 1996). The DICE structure is basically a 4-node structure. Figure 3.10 shows the composition of the latch DICE. If a node Xi is affected by a single event effect, the transistors controlled by this node are affected. However, the other transistors float storing its correct values temporally until the SEE disappears. Because of the necessary time to propagate the see through the rest of nodes is very high (AMUSAN et al., 2007), the nodes return to their internal values. Figure 3.10 shows master-slave flip-flops implemented using two DICE latches (WANG; GONG, 2004).

Several commercial rad-hard libraries are based on the DICE structure for memory cells. Cogenda, Atmel, ATK, and Aeroflex are some of them (SECRETARY, 2016).

P0 P1 P2 P3

X0 X1 X2 X3

N0 N1 N2 N3

CK

N4 N5 N6 N7

D

Figure 3.10: DICE memory cell schematic

Source: (CALIN; NICOLAIDIS; VELAZCO, 1996)

Figure 3.11: HIT memory cell schematic

Source: (BESSOT; VELAZCO, 1993)

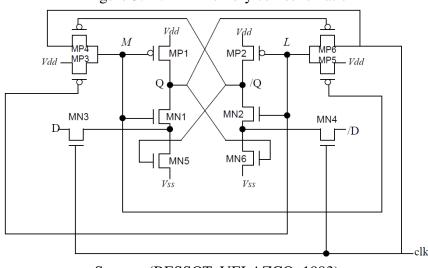

The Heavy Ion Tolerant (HIT) cell was designed for fast recovery time after a single event upset. Moreover, its low power consumption reduces the impact on performance (BESSOT; VELAZCO, 1993). The HIT cell is built using two storage structures and it is shown in Figure 3.11. The nodes Q and Qhat conserves their respective values while the clock signal is inactive. To modify the value stored in the cell the new values have to be put in the data lines. When the clock signal goes to high, the transistor MP4 or MP6 is responsible for activating the transistors MN1 and MN2. If a particle strikes the nodes Q, Qhat or M for an initial value of Q in high level, the circuit of the cell restores its original values but is affected when more than one out of nodes is attacked.

In (ARIMA et al., 2004) proposes an almost free soft error latch that keeps its state on three storage nodes PDH, NDH, and DH. The error in one node never propagates to the other nodes. The recovery process after a soft error is not depended on the duration of the charge is deposited doing the circuit almost soft-error free for any nuclear radiation energy spectrum. PDH and NDH nodes never fail simultaneously because of the polarity of soft errors; however, one of them along with the DH node might fail as a result of one neutron impact. Figure 3.12 shows the schematic of the Immune Latch Circuit.

The Soft Error Immune Latch (SEILA) developed in (UEMURA et al., 2010) is a robust latch that enhances single event rate efficiency against multi-node single event effects (MNSEEs) and single event transients on the local clock. The SEILA cell is an inter-lock type storage structure hence data corruption on one node can not corrupt storage data on the storage structure (Figure 3.13a). The data in the latch is corrupted if two critical areas, the NMOS areas on node n1 and n2, are affected by an ion strike. Though

PDH P1

CKND P5

PBH P2

PBH P2

PBH P4

P1

CKND P5

P3

PAH P4

N5

CKD N5

N5

NN1

NN1

NN1

Figure 3.12: Immune Latch diagram

Source: (ARIMA et al., 2004)

Figure 3.13: a) SEILA memory cell schematic, b) and c) shows the same area utilization for single and double height cell schemes respectively

Source: (UEMURA et al., 2010)

if a third area is compromised, the PMOS area on node 3, the data is preserved. The last one is denominated canceling area. In order to accomplish with this placement approach, the layout latch is based on double height cell (DHC) scheme illustrated in Figure 3.13b. Thus the two critical areas are keeping away putting them at the top and at the bottom of the cell layout. Otherwise, MNSEEs are attenuated by placing the canceling area between the two critical areas. It can be noticed that the size of the cell of DHC is not changed from single height cell. The mitigation of transients on the local clock of the latch is achieved by using redundant clock buffers.

In (MITRA et al., 2006) is proposed the Built-In Soft Error Resilience (BISER) technique that uses the advantage of the reduced overhead generated by replication. The BISER technique incorporates a voter for correcting soft errors. The voter is based on

Weak keeper 1D ΑВ C-OUT

0 0 C-OUT 0 1 Previous -element В value retained Previous Clock alue retained Redundant Latch

Figure 3.14: a) BISER latch diagram and b) C-element diagram and truth table

Source: (MITRA et al., 2006)

(b)

(Scan Reuse)

(a)

Figure 3.15: a) SERT diagram and b) half transition NAND gate

Source: (SHULER et al., 2009)

the use of the C-element, also called guard gate, along with a weak keeper in its output. Figure 3.14a and Figure 3.14b show respectively the configuration used for correcting errors in latches and the C-element along with its truth table.

The Single Event Resistant Topology (SERT) is a dual-rail latch design. It does not present state conflicts in its internal nodes under single event transient, so recovery is no dependent on transistor sizing (SHULER et al., 2009). The dual-rail SERT latch is shown in Figure 3.15a. The SERT latch scheme consists of an input multiplexer and half transition NAND gates. The half transition NAND gate is almost identical with the C-element (Figure 3.15b) though without one of the series-PMOS.

## 3.4.2.2 Rad-hard library of digital cells

Radiation hardened (rad-hard) libraries are developed over commercial process based on the use of the previously detailed layout techniques and including hardening memory cells. Also, some rad-hard libraries are developed over RHBP technology to improve the reliability of the circuits.

Table 3.1: Radhard standard cell libraries

| Radiation hardened Library  | CMOS Technology node |

|-----------------------------|----------------------|

| ATC18RHA ATMEL              | 180 nm               |

| ATK                         | 350 nm               |

| C65SPACE STMicroelectronics | 65 nm                |

| CERN                        | 250 nm               |

| UT90nHBD/UT130nHBD Cobham   | 90 and 130 nm        |

| Cogenda                     | 65 and 130 nm        |

| DARE IMEC                   | 180 nm               |

| BAEsystems                  | 150 nm               |

| Radlib Redcat               | 130, 150 and 180 nm  |

| Ramonchips                  | 130 and 180 nm       |

In Table 1.1 are listed several available commercial rad-hard standard cell libraries. Author in (SHULER, 2015) makes an interesting proposal relying on the uses a small cell count RHBD library. The aim of using a reduced set of cells is to make designs portable between processes of the same technology node. Moreover, to reduce the effort for the migration to modern nodes. The basic 10-cell library is composed by the following gates: an inverter, a buffer, a strong buffer, 3 variations of NAND, only one NOR, two types of 2-input MUX and a tristate buffer. Additionally, it is included a delay cell for SET filtering in dual input circuits. One of the implementations for MUX is for combinational logic use and the other one is employed to build dual interlocked memory cells as DICE or SERT. The tristate buffer may be used to implement the guard gate (C-element).

#### *3.4.2.3 Filtering*

A transient pulse can be filtered or masked by the intrinsic properties of a combinational circuit. This natural capability to avoid the propagation of glitches is strongly depended on the physical and the temporal location of the fault. The fault masking mechanisms can be classified into logical, electrical and window (timing) masking.

Logical masking avoids the propagation of a transient fault due to the input values of a multi-input gate, which receives the faulty signal. Electrical masking occurs when a transient pulse is attenuated through its propagation path. So, the pulse amplitude is not enough to induce an error. Furthermore, sizing up a gate reduces the probability that a striking particle cause a glitch of strong magnitude. Authors in (RAO; BLAAUW; SYLVESTER, 2006) show an average reduction in the soft error rate of around 8 times after and area penalty of only 5% after applying gate sizing over a set of benchmark

circuits.