## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

## HENRIQUE PLÁCIDO

# Tackling the Drawbacks of a Lagrangian Relaxation Based Discrete Gate Sizing Algorithm

Thesis presented in partial fulfillment of the requirements for the degree of Master of Microeletronics

Advisor: Prof. Dr. Ricardo Augusto da Luz Reis

Porto Alegre November 2018

### **CIP** — **CATALOGING-IN-PUBLICATION**

## Plácido, Henrique

Tackling the Drawbacks of a Lagrangian Relaxation Based Discrete Gate Sizing Algorithm / Henrique Plácido. – Porto Alegre: PGMICRO da UFRGS, 2018.

100 f.: il.

Thesis (Master) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica, Porto Alegre, BR-RS, 2018. Advisor: Ricardo Augusto da Luz Reis.

Leakage Power Minimization.

Timing Constraints.

Lagrangian Relaxation.

Cell Selection.

Physical Design.

EDA.

Microelectronics.

Reis, Ricardo Augusto da Luz.

Título.

## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Rui Vicente Oppermann Vice-Reitora: Prof<sup>a</sup>. Jane Fraga Tutikian

Pró-Reitor de Pós-Graduação: Prof. Celso Giannetti Loureiro Chaves Diretora do Instituto de Informática: Prof<sup>a</sup>. Carla Maria Dal Sasso Freitas Coordenadora do PGMICRO: Prof<sup>a</sup>. Fernanda Lima Kastensmidt

Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

| "If I have seen farther than others,               |

|----------------------------------------------------|

| it is because I stood on the shoulders of giants." |

| — SIR ISAAC NEWTON                                 |

## **ACKNOWLEDGMENTS**

To my family, for the love and support through all these years.

To my advisor, Ricardo Reis, for accepting me as his student.

To Guilherme Flach, for sharing with me his knowledge and for all the meetings we had during the development of this work.

#### **ABSTRACT**

The shrink of the devices sizes allows the number of transistors in the integrated circuits to grow, leading to an increase in the leakage power. The discrete gate sizing technique consists in assigning each gate of the circuit to a cell option among the implementation versions available in the cell library. It is a powerful method used in the design flow to carry out optimizations, e.g., timing violations fixing and power and/or area minimization. The Lagrangian relaxation based gate sizer proposed in [Flach et al. 2013] has the best leakage power results published so far for the 2012 ISPD Gate Sizing Contest benchmarks. However, its Lagrangian relaxation phase has some drawbacks. It requires many iterations to converge to a good solution in terms of leakage power. Also, during the initial iterations, the leakage power blows up, so a parcel of the iterations is used to reduce this peak of leakage power. Yet, the Lagrangian relaxation subproblem solver does not rely on any technique to perform cell option candidate filtering, so it can be very timing consuming. Therefore, in this work, the discrete gate sizing flow proposed in [Flach et al. 2013] is extended to tackle the drawbacks aforementioned. It is proposed some enhancements to the Lagrange multiplier update formula that enable the Lagrangian relaxation core to converge faster. It is also used a scaling factor to properly scale timing cost and leakage power when evaluating a cell candidate in the Lagrangian relaxation subproblem solver. So, the scaling factor, alongside the new Lagrange multipliers update method, controls the leakage power blow up during the initial Lagrangian relaxation iterations. Moreover, it is applied a cell option candidate filtering strategy to reduce the runtime of each Lagrangian relaxation iteration. Finally, the post-processing timing recovery and power recovery phases of the original work are improved to reduce the overall flow runtime. The new approach achieved leakage power results similar to the baseline work, taking  $4.28\times$  fewer iterations and  $9.11\times$  fewer cell option candidates evaluation, on average, in the Lagrangian relaxation phase. Also, the leakage power blow up during the initial iterations of the Lagrangian relaxation was reduced from  $9.55\times$  the final value, on average, to  $2.74 \times$  the final value, on average. Finally, compared to [Sharma et al. 2017], which is the fastest gate sizing algorithm published so far, the new approach produced, without using the post-processing power recovery phase, similar leakage power results in general, performing slightly better for the largest benchmark.

**Keywords:** Leakage Power Minimization. Timing Constraints. Lagrangian Relaxation.

Cell Selection. Physical Design. EDA. Microelectronics.

# Tratando as Desvantagens de um Algoritmo de Dimensionamento Discreto Baseado em Relaxação Lagrangiana

#### **RESUMO**

A redução das dimensões dos dispositivos permite que o número de transistores nos circuitos integrados aumente, levando ao aumento da potência estática do circuito. A técnica de dimensionamento discreto de portas lógicas consiste em atribuir a cada porta lógica do circuito uma célula dentre todas as opções de implementação disponíveis na biblioteca de células. É uma poderosa técnica empregada no fluxo de síntese de circuitos integrados para realizar otimizações, como, por exemplo, remoção de violações de timing e minimização de potência e/ou área do circuito. O algoritmo de dimensionamento discreto de portas lógicas baseado em relaxação Lagrangiana proposto em [Flach et al. 2013] apresenta os melhores resultados em termos de potência estática publicados até então para os benchmarks da competição de dimensionamento discreto de portas lógicas do ISPD que ocorreu em 2012 [Ozdal, Burns and Hu 2012]. Contudo, a fase de relaxação Lagrangiana desse algoritmo possui algumas desvantagens. São necessárias muitas iterações para o algoritmo convergir para uma boa solução em termos de potência estática. Também, durante as iterações iniciais, a potência estática aumenta consideravelmente, assim, uma parcela das iterações é utilizada para reduzir o pico de potência estática. Ainda, o resolvedor do subproblema Lagrangiano não utiliza nenhuma técnica de filtragem de células candidatas, então, o algoritmo pode ser muito lento. Então, nesse trabalho, o fluxo de dimensionamento discreto de portas lógicas proposto em [Flach et al. 2013] é estendido para tratar as desvantagens citadas. São propostas algumas melhorias para a fórmula de atualização dos multiplicadores de Lagrange que permitem a fase de relaxação Lagrangiana convergir mais rapidamente. Também é utilizado um fator de escala para balancear adequadamente o custo de timing e a potência estática quando uma célula candidata é avaliada pelo resolvedor do subproblema Lagrangiano. Assim, o fator de escala, juntamente com o novo método de atualização dos multiplicadores de Lagrange, controla a explosão de potência estática durante as iterações inicias da fase de relaxação Lagrangiana. Ainda, é utilizada uma estratégia de filtragem de células candidatas para reduzir o tempo de execução das iterações do algoritmo de relaxação Lagrangiana. Finalmente, as etapas de pós-processamento timing recovery e power recovery foram modificadas para reduzir o tempo de execução do fluxo. A nova abordagem atingiu resultados em termos

de potência estática similares ao algoritmo original, tendo 4,28 vezes menos iterações, em média, e 9,11 vezes menos testes de células candidatas, em média, na fase de relaxação Lagrangiana. Também, o grande aumento de potência estática durante as iterações iniciais da relaxação Lagrangiana foi reduzido de 9,55 vezes a potência final obtida, em média, para 2,74 vezes a potência final obtida, em média. Finalmente, comparado ao algoritmo de dimensionamento discreto de células proposto em [Sharma et al. 2017], que é o mais rápido publicado até então, a ferramenta desenvolvida nesse trabalho produziu, mesmo não utilizando a fase de pós processamento *power recovery*, resultados muito próximos em termos de potência estática, tendo resultados levemente melhores para o maior *benchmark*.

**Palavras-chave:** Minimização de potência Estática, Restrições Temporais, Relaxação Lagrangiana, Seleção de Células, Síntese Física, EDA, Microeletrônica.

## LIST OF ABBREVIATIONS AND ACRONYMS

ALU Arithmetic and Logic Unit

CAD Computer Aided Design

CISC Complex Instruction Set Machine

CPS Critical Path Sizing

CTS Clock Tree Synthesis

DRC Design Rule Check

EDA Electronic Design Automation

ERC Electrical Rule Check

Fast-GTR Fast Greedy Timing Recovery

GTR Global Timing Recovery

GWTW Go-With-The-Winners

HDL Hardware Description Language

IC Integrated Circuit

ISPD International Symposium on Physical Design

KKT Karush-Kuhn Tucker

LDP Lagrangian Dual Problem

LM Lagrange Multiplier

LM Linear Programming

LR Lagrangian Relaxation

LRS Lagrangian Relaxation Subproblem

LVS Layout Versus Schematic

MGS Multi-Gate Sizing

Min-Clock LR Minimum Clock Period Lagrangian Relaxation

NLDM Non-Linear Delay Model

PP Primal Problem

PR Power Recovery

PR-LR Power Reduction Lagrangian Relaxation

PRFT Power Reduction With Feasible Timing

PVT Process, Voltage and Temperature

RGS Rapid Gate Sizing

RISC Reduced Instruction Set Machine

RTL Register Transfer Level

SA Simulated Annealing

SPEF Standard Parasitic Extraction Format

STA Static Timing Analysis

TNS Total Negative Slack

TR Timing Recovery

TR-LR Timing Recovery Lagrangian Relaxation

WNS Worst Negative Slack

## LIST OF FIGURES

| Figure 1.1 Standard Cell Based Design Flow.                                              | 16  |

|------------------------------------------------------------------------------------------|-----|

| Figure 1.2 Physical Synthesis Flow.                                                      | 18  |

| Figure 1.3 Partitioning example.                                                         | 18  |

| Figure 1.4 Random placement versus placement obtained with the simulated an-             |     |

| nealing algorithm.                                                                       | 19  |

|                                                                                          |     |

| Figure 2.1 High level representation of a synchronous digital circuit.                   |     |

| Figure 2.2 Clock signal at two flip-flops considering skew and jitter                    |     |

| Figure 2.3 Example of a portion of a synchronous digital circuit                         |     |

| Figure 2.4 Directed timing graph.                                                        |     |

| Figure 2.5 Timing sense of arcs.                                                         |     |

| Figure 2.6 Propagation delay of an inverter.                                             |     |

| Figure 2.7 Rise and fall transition times.                                               |     |

| Figure 2.8 Example of an interconnection.                                                |     |

| Figure 2.9 Distributed net model.                                                        | 29  |

| Figure 2.10 Reduced net model.                                                           |     |

| Figure 2.11 Lumped capacitance model.                                                    | 29  |

| Figure 2.12 Elmore example.                                                              | 30  |

| Figure 2.13 Arrival time and slew propagation                                            | 32  |

| Figure 2.14 Required time propagation.                                                   | 33  |

| Figure 2.15 Sources of leakage current.                                                  | 36  |

|                                                                                          |     |

| Figure 3.1 Inverter gates with different driver strengths and threshold voltages         | 37  |

| Figure 4.1 Example of timing requirements propagation.                                   | 13  |

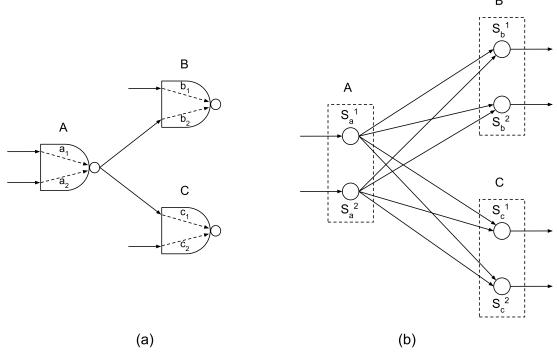

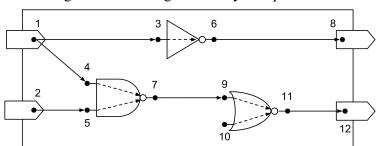

| Figure 4.2 (a) Example of subcircuit. (b) Corresponding graph model                      |     |

|                                                                                          |     |

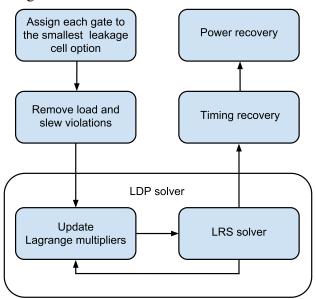

| Figure 4.3 RGS flow.                                                                     | 00  |

| Figure 5.1 Overall flow of the baseline sizer                                            | 64  |

| Figure 5.2 Example of Lambda-Delay Cost Computation                                      |     |

| Figure 5.3 Example of Lambda-Delay Sensitivity Computation                               |     |

| Tigure one Zhampie of Zamoda Belay Sensitivity Companion                                 | 0 > |

| Figure 6.1 Sizer flow with the modifications proposed in this work                       | 76  |

| Figure 6.2 Cell option candidate filtering.                                              |     |

| Figure 6.3 Timing sensitivity computation.                                               | 84  |

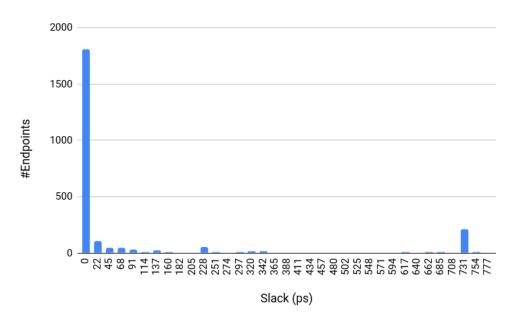

| Figure 6.4 Slack histogram for the DMA_fast benchamrk                                    |     |

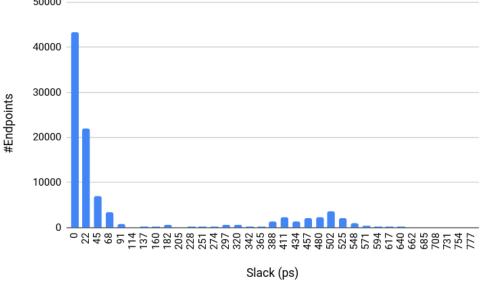

| Figure 6.5 Slack histogram for the netcard_fast benchamrk                                |     |

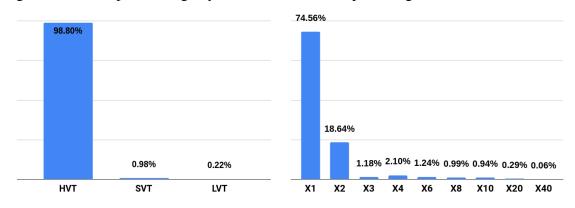

| Figure 6.6 Cell options usage by $V_{th}$ and sizes for the pci_bridge32_slow benchmark  |     |

| Figure 6.7 Cell options usage by $V_{th}$ and sizes for the pci_bridge32_fast benchmark. |     |

# CONTENTS

| 1 INTRODUCTION                                       | 14  |

|------------------------------------------------------|-----|

| 1.1 Standard Cell Based Design Flow                  | .15 |

| 1.1.1 High Level Synthesis                           | 16  |

| 1.1.2 Logic Synthesis                                |     |

| 1.1.3 Physical Synthesis                             |     |

| 1.2 Objectives of this work                          |     |

| 1.3 Organization of this Work                        |     |

| 2 CONCEPTS                                           |     |

| 2.1 Static Timing Analysis                           |     |

| 2.1.1 Synchronous Digital Circuits                   |     |

| 2.1.2 Modeling of Synchronous Digital Circuits       |     |

| 2.1.3 Timing Sense                                   |     |

| 2.1.4 Propagation Delay of a Timing Arc              |     |

|                                                      |     |

| 2.1.5 Transition Time (Slew)                         |     |

| 2.1.6 Time Modeling                                  |     |

| 2.1.6.1 Cells                                        |     |

| 2.1.6.2 Interconnections                             |     |

| 2.1.7 Timing Information                             |     |

| 2.1.8 Timing Propagation                             |     |

| 2.1.9 WNS and TNS                                    |     |

| 2.1.10 Criticality and Centrality                    |     |

| 2.2 Power Consumption in CMOS Technology             |     |

| 3 GATE SIZING                                        | .37 |

| 3.1 Gate Sizing Classification                       | .37 |

| 3.1.1 Continuous Gate Sizing                         | .38 |

| 3.1.2 Discrete Gate Sizing                           | .38 |

| 3.2 Lagrangian Relaxation based Discrete Gate Sizing | 39  |

| 4 RELATED WORK                                       | 42  |

| 4.1 Early Work                                       | 42  |

| 4.1.1 [Chan 1990]                                    |     |

| 4.1.2 [Coudert 1996] and [Coudert 1997]              |     |

| 4.1.3 [Chinnery and Keutzer 2005]                    |     |

| 4.1.4 [Held 2009]                                    |     |

| 4.1.5 [Liu and Hu 2010]                              |     |

| 4.1.6 [Huang, Hu and Shi 2011]                       |     |

| 4.1.7 [Ozdal, Burns and Hu 2012]                     |     |

| 4.1.8 [Rahman and Sechen 2012]                       |     |

| 4.1.9 [Hu et al. 2012]                               |     |

| 4.1.10 [Li et al. 2012]                              |     |

| 4.1.11 [Reimann et al. 2013]                         |     |

|                                                      |     |

| 4.1.12 [Livramento et al. 2013]                      |     |

| 4.2 State-of-the-Art                                 |     |

| 4.2.1 [Flach et al. 2014]                            |     |

| 4.2.2 [Sharma et al. 2015]                           |     |

| 4.2.3 [Reimann, Sze and Reis 2016]                   |     |

| 4.2.4 [Yella and Sechen 2017]                        |     |

| 4.2.5 [Sharma et al. 2017]                           |     |

| 4.3 Summary                                          | 61  |

| 5 BASELINE DISCRETE GATE SIZING FLOW                                    | 62 |

|-------------------------------------------------------------------------|----|

| 5.1 Formulation                                                         | 62 |

| 5.2 Baseline Flow Overview                                              |    |

| 5.2.1 Load and Slew Violations Removal                                  | 64 |

| 5.2.2 Lagrangian Dual Problem Solver                                    | 65 |

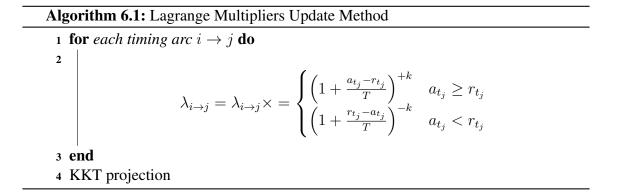

| 5.2.2.1 Lagrange Multipliers Update Method                              |    |

| 5.2.3 Lagrangian Relaxation Subproblem Solver                           |    |

| 5.2.3.1 Lambda-Delay Cost of a Cell Option                              | 67 |

| 5.2.3.2 Back-Propagated Cumulative Lambda-Delay Sensitivity             | 69 |

| 5.2.4 Timing Recovery                                                   |    |

| 5.2.5 Power Recovery                                                    | 71 |

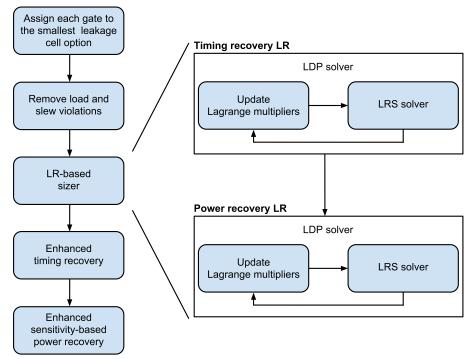

| 6 PROPOSED IMPROVEMENTS                                                 | 74 |

| 6.1 Points for Improvement in the LR Core of the Baseline Work          | 74 |

| 6.2 New Lagrangian Relaxation Formulation                               | 74 |

| 6.3 Updated Flow                                                        | 75 |

| 6.3.1 Timing Recovery Lagrangian Relaxation                             | 76 |

| 6.3.2 Power Reduction Lagrangian Relaxation                             | 78 |

| 6.3.3 Average Delay per Leakage Scaling Factor Calculation              | 80 |

| 6.3.4 Post-LR Optimization Phases Enhancement                           | 81 |

| 6.3.4.1 Enhanced Timing Recovery                                        | 81 |

| 6.3.4.2 Enhanced Sensitivity-Based Power Recovery                       | 83 |

| 6.4 Experimental Results                                                | 84 |

| 6.4.1 Runtime Reduction in LR Phase Using Cell Option Candidates Filter | 90 |

| 6.4.2 Slack Histogram Compression                                       | 91 |

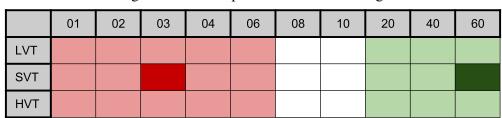

| 6.4.3 Cell Options Usage                                                | 92 |

| 7 CONCLUSION                                                            | 94 |

| 7.1 Future Works                                                        | 95 |

| REFERENCES                                                              | 96 |

#### 1 INTRODUCTION

In 1958, the first integrated circuit (IC) was designed at Texas Instruments by Jack Kilby. This technology allowed the integration of the components of an electronic circuit in the same substrate of semiconductor material [Rabaey, Chandrakasan and Nikolic 2003]. Initially, the integrated circuits were manually designed. However, with the increasing number of components, this method has become prohibitive. For instance, at the end of the 1980s, there were circuits with more than one million of transistors, such as the Intel 486 DX [Intel 2008]. Besides, time-to-market, which is the time from conception of a product to its sale, is a crucial factor, since the company must launch the product into the market in the smallest time to ensure its success. Therefore, computer aided design (CAD) tools, also known as electronic design automation (EDA) tools, were developed to automate the design of integrated circuits [Rabaey, Chandrakasan and Nikolic 2003].

The shrinking of planar MOSFETs during the last four decades enabled a continuous increase in the transistor density in the integrated circuits. However, the continuity of this tendency is very challenging for the reason that the power consumption increases as a consequence of the increasing number of transistors in ICs.

The power consumption of ICs falls into two main components: dynamic and static (leakage). The dynamic power is related to the swithing activity of the transistors, whereas the leakage power is the power consumed due to undesirable leakage currents. According to [Dadoria, Khare and Singh 2015], the leakage power corresponds to approximately 45% of the total power consumption in ICs designed using a 90nm technology.

Since many chips are embedded in mobile systems, e.g, smartphones, tablets, laptops, and so forth, the reduction of power consumption, specially the undesired leakage power, becomes an unavoidable concern because it impacts the battery's life. Moreover, it is also important to design systems with low power consumption due to energy costs.

If compared to the CMOS planar technology, the FinFET dramatically improved the leakage power in modern designs [Bhattacharya and Jha 2014], however it has not eliminated this power component. Therefore, optimization techniques addressing leakage power minimization play a major role in modern designs.

In standard cell based designs, the discrete gate sizing may be employed in the design flow to perform leakage power optimization. Due to the relevance of the discrete gate sizing, the International Symposium on Physical Design (ISPD) contests 2012 [Ozdal et al. 2012] and 2013 [Ozdal et al. 2013] addressed it. The objective in both contests was

to minimize the leakage power of the circuit while meeting timing constraints. Since then, several papers addressing this problem were published [Hu et al. 2012], [Li et al. 2012], [Livramento et al. 2013], [Flach et al. 2013], [Flach et al. 2013], [Sharma et al. 2015], [Yella and Sechen 2017], [Sharma et al. 2017].

State-of-the-art works addressing the discrete gate sizing problem rely on Lagrangian relaxation (LR) due to its effectiveness to produce good solutions in terms of leakage power. However, LR based sizers can take many LR iterations to produce a good solution in terms of leakage power and timing. For instance, although the discrete gate sizing flow proposed in [Flach et al. 2013] has the best results in terms of leakage power published so far for the ISPD 2012 Contest on Discrete Gate Sizing benchmarks [Ozdal et al. 2012], its LR core requires 100 iterations to converge to a good solution. [Sharma et al. 2017] addressed this issue by proposing a lagrange multiplier update strategy that accelerates the convergence of the algorithm. Besides the many iterations drawback, the evaluation of all cell options to compute the lowest LR local cost can be very slow, specially if a complex timing model is used. Furthermore, in the initial LR iterations of [Flach et al. 2013], the leakage power tends to grow significantly, e.g 15x the final value [Flach et al. 2013], so several iterations are required to reduce this power increase. Yet, its LRS solver does not rely on any strategy for cell option candidate filtering. [Reimann, Sze and Reis 2016] proposed a cell ranking method to filter cell candidates, while [Sharma et al. 2017] applied a simple filter only in their multi-gate-sizing step.

Considering that a design can have a large number of gates, a coarse-grained LR based sizer can be very timing consuming if the drawbacks aforementioned are not properly handled. Thus, the main objective of this work is to propose a set of strategies to tackle the drawbacks related to the LR core of the flow presented in [Flach et al. 2013].

#### 1.1 Standard Cell Based Design Flow

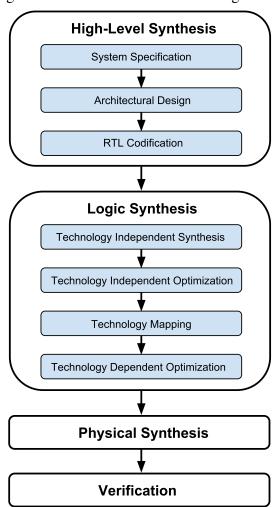

The design flow of an integrated circuit is a set of steps carried out to implement an integrated circuit from its specification. According to literature - [Sherwani 1999], [Kahng et al. 2011], [Gerez 1999], [Wang, Chang and Cheng 2009], [Lavagno, Scheffer and Martin 2006] -, a typical design flow is composed by high level synthesis, logic synthesis, physical synthesis and verification. The overall flow is depicted in Figure 1.1.

## 1.1.1 High Level Synthesis

The first step is the system specification, which is a high level representation of the system to be designed. In this step, the objectives and requeriments are specified, e.g. performance, functionalities and physical dimensions. Besides, it is also defined the fabrication technology.

After the system is specified, it is proposed a basic system architecture to satisfy the requeriments specified previously. For instance, if a processor is being designed, the engineers decide if it will be RISC (Reduced Instruction Set Computer) or CISC (Complex Instruction Set Computer), the number os ALUs (Arithmetic and Logic Unit) and floating point units, structure and number of pipelines, amount of cache memory, among others. The result of this step is a micro-architectural specification, which is a textual description of the decisions taken.

Figure 1.1: Standard Cell Based Design Flow.

Source: from author (2018)

In the last step of the high level synthesis, it is created a description of the circuit in the register transfer level (RTL). The RTL describes the system in terms of registers, flow of signals between them and the logic operations performed in these signals [Churiwala and Garg 2011]. To create the description, hardware description languages (HDLs), such as VHDL and verilog, are employed.

## 1.1.2 Logic Synthesis

In the logic synthesis step, the RTL description is translated into a gate level netlist mapped to the specified technology library. Initially, the logic synthesis is technology independent. That is, the initial gate-level netlist is composed of generic gates, such as OR, AND and NOT that are not related to any specific technology library [Wang, Chang and Cheng 2009]. Therefore, at this point, several technology-independent optimizations can be performed before mapping the netlist to the target library.

After the mapping was carried out, the resulting netlist can be optimized. As described in [Flach 2015], logic minimization, gate sizing, logic restructuring, retiming and buffering can be applied to optimize the mapped netlist.

### 1.1.3 Physical Synthesis

In the physical synthesis, it is generated the layout of the integrated circuit. Since this process is complex, the physical synthesis falls into several steps: partitioning, floor-planning, placement, clock tree synthesis (CTS) and routing [Kahng et al. 2011]. Figure 1.2 illustrates the physical synthesis flow.

An integrated circuit may be composed of millions of logic gates. Therefore, due to limitations of processing power and memory, it could not be possible to generate the layout considering the whole set of logic gates during the physical synthesis. Thus, in the partitioning step, the circuit is partitioned into several sub-circuits (blocks), so that the problem is divided into smaller and independent problems. An example of circuit partitioning is presented in Figure 1.3, which shows a circuit that was partitioned into three partitions. According to [Kahng et al. 2011], a common method employed to perform circuit partitioning is to create sub-circuits such that the number interconnections between these circuits is minimized. An example of algorithm that is based on this ap-

Physical Synthesis

Partitioning

Floorplanning

Physical Optimization

Routing

Figure 1.2: Physical Synthesis Flow.

Source: from author (2018)

proach is [Kernighan and Lin 1970], which partitions the netlist into two sub-circuits.

(a)

Figure 1.3: Partitioning example.

Source: [Sherwani 1999]

After the partitioning, the floorplanning step takes place. The floorplanning performs the estimation of the chip's dimensions, I/O pads and logic blocks placement and the power planning. The power planning distributes the vdd and gnd signals over the chip.

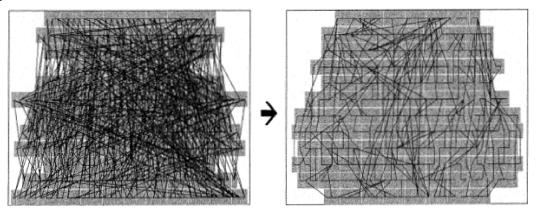

Afterwards performing the partitioning and the floorplanning, the placement is executed, which is responsible for determining the location of each logic cell. This is a crucial step, since a low quality placement can make the circuit unroutable or gener-

ate a solution that does not satisfy the performance requeriments. Figure 1.4 shows an example of a random placement and a solution obtained by performing the simulated annealing (SA). In the prior, it is possible to notice that there is a huge number of congested interconnections, while in the second the congestion was dramatically reduced.

Figure 1.4: Random placement versus placement obtained with the *simulated annealing* algorithm.

Source: adapted from [Hentschke, Johann and Reis 2005]

After the sequential elements, e.g. flip-flops, are placed, the next step is the clock tree synthesis, in which it is generated a clock tree of buffers. The clock tree distributes the clock signal to all synchronous elements, so that the timing requeriments are met.

Subsequently to the clock tree generation, the routing step determines the routes of the interconnections. In order to ensure the chip's manufacturability, the paths generated must satisfy the design rules. The main objective of this step is to route 100% of the wires, since, otherwise, the circuit will not work properly. The delay of the interconnections can degrade the performance of the design, therefore, another important objective is to minimize the total wirelength, although the placement plays the major role in this objective. The routing step usually falls into two substeps: global routing and detailed routing. The global routing performs a planning of the routing, that is, it specifies the regions of the chip where each wire will pass through. The detailed routing takes the planning carried out by the global routing and determines the exact location of each wire.

Once the layout is generated, a complete verification is performed to ensure that the solution is valid. Thus, during the physical verification, one of the processes that is executed is the design rule check (DRC). The DRC verifies if the layout respects the design rules of the manufacturing process technology, e.g. minimum distance between wires. Another process executed during the physical verification is the layout versus schematic (LVS), which generates a netlist from the layout and compares it with the original netlist

to verify if they are logically equivalent. A parasitic extraction process is also employed to obtain the electrical parameters of the layout, such as resistences, capacitances and indutances. Yet, the antenna rule checking process is performed to prevent antenna effects, which could cause damages to the transistor gates in the manufacturing process. Finally, the electrical rule check (ERC) is carried out to verify the power and ground connections and if the slew times, fanouts and capacitive loads properly meet the constraints [Kahng et al. 2011].

During the design flow, the discrete gate sizing is widely used to perform optimizations [Lee and Gupta]. Although this technique, which is the topic of this work, is not explicitly shown in the design flow discussed above, it can be used in different stages of the design flow, such as logic synthesis, technology mapping, critical path optimization and power/area optimization [Reimann, Sze and Reis 2016]. For instance, after the clock tree synthesis, it can be used to fix setup and hold violations using the clock information obtained from the CTS. After routing, it can be used once more to fix setup and hold violations [Lee and Gupta]. Yet, it can be used incrementaly in a pre-optimized design to perform power and area optimization [Reimann, Sze and Reis 2016].

It is important to highlight that, currently, the logic synthesis and physical synthesis steps are not completely separated as shown in the flow above. In the old days, the delay of interconnections were negligible if compared to the gates delay. However, today, due to the reduction of the transistor dimensions, load capacitances and channel resistences were dramatically reduced. Thus, the gate delay reduced as well. On the other hand, the shrinking of the interconnections increases their resistance due to the reduction of the transversal section. Besides, the capacitance of wires keeps increasing due to the reduction of the distance between these wires. Therefore, the delay of the interconnections has became a limiting factor in the circuit performance [Rossum 2009]. For this reason, the logic synthesis relies on physical information and the physical synthesis started to call optimization methods that were previously used only during the logic synthesis [Flach 2015]. One example of this interation between logic synthesis and physical synthesis is the placement algorithm proposed in [Stenz et al. 2000]. The algorithm takes a design whose cells are previously placed and determines the propagation delay of the wires. The delay information is used to perform transformations in the original netlist, so that the paths delay are reduced. After the netlist is changed, the cells are placed again, since during the netlist transformation process several cells can be added and removed.

## 1.2 Objectives of this work

The objectives throughout this work are:

- Understand the discrete gate sizing problem.

- Implement a discrete gate sizing flow on Rsyn [Flach et al. 2017].

- Propose improvements to tackle some drawbacks related to the LR core of the implemented algorithm.

## 1.3 Organization of this Work

This work is organized as follows: Chapter 2 covers the basic concepts related to static timing analysis and power consumption in CMOS technology; Chapter 3 discusses the gate sizing problem, presenting an overview of continuous gate sizing and covering in detail the discrete gate sizing; Chapter 4 presents a literature review of discrete gate sizing algorithms, covering the early work and state-of-the-art; Chapter 5 dives into the details of the baseline algorithm proposed in [Flach et al. 2013]; Chapter 6 presents the improvements proposed for the baseline gate sizing algorithm and the results obtained. Finally, in Chapter 7, it is presented the conclusions and future works.

#### **2 CONCEPTS**

#### 2.1 Static Timing Analysis

The Static Timing Analysis (STA) [Hitchcock, Smith and Cheng 1982, Güntzel 2000] is a technique used to evaluate the timing of a digital circuit. This method performs the timing analysis without relying on data inputs or simulations, which is in contrast with dynamic techniques, that apply simulation vectors to carry out the analysis [Lee and Gupta]. Considering a circuit with millions of gates, simulation techniques can be very slow [Bhasker and Chadha 2009], thus prohibitive, since the timing of the design must be verified several times during the design flow. On the other hand, the STA is a faster and simpler method, hence, it is able to cope with dense designs. The ideia of STA is to evaluate if the circuit will properly operate at the specified frequency by computing the best and worst case path delays [Sapatnekar 2004, Bhasker and Chadha 2009]. The next subsections dive into STA, presenting several concepts related to it.

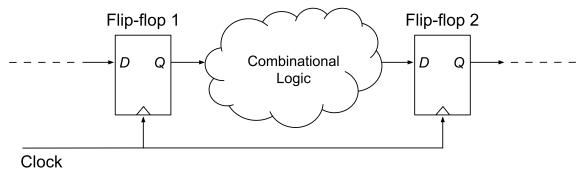

### 2.1.1 Synchronous Digital Circuits

Basically, a synchronous digital integrated circuit is composed by logic gates and storage elements, i.e., flip-flops. Due to design requeriments, a circuit can contain one or more clock domains. A clock domain could be stated as a portion of the circuit in which all flip-flops are synchronized by the same clock signal. As depicted in Figure 2.1, a subcircuit belonging to a same clock domain can be decomposed into a set of combinational blocks interconnected by flip-flops.

Figure 2.1: High level representation of a synchronous digital circuit.

Source: from author (2018)

Considering the illustration above, the signals must propagate through the combinational logic between two temporal barriers (flip-flops) within a time window. Thus, the worst path delay between each pair of flip-flops can not exceed:

$$t_{Ck \to Q,max} + t_{comb,max} \le T - t_{setup} + \delta - 2t_{jitter}$$

(2.1)

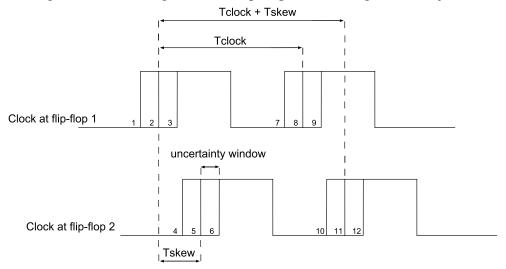

where  $t_{Ck\to Q,max}$  is the maximum propagation delay of the first flip-flop;  $t_{comb,max}$  is the maximum propagation delay of the combinational block; setup time  $(t_{setup})$  is the amount of time a signal must be stable at the input of the second flip-flip before the clock signal reaches this flip-flop; clock skew  $(\delta)$  is the spatial variation in the arrival time of the clock signal at each flip-flop;  $t_{jitter}$  is the clock uncertainty window. If the condition above is not satisfied, the circuit has a setup or late violation.

In order to avoid a hold or early violation, that is, a situation when signal at the input of a flip-flop is overwritten before it is stored in this flip-flop, the following condition must be met:

$$t_{Ck \to Q,min} + t_{comb,min} > \delta + t_{hold} + 2t_{jitter}$$

(2.2)

where  $t_{Ck \to Q,min}$  is the minimum propagation delay of the first flip flop;  $t_{comb,min}$  is the minimum propagation delay of the combinational block; hold time ( $t_{hold}$ ) is the amount of time a signal must be stable at the input of the second flip-flip after the clock signal reaches this flip-flop. Figure 2.2 shows a temporal diagram from which the conditions established in Equations 2.1 and 2.2 were derived. It is possible to notice that the Equation 2.1 was obtained by analyzing the case in which the time window that the signals have to propagate through the circuit is minimal. It corresponds to the situation when the leading edge of the current clock happens late (edge 3) and the leading edge of the next clock happens early (edge 10). The Equation 2.2 is formulated by observing the case in which the leading edge of the current clock arrives early (edge 1) in the flip-flop 1 and arrives late (edge 6) in flip-flop 2. Hence, if the minimum path delay is small enough, a signal at the input of flip-flop 2 will be overwritten.

In order to verify the existence of a late violation, a STA tool computes the maximum path delay, whereas the existence of an early violation is verified by performing the computation of the minimum path delay. The computation of the minimum path delay is called early mode analysis while the computation of the maximum path delay is called late mode analysis. For each mode, different characterizations for cells are used. Each

Figure 2.2: Clock signal at two flip-flops considering skew and jitter.

Source: adapted from [Rabaey, Chandrakasan and Nikolic 2003]

characterization is carried out at a specific process, voltage and temperature (PVT) corner. Hence, in the early mode, the cells work as fast as possible, while, for the late mode, the analysis is done such that the cells work as slow as possible. In the context of this work, only the late mode analysis is performed. Thus, from this point forward, the early mode is not addressed in the discussions.

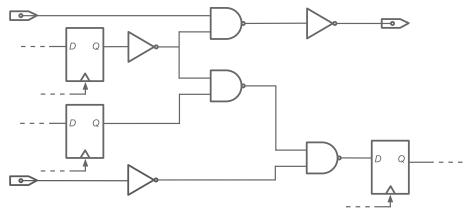

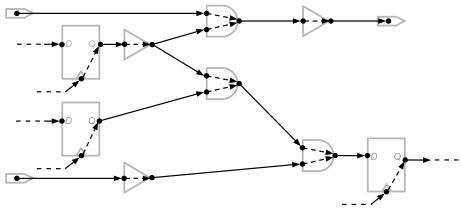

### 2.1.2 Modeling of Synchronous Digital Circuits

Figure 2.3 shows an example of a portion of a synchronous digital circuit containing combinational gates and flip-flops for storage. For the purpose of static timing analysis, a design is modeled using a directed timing graph in which the nodes represent the pins and the edges represent the timing arcs. A timing arc provides the timing information between two adjacent pins of the circuit [Lee and Gupta]. There are two types of timing arcs: cell timing arc, which connects two pins of a same cell, and net timing arc, which provides the connection between different elements, i.e, logic gates, flip-flops and i/o. Figure 2.4 shows the timing graph that was derived from the circuit depicted in Figure 2.3.

Figure 2.3: Example of a portion of a synchronous digital circuit.

Source: from author (2018)

Figure 2.4: Directed timing graph.

Source: from author (2018)

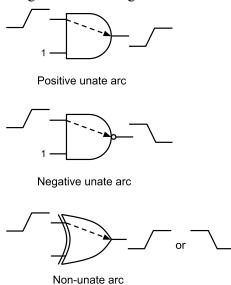

## 2.1.3 Timing Sense

Each timing arc has a timing sense, which indicates how the output changes w.r.t. the input signal transition. A timing arc is positive unate if a rise/fall transition at the input causes a rise/fall transition at the output. On the other hand, a timing arc is negative unate if a rise/fall transition at the input causes a fall/rise transition at the output. Finally, a timing arc is non-unate if the transition at the output do not depends only on the transition at the input, but also depends on the state of the other inputs. Figure 2.5 ilustrates these three cases.

Figure 2.5: Timing sense of arcs.

Source: from author (2018).

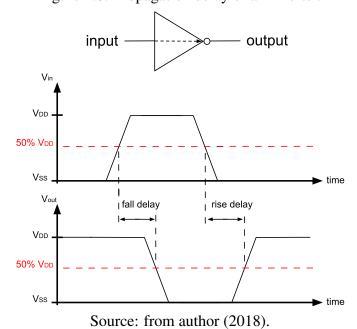

## 2.1.4 Propagation Delay of a Timing Arc

The propagation delay of a timing arc is defined as the amount of time it takes the output to reach 50% of Vdd after the input reached 50% of Vdd [Bhasker and Chadha 2009]. Figure 2.6 ilustrates the propagation delay of a negative unate timing arc.

Figure 2.6: Propagation delay of an inverter.

### 2.1.5 Transition Time (Slew)

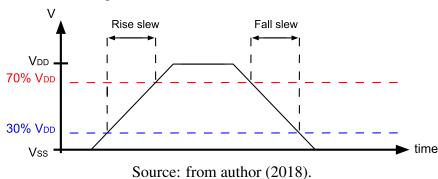

The transition time is defined as the time it takes a signal to change its logic level. The rising slew is typically measured from the time the signal reaches 30% of Vdd to the time it reaches 70% of Vdd. In the same way, the falling slew is typically measured from the time the signal reaches 70% of Vdd to the time it reaches 30% of Vdd. Another typical threshold points are 10% to 90% and vice versa and 20% to 80% and vice versa. Figure 2.7 ilustrates the measure of a rise transition time using the 30% of Vdd and 70% of Vdd threshold points.

Figure 2.7: Rise and fall transition times.

#### 2.1.6 Time Modeling

#### 2.1.6.1 Cells

The cell libraries provide look-up table models that contain sampled values of propagation delay and output slew for each timing arc of a cell. The look-up table model is also referred as non-linear delay model (NLDM) [Bhasker and Chadha 2009]. Each table entry is indexed using the input slew and output load capacitance. If the input slew and/or output load do not match any of the table entries, the delay/output slew is obtained by linear interpolation.

- **cell\_rise:** Specifies values of delay for a rise transition at the output.

- **cell\_fall:** Specifies values of delay for a fall transition at the output.

- rise\_transition: Specifies values of rise output slew.

- fall\_transition: Specifies values of fall output slew.

It is presented below two look-up tables that were provided in the ISPD 2012 Contest on Discrete Gate Sizing [Ozdal et al. 2012]. The first one contains sampled values of delay for a rise transition at the output, whereas the second one contains sampled values of rise output slew.

Table 2.1: Look-up table which provides sampled values of delay for a rise transition.

| Output load (ff) Input slew (ps) | 5.00   | 30.00  | 50.00  | 80.00  | 140.00 | 200.00 | 300.00 | 500.00 |

|----------------------------------|--------|--------|--------|--------|--------|--------|--------|--------|

| 0.00                             | 11.72  | 18.22  | 22.67  | 27.61  | 34.82  | 40.44  | 48.21  | 61.24  |

| 1.00                             | 16.93  | 23.43  | 28.60  | 34.95  | 44.15  | 51.18  | 60.65  | 75.83  |

| 2.00                             | 22.13  | 28.63  | 33.83  | 41.24  | 52.23  | 60.57  | 71.67  | 89.00  |

| 4.00                             | 32.55  | 39.05  | 44.25  | 52.05  | 66.05  | 76.76  | 90.85  | 112.34 |

| 8.00                             | 53.38  | 59.88  | 65.08  | 72.88  | 88.48  | 103.09 | 122.40 | 151.42 |

| 16.00                            | 95.05  | 101.55 | 106.75 | 114.55 | 130.15 | 145.75 | 171.59 | 213.31 |

| 32.00                            | 178.38 | 184.88 | 190.08 | 197.88 | 213.48 | 229.08 | 255.08 | 307.08 |

Table 2.2: Look-up table which provides sampled values of rise output slew.

| Output load (ff) Input slew (ps) | 5.00   | 30.00  | 50.00  | 80.00  | 140.00 | 200.00 | 300.00 | 500.00 |

|----------------------------------|--------|--------|--------|--------|--------|--------|--------|--------|

| 0.00                             | 12.50  | 13.72  | 16.38  | 20.10  | 25.17  | 28.65  | 32.95  | 39.83  |

| 1.00                             | 18.75  | 19.20  | 21.15  | 25.28  | 32.15  | 37.06  | 42.98  | 51.31  |

| 2.00                             | 25.00  | 25.09  | 26.41  | 29.91  | 37.97  | 44.09  | 51.66  | 61.86  |

| 4.00                             | 37.50  | 37.50  | 37.82  | 40.10  | 47.66  | 55.77  | 66.14  | 80.57  |

| 8.00                             | 62.50  | 62.50  | 62.50  | 62.90  | 67.51  | 74.76  | 88.78  | 110.23 |

| 16.00                            | 112.50 | 112.50 | 112.50 | 112.50 | 113.06 | 116.67 | 126.92 | 154.48 |

| 32.00                            | 212.50 | 212.50 | 212.50 | 212.50 | 212.50 | 212.50 | 215.15 | 232.09 |

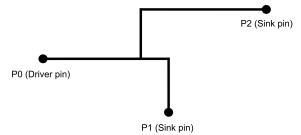

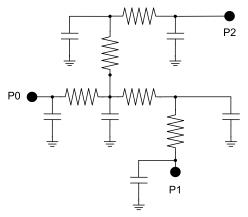

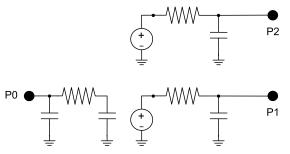

#### 2.1.6.2 Interconnections

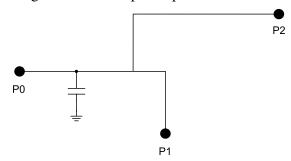

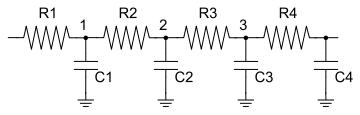

The delay of a wire is calculated based on its parasitic elements (resistences and capacitances). In this work, the interconnection parasitics are extracted from a standard parasitic extraction format (SPEF) file. In SPEF, three models of interconnections are supported: distributed net model, reduced net model and the lumped capacitance. In the distributed net model, each interconection segment has its own resistence and capacitance. In the reduced net model, the net is modeled using a resistence-capacitance-resistence structure connected to the driver pin and a resistence-capacitance structure connected to each sink pin. In the lumped capacitance model, the entire net is modeled just as a single capacitance which is summed up with the capacitances of the sink pins. Figure 2.8 shows an example of an interconnection, while Figures 2.9, 2.10 and 2.11 depict this interconnection net represented using the distributed net model, reduced net model and lumped capacitance model, respectively. In this work, only the lumped capacitance model is used, since the benchmarks of the ISPD 2012 Contest [Ozdal et al. 2012] used to perform the experiments adopt this model.

Figure 2.8: Example of an interconnection.

Source: adapted from [Bhasker and Chadha 2009]

Figure 2.9: Distributed net model.

Source: adapted from [Bhasker and Chadha 2009]

Figure 2.10: Reduced net model.

Source: adapted from [Bhasker and Chadha 2009]

Figure 2.11: Lumped capacitance model.

Source: adapted from [Bhasker and Chadha 2009]

For the lumped capacitance model, the arrival times at the driver pin of a net and at the sink pin of the same net are equal. Hence, it is not actually used to model the delay

of an interconnection. On the other hand, when the distributed net model is adopted, the delay of the interconnection is considered in the analysis. In order to compute the delay, the Elmore Delay [Elmore 1948] can be used.

Figure 2.12: Elmore example.

Source: adapted from [Bhasker and Chadha 2009]

For the circuit illustrated in Picture 2.12, the delay to the points 1, 2 and 3 are calculated as using Elmore delay as follows:

$$T_{d1} = R_1 \times (C_1 + C_2 + C_3 + C_4) \tag{2.3}$$

$$T_{d2} = R_1 \times (C_1 + C_2 + C_3 + C_4) + R_2 \times (C_2 + C_3 + C_4)$$

(2.4)

$$T_{d3} = R_1 \times (C_1 + C_2 + C_3 + C_4) + R_2 \times (C_2 + C_3 + C_4) + R_3 \times (C_3 + C_4)$$

(2.5)

The general form of the Elmore delay to the node i is given by Equation 2.6:

$$T_{di} = \sum_{k=1}^{N} (C_k \times R_{ik}) \tag{2.6}$$

where N is the number of nodes of the net and  $R_{ik}$  is the sum of all resistences shared among the paths from the source node to nodes k and i.

The slew at a node n of a net may be calculated as in [Flach et al. 2014]:

$$slew_n = \sqrt{slew_{parent}^2 + 1.93 \times (RC)^2}$$

(2.7)

where R is the resistence which connects n to its parent node and C is the downstream capacitance.

## 2.1.7 Timing Information

A STA tool can provide many information related to timing arcs and pins. It is presented below the typical information that is commonly used throughout this work.

- Arrival time at pin  $p(at_p)$ : It is the maximum time it takes a signal to arrive at the pin p.

- Required time at pin p ( $rt_p$ ): It is the maximum instant at which a signal should arrive at the pin p so that a timing violation does not occur.

- Slack at pin p ( $slack_p$ ): The slack is the difference between the required time and the arrival time at the pin p, i.e.,  $slack_p = rt_p at_p$ .

- Slew at pin p ( $slew_p$ ): Indicates the transition time at the pin p.

- **Delay of a timing arc**  $(delay_{i\rightarrow j})$ : Indicates the delay of a timing arc starting at node i and ending at node j.

Considering the late mode analysis, a negative slack at the pin P indicates that a timing violation has occurred at this pin. On the other hand, a positive slack may be explored to perform optimizations.

## 2.1.8 Timing Propagation

This subsection discusses how the typical timing information presented in the former subsection is computed for all pins of the circuit. Since the early mode is out of the scope of this work, only the timing propagation in late mode is presented.

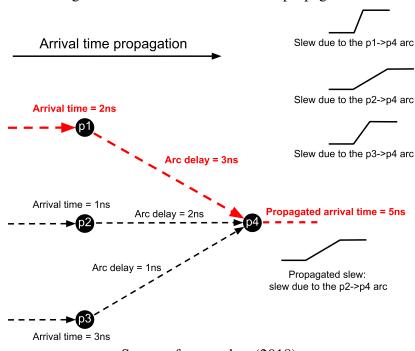

In order to compute the arrival time for each pin of the circuit, the STA tool traverses the timing graph in topological order. It starts from the primary inputs and, for each timing arc visited, the arrival time at its output is computed by summing the arrival time at its input with the timing arc propagation delay. If two or more timing arcs converge into a same output pin, e.g. a nand gate, only the worst arrival time and largest slew at the output are propagated towards the primary outputs. The example depicted in Figure 2.13 shows three timing arcs converging into a pin node. The arrival times at the p4 pin are 5ns, 3ns and 4ns due to the timing arcs p1->p4, p2->p4 and p3->p4, respectively. Hence, the largest arrival time, which is 5ns, is propagated forward. Also, the largest slew at the p4 pin is due to the p2->p4 timing arc, therefore it is the propagated transition time.

Figure 2.13: Arrival time and slew propagation.

Source: from author (2018).

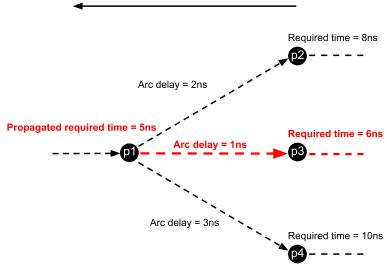

After the arrival times for all pins of the circuit are obtained, the timing graph is traversed in reverse topological order to compute the required time and slack for each node. The required time at each endpoint node is set as its target delay. The required time for a non-endpoint node  $v_i$  is computed as:

$$rt_{v_i} = min(rt_{v_j} - delay_{v_i \to v_j}), v_j \in fanout(v_i)$$

(2.8)

Figure 2.14 illustrates an example of required time propagation. The required times at the node p1 are 6ns, 5ns and 7ns due to the timing arcs p1->p4, p2->p4 and p3->p4, respectively. Therefore, the p1 node receives the minimum required time, which is 5ns.

Algorithm 2.1 summarizes the static timing analysis for the late mode. For the sake of simplicity, this algorithm presents the STA in a generic way, omitting the type of transition at each node, since it depends on the unateness of the timing arcs. The term  $slew_{v_i \to v_j}$  refers to a transition at the node  $v_j$  due to the timing arc  $v_i \to v_j$ . The other terms are the presented in the former subsection.

Figure 2.14: Required time propagation.

Required time propagation

Source: from author (2018).

## Algorithm 2.1: Static Timing Analysis

- 1 set arrival time of startpoints

- 2 set required time of endpoints

- 3 for each node  $v_j$  in topological order do

10 end

11 **for** each node  $v_i$  in reverse topological order **do**

12

$$rt_{v_i} \leftarrow +\infty$$

13 **for** each timing  $arc\ v_i \rightarrow v_j$  **do**

14  $rt_{v_i} \leftarrow min(rt_{v_i}, rt_{v_i} - delay_{v_i \rightarrow v_j})$

15 **end**

16  $slack_{v_i} \leftarrow rt_{v_i} - at_{v_i}$

17 end

#### **2.1.9 WNS and TNS**

For the late mode, the worst negative slack (WNS) is the slack of the endpoint which has the largest timing violation. The total negative slack (TNS) is the summation of all negative slacks of the endpoints.

## 2.1.10 Criticality and Centrality

The criticality of a pin  $\in [0,1]$  is defined as the worst negative slack of this pin divided by the worst negative slack of the design. The centrality of a pin  $\in [0,1]$  is an estimation of how many and how critical are the endpoints affected by this pin [Flach et al. 2016].

### 2.2 Power Consumption in CMOS Technology

The power dissipation in CMOS circuits is divided into two componentes [Weste and Harris 2010]:

- Dynamic power

- Static power

The dynamic power is related to the charging and discharging of the load capacitance and the "short circuit" current that flows when both PMOS and NMOS networks are partially active. When the pullup stack of a gate is active, it charges the output load capacitance. Thus, a certain quantity of energy is drawn from the power supply. Part of this energy is stored in the output load capacitance, while the remaining part is dissipated in the PMOS transistores. When the output load is discharged, its energy is dissipated in the NMOS transistores. The total energy drawn from the power suply is given as follows:

$$E = \frac{C_L \times Vdd^2}{2} \tag{2.9}$$

where  $C_L$  is the output load capacitance and Vdd is the power supply voltage.

The power dissipated is computed based on the switching activity factor, which is a statistical measure of how many times the device switches per second. Therefore, the power dissipated is calculated as:

$$P_{dun} = C_L \times V dd^2 \times f_{0 \to 1} \tag{2.10}$$

where  $f_{0\rightarrow 1}$  is the switching activity factor.

Since the transition time of the input signal is not zero, there is a short period of time when both NMOS and PMOS transistors are active simultaneously. Therefore, a direct current path between Vdd and GND exists during this period. The power consumption due the direct path current can be approximately calculated by assuming that the current spikes have triangle shapes and that the gate is symmetrical in its rising and falling output edges. Thus, the energy drawn from the power supply during the switching period is given by:

$$E = t_{sc} \times Vdd \times I_{peak} \tag{2.11}$$

where  $t_{sc}$  is the period of time when both NMOS and PMOS are conducting and  $I_{peak}$  is the maximum value of the direct path current during  $t_{sc}$ . Then, the average power consumption is

$$P = t_{sc} \times V dd \times I_{peak} \times f \tag{2.12}$$

where f is the switching activity factor.

The static power is a consequence of the subthreshold, gate and reverse-biased diode juntions leakage currents [Weste and Harris 2010]. The subthreshold leakage current flows between drain-source when it is applied a gate-source voltage  $(V_{GS})$  smaller than the threshold voltage  $(V_{th})$ . The smaller the  $V_{th}$ , the larger the leakage current when the transistor is "OFF", that is, when  $V_{GS}$  is 0V. Therefore, the smaller the  $V_{th}$ , the larger the static power consumption. The gate leakage current is caused by carriers that are tunneled through the gate when it is biased. This current depends on the thickness of the gate oxide and voltage across the gate [Weste and Harris 2010]. The last component of static power, junction leakage, is caused by junction current that flows when the drain or source diffusion is biased with a potential different from the substrate. Figure 2.15 illustrates the three leakage components.

Gate leakage

Subthreshold leakage

Junction leakage

Figure 2.15: Sources of leakage current.

Source: from author (2018)

In this work, only the static power is optimized. The leakage power information of each cell is provided by a liberty file. The liberty file is the industry standard format for representing timing and power information of the cells provided by a library [Prakash 2007]. For example, for the inverter cell in01s01 of the ISPD2012 benchmark suite [Ozdal et al. 2012], the static power is given by the following field:

cell\_leakage\_power: 1.00;

The leakage power unit is specified in the liberty file header as:

leakage\_power\_unit : 1uW;

## **3 GATE SIZING**

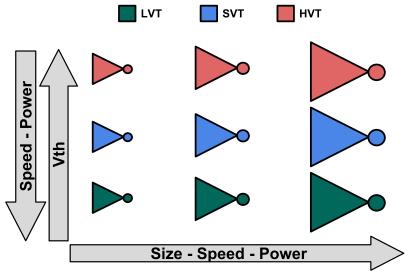

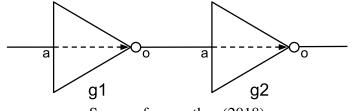

In standard cell based designs, the gate-level netlist is mapped to a technology library, which contains different implementation options for each available logic function. Considering a particular logic function, the versions differ in the width of the gate's transistors, referred here as the size of the gate, and  $V_{th}$ . Hence, they have different timing and leakage power characteristics to tradeoff. As illustrated in Figure 3.1 for a not gate, the larger is the size, the faster it is, however, it has a greater power consumption. In the same way, the lower the  $V_{th}$ , the greater the speed and the power consumption. In this context, the discrete gate sizing consists in assigning each gate of the netlist to an implementation option available in the cell library. It is a powerful technique that can be used in many stages of the design flow to perform optimizations, such as timing violations fixing and power and/or area minimization.

Figure 3.1: Inverter gates with different driver strengths and threshold voltages.

Source: from author (2018)

## 3.1 Gate Sizing Classification

The gate sizing algorithms falls into two main approaches: continuous gate sizing and discrete gate sizing [Lee and Gupta]. The continuous gate sizing is not in the scope of this work, however, for the sake of contextualization, it will be presented next an overview about it.

## 3.1.1 Continuous Gate Sizing

In the continuous gate sizing approach, the gates can be implemented using transistors of any size and  $V_{th}$ . Due to the continuous nature of the transistor parameters, the gate sizing problem can be formulated using convex delay models. Therefore, it is possible to find a set of continuous sizes and  $V_{th}$  that optimally solves the optimization problem. Since the cells must be generated considering the solution found by the gate sizing algorithm, a full-custom methodology or automatic cell generation are required. In literature, several works addressing continuous sizing can be found, such as [Fishburn and Dunlop 1985], [Berkelaar and Jess 1990], [Chen, Chu and Wong 1999], [Tennakoon and Sechen 2002], [Posser et al. 2011] among others.

## 3.1.2 Discrete Gate Sizing

As mentioned earlier, the discrete gate sizing consists in assigning each gate of the netlist to an cell option available in the cell library. It is a combinatorial optimization problem and [Li 1993] proved to be NP-Hard, thus, efficient heuristic algorithms are fundamental to solve this problem within feasible runtimes. The first works to tackle the discrete gate sizing directly in the discrete domain were [Chan 1990] and [Coudert 1996]. Since then, several approaches have been proposed, such as linear programming [Chinnery and Keutzer 2005], target slew [Held 2009], dynamic programming [Liu and Hu 2010, Ozdal, Burns and Hu 2011], sensitivity guided metaheuristic [Hu et al. 2012], simulated annealing [Reimann et al. 2013] and Lagrangian relaxation [Liu and Hu 2010, Huang, Hu and Shi 2011, Li et al. 2012, Livramento et al. 2013, Flach et al. 2014, Sharma et al. 2015, Reimann, Sze and Reis 2016, Yella and Sechen 2017, Sharma et al. 2017]. All these algorithms are covered in the next chapter.

In this work, the discrete gate sizing is used to minimize the leakage power of a given circuit subject to timing constraints. Therefore, the discrete gate sizing for power optimization can be formally defined as:

**minimize** leakage

**subject to**

$$a_{t_i} + delay_{i \to j} \le a_{t_j}, \quad \forall i \to j \in Arcs$$

$$a_{t_k} \le T, \quad \forall k \in Endpoints$$

$$x_i \in Sizes_i$$

(3.1)

where  $x_i$  is an implementation option of the gate i; Sizes $_i$  is the set of implementation options of the gate i; T is the clock period.

Continuous gate sizing can be used to guide the discrete gate sizing. The problem is initially solved in the continuous domain, then, the solution is mapped to the discrete domain. The drawback of this approach is that the mapping process degrades the solution [Ozdal, Burns and Hu 2012]. Some of the works that rely on this strategy are [Chuang, Sapatnekar and Hajj 1993] and [Sirichotiyakul et al. 1999].

## 3.2 Lagrangian Relaxation based Discrete Gate Sizing

Lagrangian Relaxation is a mathematical technique used to handle optimization problems with hard constraints. In the LR approach, the original optimization problem, called Primal Problem (PP), is rewritten by removing the hard constraints and incorporating them into the objective function, making the problem easier to solve. The PP is described in a general way as follows:

minimize

$$f(x)$$

subject to  $g_i(x) \le 0$   $i = 1, 2, ..., n$  (3.2)

$h_j(x) = 0$   $j = 1, 2, ..., m$

where f(x) is the function that will be minimized and the hard constraints are given by  $g_i(x)$  and  $h_j(x)$ .

By incorporating the hard constraints into the objective function, it is obtained the relaxed problem, which is given as follows in Equation 3.3:

minimize

$$\mathcal{L}(x,\lambda,\mu)$$

subject to  $\lambda_i \in \Re_+$   $i=1,2,\ldots,n$  (3.3)

$\mu_j \in \Re$   $j=1,2,\ldots,m$

where  $\mathcal{L}(x, \lambda, \mu)$  is given by

$$\mathcal{L}(x,\lambda,\mu) = f(x) + \sum \lambda_i g_i(x) + \sum \mu_j h_j(x). \tag{3.4}$$

The weights  $\lambda_i$  and  $\mu_j$  in Equations 3.3 and 3.4 are called Lagrange multipliers (LM), which indicate how much the constraint is being violated. The solution of the relaxed problem is a lower bound to the solution of the original problem, thus:

$$\mathcal{L}(\tilde{x}, \lambda, \mu) \le f(\hat{x}) \tag{3.5}$$

where  $\hat{x}$  is the optimum solution of the original problem and  $\tilde{x}$  is the solution of the relaxed problem. Therefore, the goal of the LR is to find the solution of the relaxed problem closest to the solution of the original problem, in other words, the maximum lower bound. The maximization of the relaxed objective function is called the Lagrangian dual problem (LDP), Equation 3.6.

maximize min

$$f(x) + \sum \lambda_i g_i(x) + \sum \mu_j h_j(x)$$

subject to  $\lambda_i \geq 0 \qquad i = 1, 2, \ldots, n$  (3.6)

$\mu_j \in \Re \qquad j = 1, 2, \ldots, m$

Considering the equation above, the minimization problem is called Lagrangian relaxation subproblem (LRS). Each LRS is defined by a set of Lagrange multipliers.

When applying the LR to solve the discrete gate sizing for leakage power minimization, the objective function defined in the Equation 3.1 can be rewritten by incorporating into it the relaxed constraints, as shown below in Equation 3.7.

$$\mathcal{L}_{\lambda}(x, a_{t}) = leakage + \sum_{\forall i \to j} \lambda_{i \to j} \left( a_{t_{i}} + delay_{i \to j} - a_{tj} \right) + \sum_{\forall i \in \text{ endpoints}} \lambda_{i} \left( a_{t_{i}} - T \right)$$

$$(3.7)$$

Therefore, the LRS for a set of multipliers  $\lambda$  is given as follows in 3.8:

$$\mathcal{LRS}_{\lambda}$$

:

minimize  $\mathcal{L}_{\lambda}(x, a_t)$  (3.8)

subject to  $x_i \in \text{Sizes}_i$

As shown in [Chen, Chu and Wong 1999], by applying the Karush-Kuhn-Tucker

(KKT) conditions for optimality, the  $\mathcal{LRS}_{\lambda}$  can be simplified to:

$$\mathcal{LRS}_{\lambda}(simplified)$$

:

**minimize**

$$leakage + \sum_{\forall i \to j} \lambda_{i \to j} delay_{i \to j}$$

(3.9)

**subject to**  $x_i \in \text{Sizes}_i$

This simplification implies that the sum of the Lagrange multipliers of the incomming timing arcs of a given pin must be equal to the sum of the Lagrange multipliers of the outgoing arcs of this pin:

$$\sum_{\forall i \to j} \lambda_{i \to j} = \sum_{\forall j \to k} \lambda_{j \to k} \tag{3.10}$$

#### **4 RELATED WORK**

This chapter presents a review of the discrete sizing algorithms. First, it is introduced the early work, then, the state-of-the-art techniques are covered.

## 4.1 Early Work

## 4.1.1 [Chan 1990]

The algorithm proposed in [Chan 1990] has two phases: in the first one, the circuit is traversed from the primary inputs to the primary outputs and, for each visited gate, it is calculated the lower bound and upper bound timing requirements. Considering a gate u, its timing values pair is calculated by subtracting every possible delay that u can assume from the timing requirements that were propagated from its predecessor gates. A gate that has two or more inputs receives pairs of timing values from two or more predecessor gates. Therefore, the timing requirements of this gate are calculated considering only the intersection of the requirements of its predecessors.

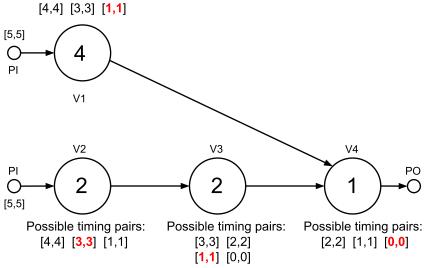

In the second phase, the circuit is traversed from outputs to inputs. Each gate is assigned to a cell option that satisfies the timing requirements of the gate and that minimizes the total cost e.g. power. It is presented below in Figure 4.1 an example that considers a simplified timing model in which a delay of a logic gate is inversely proportional to its size and does not depend on the output load. Although the timing model used is simplistic, any timing model can be used in the algorithm. For the example below, the clock period T is 5 and the size options for the gates V1, V2, V3 and V4 are  $\{1, \frac{1}{2}, \frac{1}{4}\}$ . Due to the delay model used, the delay of each gate is calculated as  $delay = \frac{1}{size}$ . Since all gates have the same size options, the possible delay all gates can assume are 1, 2 and 4. The algorithm starts by assigning to the primary inputs the pair of timing requirements [5,5], therefore, this pair is propagated to the nodes V1 and V2. For these nodes, the possible pairs of timing requirements are [4,4], [3,3] and [1,1], that are propagated forward. The node V3 received the pairs [4,4], [3,3] and [1,1] from V2, therefore, its possible pairs of timing requirements are [3,3], [2,2], [1,1] and [0,0], that are propagated to V4. The node V4 received from V1 the pairs [4,4], [3,3] and [1,1] and received from V3 [3,3], [2,2], [1,1]. Hence, only the pairs that intersect will be considered in V4, that are [3,3] and [1,1]. From these pairs, the timing requirements calculated for V4 are [2,2], [1,1] and [0,0]. After all requirements were computed, it is performed the cell option assignment, such that the lower bound and upper bound requirements at each node are satisfied. For this example, the delay at the nodes V1, V2, V3 and V4 are 4, 2, 2 and 1, respectively, and they satisfy the timing requirements highlighted with the red color.

Figure 4.1: Example of timing requirements propagation. Possible timing pairs:

Source: adapted from [Chan 1990]

The algorithm has a pseudo-polynomial runtime if the circuit has a tree structure. Circuits that do not have a tree structure are expanded into a cloned tree.

## 4.1.2 [Coudert 1996] and [Coudert 1997]

In this work, it is presented a general purpose gate sizing algorithm that can be used to optimize delay, power and area. Different from the previous works, it uses a look-up table delay model since, as the author states, linear delay models are quite inaccurate.

The delay optimization is based in a technique that alternates an optimization and a perturbation steps until there are not room for improvements. In the optimization step, the netlist is traversed and, for each visited gate, the cell options are evaluated based on the gradient of the local cost. For each cell option, the change in the local cost is computed only considering the gates that belong to the first two levels of fanin and fanout. The gate and its implementation option that causes the largest reduction in the local cost are inserted into a list of gates that have potential to be sized. After the whole netlist have been traversed, the algorithm resizes the gates that maximise the slack of the circuit. This optimization method drives the solution into a local minimum, therefore, the perturbation

step is executed to get the solution out of this point, so that a potentially better solution can be found.

The power or/and area optimization is performed on top of a delay optmized solution. It is executed the optimization method described earlir with a local cost function Relax, Equation 4.1. This function balances the gain in power taking into account the delay, so that it acts as a penalty/benefit function. In the Relax function,  $S_0$  is the current slack;  $\Delta S$  is the slack variation;  $\Delta P$  is the variation in power;  $\epsilon$  and  $\alpha$  are precomputed values considering characteristics of the circuit.

$$Relax = (\alpha \Delta P - \epsilon) \times \phi \left(\frac{\Delta S}{\epsilon + |S_0|}\right), \text{ where}$$

$$\phi(x) = \begin{cases} 1 + x & \text{if } x \ge 0\\ \frac{1}{1 - x} & \text{otherwise} \end{cases}$$

(4.1)

## 4.1.3 [Chinnery and Keutzer 2005]

[Chinnery and Keutzer 2005] proposed a discrete gate sizing formulation using linear programming (LP) for power reduction. The technique is divided into two main steps that alternate until the power improves less than a threshold value. In the first one, the algorithm starts on top of a design which was previously optimized by a comercial tool and, for each gate, it is computed its smallest sensitivity value, which is given by:

$$sensitivity = \frac{\Delta P}{\Delta d} \tag{4.2}$$

where  $\Delta P$  and  $\Delta d$  are the power and delay variations, respectively, w.r.t the current cell option.

The linear program finds for each gate i a real value  $\gamma_i$  in the range [0,1], which indicates if the gate must be swapped to the cell option with the smalles sensitivity. A gate i is swapped if its value is greater than 0.99. If timing constraints were violated, the second step is executed to fix the violations.

## 4.1.4 [Held 2009]

This work presents an algorithm based on target slew. The technique is divided into two main phases: fast global gate sizing and local search gate sizing.

In the first phase, the algorithm starts by assigning to the output pin of each gate a target slew, such that the input slew limit of the fanout is not violated. Then, iteratively, it is performed a cell assignment step and a target slew refinement until the stopping criterion is met. During the cell assignment step, the circuit is traversed in reverse topological order. Each visited gate is assigned to the smallest cell option, so that that the target slew at its output is met. Since the circuit is being traversed from outputs to the inputs, the fanout gates are already sized, therefore, the downstream capacitance is known. However, the choice of the cell option also depends on the input slew, which is unknown, since the fanin gates have not been sized yet. Hence, considering a predecessor pin p', the input slew is estimated using the followin formula:

$$\operatorname{est\_slew}(p') = \theta \operatorname{slewt}(p') - (1 - \theta) \operatorname{slew}(p') \tag{4.3}$$

where  $\theta$  is the weighting factor  $\in$  [0,1], such that in the initial iteration  $\theta$  is equal to 1 and is updated in the slew refinement; slewt(p') is the target slew at p'; slew(p') is the slew at p'.

During the slew refinement, the target slew at each gate output pin p is updated based on the global and local criticality of p. The global criticality of p, denoted as  $slk^+(p)$ , is the slack of this pin, whereas the local criticality indicates if the worst slack of p or any predecessor pin of p of cell p can be improved by increasing or decreasing the slewt(p). Hence, it is defined the predecessor criticality of cell p slp as:

$$slk^{-}(c) = min\{slack(p') \mid p' \text{ direct predecessor of } c\}$$

(4.4)

Therefore, the local criticality of p, lc(p), is calculated considering  $slk^+(p)$  and  $slk^-(c)$  as follows:

$$lc(p) = \max\{slk^{+}(p) - slk^{-}(c), 0\}$$

(4.5)

So, if p is global critical and lc(p) is equal to 0, the target slew of p is decreased by subtrating from it a number that is proportional to  $|slk^+|$ . Otherwise, the target slew of p is increased.

In the local search gate sizing phase, the solution obtained in the fast global gate sizing is improved. In each iteration of this phase, it is selected a small set of gates connected to the most critical nets. Then, each gate of the set is sized to its local optimum considering a more accurate slack evaluation.

## 4.1.5 [Liu and Hu 2010]

[Liu and Hu 2010] proposed a Lagrangian relaxation based algorithm to address power optimization subject to timing constraints. In their formulation, they consider two components of the power consumption. The first is the dynamic power, given by  $1/2\alpha V_{DD}^2 f_{clk}C$ , where  $\alpha$  is the swithing factor of a gate,  $f_{clk}$  is the clock frequency and C is the output capacitance of a gate due to wires and gates. The second is the leakage power, given by  $V_{DD}I_{off}$ , where the off current  $I_{off}$  is provided by the cell library. To solve the Lagrangian Subproblem, they relied on a dynamic programming-like technique, while the Lagrangian dual problem was addressed using the subgradient method [Bazaraa 2003].

The Lagrangian objective function, which was simplified as in [Chen, Chu and Wong 1999], is given by

$$\phi(w, u; \mu) = \sum_{v_i \in V} p(v_i) + \sum_{v_j, v_i \in E} \mu_{ji} D(v_j, v_i)$$

(4.6)

where w is the vector of gate sizes, u is the gate  $V_t$  levels,  $D(v_j, v_i)$  is the delay of the gate  $v_i$  and  $\mu_{ji}$  is the Lagrangian multiplier related to the delay of the gate  $v_i$ . The objective function  $\phi(w, u; \mu)$  is evaluated through the dynamic programming using the weighted summation of power and delay in the fanout cone, which is recursively calculated traversing the circuit in reverse topological order. The minimum summation of power and delay in the fanout cone is given by

$$f(v_i^k) = \sum_{i} min_{h \in options(v_j)} (f(v_j^h) + \mu_{ij} D(v_i^k, v_j^h)) + p(v_i^k)$$

$$(4.7)$$

where  $v_i^k$  is an implementation option of the gate  $v_i$ ,  $v_j^h$  is an implementation option of the fanout gate  $v_j$  and  $D(v_i^k, v_j^h)$  is the delay of the gate  $v_i$ .

After  $f(v_i^k)$  is calculated, the circuit is forward traversed in order to assign to each gate an implementation option. The algorithm chooses the option with the lowest cost,

defined by

$$solution(v_i) = min_{k \in options(v_i)} (f(v_i^k) + \sum_{v_j \in fanin(v_i)} (\mu_{ji} D(v_j, v_i^k) + p(v_j))). \tag{4.8}$$

## 4.1.6 [Huang, Hu and Shi 2011]

As in [Liu and Hu 2010], this work aims the optimization of power consumption (dynamic and static) subject to timing constraints using Lagrangian relaxation. However, the authors state that for discrete gate sizing, the Lagrangian dual problem is no longer convex as in continuous cases, so the subgradient method is inefficient. To handle this drawback, they proposed a projection-based descent method, which relies on the history of previous iterations to update the Lagrangian multipliers. In each iteration, the algorithm calculates the change in the Lagrangian multipliers at the primary outputs using the equation

$$\Delta\mu_i = \frac{q_i - a_i}{\eta'(T_i, \mu_i)} \tag{4.9}$$

where  $q_i$  is the required arrival time,  $a_i$  is the arrival time and  $\eta'$  is function of the current value of the Lagrangian multiplier and the table  $T_i$  of past values of arrival times and Lagrangian multipliers. After the multiplier at the primary output is updated,  $\Delta\mu$  is distributed to the other nodes of the circuit in reverse topological order. Although  $\mu$  must be a non-negative value,  $\Delta\mu$  can be negative if the constraint is met.

#### **4.1.7** [Ozdal, Burns and Hu 2012]

In [Ozdal, Burns and Hu 2012] (extension published in journal of the paper [Ozdal, Burns and Hu 2011]), the authors addressed discrete gate sizing aiming leakage power minimization for high-performance industrial designs. They proposed a Lagrangian relaxation formulation that decouples timing analysis from optimization, so that the sizer can rely on slack values computed by a signoff timer. This allows the encapsulation of the complexity of the timing analysis into the signoff timing engine, enabling the optimization engine to rely on simpler timing models. In their formulation, the LRS formula

is given as follows:

$$\alpha \times leakage\ power + \sum_{i \to j} \mu_{i \to j} delay_{i \to j} + \sum_{po} \mu_{po}(-r_{t_{po}}) + \sum_{pi} \mu_{pi} a_{t_{pi}}$$

(4.10)

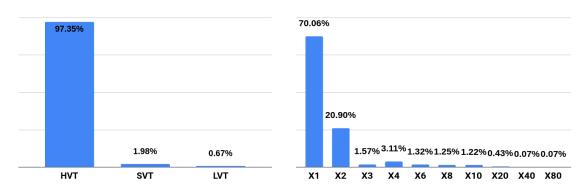

where  $\alpha$  is a scaling factor to balance leakage power and timing; po and pi are primary outputs and primary inputs, respectively;  $i \to j$  is a timing arc from the node i to the node j;  $\mu_{i \to j}$ ,  $\mu_{po}$  and  $\mu_{pi}$  are the Lagrange multipliers;  $r_{t_{po}}$  is the required time at primary outputs and  $a_{t_{pi}}$  is the arrival time at primary inputs. The terms  $r_{t_{po}}$  and  $a_{t_{pi}}$  are fixed, so, the only variables in this formula are the cell leakage power and the timing arc delay of each cell. The optimization of this LRS formula can be performed relying on the data of the cell library. Thus, the signoff timer is called only once per LR iteration after all cell options were chosen in the LRS solver.