## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

### JUCEMAR LUIS MONTEIRO

# Algorithms to Improve Area Density Utilization, Routability and Timing During Detailed Placement and Legalization of VLSI Circuits

Thesis presented in partial fulfillment of the requirements for the degree of Doctor of Microeletronics

Advisor: Prof. Dr. Marcelo de Oliveira Johann

Coadvisor: Prof. Dr. Laleh Behjat

### CIP — CATALOGING-IN-PUBLICATION

Monteiro, Jucemar Luis

Algorithms to Improve Area Density Utilization, Routability and Timing During Detailed Placement and Legalization of VLSI Circuits / Jucemar Luis Monteiro. – Porto Alegre: PGMICRO da UFRGS, 2019.

246 f.: il.

Thesis (Ph.D.) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica, Porto Alegre, BR–RS, 2019. Advisor: Marcelo de Oliveira Johann; Coadvisor: Laleh Behjat.

1. Microelectronic. 2. EDA. 3. Placement. 4. Placement Optimization. 5. Network Flow. 6. Branch and Cut. I. Johann, Marcelo de Oliveira. II. Behjat, Laleh. III. Título.

## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Rui Vicente Oppermann Vice-Reitora: Prof<sup>a</sup>. Jane Fraga Tutikian

Pró-Reitor de Pós-Graduação: Prof. Celso Giannetti Loureiro Chaves Diretora do Instituto de Informática: Prof<sup>a</sup>. Carla Maria Dal Sasso Freitas

Coordenador do PGMICRO: Prof. Tiago Roberto Balen

Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

Esta tese é dedicada aos meus pais, Juvencio e Gilvite, e ao meu avô, Angelo Baldissera. This thesis is dedicated to my parents, Juvencio and Gilvite, and my grandparent, Angelo Baldissera.

### **ACKNOWLEDGEMENT**

To my parents.

To my supervisors Dr. Marcelo Johann and Dr. Laleh Behjat

To the evaluation committee members Dr. Andrew Kahng, Dr. Patrick Groeneveld and Dr. Ismail Bustany.

To the UFRGS colleagues Guilherme, Mateus, Éder, Henrique, Isadora and Gracieli.

To the University of Calgary and ELAP program for the researching exchange scholarship.

To Nima for the collaboration.

To Synopsys and Cadence for the internship opportunities.

To the CAPES for the Ph.D. scholarship.

The thesis work had soundtracks composed by Epica, Within Temptation, Delain, Amaranthe, AC/DC, Black Sabbath, Iron Maiden, Scorpions, Taylor Davis, and Lindsey Stirling.

#### **ABSTRACT**

Placement is a challenging stage in the Very Large-Scale Integration (VLSI) physical design flow. In modern VLSI designs, several design restrictions have been imposed to address the complexity of advanced Complementary Metal-Oxide Semiconductor (CMOS) fabrication nodes. Design restrictions have a considerable influence on achieving the optimized circuit solution. The quality of the placement solution has a significant impact on circuit performance. In placement, achieving circuit requirements of timing and routability is a very challenging task. Timing and routability requirements are especially hard to achieve in circuits which have regions with high-density area utilization. Moreover, the quality of placement has a direct influence on circuit quality and optimization effort of Clock Tree Synthesis (CTS), routing, and post-placement algorithms. In this thesis, the first contribution is an incremental timing-driven placement algorithm subject to routability. The proposed timing-driven placement algorithm relies on net and path characteristics to compute optimized-timing cell positions. Optimized-timing positions are accepted only if these positions are inside regions free of routing violation. The second contribution is a cell spreading algorithm. The objective is to move cells out of high-density regions considering adverse side effects on moved cells. The proposed cell spreading algorithm relies on network flow and branch and cut techniques to minimize high-density regions. Area flows are moved from high-density to low-density regions with optimized cost paths. Therefore, cell concentration is reduced, and white spaces are opened in high-density regions with minimized adverse side effects on moved cells. Legalization, detailed placement, and post-placement algorithms can use these white spaces to further optimize the placement solution. In high-density regions, white spaces are limited resources. In the traditional placement flow (global placement, legalization, and detailed placement), the placement optimization is limited by the strict placement flow. The proposed cell spreading algorithms can be integrated into a mixed placement flow that is composed of interleaved legalization and detailed placement algorithms. In this mixed placement flow, the restriction to optimize detailed placement in a legalized netlist can be relaxed. Detailed placement algorithms can achieve further placement optimization with less restricted placement formulation. The focus of legalization algorithms can only be to fix cell overlap with minimized adverse effects on placement, instead of also fix density area violation. The proposed cell spreading algorithm is applied in legalization and detailed placement stages to optimize area density utilization. The proposed legalization algorithm has achieved improvement on average (30%) and maximum (350%) cell displacement compared to the state of the arts legalization algorithms. In detailed placement, the proposed algorithm has been evaluated in industrial and academic placement flows. In industrial placement flow, the proposed cell spreading algorithm has achieved improvement in cell displacement, power consumption, and timing. The proposed cell spreading algorithm can improve the quality of placement in mixed placement flow in both industrial and academic environments. The proposed algorithm provides a uniform cell distribution placement in constrained designs with minimized adverse side effects on moved cells.

**Keywords:** Microelectronic. EDA. Placement. Placement Optimization. Network Flow. Branch and Cut.

# Algoritmos para Aprimorar Densidade de Utilização de Área, Rotabilidade e Tempo de Propagação Durante o Posicionamento Detalhado e a Legalização de Circuitos VLSI

#### **RESUMO**

O posicionamento é um estágio desafiante no fluxo de projeto físico para integrar circuitos VLSI (sigla do inglês Very Large-Scale Integration (VLSI)). Em projetos modernos de circuitos VLSI, diversas restrições de projeto são impostas para visar a complexidade dos avançados nodos de fabricação CMOS (sigla do inglês). As restrições de projeto têm uma considerável influência em obter soluções otimizadas de circuitos. A qualidade do posicionamento tem uma significativa influência no desempenho do circuito. No posicionamento, obter os requisitos do circuito em tempo de propagação e rotabilidade é uma tarefa desafiante. Requerimentos de tempo de propagação e rotabilidade são especialmente difíceis de obter em circuitos que tem regiões com alta densidade de utilização de área. Além disso, a qualidade do posicionamento tem influência direta na qualidade do circuito e no esforço de otimização dos algoritmos de síntese da árvore de relógio (sigla do inglês CTS), roteamento e pós-posicionamento otimização. A primeira contribuição apresentada nessa tese é um algoritmo incremental de posicionamento para otimizar violações no tempo de propagação sujeito a rotabilidade. O algoritmo proposto é baseado em características das redes e dos caminhos de dados para computar posições otimizadas para as células. Posições otimizadas são aceitas somente se elas estão dentro de regiões livres de violações de roteamento. A segunda contribuição apresentada nessa tese é um algoritmo de espalhamento de células. O objetivo é mover células fora de regiões com alta densidade de área considerando efeitos adversos nas células movidas. O algoritmo proposto é baseado em técnicas de network flow e branch and cut para minimizar regiões com alta densidade de área. Fluxos de área são movidos de regiões com alta densidade de área para regiões com baixa densidade de área com caminhos com custo otimizado. Assim sendo, a concentração de células é reduzida e espaços são abertos em regiões com alta densidade de área com minimizado efeitos adversos nas células movidas. Algoritmos de legalização, posicionamento detalhado e pós-posicionamento podem utilizar esses espaços abertos para otimizar mais a solução de posicionamento. Em regiões com alta densidade de área, espaços são recursos limitados. No fluxo de posicionamento tradicional (posicionamento global, legalização e posicionamento detalhado), a otimização do

posicionamento é limitada pelo fluxo tradicional. O algoritmo proposto de espalhamento de células pode ser integrado em um fluxo misto de posicionamento que é composto de algoritmos intercalados de legalização e posicionamento detalhado. Nesse fluxo de posicionamento misto, a restrição para otimizar posicionamento detalhado em uma netlist legalizada pode ser relaxada. Algoritmos de posicionamento detalhado podem obter melhor posicionamento com uma formulação de posicionamento menos restrita. O foco dos algoritmos de legalização pode ser somente remover sobreposição de células com efeitos adversos minimizados no posicionamento ao invés de também minimizar violações de densidade de utilização de área. O algoritmo proposto de espalhamento de células é aplicado nos estágios de legalização e posicionamento detalhado para otimizar densidade de utilização de área. O algoritmo proposto de legalização obteve melhoria no espalhamento médio (30%) e máximo (350%) de células comparado com algoritmos de legalização estado da arte. No posicionamento detalhado, o algoritmo proposto foi avaliado em fluxos de posicionamento industrial e acadêmico. No fluxo de posicionamento industrial, o algoritmo proposto melhorou espalhamento de células, potência dissipada e tempo de propagação. O algoritmo proposto de espalhamento de células pode melhorar a qualidade do posicionamento em fluxos de posicionamento mistos em ambiente industrial e acadêmico. O algoritmo proposto fornece posicionamento com distribuição uniforme de células em projetos limitados com efeitos adversos minimizados nas células movidas.

Palavras-chave: EDA, Posicionamento, Otimização, Network Flow, Branch and Cut.

### LIST OF ABBREVIATIONS AND ACRONYMS

**ABU** Average Bin Utilization

**ACD** Average Cell Displacement

**ACM** Association for Computing Machinery

**ASIC** Application-Specific Integrated Circuit

**AT** Arrival Timing

B2B Bound to Bound

**BFS** Breadth-First Search

**BIST** Built-In Self-Test

**CCS** Composite Current Source

**CMOS** Complementary Metal-Oxide Semiconductor

**CPPR** Common Path Pessimism Removal

CPU Central Processing Unit

**CTS** Clock Tree Synthesis

**DAC** Design Automation Conference

**DEF** Design Exchange Format

**DRAM** Dynamic Random-access Memory

**ECSM** Effective Current Source Model

**EDA** Electronic Design Automation

Eh?L Eh?Legalizer

**ELAP** Emerging Leaders of the Americas Program

**FPGA** Field-Programmable Gate Array

FPL FastPlace Legalizer

**FSM** Finite-state Machine

**GCC** GNU Compiler Collection

GCell Global Cell

**GND** Ground

**GPU** Graphics Processing Unit

**GRO** Global Routing Overflow

**HDL** Hardware-Description Language

**HPWL** Half Perimeter Wire Length

IC Integrated Circuit

ICCAD International Conference on Computer Aided Design

**ILP** Integer Linear Programming

**IO** Input/Output

**IP-Core** Semiconductor Intellectual Property Core

**ISCAS** International Symposium on Circuits and Systems

**ISPD** International Symposium on Physical Design

**ITDP** Incremental Timing-Driven Placement

LAL Look Ahead Legalization

LCB Local Clock Buffer

**LEF** Layout Exchange Format

**LP** Linear Programming

**MIP** Mixed Integer Programming

NDR Non Default Rule

**NFCS** Network Flow-based Cell Spreading

**NFL** Network Flow-based Legalization

**NLDP** Non Linear Delay Model

**NPA** Non Placeable Area

**NP** Nondeterministic Polynomial Time

OAL Obstacle-aware Legalization

**OF** Overfilled

**P** Polynomial Time

**PATMOS** International Workshop on Power And Timing Modeling, Optimization and Simulation

PCB Printed Circuit Board

**PEKO** Placement Examples with Known Optimal

PLL Phase-locked Loop

**PTM** Predictive Technology Model

PVT Process, Voltage, and Temperature

**QoR** Quality of Results

**RAITDP** Routing-aware Incremental Timing-driven Placement

**RAT** Required Arrival Timing

**RMST** Rectilinear Minimum Spanning Tree

**RO** Routing Overflow

**RSA** Rectilinear Steiner Arborescence

**RSMT** Rectilinear Steiner Minimum Tree

**RTL** Register-Transfer Level

**SA** Simulated-Annealing

**SPEF** Standard Parasitic Exchange Format

**SRAM** Static Random-Access Memory

**STA** Static Timing Analysis

**STST** Single-Trunk Steiner Tree

**TAU** International Workshop on Timing Issues in the Specification and Synthesis of Digital Systems

TNS Total Negative Slack

**TQoR** Timing Quality of the Results

**VDD** Power

VIA Vertical Interconnect Access

**VLSI** Very Large-Scale Integration

WNS Worst Negative Slack

# LIST OF SYMBOLS

| x                    | Absolute Value           |

|----------------------|--------------------------|

| $\alpha$             | Alpha                    |

| β                    | Beta                     |

| C                    | Capacitance              |

| (x, y)               | Cartesian point          |

| {}                   | Curly Brackets           |

| $^{\circ}\mathrm{C}$ | Degree Celsius           |

| Δ                    | Delta                    |

| $\frac{x}{y}$        | Division                 |

| 3                    | Exist an element         |

| =                    | Equal Symbol             |

| $\forall$            | For all elements         |

| f(x)                 | Function Sign            |

| $\gamma$             | Gamma                    |

| >                    | Greater Than             |

| $\geq$               | Greater Than or Equal to |

| $\in$                | In Symbol                |

| $\infty$             | Infinity                 |

| $\mathbb{I}$         | Integer Numbers          |

| <                    | Less Than                |

| $\leq$               | Less Than or Equal to    |

| m                    | Meter                    |

| m                    | Milli                    |

| μ                    | Micro                    |

mod Modulo Operation

× Multiplication

n Nano

Natural Numbers

Negative or Subtraction Sign

$\omega$  Omega

() Parenthesis

% Percentage

$\pi$  Pi

+ Positive or Addition Sign

$\mathbb{R}$  Real Numbers

RC Resistance-Capacitance

$\rightarrow$  Right Arrow

s Second

$\sqrt{x}$  Square Root

$\{x,y\}$  Set Sign

$\sum$  Summation

au Tau

$\overrightarrow{x}$  Vector representation

Vertical Slash

V Volt

## LIST OF FIGURES

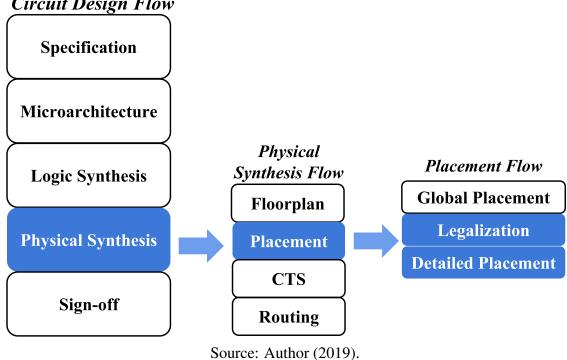

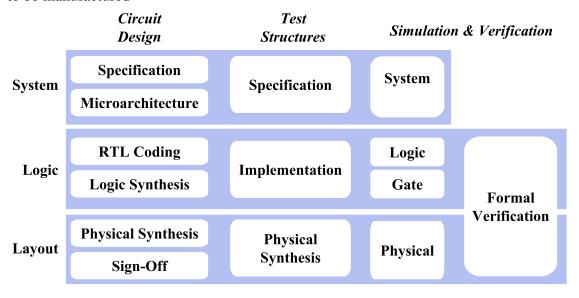

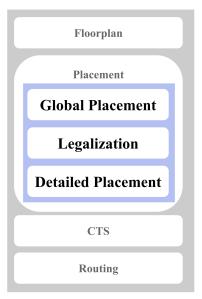

| Figure 1.1 Digital design flow. In this thesis, the proposed contributions are to optimized placement solutions in legalization and detailed placement stages                                                                                                                                                      | 32 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

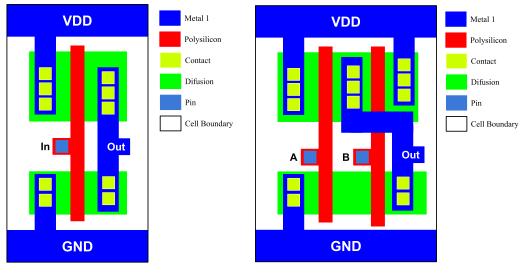

| Figure 2.1 Layout of inversor (a) and NAND (b) standard cells. Layout is a set of rectangular geometries that abstract electric functions. Standard cells are implementations of Boolean functions                                                                                                                 | 38 |

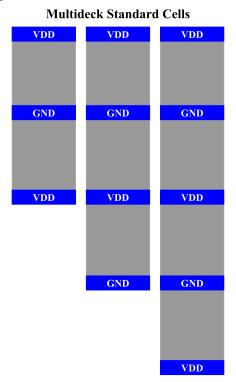

| Figure 2.2 Multideck standard cells have cell height higher than default cell height.  These standard cells have overlap with two or more rows                                                                                                                                                                     | 39 |

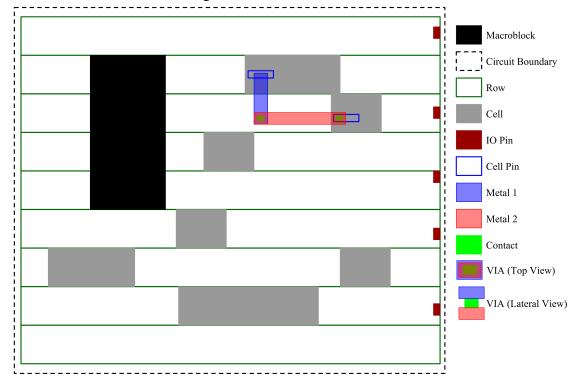

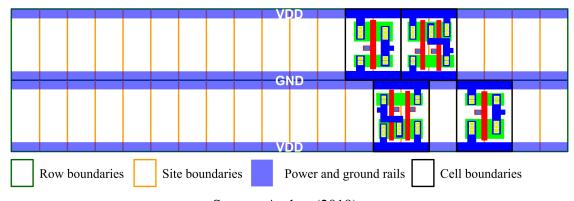

| Figure 2.3 An example of a digital circuit. Digital circuit may be composed of macroblocks, cells, Input/Output (IO) pins or pads, wires and Vertical Interconnect Accesses (VIAs). Cells are placed inside circuit core boundaries. These cells are aligned to row and site boundaries.                           | 40 |

| Figure 2.4 A row is a small part of the circuit core. Rows are divided into site areas. Cells must be aligned to the left, bottom and top site boundaries. Rows also share power rails with neighboring rows. Power rails are parallel and horizontal metal track to provide Power (VDD) and Ground (GND) to cells |    |

| Figure 2.5 In digital circuits, the clock is a periodic square wave. The clock signal controls and synchronizes operations of sequentical circuit elements                                                                                                                                                         |    |

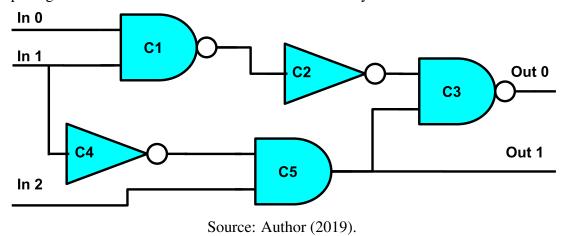

| Figure 2.6 In combinational circuits, the circuit operation depends only on changing input signals. Combinational circuits do not have memory elements                                                                                                                                                             |    |

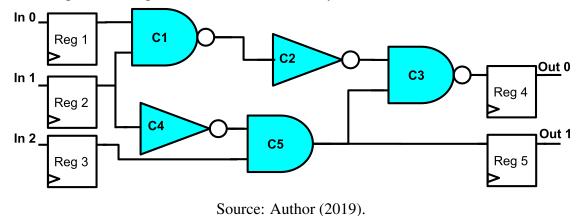

| Figure 2.7 In sequential circuits, the circuit operation depends on clock transition to launch input data. Sequential circuits have memory elements                                                                                                                                                                | 44 |

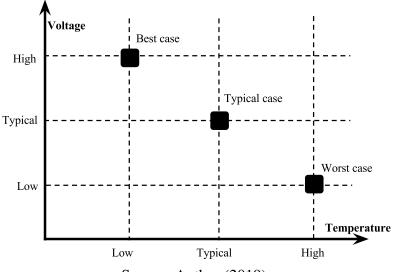

| Figure 2.8 Corner cases to characterize digital circuits. The best case provides the optimal condition to a signal propagation while the worst case provides the inverse condition to a signal propagation                                                                                                         | 47 |

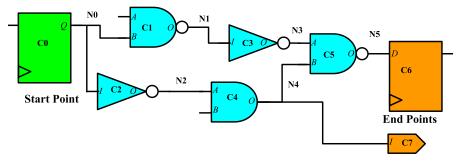

| Figure 2.9 An example of a part of a digital circuit                                                                                                                                                                                                                                                               |    |

| Figure 2.10 Representative Static Timing Analysis (STA) graph of the circuit in Figure 2.9                                                                                                                                                                                                                         | 49 |

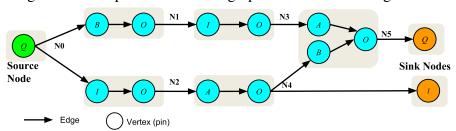

| Figure 2.11 Required arrival timing window. A data signal must arrive at the end point after the minimum (early) and before the maximum (late) required arrival timings                                                                                                                                            | 50 |

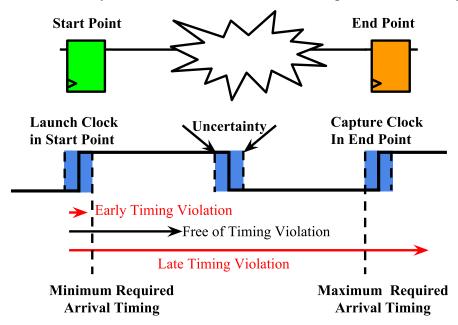

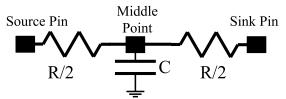

| Figure 2.12 $\pi$ wire model. Electric properties of wire segments are modeled with two capacitors that are connected by resistor                                                                                                                                                                                  |    |

| Figure 2.13 T wire model. Electric properties of wire segments with two resistors and one capacitor. One terminal of each resistor is connected to the capacitor                                                                                                                                                   |    |

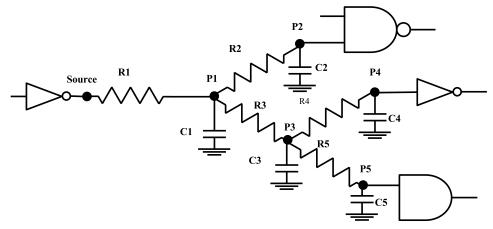

| Figure 2.14 Example of a structured RC tree network. Electric signal delay is computed from source to P5 points with Elmore model                                                                                                                                                                                  |    |

| Figure 2.15 Digital design flow comprises of three main parallel flows that are split into several steps. The circuit implementation starts with requirement documents. After several synthesis, optimization, verification, simulation steps,                                                                     |    |

| the circuit layout is ready to be manufactured                                                                                                                                                                                                                                                                     |    |

| design metrics                                                                                                                                                                                                                                                                                                     | 58 |

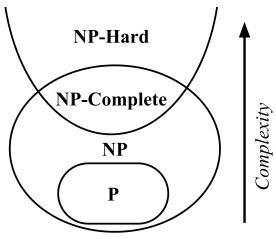

| Figure 3.1 Diagram of intersection among classes Polynomial Time (P), Nondetermin Polynomial Time (NP), NP-complete and NP-hard problems                                                                                                                                                                           |    |

| Figure 3.2 An example of a graph tree                                                                                                                                                                                                                                                                              | 65 |

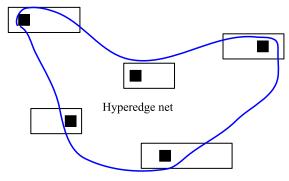

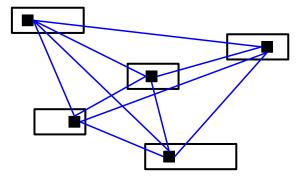

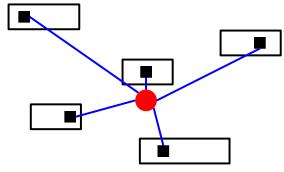

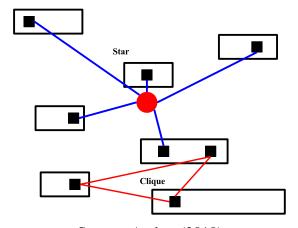

| Figure 3.3 Hyperedge nets must be decomposed into a set of pair connections between only two points using a net model. In this example, the net with five pins is decomposed into clique, star, hybrid and Bound to Bound (B2B) net models                            | 9          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Figure 3.4 All net pins are connected to each other when hyperedge nets are decomposed with the clique net model                                                                                                                                                      | 9          |

| Figure 3.5 All net pins of hyperedge nets are connected to a central point in the star net model                                                                                                                                                                      | 0          |

| Figure 3.6 In the hybrid net model, hyperedge nets that have up to 3 pins are decomposed using the clique net model. Remaining hyperedge nets are decomposed using the star net model                                                                                 | 0          |

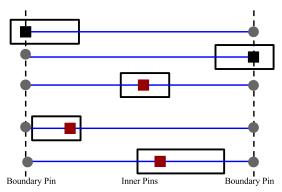

| Figure 3.7 In the B2B net model, net pins are classified into inner and outer pins. All pins of each net are connected to boundaries of net bound box. Two independent B2B net models are built for abscissa and ordinate axis of each net .7                         |            |

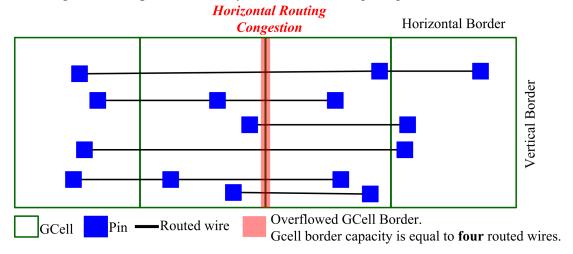

| Figure 3.8 An example of Global Cells (GCells). A GCell grid is a grid of bins which covers the circuit core. Each GCell has on each border routing capacity. Routed wires cross GCell border. A GCell grid is a simple and fast way to estimate routing congestion   | <b>'</b> 5 |

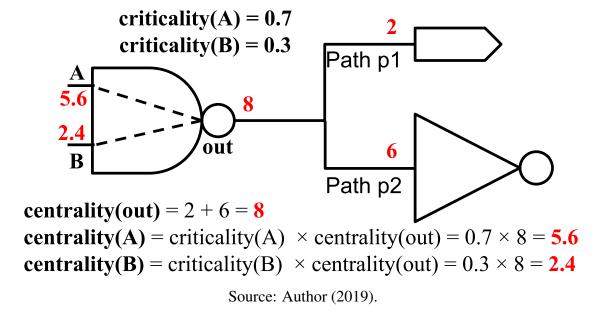

| Figure 3.9 Example to compute centrality of critical timing pins                                                                                                                                                                                                      |            |

| Figure 3.10 Grids of bins which do not have overlap and have overlap with macroblocks and fixed cells                                                                                                                                                                 |            |

| Figure 4.1 Placement optimization flow is composed of global placement, legalization, and detailed placement stages                                                                                                                                                   | 5          |

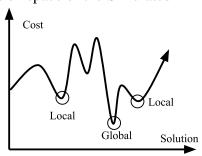

| Figure 4.2 Solution space of the Simulated Annealing algorithm8                                                                                                                                                                                                       |            |

| Figure 4.3 Examples of global and legalized placement solutions9                                                                                                                                                                                                      |            |

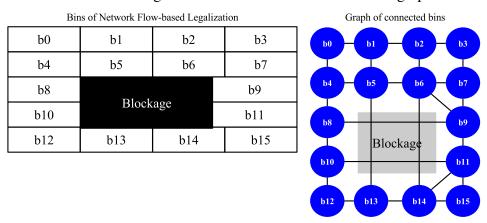

| Figure 4.4 Bins are connected to their immediate neighbors or the bins on the opposite side of macroblocks or blockages. Connected bins are modeled as a                                                                                                              |            |

| graph9                                                                                                                                                                                                                                                                | 9          |

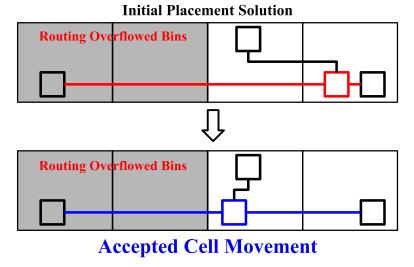

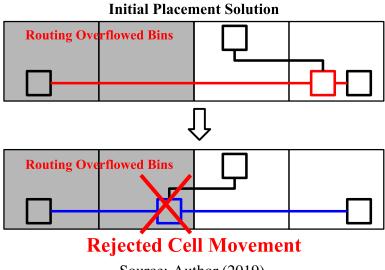

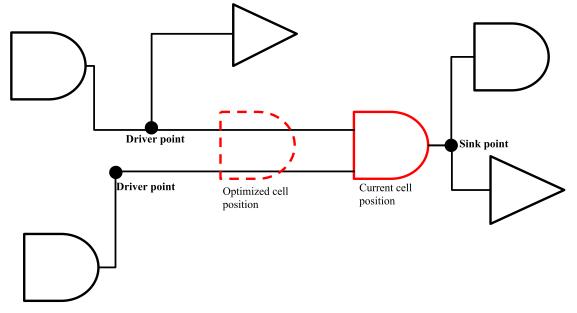

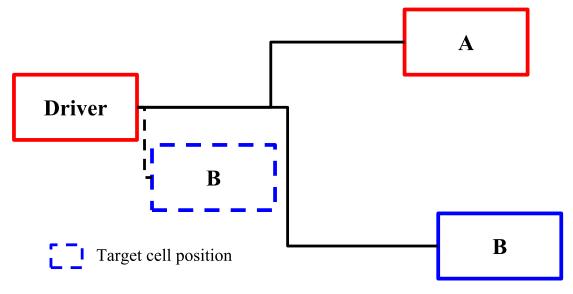

| Figure 5.1 In the proposed Routing-aware Incremental Timing-driven Placement (RAITDP) algorithm, timing critical cells are moved to positions which timing violation is improved and Routing Overflow (RO) is lower than the RO in current positions                  | 18         |

| Figure 5.2 In the proposed RAITDP algorithm, cell movements are rejected if target positions have RO. Routability restriction is relaxed if both optimized and                                                                                                        |            |

| current cell positions are inside of the same GCell                                                                                                                                                                                                                   |            |

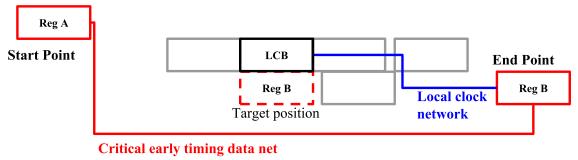

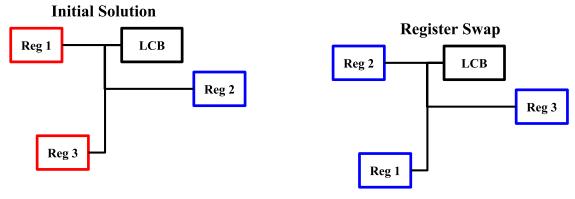

| Figure 5.4 Exploring clock skew to minimize early timing violation. End point register which is the end point of an early timing violation path is moved closer to its Local Clock Buffer (LCB). In this approach, clock latency is reduced in the end point register |            |

| Figure 5.5 Early timing violation is minimized by increasing wire capacitance and resistance in the combinatorial critical timing cell                                                                                                                                |            |

| Figure 5.6 Registers that have the same local clock network are swapped to minimize early timing violation                                                                                                                                                            |            |

| Figure 5.7 End point register of early timing violation paths are moved away from the data driver cell                                                                                                                                                                |            |

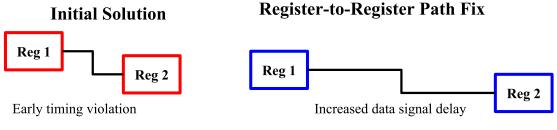

| Figure 5.8 Cluster of late critical timing cells is built. Critical timing cells are         |

|----------------------------------------------------------------------------------------------|

| moved towards optimized-timing positions. In this approach, late timing vio-                 |

| lation is minimized                                                                          |

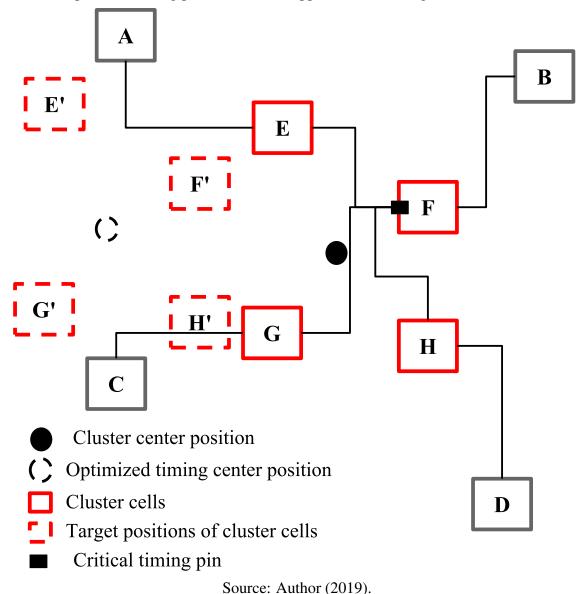

| Figure 5.9 Critical timing buffer is moved to optimized position. In this position,          |

| the total signal delay is locally minimized in input and output nets of the buffer 127       |

| Figure 5.10 Late critical timing cells are moved to optimized-timing positions129            |

| Figure 5.11 In late critical timing nets, non critical timing sink cells are moved           |

| closer to their driver cells. In this approach, wire capacitance of branches is              |

| reduced in critical timing nets                                                              |

| Figure 5.12 Moving non critical late timing cells from overfilled bins to a neighbor-        |

| ing bin with white space. In this approach, area density violation is minimized              |

|                                                                                              |

| by moving out non critical timing cell                                                       |

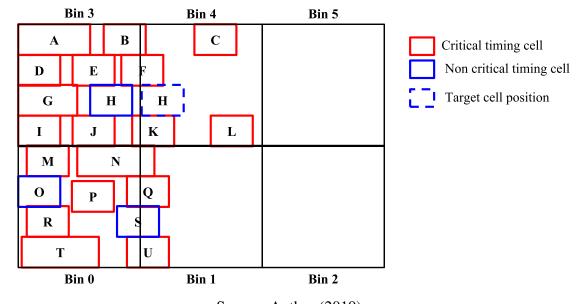

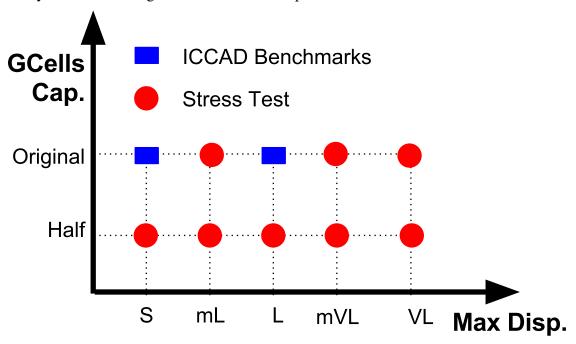

| Figure 5.13 Cell displacement constraint and GCell capacity corner cases to com-             |

| prehensively evaluated timing violations and RO improvement from the International           |

| Conference on Computer Aided Design (ICCAD) benchmarks                                       |

| Figure 5.14 In the original GCell capacity, there is no significant RO from the 2015         |

| ICCAD benchmarks                                                                             |

| Figure 5.15 In the half GCell capacity, there is more RO to properly evaluate the            |

| proposed RAITDP                                                                              |

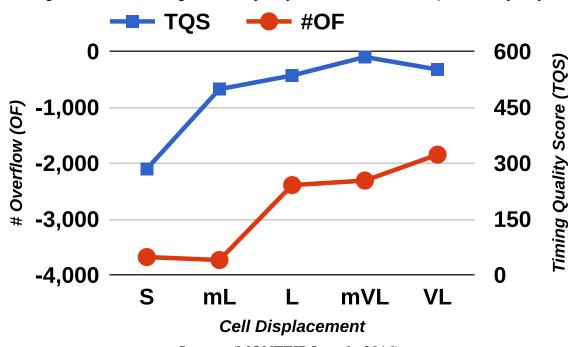

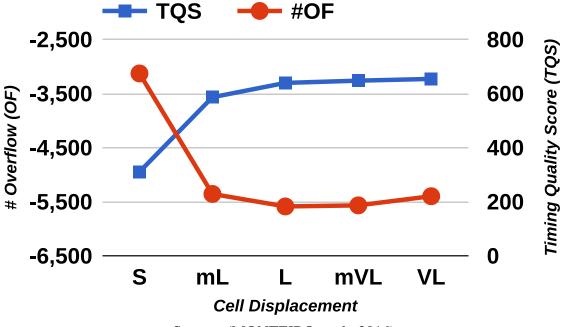

| Figure 5.16 The average RO and quality scores for the set <i>Half</i> GCell capacity144      |

| Figure 5.17 The average RO and quality scores for the set <i>Original GCell capacity</i> 145 |

| rigureeri, rine average ite ana quanty secres for an sec everyonas e con capacity arise      |

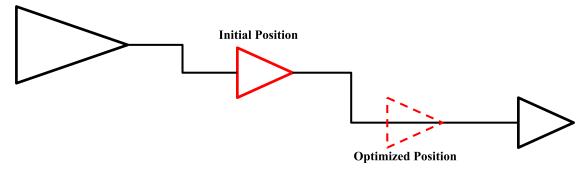

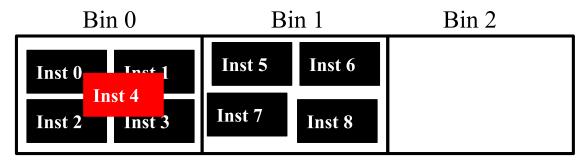

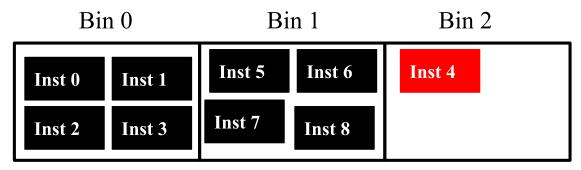

| Figure 6.1 Cell spreading approaches are presented. Cells can be directly moved              |

| to the nearest white space location. Optimized-cost paths can be computed                    |

| to move cells out from high-density regions through intermediate regions to a                |

| low-density region                                                                           |

| Figure 6.2 Example of flagging cells and computing outflow area                              |

| Figure 6.3 Example of search tree to compute optimized-cost path                             |

|                                                                                              |

| Figure 6.4 Example of cell movement between neighboring bins                                 |

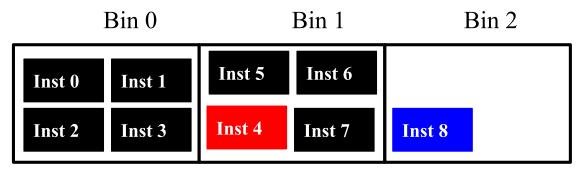

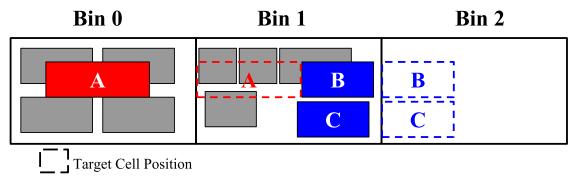

| Figure 6.5 Area overfill in bin 1 may be fixed by computing the path composed of             |

| bin 0, bin 1 and bin 2 to spread cells. Cells B and C will be moved to bin 2 to              |

| open space to receive cell A from bin 0                                                      |

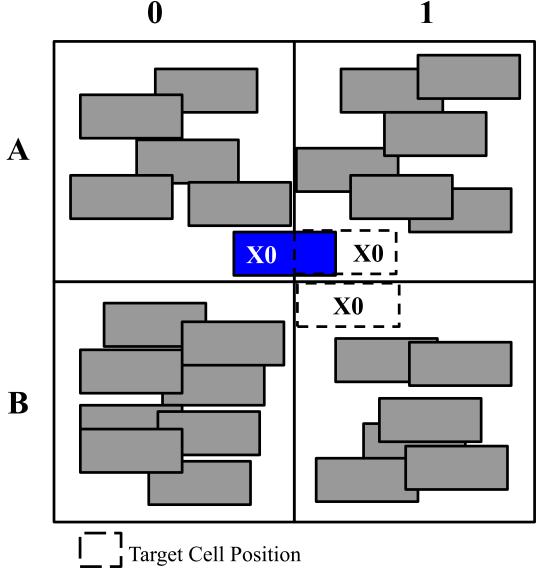

| Figure 6.6 The same cell is shared in two pairs of neighboring bins. The shared              |

| cell will cause mismatch in the inflow and outflow in the pairs of neighboring               |

| bins                                                                                         |

|                                                                                              |

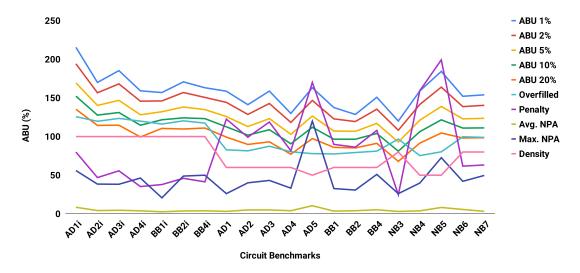

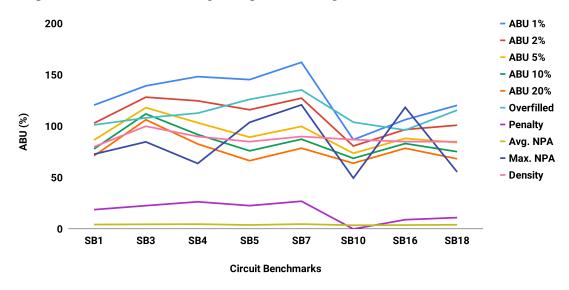

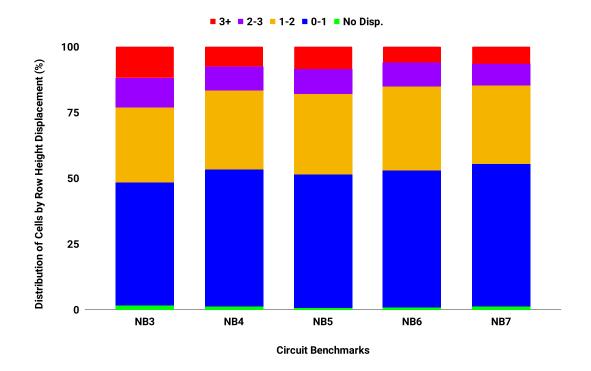

| Figure 7.1 Average Bin Utilization (ABU) distributions from the 2006 International           |

| Symposium on Physical Design (ISPD) benchmarks are presented. Circuits                       |

| have been placed with the RePlace global placement algorithm179                              |

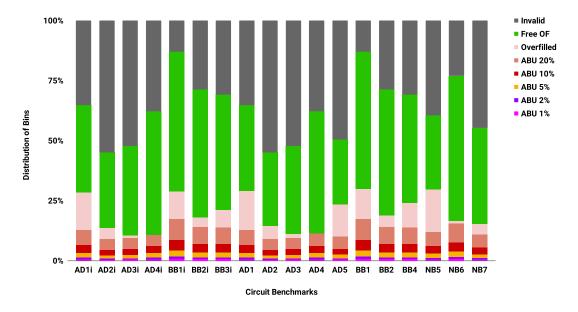

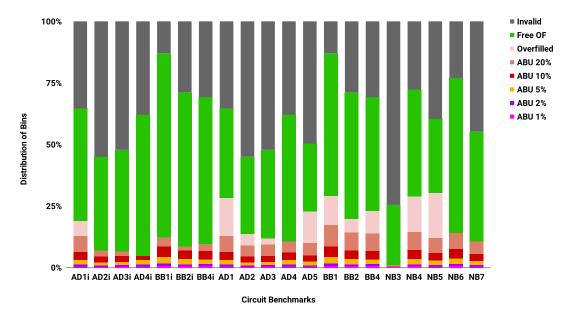

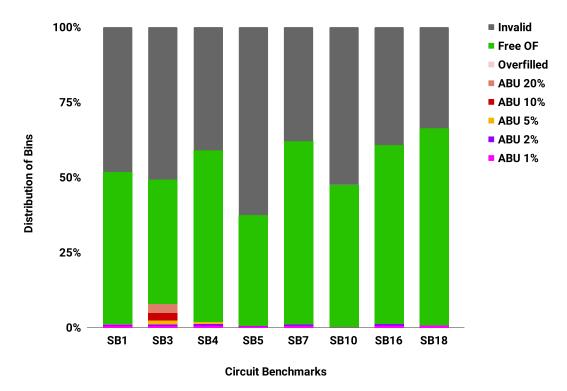

| Figure 7.2 Distribution of bins with area density violation, free of area density vi-        |

| olation and invalid bins. The 2006 ISPD contest benchmarks are placed with                   |

| the RePlace global placement algorithm180                                                    |

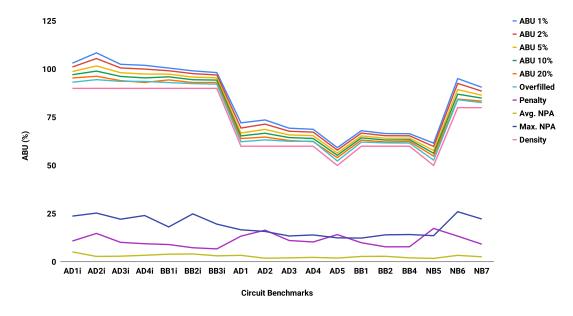

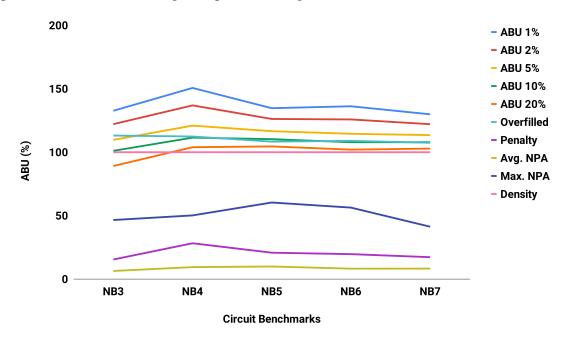

| Figure 7.3 ABU, and Non Placeable Area (NPA) from the 2006 ISPD benchmarks                   |

| are presented. These circuits have been placed with the FastPlace global                     |

| placement algorithm                                                                          |

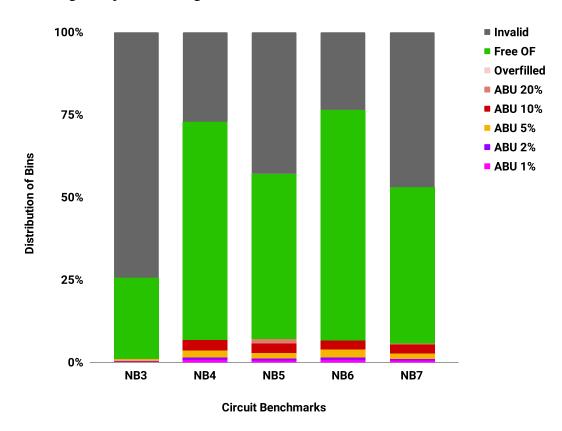

| Figure 7.4 Distribution of bins with area density violation, free of area density vio-       |

| lation and invalid ABU bins. The 2006 ISPD contest benchmarks are placed                     |

| with the FastPlace global placement algorithm                                                |

| Figure 7.5 ABU from the 2006 ISPD benchmarks is presented. These circuits have               |

| been placed with the Eh?Placer global placement algorithm 185                                |

| DOLLE DIVICED WITH THE PROPERTIONED VIOLATED INCENTED ALVOHUM                                |

| Figure 7.6 Distribution of bins with area density violation, free of area density vi- |     |

|---------------------------------------------------------------------------------------|-----|

| olation and invalid ABU bins. The 2006 ISPD contest benchmarks have been              |     |

| placed with the Eh?Placer global placement algorithm                                  | 186 |

| Figure 7.7 ABU from the 2015 ICCAD benchmarks is presented. These circuits            |     |

| have been placed with the Eh?Placer global placement algorithm                        | 187 |

| Figure 7.8 Distribution of bins with area density violation, free of area density vi- |     |

| olation and invalid ABU bins. The 2015 ICCAD contest benchmarks have                  |     |

| been placed with the Eh?Placer global placement algorithm                             | 188 |

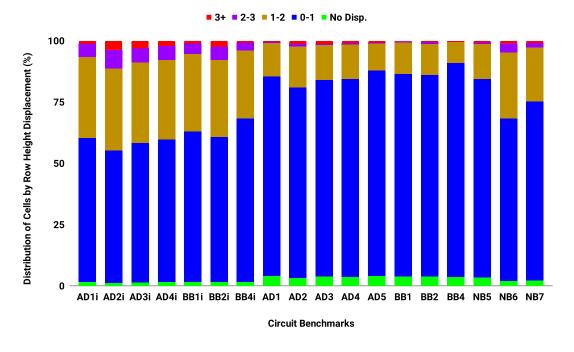

| Figure 7.9 Cell displacement from the 2006 ISPD contest benchmarks is presented.      |     |

| These circuits have been placed with the RePlace global placement algorithm.          | 190 |

| Figure 7.10 Cell displacement from the 2006 ISPD contest benchmarks is pre-           |     |

| sented. These circuits have been placed with the FastPlace global placement           |     |

| algorithm                                                                             | 193 |

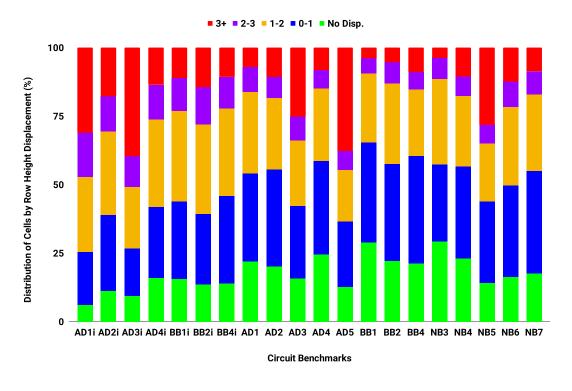

| Figure 7.11 Cell displacement of Newblue 3 to 7 circuits from the 2006 ISPD con-      |     |

| test benchmarks. These circuits have been placed with the Eh?Placer global            |     |

| placement algorithm                                                                   | 195 |

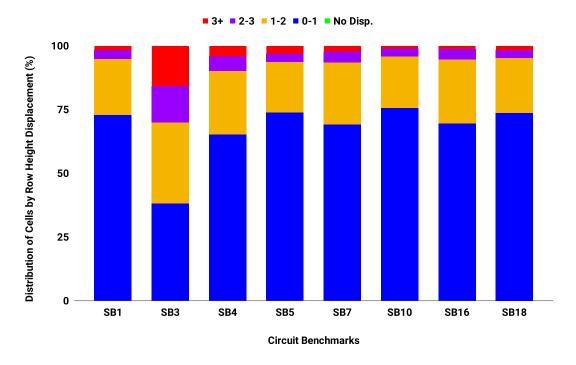

| Figure 7.12 Cell displacement of the proposed Network Flow-based Legalization         |     |

| (NFL) from the 2015 ICCAD contest benchmarks is presented. Circuits have              |     |

| been placed with the Eh?Placer global placement algorithm                             | 197 |

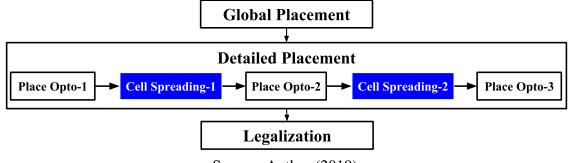

| Figure 8.1 The optimization flow of the proposed Network Flow-based Cell Spread-      |     |

| ing (NFCS) algorithm in commercial flow                                               | 201 |

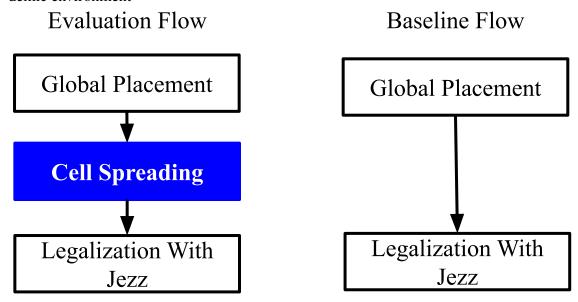

| Figure 8.2 Experimental configuration of the proposed cell spreading algorithm in     | 201 |

| academic environment                                                                  | 204 |

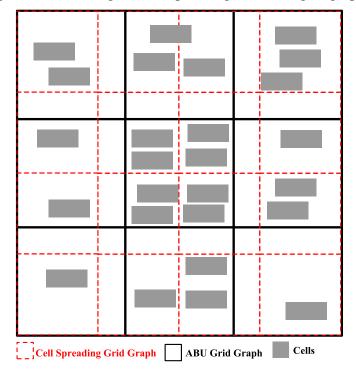

| Figure 8.3 Non-aligned cell spreading and ABU grid graphs                             |     |

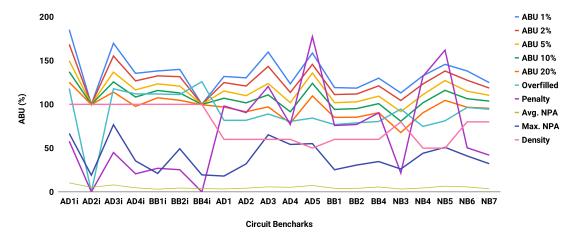

| Figure 8.4 ABU distributions from the 2006 ISPD circuits are presented. The cell      | 201 |

| spreading and ABU grid graphs are not aligned. Circuits have been placed              |     |

| with the FastPlace global placement algorithm                                         | 206 |

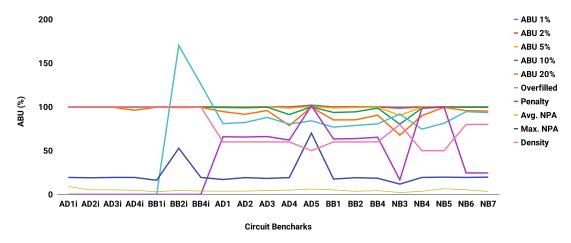

| Figure 8.5 ABU distributions from the 2006 ISPD circuits are presented. Cell          | 200 |

| spreading and ABU grid graphs are aligned. Circuits have been placed with             |     |

| the FastPlace global placement algorithm                                              | 210 |

| are raise from biacomone argorium                                                     |     |

## LIST OF TABLES

| Table 3.1 Weights of average area utilization of $\gamma$ highest overfilled bins74                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 3.2 2014 and 2015 ICCAD contest weights to compute the Timing Quality of the Results                                                                                                                                                   |

|                                                                                                                                                                                                                                              |

| Table 5.1 Results comparing the developed RAITDP with the top 3 teams from the 2015 ICCAD contest and Incremental Timing-Driven Placement (ITDP) (FLACH et al., 2016) for the set <i>Original</i> GCell capacity of Fig. 5.13141             |

| Table 5.2 Timing violation and routing overflow improvement by changing cell displacement constraint and GCell capacity as introduced in Figure 5.13143                                                                                      |

| Table 7.1 Chracteristics of the 2006 ISPD contest circuit bechmarks                                                                                                                                                                          |

| Table 7.2 Chracteristics of the 2015 ICCAD contest circuit bechmarks                                                                                                                                                                         |

| Table 7.3 ABU, NPA and area density constraints of the 2006 ISPD circuit benchmarks are given. These circuits have been placed with the RePlace global                                                                                       |

| placement algorithm. ABU, NPA and area density constraints are presented                                                                                                                                                                     |

| in percentages                                                                                                                                                                                                                               |

| marks are presented. These circuits have been placed with the FastPlace global placement algorithm. ABU, NPA and area density constraints are pre-                                                                                           |

| sented in percentages                                                                                                                                                                                                                        |

| Table 7.5 ABU, NPA and area density constraints of the 2006 ISPD circuit benchmarks are presented. These circuits have been placed with the Eh?Placer global placement algorithm. ABU, NPA and area density constraints are pre-             |

| sented in percentages                                                                                                                                                                                                                        |

| Table 7.6 ABU, NPA and area density constraints of the 2015 ICCAD circuit benchmarks are presented. These circuits have been placed with the Eh?Placer global placement algorithm. ABU, NPA and area density constraints are pre-            |

| sented in percentages                                                                                                                                                                                                                        |

| Table 7.7 Experimental Results of the proposed NFL algorithm are compared with FastPlace Legalizer (FPL) and Jezz. The 2006 ISPD circuit benchmarks have been placed with RePlace algorithm                                                  |

| Table 7.8 Experimental Results of the proposed NFL algorithm are compared with                                                                                                                                                               |

| FastPlace Legalizer (FPL) and Jezz. The 2006 ISPD benchmarks are placed with the FastPlace algorithm                                                                                                                                         |

| Table 7.9 The proposed NFL algorithm is evaluated from the 2006 ISPD benchmarks. The 2006 ISPD benchmarks have been placed with the Eh?Placer al-                                                                                            |

| gorithm. Experimental results of the proposed NFL algorithm are compared with Jezz and Eh?Legalizer (Eh?L) algorithms                                                                                                                        |

| with the Jezz legalizer. The 2015 ICCAD benchmarks are placed with the                                                                                                                                                                       |

| Eh?Placer algorithm196                                                                                                                                                                                                                       |

| Table 8.1 Experimental results in the commercial environment. The proposed NFCS algorithm is inserted in two stages of the commercial detailed placement flow. The two flows (with and without) the proposed NFCS algorithm are compared.202 |

| Table 8.2 ABU improvement from the proposed NFCS algorithm in non-aligned ABU and cell spreading grid graphs. ABU, NPA and area density restriction (density) are presented in percentage                                                    |

| (uchsity) are dieschied in dercentage                                                                                                                                                                                                        |

| Table 8.3 The Average Cell Displacement (ACD) of the proposed NFCS algorithm in non-aligned ABU and cell spreading grid graphs. The ACD is presented    |      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| in number of row heights.                                                                                                                               | 207  |

| Table 8.4 Legalization results from Jezz and CSJ flows in non-aligned ABU and cell spreading grid graphs.                                               | 208  |

| Table 8.5 ABU improvement from the proposed NFCS algorithm in aligned ABU                                                                               | 208  |

| and cell spreading grid graphs. ABU, NPA and area density restriction (den-                                                                             |      |

| sity) are presented in percentage.                                                                                                                      | 209  |

| Table 8.6 ACD of the proposed NFCS algorithm in aligned ABU and cell spreading                                                                          |      |

| grid graphs. ACD is presented in number of row heights.                                                                                                 | 211  |

| Table 8.7 Legalization results from Jezz and CSJ flows in aligned ABU and cell                                                                          |      |

| spreading grid graphs.                                                                                                                                  | 212  |

| Table 8.8 Experimental results on academic circuits. The proposed NFCS algo-                                                                            |      |

| rithm is evaluated in two legalization flows. The first flow is composed only                                                                           |      |

| of the legalizer while the second flow is composed of the proposed algorithm and the legalizer.                                                         | 214  |

| Table 8.9 Experimental results of the proposed algorithm in academic benchmarks.                                                                        | ∠14  |

| The proposed NFCS algorithm is evaluated in two flows. In one flow, MDP (LI                                                                             | N    |

| et al., 2016) binary is executed before NFCS algorithm. In the second flow,                                                                             |      |

| only MDP is executed.                                                                                                                                   | 214  |

|                                                                                                                                                         |      |

| Table A.1 Distribution of bins with ABU violation (ABU 1% to 20%), Overfilled                                                                           | 222  |

| (OF) bins, bins free of OF, NPA, invalid and total bins.                                                                                                | 233  |

| Table A.2 The number of bins with area density violations, free of overfill and invalid ABU. The 2006 ISPD contest benchmarks are placed with the Fast- |      |

| Place global placement algorithm.                                                                                                                       | 235  |

| Table A.3 The total number of bins are presented. These bins are classified into                                                                        |      |

| area density violation, free of overfill area and invalid types. In the 2006                                                                            |      |

| ISPD contest benchmarks, Newblue circuits from 3 to 7 have been placed                                                                                  |      |

| with the Eh?Placer global placement algorithm.                                                                                                          | 235  |

| Table A.4 The total number of bins are presented. These bins are classified into                                                                        |      |

| area density violation, free of overfill area and invalid types. The 2015                                                                               |      |

| ICCAD contest circuit benchmarks are placed with the Eh?Placer global                                                                                   | 226  |

| placement algorithm.                                                                                                                                    | 236  |

| Table A.5 Distribution of total cells by row height displacement for circuits from the 2006 ISPD benchmarks.                                            | 238  |

| Table A.6 Distribution of cells by row height displacement for circuits from the                                                                        | 236  |

| 2006 ISPD benchmarks                                                                                                                                    | 238  |

| Table A.7 Distribution of total cells by row height displacement                                                                                        |      |

| Table A.8 Distribution of cells by row height displacement for circuits from the                                                                        | 237  |

| 2006 ISPD benchmarks                                                                                                                                    | 239  |

| Table A.9 Distribution of total cells by row height displacement for Newblue 3 to                                                                       |      |

| 7 circuits from the 2006 ISPD benchmarks.                                                                                                               | 240  |

| Table A.10 Distribution of cells by row height displacement for Newblue 3 to 7                                                                          |      |

| circuits from the 2006 ISPD benchmarks.                                                                                                                 | 240  |

| Table A.11 Distribution of total cells by row height displacement for circuits from                                                                     |      |

| the 2015 ICCAD benchmarks.                                                                                                                              | 241  |

| Table A.12 Percentage of cell distribution by row height displacement for circuits                                                                      | 0.44 |

| from the 2015 ICCAD benchmarks.                                                                                                                         | 241  |

| Table B.1 The Electronic Design Automation (EDA) contests in past years hosted |     |

|--------------------------------------------------------------------------------|-----|

| by ISPD                                                                        | 245 |

| Table B.2 The EDA contests in past years hosted by International Workshop on   |     |

| Timing Issues in the Specification and Synthesis of Digital Systems (TAU)      |     |

| and International Workshop on Power And Timing Modeling, Optimization          |     |

| and Simulation (PATMOS)                                                        | 245 |

| Table B.3 The EDA contests in past years hosted by Design Automation Confer-   |     |

| ence (DAC)                                                                     | 245 |

| Table B.4 The EDA contests in past years hosted by ICCAD                       | 246 |

| - ·                                                                            |     |

# CONTENTS

| 1 INTRODUCTION                                                    | 29 |

|-------------------------------------------------------------------|----|

| 1.1 Motivation                                                    |    |

| 1.2 Contributions                                                 |    |

| 1.3 Thesis Organization                                           | 33 |

| 2 DIGITAL CIRCUIT DESIGN                                          | 37 |

| 2.1 Introduction                                                  |    |

| 2.2 Digital Circuit Definitions                                   | 37 |

| 2.2.1 Library Cells                                               | 38 |

| 2.2.2 Digital Circuit                                             | 39 |

| 2.2.3 Manufacturing Process                                       | 41 |

| 2.2.4 Clock Signal                                                | 42 |

| 2.2.5 Memory Components                                           |    |

| 2.2.6 Combinational and Sequential Circuits                       | 43 |

| 2.2.7 Digital Circuit Designs                                     | 44 |

| 2.2.8 Circuit Power and Timing Characterization                   |    |

| 2.2.9 Digital and Analogical Circuits                             | 47 |

| 2.3 Static Timing Analysis                                        | 47 |

| 2.4 Electrical Wire Models                                        | 51 |

| 2.4.1 Traditional Electrical Wire Models                          | 52 |

| 2.5 Digital Design Flow                                           | 54 |

| 2.5.1 Design flow                                                 | 54 |

| 2.5.2 Test Structure Flow                                         | 56 |

| 2.5.3 Formal Verification and Simulation                          | 56 |

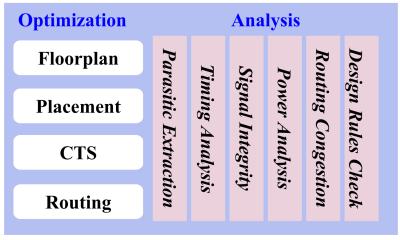

| 2.5.4 Physical Synthesis Flow                                     | 57 |

| 2.6 Summary                                                       |    |

| 3 ELECTRONIC DESIGN AUTOMATION                                    | 61 |

| 3.1 Introduction                                                  | 61 |

| 3.2 Algorithm Definitions                                         | 62 |

| 3.3 Graph Definitions                                             | 64 |

| 3.4 Optimization Algorithms                                       |    |

| 3.4.1 Network Flow                                                | 66 |

| 3.4.2 Branch and Cut                                              | 67 |

| 3.5 Models to Decompose Hyperedge Nets                            | 68 |

| 3.6 Circuit Evaluation Metrics                                    | 71 |

| 3.6.1 Wire Length                                                 | 72 |

| 3.6.2 Area Density Utilization                                    | 73 |

| 3.6.3 Routing Congestion                                          | 75 |

| 3.6.4 Timing Violations                                           | 77 |

| 3.6.5 Driver Strength, Criticality and Centrality                 | 78 |

| 3.6.5.1 Driver strength                                           | 78 |

| 3.6.5.2 Criticality                                               | 79 |

| 3.6.5.3 Centrality                                                | 79 |

| 3.6.6 Cell Displacement                                           | 80 |

| 3.7 Grid of Bins for Network Flow-based Cell Spreading Algorithms | 81 |

| 3.8 Physical Synthesis                                            | 82 |

| 3.9 Summary                                                       |    |

| 4 DIGITAL CIRCUIT PLACEMENT                                       | 85 |

|                                                                   |    |

| 4.2 Global Placement                                                      | 86         |

|---------------------------------------------------------------------------|------------|

| 4.2.1 Stochastic Global Placement.                                        |            |

| 4.2.2 Partitioning-based Placement                                        |            |

| 4.2.3 Analytical Global Placement                                         |            |

| 4.2.4 Wire Length-driven Global Placement                                 |            |

| 4.2.5 Timing-driven Global Placement                                      |            |

| 4.2.6 Routing-driven Global Placement                                     |            |

| 4.3 Legalization                                                          | 96         |

| 4.3.1 Network Flow-based Legalization Algorithms                          |            |

| 4.4 Detailed Placement                                                    |            |

| 4.4.1 Wire Length-driven Detailed Placement                               | 102        |

| 4.4.2 Timing-driven Detailed Placement                                    |            |

| 4.4.3 Routing-driven Detailed Placement                                   |            |

| 4.5 Summary                                                               | 105        |

| 5 ROUTING-AWARE INCREMENTAL TIMING-DRIVEN PLACEMENT                       | 107        |

| 5.1 Introduction                                                          | 107        |

| 5.2 The Proposed Routing-aware Incremental Timing-driven Placement Op-    |            |

| timization Algorithm                                                      | 108        |

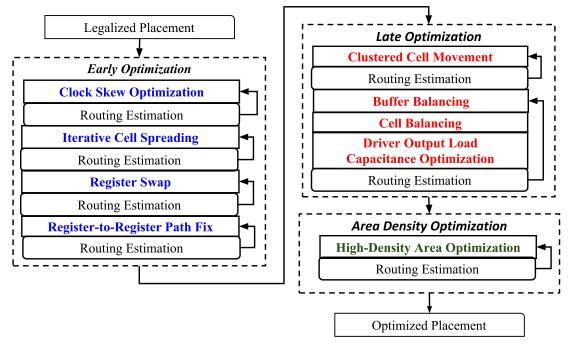

| 5.2.1 Algorithm Outline                                                   | 111        |

| 5.2.2 Early Optimization                                                  |            |

| 5.2.2.1 Clock Skew Optimization                                           | 112        |

| 5.2.2.2 Iterative Cell Spreading                                          |            |

| 5.2.2.3 Register Swap                                                     | 117        |

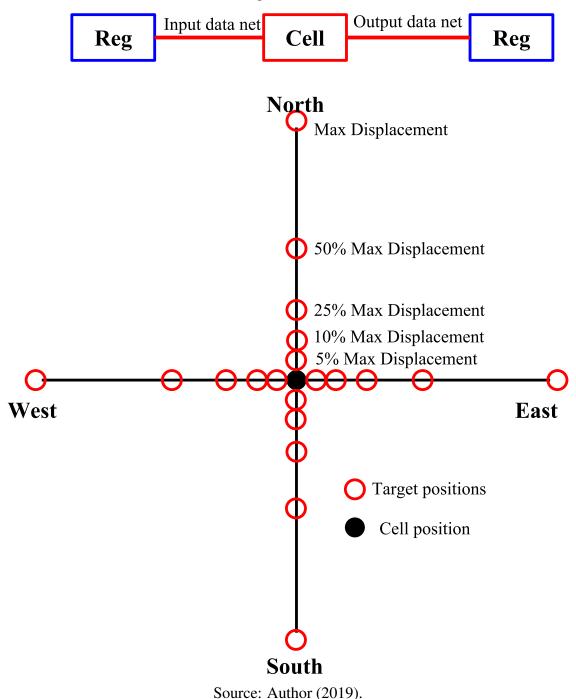

| 5.2.2.4 Register-to-Register Path Fix                                     |            |

| 5.2.3 Late Optimization                                                   |            |

| 5.2.3.1 Clustered Cell Movement                                           |            |

| 5.2.3.2 Buffer Balancing                                                  |            |

| 5.2.3.3 Cell Balancing                                                    |            |

| 5.2.3.4 Driver Load Capacitance Optimization                              |            |

| 5.2.4 Area Density Optimization                                           |            |

| 5.2.5 Cell Movement Algorithm                                             |            |

| 5.3 Experimental Results                                                  |            |

| 5.3.1 Experimental Setup                                                  |            |

| 5.3.2 Numerical Results                                                   |            |

| 5.4 Summary                                                               | 145        |

| 6 THE PROPOSED NETWORK FLOW-BASED CELL SPREADING AL-                      | 4.48       |

| GORITHM                                                                   |            |

| 6.1 Introduction                                                          |            |

| 6.2 Overview of the Proposed Network Flow-based Cell Spreading Technique. |            |

| 6.2.1 An Example of Cell Spreading                                        |            |

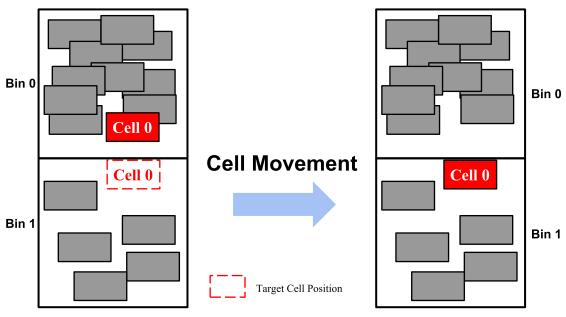

| 6.2.3 Cell Movement                                                       |            |

|                                                                           |            |

| 6.3 Grid Graph                                                            |            |

| 6.4 The Proposed Cell Spreading Algorithm                                 |            |

| 6.4.1 Path Augmentation Algorithm                                         |            |

| 6.4.3 Cell Movement Algorithm                                             |            |

| 6.5 Summary                                                               |            |

| 7 THE PROPOSED NETWORK FLOW-BASED CELL SPREADING AP-                      | 100        |

| PLIED IN LEGALIZATION                                                     | 160        |

| 7.1 Introduction                                                          |            |

|                                                                           | ·• • • • / |

| 7.3 The Proposed Network Flow-based Legalization Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | .170                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| 7.5 The Troposed Network Flow-based Leganization Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | .171                                                             |

| 7.3.1 Cell Legalization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | .172                                                             |

| 7.4 Experimental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                  |

| 7.4.1 Characteristics of the Circuits in the Contest Benchmarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | .173                                                             |

| 7.4.1.1 Characteristics from the 2006 ISPD Benchmarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | .173                                                             |

| 7.4.1.2 Characteristics from the 2015 ICCAD Benchmarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | .176                                                             |

| 7.4.2 Global Placement Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | .178                                                             |

| 7.4.2.1 RePlace Solution from the 2006 ISPD Benchmarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | .178                                                             |

| 7.4.2.2 FastPlace Solution from the 2006 ISPD Benchmarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | .181                                                             |

| 7.4.2.3 Eh?Placer Solution from the 2006 ISPD Benchmarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | .183                                                             |

| 7.4.2.4 Eh?Placer Solution from the 2015 ICCAD Benchmarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | .184                                                             |

| 7.4.3 Experimental Results of Legalization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | .187                                                             |

| 7.4.3.1 Legalization Results of the RePlace placement solutions from the 2006 ISPD contest benchmarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | .187                                                             |

| 7.4.3.2 Legalization Results of the FastPlace placement solutions from the 2006                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                  |

| ISPD contest benchmarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | .190                                                             |

| 7.4.3.3 Legalization Results of the Eh?Placer placement solutions from the 2006 ISPD contest benchmarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | .194                                                             |

| 7.4.3.4 Legalization Results of the Eh?Placer placement solutions from the 2015                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                  |

| ICCAD contest benchmarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | .195                                                             |

| 7.5 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                  |

| 7.5.1 Summary of Global Placement Solutions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                  |

| 7.5.2 Summary of Legalization Solutions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                  |

| 8 THE PROPOSED NETWORK FLOW-BASED CELL SPREADING AP-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                  |

| PLIED IN DETAILED PLACEMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | .199                                                             |