# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

## LEANDRO ÁVILA DE ÁVILA

## **Cross-Layer Energy Model of IR-UWB for Short-Range Communication Systems**

Thesis presented in partial fulfillment of the requirements for the degree of Doctor in Microeletronics

Advisor: Prof. Dr. Sergio Bampi

## CIP - CATALOGING-IN-PUBLICATION

Ávila de Ávila, Leandro

Cross-Layer Energy Model of IR-UWB for Short-Range Communication Systems / Leandro Ávila de Ávila. – Porto Alegre: PPGC da UFRGS, 2019.

150 f.: il.

Thesis (Ph.D.) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica, Porto Alegre, BR-RS, 2019. Advisor: Sergio Bampi.

I. Bampi, Sergio. II. Título.

## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Rui Vicente Oppermann Vice-Reitor: Prof. Jane Fraga Tutikian

Pró-Reitor de Pós-Graduação: Prof. Celso Giannetti Loureiro Chaves Diretor do Instituto de Informática: Prof. Carla Maria Dal Sasso Freitas Coordenadora do PGMicro: Prof. Fernanda Gusmão de Lima Kastensmidt Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

## **ACKNOWLEDGMENTS**

I would like to thank my advisor, Prof. Dr. Sergio Bampi, for all his support in recent years. He has always been a friend hand and shoulder, which bring me more than technical knowledge, gave me a lot of clarification and a way to follow until this final version of this thesis. I will be very and eternally grateful to him.

It was very important for me to meet excellent professionals with whom I had the pleasure of living in our academic environment. Thanks Prof. Dr. Juergen Rochol (my unofficial coadvisor on many occasions), Prof. Dr. Edison Pignaton, and Prof. Dr. Rafael Kunst. They added precious value with their advisement for the development of my thesis, whenever I needed. And in the army, my special thanks to Lt. Col. Luciene da Silva Demenicis (even while she was in IME), Col. Mario Jorge Costa Câmara, and Col. Jorgito Matiuzzi Stocchero also for their invaluable support when I most needed it.

Also, it is essential at this moment to recognize all members of my research group, since the beginning they fought on my side for novel academic contributions, always focusing on the best results. The road was turbulent, but we had meaningful results. And there is another special group of people that I would like to thank for their invaluable support and contribution, my colleagues from Lab 110 and 215, for them I would rather not make a list of names, cause I am afraid of committing any injustice.

My special thanks also to the UFRGS and the Brazilian Army by last years, institutions that I have been connected and I will intend to work for a long time ahead, one of my purposes is to develop a common research project agenda together. I believe both can win for science and technology of Brazil if they work together.

I dedicated this academic work to my beloved wife (Cíntia G. Simão de Ávila), to my son (Pedro) and daughter (Ana), they always gave me their cooperation and support during all the steps of this difficult journey. Thanks to my parents, Claudete and Hildo (*in memoriam*), I became the man I am. Thanks also to my brother Alex. I always say thank God for my family, my job and my career. Therefore, I feel blessed and in the obligation to dedicate me more and more to growth in all levels and areas of my life.

#### **ABSTRACT**

Short-range data communications and microelectronics circuits design are distinct and important fields of knowledge and there are few points of convergence between them in academic research. In the academic literature of each field there are few inter-related works and it is sparse the cross-referencing between them. All equipment for communication systems uses integrated circuit (ICs), which indicates a key connection between these engineering fields. The Open System Interconnection reference model is devoted to describe the abstraction levels in layers with their components, known as OSI layers. The power profiles of the first and second levels (PHY and MAC) for data communication are among the main concerns of this work. The PHY level is associated with the hardware (microelectronic devices included), and the MAC concentrates the low-level strategies to control the medium access. The energy of the whole system can be minimized by performing direct control on the PHY and MAC layers and, in this sense, the interplay between them constitutes a cross-layer model. At the PHY level, where the integrated circuits design contributes with gains when the investigation of architectures, circuits and devices produce better hardware performance, specific tools are used to reach power reduction, representing a partial optimization of the model. At the MAC level, other aspects impact energy consumption and need to be assessed - for example, the duty cycle and algorithms to deal with fails in the communication process. In this work, the context where the data communication is employed is based on IEEE 802.15.6 standard, for wireless body area networks (WBANs). This work focuses mainly on the logic design of the forward error correction (FEC) coding and decoding hardware. The CODECs are embedded inside the transceivers, and these transceivers can be part of the nodes of a wireless sensor network. This research addresses the energy consumption model involving these modules. At the PHY level, the electrical UWB waveforms generated by the TX are also analyzed for better energy efficiency. This thesis covers three design aspects of the communication systems, which adheres to the 802.15.6 standard, and are at different layers, modeling the energy required in a cross-layer view. Namely, these aspects are: the way by which Ultra-Wideband (UWB) communication takes place with impulse modulation over the 3.1 GHz - 10.6 GHz bands, the relationship of the analytic equations of the energetic model concerning also the link budget, and the low-power hardware comparison, focusing on the FEC decoding hardware that was designed in this thesis. The contributions of the research include: i) the pulse-shaping and modulation analysis, with a PPM modulation, with 3 or more bits, using PSWF pulses for higher spectral and energy efficiencies; ii) the BCH FEC decoder, designed in CMOS VLSI, with demonstrated advantages over the QC-LDPC, as the latter consumes 3.76 times more power for similar coding and data rates; iii) the improvement of the cross-layer energy efficiency model for IR-UWB, and its simulation in the operating scenario with multiple nodes that adhere to the IEEE standard 802.15.6.

**Keywords:** WBAN, Ultra-wide Band - UWB, IR-UWB, Cross-Layer Energy Model, Energy Efficiency, CMOS Digital Design.

## Modelo Energético *Cross-Layer* de IR-UWB para Sistemas de Comunicação de Curto Alcance

## **RESUMO**

Sistemas de comunicação de dados de curto alcance no nível sistêmico e a microeletrônica são dois campos distintos e importantes do conhecimento, e normalmente são tratados separadamente nas pesquisas acadêmicas. O inter-relacionamento entre eles e as referências cruzadas são esparsas na bibliografia acadêmica especializada de cada campo. Todos os equipamentos para comunicação usam circuitos integrados, o que indica uma conexão intrínseca entre estes campos da engenharia. Na comunicação de dados, o modelo de Camadas OSI (Open System Interconnection Reference Model) possibilita a abstração em níveis, com seus componentes denominados em camadas. Os perfis de consumo energético para a primeira e segunda camadas (PHY e MAC) são temas principais deste trabalho. A camada física (nível 1, ou PHY) é diretamente associada ao hardware (incluindo os circuitos integrados), na qual o projeto ou design de chips é efetivamente utilizada, e o nível MAC concentra as estratégias de baixo-nível (em hardware/software) para controlar o acesso ao meio físico de transmissão/recepção. A energia consumida no sistema todo pode ser minimizada pelo controle direto nas camadas PHY e MAC, e, neste sentido, a relação entre estas constitui o modelo de multi-camadas (Cross-Layer). No nível PHY, no qual o projeto de circuitos integrados contribui com ganhos quando a investigação de arquiteturas, circuitos e dispositivos produz melhor desempenho do hardware, ferramentas específicas são usadas para obter redução de potência, representando então uma otimização parcial do modelo. Aspectos da camada de controle de acesso ao meio (nível 2, MAC) - como o ciclo de trabalho e os algoritmos para tratar com falhas no processo de comunicação, por exemplo - também são abordados para a constituição do modelo Cross-Layer que seja energeticamente eficiente. Neste trabalho, a comunicação de dados é tratada no contexto das redes sem fio de abrangência corporal (WBAN) que aderem ao padrão IEEE 802.15.6. O projeto lógico de circuitos digitais CMOS para correção de erros à frente na comunicação (codificadores e decodificadores, ou codecs de FEC) é um foco deste trabalho. Os codecs são parte do hardware dos transceptores, e estes são parte dos nós de uma rede de sensores sem-fio. No nível PHY, as formas de ondas elétricas UWB geradas pelo TX são também analisadas para melhor eficiência energética. Esta tese cobre três aspectos do design do sistema de comunicação, que adere ao standard 802.15.6, e que estão em diferentes níveis, modelando o consumo energético numa abordagem Cross-Layer. Aspectos que estão relacionados à potência demandada no sistema, sendo eles: o formato pelo qual ocorre a comunicação em *Ultra-Wideband* (UWB), utilizando sinais em Rádio Frequência na faixa de 3,1 GHz até 10,6 GHz com modulação por impulso (IR-UWB), a correlação existente nas equações analíticas de um modelo energético (considerando-se o comportamento da potência do sinal no meio de propagação - atenuações e ganhos) e, por fim, a comparação da potência consumida pelo hardware *low-power* do decodificador de erros que foi projetado nesta tese com decodificadores alternativos. As contribuições do trabalho abrangem: i) a análise da modulação e pulse-shaping, com a modulação PPM, com 3 ou mais bits, usando pulsos PSWF para eficiência energética e espectral; ii) O decodificador FEC BCH, projetado em VLSI CMOS, com vantagens sobre o decodificador QC-LDPC, pois este consome 3,76 vezes mais potência para taxas de codificação similares; iii) o aperfeiçoamento de um modelo de eficiência energética "cross-layer"para o IR-UWB, e sua simulação em cenário de operação com múltiplos nodos aderentes ao standard IEEE 802.15.6.

## **Palavras-chave:**

WBAN, Ultra-wide Band, IR-UWB, FEC, BCH, Eficiência Energética, Modelo Cross-Layer, Circuitos Digitais CMOS.

## **LIST OF FIGURES**

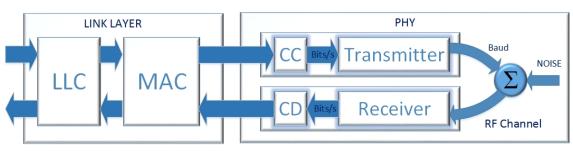

| 1.1  | Transceiver Block Diagram                                               | 21 |

|------|-------------------------------------------------------------------------|----|

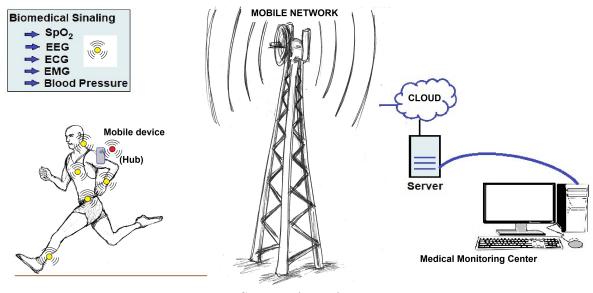

| 1.2  | Example of WBAN's architecture – network for human signal monitoring.   | 23 |

| 1.3  | Network for a Smart City with IoT sensors around                        | 24 |

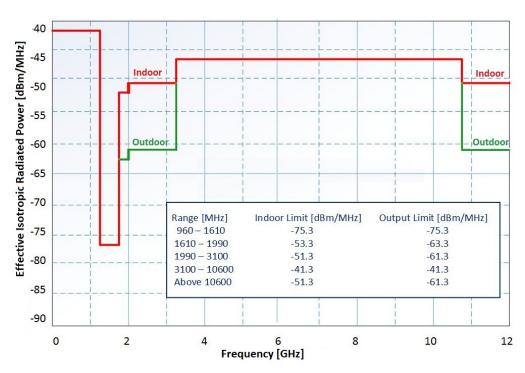

| 2.1  | FCC Mask and its limits (indoor in red color, outdoor in green color)   | 30 |

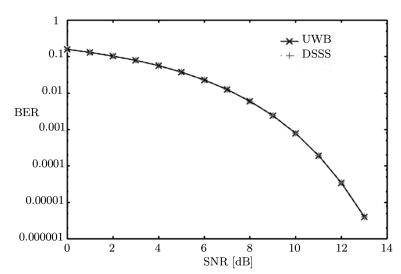

| 2.2  | BER vs. SNR of wideband systems DSSS and UWB for a single user          | 33 |

| 2.3  | Data Rate versus Energy/Battery Lifetime                                | 35 |

| 2.4  | Energy efficiency of various wireless (a) transmitter and (b) receiver  | 36 |

| 2.5  | Hub and Node WBAN Protocol                                              | 38 |

| 2.6  | Design Flow for the Logic Synthesis                                     | 45 |

| 2.7  | Physical Synthesis Flow of the Design                                   | 47 |

| 3.1  | Example of spread spectrum on the IR-UWB                                | 53 |

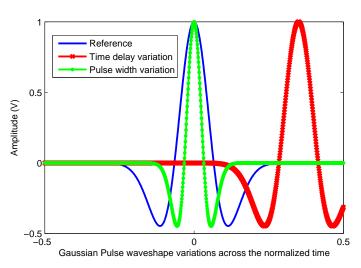

| 3.2  | Gaussian pulse with variations                                          | 54 |

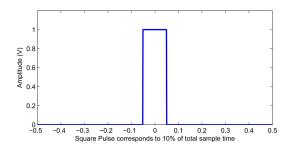

| 3.3  | plots of square wave and its spectrum                                   | 55 |

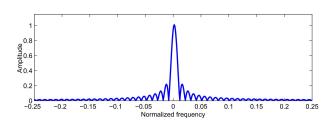

| 3.4  | PSWF variations in time and their respective PSD squares in frequency   | 56 |

| 3.5  | A PSWF pulse over time                                                  | 56 |

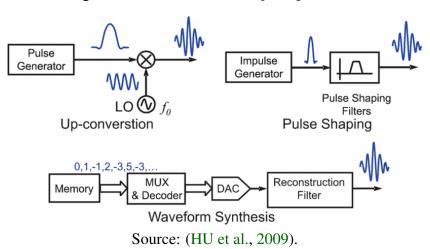

| 3.6  | Some methods for pulse generation                                       | 60 |

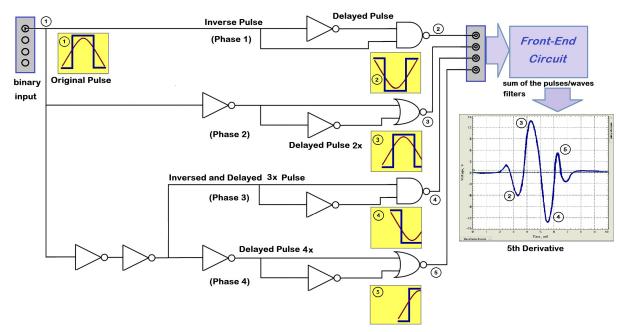

| 3.7  | Circuit schematic for 5th derivative of Gaussian pulse                  | 61 |

| 3.8  | Schematic diagram for one PSWF pulse generators                         | 61 |

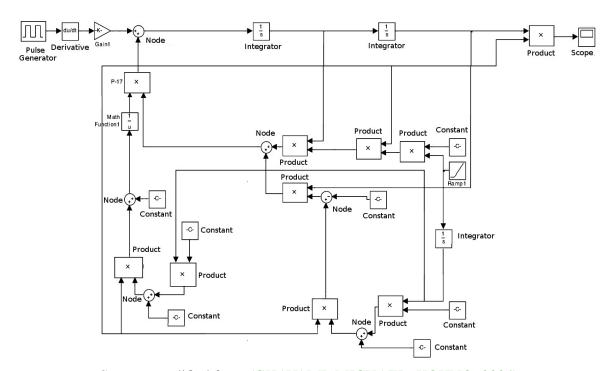

| 3.9  | Comparison of the spectral efficiency of the pulses                     | 64 |

| 3.10 | Energy spent to transmit the 255 bytes,                                 | 64 |

| 4.1  | Cross-Layer Figure Model with General Energy Manager                    | 70 |

| 4.2  | FEC's Encoder and Decoder in the Transceiver (IEEE, 2012)               | 71 |

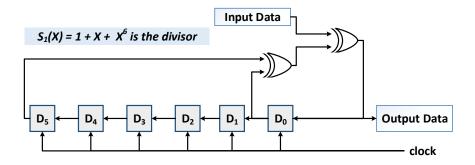

| 4.3  | Encoder for BCH (63,51,2)                                               | 73 |

| 4.4  | Example of decoder block diagram for BCH                                | 74 |

| 4.5  | Berlekamp-Massey Algorithm with inversion                               | 75 |

| 4.6  | Polynomial divisor                                                      | 75 |

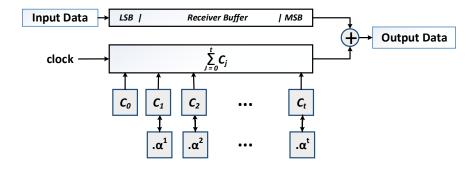

| 4.7  | Chien's search circuit                                                  | 76 |

| 4.8  | Parity check matrix constructed using the CPA approach (HAN, 2007)      | 77 |

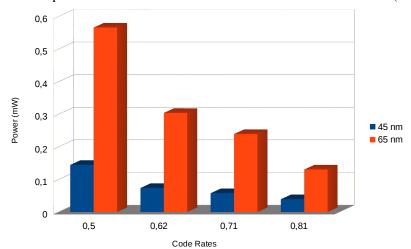

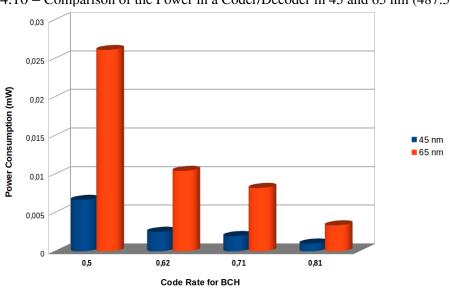

| 4.9  | Comparison of the Power in a Coder/Decoder in 45 and 65 nm (100MBps).   | 81 |

| 4.10 | Comparison of the Power in a Coder/Decoder in 45 and 65 nm (487.5Kbps). | 81 |

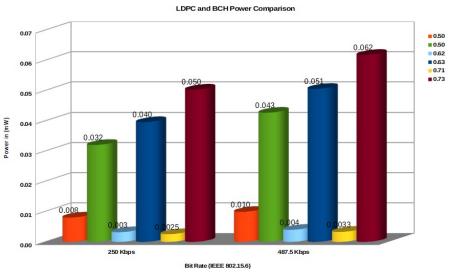

| 4.11 | Comparison of FECs (at 250 and 487.5 Kbps)                              | 82 |

| 5.1  | General Hardware Architecture of a sensor node                          | 85 |

| 5.2  | Block Diagram Example of a Transmitter                                  | 85 |

| 5.3  | Channel Decoding Block                                                      | 37  |

|------|-----------------------------------------------------------------------------|-----|

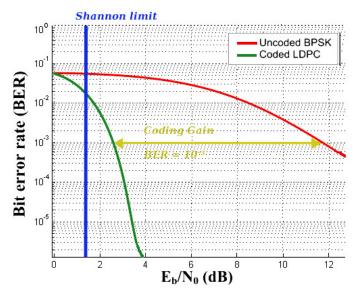

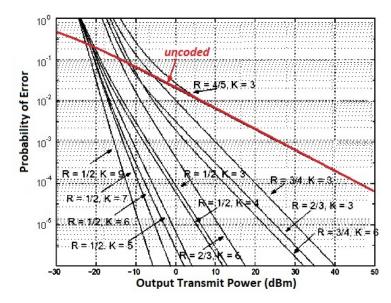

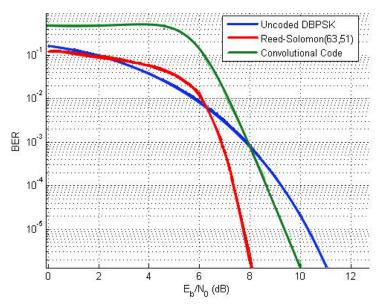

| 5.4  | Bit error rate comparison between uncoded and encoded systems 8             | 88  |

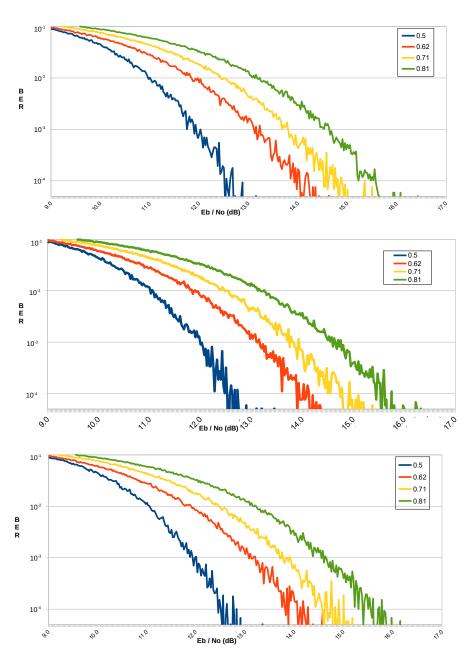

| 5.5  | Error Probability for Uncoded and Code Rate variations                      | 39  |

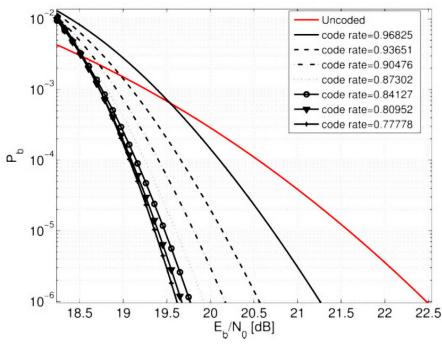

| 5.6  | Bit Error Probability versus Eb/N0 at the receiver                          | 90  |

| 5.7  | Data Structure over MAC level and PHY layer                                 | 91  |

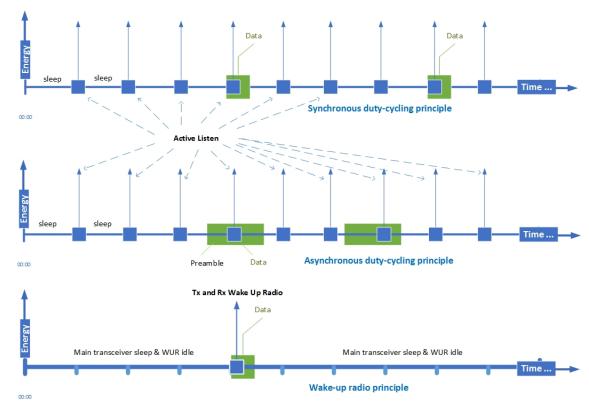

| 5.8  | Comparison between three forms of radio operation and duty-cycling 9        | 94  |

| 5.9  | Type II HARQ - block diagram                                                | 95  |

| 5.10 | FEC mechanisms versus SNR for WBAN specification                            | )() |

| 5.11 | Simulation results with a SNR variable                                      | )1  |

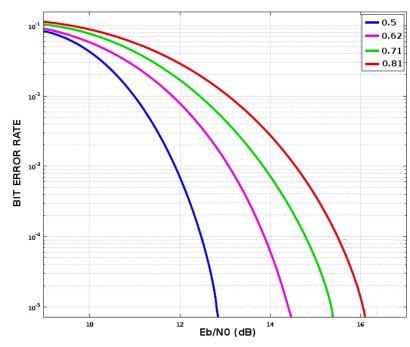

| 5.12 | BCH Code Rates for AWGN Channel (BER vs. $E_B/N_0$ )                        | )2  |

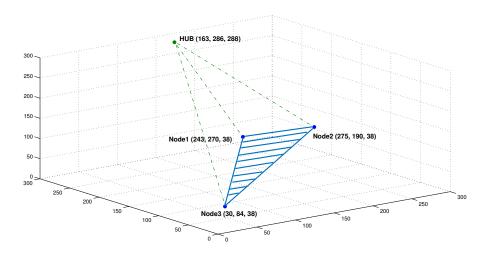

| 5.13 | Hub to a plane composed of three nodes, example                             | )3  |

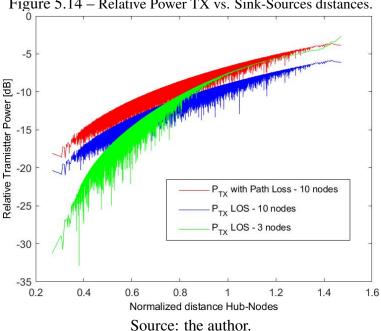

| 5.14 | Relative Power TX vs. Sink-Sources distances                                | )5  |

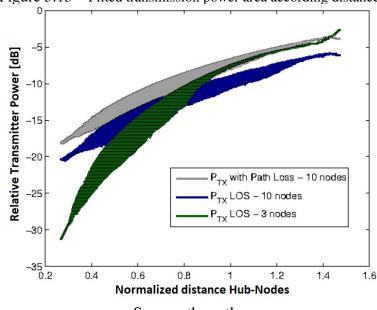

| 5.15 | Fitted transmission power area according distances                          | )6  |

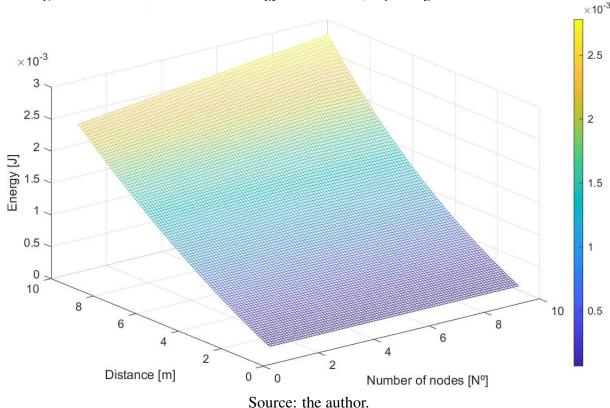

| 5.16 | Variation of the link energy in the WBAN, depending on the distance and     |     |

|      | nodes                                                                       | 17  |

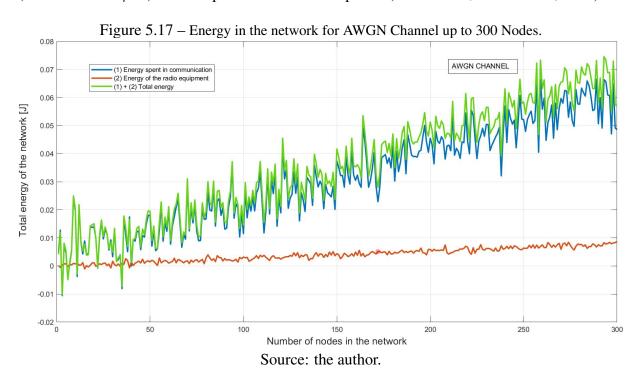

| 5.17 | Energy in the network for AWGN Channel up to 300 Nodes                      | 20  |

| 1    | MAC Frame Format for WBAN                                                   | 38  |

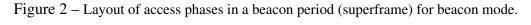

| 2    | Layout of access phases in a beacon period (superframe) for beacon mode. 13 | 38  |

| 3    | MB-OFDM Bands distribution                                                  | 12  |

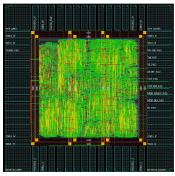

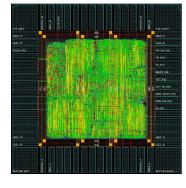

| 4    | Initial Setup; Floorplanning; and Powerplanning                             | 13  |

| 5    | Roating; Verification Stage; and Final IC                                   | 13  |

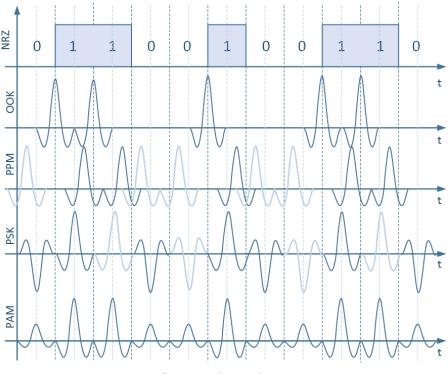

| 6    | Modulation Types for a Binary Example                                       | 14  |

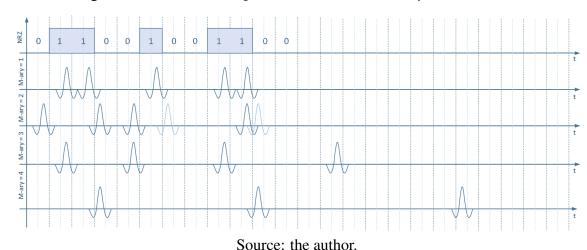

| 7    | Modulation using codification PPM with M-ary, M from 1 to 4 14              | 15  |

|      |                                                                             |     |

## **LIST OF TABLES**

| 2.1  | Time Hopping Spread Spectrum and IR-UWB Characteristics           |

|------|-------------------------------------------------------------------|

| 2.2  | Characteristics of UWB systems                                    |

| 2.3  | UWB operating frequency bands                                     |

| 2.4  | User Priority in WBAN                                             |

| 2.5  | Power Consumption in a BLE receiver front-end components          |

| 2.6  | Power Consumption of a BLE Transceiver                            |

| 2.7  | Key Parameters for an IR-UWB WBAN system                          |

| 2.8  | TX Power consumption overview                                     |

| 2.9  | IR-UWB WBAN specifications                                        |

| 3.1  | The first five derivatives of Gaussian pulse                      |

| 3.2  | Pulses and communication parameters                               |

| 4.1  | BCH code rates                                                    |

| 4.2  | WBAN Stream Parameters                                            |

| 4.3  | QC-LDPC Codes                                                     |

| 4.4  | Area and Power Comparison for Low Data Rates                      |

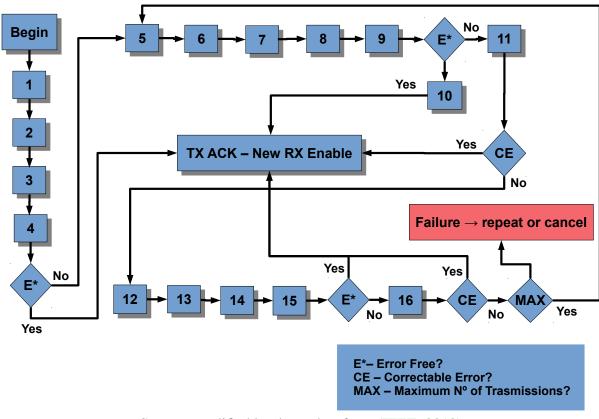

| 5.1  | Type II HARQ, Flowchart Description                               |

| 5.2  | Hardware Power Consumption per Code Rate                          |

| 5.3  | Simulation Parameters to model the Power in the Receiver          |

| 5.4  | Performance summary of UWB chipsets                               |

| 5.5  | Roadmap of the Wireless Integrated Circuits and Systems Group 107 |

| 5.6  | Performance summary of IR-UWB (Tx/Rx)                             |

| 5.7  | Performance of the IR-UWB (7 <sup>th</sup> Derivative)            |

| 5.8  | Performance summary of FM-UWB (Tx/Rx)                             |

| 5.9  | Performance and Comparison of References                          |

| 5.10 | A Summary of the Energy from the Previous Tables                  |

| 5.11 | Characteristics of off-the-shelf ICs                              |

| 5.12 | Interesting Power and Energy values                               |

| 5.13 | Simulation parameters                                             |

| 5.14 | Simulation parameters for the model                               |

| 1    | A.1 - Estimated number of bits in the packets                     |

| 2    | Positioning to convert in pulses over time                        |

## **NOMENCLATURE**

| (P.T)               | $\frac{1}{2}$ Power multiplying the setup time in the receiver |

|---------------------|----------------------------------------------------------------|

| (P.T)               | setup,TX Power multiplying the setup time in the transmitter   |

| $\alpha_i$          | The node switching activity factor                             |

| $\beta_i$           | Input signal time and short circuit factor                     |

| $\chi_n$            | The eigenvalue the PSWF function                               |

| δ                   | Complementary percentage value of $\phi$                       |

| $\epsilon_{add}$    | Addiction operation energy consumption                         |

| $\epsilon_{enc/de}$ | c Energy consumption of encoding/decoding                      |

| $\epsilon_{inv}$    | Inverse operation energy consumption                           |

| $\epsilon_{mult}$   | Multiplication operation energy consumption                    |

| $\eta$              | Power efficiency                                               |

| λ                   | Free space wavelength                                          |

| $\lambda_n$         | Power effectiveness of the pulse                               |

| Ω                   | Bandwidth                                                      |

| $\omega_c$          | Column weight                                                  |

| $\omega_r$          | Row weight                                                     |

| $\phi$              | The percentage of encoder or decoder in the whole circuit      |

| $\psi_n(t)$         | PSWF function                                                  |

| $\sigma(x)$         | Error-location polynomial                                      |

| $\sigma$            | Standard of the normal function                                |

| $\sigma^2$          | Power spectrum energy                                          |

| $\sigma^2$          | Variance parameter of the pulse                                |

Delay since the reference

$au_0$

- $\xi$  Modulation parameter rate

- $\xi$  Ratio of the Rx/Tx mean time spent

- a Amplitude of the signal

- B Bits in preamble or in data

- b Bits per symbol

- BW The bandwidth

- C LDPC code

- c A constant

- c A valid codeword

- C(t) Channel capacity

- c(x) Transmitted message

- $C_{L_i}$  Node load capacitance

- d Distance

- E Energy

- e(x) Probabilistic error

- $e_0$ ;  $e_1$  Electric fields

- $E_T^{TX}$  Minimum threshold for communication

- $e_{amp}$  Energy consumption of the power amplifier

- $E_{PL}$  Losses due the communication link

- $E_{RX}^{Com}$  Receiver energy spent on the communication

- $E_{RX}^{hw}$  Energy due to remaining hardware except for encoder or decoder

- $E_{RX}^{i,Proc}$  Receiver energy spent in digital processing

- $E_{TX}^{j,Com}$  Transmitter energy spent on the communication

- $E_{TX}^{Proc}$  Transmitter energy spent in digital processing

- ${\cal E}_T^{Com}$  Total energy from the communication

$E_T^{Proc}$  Total energy of the processing circuit

erfc(x) Complementary error function

*f* Frequency

$F_{op}$  Operating frequency

g(t) Generator polynomial

$G_d$  Power gain factor

$g_r$  Receiver gain

$g_t$  Transmitter gain

$h_r$  Receiver height

$h_t$  Transmitter height

k Original message length

L Packet length

$LLR(c_i)$  Log-likehood ratio

M Cardinality of the constellation

M Modulation parameter

m Mean of the normal function

m Number of bits in the message

$n \times m$  Codeword length vs. a set of parity equations

n Encoded message length

$N_f$  Receiver noise figure

$N_{CW}$  Number of codewords

$N_{pad}$  Pad bits number

$N_{PSDU}$  Number of bits in PSDU packet

$N_{tx,i}$  Number of transmissions required for success in communication

P Power

$P_b$  Probability bit error

$P_c$  Circuit power consumption

$P_{rx}$  Receiver power consumption

$P_{syn}$  Frequency synthesizer power consumption

$P_{tx,circ}$  Circuit power consumption of the transmitter

$P_{tx,RF}^{i}$  RF power consumption of the transmitter

Pr Probability

Ratio between codeword lenght and additional parity bits

r(x) Received message

$S_T^{RX}$  Sensitivity level of the receiver

SNR Signal-to-Noise in dB

T Pulse duration for PSWF

t Time

$T_p$  Pulse duration

$T_s$  Smapling time between pulses

$T_{ACKW}$  Wait time for a acknowledge message

$T_{on}$  Transceiver on time

$T^i_{packet}\,$  Transmitted frame duration

$T_{tr}$  Frequency synthesizer setting time

W Bandwidth

$x_0$  Initial point of the normal function

c Speed of the light

*k* Number of bits in a packet

t Correction capacity of FEC decoder

**H** Edge between variable and check nodes

y Received codeword at the decoder input

## LIST OF ABBREVIATIONS AND ACRONYMS

ADC Analog-to-digital converters

AWGN Additive White Gaussian Noise

ASIC Application-Specific Integrated Circuit

APP "a posteriori" probability

BCH Bose, Chaudhuri, and Hocquenghen codes

BEP Bit Error Probability

BER Bit Error Rate

BP Belief Propagation

BPSK Binary Phase Shift Keying

CAP Contention Access Phase

CMOS Complementary Metal-Oxide Semiconductor

CNs Check Nodes

CPA *Circulant permutation array*

CTS Clock Tree Synthesis

CSMA Carrier Sensing Multiple Access

DBPSK Differential Binary Phase-Shift Keying

DCA Digital-to-analog converters

DQPSK Differential Quadrature Phase-Shift Keying

DSE Design Space Exploration

EAP Phases-exclusive Access phase

Eeff Energy Efficiency

Eeff-M Energy Efficiency Model

ECC Error Control Coding

ECG Electrocardiogram

EEG Electoencephalogram

EIRP Effective Isotropically Radiated Power

FCC Federal Communications Commission

FCS Frame Check Sequence

FE Front-End

FEC Forward Error Correction

FFT Fast Fourier Transform

FIR Finite Impulse Response Filter

FM-UWB Frequency Modulated Ultra Wideband

FSK Frequency Shift Keying

GEM General Energy Manager

GDSII Graphic Design System II

HARQ Hybrid Automatic Repeat reQuest

HBC Human Body Communications

IC(s) *Integrated Circuit(s)*

IEEE Institute of Electrical and Electronics Engineers

IoT Internet of Things

IP Intellectual Property

IR-UWB Impulse Radio for Ultra Wideband

ISM Industrial, Scientific, and Medical

ISO International Organization for Standardization

ITRS International Technology Roadmap for Semiconductors

ITU International Telecommunications Union

LEC Logic Equivalence Checking

LDPC Low Density Parity-Check Codes

LLC Logical Link Control

LOS Line of Sight

MAC Medium Access Control

MAP Managed Access Phase

MB-OFDM Multi-band OFDM

MICS Medical Implant Communication Service

MPDU MAC Protocol Data Unit

MSDU MAC Service Data Unit

M2M Machine to Machine

MSA Min-Sum Algorithm

NB Narrowband

NLOS Non-Line of Sight

PHY Physical Layer

PLPC Physical Layer Convergence Protocol

PLL Phase Locked Loop

PPDU Physical Protocol Data Unit

PPM Pulse Position Modulation

PRF Pulse repetition frequency

PSD Power Spectral Density

PSDU Physical Service Data Unit

PSWF Prolate Spheroidal Wave Function(s)

OFDM Orthogonal Frequency Division Multiplexing

OOK On-Off Keying (modulation)

OSI Open System Interconnection

QoS Quality of Service

QPSK Quadrature Phase-Shift Keying

RAP Random Access Phase

RC Resistance and Capacitance

RF Radio Frequency

RFID Radio Frequency Identification

RS Reed-Solomon Code

RTL Register Transfer Level

RX/Rx Reception or Receiver

SAP Service Access Point

SDC Synopsys Design Constraints

SDF Standard Delay Format

SINR Signal to Interference Plus Noise Ratio

SNR Signal to Noise Ratio

SPA sum-product algorithm

SoC System on a Chip

TCL Tool Command Language

TX/Tx Transmission or Transmitter

TOA Time of Arrival

UWB Ultra Wideband

VHDL VHSIC Hardware Description Language

VNs Variable Nodes

VHSIC Very High Speed Integrated Circuit

VLSI very large-scale integration

WBAN Wireless Body Area Network

WET Wireless Energy Transfer

WMTS Wireless Medical Telemetry Services

WSN Wireless Sensor Networks

WUR Wake-up Radio

## **CONTENTS**

| 1 II  | NTRODUCTION                                                         | 20 |

|-------|---------------------------------------------------------------------|----|

| 1.1   | Motivation                                                          | 21 |

| 1.2   | Objectives                                                          | 24 |

| 1.3   | Relevant Issues and Contributions                                   | 25 |

| 1.4   | Thesis Organization - Outline                                       | 26 |

| 2 C   | CONTEXTUALIZATION AND THE STATE OF ART                              | 27 |

| 2.1   | IR-UWB Communication                                                | 28 |

| 2.1.1 | UWB regulation                                                      | 29 |

| 2.1.2 | IR-UWB spectral management                                          | 31 |

| 2.1.3 | UWB PHY Specifications                                              | 33 |

| 2.2   | Standard Overview (IEEE Std 802.15.6)                               | 36 |

| 2.2.1 | Data Communication in UWB                                           | 38 |

| 2.2.2 | Comparison of the Power in Transceivers for Data Communication      | 39 |

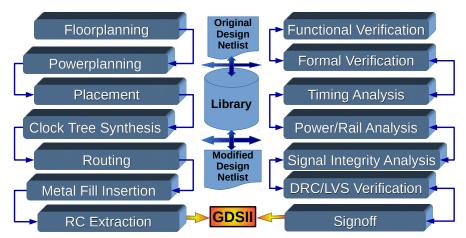

| 2.3   | Digital Integrated Circuit Design based on Standard-Cells           | 40 |

| 2.3.1 | Some Low-Power Techniques                                           | 41 |

| 2.3.2 | Digital Circuit Design Method: the Standard-cell Approach and Tools | 43 |

| 2.4   | Related Works                                                       | 47 |

| 2.4.1 | Cross-Layer Reference Work                                          | 48 |

| 2.4.2 | BCH Reference Work                                                  | 49 |

| 2.4.3 | A Low-power IR-UWB CMOS Transceiver                                 | 49 |

| 2.4.4 | Initial Specification Summary                                       | 51 |

| 2.5   | Summary                                                             | 51 |

| 3 U   | IWB PULSE SHAPING AND MODULATION                                    | 52 |

| 3.1   | Pulse Shaping                                                       | 52 |

| 3.2   | Pulse Shape Analysis                                                | 56 |

| 3.2.1 | PSWF – Frequency vs. Time Design                                    | 57 |

| 3.2.2 | Pulse Generation Hardware                                           | 59 |

| 3.2.3 | Pulse Reference Values                                              | 62 |

| 3.2.4 | Synchronization Problem                                             | 62 |

| 3.3   | Modulation and Coding Evaluation for Energy Efficiency              | 63 |

| 3.3.1 | Modulation Techniques Comparison                                    | 65 |

| 3.3.2 | Specification Summary (Cont'd)                                      | 65 |

| 3.4   | Summary                                                             | 66 |

| 4          | FORWARD ERROR CORRECTION (FEC) DECODING             | 67  |

|------------|-----------------------------------------------------|-----|

| 4.1        | FEC Review                                          | 67  |

| 4.1.1      | BCH and LDPC Theory                                 | 67  |

| 4.1.2      | FEC Code Performance                                | 68  |

| 4.1.3      | Reconfiguration Process                             | 69  |

| 4.2        | FEC Architectures                                   | 71  |

| 4.2.1      | Forward Error Correcting Codes                      | 72  |

| 4.3        | Power Comparison Ralated to the Modules of the FECs | 80  |

| 4.4        | Complementary Comparison of Hardware Energy         | 81  |

| 4.5        | Summary                                             | 82  |

| _          |                                                     |     |

|            | CROSS-LAYER ENERGY MODELING                         | 83  |

| 5.1        | Communication Aspects of PHY Layer in WBANs         | 83  |

| 5.1.1      |                                                     | 84  |

| <b>5.2</b> | Channel Coding for WBANs                            | 86  |

| 5.2.1      | Energy Impact of the Protocols in MAC Level         | 89  |

| 5.2.2      | Cross-Layer Energy Efficiency Model                 | 92  |

| <b>5.3</b> | Link Budget Influences                              | 99  |

| 5.3.1      | Link for the WBAN (Distance vs. TX/RX Power)        | 102 |

| <b>5.4</b> | Benchmarking and Roadmapping                        | 105 |

| 5.5        | Enhanced Cross-Layer Proposal                       | 111 |

| 5.5.1      | Energy Efficiency Model (PHY Level)                 | 111 |

| <b>5.6</b> | Summary                                             | 122 |

| 6          | CONCLUSIONS AND FUTURE WORK                         | 123 |

|            |                                                     | 123 |

| 6.1.1      |                                                     |     |

| 6.1.2      |                                                     |     |

| 6.1.3      | -                                                   |     |

| 6.2        | Future Works                                        |     |

| <b>U.</b>  | rutte works                                         | 120 |

| REF        | ERENCES                                             | 127 |

#### 1 INTRODUCTION

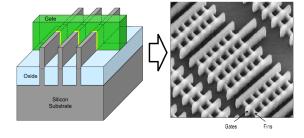

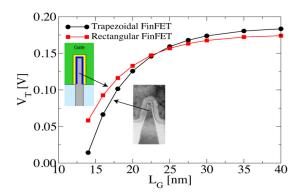

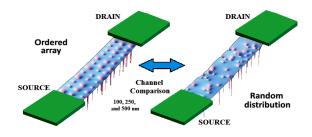

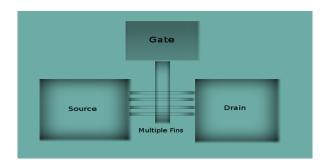

A new stage of technological resources is emerging in the first decades of the  $21^{st}$  century. Big Data and data analytics, new buzzwords that congregate several concepts, have a central role in a system where the information is unfolded over several domains such as Internet-of-Things (IoT), healthcare system integration, data fusion, advanced sensors spread over Smart-Cities or smart physical infrastructures, and so on. All these topics are interconnected in a certain way. Technical advances in microelectronics, in parallel with this macro-context, e.g., three dimensions (3-D) Integrated Circuits (ICs) (VERHELST; DEHAENE, 2009), FinFET transistors below 10 nm sizes, and many others, are available to drive to new information processing ways and to modify key aspects of the power consumption of the most advanced hardware, and ICs in particular. Microelectronics has an essential role in such scenario, developing key components of the devices that allow sensing the available data, gathering information by wireless and wired networks that operate seamlessly, selecting, storing and processing them (GAMBINI et al., 2012). As every single part of the whole system spends very tiny portions of energy, at some moment, the total energy required for this widely distributed system reaches a considerable amount of energy to keep it unceasingly operating. Thus, ultra-low-power hardware components and the respective low-power communication systems are increasingly under demand.

Moreover, humanity always strived for better quality of life. A multidisciplinary work-force becomes every day more active across the academic and industrial world, in some cases improving this effort with government support. Therefore, one of the areas of greatest commitment is the preservation of the human health, an area in which financial resources are heavily spent, where the biomedical systems are inserted. Enabling new, challenging and deep research in engineering, towards modern and smart health-care systems. Recent advances for better biomedical systems are studied today, as addressed in many academic surveys (CHEN et al., 2011), (ULLAH et al., 2012), (MOVASSAGHI et al., 2014).

As a result, the establishment of the standards and amendments by IEEE is synchronized with the current research efforts. The new wireless technologies applied specifically to human interface, medical communication system, and interaction possibilities contribute to stimulate research on several related areas and to exploit new energy efficiency techniques. Based on these IEEE standards, every single work brings contributions for effective deployment of human health care and associated activities. Reduction of the energy consumption can be studied at different levels, starting at the source that generates the information in the human body, up to the information sink - and including all ways and communication channels in which data propagation occurs.

The self-reconfigurable features of the communication system intend an adaptation based on the feedback from the physical communication channel, regarding its energy which impacts the quality of information sent or the demand for better quality of service (QoS). This feedback

signal alerts the transceivers about the needs for changes, which include actions to promote variations on rates, on channel coding schemes, filter adjustments with a selection, all that may change the communication throughput and quality. The self-awareness over RF channel is directed to get the better optimization point with such variations and at some moments to fulfill the immediate needs.

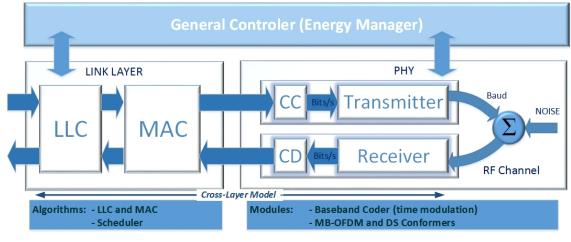

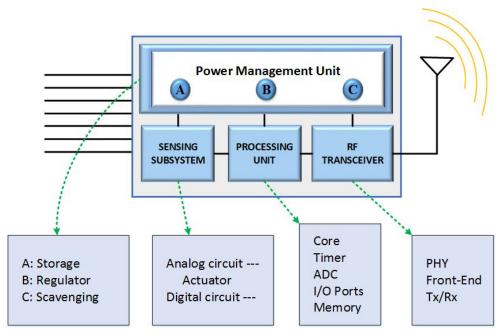

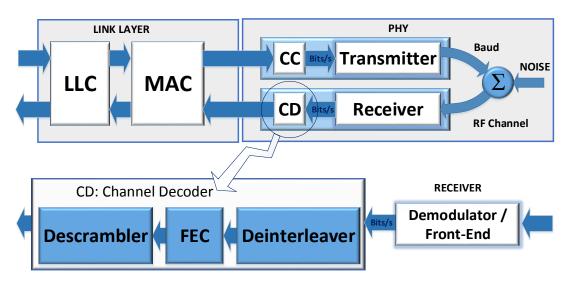

Keeping these aspects in mind, this thesis analyzes the energy efficiency of parts of a communication system that could be used in the biomedical domain. A few energy optimization opportunities are subject of the research. The transceiver block-diagram of Figure 1.1 represents the architecture of the interface between the link and the physical layers. In this research we focus in wireless body area network (WBAN), following the standard 802.15.6 from IEEE (IEEE, 2012). The research is about the PHY layer integrated with the MAC sublayer to exploit the benefits of such a cross-layer model, considering that the applications are in the biomedical field.

Figure 1.1 – Transceiver Block Diagram.

Source: (ROCHOL, 2012), modified by the author.

In Fig 1.1, the following LLC, MAC, CC, and CD blocks stand for, respectively, the Logic Link Control, the Channel Coding, the Medium Access Control, and the Channel Decoding. Particularly, the channel coding and decoding (CC/CD) will be addressed at the logic circuit design level in this thesis, to model its energy efficiency.

## 1.1 Motivation

Currently, energy efficiency is a very relevant topic for many new technologies. Low Power, used internally in the RF circuits, is always pursued and now also has an inflection point characterized by the use of Ultra-Low Power range. The new advances in wireless communication systems combined with the constant evolution and challenges of IC (integrated circuits) design provides the motivation for the topic of this Thesis, in which the IR-UWB system as well as circuit characteristics will be assessed and researched. An example is the level of evolution and of the scalability of the digital CMOS designs, which benefit directly from the geometry scaling that has marked successive CMOS generations over the years. More recently, Low Power CMOS design techniques became a hard-to-miss feature for these designs. Moreover, the

increased demand for digital signal processing integrated into a single chip or using systems-on-a-chip (SoC) have resulted in a great need for new designs and research in applying low power CMOS to communication systems. Even bio-engineering technology has benefited from the low power characteristics of CMOS circuits.

For the energy efficient systems design, it is desirable to develop and to master a model that represents the energy consumption across the first two layers (ISO, 1988) and that translates the impact of any technological microelectronic node into the system. Such model needs parameterization and scalability, and that provides the motivation of this Thesis to tackle energy consumption in different levels of the IR-UWB communication system. A particular application scenario is also needed to feed critical model parameters. For this reason, medical system applications are in the background of the motivation for the global objective of this work. The application of the UWB frequency range and the intermittent nature of the communication, as well as its desired low power, are good properties of the system to be applied in biomedical sensor instrumentation. The high capability of penetration in biological tissues, which allows non-invasive methods, is also advantageous in UWB.

The use of Impulse Radio (IR) can satisfy the necessary efficiency and simplicity by leveraging the use and access of the spectrum, which is the best option under some circumstances, current in use (LECOINTRE; DRAGOMIRESCU; PLANA, 2008). In the IR technique, very short pulses are transmitted spending relatively minimum energy. The IR has an inherent simplicity in the design of the TX, since it is carrier-less. The challenge in this communication system by IR is that the RX has to perform a non-synchronous detection of such short pulses, which presents timing and multi-path effects that have to be dealt with by the RX front-end design. A significant number of academic and industrial investigations on UWB using such technology are known usually by the term IR-UWB (OPPERMANN; HAMALAINEN; IINATTI, 2004). In the years 2000 and onwards, much research was devoted to IR-UWB circuits and systems development. Furthermore, there are several open optimization possibilities in literature, since a simple digital circuit design up to a complex organization of intra-layer blocks, surfacing all the concepts that bring advantages in terms of ultra-low power use.

An example of these advantages may be characterized in a practical case, such as the delayed replacement of pacemakers in patients due the durability extended over the time of their batteries, as a result of the use of energy efficiency circuits. Nevertheless, the application mentioned in this thesis is the WBAN using UWB; the energy model is also intended to be suitable for non-medical areas (*e.g.*, in the military area). Therefore, this wireless sensor network paradigm serves a variety of medical and non-medical applications with the respective adjusts, but only IR-UWB for WBAN is addressed in deep here.

As a case study, Fig. 1.2 shows an example of outdoor application, where the architecture follows a star topology of nodes (devices in the runner and the smartphone), monitoring in real time and directing the information to a medical monitoring center. The devices coupled to the runner include sensors and RF transceivers, which have a convergence point to receive

Figure 1.2 – Example of WBAN's architecture – network for human signal monitoring.

Source: the author.

and coordinate all data (the Hub). The collected information travels through the networks until arriving at the agent that will carry out the analysis - which in this example could be a center of medical monitoring. The remote individual information, such as Oxygenation  $(SpO_2)$ , Electroencephalogram (ECG), Electrocardiogram (EEG), Electromyogram (EMG), and Blood Pressure, are then available to the monitoring center anywhere in the globe.

Resources sharing minimizes or even avoids the traffic overload generated by applications in a complex network such as smart surveillance using the Internet of Things sensors, as shown in (KUNST et al., 2018). To deal with an heterogeneous network scenario (*e.g.*, smart cities and military surveillance such as borderline security) some requirements are essential, for instance, keep the thresholds of delay, interference, and jitter on the communication, QoS of the real-time video application, low overhead control mechanism, cost-benefit of the spectrum allocation, and respect the time constraints for handover operation. Figure 1.3 represents an example.

The IEEE 802.15.6 deals with body area networks or wireless communication for personal networks with the purpose of short-range monitoring and communicating actions to actuators, if and when necessary. This standard regulates mainly the techniques for medical application of the most critical physiologic signals, as a way to get better results to diagnose diseases and alterations. Although not restricted to biomedical applications, in a broader sense it could be seen as a wireless sensor network (WSN). Moreover, WBAN's research is a current topic, either to find reliability, a better energy efficiency during a long time of operation, or even to meet the security requirements. Thus, new concepts can be availed for the purpose of this research. Finally, these bidirectional and interconnected topics bring by themselves more motivational strength.

IoT Devices

Cyber Cloud

Mobile device

Network

Server

Medical Monitoring Center

Figure 1.3 – Network for a Smart City with IoT sensors around.

Source: the author.

## 1.2 Objectives

The establishment of high-level energy models is one of the objectives of this work. This will be done assuming UWB communication for the WBAN. Several aspects are addressed, and these include: i) the effects of the UWB pulse shapes generated at the TX in terms of energy efficiency, as an impulse radio (IR-UWB); ii) the hardware of the FEC decoder analysed at the CMOS logic design abstraction; iii) the evaluation of the Wake-Up Radios (WUR), the interaction between the PHY-MAC protocols, and the Front-End power consumption; iv) the link budget and the assessment over the MAC performance. The two main layers (PHY and MAC) of the cross-layer architecture of the WBAN are addressed for such purpose. Additionally, the peer-to-peer communication made by IR-UWB baseband transceivers in a star topology (IEEE, 2012) is the base to configure the communication system context for a body-area environment.

As the thesis addresses issues of digital communications and links them to microelectronics design, the PHY level of the system is focused. The FEC hardware is where CMOS digital logic design is applied from the FEC algorithm down to the FEC logic netlist, where the correspondent power equations and estimated values can be determined with high precision by the EDA tools. In the application scenario, the thesis considers the energy model of an IR-UWB transmitter. Furthermore, an overview of the algorithms and their protocols for energy efficiency at MAC level are presented in this work as a part of the system, as well as the power consumption that is used at the operation level, necessary for communication and information exchange. A set of energy benchmarks and related works from literature are assessed as references. The final power budget of the whole system is aimed to be achieved with its theoretical and analytical evaluation.

Synthetically, the research questions which comprise the body of the results in this thesis are:

- 1. Determine which waveforms and modulation variations for the UWB transmission have the best performance, analyzing the parameters such as the coding efficiency, payload impact, throughput, and the gain from theoretical prolate spheroidal wave functions (PSWF) usage.

- Investigate the forward error correction block (FEC), working with FEC coding (PHY layer) with VHDL synthesis possibilities to estimate the power for different code types, and FEC parametric variations.

- 3. Verify the energy consumption of the baseband block using data from a synthesis of the VHDL code (checking the usual energy per bit/pulse). The resulting circuits will impact on the global energy consumption model.

- 4. The communication between two transceivers, considering the channel, the link budget, leading to a new Energy Efficiency Model ( $E_{eff}$ -M) for the network.

- 5. Additionally, get the specifications for the energy efficiency model, based on MAC protocols and mainly in the operation duty cycles.

#### 1.3 Relevant Issues and Contributions

The main contribution is to define a new model based on the existing ones (KARVONEN; IINATTI; HÄMÄLÄINEN, 2015), replacing the instruction cycle components by the information of power consumption from the benchmarking and the decoder hardware of the FEC.

The contributions are aligned to the respective objectives, and the microelectronics design aspects are emphasized in the FEC hardware design for low power consumption:

- UWB waveforms and modulation techniques are explored and optimized for energy, contributing to an adjustable level of energy efficiency at both the TX and RX.

- Different implementations of UWB transceiver design are analyzed, with a comparison of their features, mainly the power, IC area, and operational frequency.

- The work is based on the WBAN architecture, thus the UWB transmitter is planned to be suitable to such network and to consider the pros and cons due to the cross-layer interaction.

- The problem formulation is made to improve the model of energy, where an assessment of the best synchronization between nodes and the hub is necessary.

Taking advantage of the technological scale independence of digital design to suit it into microelectronics technological nodes, some designs were exploited such as 180 nm, 65 nm or smaller.

The FEC coding schemes and the IR-UWB perspectives are reviewed. The proposal places the IR-UWB as the core communication system for this kind of network. At this point, the Energy Efficiency Model begins to be modeled toward a cross-layer Approach, considering the MAC and PHY interdependencies. Improvements are investigated in a cross-layer energy

efficiency model for IR-UWB transmitter, applications in WBANs are modeled mainly at the PHY layer as focus, aiming to maximize the energy efficiency. The adaptation of the IR-UWB to the spectrum and environment conditions is necessary for the communication to achieve the best results. Then, the energy evaluation for the system is directed to the hardware design, for the codecs designed in CMOS VLSI, and to the top level analysis.

## 1.4 Thesis Organization - Outline

This thesis is organized as follows: Chapter 2 presents an introduction to Impulse Radio (UWB context and regulation) and an overview of the Standard IEEE 802.15.6, regarding the wireless body area networks. To bridge the text towards those interested only in the data communication field, an introductory text about microelectronics and its design techniques is included in this chapter.

In Chapter 3, at the bottom level of the model, a Pulse Shape Analysis is made, and some digital designs exemplify the PHY layer. Possible energy gains due to specific UWB signal waveforms and time-frequency domains are considered. The circuit of the transmitter is detailed, and the proposed design intend to be compatible with modulation modes and techniques. The concepts and theoretical basis are also placed in this chapter for the IR-UWB.

Forward Error Correction for decoding mechanisms is addressed in Chapter 4, as well as the conceptual review of the forward error correction methods for BCH and LDPC. Both FEC algorithms are considered in this chapter, two different FEC designs are addressed, and a power comparison among these designs are presented.

The convergence of results is presented in Chapter 5, highlighting the link budget influences, Communication aspects of PHY Layer and Channel Coding for WBANs, such as the power values from the benchmarking and the cross-layer energy protocols (some MAC layer procedures are addressed). At this point, the improvements on the energy model are presented, highlighting the impact on energy efficiency.

Finally, Chapter 6 presents the conclusions of this Thesis and lists possible future works.

#### 2 CONTEXTUALIZATION AND THE STATE OF ART

The Work Group of IEEE to standardization of WBANs published the IEEE 802.15.6 (IEEE, 2012) in February 2012. The purpose was to regulate networks where low-power devices are their components, a WSN of short-range applied at human body area, taking signals to a single hub – which is, in other words, the coordinator or the sink of a network with several nodes. This chapter presents a quick overview of some aspects of this standard, as a way to view the problem addressed in this thesis.

The IEEE 802.15.6 Standard gives the possibility to choose between Narrowband (NB), Ultra Wideband (UWB), and Human Body Communications (HBC) as the PHY layer to be used in the WBAN. They are used to proceed with communication and determine how the access mechanism will work. The author chose the scope of this research to be the UWB, where the microwave frequencies are employed with ultra-fast pulses, which lie in a range from 3.1 GHz up to 10.6 GHz. The properties of these pulses can be exploited for the proposed IR transmitter design. This spectrum has as one of its advantages the possibilities of use in other applications, not limited to the human body scan. The UWB was considered since in the first decade of the years 2000 it was proposed as a better choice to deliver Industrial, Scientific, and Medical (ISM) signals. It has a complete set of work experiences of more than one decade. There is a scenario favorable to merge and to consolidate knowledge on UWB in the present (ULLAH et al., 2012). Other commercial technologies evolved over the years to compete for short-range communications, all based on narrow band communications, like Bluetooth Low-energy (BLE) and ZigBee, which today have a more significant impact in real world applications than the proposed 802.15.6 in an UWB PHY.

Some potential pros and cons of UWB for communication are:

- IR-UWB has simple implementation when compared with another types of radio hardware, specially at the RF front-ends.

- UWB has a considerable Multipath resistance, but it is susceptible to interference.

- UWB is considered by some as ideal for short-range communications, although such claim has not led to the rise of UWB communications over the more consumer-market penetration experienced by Bluetooth and 802.11.nn WiFi, for example.

- The pulsed natured of the UWB TX/RX can achieve both high and low (for power savings) data rates, i.e. throughput is easily adjustable.

- The duty cycle nature of IR-UWB can cause synchronization issues, but it is easy to handle.

- By using UWB hardware, its simplicity will imply a more simplified RF front-end, and subsequent signal processing, and with the consequent reduction in the energy consumption.

Good examples of applications using UWB are given in the literature, and include automotive guidance radar, RF Identification (RFID), penetration radar imaging, telemetry and location devices, surveillance and guidance systems, targeting tracking, and particularly others used in the military context. Some other examples of ISM usage of UWB are exemplified by satellite

communications, as global navigation (ANTREICH; NOSSEK, 2011), radar systems based on UWB signals, soldiers locations in campaign arranging and maneuver, among others (GAM-BINI et al., 2012).

Specifically, the concerns of this research converge for the use of IR-UWB over a WBAN context. In medical applications, the collection of biological signals and all of their data through monitoring devices allows viewing and controlling user conditions in specific scenarios. The networks dealing with biomedical signaling of the human health conditions will be increasingly present also outside hospitals facilities. Thus, the human-machine interface or even Machine-to-Machine (M2M) interfaces tend to be always used in the next generation of operational designs.

As a specific case of WSN, the WBAN scenarios follow a star topology, distributing the elements from an initial network configuration to slaves nodes through the master node (hub or the coordinator). The correct coordination exchanging messages on the communication system keeps it running. Thus, between the hub and nodes direct frame exchanges occur, and, eventually, a relay-capable node can be added. Thus another level of communication can work and enlarging the network extension becomes possible using this two-hop star WBAN topology. As mentioned before, in the global model of the IR-UWB baseband transmitter this work focus on two layers: PHY layer, and the MAC sub-layer (of the Link Layer). And both are addressed in a Cross-Layer model. For that reason, the required MAC definitions will follow IEEE 802.15.6.

Remarkably, there are other standards that can be used as references in addition to IEEE 802.15.6, for instance: IEEE 802.15.4j TM-2013 – an alternative physical layer extension to support medical body area network (MBAN) Services operating in the 2,360 MHz – 2,400 MHz band and IEEE 802.15.4k – physical layer specifications for low energy, critical infrastructure monitoring (LECIM) networks. Summaries of these WBAN standards exist in some works of the literature, *e.g.*, (BARRAS, 2010).

The specification for low data-rate, low consumption, and very low hardware and architecture complexities was placed by IEEE 802.15.4 standards, developed for Wireless Sensor Networks. It is a low-power version of IEEE 802.11 for WLANs and the precursor of IEEE 802.15.6. There are also other sets of frequencies for biomedical engineering applications, *e.g.*, with a range of 402-405 MHz used for implants in the medical implant communication service (MICS). Therefore, these standards represent opportunities to be exploited in this field.

## 2.1 IR-UWB Communication

UWB radio frequencies are spread over the 7.5 GHz bandwidth, ranging from 3.1 GHz to 10.6 GHz. UWB has been considered since the early 2000's as one of the most useful choices for short-range communications. By consequence, the ultra-low power transceiver designs for UWB is a current topic in scientific studies, where shaping the pulses of sub-nanosecond duration is a challenging circuit design task. Impulse radio for UWB (IR-UWB) transmission is carrier-less and has human body permeability as one of its properties, which makes it attractive

in terms of energy consumption, versatility, and potential for a short-range application. It demands low-power and simple hardware implementations while imposing a fine time resolution achievable in advanced complementary metal oxide semiconductor (CMOS) integrated circuits.

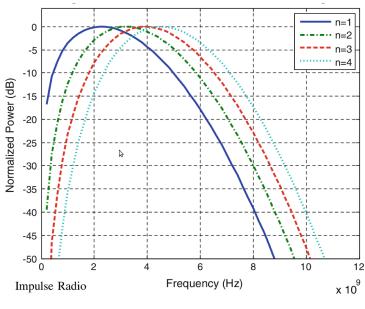

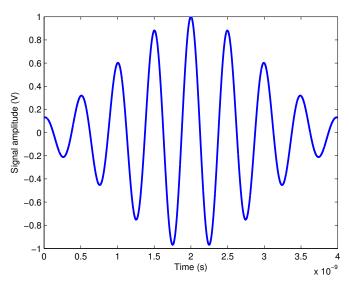

Ensuring low-power consumption in IR-UWB is of paramount importance in current technology (GHASEMPOUR et al., 2012). Improved energy efficiency ( $E_{eff}$ ) is attainable with a transmitter design which allows transmission parameters to self-reconfigure (OTT; EISNER; EIBERT, 2012). Traditional setups of such parameters use Gaussian- and square-like pulses. Throughout this work, the waveforms exploration is extended by the use of Prolate Spheroidal wave functions (PSWFs) (NEVES et al., 2012), (SLEPIAN; POLLAK, 1961), in addition to the former ones. The block that produces PSWFs is typically linked to the modulation block in the transmitter, where the modulation techniques, e.g., pulse position modulation (PPM), on-off keying (OOK), or binary phase shift keying (BPSK), also aiming to improve energy savings (NIEMELA; HÄMÄLÄINEN; IINATTI, 2013).

Therefore, the IR-UWB analysis will evaluate three basic classes of waveform implementations: (I) Gaussian pulse and its derivatives, (II) PSWFs function/formats, and (III) square pulse. The comparison metric will be the impact caused by each class of waveform on the  $E_{eff}$  of the IR-UWB system. As mentioned before, implementations of this UWB system are in satellite communications, such as global navigation, radar systems, medical imaging, embedded in vehicles, surveillance and monitoring areas, radio frequency identification (RFID), sports medicine, among others (GAMBINI et al., 2012).

The energy concepts used for wireless body area networks (WBAN) communications are extendable to correlated wireless communication systems, such as wireless sensor networks and electronic vests to monitor physiological activities, for example, electrocardiogram (ECG) (CHÉTELAT et al., 2016). Applications of IR-UWB in the context of WBAN, specified in the standard IEEE 802.15.6 (IEEE, 2012), deal with 250 Kbps or 487.5 Kbps, as is the case of e-health systems that are used to monitor human conditions by their biological and behavioral signals. Are essential to keep both values in mind for the simulations described in some of the chapters ahead.

## 2.1.1 UWB regulation

The regulations of the USA Federal Communications Commission (FCC, 2002) and by the European Association for standardizing information and communication systems (ECMA organization), which issued the standards (ECMA, 2008a) and (ECMA, 2008b), are essential references for this subject. FCC standardization provides a spectrum mask for UWB channels and ECMA deals with High Rate Ultra Wideband PHY and MAC Standard including its interface. How to perform the most efficient integration among OSI layers is an issue left to the actual system implementation. The understanding of RF transmitter blocks contributes to such purpose. A large number of documents dealing with UWB brings the masked figure determined

by the (FCC, 2002). It is limited in dBm per MHz with the corresponding variation for each frequency. Figure 2.1 shows the limits of this mask, both indoor and outdoor. In most of the mask, Indoor overlaps the outdoor, indicating that the effective isotropic radiated power is the same for both.

Figure 2.1 – FCC Mask and its limits (indoor in red color, outdoor in green color)

Source: (FCC, 2002), modified by the author.

The development of the circuits, as mentioned in (WENTZLOFF, 2007), should then focus on the energy efficient aspects. The advantages need to be evaluated in terms of energy consumption from the several IR-UWB implementations existing in the literature, thus new constraints can bring new opportunities, an example of the recent 5G boundaries at 5.25 or 6 GHz are inside UWB range, invalidating some implementations whereas open issues in IR-UWB still exist to solve problems like interference and co-working.

On the other hand, differently from the FCC, the mask provided by the European ECC regulation is located at two separate bands, which have operating frequencies in 3.1-4.8 GHz and 6-8.5 GHz. ECMA originally stood for "European Computer Manufacturers Association" and is now seen as an international body (BARRAS, 2010). In 2005, ECMA released two proposals for high-speed UWB standardization.

The ECMA-368 standard (ECMA, 2008a), entitled "High Rate Ultra Wideband PHY and MAC Standard" was approved as ISO/IEC 26907 International Standard in March 2007, specifying a distributed medium access control (MAC) sublayer and a physical layer (PHY) for wireless networks, compatible to high data rate communications between a diverse set of mobile and fixed electronic devices. It was followed by the ECMA-369 standard - "MAC-PHY Interface for ECMA-368" (ECMA, 2008b), later approved as ISO/IEC 26908 and specified

the MAC-PHY interface for a high rate for ultra-wideband wireless transceiver. The European Telecommunications Standards Institute (ETSI, 2015) also uses two bands (from 3.1 GHz to 4.8 GHz, and from 6.0 GHz to 8.5 GHz), which differs from the FCC specification. The International Telecommunication Union - Radiocommunication Sector (ITU-R) (SECTION, 2015) is another body involved in these regulations.

## 2.1.2 IR-UWB spectral management

The short-range wireless communication collaboratively working in an *ad hoc* sensor network is a promising technology. A way to implement that is using, in the PHY layer, the IR-UWB or another IR technique, like the Multi-band Orthogonal Frequency Division Multiplexing (MB-OFDM), as shown in Appendix "D". Where the spectrum is divided into up to 14 separated bands with a range of 528 MHz each. Meanwhile, UWB can be defined as a direct to antenna transmission, for which the emitted signal bandwidth (BW) is around 500 MHz (the signal bandwidth defined for a -10 dB reduction with respect to the peak in its power spectrum density) or for signals of 20% of fractional bandwidth (SECTION, 2015) and (ETSI, 2015), which is the -10 dB BW divided by the band central frequency. Also, UWB is associated with radio equipments employing signals with a bandwidth higher than 1.5GHz or, as an alternative, whose signals have a -10 dB intensity range spread over at least 25% of the spectrum.

The spread-spectrum due the IR-UWB has its bandwidth located from 3.1 GHz up to 10.6 GHz, reflecting a major challenge to generate at the TX antenna ultra-fast pulses of sub-nanosecond duration, in a sequence as in Equation 2.1. This transmission mode has other features which make it attractive in terms of energy, versatility, and potential use. For instance, the IR-UWB does not use a carrier, the transmission can employ low power, simple hardware (without an RF mixer), and has a very low time resolution. The digital modulations in this context can be OOK (on-off keying) or PPM (pulse position modulation), considered later in this study.

$$UWB_{signal}(t) = \sum_{-\infty}^{\infty} amplitude.signal_{waveform}(time - delays)$$

(2.1)

A summary of techniques for UWB signals is as follows. The IR-UWB can be divided into two different multiple access techniques, the Direct Sequence Ultra-Wideband (DS-UWB) and the Time Hopping ultra-wideband (TH-UWB). In MB-OFDM the spectrum has sub-bands of the bandwidth of 528MHz each (ECMA-369). The Orthogonal Frequency Division Multiplexing (OFDM) technique is used in both Spread Spectrum Direct Sequence Spread Spectrum (DSSS) and Time Hopping Spread Spectrum (THSS), and they are generated by continuous sinusoidal waves modulated with a fixed carrier frequency. Otherwise, the DS-UWB and TH-UWB are typically baseband signals and are composed by narrow UWB pulses. For standard purposes, the DS-UWB (the shaded row) is the main interest for the WBAN design, with bandwidths set at 499.2 MHz. Some characteristics of such signals are summarized in Tables 2.1

## and 2.2.

Table 2.1 – Time Hopping Spread Spectrum and IR-UWB Characteristics.

|                                                 | Type   | Characteristics                          | Bandwidth        |

|-------------------------------------------------|--------|------------------------------------------|------------------|

| Spread Spectrum DSSS Sinusoidal continuous wave |        | Sinusoidal continuous waves are          | >= 500MHz        |

|                                                 | THSS   | modulated with a fixed carried frequency |                  |

| IR-UWB DS-UWB                                   |        | Baseband signals                         | < 500MHz         |

|                                                 | TH-UWB | and narrow UWB pulses                    | (typ. 499.2 MHz) |

| Similarities 1) Advantageous use of a very large bandwidth. |                                                        |  |  |

|-------------------------------------------------------------|--------------------------------------------------------|--|--|

|                                                             | 2) Avoid effects of interference from signals sources. |  |  |

Source: (HERINGER, 2007), complemented by the author.

Table 2.2 – Characteristics of UWB systems.

| Specifications        | MB-OFDM                  | IR (DS-UWB)                   |

|-----------------------|--------------------------|-------------------------------|

| Number of Sub-bands   | 3 mandatory up to 14     | 2 (3.1 – 4.85; 6.2 – 9.7) GHz |

| Sub-band Bandwidth    | 528 MHz                  | 1.75 GHz (lower band)         |

| Number of Sub-carries | 122                      | Baseband Signals              |

| Spreading Factor      | 1, 2                     | 1-24                          |

| Data rates (Mbps)     | 53.3, 80, 110, 160       | 28, 55, 110, 220              |

|                       | 200, 320, 480            | 500, 660, 1000, 1320          |

| Modulation            | QPSK                     | BPM (mandatory), MBOK         |

| Multiple Access       | Based on time-freq codes | Based on PN codes             |

Source: adapted from (HERINGER, 2007).

Fig. 2.2 shows the trend of the bit error-rate (BER) in the transmission according to the channel quality (i.e. the signal-to-noise ratio - SNR at the RX), which indicates the behavior of the wideband system for two modulation techniques presented in the Table 2.1 (DS-UWB and DSSS). The trend in the figure is for a single user. For multiple users, the UWB tends to keep the same behavior, and the DSSS presents improvements in terms of error overruns. The SNR can be translated further in terms of the necessary energy to be coupled at the TX antenna to proceed with a given BER in the communication.

The European Commission (EC) through the European Technical Standards Institute (ETSI) deals with -41.3 dBm/MHz in the frequency bands 4.2 to 4.8 GHz and 6.0 to 8.5 GHz. Extendable at the lower frequencies to 3.1 GHz and also up to 9 GHz in the higher band. Singapore, for instance, to stimulate the study and development of UWB usage, established an UWB friendly zone, allowing the relaxation of the effective isotropic radiated power limit of -35.3dBm/MHz from 2.2 GHz to 10.6 GHz.

The IEEE-Std 802.15.3a proposal for high-data-rate has led to the multi-band MB-OFDM (14 bands of 528 MHz) UWB, a carrier-based communication protocol that divides the 3.1-10.6GHz UWB spectrum. The 802.15.3a task group also outcomes a Direct Sequence (DS) UWB standard, supported by the UWB Forum, using a very narrow pulse (from 100 ps to 1 ns) and considering a low band from 3.1 and 5.15 GHz and a high-frequency band between 5.825 and 10.6 GHz (FERNANDES; WENTZLOFF, 2010).

Figure 2.2 – BER vs. SNR of wideband systems DSSS and UWB for a single user.

Source: (GHAVAMI; MICHAEL; KOHNO, 2004).

The OFDM technique has been widely used in several types of wireless systems. Biomedical monitoring is being increasingly investigated, primarily when it is assigned to WBAN context. An example of a digital modulator VLSI circuit intended to use these techniques is presented in Appendix D. A vast number of contenders or competitor possibilities are in use in the universal worldwide ISM used around 2.4 to 2.5 GHz, in this case for narrowband transmissions.

In this frequency management scenario two other important bands exist: the Medical Implant Communications Service (MICS) and the Wireless Medical Telemetry Services (WMTSs). The former has the frequency range of 402-405 MHz and is used for implant communications, whereas the latter is used for medical telemetry systems, from 420-870 MHz, also in narrowband spectrum. It is worth to mention that, in general, the communication authorities of a country are capable of regulating the available frequencies for WBANs.

## 2.1.3 UWB PHY Specifications

There are two modes of operation in the WBAN according to the standard 802.15.6: the default mode and the high QoS, the latter is used only in high-priority medical applications. IR-UWB is mandatory in both default and High QoS modes, and FM-UWB is optional as PHY in

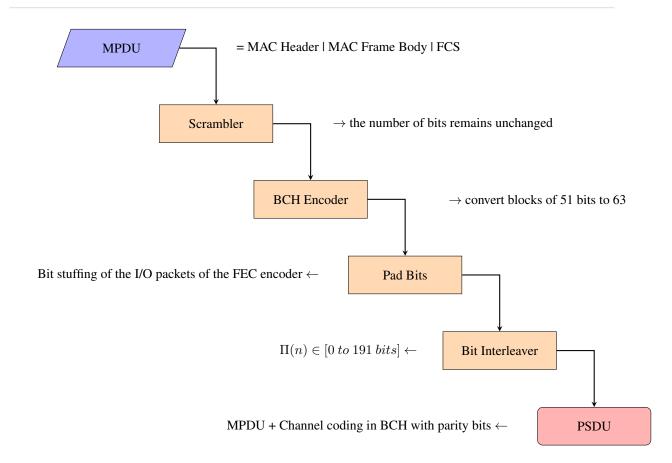

the default mode. The PSDU construction for the transmission is formatted with one scrambler, one interleaver, and the FEC encoder, adding Pad bits to complete the block.

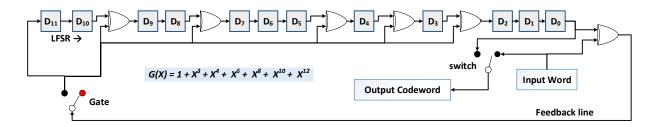

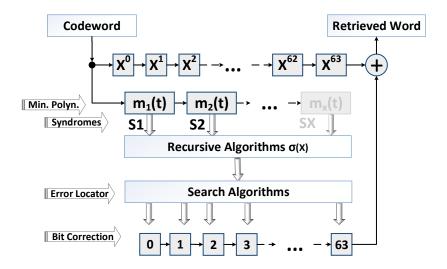

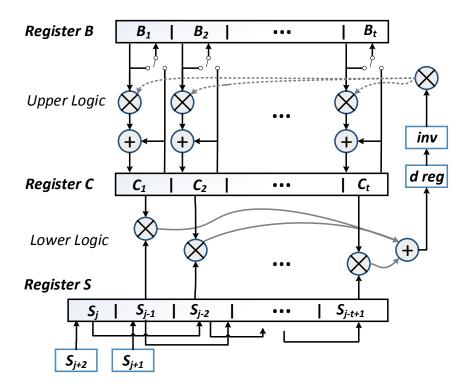

The Bose, Chaudhuri, and Hocquenghem (BCH) FEC encoder allows, in default mode, the use of a message with length of 51 bits generating the encoded message with 63 bits length, the maximum bit correction in that case is "2", BCH(63,51,2). Otherwise, at high quality or simply high QoS mode, the encoded message will have 126 bits length for a 64 bits message with a capability of up to 10 bit-flips of correction, ensuring higher robustness, i.e. BCH(126,64,10).

The Pad bits are added to align at a symbol boundary. The Equation 2.2 gives the pad bits number according to the cardinality of the constellation (M) of a given modulation scheme, according to the standard. The  $N_{CW}$  is the number of codewords, and each "N" is related to its equivalent number of bits in a packet. "n" and "k" are taken according to the BCH(n,k,t) code, representing the encoded message and the original one.

$$N_{pad} = log_2(M) \left[ \frac{N_{PSDU} + (n-k)N_{CW}}{log_2(M)} \right] - \left[ N_{PSDU} + (n-k)N_{CW} \right]$$

(2.2)

To proceed transmission, the PPDU bits are transformed into RF signals. For QoS mode, the BPSK/QPSK modulation schemes are chosen, and OOK is preferred for default mode. The modulation scheme that is not the priority in each mode becomes optional in that mode. But for both, the wideband frequency modulation (FM-UWB) is optional.

The number of pulses transmitted in one second is the pulse repetition frequency (PRF) parameter. PRF and other timing parameters are set to produce the expected data rates for OOK and DBPSK/DQPSK modulations. As an example of setting parameters that influence the data rate, the FEC code rate for high QoS must be set as 0.5, otherwise it is set to 0.81. As well as the number of possible pulse positions can be 32 and the waveform can vary in nanoseconds pulse duration (2.003 ns - 64.103 ns).

Table 2.3 contains the low and high bands according to the IEEE 802.15.6 standard, and at least one of specified band groups shall transmit in the UWB.

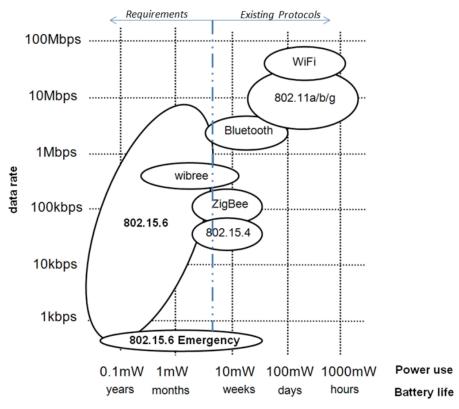

Figure 2.3 represents the scenarios in which short-range data communication are grouped in broad regions (in the energy vs. data rate graph) (MOVASSAGHI et al., 2014). It is to be noted that systems requirements that may comply to the IEEE standards 802.15.6 and 802.15.4 are very promising for sub-mW power, long battery life (months to years), in applications that can operate at very low data rates (below hundreds of Kbps). The medical applications and WBAN, considered in this thesis, require the communication system to stay in the bottom left extreme of figure 2.3. This is the energy constraint that is the focus of this work.

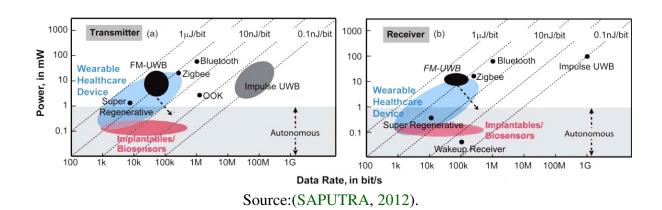

Some authors (SAPUTRA, 2012) mentioned that the energy efficiency improvements in autonomous applications such as implantable biosensors are required to compete with other radio schemes (*e.g.*, wake-up receiver or super regenerative transceiver). Fig. 2.4 depicted the context of Power (in mW) versus the throughput of the application (bit/s). In this case, contrasting to the one shown in Fig. 2.3, several technologies are presented separately on the

Table 2.3 – UWB operating frequency bands.

| Channel | Band | $f_{central}$ (MHz) | $f_{min}$ (MHz) | $f_{max}$ (MHz) |

|---------|------|---------------------|-----------------|-----------------|

| 0       | Low  | 3494.4              | 3244.8          | 3744            |

| 1       | Low  | 3993.6              | 3744            | 4243.2          |

| 2       | Low  | 4492.8              | 4243.2          | 4742.4          |

| 3       | High | 6489.6              | 6240            | 6739.2          |

| 4       | High | 6988.8              | 6739.2          | 7238.4          |

| 5       | High | 7488.0              | 7238.4          | 7737.6          |

| 6       | High | 7987.2              | 7737.6          | 8236.8          |

| 7       | High | 8486.4              | 8236.8          | 8736            |

| 8       | High | 8985.6              | 8736            | 9235.2          |

| 9       | High | 9484.8              | 9235.2          | 9734.4          |

| 10      | High | 9984.0              | 9734.4          | 10234           |

Source: IEEE 802.15.6 modified by the author.

Figure 2.3 – Data Rate versus Energy/Battery Lifetime.

Source: (MOVASSAGHI et al., 2014), modified by the author.

Figure 2.4 – Energy efficiency of various wireless (a) transmitter and (b) receiver.

## 2.2 Standard Overview (IEEE Std 802.15.6)

The communications regulated by the IEEE Std 802.15.6 occur in the vicinity of, or inside, a human body. It is titled as IEEE Standard for local and metropolitan area networks - Part 15.6: Wireless Body Area Networks. However, due to a multitude of components and devices, the standard does not specify the type of them and how these components operate, as well as their format. Each application and engineering development requirements will guide the choice (it could be a sensor application type, *e.g.*, for IoT) and other key communication system specifications - for example, the selected spectrum.

The standard details some essential aspects that come from: the general framework elements, the MAC frame formats and functions, and even the three PHY specifications, where the security service is intrinsically associated. This section highlighted some of such aspects, as an overview focused on the UWB, ISM, and MICS. The standard serves well the cross-layer modeling purpose of this work, because the first two layers of the network (PHY and MAC) are conforming to the proposed analysis. Three PHY layers already mentioned are supported by the MAC level according to this standard.

How to increase the useful life of each node in a WBAN is a significant attribute currently pursued by the researchers because it directly impacts the energy required for the operations of the whole system. Moreover, battery life is key to many WBAN systems in health monitoring. Thus, new and low-power techniques in the energy-constraint sensor nodes are extremely desirable. The standard allows to accommodate in this direction, formatting the packets into unique frames, while guiding the access mechanism.

The relationship between energy and data packets lengths is direct. A low-overhead protocol is important for low-power communications. The power used is proportional to the amount of bits per second required for communication following the standard. Therefore, for each PHY layer, it is essential to define frame formats, functions, modulations, and security services as a general specification. All of them are detailed by default according to some limits where the

structure of IEEE Std 802.15.6 is characterized by logically organized data packets that allow the elaboration of hierarchical and sub-contained information.

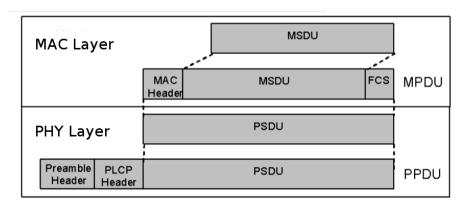

Due to the direct relationship between dissipated energy and the data unit organization in a communication environment, the WBAN standard proposes a hierarchical, self-contained packet structure (data packets nominations and acronyms) organized as follows: