# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL ESCOLA DE ENGENHARIA DEPARTAMENTO DE ENGENHARIA ELÉTRICA

#### **GABRIEL BERTALUCI DA COSTA**

## ANÁLISE DE VIABILIDADE DE UMA NOVA TOPOLOGIA PARA CONVERSORES A/D DO TIPO SAR

#### **GABRIEL BERTALUCI DA COSTA**

### ANÁLISE DE VIABILIDADE DE UMA NOVA TOPOLOGIA PARA CONVERSORES A/D DO TIPO SAR

Projeto de Diplomação II entregue ao Departamento de Engenharia Elétrica da Universidade Federal do Rio Grande do Sul – UFRGS, como parte dos requisitos para a graduação em Engenharia Elétrica.

Orientador: Prof. Dr. Tiago Roberto Balen

#### GABRIEL BERTALUCI DA COSTA

### ANÁLISE DE VIABILIDADE DE UMA NOVA TOPOLOGIA PARA CONVERSORES A/D DO TIPO SAR

Este Projeto de Diplomação foi analisado e julgado adequado para a obtenção de grau de Bacharel em Engenharia Elétrica e aprovado em sua forma final pelo Orientador e pela Banca Examinadora designada pelo Departamento de Engenharia Elétrica da Universidade Federal do Rio Grande do Sul.

| Orientador:                              |

|------------------------------------------|

| Prof. Dr. Tiago Roberto Balen, UFRGS     |

| BANCA EXAMINADORA                        |

| Prof. Dr. Tiago Roberto Balen, UFRGS     |

| Prof. Dr. Hamilton Duarte Klimach, UFRGS |

| Prof. Dr. Filipe Dias Baumgratz, UFRGS   |

#### **AGRADECIMENTOS**

Agradeço ao meu orientador, Prof. Dr. Tiago Roberto Balen, pela compreensão e a oportunidade de desenvolvimento deste trabalho.

Agradeço também aos meus pais, Cristiane e Fabiano, por todo carinho, apoio, força, compreensão e palavras de conforto que me deram ao longo dos anos e por tudo que fizeram para que este momento enfim ocorresse.

Agradeço aos colegas de curso Leomar Radke, Lucas Alves, Pedro Morgan e Vinícius Ceriotti por todas as longas noites mal dormidas de estudos e trabalhos e por todas as alegrias que a amizade de vocês me proporcionou ao longo desta trajetória.

Por fim, agradeço à todas as pessoas que estiveram ao meu lado ao longo destes anos, me incentivando e compreendendo minha ausência durante o período da graduação.

#### RESUMO

Os conversores analógicos-digitais por aproximações sucessivas (SAR ADC) do tipo redistribuição de carga são amplamente utilizados em diversas aplicações, principalmente nas que exigem um baixo consumo de área e energia. De forma a tentar melhorar a aplicação destes conversores, se faz necessário o estudo e desenvolvimento de novas tecnologias e topologias. Este trabalho apresenta o desenvolvimento, simulação e análise de viabilidade de uma nova topologia para um conversor analógico-digital por aproximações sucessivas. Esta topologia visa reduzir a área ocupada pelo banco de capacitores quando comparada à do conversor convencional. Através da utilização da parte analógica de um conversor SAR de 1 bit, realiza-se a conversão e após cada comparação, ajusta-se a tensão residual. Para o ajuste da tensão utiliza-se um dobrador de tensão com capacitores de mesmo tamanho da capacitância unitária do circuito do conversor. Após o ajuste da tensão residual a mesma realimenta o circuito inicial para realizar a conversão do próximo bit.

**Palavras-chave**: Conversor A/D. Aproximações Sucessivas. Conversores Cíclicos. Redistribuição de carga. Dobrador de tensão.

#### **ABSTRACT**

Successive Approximation Register (SAR) Analog to Digital Converters (ADCs) based on charge redistribution are widely used in a variety of applications, especially those requiring low power and low area consumption. In order to improve the application of these converters, it is necessary to study and develop new technologies and topologies. This work presents the development, simulation and feasibility analysis of a new topology for a successive approximation analog-to-digital converter. This topology aims to reduce the capacitor bank area when compared to the conventional converter. By using the analog part of a 1-bit SAR converter, the conversion is performed and after each comparison, the residual voltage is adjusted. To adjust the voltage, a voltage doubler with capacitors of the same size as the unit capacitance of the converter circuit is used. After adjusting the residual voltage, it will feedback the initial circuit to convert the next bit.

**Keywords**: Analog to Digital Converters. Successive Approximation Register. Cyclic Converters. Charge Redistribution. Voltage Doubler.

#### SUMÁRIO

| 1 | Intr  | odução                                                                     | 10 |

|---|-------|----------------------------------------------------------------------------|----|

|   | 1.1   | Motivação                                                                  | 10 |

|   | 1.2   | Objetivo                                                                   | 11 |

| 2 | Co    | nversores A/D                                                              | 12 |

|   | 2.1   | Principais arquiteturas                                                    | 15 |

|   | 2.2   | Conversor A/D Dupla Rampa                                                  | 16 |

|   | 2.3   | Conversor A/D do tipo Flash                                                | 18 |

|   | 2.4   | Conversor A/D do tipo Flash em dois passos                                 | 20 |

|   | 2.5   | Conversor A/D do tipo Pipeline                                             | 21 |

|   | 2.6   | Conversor A/D do tipo SAR                                                  | 22 |

|   | 2.7   | Topologia clássica do conversor A/D SAR baseado em redistribuição de carga | 24 |

|   | 2.8   | Conversores Cíclicos                                                       | 33 |

| 3 | De    | senvolvimento da nova topologia para o conversor SAR                       | 36 |

|   | 3.1   | Parte Analógica                                                            | 36 |

|   | 3.2   | Lógica de Controle Digital                                                 | 42 |

| 4 | Sin   | nulações                                                                   | 46 |

|   | 4.1   | MATLAB                                                                     | 46 |

|   | 4.2   | LTSPICE                                                                    | 46 |

| 5 | Re    | sultados e Discussão                                                       | 49 |

|   | 5.1   | Simulações do Circuito de Controle das Chaves                              | 49 |

|   | 5.2   | Simulações dos Sinais do Circuito Analógico                                | 52 |

|   | 5.3   | Simulações contendo não-idealidades                                        | 58 |

|   | 5.4   | Viabilidade da nova topologia                                              | 63 |

| 6 | Co    | nclusão                                                                    | 65 |

| 7 | Re    | ferências                                                                  | 67 |

| Α | pêndi | ce 1 – Netlist Spice                                                       | 69 |

| Α | pêndi | ce 2 – Código MATLAB                                                       | 73 |

#### **LISTA DE IMAGENS**

| Figura 1 - Entradas e saídas de um conversor analógico-digital                        | .10 |

|---------------------------------------------------------------------------------------|-----|

| Figura 2 - Diagrama conversores A/D e D/A                                             | .12 |

| Figura 3 - Exemplo de erro de aliasing                                                | .13 |

| Figura 4 - Exemplo de amostragem com e sem retenção                                   | .13 |

| Figura 5 - Exemplo de reconstrução de um sinal com e sem retenção                     | .14 |

| Figura 6 - Aproximação da amplitude do sinal contínuo para o valor discreto mais      |     |

| próximo                                                                               |     |

| Figura 7 - Comparativo de características de algumas arquiteturas de conversores      |     |

| A/D                                                                                   | .15 |

| Figura 8 - Diagrama simplificado para um conversor A/D dupla rampa                    | .16 |

| Figura 9 - Exemplo de conversão para um conversor dupla rampa de três bits            | .18 |

| Figura 10 - Arquitetura de um conversor A/D Flash                                     | .19 |

| Figura 11 - Diagrama de blocos de um conversor A/D Flash em dois passos               | .20 |

| Figura 12 - Diagrama de blocos de um conversor A/D Pipeline                           | .21 |

| Figura 13 - Exemplo de conversão com busca binária para conversor de 5 bits           | .23 |

| Figura 14 - Fluxograma do funcionamento da busca binária por aproximações             |     |

| sucessivas utilizando 2 bits                                                          |     |

| Figura 15 - Matriz de capacitores e divisor capacitivo equivalente                    | .25 |

| Figura 16 - Circuito base para o conversor SAR por redistribuição de carga            | .26 |

| Figura 17 - Banco de capacitores para um conversor de 8 bits                          | .26 |

| Figura 18 - Banco de capacitores equivalente após a primeira redistribuição           | .28 |

| Figura 19 - Banco de capacitores equivalente após a segunda redistribuição, caso      | 0   |

| resultado da comparação anterior tenha sido nível lógico alto                         | .29 |

| Figura 20 - Banco de capacitores equivalente após a segunda redistribuição, caso      |     |

| resultado da comparação anterior tenha sido nível lógico baixo                        | .30 |

| Figura 21 - Lógica de controle para um conversor de N bit                             |     |

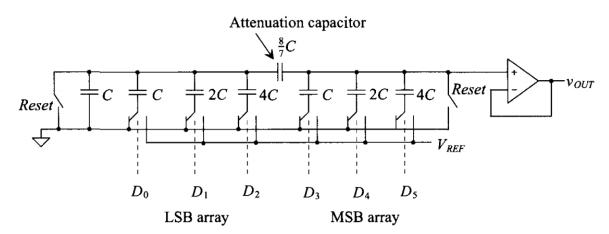

| Figura 22 - Topologia para um conversor SAR de 6 bits com capacitor atenuador         | .32 |

| Figura 23 - Diagrama de blocos genérico para um conversor cíclico                     |     |

| Figura 24 - Circuito de um conversor cíclico com capacitor chaveado                   |     |

| Figura 25 - Topologia básica para um conversor SAR de 1 bit                           |     |

| Figura 26 - Topologia desenvolvida para o dobrador da tensão residual                 | .38 |

| Figura 27 - Topologia do dobrador na etapa de amostragem                              |     |

| Figura 28 - Topologia do dobrador na etapa da dobra de tensão                         | .39 |

| Figura 29 - Circuito da parte analógica do conversor                                  |     |

| Figura 30 - Diagrama de estados da parte operativa do conversor                       |     |

| Figura 31 - Sequenciador para um conversor de 4 bits                                  |     |

| Figura 32 - Flip-flop do tipo JK descrito através das portas lógicas                  |     |

| Figura 33 - Flip-flop do tipo D modelado a partir de um flip-flop do tipo JK          | .47 |

| Figura 34 - Topologia desenvolvida no LTSPICE                                         |     |

| Figura 35 - Sinais de saída dos flip-flops da máquina de estados principal            |     |

| Figura 36 - Sinais de controle das chaves                                             |     |

| Figura 37 - Sinais de controle da chave S <sub>C0</sub> para comparador em nível alto | .51 |

| Figura 38 - Sinais de controle da chave S $_{ m C0}$ para comparador em nível baixo    | 51     |

|----------------------------------------------------------------------------------------|--------|

| Figura 39 - Sinais Vcomp- e Vouт ao longo da conversão                                 | 52     |

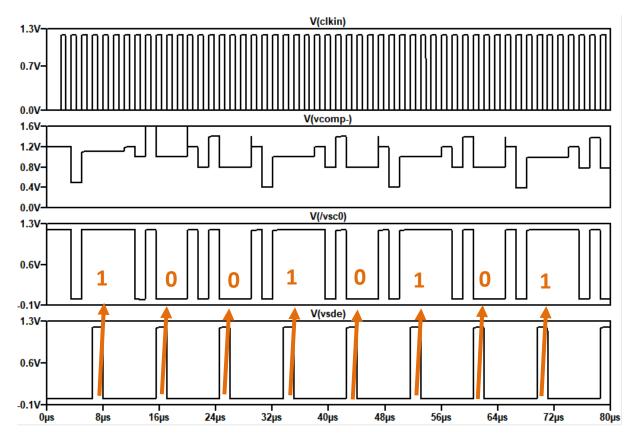

| Figura 40 - Sinal de saída negado do flip-flop JK e sinal V <sub>SDE</sub>             | 54     |

| Figura 41 - Sinais de saída para V <sub>IN</sub> = 0 V                                 | 55     |

| Figura 42 - Sinais de saída para V <sub>IN</sub> = 1,2 V                               | 55     |

| Figura 43 - Sinais de saída para V <sub>IN</sub> = 0,7 V                               | 56     |

| Figura 44 - Sinais de saída do sequenciador com 8 bits para V <sub>IN</sub> = 0,7 V    | 57     |

| Figura 45 - Sinais de saída do sequenciador com 12 bits para V <sub>IN</sub> = 0,7 V   | 58     |

| Figura 46 - Amplificador não-inversor                                                  | 59     |

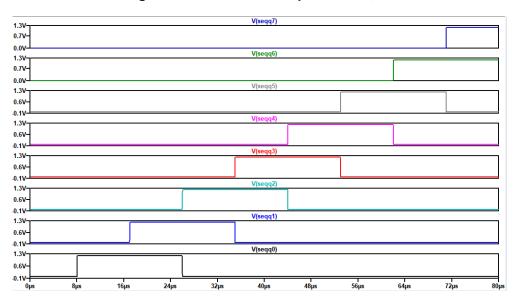

| Figura 47 - Sinais de saída com o erro de 1% no buffer e V <sub>IN</sub> = 0,7 V       | 59     |

| Figura 48 - Sinais de saída para V <sub>IN</sub> = 0,9 V                               | 60     |

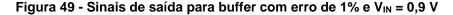

| Figura 49 - Sinais de saída para buffer com erro de 1% e V <sub>IN</sub> = 0,9 V       | 60     |

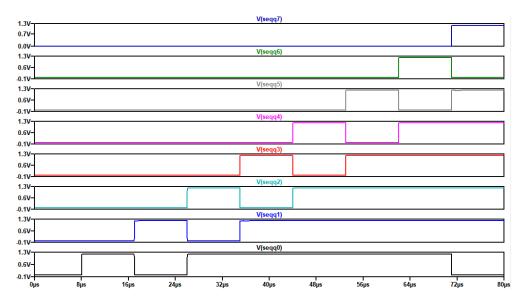

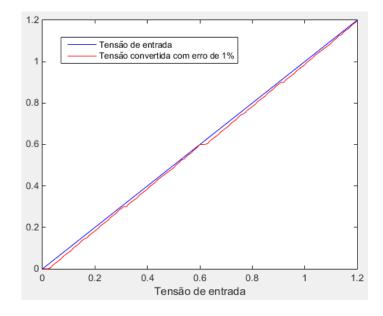

| Figura 50 – Simulação matemática comparando a tensão convertida e a tensão             | o de   |

| entrada sem considerar o erro no buffer                                                | 61     |

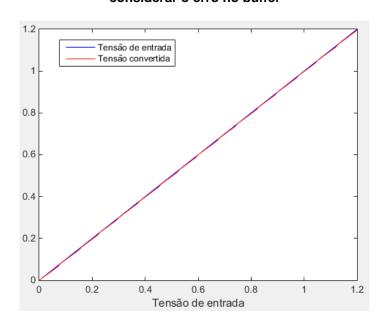

| Figura 51 - Simulação matemática comparando a tensão convertida e a tensão             | de     |

| entrada considerando o erro de 1% no buffer                                            | 61     |

| Figura 52 - Sinais de saída utilizando resistência de chave aberta de 10G $\Omega$ e e | ntrada |

| V <sub>IN</sub> = 0,7 V                                                                | 62     |

| Figura 53 - Sinais de saída utilizando resistência de chave aberta de 1G $\Omega$ e en | trada  |

| V <sub>IN</sub> = 0,7 V                                                                | 63     |

#### 1 Introdução

#### 1.1 Motivação

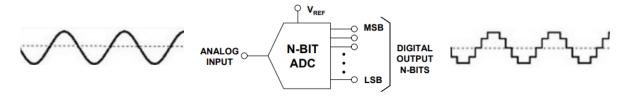

Os conversores analógico-digitais (A/D ou ADC) transformam as grandezas analógicas, características da maioria dos fenômenos do "mundo real", à linguagem digital, usada em processamento de informações, computação, transmissão de dados e sistemas de controle (KESTER, 2005). Este processo é ilustrado na Figura 1.

Figura 1 - Entradas e saídas de um conversor analógico-digital

FONTE: (KESTER, 2005)

O crescimento do processamento de informações no domínio digital, resultou na ampla utilização dos conversores para obter as informações do domínio analógico.

Os avanços na tecnologia de semicondutores, juntamente com o aumento da demanda, impulsionaram inovação significativa em conversores de dados durante as últimas décadas (MANGANARO, 2012).

Diversos tipos de conversores estão disponíveis no mercado atual para as mais diversas aplicações. A aplicação em si, é normalmente o fator determinante para a escolha do tipo a ser empregado.

Com o avanço da tecnologia e as diversas opções disponíveis de conversores, se faz necessário o estudo de novas tecnologias ou topologias que inovem ou melhorem o funcionamento dos mesmos.

#### 1.2 Objetivo

Conversores A/D do tipo Registrador de Aproximações Sucessivas (Sucessive Approximation Register – SAR) tem sido o esteio da aquisição de dados por muitos anos e permitem uma resolução aceitável associada à velocidade de conversão (KESTER, 2005). Entretanto, quando se faz necessário uma maior resolução, a área associada ao banco de capacitores utilizados para realizar a conversão tem um aumento expressivo.

O presente trabalho tem como objetivo o desenvolvimento e estudo de viabilidade de uma nova topologia proposta para reduzir a área de um conversor A/D SAR baseado em redistribuição de carga. Esta nova topologia é baseada em um SAR de 1 bit em que, após cada comparação, ajusta a tensão residual e a utiliza para realizar uma nova comparação.

Através desta nova topologia, o aumento da resolução do conversor não afetará a área do mesmo, entretanto terá uma grande dependência associada ao tempo de conversão. Quanto maior a resolução, maior o tempo de conversão, reduzindo assim a frequência de operação.

Ao longo do trabalho serão apresentadas algumas arquiteturas de conversores A/D que agregarão conceitos e servirão de base para o desenvolvimento da nova topologia.

#### 2 Conversores A/D

O conversor analógico-digital transforma a entrada analógica, usualmente na forma de tensão ou corrente, em uma saída digital. O conversor digital-analógico (D/A ou DAC), por sua vez, possui a função oposta e converte um sinal digital de entrada para um sinal analógico de saída, conforme representado na Figura 2.

Analog Input

Digital Output  $b_0$   $b_1$   $b_1$

Figura 2 - Diagrama conversores A/D e D/A

**FONTE: (GUSTAVSON, 2002)**

Conversores digitais-analógicos convertem sinais discretos para analógicos. Esta conversão, porém, é limitada pela resolução do sinal digital de entrada. Um número pré-definido de sinais de entrada gerará um número determinado de sinais de saída. Em um conversor A/D, o sinal analógico de entrada possui uma infinidade de valores que necessitam ser quantizados, uma das características que tornam este processo mais difícil do que o citado anteriormente (GUSTAVSSON, 2002).

O processo de conversão de um sinal analógico ocorre em diversas etapas. Primeiramente, o sinal de entrada é aplicado em um filtro passa-baixa de forma a limitar a frequência do sinal e prevenir o erro de *aliasing (BAKER, 2008)*.

O erro de *aliasing* ocorre quando o critério de Nyquist não é cumprido, ou seja, a frequência de amostragem utilizada (f<sub>s</sub>) é inferior ao dobro da máxima frequência do sinal analógico. Quando esse erro acontece, o conversor D/A não possui amostras suficientes para reconstruir o sinal e, o sinal reconstruído será diferente do originalmente amostrado. Um exemplo de erro de *aliasing* é demonstrado na Figura 3 nos sinais de 19MHz e 39 MHz, pois a frequência de amostragem de 20MHz é inferior ao dobro da frequência do sinal. Nesses sinais, portanto, a amostragem obtida criaria uma reconstrução igual à do sinal de 1MHz.

f<sub>signal</sub>= 1 MHz

f<sub>signal</sub>= 19 MHz

f<sub>signal</sub>= 39 MHz

1 μs

Figura 3 - Exemplo de erro de aliasing

FONTE: (PELGROM, 2010)

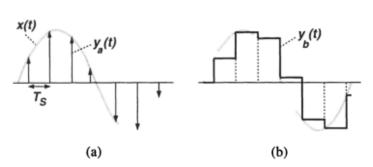

Após o processo de corte das altas frequências, o sinal de entrada será submetido ao circuito de amostragem e retenção (Sample and Hold - S/H), no qual o sinal será amostrado, em uma frequência determinada, e o valor da amostra será retido até o conversor A/D processar a informação.

A Figura 4a apresenta uma amostragem ideal, onde o sinal analógico é multiplicado por uma sequência de impulsos, porém, esse sinal é de difícil análise e gera diversos erros devido ao seu curto período de amostragem. Na Figura 4b, o valor da forma de onda do sinal no instante da amostragem é capturado e mantido até a amostragem seguinte, de forma que o conversor processe corretamente. Durante o período de retenção, o sinal amostrado será quantizado e o codificador realizará a conversão para o valor digital correspondente.

Figura 4 - Exemplo de amostragem com e sem retenção

FONTE: (RAZAVI, 1995)

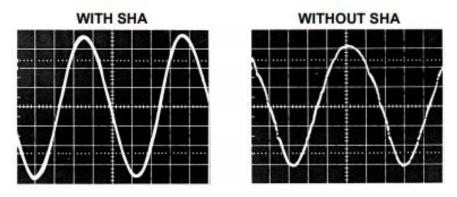

A Figura 5 mostra a comparação entre a reconstrução do sinal obtido por um conversor A/D Flash com e sem o circuito de retenção.

Figura 5 - Exemplo de reconstrução de um sinal com e sem retenção

FONTE: (KESTER, 2005)

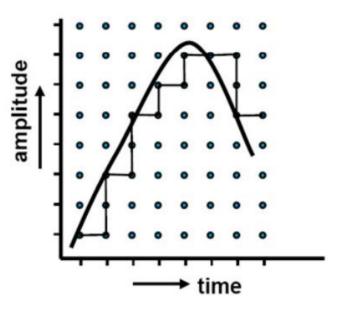

Após isto é realizado o processo de quantização, que corresponde à discretização do sinal amostrado. Durante a quantização, o nível do sinal é comparado com faixas de valores de referência, conforme a Figura 6. A faixa de valores de referência apresenta um número limitado de níveis. A amplitude do sinal contínuo é aproximada ao nível discreto mais próximo. Cada conversão analógica-digital produzirá erros de arredondamento, denominados erros de quantização.

Figura 6 - Aproximação da amplitude do sinal contínuo para o valor discreto mais próximo

FONTE: (PELGROM, 2010)

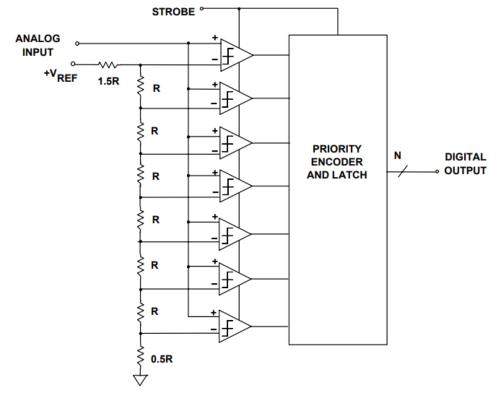

#### 2.1 Principais arquiteturas

Por possuir muitas aplicações nos mais diferentes domínios, os conversores possuem diversas arquiteturas. Para escolher o conversor adequado para determinada aplicação, é necessário analisar não apenas a precisão ou número de bits. Arquiteturas diferentes estão disponíveis, cada uma exibindo vantagens e desvantagens entre si (MICROCHIP TECHNOLOGY, 2004).

Dentre as diferenças apresentadas entre as arquiteturas, podem-se citar algumas como: consumo de energia, utilização de área em silício, velocidade de conversão, tensão de operação e resolução.

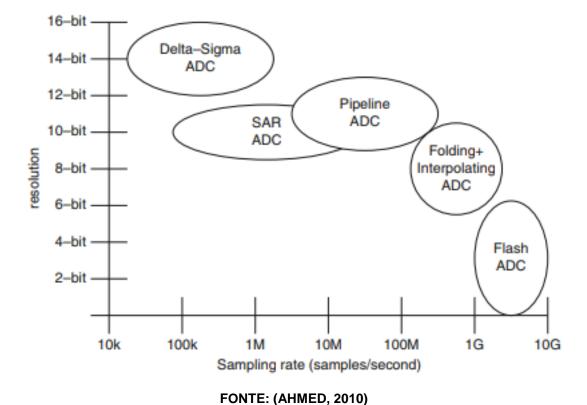

A Figura 7 mostra um comparativo entre as principais arquiteturas de conversores A/D, relacionando o número de bits e a taxa de amostragem.

Figura 7 - Comparativo de características de algumas arquiteturas de conversores A/D

A Tabela 1 demonstra um comparativo entre as principais arquiteturas em relação à latência, velocidade, resolução e área.

Arquitetura Latência Velocidade Resolução Área Flash Alta Alta Baixa Baixa SAR Baixa Baixa/Média Média/Alta Baixa Foldin + Interpolating Média/Alta Média Alta Baixa Delta-sigma Alta Baixa Alta Média **Pipeline** Alta Média/Alta Média/Alta Média

Tabela 1 - Comparativo entre os principais conversores A/D

FONTE: (AHMED, 2010)

#### 2.2 Conversor A/D Dupla Rampa

Essa modelo de conversor é bastante popular. Realiza a conversão de maneira indireta, primeiro convertendo em função do tempo, depois convertendo para um valor digital utilizando um contador. Esse modelo é muito utilizado em voltímetros digitais e aplicações nas quais o tempo de conversão possa ser relativamente mais lento em troca de uma redução de ruído devido à integração do sinal amostrado de entrada (SHEINGOLD, 1986).

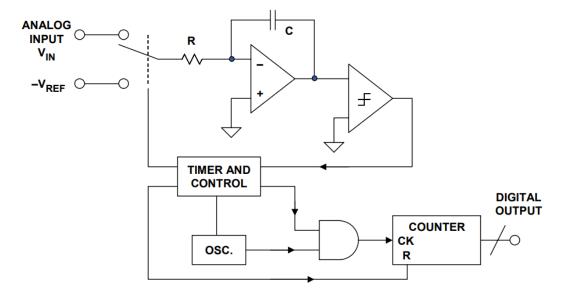

A Figura 8 mostra um diagrama simplificado para este modelo de conversor.

Figura 8 - Diagrama simplificado para um conversor A/D dupla rampa

FONTE: (KESTER, 2005)

Segundo Kester (KESTER, 2005), o início da conversão se dá quando o sinal analógico de entrada é aplicado à um integrador enquanto o contador é iniciado, contando os pulsos do relógio.

Após um período pré-determinado de tempo (T), a carga acumulada no capacitor será proporcional à média do valor de entrada no intervalo de tempo T. A partir disso, inicia-se a segunda parte do processo, onde uma tensão de referência com polaridade contrária é aplicada ao integrador.

No instante em que a nova tensão é aplicada, a integral em rampa será no sentido contrário e o contador será zerado e reiniciado. Quando o valor do sinal do integrador atingir zero, após um intervalo de tempo t<sub>x</sub>, o contador para e o circuito é reiniciado.

Como o integrador é inversor, o sinal de entrada deverá ser negativo. Dessa forma, a inclinação da rampa de subida será:

$$\alpha = \frac{V_{IN}}{RC} \tag{1}$$

Onde V<sub>IN</sub> representa a tensão analógica de entrada e R e C respectivamente o valor da resistência e capacitância indicados na Figura 8.

Já a inclinação da rampa de descida será:

$$\alpha = \frac{-V_{REF}}{RC} \tag{2}$$

Onde VREF representa a tensão de referência.

Como a carga obtida inicialmente é proporcional a T.V<sub>IN</sub>:

$$Q_{obtida} = k \cdot T \cdot V_{IN} \tag{3}$$

A carga perdida é proporcional à tx. VREF:

$$Q_{perdida} = k \cdot t_x \cdot V_{REF} \tag{4}$$

E as cargas obtidas e perdidas possuem idealmente o mesmo valor. Tem-se que:

$$Q_{ohtida} = Q_{nerdida} \tag{5}$$

$$k \cdot T \cdot V_{IN} = k \cdot t_{x} \cdot V_{REF} \tag{6}$$

$$\frac{t_x}{T} = \frac{V_{IN}}{V_{REF}} \tag{7}$$

Então, o número de contagens da rampa de descida em relação à de subida será de t<sub>x</sub>/T, ou V<sub>IN</sub>/V<sub>REF</sub>.

Na Figura 9, é apresentado um exemplo de conversão para um conversor de 3 bits, onde as tensões  $V_A$  e  $V_B$  são integradas por oito ( $2^3$ ) períodos de relógio. O tempo de descarga para as duas tensões, varia.

A tensão V<sub>A</sub> leva 3 contagens do relógio para atingir o zero. Portanto, em um conversor de 3 bits, o valor da saída digital seria dois (0b010), considerando que a primeira contagem equivale à saída digital zerada (0b000). Já a tensão V<sub>B</sub> leva 6 ciclos de relógio, logo, o resultado da conversão seria cinco (0b101).

Figura 9 - Exemplo de conversão para um conversor dupla rampa de três bits

#### 2.3 Conversor A/D do tipo Flash

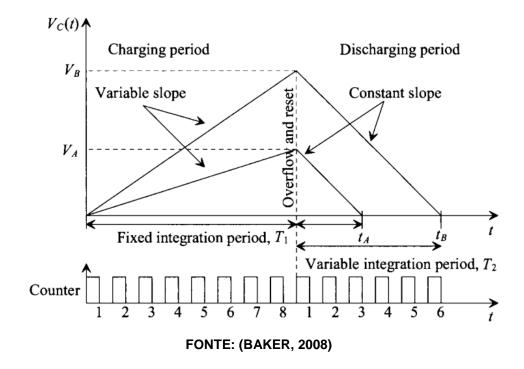

Utilizados em projetos onde é necessária uma alta velocidade de conversão, os conversores flash podem atingir taxas de amostragem muito altas. Há um comparador para cada nível de quantização. Os níveis de referência para os comparadores são gerados por uma sequência de resistores.

Um codificador é usado para gerar a saída no formato digital. Em geral, um conversor *Flash* converte em um único ciclo de relógio, sendo essa a sua principal vantagem em relação à outras arquiteturas.

A Figura 10 apresenta a estrutura deste conversor. Nesta arquitetura, a tensão de referência V<sub>REF</sub> é dividida em 2<sup>N</sup> partes através de uma cadeia de resistores. Cada uma dessas partes é conectada aos comparadores do circuito. Então, a tensão de entrada V<sub>IN</sub> é comparada com os diferentes valores de referência. Cada um dos 2<sup>N</sup>-1 comparadores irá apresentar saída com nível lógico alto quando a tensão V<sub>IN</sub> for maior que a respectiva tensão de referência particionada. Então, um codificador transformará o valor dessas saídas em um sinal digital equivalente ao número de bits utilizado no conversor (BAKER, 2008).

Figura 10 - Arquitetura de um conversor A/D Flash

FONTE: (KESTER, 2005)

O principal problema relacionado a esta arquitetura é que o número de comparadores aumenta exponencialmente de acordo com a quantidade de bits. Para N bits, são necessários 2<sup>N</sup> -1 comparadores. Devido a isto, o número de bits utilizados nessa arquitetura é usualmente limitado, pois a área utilizada, o consumo de potência

e a complexidade do circuito seriam muito elevados para altas resoluções (GUSTAVSSON, 2002).

#### 2.4 Conversor A/D do tipo Flash em dois passos

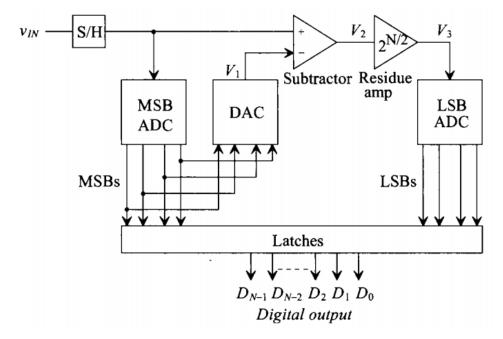

Outro modelo de conversor é o denominado Flash em dois passos. A Figura 11 mostra o diagrama de blocos básico, composto principalmente de dois conversores Flash e um conversor D/A.

Figura 11 - Diagrama de blocos de um conversor A/D Flash em dois passos

**FONTE: (BAKER, 2008)**

Após a entrada ser amostrada, a metade mais significativa de bits (Most Significant Bits - MSBs) é convertida pelo primeiro Flash. Pode-se dizer que este conversor realiza uma estimativa do valor da entrada (BAKER, 2008).

Após esta primeira estimativa, este valor digital é então convertido novamente para tensão analógica por um conversor D/A e subtraído da entrada original.

O resultado da subtração, denominado resíduo, é então multiplicado por 2<sup>N/2</sup> e inserido no segundo conversor. Esta multiplicação permite que os dois conversores

Flash sejam idênticos e também aumenta o nível de quantização do sinal de entrada no segundo conversor.

A partir disso, o segundo conversor entra em ação produzindo os bits menos significativos, realizando o ajuste fino da conversão.

A vantagem dessa arquitetura é que o número de comparadores é amplamente reduzido em comparação com o Flash simples – de  $2^N$  - 1 para  $2(2^{N/2}-1)$  – pois utiliza dois conversores Flash, cada um com metade do número de bits do original. Por exemplo, um conversor Flash de 10 bits requer 1023 comparadores, enquanto o Flash em dois passos somente 62.

A desvantagem é que o processo de conversão é feito em dois passos ao invés de um, com a velocidade limitada pela largura de banda e o tempo requerido sendo limitado pelo amplificador de resíduo e o subtrator.

#### 2.5 Conversor A/D do tipo Pipeline

De maneira similar a qual o Flash em dois passos divide a conversão em dois estágios, o conversor analógico-digital pipeline pode dividir a conversão em vários. É um conversor de N-passos, onde N é o número de bits e cada bit é convertido em um estágio. Capaz de atingir altas resoluções com velocidades relativamente rápidas, o conversor pipeline consiste de N estágios conectados em série, em que cada estágio contém um conversor de 1-bit, um circuito de amostragem e retenção, um somador e um amplificador de ganho dois, conforme Figura 12.

$v_{IN}$  S/H  $V_{P1}$   $V_{REF}$   $V_{N-1}$   $V_{REF}$   $V_{N-1}$   $V_{REF}$   $V_{N-1}$   $V_{REF}$   $V_{N-1}$   $V_{REF}$   $V_{N-1}$   $V_{REF}$   $V_{N-1}$   $V_{N-1}$

Figura 12 - Diagrama de blocos de um conversor A/D Pipeline

FONTE: (BAKER, 2008)

Após o sinal de entrada ser amostrado, é comparado com V<sub>REF</sub>/2. A saída do comparador é o bit de conversão do estágio.

Se  $V_{\text{IN}} > V_{\text{REF}}/2$ , a saída do comparador será nível lógico alto,  $V_{\text{REF}}/2$  será subtraído do sinal retido e o resultado irá para o amplificador. Se  $V_{\text{IN}} < V_{\text{REF}}/2$ , a saída do comparador será nível lógico baixo e o sinal de entrada original irá para o amplificador. O sinal que vai para o amplificador é denominado resíduo.

O resíduo, então, sofre o ganho de valor dois e segue para a amostragem e retenção do próximo estágio.

A principal vantagem do conversor pipeline é a sua alta taxa de conversão. Após a latência inicial de N ciclos do relógio, uma conversão será completada a cada ciclo do relógio. Enquanto o resíduo do primeiro estágio está sendo operado pelo segundo estágio, o primeiro estágio está livre para operar a próxima amostra. Cada estágio opera no resíduo passado adiante, o que permite rápidas conversões. Uma das desvantagens, por outro lado, é a latência inicial de N ciclos do relógio antes da primeira saída digital ocorrer (BAKER, 2008).

Outro ponto a ser destacado nesse estilo de conversor é a dependência em relação ao bit mais significativo. Um erro no primeiro estágio será propagado através da conversão de todos os outros bits, resultando em uma conversão diferente da esperada.

#### 2.6 Conversor A/D do tipo SAR

Apesar de ser mais lento que outros modelos de conversores como Pipeline e Flash, o consumo de energia baixo nos conversores com arquitetura do tipo SAR a torna uma arquitetura muito utilizada (ROBOT PLATAFORM, 2010).

Esta arquitetura funciona através do método de busca binária para determinar o valor digital da entrada analógica. A busca se baseia em N comparações sucessivas entre a entrada analógica e uma tensão de referência produzida por um conversor D/A.

O método mais comum de busca binária do conversor SAR inicia-se pelo bit mais significativo (MSB), determinando se o valor de V<sub>IN</sub> é maior ou menor do que

<sup>1</sup>/<sub>2</sub>V<sub>REF</sub>. Após a primeira comparação, o próximo bit é ativado e uma nova comparação é feita. A cada etapa, ocorre um estreitamento na faixa de possíveis resultados. A Figura 13 mostra um exemplo de conversão para 5 bits.

$V_{dac}$   $V_{ref}/2$   $V_{ref}/4$   $b_4=0$   $b_2=1$   $b_3=1$   $b_1=0$

Figura 13 - Exemplo de conversão com busca binária para conversor de 5 bits

FONTE: (GUSTAVSSON, 2002)

A conversão inicia com a amostragem do sinal analógico. Em seguida, o circuito de controle ativa o MSB e desativa os demais bits. Este valor digtal é aplicado no conversor D/A gerando a tensão analógica de ½ V<sub>REF</sub>. Esta tensão é então comparada com o valor da entrada V<sub>IN</sub>. Caso V<sub>IN</sub> seja maior, a lógica de controle manterá o MSB ativo. Caso contrário, a lógica de controle desativará o MSB.

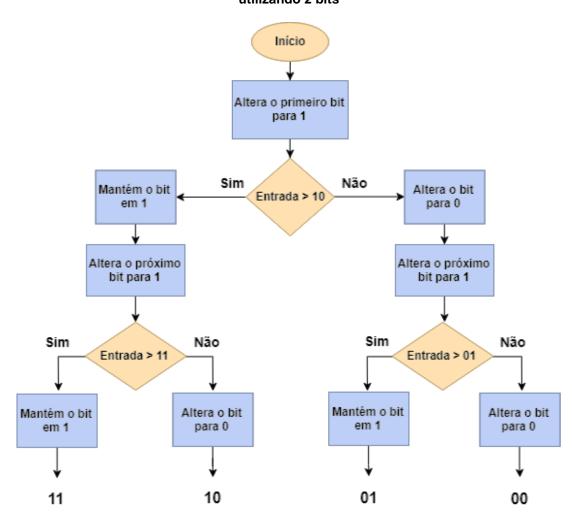

Após este primeiro passo, o segundo bit é ativado e uma nova comparação é feita. Este processo é repetido sucessivamente até que todos os bits tenham sido definidos. Após isso, o sinal analógico estará convertido em formato digital. A Figura 14 exemplifica o algoritmo de aproximações sucessivas para 2 bits.

Exatidão, linearidade e velocidade deste modelo de conversor são diretamente afetadas pelas propriedades do conversor D/A e do comparador. Em geral, o tempo de estabilização do D/A e o tempo de resposta do comparador são considerados mais lentos que o tempo de comutação dos elementos digitais. (SHEINGOLD, 1986).

Figura 14 - Fluxograma do funcionamento da busca binária por aproximações sucessivas utilizando 2 bits

### 2.7 Topologia clássica do conversor A/D SAR baseado em redistribuição de carga

O circuito de um conversor A/D SAR baseado em redistribuição de carga consiste de quatro blocos principais: um banco de capacitores, um comparador, um conjunto de chaves e o controle digital das chaves.

O banco de capacitores consiste de N + 1 capacitores, onde N é o número de bits do conversor e cada bit é associado a um capacitor.

Neste conversor os valores a serem comparados na busca binária são obtidos através de capacitores atuando como D/A. Estes capacitores são associados para formar diversos divisores de tensão capacitivos, gerando assim os valores de tensão para futura comparação.

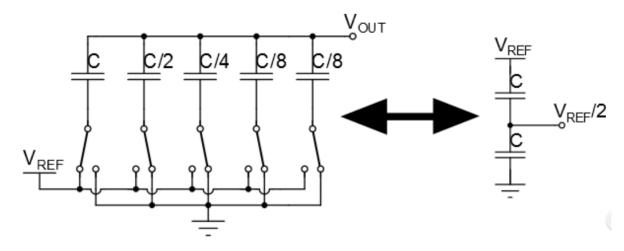

A Figura 15 apresenta um divisor capacitivo que poderia ser utilizado em um conversor de 4 bits.

Figura 15 - Matriz de capacitores e divisor capacitivo equivalente

FONTE: (LANOT, 2014)

Através do arranjo das chaves, é possível obter a tensão desejada para a comparação. Por exemplo, no caso do chaveamento do circuito da Figura 15, a capacitância equivalente vista pelo nó de saída V<sub>OUT</sub> do divisor é a mesma tanto em relação à V<sub>REF</sub> quanto em relação ao *ground*. Desta forma, o valor da tensão de saída será equivalente à metade do valor da tensão de entrada.

As comparações do sinal de referência com esses valores são realizadas em um comparador, que colocará a saída em nível lógico alto se a tensão de referência for maior que a de comparação ponderada pelos capacitores, ou nível lógico baixo caso contrário. A saída do comparador controlará a ponderação da tensão de referência para permitir a convergência do sinal digital de saída através da lógica de controle, que implementará o algoritmo executando o correto chaveamento.

O circuito base para um conversor A/D por redistribuição de carga de 8 bits está apresentado na Figura 16.

Figura 16 - Circuito base para o conversor SAR por redistribuição de carga

FONTE: (LANOT, 2014)

BARRAMENTO

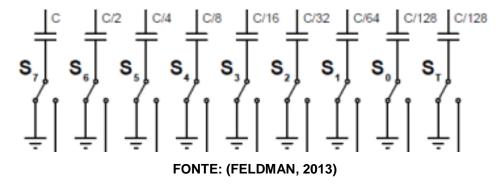

Os valores dos capacitores no banco são equivalentes ao mostrado na Figura 17.

Figura 17 - Banco de capacitores para um conversor de 8 bits

Os passos da conversão em um SAR de redistribuição de carga, utilizando um conversor de terminação simples para simplificar a explicação, são apresentados a seguir:

#### 1) Amostragem:

SW\_SHARED

Etapa na qual a tensão a ser convertida é amostrada. Inicia-se com as chaves  $S_0$  à  $S_7$  dos capacitores, conectando-os ao barramento comum. A chave superior  $S_A$  conecta  $V_{REF}$  e a chave do barramento  $S_B$  é posicionada em  $V_{IN}$ .

Com este chaveamento realizado, a rede capacitiva será carregada com uma diferença de potencial de V<sub>REF</sub> – V<sub>IN</sub>. Como a carga armazenada em um banco de capacitores é dada por:

$$O = C \cdot \Delta V \tag{8}$$

Onde C é a capacitância total do banco e ΔV a variação de tensão. Sabendo que a capacitância do banco é 2C, a carga total armazenada no banco será:

$$Q = 2C \cdot (V_{REF} - V_{IN}) \tag{9}$$

#### 2) Retenção:

A chave S<sub>A</sub> desconecta V<sub>REF</sub> e as chaves dos capacitores conectam os mesmos ao *ground*. Como não há caminho para a descarga dos capacitores durante o chaveamento, a carga permanecerá a mesma.

Assim, como a tensão na parte inferior dos capacitores é zero, devido à conexão com o *ground*, e a diferença de potencial é V<sub>REF</sub> – V<sub>IN</sub>, a tensão V<sub>COMP</sub>-passará a ser V<sub>REF</sub> – V<sub>IN</sub> e a carga do banco permanecerá a mesma.

A razão para a amostragem do sinal de entrada ser relacionada à V<sub>REF</sub>, ao invés do *ground*, é para evitar uma tensão negativa entre o nó V<sub>COMP</sub>- e o *ground*. Isso se deve ao fato de que quando chaves MOSFET são utilizadas, uma tensão negativa neste nó pode modificar o transistor NMOS, que conecta os capacitores ao *ground* durante esta fase de retenção, descarregando o banco (BECKER et al., 2017). A tensão V<sub>REF</sub> utilizada nesta fase é cancelada na comparação devido ao mesmo realiza-la em relação à V<sub>REF</sub>.

#### 3) Redistribuição de carga:

Etapa na qual se inicia a conversão. A chave S<sub>B</sub> conecta-se à V<sub>REF</sub>, e a chave associada ao bit mais significativo, neste caso, chave S<sub>7</sub>, conecta o capacitor ao barramento. Com isto, um divisor capacitivo é formado entre o capacitor C<sub>7</sub> e a associação paralela de C<sub>6</sub> à C<sub>0</sub>. Os valores das capacitâncias seguem o padrão mostrado na Figura 17. A associação paralela de C<sub>6</sub> à C<sub>0</sub> possui o mesmo valor de C<sub>7</sub>, neste caso representado por C. O circuito equivalente é apresentado na Figura 18.

Figura 18 - Banco de capacitores equivalente após a primeira redistribuição

Este divisor capacitivo, com dois capacitores de mesmo valor, resulta em um aumento da tensão V<sub>COMP</sub>- em V<sub>REF</sub>/2. Como pode ser observado a seguir.

A carga total do banco é de:

$$Q_{TOTAL} = 2C \cdot (V_{REF} - V_{IN}) \tag{10}$$

Já a carga de cada um dos lados do divisor é de:

$$Q_1 = C \cdot (V_{COMP} - V_{REF}) \tag{11}$$

$$Q_2 = C \cdot (V_{COMP}) \tag{12}$$

Sendo Q<sub>1</sub> a carga no capacitor C<sub>7</sub> e Q<sub>2</sub> a carga na associação de capacitores de C<sub>6</sub> à C<sub>0</sub>. Como não ocorreu descarga durante o chaveamento, tem-se que:

$$Q_{TOTAL} = Q_1 + Q_2 \tag{13}$$

Assim, substituindo (10), (11) e (12) em (13):

$$2C \cdot (V_{REF} - V_{IN}) = C \cdot (V_{COMP} - V_{REF}) + C \cdot (V_{COMP})$$

$$\tag{14}$$

Resultando em uma tensão V<sub>COMP</sub>- de:

$$V_{COMP-} = V_{REF} - V_{IN} + \frac{V_{REF}}{2}$$

(15)

O comparador então realiza a comparação entre seus terminais onde estão conectados V<sub>COMP</sub>- e V<sub>REF</sub>. Ou seja, é realizada a seguinte comparação:

$$V_{REF} > V_{REF} - V_{IN} + \frac{V_{REF}}{2} \tag{16}$$

Que simplificada resulta em  $V_{IN} > V_{REF}/2$ , ou seja, a tensão de entrada amostrada é comparada com metade da tensão de referência. Caso a comparação seja verdadeira, a saída do comparador irá para um nível lógico alto, caso contrário um nível lógico baixo.

O valor da saída do comparador representará o bit mais significativo da conversão, que será então armazenado. Caso este valor seja de nível alto, a chave

S<sub>7</sub> será mantida conectada ao barramento, caso contrário a chave conectará o capacitor ao *ground*.

Depois de completada esta fase de redistribuição de carga, o processo de redistribuição é feito novamente, desta vez com a chave S<sub>6</sub>, que conectará o capacitor ao barramento, gerando um novo divisor capacitivo.

Este divisor depende do resultado da comparação anterior, portanto há dois casos possíveis:

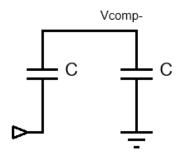

- Caso o resultado da comparação tenha sido nível lógico alto, fazendo com que a chave S<sub>7</sub> permanecesse conectada ao barramento, o divisor seria entre associação de C<sub>7</sub> e C<sub>6</sub> e a associação entre os capacitores C<sub>5</sub> até C<sub>0</sub>. Desta forma, o circuito equivalente seria o apresentado na Figura 19.

Figura 19 - Banco de capacitores equivalente após a segunda redistribuição, caso o resultado da comparação anterior tenha sido nível lógico alto

As cargas Q<sub>1</sub> e Q<sub>2</sub> seriam:

$$Q_1 = \frac{3C}{2} \cdot (V_{COMP} - V_{REF}) \tag{17}$$

$$Q_2 = \frac{C}{2} \cdot (V_{COMP-}) \tag{18}$$

Desta forma, como Q<sub>TOTAL</sub> permanece a mesma, substituindo (10), (17) e (18) em (13), tem-se que:

$$2C \cdot (V_{REF} - V_{IN}) = \frac{3C}{2} \cdot (V_{COMP-} - V_{REF}) + \frac{C}{2} \cdot (V_{COMP-})$$

(19)

A tensão V<sub>COMP-</sub>, então, seria dada por:

$$V_{COMP-} = V_{REF} - V_{IN} + \frac{V_{REF}}{2} + \frac{V_{REF}}{4}$$

(20)

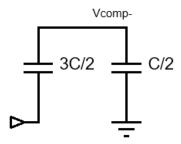

- Caso o resultado da comparação tenha sido nível lógico baixo, fazendo com que a chave S<sub>7</sub> fosse conectada ao *ground*, o divisor seria entre C<sub>6</sub> e a associação de

todos os outros capacitores. Desta forma, o circuito equivalente seria o apresentado na Figura 20.

Figura 20 - Banco de capacitores equivalente após a segunda redistribuição, caso o resultado da comparação anterior tenha sido nível lógico baixo

As cargas Q<sub>1</sub> e Q<sub>2</sub> seriam:

$$Q_1 = \frac{C}{2} \cdot (V_{COMP} - V_{REF}) \tag{21}$$

$$Q_2 = \frac{3C}{2} \cdot (V_{COMP}) \tag{22}$$

De forma similar ao caso anterior, substituindo (10), (21) e (22) em (13), temse que:

$$2C \cdot (V_{REF} - V_{IN}) = \frac{C}{2} \cdot (V_{COMP-} - V_{REF}) + \frac{3C}{2} \cdot (V_{COMP-})$$

(23)

A tensão V<sub>COMP-</sub>, então, seria dada por:

$$V_{COMP-} = V_{REF} - V_{IN} + \frac{V_{REF}}{4}$$

(24)

Assim, analisando (20) e (24), considerando b<sub>7</sub> como o valor do bit mais significativo da conversão armazenado anteriormente, temos que a tensão V<sub>COMP</sub>-será:

$$V_{COMP-} = V_{REF} - V_{IN} + b_7 \frac{V_{REF}}{2} + \frac{V_{REF}}{4}$$

(25)

Após esta redistribuição uma nova comparação é feita. O resultado da conversão será o segundo bit mais significativo e decidirá se a chave  $S_6$  é mantida no barramento ou conectada ao *ground*. Este processo se repete até todos os bits serem determinados.

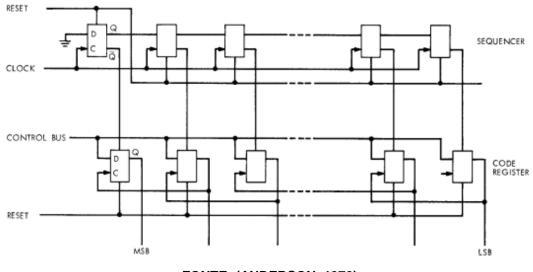

A lógica de controle é necessária para realizar o algoritmo de busca binária para achar o nível de quantização que expressa a entrada analógica. O circuito clássico apresentado por Anderson (ANDERSON, 1972), mostrado na Figura 21, é amplamente utilizado.

A parte de cima é conhecida como sequenciador, consistindo em um registrador de deslocamento que propaga o sinal lógico alto na saída inversora do primeiro *flip-flop* até o último, ou seja, a cada ciclo de relógio um *flip-flop* terá o sinal alto na saída inversora. A saída de cada um desses *flip-flops* é conectada a um *flip-flop* do circuito de baixo. Quando a mesma é acionada, o flip-flop correspondente será atualizado de acordo com a saída do comparador (ANDERSON, 1972).

Figura 21 - Lógica de controle para um conversor de N bit

FONTE: (ANDERSON, 1972)

As saídas dos flip-flops de baixo agem como sinais de controle para as chaves do banco de capacitores. Os valores dos registradores ao final de cada ciclo de conversão representam o sinal digital.

Uma das desvantagens desta topologia é que para cada bit adicionado ao conversor, o valor da capacitância que deverá ser adicionada é o dobro da anterior. Assim, para otimizar à área equivalente do banco, escolhe-se o capacitor da chave So de forma a possuir a menor capacitância de acordo com a tecnologia utilizada. Entretanto, para um conversor de 8 bits, o valor do capacitor conectado em So deverá ser 128 vezes maior do que o de So. Então, devido ao fato de a capacitância possuir

uma relação proporcional com a área das placas do capacitor, em um capacitor de placas paralelas, por exemplo, dada por:

$$C = \frac{\varepsilon A}{d} \tag{26}$$

Onde A é a área do capacitor,  $\varepsilon$  a permissividade do meio isolante e d a distância entre as placas. A área do capacitor em S<sub>7</sub> será muito maior que a área do capacitor em S<sub>0</sub>, e a cada novo capacitor adicionado a área aumentará ainda mais. Desta maneira, para cada bit extra que for inserido, de forma a aumentar a resolução do conversor, ocorre um aumento significativo na área do banco de capacitores, demandando uma área considerável no *chip*.

Existem algumas técnicas possíveis de serem utilizadas para reduzir a área total do banco de capacitores. Uma delas é a técnica de repartir o arranjo de capacitores. Para isso, um capacitor atenuador é acrescentado, obtendo-se um arranjo responsável pela parte menos significativa (LSB) e um pela parte mais significativa (MSB) (BAKER, 2008).

Um exemplo de arranjo dividido para um conversor de 6 bits é mostrado na Figura 22. Note que o bit menos significativo, D<sub>0</sub>, agora corresponde à chave mais à esquerda, já o mais significativo, D<sub>5</sub>, corresponde à chave mais à direita.

Figura 22 - Topologia para um conversor SAR de 6 bits com capacitor atenuador

**FONTE: (BAKER, 2008)**

Pode-se observar que os valores das capacitâncias diminuíram em relação a topologia original, pois para um conversor de 6 bits o capacitor associado ao bit mais

significativo seria 32 vezes maior que o associado ao bit menos significativo. Através desta técnica ele é somente 4 vezes maior.

Para o funcionamento desta técnica, o valor do capacitor de atenuação deverá ser obtido por:

$$C_{ATENUAÇÃO} = \frac{soma\ do\ arranjo\ de\ capacitores\ LSB}{soma\ do\ arranjo\ de\ capacitores\ MSB} \cdot C \tag{27}$$

#### 2.8 Conversores Cíclicos

A topologia de desenvolvimento e estudo deste trabalho utiliza uma arquitetura baseada em um conversor de 1 bit. Cada bit é convertido analisando o resíduo da conversão do estágio anterior de maneira similar à do conversor *Pipeline* e *Flash* em dois passos. Nesta arquitetura, porém, o resultado é obtido através de uma abordagem sequencial utilizando o mesmo circuito repetidamente para executar a operação de cada um dos estágios.

Ao longo do desenvolvimento do trabalho, estudou-se a nova topologia e também buscou-se analisar a viabilidade desta arquitetura. Contudo, ao findar do trabalho, descobriu-se que esta técnica já havia sido estudada e já era utilizada por outras topologias, nos denominados conversores cíclicos.

Os conversores cíclicos quando comparados com as arquiteturas do tipo *Pipeline* são melhores em relação à área ocupada, porém, possuem uma menor taxa de conversão (PUPALLA, 2012).

Nestes conversores, cada bit é determinado comparando a tensão de entrada com a referência e o resíduo é gerado multiplicando por dois a diferença entre a entrada e o equivalente analógico da saída digital (HASAN et al., 2002).

A Figura 23 apresenta um diagrama de blocos genérico para um conversor cíclico.

V<sub>res</sub>(i)

S/H

A

D

A

N bits

Figura 23 - Diagrama de blocos genérico para um conversor cíclico

FONTE: (HASAN et al., 2002)

O bloco inicial é o de amostragem e retenção, seguido pelo conversor A/D. Após a conversão, o valor digital é armazenado no registrador e convertido analogicamente através de um conversor D/A. O sinal digital convertido para analógico é então subtraído do sinal original e recebe um ganho de dois. Em seguida, esta tensão residual é utilizada na realimentação do circuito.

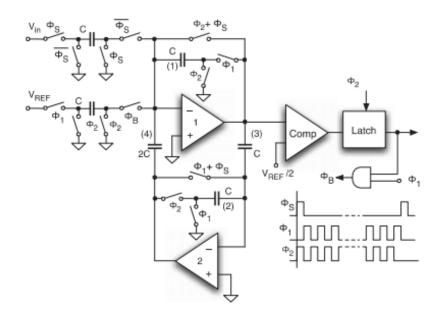

Um exemplo de topologia que utiliza esta técnica pode ser observado na Figura 24.

Figura 24 - Circuito de um conversor cíclico com capacitor chaveado

**FONTE: (MALOBERTI, 2007)**

Conforme Maloberti (MALOBERTI, 2007), esta topologia utiliza dois amplificadores operacionais em um *loop* de realimentação fechada. A conversão começa com a fase de amostragem  $\Phi_S$  que é utilizada para pré-carregar um dos capacitores chaveados com a tensão de entrada. Além disso,  $\Phi_S$  também torna o circuito livre dos erros de *offset*, visto que durante essa fase as capacitâncias são précarregadas com a tensão de *offset*.

O próximo período  $\Phi_1$  é utilizado para injetar o sinal de entrada no *loop*. A configuração não-inversora e o ganho unitário fazem com que a tensão de entrada seja reproduzida na saída do primeiro amplificador e armazenada na capacitância (3). O bit é determinado através da comparação deste valor com  $V_{REF}/2$ .

O segundo amplificador carrega a capacitância (4) que possui o dobro do valor da capacitância unitária, o que acaba gerando uma multiplicação por dois no sinal de entrada. Enquanto isso, o outro capacitor chaveado de entrada injeta a carga  $CV_{REF}$  no circuito se  $\Phi_B$ , resultado da comparação, estiver ativa. Assim, a saída do primeiro amplificador será:

$$V = 2V_{IN} - V_{REF} = 2\left(V_{IN} - \frac{V_{REF}}{2}\right) \tag{28}$$

Esta tensão é equivalente ao resíduo do primeiro estágio multiplicado por dois. O próximo ciclo opera da mesma forma para determinar o próximo bit e o processo continua até todos os bits serem definidos.

Apesar desta arquitetura já ser conhecida e estudada, a nova topologia proposta utiliza conceitos diferentes baseados neste estilo de arquitetura e, portanto, deve ser analisada de forma a verificar sua viabilidade.

#### 3 Desenvolvimento da nova topologia para o conversor SAR

#### 3.1 Parte Analógica

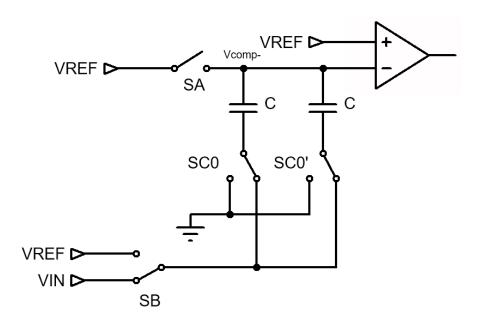

O funcionamento da topologia proposta baseia-se no princípio de realimentação demonstrado anteriormente. O processo inicial pode ser representado por um conversor de redistribuição de carga de 1 bit, conforme Figura 25.

Figura 25 - Topologia básica para um conversor SAR de 1 bit

Esse processo de conversão será bastante similar ao da topologia original, seguindo as seguintes etapas:

#### 1) Amostragem:

Ocorre de maneira igual ao processo de amostragem original. Inicia-se com as chaves  $S_{C0}$  e  $S_{C0}$  conectando os capacitores ao barramento comum. A chave superior  $S_A$  conecta  $V_{REF}$  e a chave do barramento  $S_B$  é posicionada em  $V_{IN}$ . O banco de capacitores é carregado com carga  $Q=2C\cdot (V_{REF}-V_{IN})$ .

### 2) Retenção:

A chave  $S_A$  desconecta  $V_{REF}$  e as chaves dos capacitores conectam os mesmos ao *ground*. Como não há caminho para a descarga dos capacitores durante o chaveamento, a carga permanecerá e a tensão  $V_{COMP}$ - será  $V_{REF} - V_{IN}$ .

#### 3) Redistribuição de carga:

A chave S<sub>B</sub> conecta-se à V<sub>REF</sub> e a chave S<sub>1</sub> conecta o capacitor ao barramento, formando o mesmo divisor capacitivo original. Este divisor capacitivo com dois capacitores de mesmo valor, conforme visto anteriormente, resulta em um aumento da tensão V<sub>COMP</sub>- em V<sub>REF</sub>/2. Resultando em uma tensão V<sub>COMP</sub>- de:

$$V_{COMP-} = V_{REF} - V_{IN} + \frac{V_{REF}}{2}$$

(29)

O comparador, da mesma forma que originalmente, compara  $V_{IN} > V_{REF}/2$ , gera na sua saída o valor do bit mais significativo (b<sub>N</sub>) e mantém a chave do capacitor C<sub>1</sub> conectada ao barramento ou conecta a mesma ao *ground*. Fazendo com que a tensão  $V_{COMP}$ - seja:

$$V_{COMP-} = V_{REF} - V_{IN} + b_N \frac{V_{REF}}{2} \tag{30}$$

O segundo processo é o da realimentação. Para isso, nesta etapa a tensão V<sub>COMP-</sub> passará por um buffer, sendo agora chamada de V<sub>BUFFER</sub>, e irá para o dobrador de tensão apresentado na Figura 26.

Este dobrador, através de chaveamento, irá obter o resíduo da conversão, a parte que ainda não foi convertida, e utilizá-lo para realimentar o circuito e realizar uma nova conversão para os próximos bits.

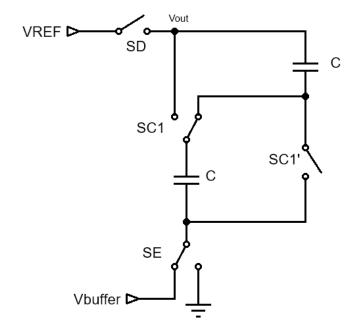

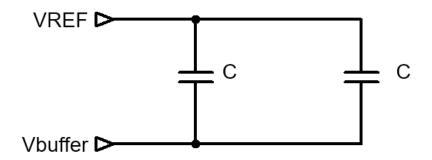

Figura 26 - Topologia desenvolvida para o dobrador da tensão residual

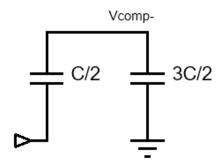

De forma a obter o resíduo, se faz necessário remover a parcela inicial de  $V_{REF}$  do valor da tensão  $V_{COMP}$ . Para isso, inicialmente a chave  $S_D$  será fechada conectando  $V_{REF}$  à  $V_{OUT}$ , a chave  $S_{C1}$  conectará o capacitor à  $V_{OUT}$ , a chave  $S_{C1}$  será fechada e a chave  $S_E$  se conectará à  $V_{BUFFER}$ . Assim, os dois capacitores estarão em paralelo, conforme a Figura 27.

Figura 27 - Topologia do dobrador na etapa de amostragem

Dessa forma, o banco será carregado com  $Q=2C\cdot (V_{REF}-V_{BUFFER})$ . Após isso, a chave  $S_D$  é aberta e  $S_E$  conecta-se ao *ground*. Como não há caminho para a descarga dos capacitores durante o chaveamento, a carga permanecerá a

mesma e a tensão V<sub>OUT</sub> será V<sub>REF</sub> – V<sub>BUFFER</sub>. Como V<sub>BUFFER</sub> é a tensão de V<sub>COMP</sub>- do conversor, a tensão de saída será:

$$V_{OUT} = V_{REF} - V_{BUFFER} = V_{REF} - \left(V_{REF} - V_{IN} + b_N \frac{V_{REF}}{2}\right)$$

(31)

Ou seja:

$$V_{OUT} = V_{IN} - b_N \frac{V_{REF}}{2} \tag{32}$$

O banco estará carregado com uma carga de:

$$Q_{TOTAL} = 2C \cdot (V_{IN} - b_N \frac{V_{REF}}{2}) \tag{33}$$

A seguir, a chave S<sub>C1</sub> conectará um capacitor ao outro e a chave S<sub>C1</sub> será aberta. Desta forma, os dois capacitores estarão em série, conforme a Figura 28.

Figura 28 - Topologia do dobrador na etapa da dobra de tensão

Após o chaveamento, a carga de cada um dos capacitores será:

$$Q_1 = C \cdot (V_X) \tag{34}$$

$$Q_2 = C \cdot (V_{OUT} - V_X) \tag{35}$$

Como não ocorreu descarga durante o chaveamento, a soma das cargas permanece a mesma. Portanto:

$$2C \cdot \left(V_{IN} - b_N \frac{V_{REF}}{2}\right) = C \cdot (V_X) + C \cdot (V_{OUT} - V_X)$$

(36)

Simplificando:

$$V_{OUT} = 2\left(V_{IN} - b_N \frac{V_{REF}}{2}\right) \tag{37}$$

Então, a tensão de saída do dobrador será o dobro da tensão residual. Esta tensão, após passar por um buffer, será utilizada como a tensão de entrada para as futuras conversões. A tensão deve ser dobrada, pois da mesma forma que nos conversores pipeline, flash em dois passos e cíclicos, será possível realizar a próxima comparação com o mesmo banco de capacitores e a mesma tensão de referência utilizada durante o primeiro ciclo.

Após esta etapa o ciclo inicia-se novamente, desta vez com a tensão residual dobrada sendo a nova tensão de entrada. O número de repetições deste ciclo será equivalente ao número de bits desejados do conversor.

Assim, quando o processo de amostragem e retenção ocorrer e o banco for carregado com  $V_{REF}$  –  $V_{IN}$ , a tensão de entrada será  $2V_{IN}$  +  $b_NV_{REF}$ . Dessa forma, a carga no banco de capacitores será:

$$Q_{TOTAL} = 2C \cdot (V_{REF} - 2V_{IN} + b_N V_{REF}) \tag{38}$$

Após o chaveamento e a redistribuição da carga igual à anterior, a carga de cada um dos lados do divisor será de:

$$Q_1 = C \cdot (V_{COMP} - V_{REF}) \tag{39}$$

$$Q_2 = C \cdot (V_{COMP}) \tag{40}$$

Como não ocorreu descarga durante o chaveamento, tem-se que:

$$2C \cdot (V_{REF} - 2V_{IN} + b_N V_{REF}) = C \cdot (V_{COMP} - V_{REF}) + C \cdot (V_{COMP})$$

(41)

Resultando em uma tensão VCOMP- de:

$$V_{COMP-} = V_{REF} - 2V_{IN} + b_N V_{REF} + \frac{V_{REF}}{2}$$

(42)

O comparador então realiza a comparação entre seus terminais, onde estão conectados V<sub>COMP</sub>- e V<sub>REF</sub>:

$$V_{REF} > V_{REF} - 2V_{IN} + b_N V_{REF} + \frac{V_{REF}}{2}$$

(43)

Que simplificada resulta em:

$$V_{IN} > \frac{b_N V_{REF}}{2} + \frac{V_{REF}}{4} \tag{44}$$

Ou seja, realiza a comparação se a tensão de entrada é maior que 0,25V<sub>REF</sub> ou 0,75V<sub>REF</sub>.

Dessa forma, o circuito que representa a parte analógica do conversor é o mostrado na Figura 29.

Figura 29 - Circuito da parte analógica do conversor

A seguir, um exemplo da conversão para um conversor de 2 bits com valores para facilitar o entendimento. Considerando  $V_{REF} = 1,2 \text{ V e } V_{IN} = 0,8 \text{ V}$ , temos o seguinte:

No primeiro ciclo será feita a amostragem e retenção, carregando o banco com  $V_{REF} - V_{IN}$ , neste caso 0,4 V. Após a redistribuição de carga, a tensão no barramento será  $V_{REF} - V_{IN} + V_{REF}/2$ , neste caso 1 V. A comparação com os 1,2 V de  $V_{REF}$  será feita e a saída do comparador estará em nível lógico alto.

Este nível lógico alto representa que a tensão de entrada é maior que a metade da tensão de referência. Devido a isto, a chave do capacitor C<sub>1</sub> permanecerá conectada ao barramento e o bit mais significativo será 1.

Neste momento é preciso utilizar o resíduo desta conversão, ou seja, a diferença entre o valor da entrada e o valor já convertido. Para isso, remove-se a parcela de  $V_{REF}$  da tensão  $V_{COMP-}$ , neste caso 1,2 V – 1 V = 0,2 V, e realimenta-se o circuito. Entretanto, primeiramente é necessário dobrar a tensão residual.

Com  $V_{IN} = 0,4$  V no novo ciclo,  $V_{REF} - V_{IN} + V_{REF}/2$  será 1,4 V. A comparação com os 1,2 V de  $V_{REF}$  será feita e a saída do comparador estará em nível lógico baixo, representando que o próximo bit será 0. Desta forma, a chave relacionada ao capacitor

$C_1$  retornaria ao *ground*, fazendo com que  $V_{COMP}$  seja  $V_{REF} - V_{IN} = 0.8$  V. Assim, a nova tensão residual seria 1.2 V - 0.8 V = 0.4 V.

Considerando os dois bits calculados, tem-se 0b10 na saída digital. O valor da conversão para 2 bits é dado por:

$$V_{2bits} = \frac{V_{REF}}{2^2} \cdot (b_1 \cdot 2^1 + b_0 \cdot 2^0) \tag{45}$$

Logo, para o exemplo acima:

$$V_{2bits} = \frac{1,2V}{4} \cdot (1 \cdot 2^1 + 0 \cdot 2^0) = 0,6 V$$

(46)

Este processo poderá continuar para quantos bits forem necessários, aproximando-se cada vez mais do valor real da entrada.

A capacitância total do banco é diretamente dependente do número de capacitores necessários e também do valor da capacitância unitária. Para reduzir o consumo de potência, o valor da capacitância unitária deverá ser mantido o menor possível. Entretanto, o tamanho dos capacitores deve suprir os requisitos de ruído, as propriedades de casamento de capacitância e também as regras do processo de manufatura (DORNELAS, 2018).

Para o processo de manufatura CMOS 130nm, para citar um exemplo de processo utilizado no desenvolvimento destes conversores, o menor capacitor metalisolante-metal disponível é de 60 fF (DORNELAS, 2018). Essa capacitância pode ser reduzida através do uso de dois desses capacitores em série de forma à deixa-la em 30 fF. Como o objetivo do projeto é a redução de área, esta estratégia não se torna viável pois utiliza dois capacitores, portanto o circuito foi desenvolvido utilizando capacitâncias de 60 fF.

## 3.2 Lógica de Controle Digital

O sistema de controle das chaves presentes no conversor A/D por redistribuição de carga é realizado por uma máquina de estados principal e mais alguns elementos como portas lógicas e flip-flops utilizados para simplificar a implementação. Este sistema digital de controle não é o principal foco do trabalho, por

isso foi desenvolvido de maneira simplificada baseado nas etapas demonstradas do conversor.

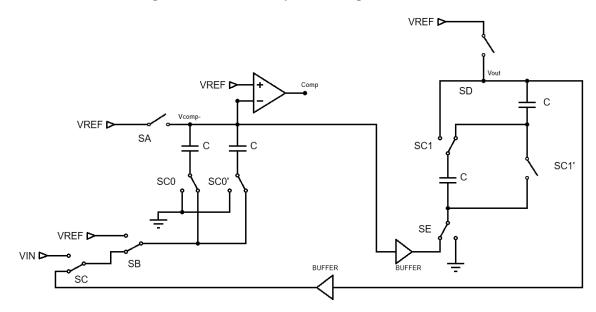

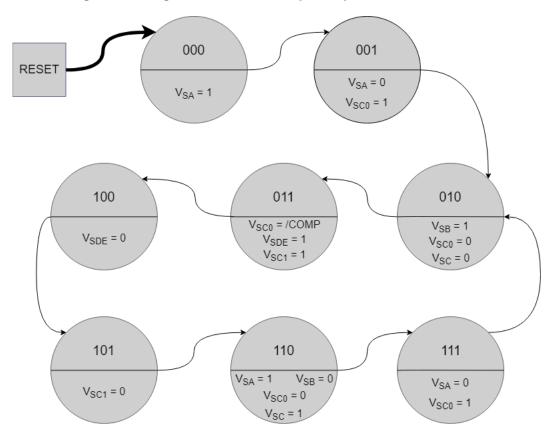

A máquina de estados principal é responsável pelo controle das chaves e também controla os sinais dos N flip-flops utilizados para armazenar o valor digital convertido. A partir da análise do chaveamento necessário, determinou-se os sinais de controle necessários para controlar as chaves, especificados na Tabela 2, e elaborou-se o diagrama de estados demostrado na Figura 30.

Tabela 2 - Relação entre os sinais de controle e chaves controladas

| 3                 |                 |

|-------------------|-----------------|

| Sinal de controle | Chave           |

| Vsa               | Sa e Sco        |

| VsB               | SB              |

| Vsc               | Sc              |

| Vsc <sub>0</sub>  | Sc <sub>0</sub> |

| Vsde              | SD e SE         |

| Vsc <sub>1</sub>  | Sc1 e Sc1'      |

Para o controle da chave  $S_{C0}$  foi utilizado um flip-flop JK, pois o sinal de controle necessitava manter-se constante ao longo de algumas bordas do relógio. O flip-flop JK foi utilizado, pois quando as duas entradas estiverem em nível lógico baixo, o valor do próximo estado será o valor do estado atual, mantendo-se constante, conforme apresentado na Tabela 3.

Tabela 3 - Tabela verdade do flip-flop JK

| Operação do Flip Flop JK |   |       |           |  |  |  |  |

|--------------------------|---|-------|-----------|--|--|--|--|

| J                        | K | Qpróx | Descrição |  |  |  |  |

| 0                        | 0 | Q     | Mantém    |  |  |  |  |

| 0                        | 1 | 0     | Reseta    |  |  |  |  |

| 1                        | 0 | 1     | Seta      |  |  |  |  |

| 1                        | 1 | /Q    | Alterna   |  |  |  |  |

A partir do diagrama elaborado, foram feitas tabelas verdades para a lógica de próximo estado e sinais de saída da máquina de estados. Em seguida, foram obtidas as expressões lógicas para implementação do circuito.

Figura 30 - Diagrama de estados da parte operativa do conversor

As expressões para a lógica de próximo estado obtidas foram as seguintes:

$$D_2 = Q_2 \overline{Q_1} + Q_2 \overline{Q_0} + \overline{Q_2} Q_1 Q_0 \tag{47}$$

$$D_1 = Q_1 \overline{Q_0} + \overline{Q_1} Q_0 + Q_2 Q_1 \tag{48}$$

$$D_1 = \overline{Q_0} \tag{49}$$

As expressões para as saídas da máquina de estados foram as seguintes:

$$V_{SA} = \overline{Q_2} \, \overline{Q_1} \, \overline{Q_0} + Q_2 Q_1 \overline{Q_0} \tag{50}$$

$$V_{SB} = Q_2 \overline{Q_1} + \overline{Q_2} Q_1 \tag{51}$$

$$V_{SC} = Q_2 Q_1 \tag{52}$$

$$V_{SDE} = \overline{Q_2} Q_1 Q_0 \tag{53}$$

$$V_{SC1} = Q_2 \overline{Q_1} \overline{Q_0} + \overline{Q_2} Q_1 Q_0 \tag{54}$$

$$V_{SC0\_J} = \overline{Q_2} \, \overline{Q_1} \, \overline{Q_0} + Q_2 Q_1 \overline{Q_0} + \overline{Q_2} Q_1 \overline{Q_0} \, \overline{COMP}$$

(55)

$$V_{SC0\_K} = \overline{Q_1}Q_0 + Q_2Q_0 + \overline{Q_2}Q_1\overline{Q_0}\overline{COMP}$$

(56)

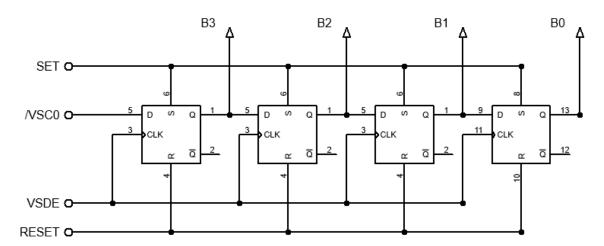

O sinal V<sub>SC0</sub> que controla a chave S<sub>C0</sub> contém a informação inversa sobre o resultado da comparação ao longo da conversão. Para que a leitura do valor digital da conversão possa ser obtida, é necessário armazenar os bits em registradores. Dessa forma, foi desenvolvido o sequenciador da Figura 31 com a entrada sendo o sinal V<sub>SC0</sub> negado.

O sinal V<sub>SDE</sub> foi utilizado como relógio do sequenciador, pois o mesmo é ativado logo após a comparação entre V<sub>COMP</sub> e V<sub>REF</sub> ser realizada. Desta forma, após cada comparação o valor obtido é transmitido para o flip-flop seguinte. A Figura 31 mostra o exemplo de um sequenciador para um conversor de 4 bits. Para cada bit extra desejado, deverá ser adicionado um novo flip-flop.

Figura 31 - Sequenciador para um conversor de 4 bits

### 4 Simulações

#### 4.1 MATLAB

Inicialmente foi utilizado o software MATLAB para avaliar se matematicamente o funcionamento do circuito seria possível. Foi desenvolvido um código simples baseado nas equações de cargas descritas previamente neste trabalho. No código, através do cálculo das cargas e tensões nos capacitores do banco, o valor da entrada analógica é convertido em um valor digital com o número de bits desejados.

#### 4.2 LTSPICE

O software seguinte utilizado foi o LTSPICE. Este software é um simulador que mescla a análise de circuitos tanto através de desenho como através de arquivos de texto (*netlist*) contendo uma descrição dos componentes e conexões.

O circuito sobre o qual foram feitas as simulações, contém a parte analógica envolvendo os capacitores e as chaves, e também apresenta a parte digital de controle das chaves e armazenamento da saída digital.

Como este trabalho tem por objetivo a análise do funcionamento da nova topologia e a lógica de controle digital não é o principal foco, algumas não idealidades do circuito digital foram ignoradas. Dessa forma, o circuito digital foi descrito através de componentes ideais considerando atrasos nas portas lógicas de 1 nanossegundo.

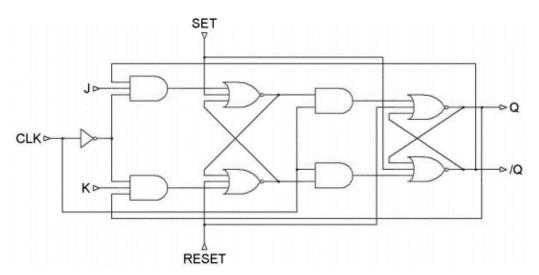

Os flip-flops utilizados neste projeto foram descritos utilizando portas lógicas. O flip-flop descrito foi o do tipo JK e pode ser observado na Figura 32. Este flip-flop, além das entradas J, K e CLK, possui duas entradas Set e Reset assíncronas, isto é, independentes da borda do relógio.

Figura 32 - Flip-flop do tipo JK descrito através das portas lógicas

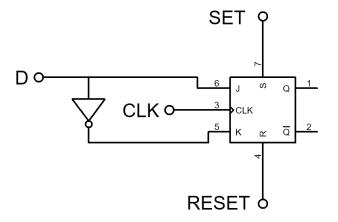

Para a descrição dos flip-flops do tipo D, foi utilizado o flip-flop JK com um inversor conectado entre as entradas J e K e a entrada D conectada na entrada J, conforme a Figura 33.

Figura 33 - Flip-flop do tipo D modelado a partir de um flip-flop do tipo JK

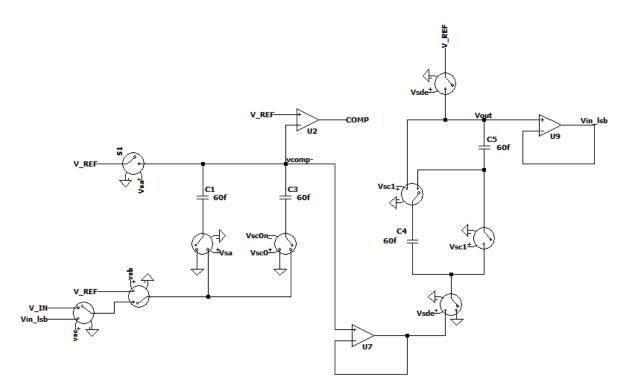

Após a descrição dos flip-flops ser realizada, foi modelado no LTSPICE o circuito analógico mostrado anteriormente. O circuito modelado está apresentado na Figura 34.

Figura 34 - Topologia desenvolvida no LTSPICE

Em seguida, foram descritos através de arquivo de texto a máquina de estados principal, a lógica de próximo estado e a lógica dos sinais de saída, utilizando portas lógicas. Por fim, também através de texto, foi descrito o sequenciador para 8 bits para armazenar a saída digital. A descrição completa do circuito pode ser observada no *netlist* apresentado no Apêndice 1 do trabalho.

### 5 Resultados e Discussão

## 5.1 Simulações do Circuito de Controle das Chaves

Em um primeiro momento, pode-se analisar os sinais obtidos no circuito digital de controle. Posteriormente, será feita a análise da parte analógica, onde serão observados os sinais nos capacitores.

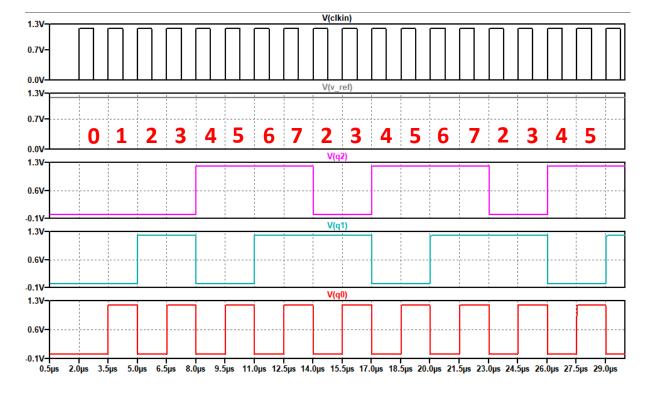

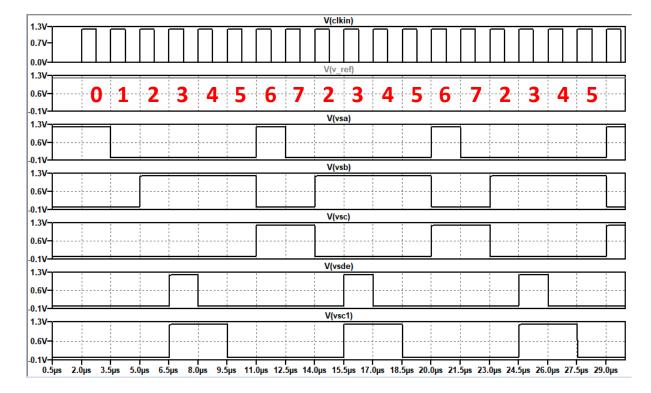

Na Figura 35, estão apresentadas, além do sinal de relógio, as saídas dos flipflops da máquina de estados principal de forma a observar a lógica de próximo estado. Os números em vermelho representam o estado equivalente aos sinais Q0, Q1 e Q2.

Figura 35 - Sinais de saída dos flip-flops da máquina de estados principal

Pode-se observar que os estados correspondem corretamente aos valores previstos pelo diagrama da Figura 30.

Na Figura 36, observa-se os sinais de controle das chaves da máquina de estados principal. Na figura não é apresentado o sinal da chave V<sub>SC0</sub>, pois o mesmo depende do resultado do comparador.

Figura 36 - Sinais de controle das chaves

Observa-se, na Figura 36, o correto funcionamento da máquina de estados. No estado 0, somente  $V_{SA}$  começa como nível alto. Na borda seguinte do relógio,  $V_{SA}$  é zerada e no estado 2  $V_{SB}$  é ativado.

Em seguida, V<sub>SDE</sub> e V<sub>SC1</sub> são ativados em conjunto no estado 3 e nos dois estados que prosseguem V<sub>SDE</sub> e V<sub>SC1</sub> são zerados respectivamente um em cada estado.

No estado 6, V<sub>SA</sub> e V<sub>SC</sub> são ativados e V<sub>SB</sub> é zerado. No estado 7, V<sub>SA</sub> é zerado e o ciclo retorna ao estado 2, onde V<sub>SB</sub> será ativado e V<sub>SC</sub> zerado.

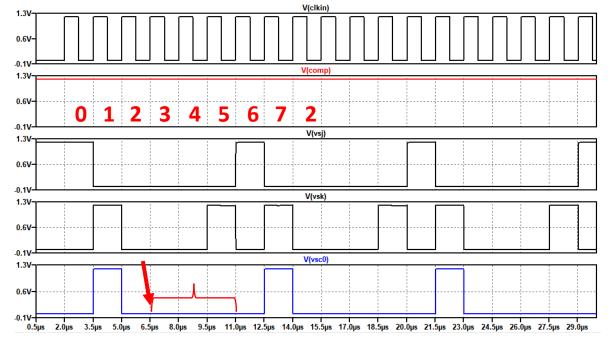

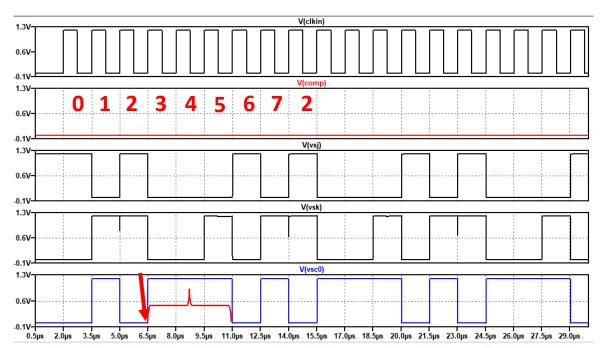

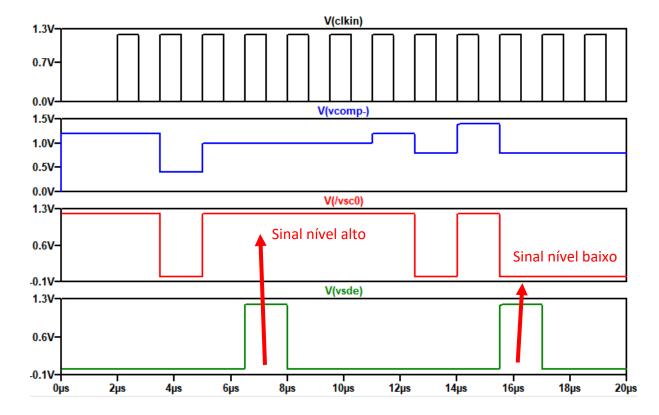

Nas Figuras 37 e 38, observa-se os sinais  $V_{SC0\_J}$  e  $V_{SC0\_K}$  que estão conectados em um flip-flop JK cuja saída é o sinal  $V_{SC0}$ . Os sinais  $V_{SC0\_J}$  e  $V_{SC0\_K}$  dependem do valor do sinal do comparador. Devido a isso, na Figura 37 é mostrado o sinal  $V_{SC0}$  considerando-se o sinal do comparador sempre em nível lógico alto.

Dessa forma, após a redistribuição de carga e chaveamento de S<sub>C0</sub> no estado 2, como o comparador apresenta um nível lógico alto, V<sub>SC0\_J</sub> e V<sub>SC0\_K</sub> estarão em nível lógico baixo. Devido a isso, a chave deverá manter sua posição pelos próximos três ciclos de relógio. Esse comportamento está destacado na Figura 37.

Figura 37 - Sinais de controle da chave S<sub>CO</sub> para comparador em nível alto

Na Figura 38, é mostrado o sinal V<sub>SC0</sub> considerando-se o sinal do comparador sempre em nível lógico baixo. Dessa forma, após a redistribuição de carga e chaveamento da chave S<sub>C0</sub> no estado 2, como o comparador apresenta um nível lógico baixo, V<sub>SC0\_J</sub> e V<sub>SC0\_K</sub> estarão em nível lógico alto. Devido a isso a chave deverá trocar sua posição e manter-se assim pelos três próximos ciclos de relógio. Esse comportamento está destacado na Figura 38.

Figura 38 - Sinais de controle da chave S<sub>CO</sub> para comparador em nível baixo

Pode-se observar, nas Figuras 37 e 38, que no estado 1  $V_{SC0}$  é ativado, sendo desativado no estado seguinte. No estado 3, local destacado pelas setas vermelhas, o sinal  $V_{SC0}$  deverá ser o contrário do resultado da comparação. Esse valor é mantido durante outros dois estados, período destacado em vermelho, e depois zerado.

## 5.2 Simulações dos Sinais do Circuito Analógico

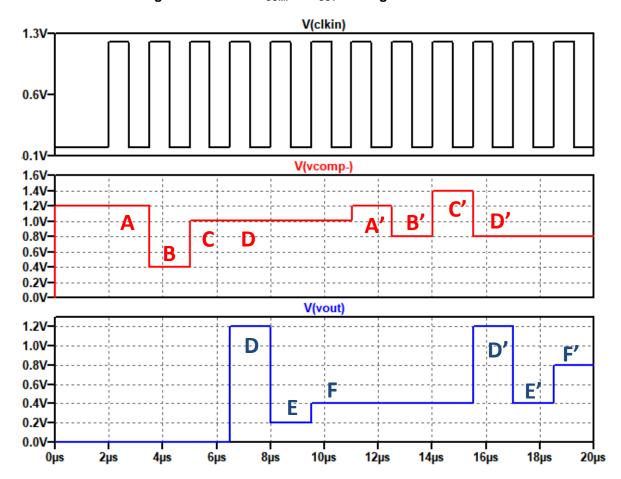

Nesta seção, é feita a análise da parte analógica do circuito utilizando os sinais de controle mostrados anteriormente. São observados os sinais do barramento superior V<sub>COMP</sub>- e do dobrador de tensão V<sub>OUT</sub>.

Para realizar esta simulação foi utilizada uma tensão analógica de entrada  $V_{IN}$  com o valor de 0,8 V e a tensão de referência  $V_{REF}$  de 1,2 V, mesmos valores do exemplo demonstrado previamente neste trabalho. A Figura 39 apresenta os sinais  $V_{COMP}$  e  $V_{OUT}$  juntamente com o relógio.

Figura 39 - Sinais V<sub>COMP-</sub> e V<sub>OUT</sub> ao longo da conversão

Percebe-se, na Figura 39, que em um primeiro momento, destacado com a letra **A**, o valor do sinal V<sub>COMP-</sub> é de 1,2 V, ou seja, é o valor V<sub>REF</sub> conforme esperado. Esse é o estado no qual ocorre a carga nos capacitores.

Na borda de subida seguinte do relógio, estado  $\bf B$ , a chave  $S_A$  desconecta  $V_{REF}$  do circuito e as chaves dos capacitores conectam os mesmos ao *ground*. Portanto, conforme demonstrado previamente,  $V_{COMP}$ - será  $V_{REF}$  –  $V_{IN}$ , nesse caso 0,4 V.

No estado mostrado em  $\mathbf{C}$ , ocorre a redistribuição de carga. A tensão no barramento será acrescentada com  $V_{REF}/2$ , neste caso colocando o valor em 1 V. A comparação com os 1,2 V de  $V_{REF}$  será feita e a saída do comparador estará em nível lógico alto. Devido a isto, no estado  $\mathbf{D}$  a chave do capacitor  $S_{C0}$  permanecerá conectada ao barramento e a tensão permanecerá em 1 V até o próximo ciclo de conversão, representado por  $\mathbf{A}$ '.

Ao mesmo tempo em que a chave S<sub>C0</sub> é mantida, o banco de capacitores do dobrador de tensão será carregado com V<sub>REF</sub> – V<sub>COMP-</sub> e o valor da tensão V<sub>OUT</sub> será 1,2 V. No estado **E**, a chave S<sub>E</sub> conectará os capacitores ao *ground* e a tensão V<sub>OUT</sub> será V<sub>REF</sub> – V<sub>COMP-</sub>, nesse caso 0,2 V. No estado **F**, ocorre a dobra da tensão V<sub>OUT</sub>, assumindo o valor de 0,4 V e mantendo-se assim até a nova etapa de dobra de tensão.

Após esta primeira conversão, o valor de 0,4 V de  $V_{OUT}$  é utilizado como entrada e o ciclo recomeça. Em **A'**, temos a tensão  $V_{COMP}$  em 1,2 V novamente. No estado **B'**,  $V_{COMP}$  será  $V_{REF}$  menos a nova tensão de entrada, resultando nesse exemplo em 0,8 V. Após isso, em **C'** ocorre o acréscimo de  $V_{REF}/2$ , tornando  $V_{COMP}$  em 1,4 V.

Com V<sub>COMP</sub>- como 1,4 V, o comparador apresentará um nível lógico baixo. Dessa forma, a chave S<sub>C0</sub> deverá retornar à posição anterior, tornando V<sub>COMP</sub>- novamente em 0,8 V, representado pelo estado **D**', e permanece nesse valor até o próximo ciclo. Neste mesmo estado ocorre o início da nova dobra de tensão. No estado representado por **E**', tem-se V<sub>OUT</sub> como V<sub>REF</sub> – V<sub>COMP</sub>- = 0,4 V e no estado seguinte ocorre a dobra para 0,8 V.

O processo continua para quantos bits forem necessários. O valor da conversão de cada bit pode ser obtido através do sinal de saída Q negado do flip-flop JK que controla a chave S<sub>C0</sub>. Esse sinal pode ser lido no momento em que o sinal V<sub>SDE</sub> é mudado para nível lógico alto. No mesmo exemplo apresentado acima, o valor de saída deste flip-flop e o sinal V<sub>SDE</sub> são apresentados na Figura 40.

Figura 40 - Sinal de saída negado do flip-flop JK e sinal V<sub>SDE</sub>

Desta forma, neste exemplo, o valor da conversão para dois bits é representado por 0b10.

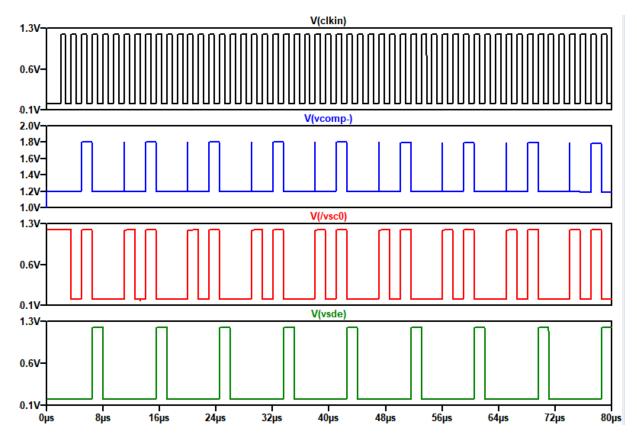

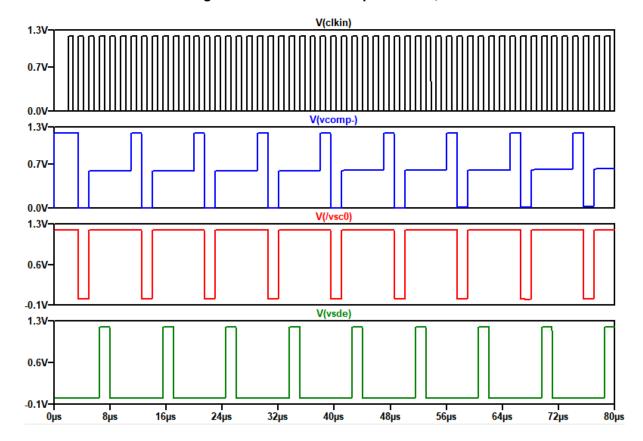

Na Figura 41, está apresentado em um período de tempo maior, para apresentar uma melhor resolução, o valor da conversão para uma entrada analógica no conversor de valor zero. Já na Figura 42, está apresentada a situação oposta, onde a tensão de entrada é a tensão máxima permitida pelo conversor, nesse caso 1,2 V. Nessas duas figuras, estão apresentados os valores dos sinais V<sub>COMP-</sub>, para demonstrar o funcionamento do circuito ao longo do tempo, do sinal negado de saída do flip-flop JK que controla a chave S<sub>CO</sub> e o sinal V<sub>SDE</sub>, esses dois últimos sinais estão apresentados para mostrar o valor da saída digital.

O valor da saída digital pode ser obtido analisando o valor negado de V<sub>SCO</sub> quando V<sub>SDE</sub> está em nível lógico alto.

Figura 41 - Sinais de saída para V<sub>IN</sub> = 0 V

Na Figura 41, pode-se perceber que em todos os instantes em que V<sub>SDE</sub> estava em nível lógico alto o sinal V<sub>SC0</sub> negado estava em nível lógico baixo. Dessa forma, a conversão para 0 V seria de 0b00000000, conforme esperado. Já na Figura 42, pode-se perceber que em todos os instantes em que V<sub>SDE</sub> estava em nível lógico alto o sinal V<sub>SC0</sub> negado estava em nível lógico alto. Dessa forma, a conversão para a tensão máxima de 1,2 V seria de 0b11111111, conforme esperado.

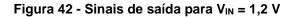

A Figura 43 apresenta o caso da conversão para uma entrada de 0,7 V. Na imagem estão destacados os bits convertidos que formam a saída digital.

Figura 43 - Sinais de saída para V<sub>IN</sub> = 0,7 V

Com a faixa de entrada do conversor sendo de 0 a 1,2 V - nesta simulação foram analisados 8 bits - a resolução do conversor pode ser calculada da seguinte forma:

$$q = \frac{V}{2^n - 1} = \frac{1,2V}{2^8 - 1} = 4,706mV \tag{57}$$

Portanto, cada bit do resultado da saída digital será equivalente a 4,706 mV. Assim, a saída 0b10010101, 149 em decimal, observada na Figura 41 representará a seguinte tensão de entrada.

$$V_{IN} = q \cdot V_{DIGITAL} = 4,706 mV \cdot 149 = 0,7011 V \tag{58}$$

Comparando o valor obtido de 0,7011 V com o valor da entrada de 0,7 V, notase que a conversão foi realizada com sucesso, validando desta forma a funcionalidade do conversor.

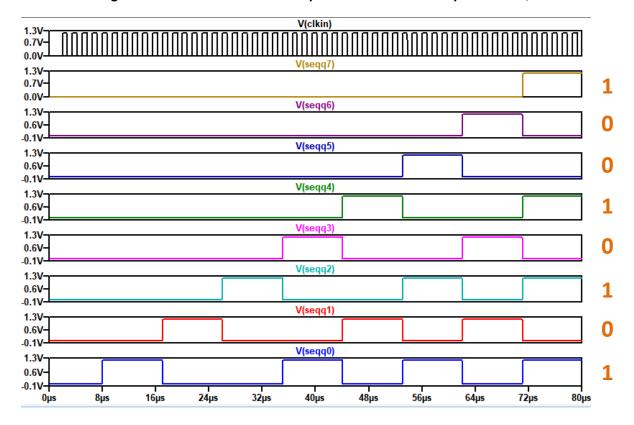

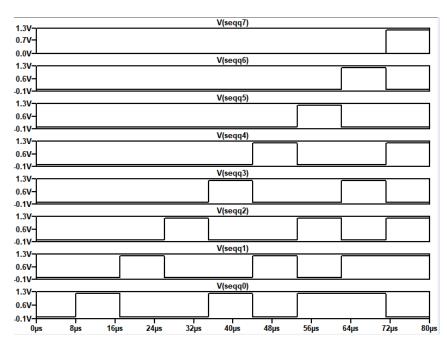

Para obter a saída digital em somente um instante de tempo, pode-se analisar as saídas do sequenciador de 8 bits utilizado. A entrada do sequenciador é o sinal V<sub>SCO</sub> negado e o relógio é o sinal V<sub>SDE</sub>. As saídas do sequenciador podem ser observadas na Figura 44.

O sinal V<sub>SEQ\_Q0</sub> é a saída do primeiro flip-flop do sequenciador, e representa a saída digital ao longo do tempo. Os sinais seguintes representam o sinal V<sub>SEQ\_Q0</sub> deslocado um ciclo de relógio por vez, dessa forma, ao final de 8 ciclos, cada sinal representará um bit da saída digital.

Figura 44 - Sinais de saída do sequenciador com 8 bits para  $V_{IN} = 0.7 \text{ V}$

Observa-se que as saídas do sequenciador formam a palavra digital 0b10010101, a mesma observada anteriormente.

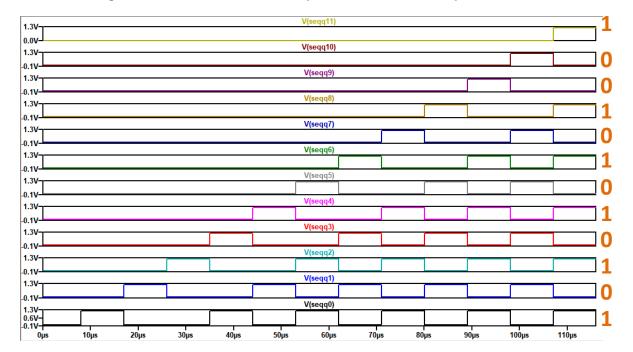

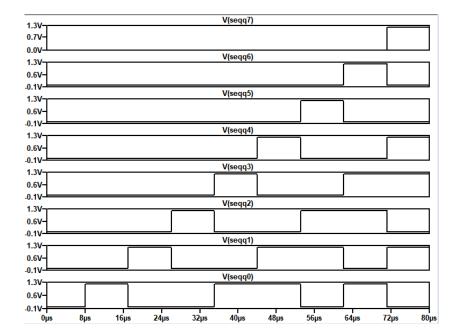

Como a vantagem desta topologia é o seu uso para múltiplos bits sem ser necessário a adição de novos capacitores, na Figura 45 está representado a conversão de 0,7V para 12 bits. Para realizar esta conversão, a única mudança a ser realizada no circuito foi a adição de mais 4 flip-flops no sequenciador.

Figura 45 - Sinais de saída do sequenciador com 12 bits para V<sub>IN</sub> = 0,7 V

Através desta configuração, a palavra digital obtida foi 0b10010101010101, que no conversor desenvolvido representa uma tensão de entrada de 0,70007 V. Percebese a melhora na conversão em relação ao conversor de 8 bits, devido à menor resolução associada.

Idealmente, esta topologia de conversor poderia seguir para quantos bits fossem necessários, sendo somente limitada pelo tempo de conversão. Entretanto, as não-idealidades existentes em um circuito real causam erros. Por isso, uma análise com algumas possíveis não-idealidades deve ser realizada.

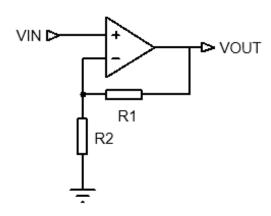

# 5.3 Simulações contendo não-idealidades

Um dos possíveis erros devido a não-idealidade pode ser causado por um ganho não unitário do buffer que conecta os circuitos de redistribuição e de dobra de tensão. Para simular este erro, foi implementado um amplificador não inversor,

topologia da Figura 46, com um ganho de 1,01. Ou seja, um buffer com o erro de ganho de 1%.

Figura 46 - Amplificador não-inversor

Como o ganho de um amplificador não inversor é dado por:

$$G = 1 + \frac{R1}{R2} \tag{58}$$

Dimensionando R2 como sendo 100 vezes maior que R1 tem-se o ganho de 1,01. Simulando com a tensão de entrada  $V_{\rm IN}$  = 0,7 V e com o erro de ganho do buffer de 1%, obteve-se o resultado da Figura 47. Retornando uma saída digital de 0b10010001, que neste conversor representa uma tensão de 0,6823 V.

V(seqq7) 0.7V 0.0V-V(seqq6) 1.3V 0.6V--0.1V V(seqq5) 1.3V 0.6V -0.1V-1.3V 0.6V -0.1V 1.3V 0.6V--0.1V V(seqq2) 1.3V 0.6V -0.1V-V(seqq1) 1.3V 0.6V V(seqq0) 1.3V-0.6V-24µs 64µs 32µs 40µs

Figura 47 - Sinais de saída com o erro de 1% no buffer e V<sub>IN</sub> = 0,7 V

Para uma tensão de entrada  $V_{IN} = 0.9$  V cujo valor da saída deveria ser o da Figura 48, com o erro de 1% obteve-se a saída da Figura 49.

Figura 48 - Sinais de saída para V<sub>IN</sub> = 0,9 V

Neste caso, o erro de conversão ocorre já no segundo bit. Entretanto, ao longo da conversão esse erro é compensado pelos demais bits. Com isso, ao fim da conversão o valor obtido para o caso de erro de ganho é de 0,894 V.

Observa-se que o erro relacionado a esta não-idealidade depende do valor da tensão de entrada. Assim, para uma melhor visualização da tensão convertida relacionada ao erro, simulou-se matematicamente através do software MATLAB a tensão de saída com e sem o erro de ganho de 1% no buffer. O código pode ser observado no Apêndice 2. O resultado dessas simulações para um conversor de 8 bits pode ser visto nas Figuras 50 e 51.

Figura 50 – Simulação matemática comparando a tensão convertida e a tensão de entrada sem considerar o erro no buffer

Figura 51 - Simulação matemática comparando a tensão convertida e a tensão de entrada considerando o erro de 1% no buffer

Observa-se que este erro ocorre ao longo de todo o intervalo de conversão e possui grande relevância. Isso ocorre, pois, após a tensão passar pelo buffer a mesma é dobrada, ou seja, o erro é dobrado juntamente com a tensão e em seguida esta tensão passa novamente pelo buffer, aumentando ainda mais o erro e propagando o mesmo ao longo de toda a conversão.

Outro possível erro devido a não-idealidade pode ser causado pela resistência, idealmente infinita, que existe quando a chave está em estado aberto. As simulações para uma resistência de 100 G $\Omega$  não apresentaram diferenças visíveis em relação as simulações com chaves ideais. Já para uma resistência de 10 G $\Omega$ , a saída digital já apresentou variação, sendo mostrada na Figura 52. A Figura 53 apresenta a saída utilizando uma resistência de 1 G $\Omega$ .