# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

AUGUSTO ANDRÉ SOUZA BERNDT

Boolean Optimization of Neural Network Circuits Using Signal Probabilities and Approximate Computing Through Constant Propagation

> Thesis presented in partial fulfillment of the requirements for the degree of Master of Microelectronics

Advisor: Prof. Dr. Paulo Francisco Butzen Coadvisor: Prof. Dr. André Inácio Reis

Porto Alegre March 2020 Berndt, Augusto André Souza

Boolean Optimization of Neural Network Circuits Using Signal Probabilities and Approximate Computing Through Constant Propagation / Augusto André Souza Berndt. – Porto Alegre: PG-MICRO da UFRGS, 2020.

101 f.: il.

Thesis (Master) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica, Porto Alegre, BR–RS, 2020. Advisor: Paulo Francisco Butzen; Coadvisor: André Inácio Reis.

1. EDA. 2. Neural network. 3. AND-inverter graph. 4. Boolean optimization. 5. Constant propagation. 6. Approximate computing. I. Butzen, Paulo Francisco. II. Reis, André Inácio. III. Título.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL Reitor: Prof. Rui Vicente Oppermann Vice-Reitora: Prof<sup>a</sup>. Jane Fraga Tutikian Pró-Reitor de Pós-Graduação: Prof. Celso Giannetti Loureiro Chaves Diretora do Instituto de Informática: Prof<sup>a</sup>. Carla Maria Dal Sasso Freitas Coordenador do PGMICRO: Prof. Tiago Roberto Balen Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

"The only absolute truth is that there are no absolute truths." — PAUL KARL FEYERABEND

## AGRADECIMENTOS

Gostaria de agradecer aos meus pais Nara Berndt e Ricardo Berndt que me incentivaram desde cedo a ser uma pessoa estudiosa, investindo seu esforço para minha formação acadêmica e como pessoa. Agradeço por terem desenvolvido meu intelecto de uma pessoa curiosa que busca entender a essência dos acontecimentos ao nosso redor e que envolvem nossa existência. Se não fosse por isto, nunca teria iniciado um projeto de mestrado acadêmico.

Agradeço também meus mentores André Reis e Paulo Butzen por toda sua paciência e tempo investidos comigo e para o desenvolvimento desse projeto. Graças a eles aprendi uma diversidade de assuntos e técnicas na prática durante o desenvolvimento do projeto. Agradeço todo seu conhecimento e orientações que foram transmitidos. Tive uma evolução como pessoa e pesquisador notável ao longo destes dois anos de mestrado, graças a eles.

Agradeço também a minha namorada Bruna Martins e sua família por terem me acolhido como um membro a mais em sua família enquanto residia em Porto Alegre realizando a execução deste mestrado.

Por fim agradeço aos membros da banca, os professores Cristina Meinhardt, José Azambuja e Raphael Brum pela sua participação, críticas e comentários complementando com a finalização deste trabalho.

# ABSTRACT

The development of electronic devices has demonstrated amazing capabilities since the introduction of the transistor device. Humanity is more than ever, virtually connected. Information is at the grasp of most current human beings, thanks to the expansion and improvement of integrated circuits. The construction of an integrated circuit usually follows an iterative design flow, and research on this topic is crucial to keep this technology naturally undergoing progress. Although, the implementation of emerging technologies such as artificial intelligence and even the recess that Moore's Law faces are obstacles that researchers face and attempt to overcome by finding suitable solutions to such present problems composing in current technologies. Even though the concept and experimental implementation of artificially intelligent devices is a long craving wish among researchers, it is only in the present days that its actual usage in the real world is happening. The development of integrated circuits jointly with the introduction of *big data* and *internet of* things (IoT) allows for a plausible common ground for the employment of artificially intelligent devices in current commodities. Nonetheless, the research and study on the area also sustain an increase in attention by researchers to achieve better, faster, and less power consuming technologies. On the other hand, neural networks (NNs) specifically tend to be extensively power and area consuming. Companies work around it by using data centers and provide inference for their users. But even still, optimizations seeking more compact or even less power consuming neural networks should be pursued. Integrated circuit designers face a considerable challenge when attempting to implement hardware with a certain limited budget, like smartphones or IoT devices, that can process current neural networks. This work focuses on optimizing circuits representing neural networks in the form of AND-inverter graphs (AIGs). The optimization is done by analyzing the training set of the neural network to find constant bit values among the AIG nodes. The constant values are then propagated through the AIG, which results in removing unnecessary nodes. Furthermore, a trade-off between neural network accuracy and its reduction due to constant propagation is investigated by replacing with constants those nodes that are likely to be zero or one. The experimental results show a significant reduction in circuit size with negligible loss in accuracy. For example, for a neural network, we were able to reduce its size to 63.3% and its depth to 82.0% from their original values with no reduction in accuracy, or even 59.1% in size and 77.9% in depth from original values while loosing only 1% in accuracy.

**Keywords:** EDA. Neural network. AND-inverter graph. Boolean optimization. Constant propagation. Approximate computing.

# Otimização Booliana de Circuitos de Redes Neurais Usando Probabilidade de Sinais e Computação Aproximada Através da Propagação de Constantes

#### **RESUMO**

O desenvolvimento de dispositivos eletrônicos tem demonstrado capacidades surpreendentes desde a introdução do dispositivo transistor. A humanidade está mais do que nunca virtualmente conectada, a informação está ao alcance da maioria dos seres humanos atuais graças a expansão e melhorias de circuitos integrados. A construção de um circuito integrado geralmente segue um projeto iterativo e pesquisas neste tópico são cruciais para mantê-la naturalmente progredindo. No entanto, a implementação de tecnologias emergentes como inteligência artificial e até o recesso que a Lei de Moore enfrenta são obstáculos que pesquisadores enfrentam e tentam superar através da procura soluções aplicáveis para estes problemas atuais. Por mais que o conceito e a implementação de dispositivos compostos de inteligência é um desejo almejado por pesquisadores a muito tempo, somente nos dia atuais que sua utilização está realmente acontecendo no mundo atual. O desenvolvimento de dispositivos eletrônicos juntamente com a introdução de big data e da internet das coisas (IoT) proporcionam um ambiente saudável para a concepção de dispositivos compostos de inteligencia artificial em commodities atuais. Não obstante o estudo e pesquisa na área recebe um aumento na atenção dada por pesquisadores para atingir tecnologias melhores, mais rápidas e que consomem meno energia. No entanto, redes neurais especificamente tendem a consumir muita energia e exigir muita área de implementação, companhias industriais improvisam soluções utilizando data centers para providenciar a capacidade de inferência para seus usuários. Mesmo assim, otimizações que buscam redes neurais mais compactas ou que utilizem menos energia devem ser almejadas. Projetistas de circuitos integrados enfrentam um gigantesco desafio enquanto tentam implementar um hardware com orçamento limitado, como smartphones ou dispositivos IoT que são capazes de processar redes neurais atuais. Este trabalho foca na otimização de circuitos que representam redes neurais na forma de grafos AND-inversores (AIG). A otimização é feita analisando o conjunto de treinamento da rede neural para encontrar bits constantes nos nodos do AIG. Os valores constantes são então propagados pelo AIG, no qual resulta em remover nodos desnecessários. Além disso, o comprometimento entre a precisão da redes neurais e a sua redução é investigado devido a propagação de constantes através da reposição de nodos que tendem a serem constantes zero ou um. Os resultados

experimentais mostram uma significante redução em tamanho e profundidade do circuito com uma perda insignificante de precisão. Por exemplo nós conseguimos reduzir uma rede neural em tamanho para 63.3% e profundidade para 82.0% dos seus valores originais sem nenhuma perda de precisão, ou até 59.1% de tamanho e 77.9% de profundidade dos valores originais enquanto a rede perdeu somente 1% de precisão.

**Palavras-chave:** EDA, grafo AND-inversor, redes neurais, computação aproximada, otimização booleana.

# LIST OF ABBREVIATIONS AND ACRONYMS

- AIG AND-Inverter Graph

- AI Artificial Intelligence

- AN All Nodes

- ASIC Application-Specific Integrated Circuit

- BDD Binary Decision Diagram

- CEC Combinational Equivalence Check

- CIFAR Canadian Institute For Advanced Research

- CNN Convolutional Neural Network

- DAG Directed Acyclic Graph

- EDA Electronic Design Automation

- FPGA Field Programmable Gate Array

- FB-LD Functional Based on Logic Depth

- FB-NPD Functional Based on Number of Nodes Per Level

- GPU Graphics Processing Unit

- ILSVRC ImageNet Large Scale Visual Recognition Challenge

- IoT Internet of Things

- LD Logic Depth

- LUT Look-Up Table

- MAC Multiply Accumulate

- MIG Majority-Inverter Graph

- MNIST Modified National Institute of Standards and Technology

- NN Neural Network

- OPI Only Primary Inputs

- PI Primary Input

| РО   | Primary Output         |  |  |  |

|------|------------------------|--|--|--|

| ReLu | Rectified Linear Unit  |  |  |  |

| RDF  | Random Decision Forest |  |  |  |

| SOP  | Sum-of-Products        |  |  |  |

- TH Threshold Probability Variable

- VHDL Very High Speed Integrated Circuit Hardware Description Language

- XAIG XOR-AND-Inverter Graph

# LIST OF FIGURES

| Figure 2.1 XOR in AIG representation.                                                    | 22   |

|------------------------------------------------------------------------------------------|------|

| Figure 2.2 Constant propagation procedure and resulting AIG                              | 25   |

| Figure 2.3 Structural hashing usage on example AIG.                                      |      |

| Figure 2.4 Model of a neuron                                                             | 29   |

| Figure 2.5 Set of activation functions for a neuron                                      | 31   |

| Figure 2.6 Feature space for neural networks with different activation functions         | 31   |

| Figure 2.7 Fully connected single layer neural network for recognition of the MNIST      |      |

| dataset.                                                                                 | 33   |

| Figure 2.8 Example of a set of features for the digit 0                                  |      |

| Figure 2.9 Graphical representation of the cost function of a two input neural network   | 3.35 |

| Figure 2.10 IEEE 754 single precision floating point decimal in binary.                  | 42   |

| Figure 2.11 Example of a fixed point decimal number in binary (0011.0110=3.375)          |      |

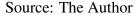

| Figure 2.12 Block diagram of a MAC unit for NNs.                                         |      |

| Figure 2.13 Multiple MAC units implementing a NN layer with a tree shape                 |      |

| Figure 3.1 Types of layers and number of neurons per layer for the experimental          |      |

| NN models.                                                                               | 48   |

| Figure 3.2 A probability color scale calculated based on the MNIST dataset of the        |      |

| PI nodes of the AIGs proposed.                                                           | 50   |

| Figure 3.3 A probability color scale calculated based on the MNIST dataset of the        |      |

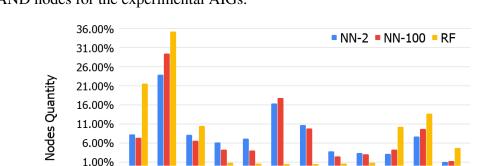

| internal AND nodes for the experimental AIGs.                                            | 50   |

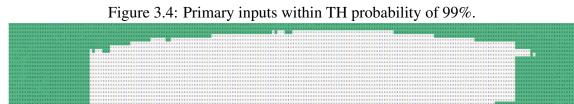

| Figure 3.4 Primary inputs within TH probability of 99%                                   | 51   |

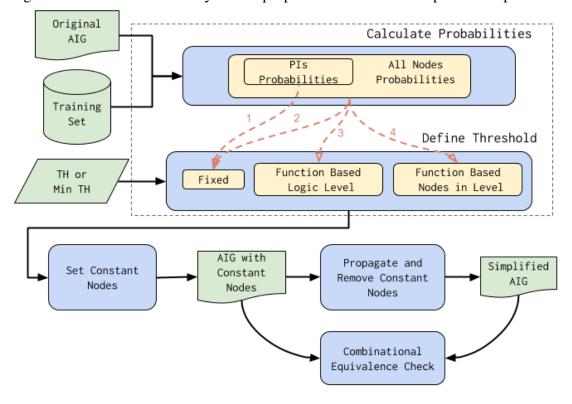

| Figure 3.5 Flowchart summary for the proposed methods and the performed pro-<br>cedures. | 52   |

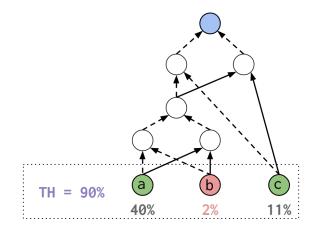

| Figure 3.6 Probability and threshold values with OPI method.                             |      |

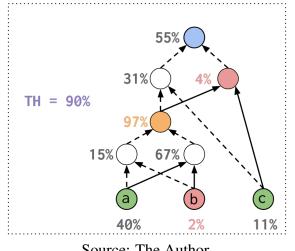

| Figure 3.7 Probability and threshold values with AN method                               |      |

| Figure 3.8 Graph showing the three different distributions used on the functional        | .50  |

| based methods.                                                                           | 58   |

| Figure 3.9 Probability and threshold values with FB-LD Method                            |      |

| Figure 3.10 Number of Nodes in each LD for the Proposed NNs and RDF                      |      |

| Figure 3.11 Probability and threshold values with the FB-NPD method.                     |      |

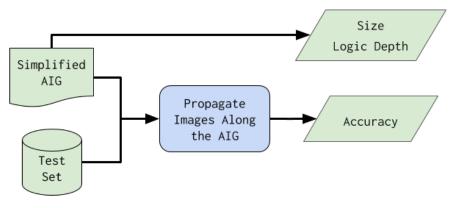

| Figure 3.12 AIG's data extraction after simplification                                   |      |

| rigure 5.12 Arto's data extraction arter simplification                                  | .07  |

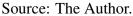

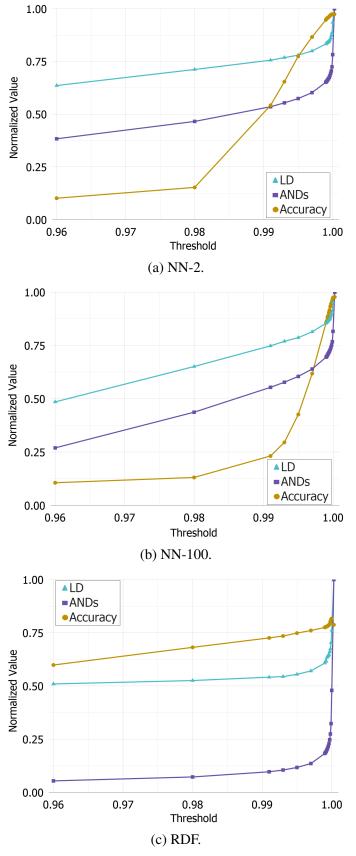

| Figure 4.1 Accuracy, logic depth and number of AND nodes for the OPI method              |      |

| with fixed THs.                                                                          | 71   |

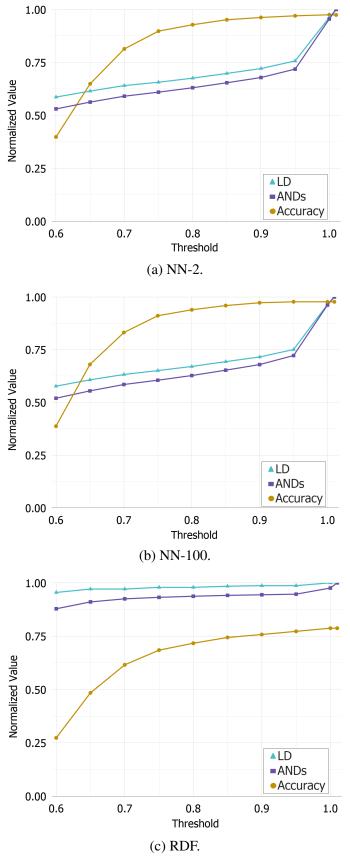

| Figure 4.2 Number of AND nodes in each LD with different TH values for the OPI           |      |

| method                                                                                   | 72   |

| Figure 4.3 Accuracy, logic depth and number of AND nodes for the AN method               |      |

| with fixed THs                                                                           | 75   |

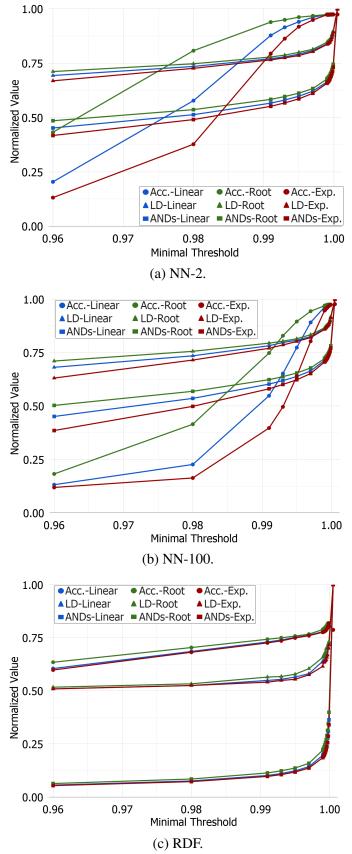

| Figure 4.4 Accuracy, logic depth and number of AND nodes for the FB-LD method            |      |

| with minimal THs.                                                                        | 78   |

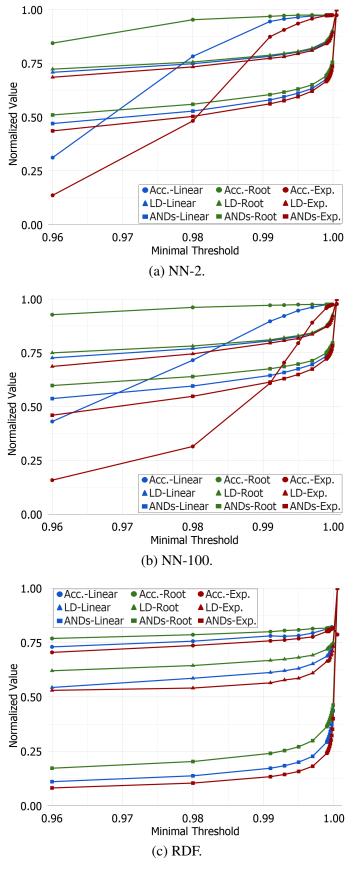

| Figure 4.5 Accuracy, logic depth and number of AND nodes for the FB-NPD method           |      |

| with minimal THs.                                                                        | 81   |

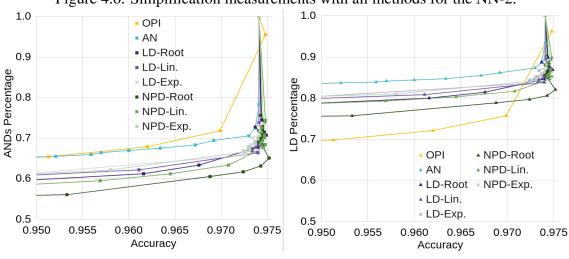

| Figure 4.6 Simplification measurements with all methods for the NN-2.                    |      |

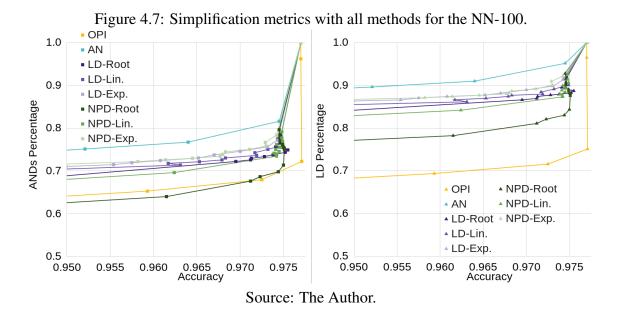

| Figure 4.7 Simplification metrics with all methods for the NN-100.                       |      |

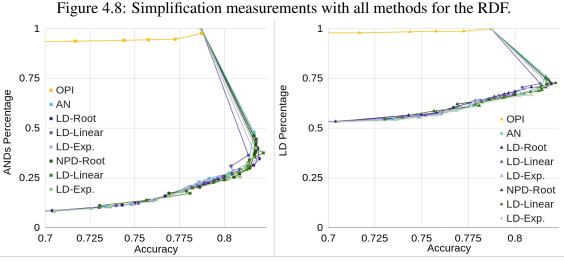

| Figure 4.8 Simplification measurements with all methods for the RDF.                     |      |

|                                                                                          |      |

# LIST OF TABLES

| Table 2.1   AND logic under constants.                                                   | 26 |

|------------------------------------------------------------------------------------------|----|

| Table 4.1 Simplification measurements with 100% TH for the OPI method                    | 73 |

| Table 4.2 Simplification measurements at 1% accuracy loss for the OPI method             | 74 |

| Table 4.3 Simplification measurements with 100% threshold probability value for          |    |

| the AN method                                                                            | 76 |

| Table 4.4 Simplification measurements at 1% accuracy loss for the OPI and AN             |    |

| methods                                                                                  | 77 |

| Table 4.5 Simplification measurements at 1% accuracy loss for the OPI, AN and            |    |

| FB-LD methods.                                                                           | 79 |

| Table 4.6 Simplification measurements at 1% accuracy loss for all methods                | 82 |

| Table 4.7         Simplification measurements for the lowest FoM achieved in each method |    |

| with NN-2.                                                                               | 87 |

| Table 4.8         Simplification measurements for the lowest FoM achieved in each method |    |

| with NN-100                                                                              | 88 |

| Table 4.9       Simplification measurements for the lowest FoM achieved in each method   |    |

| with RDF.                                                                                | 88 |

|                                                                                          |    |

# CONTENTS

| 1 INTRODUCTION                                          |     |

|---------------------------------------------------------|-----|

| 1.1 Problem Definition                                  |     |

| 1.2 Proposal and Contributions                          |     |

| 1.3 Dissertation Outline                                |     |

| 2 BACKGROUND                                            |     |

| 2.1 Logic Circuits                                      |     |

| 2.1.1 Data Structures to Represent Logic Circuits       | 20  |

| 2.1.2 Nodes Probabilities                               |     |

| 2.1.3 AIG Simplification Under Constants                |     |

| 2.1.4 Structural Hashing                                |     |

| 2.2 Neural Networks                                     |     |

| 2.2.1 Neural Network Structure and Learning             |     |

| 2.2.2 Neuromorphic Hardware                             |     |

| 2.2.3 Neural Network Optimizations                      |     |

| 2.2.4 Boolean Optimizations for Neural Network Circuits | 39  |

| 2.3 Boolean Representation of Neural Networks           |     |

| 2.3.1 Boolean Representation of Decimal Values          |     |

| 2.3.2 Multiply Accumulate Operation                     |     |

| 3 METHODOLOGY                                           |     |

| 3.1 Experimental Models                                 |     |

| <ul><li>3.1.1 AIG Models Signal Probabilities</li></ul> |     |

| 3.2.1 Only Primary Inputs                               |     |

| 3.2.2 All Nodes                                         |     |

| 3.2.3 Functional Based                                  |     |

| 3.3 Description of Experiments                          |     |

| 3.4 Used Metrics                                        |     |

| 3.4.1 Accuracy Loss - Interpolation                     |     |

| 3.4.2 Figure of Merit                                   |     |

| 4 RESULTS                                               |     |

| 4.1 Only Primary Inputs                                 |     |

| 4.1.1 100% Threshold                                    |     |

| 4.1.2 1% Accuracy Loss                                  | 73  |

| 4.2 All Nodes                                           | 74  |

| 4.2.1 100% Threshold                                    | 76  |

| 4.2.2 1% Accuracy Loss                                  | 76  |

| 4.3 Functional Based - Logic Depth                      | 77  |

| 4.3.1 1% Accuracy Loss                                  |     |

| 4.4 Functional Based - Number of Nodes Per Depth        |     |

| 4.4.1 1% Accuracy Loss                                  |     |

| 4.5 General Comparison of the Proposed Methods          |     |

| 4.5.1 Trade-off Among Methods                           |     |

| 5 CONCLUSION                                            |     |

| 5.1 Contributions Summary                               |     |

| 5.2 Future Work                                         |     |

| REFERENCES.                                             |     |

| APPENDIX A — PROGRAMMING TOOLS AND TECHNIQUES           | 100 |

# **1 INTRODUCTION**

Artificial intelligence (AI) is the study behind the capability that an entity has to understand and solve problems in the real world. Its objective is to perceive its environment and react upon it, usually learning about the environment in an attempt to maximize its chances of achieving a goal (RUSSELL; NORVIG, 2016). *Neural networks* (NNs) present themselves as an AI entity, which are non-linear mathematical models inspired by biological neural networks (NIELSEN, 2015; HAYKIN, 1994). This technology is capable of receiving information, processing this information, and giving a response as output. Neural Networks are usually used to recognize patterns and also on classification problems. Classification by image recognition has shown itself a problem that NNs excel at solving, sometimes even surpassing human capabilities (RUSSAKOVSKY et al., 2015; GYSEL, 2016). Although this high expertise in solving problems comes with the cost of high demand for computational capacity and effectiveness (XU et al., 2018; MISRA; SAHA, 2010). The emerging of *internet of things* (IoT) devices and smartphones are leveraging the demand for AI inferences in everyday life.

A NN is an interconnected group of neurons, inspired by the structure of a living being's brain. Each neuron inside a NN may form one or multiple weighted synapses, and the neurons are grouped in layers. The first layer being the input layer, followed by an arbitrary number of hidden layers and an output layer that gives the NN's solution to the presented input. NN implementations go through a training phase that covers thousands of examples to learn from. Each iteration of the learning phase processes instances of the training set and refines the NN parameters with a backpropagation process based on the stimulation presented by the training set, responsible for finding intricate structures in the training set. The same set of data is processed multiple times as the network is continually refined. The type in which the learning occurs is defined by how the NN's *parameters* adjust during the learning stage. The idea is to search for a good possible solution by iteratively modifying the NN's parameters, usually a *gradient descent* approach is used to search for a local minimum about the NN's loss function (HAYKIN, 1994; NIELSEN, 2015; BISHOP et al., 1995).

# **1.1 Problem Definition**

NNs are mostly implemented as software (WEI et al., 2018; BAI et al., 2018; ZHANG et al., 2018; HU; SHEN; SUN, 2018). Specifically, NNs presented in the ImageNet Large Scale Visual Recognition Challenge (ILSVRC) challenge have shown an amazing development of knowledge to infer on images. Although this inference capability is software-based and comes with a high processing requirement, in some of the challenges processing budgets are imposed, making a closer correlation with the requirements for the implementation and usage of NNs as hardware (RUSSAKOVSKY et al., 2015). That much improvement on the NN's capabilities also comes with the price of high processing and power consumption demand. Even though there are cloud-based servers that offer NN's inference online and companies make use of them to perform the highly demanded inference and training processes needed for their AI-based commodities (LECUN, 2019). So many requirements delay the implementation of NNs as hardware, for example, their implementation in mobile systems, since an excessive amount of components and energy power is required, which are not available. Nonetheless, the device's edge inference capabilities should reduce the processing and power requirements to execute and employ NNs on present mobile and IoT devices, which have low computational capabilities and require low power consumption. Research on this topic is required, so this may be possible.

Neuromorphic hardware already implemented vary from analog, digital and optical signal types (XU et al., 2018; CALVERT; MARINOV, 2000; HAMERLY et al., 2019) and platforms such as FPGAs, GPUs and ASIC (LECUN, 2019; NIELSEN, 2015; XU et al., 2018). All of them have a different set of flaws (like accuracy loss, large space, and power usage or low processing speed) and delays their commercial practice (MISRA; SAHA, 2010; XU et al., 2018). As shown by (XU et al., 2018), there is a gap between the required processing power by NNs implemented as software in academia and the development of hardware to process such NNs, which lags in processing capability compared to the NNs implemented in software. Also, EDA tools have a hard time to develop an efficient synthesis for NNs. Neuromorphic hardware requires a large silicon area due to a large number of logic gates and a high number of connections between layers, which introduces routing congestion (ARDAKANI et al., 2017). This is why NNs are still lagging on market nodes such as smartphones, IoT devices, and edge devices. NNs are already being used by researchers to execute logic synthesis (HAASWIJK et al., 2018). However, it is yet to be discovered how to efficiently reproduce logic synthesis steps to design an NN circuit (HE; SUN, 2015; QIU et al., 2016; ARDAKANI et al., 2017).

In the work presented herein, we propose four different variants to reduce the size and depth of NNs when represented in a boolean format, more precisely NNs represented with the AND-inverter graph (AIG) data structure. During the project execution of an integrated circuit, its project goes through iterative processes, and the AIG data structure is actively used in *logic synthesis* stages such as technology mapping and independent technology optimizations (CHANDRASEKHARAN et al., 2016; MISHCHENKO; CHATTERJEE; BRAYTON, 2006; WANG et al., 2017). To expose the unusual number of building blocks required by NNs, we can see that, for example, the NN reported by (COATES et al., 2013) had around 1 million neurons and 10 billion synaptic weights. The number of *multiply accumulate* (MAC) units required to implement an NN in hardware does not reflect the size in which researchers are used to working with to build electronic devices. For example, in the IWLS'19 contest, its largest AIG had almost 1.8 million AND nodes. We would require various amounts of AND nodes to represent each MAC for the NN design. The machine learning models represented in AIG used in our work range from 45 to 80 million AND nodes, at least 25 times larger than the largest AIG in the IWLS'19 contest (International Workshop on Logic and Synthesis, 2019). Without saying that the NNs used in this work has only 333 thousand parameters (the trainable components of a NN are usually known as *parameters* such as the weight and bias, while the non-trainable components are called *hyperparameters* such as the number of hidden layers in the NN), in comparison to the winner of ILSVRC ImageNet 2016 contest the ResNet which had 60 million parameters (HE et al., 2016). This exposes the challenge it is to have a boolean representation for NNs with the current knowledge on the field. The NNs used in the present work show themselves with enormous sizes when passed to the AIG format, being not even close to what the logic synthesis research community are used to work with.

#### **1.2 Proposal and Contributions**

To improve the design of hardware for NNs, we work on its boolean representation and adopt an approximate computing strategy. We insert small acceptable errors to decrease the project's cost. This is a common approach to the design of arithmetic, energy-efficient, or quality configurable circuits (HAN; ORSHANSKY, 2013; WU; QIAN, 2016; YAO et al., 2017; VENKATARAMANI; ROY; RAGHUNATHAN, 2013; CHANDRASEKHARAN et al., 2016; WANG et al., 2017). In our work, we use the training set to extract the probabilities of all the nodes in the circuit. We might then consider signals with high probability values to be constants, which allows us to apply simplifications on the circuit. This process is done on already trained NN circuits represented as AIGs.

We propose an analysis to evaluate the behavior of the NN when its size is reduced based on constant and nearly constant signal propagation. The simplification under constants is a technique already known (MICHELI, 1994), although not every circumstance allows its use as the circuit's input set is not always known. Also, the problem's complexity grows exponentially with the circuit's input size. NNs are good candidates to make use of such technique because the training set exposes a considerable amount of its possible input vectors.

Altogether four different ways are presented to define which nodes will be established as constants. Furthermore, we propose two different metrics to compare the trade-off in accuracy loss versus size and depth among the methods proposed. Our contributions are listed as follows.

- We implement a probability calculation of signals in an NN represented as a circuit in its AIG format by simulation and directed by the NN's training dataset.

- We define nodes to be set as constants based on the nodes' probabilities in which surpass a certain *threshold*. The AIG may be simplified after the definitions of such constants.

- We propose four different manners to define a node's threshold probability, the idea behind them is to search for the unimportant nodes and set them as constants while leaving the important ones untouched.

- 1. At first, a fresh approach where only the AIG's primary inputs may be turned as constants is proposed. Even a naive concept such as this one, can considerably simplify the NN's size and depth. This method was previously published in (BERNDT et al., 2019).

- 2. A second approach is proposed where we may turn into constants any node of the AIG with a fixed threshold probability value. In this method, the threshold is fixed, meaning its the same for all nodes in the AIG.

- 3. A third and fourth method is presented in which variable thresholds are used,

meaning that the nodes in the AIG have different thresholds. These thresholds are calculated based on the node's characteristics, such as its *logic depth* (LD) or the *amount of nodes* present in an equal logic depth.

We apply our simplification methods on two NNs and a *Random Decision Forest* (RDF) model, the RDF model is used mainly to show that our approach is not structurally constrained. The four methods proposed presented different behavior on each of the machine learning models. Some analyses are made at the last chapter of the present work to expose the worthwhile trade-off from accuracy loss versus size and depth reduction, by making a comparison among the methods concerning the utilized experimental models. We were able to achieve a reduction of 18% in depth and 27% in size with no reduction in accuracy for a NN model and 22.1% reduction in depth and 40.9% in size with the cost of only 1% reduction in accuracy for the same NN, for example.

#### **1.3 Dissertation Outline**

The rest of this dissertation is organized as follows. The next Chapter 2 presents some background and preliminary information on subjects that are essential for the proper understanding of the contributions of this work, such as details about a NN design, AIG simplification particularities and the conversion of a NN to a boolean representation. Chapter 3 discusses the experimental machine learning models used to evaluate our contributions and present our contributions based on optimization for NNs in an AIG representation. Afterward, Chapter 4 presents the results achieved with experiments realized on top of the machine learning models with the usage of the proposed methods. Analyses are made for the performance achieved with each different method and each type of machine learning model with the results presented by the experiments realized. We attempt to analyze what is the trade-off for size and depth reduction versus accuracy loss for each situation. In Chapter 5, a conclusion is presented enclosing the work presented herein.

# **2 BACKGROUND**

This chapter describes the necessary background on topics that are fundamental to perceive and understand the work presented herein properly. We begin by explaining the data structure used for the reduction of NN circuits in their logical representation. Next, we briefly expose the idea behind the probability of elements in a circuit. Afterward, we explain how the reduction of logic circuits is made with the presence of constant variables. Afterward, it is discussed about the structure and learning process of a NN. Next, we present an overview of the bibliography concerning the implementation and optimizations of neuromorphic hardware. In the last section of this chapter, we present the issues and requirements for the implementation of a boolean representation of a NN.

#### **2.1 Logic Circuits**

The manufacture and design of integrated chips are based on iteratively compiling, optimizing, and verifying the hardware description language of a circuit to achieve its physical representation layout. These processes are usually summarized in a design flow, in which chip designers follow to coordinate the synthesis of an error-free integrated chip. A general design flow is divided into categories: high-level synthesis, logic synthesis, physical synthesis, and verification (WESTE; HARRIS, 2015; MATOS; CARRABINA; REIS, 2018; POSSANI et al., 2018).

When progressing along with the design flow, there are intermediate steps to follow, such as the *logical synthesis* step that is responsible for making technology-independent optimizations and technology mapping. Following logic synthesis, it is performed the *physical synthesis* step, which is responsible for placing and routing of logic gates. It is required that the circuit's specification is already mapped with respect to a library of cells. The library specifies the logic and electric characteristics for each type of logic gates. A good mapping algorithm is one able to find a combination of logic gates that can precisely represent the circuit's logic with the least amount of area, power dissipation, and delay as possible, these may vary depending on the synthesis objectives. The verification steps are the ones responsible for estimating such metrics and analyzing the quality of the synthesized circuit along each step of the design flow, including the logic synthesis steps. To find a good combination of logic gates available in a library is a non-deterministic problem since there may be different combinations of logic gates that can

map into the same boolean logic (MATOS; CARRABINA; REIS, 2018; MISHCHENKO et al., 2015).

Another process executed during logic synthesis is the one called technologyindependent optimization, or multi-level logic optimization as its also called, in which optimizations are applied before technology mapping attempting to reduce the size and depth of the structure representing the circuit while maintaining its logic function, regardless of technology mapping and physical characteristics (BRAYTON et al., 1987; MISHCHENKO; CHATTERJEE; BRAYTON, 2006; YU; CIESIELSKI; MISHCHENKO, 2018; POSSANI et al., 2018). The reduction in size and depth of the logic representation of a circuit is proven to be correlated with the circuit's area and delay, respectively (BRAYTON; HACHTEL; SANGIOVANNI-VINCENTELLI, 1990; MICHELI, 1994). More precisely, for the AIG data structure that is used in this work, the size is determined by the number of nodes in the AIG, and its depth is determined by the number of nodes in the longest path going from a primary input to a primary output. The technologyindependent optimization steps usually takes a considerable amount of time to execute and are of great importance, since the logic representation synthesized during logic synthesis will have a direct impact on the Quality of Result in later steps of the design flow, like technology mapping (CHATTERJEE et al., 2006; LIU; ZHANG, 2017) and also in placing and routing steps (WANG; CHANG; CHENG, 2009).

# 2.1.1 Data Structures to Represent Logic Circuits

In this subsection, we briefly present some of the data structures used to represent logic circuits. A circuit may be structured as a boolean function, and there are some different data structures able to depict such functions.

# 2.1.1.1 Binary Decision Diagram

There are several types of data structures that represent logic circuits used during logic synthesis steps. For example, the binary decision diagram (BDD) is a rooted Directed Acyclic Graph (DAG); in other words, it is a directed graph without the presence of cycle paths within it. It represents a set of binary decisions converging in a final decision that may be true or false. These decisions would be represented by the graph's vertices and the edges the path to follow after a decision is made. In (BRYANT, 1986) it

was introduced the ability to make canonical representations with BDDs. However, this data structure grows exponentially in size with relation to the number of variables, being an impractical approach a lot of the times (MICHELI, 1994; WANG; CHANG; CHENG, 2009).

#### 2.1.1.2 Boolean Networks

A *boolean network* is also a DAG structure able to represent multi-level logic circuits, although its vertices are not decisional ones, they represent the circuit's logic itself. A boolean network is composed of three types of vertices (also called nodes): *primary inputs* (PIs), which have no incoming edges, *primary outputs* (POs) which have no outgoing edges and internal nodes which compose the circuit's internal structure. Each internal node may also be considered an intermediate or local function, which is associated with a circuit's segment (MATOS; CARRABINA; REIS, 2018; MICHELI, 1994). Next, we shall briefly expose some examples of boolean networks. The last is the AIG data structure in which we make use of and explain in deeper detail.

#### 2.1.1.3 Sum-of-Products

The *sum-of-products* (SOP) is a form of boolean formula, also known as *disjunctive normal form*, composed of disjunctions (sums) of conjunctions (products) of literals. In (BRAYTON et al., 1987), SOPs are used to make an area estimation of the circuit's representation, in (BARTLETT et al., 1987) SOPs are not only used to estimate area but also to apply logic manipulations. Even though any boolean formula may be represented in the SOP format, its representation is not canonical and heterogeneous, reducing its practical use in logic synthesis.

#### 2.1.1.4 AND-Inverter Graph

On the other hand, a homogeneous representation of logic circuits is more attractive, since it makes for easier manipulation of internal nodes. Homogeneous boolean networks examples of data structures would be: AND-inverter graphs, *XOR-AND-inverter graphs* (XAIG) or even *majority-inverter graphs* (MIG). These data structures can reproduce any possible logic under their primitive operations (MATOS; CARRABINA; REIS, 2018; Soeken et al., 2016). The XAIG would be an extension to the AIG structure with the possible usage of XOR nodes, in the work (Háleček; Fišer; Schmidt, 2017) the XAIG structure shows some improvements on synthesis concerning area and delay with some benchmark circuits, although with inferior results for other circuits when compared to the AIG structure. In the work (Amarú; Gaillardon; De Micheli, 2016) the MIG structure was introduced, where it achieved some minor, but still relevant, reductions in delay, area and power with experimental results when compared to the conventional AIG structure. In the present work, we make use of the AIG data structure and it shall be further explained.

The usage of AND-inverter graphs for logic synthesis dates back to the '60s, with the works (HELLERMAN, 1963; DARRINGER et al., 1981), even though the community still acclaims the AIG data structure and its variants to its usage in technology mapping and multi-level logic optimizations. An AND-inverter graph is a directed acyclic graph composed of primary inputs, primary outputs, and two-input AND nodes. All internal nodes in an AIG are AND nodes with exactly two *fanin* inputs and an arbitrary number of *fanout* outputs. Any AND node may be established as a PO. Direct or negated edges connect the nodes. Continuous lines represent a direct edge, while dotted lines represent the negated ones (YU; CIESIELSKI; MISHCHENKO, 2018; MISHCHENKO; CHATTERJEE; BRAYTON, 2006).

Source: The Author.

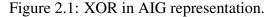

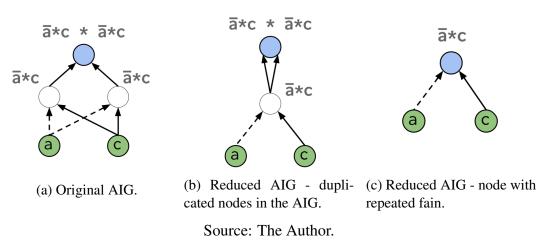

Figure 2.1 shows an AIG representation of a three-input XOR logic function, composed of six AND nodes in white, three PI nodes in green and one PO node in blue. Since an AIG is built with AND and NOTs (negated edges), they can represent any logic circuit. During the execution of the Design Flow, the logic synthesis stage consists of converting a high-level description of a design into an optimized gate-level representation. The AIG data structure is broadly used in such steps, mainly to apply technology-independent optimizations and technology mapping on circuits (YU; CIESIELSKI; MISHCHENKO, 2018; MISHCHENKO; CHATTERJEE; BRAYTON, 2006). The ABC academic logic synthesis CAD tool that offers a diversified range of operations able to optimize an AIG representation of a circuit or even execute a technology mapping if a library is provided (Berkeley Logic Synthesis and Verification Group, 2019).

The main advantages of the AIG structure would be: (1) its homogeneous characteristic, meaning that it is easier for logic manipulations. (2) its structure is easily compressed, the AIGER format may be used to do so, where a binary compression is applied to the AIG description, taking less memory to store the AIG (BIERE, 2007) such representation is used on the proposed work. And (3) the number of nodes and the logic depth in an AIG is correlated with the final circuit's area and delay respectively (BRAYTON; HACHTEL; SANGIOVANNI-VINCENTELLI, 1990; MICHELI, 1994). In this work, we make use of the AIG data structure to implement and experiment on our proposed methods to apply technology-independent optimizations oriented for NNs.

#### 2.1.2 Nodes Probabilities

In this session, we describe a known topic, which is the probability of nodes in an AIG. Such an idea of defining probabilities for a circuit's components is commonly used on the logic gate level of abstraction to estimate static power dissipation, reliability, and aging metrics of a circuit (FRANCO et al., 2008; FLAQUER et al., 2010). A signal refers to the binary information that is being passed through a node or nodes in an AIG. The probability of a boolean node is the likelihood that this node will have certain boolean value when the circuit is operating, and signals are passing through it. A boolean variable or node has only two possible values, for example a boolean variable  $f = {\text{true}, \text{false}}$  or even  $\{1,0\}$ . If for example, we had the XOR AIG from Figure 2.1 on an operating circuit and we were able to count each time the node f was set to *true*, we could divide this counter by the total number of times an input vector of signals was applied to the circuit. We would have the signal probability for such AND node to be *true*, denoted by P(f = 1). Equation 2.1 demonstrates the function to calculate the probability of node f to be *true* and Equation 2.2 demonstrates this nodes probability of to be *false*, denoted by

P(f = 0).

$$P(f=1) = \frac{Number of Operations f = true}{Total Operations}$$

(2.1)

$$P(f=0) = \frac{Number \, of \, Operations \, f = false}{Total \, Operations} \tag{2.2}$$

On real-world verification of circuits, the designers almost in every situation can't apply the process just explained of simulating the circuit for known combinations of input vectors. Then, a naive way to calculate the probabilities in a circuit is to process all the possible combinations of input vectors for such a circuit. Although this approach is limited, since its complexity grows exponentially for the number of primary inputs, being viable only with tiny circuits. This is true not only for AIGs but also for any other way to represent and simulate a circuit.

As all the possibles outcomes of a signal are only two possible values, we may state equations 2.3 and 2.4 complement each other, meaning that if the probability of a node being *true* is known its probability of being *false* may also be calculated and vice versa.

$$P(f = 1) = 1 - P(f = 0)$$

(2.3)

$$P(f = 0) = 1 - P(f = 1)$$

(2.4)

Such a task of calculating the probability of all nodes in a logic circuit or even in an AIG representation is not trivial. It is yet to be discovered an algorithm that can calculate the exact value of signal probabilities in a logic circuit, so far heuristics have been used to do so (FLAQUER et al., 2010; ANGLADA et al., 2016). On the other hand, with the fact that a training dataset supplements a NN trained with supervised learning, it may be used to calculate the probability of internal nodes in an AIG that implements a NN. When we calculate the probability of nodes, we would like to take into consideration all possible input vectors. On the other hand, if we use the NN's training set, we are not calculating such probability based on the whole set of possible combinations of inputs. However, a calculation based on the behavior denoted by the training set, which usually has a large number of items. In other words, the training set allows the nodes probabilities calculation based on the input pattern behavior of the problem to be classified or solved by the NN.

# 2.1.3 AIG Simplification Under Constants

In this section, we shall demonstrate how a circuit in an AIG format has some of its nodes removed when constant variables are present. A variable that is a constant may be a constant-1 or 0. It is a node present in the AIG in which its value never changes, regardless of the input vector that is being applied on the AIG. There is no possible combination of inputs that may flip a constant.

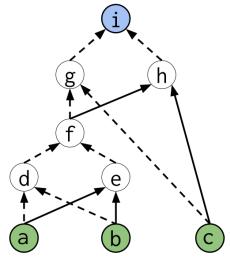

If we assume that the XOR's PI node b from Figure 2.1 is a constant-1, then we would be able to propagate this signal along the XOR in AIG format. Figure 2.2a shows the constant propagation process. Notice that PI b was set as 0, while the other PIs remain the same variables. Then the constant is propagated along the graph. This may be done with a *depth first search* starting from the AIG's POs. Any node that a constant reaches will also be a constant, except when a constant-1 reaches a node jointly with a non-constant. In this case, the constant ceases to exist. In Figure 2.2a, it can be seen that after propagation the constant on node b ended up removing three nodes and in node f (referencing Figure 2.1) the constant met the non-constant propagated as a and ceased to exist.

Since all nodes in an AIG are two-input AND nodes, we may make some as-

sumptions based on the logic AND behavior in the presence of a constant variable. Table 2.1 shows the truth table of an AND logic with the variable b as a constant-0 and as a constant-1. Notice that when the PI b is set to 0, this AND node fanout will always be 0, and when the PI b is set to 1, its fanout will always replicate the other non-constant fanin. In both cases, a node representing this AND logic with a constant as input may be removed. Applying this simplification to the XOR in Figure 2.2a supposing PI b is a constant-0, we get as a result from the AIG in Figure 2.2b, which has fewer nodes than the original AIG.

Table 2.1: AND logic under constants.

| constant-0 |   | constant-1 |   |   |         |

|------------|---|------------|---|---|---------|

| a          | b | a AND b    | a | b | a AND b |

| 0          | 0 | 0          | 0 | 1 | 0       |

| 1          | 0 | 0          | 1 | 1 | 1       |

Source: The Author

#### 2.1.4 Structural Hashing

When the propagation of constants simplifies an AIG, several re-connections are made in the AIG. For example, the AIG in Figure 2.2 had a replacement of the fanin for the two white nodes that remained after simplification. The replacement was the PI a. But let us assume that the resulting AIG after simplification was the one from Figure 2.3a with some polarity connections modified, notice that in this case, both white AND nodes have exactly the same pair of fanins: (! a \* c). These two nodes are redundant. One node is sufficient to represent this intermediate logic inside the AIG. The structural hashing technique is used to resolve such a problem. It consists of using a *hash table* to store each node's fanin information. The key value for the hash is the combination of the node's fanin pair. For each re-connection done during simplification, a new key is generated for the reconnected node, and a lookup is realized in the hash table to check if the new key is already present in an existing hash instance. If it is, a new fanout connection on the existing node is added, while the redundant node generated is disregarded. If otherwise, the new key is not found, the key value of the node that was reconnected must be updated in the hash table. Figure 2.3b presents the case where one of the repeated white nodes was found in the hash table and added as a fanout on the located node.

Notice in the resulting AIG from Figure 2.3b that the output node ends up having

Figure 2.3: Structural hashing usage on example AIG.

the same nodes in its two fanins, this follows the *idempotent* rule of boolean algebra, meaning that for an arbitrary boolean variable we may state A \* A = A, or even for the example demonstrated in Figure 2.3b: (!a \* c) \* (!a \* c) = (!a \* c). Then, following the simplification process in the AIG, re-connections are done on the PO's fanins and its key value on the hash table is to be updated, although the fanins both have the same value, this way we may remove the current PO and set the intermediate node with logic (!a \* c)as the new PO, resulting in the AIG from Figure 2.3c.

The process demonstrated in Figure 2.3 presents two different situations that the re-connections done during simplification may bring to the nodes in the simplified AIG. They are both unnecessary for the AIG's structural representation, increasing the logic depth and number of nodes and they should be always treated when they occur. The experiments executed in this work presented a relatively rare occurrence of such situations, occuring in no more than 1% of the nodes for the AIGs used in this work.

## 2.2 Neural Networks

The study of NNs for image recognition dates back to the late 80's (HAYKIN, 1994; BISHOP et al., 1995), although its practical usage on real world applications could only be happening now a days in the world, with the introduction of IoT devices for example. Aside from this influences on the research area but also the introduction of *Big Data*, thanks to people that work hard to assemble and label images in a large scale is one of the factors that allowed this technology of image recognition by NNs to grow as much. The proper compiling of image datasets allows for an outstanding development of

supervised training of NNs in a substantially low amount of years (GYSEL, 2016; MIT 6.S191, 2019).

Competitions and contests are a competent approach to motivate researchers into finding better solutions for present unsolved or partially solved problems. The ImageNet challenge ILSVRC has demonstrated great improvements in the last 10 years among the solutions proposed by competitors (RUSSAKOVSKY et al., 2015). The introduction of *Convolutional Neural Networks* (CNN) was a remarkable achievement, since the first time a CNN won the competition with AlexNet (KRIZHEVSKY; SUTSKEVER; HINTON, 2012) the accuracy results presented by competitors improved significantly, to a point that every winner since 2012 made use of CNNs, even coming to surpass human capabilities in image recognition after further improvements with ResNet (HE et al., 2016). These NNs are composed of millions of parameters and demand for billions of operations bringing an extremely high demand to its hardware implementation (GYSEL, 2016; XU et al., 2018).

A great part of the development in NNs for image recognition comes with the increment of deeper NNs, for example the ResNet comes with the cost of being composed of 152 layers of neurons. In the NNs proposed in this work, the NNs have only 3 fully connected layers and they already exceed at least 25 times the number of nodes than the largest AIG presented in the IWLS contest of 2019 (International Workshop on Logic and Synthesis, 2019). With such high requirements, optimization processes that enable a more compact NN should enhance the capability of building neuromorphic hardware.

#### 2.2.1 Neural Network Structure and Learning

In this section we shall briefly explain the structure and the learning process of NNs and how they are able to learn to classify input images. In its essence a NN is nothing more than a mathematical model composed of a network of multiple MAC operations. A NN may be represented by an interconnected number of neurons and we shall begin by explaining how the neuron structure work, followed by the non-linearity aspect of the NN and also how to learning process takes place.

# 2.2.1.1 The Neuron

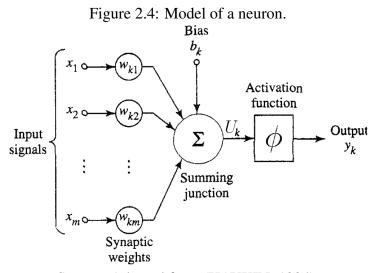

The basic building block of a NN is the neuron, inspired by the structure of a living being's brain. Figure 2.4 demonstrates an illustration of a model of a neuron denoted by k,

it is composed of an arbitrary number of input signals  $x_1, x_2, ..., x_m$  and an output  $y_k$ , each input connection (synapse) is composed of a *weight* value  $w_{k1}, w_{k2}, ..., w_{km}$  multiplied by its referenced input signal x. Equation 2.5 demonstrates the summation of all input synapses for neuron k.

Source: Adapted from (HAYKIN, 1994).

$$U_{k} = \sum_{j=1}^{m} w_{kj} x_{j}$$

$$= w_{k1} x_{1} + w_{k2} x_{2} + \dots + w_{km} x_{m}$$

(2.5)

The neuron from Figure 2.4 also consists of an *activation function* denoted by  $\phi$ . There are different types of activation functions and their purpose is to convert the neuron's output to be non-linear. This limits the amplitude of its output to a finite value. The neuron's model is composed of a *bias* value, denoted by  $b_k$ , it is an additional parameter that is used to adjust each neuron's output along with the inputs *weighted sum*. Thus, the bias is a constant which helps the model in a way that it can fit best for a given type of data. That being said, Equation2.6 presents the function for the neuron's output value denoted by  $y_k$ , where the bias is simply a constant added to the sum and  $u_k$  is a summation. The output of the neuron is then given by these two variables applied to the activation function. The bias and the activation function of a neuron are used to improve the NN's learning capabilities and the NN's weights are iteratively modified to find weight values that output the proper labeling for the input images. This updating of the weights is the learning process properly said. An important measurement for a NN is its accuracy, which in supervised learning classification, is defined as the number of elements that the NN was able to correctly classify for the training set or the test set (HAYKIN, 1994; BISHOP et al., 1995; NIELSEN, 2015).

$$y_k = \phi(U_k + b_k) \tag{2.6}$$

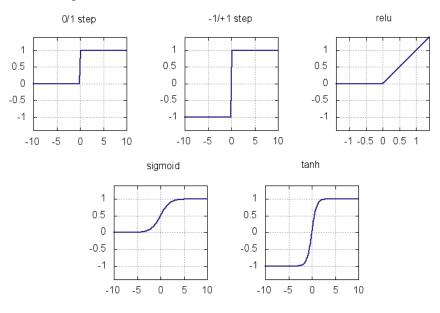

#### 2.2.1.2 Activation Functions

Figure 2.5 presents five different activation functions and demonstrates how each of them modifies the neuron's output  $y_k$  with regard to a range of  $u_k$  values. The purpose of an activation function is to make the neuron's output to be non-linear and different activation functions present different distribution of values for certain types of data. In the *Rectified Linear Unit* (ReLu) for example, its non-linearity lies in the fact that for every negative  $U_k$  value it renders a  $y_k$  value of 0, while for values of  $U_k$  greater or equal to 0 the function's output is the same. Without its non-linear aspect, the ReLu function would be the *identity function*  $y_k = u_k$ . The addition of non-linear. The neuron's function is done because real world problems are almost always non-linear. The neuron's activation function calculation is the last procedure done by a neuron. If the neuron is not an output neuron, its output will be connected to the input signal of another neuron (HAYKIN, 1994; BISHOP et al., 1995; NIELSEN, 2015).

The Sigmoid activation function used to be the most frequently used in NNs (GY-SEL et al., 2018), but it has an issue during learning called the *vanishing gradient* with regards to the loss function, which is an equation used during training to measure the NN's learning rate. For this reason the ReLu was introduced by (NAIR; HINTON, 2010), which solves the vanishing gradient problem and it is present in most state-of-the-art NNs' activation functions (GYSEL et al., 2018).

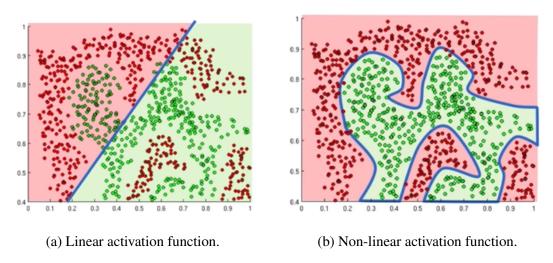

Figures 2.6a and 2.6b presents an example of classifications done by two NNs which differ with their activation functions used in their neurons. These types of graphs are called *feature spaces*. Their data points represent the input dataset and the NN would be responsible for dividing the feature space. In the examples presented, we have a NN with two input neurons, one represented by the vertical axis and and the other by the horizontal axis. No matter the size of a NN, if a linear activation function is used, the NN will only be able to linearly divide the feature space, like in Figure 2.6a, on the other hand if a non-linear activation function is used one is able to modify the NN's weights and achieve a division such as in figure 2.6b. Real world problems actually

Figure 2.5: Set of activation functions for a neuron.

Source: Adapted from (BAGCHI, 2019).

have many more inputs required, a NN model might even have millions of inputs and the visualization of its feature space is unfeasible, although the example demonstrated should give a better understanding on how a NN classifies the input set presented (MIT 6.S191, 2019; HAYKIN, 1994; BISHOP et al., 1995; NIELSEN, 2015).

Figure 2.6: Feature space for neural networks with different activation functions.

Source: (MIT 6.S191, 2019)

# 2.2.1.3 Fully Connected Layer

If we stack up an arbitrary number of neurons, we would have a *layer*, and if we put together an arbitrary number of layers, we would have a Neural Network. A layer

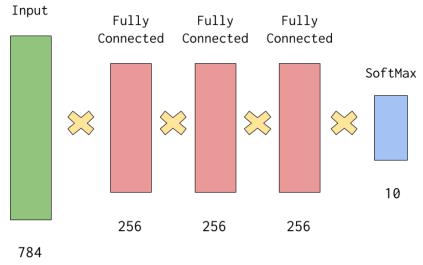

may be an *input layer*, an *output layer* or a *hidden layer*. The purpose of a layer is to extract *features* from the input data, a feature being a certain portion of the image in which may be frequently found in images belonging to the same category. There are different types of hidden layers with different approaches to extract features from input data, sometimes by having a different type of activation function on its neurons or a different set of connections among neurons, such as a convolutional layer, soft-max, maxpooling, ReLu or fully connected layer. The latter being the most straight forward one (NIELSEN, 2015; MIT 6.S191, 2019). Even though the great advancements in NNs is due to the introduction of *convolutional neural networks*, for the sake of simplicity, in the present work we shall bring our focus to fully connected layers, since our focus is not to improve the capabilities of NNs but to reduce their complexity in their boolean representation.

Figure 2.7 presents a *feedforward* NN with a *fully connected* hidden layer. This NN is called feedforward because it doesn't have any cycles, *recurrent neural networks* are the ones that would have such configuration (NIELSEN, 2015). In our feedforward example, we have only one hidden layer, and each of its neurons is connected to all neurons in the input layer and all neurons from the output neuron. The NN presented in Figure 2.7 has the goal of identifying handwritten digits from the images in the *Modified National Institute of Standards and Technology* (MNIST) dataset (DENG, 2012). The NN is composed of 784 neurons in the input layer since the image area is composed of 28 \* 28 = 784 pixels; this way, we have one neuron for each pixel in the image. The pixel is a grey-scale ranging from 0 to 255, 15 neurons for the fully connected layer, and 10 neurons in the output layer, one for each labeling of the digits (NIELSEN, 2015; HAYKIN, 1994; BISHOP et al., 1995).

The purpose of a neuron in the hidden layer is to detect *features*, which are patterns with a frequent occurrence among the input images. For example, the shape of an object or letter. The idea is to modify the weights of the synapses during learning in such a way that the features may be identified. Figure 2.8 presents a set of features for the digit 0. We could say, for example, that the first four neurons in the hidden layer are each one responsible for identifying each of the four features. This is settled by applying high weight values for the synapses that are connected to the set of input neurons that represent the feature's drawing (NIELSEN, 2015; HAYKIN, 1994).

Hidden Layer 28p **Output Layer** 0 28p 1 2 3 Input Layer Δ 784 neurons 5 6 7 8 9 Source: Adapted from (NIELSEN, 2015). Figure 2.8: Example of a set of features for the digit 0.

Figure 2.7: Fully connected single layer neural network for recognition of the MNIST dataset.

Source: Adapted from (NIELSEN, 2015).

#### 2.2.1.4 Pooling Layer

While a fully connected or a convolutional layer is used to identify features in the input data, a *pooling* layer is responsible for summarizing the average presence of a feature and the most activated presence of a feature. In other words, the pooling layer is responsible for downsampling the present features in the input. It manipulates the features by reducing the data dimensions by summarizing the output of batches of neurons into a single neuron. Pooling layers are mostly seen on the final layers of a NN, but some times may be used in between layers to streamline the computation. To mention a few types of pooling layers that are commonly seen: *max-pooling*, where it retrieves the maximum value between a batch of neurons in the previous layer. *Average-pooling*, which retrieves the average values among a batch of neurons in the previous layer. And *soft-max* pooling layer in which assigns decimal probabilities to each class. In other words, we would have one neuron for each class that the NN is responsible for classifying, where each neuron has a value range of 0.0 up to 1.0. The summation among the neurons in the soft-max layer adds up to 1.0; this way, the soft-max outputs the probability that input has to be

classified in each class, according to the NN.

#### 2.2.1.5 Learning

For a NN trained with supervised learning, it needs something to learn from. Image datasets are then used, and there are different datasets available online with a vast amount of types of images such as animals, vehicles, objects and so forth. For example the CIFAR (KRIZHEVSKY; HINTON et al., 2009), the MNIST (DENG, 2012) or even the ImageNet (YANG et al., 2019) datasets are commonly used in researches on the topic of NN for image recognition. This type of learning based on previously known data is called *supervised learning*. It may be used on other types of datasets, aside from images, such as sound recording, video and text speech (HAYKIN, 1994; BISHOP et al., 1995; NIELSEN, 2015).

To measure a NN's learning rate, a *loss function* is used. It is calculated after feeding the NN with all of the input elements and iteratively modifying it to find weight values that output the proper labeling for the inputs. This updating of the weights is the learning properly said (HAYKIN, 1994; BISHOP et al., 1995; NIELSEN, 2015).

A fully connected NN may be represented with a matrix-vector product, such as demonstrated by Equation 2.7, the variable  $\mathbf{y}$  represents the output vector for each of the output neurons,  $\mathbf{x}$  represents the input vector,  $\mathbf{W}$  the weights matrix for all layers,  $\mathbf{b}$  the bias vector for each layer.

$$\mathbf{y} = \mathbf{W} \cdot \mathbf{x} + \mathbf{b} \tag{2.7}$$

The output vector from the NN in Figure 2.7 would be a 10-dimensional vector **y**, remember that this NN classifies the MNIST dataset composed of handwritten digits ranging from 0 to 9. And for an input image represented as a vector **x** the NN's output is given by  $\mathbf{y}(\mathbf{x})$ . For example, if an input image is labeled as a 5, we would want the NN's output to  $\mathbf{y}(\mathbf{x}) = \mathbf{t}(\mathbf{x}) = (0,0,0,0,1,0,0,0,0)$ , the variable **t** being the *target* for the input **x**. The idea is to modify the weights and bias of the NN so that its output  $\mathbf{y}(\mathbf{x})$  approximates to  $\mathbf{t}(\mathbf{x})$  for the training inputs **x**. Equation 2.8 presents the *cost function* denoted by *C*, also known as *loss function*, which maps the error for all the neurons in the NN into a real value. This equation is the quadratic cost function and it is also known as the *mean squared error* calculated for all of the NN's neurons (HAYKIN, 1994; BISHOP et al.,

$$C(\mathbf{W}, \mathbf{b}) = \frac{1}{2n} \sum_{\mathbf{x}} ||\mathbf{t}(\mathbf{x}) - \mathbf{y}(\mathbf{x})||^2$$

(2.8)

In Equation 2.8 the target for an input  $\mathbf{x}$  is denoted by  $\mathbf{t}(\mathbf{x})$ , the actual output value being  $\mathbf{y}(\mathbf{x})$  and *n* the number of training inputs. Notice that the function  $\mathbf{y}(\mathbf{x})$  is dependent on the NN's weights denoted by  $\mathbf{W}$  and we wish to find a set of weight values that approximates every input  $\mathbf{x}$  to its target  $\mathbf{t}(\mathbf{x})$  and this is achieved by minimizing the cost function. The learning problem consists of searching for a set of weight values denoted by  $\mathbf{W}^*$  in the cost function space that has a small cost (HAYKIN, 1994; BISHOP et al., 1995; NIELSEN, 2015).

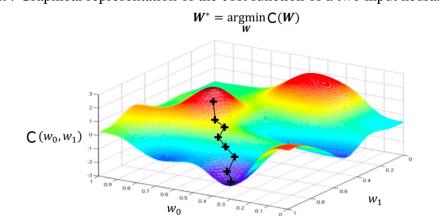

Figure 2.9 presents an hypothetical cost function space for a NN with only two inputs, the weight set for each input is defined by the  $w_0$  and the  $w_1$  axis, while the  $C(w_0, w_1)$  shows the cost achieved for every weight value between 0 and 1. In realworld applications, some NN might have even millions of input neurons, and the graphical representation of such NNs is not suitable. Also, during training, it is impractical to compute all the possible combination of weights to find out which is the lowest cost function possible, heuristics are then used to find an acceptably small enough cost function to define the NN's weights (HAYKIN, 1994; BISHOP et al., 1995; NIELSEN, 2015).

Figure 2.9: Graphical representation of the cost function of a two input neural network.

Source: Adapted from (MIT 6.S191, 2019).

The goal of the learning process is to search for the minimal cost function by modifying the weights of the NN. The *gradient descent* technique may be used to do so, the gradient being the partial derivative of the loss function. The gradient is calculated iteratively, each time updating the NN's weight values, to look for the nearby minimum value in the loss function space. The process known as *backpropagation* is used to calculate the gradients of all layers in a NN, where the partial derivatives are calculated layer by layer. The iterative calculation of the gradient descent is illustrated in Figure 2.9. It is represented by the updating of weight values in the NN and is depicted as a few connected black data points cross following a downwards path in the cost function space. An improvement in the gradient descent technique is the *stochastic gradient descent*, which increases the reach of the search space and speeds up the learning process by making use of batches of training set instances (HAYKIN, 1994; BISHOP et al., 1995; NIELSEN, 2015).

During training of a NN *epochs* are used, where an epoch is the number of times a NN completes a full cycle reviewing the whole training set, in other words, when we say a NN was trained with 100 epochs, the NN went through the whole training set 100 times and each time modifying its weight values. If a NN is trained with too many epochs, it tends to get *overfitted*, where an overfitted NN is too attached to the training set. For example, if we are building a NN model able to recognize dogs present in an image and its training set happens to be composed of dogs only facing left, it might not be able to recognize dogs facing to the right, if too many epochs are used. The overfitting of a model is defined by the difference in accuracy it gives from the training set to the accuracy resulting on the test set. If it provides a high accuracy for the training set and a lower accuracy for the test set, it may be considered an overfitted NN. We would like for a NN to perform well on unseen data, then we may say that usually, we would not like for a NN to be overfitted.

#### 2.2.1.6 Random Forest

A *Random Forest* or *Random Decision Forest*, as it is also known, is another technique of machine learning aside from NNs. Like with NNs, a RDF may be used to solve *classification* or *regression analysis* problems. An RDF is composed of multiple amounts of *decision trees*, where its random aspect brings the ability to overcome the overfitting lead by the usage of simple decision trees. The input is presented at the tree branches (also known as conjunctions of features), while the classification is given as output at the leaves (FRIEDMAN; HASTIE; TIBSHIRANI, 2001).

## 2.2.2 Neuromorphic Hardware

The desire for superior processing power and storage capacity brings researchers to explore different manufacturing implementations than the usual technologies. Accelerators are becoming acclaimed alternatives besides conventional designs, although this is only the case for specific types of workloads such as Machine Learning in general. Hardware accelerators for NNs are an emerging technology, and there is not an established standard design for it yet. So far, the technologies that have been proposed for NNs dedicated hardware are based on CPU, FPGA, GPU, and ASIC designs. However, as stated by (XU et al., 2018; NURVITADHI et al., 2017) GPU implementations are staggering on their processing power capabilities, ASIC designs seem to be more promising strategies since they are achieving better performance density overall. On the other hand, some works such as (NURVITADHI et al., 2016; NURVITADHI et al., 2017) show that there might be a reascend for FPGA designs for NNs, with future improvements on this technology, at the very least FPGAs are performing better than GPU designs.

The need for edge inference is growing larger. So far, companies adopt the usage of large scale servers in data centers for cloud-based inference. For example, as stated by (LECUN, 2019), Facebook executes  $3 * 10^{14}$  predictions each day on their data-centers and the need for better performance density on devices grows larger (NURVITADHI et al., 2017).

Memristors are resistive devices able to both store and process information. They recently have been used to implement NNs accelerators and demonstrate good results on its processing capabilities, because it allows high processing elements density with good power efficiency. Memristors are built in a crossbars fashion to emulate plastic synapses in hardware devices. This approach is a good candidate to be explored because of its efficient matrix-vector multiplication, and NNs happen to require large amounts of such arithmetic (HU et al., 2016; JO et al., 2010; LI et al., 2018). A new approach to the usage of hardware accelerators for NNs is presented in the work (ZHOU et al., 2018) that exploits the sparsity characteristic of NNs. Their design achieves higher power efficiency and speedup when compared to the previous state-of-the-art NN accelerator published at (CHEN et al., 2014).

The works (AKOPYAN et al., 2015; DEBOLE et al., 2019) introduces a complete Design Flow for their neuromorphic hardware implementation. It is an event-driven, configurable, and scalable design, and it is said to be the "largest neurosynaptic computer

ever built" with 256 million low-precision synapses and 1 million neurons on a spiking NN system. This design also has a crossbar fashion like memristors implementations, but its processing elements are made of their proposed neurosynaptic cores instead of memristors.

With the high processing power requirement that NNs bring, it is a hard challenge to manufacture a trained NN as an affordable chip. There have been a fair amount of proposed ways to compact NNs, mainly by handling its parameters like weights and synapses, during or after training, for example. But not as much has been done in the logic circuit level of abstraction. When we work at this stage we are attempting to reduce the parameters of a NN's logic representation like its number of nodes in an AIG or even its logic depth. In the subsections to come we present two approaches researchers take to compact NNs, the first and most common is focused on optimizing the NN by handling its core parameters like weights and synapses and another direction to reduced neuromorphic hardware requirements, which is most related to this work, where optimizations are applied to the boolean representation or logic circuits that represent NNs.

#### 2.2.3 Neural Network Optimizations

Among the existing optimizations proposed by researchers, approximate computing is commonly one used to reduce the complexity of NNs (WANG et al., 2017; GYSEL, 2016; HAN; ORSHANSKY, 2013). For example, the quantization technique, which consists of reducing the number of bits to compose the digital representation of the NN's decimal values, is seen to be studied and used. Different approaches to do so are proposed. In (GYSEL et al., 2018), the need for multiply operations is reduced some times even completely removed, leaving adder-only arithmetic for the NN's implementation in hardware. This work uses an approach of *dynamic* fixed-point quantization (COURBARIAUX; BENGIO; DAVID, 2014), where different parts of the NN take different fixed-point lengths for the fractional part. Other works also make use of fixedpoint arithmetic and attempt to quantize the bit-width of parameter representation (LIN; TALATHI; ANNAPUREDDY, 2016; HWANG; SUNG, 2014; SUNG; SHIN; HWANG, 2015; GUPTA et al., 2015). The works (COURBARIAUX; BENGIO; DAVID, 2015; HWANG; SUNG, 2014) can quantize the NNs to have binary weights and prove to achieve the slight loss in accuracy with such a simple representation for the NN's parameters. The quantization approach is an approximate computing strategy since it reduces the numerical representation of parameters.

Another common approach to reducing NN parameters is the pruning technique, in which attempts to cut-off pieces of the NN but preserving its accuracy. Pruning may be applied at network connections and removes unnecessary ones by learning which synapses are essential or even searching for redundant ones. This way, making a sparser version of the NN. The motivation behind the pruning procedure is on top of the assumption that NNs tend to be over parametrized, and similar accuracy may be obtained by making them smaller. In reference (LEE; AJANTHAN; TORR, 2018), pruning is applied before training in a single run, unlike other previous pruning approaches such as (HAN et al., 2015; HAN; MAO; DALLY, 2015; KARNIN, 1990; CARREIRA-PERPINAN; IDELBAYEV, 2018), in which require iteratively retraining of the NN. A commonly used pruning measurement is by limiting the magnitudes of the weights, where weights smaller than a certain threshold are removed (LEE; AJANTHAN; TORR, 2018; HAN et al., 2015; CARREIRA-PERPINAN; IDELBAYEV, 2018).

To cite some other techniques commonly seen and well accepted in the research area of compacting NNs: rank approximation (JADERBERG; VEDALDI; ZISSERMAN, 2014), structured sparsity (WEN et al., 2016), weight sharing (ULLRICH; MEEDS; WELLING, 2017; HAN et al., 2016), since it is common for a NN to have multiple similar weight values, the NN complexity is reduced by putting similar weight values in bins and retraining the NN with the binned values. Specifically, the work (HAN et al., 2016) discovered that 16 weight values are sufficient in many cases.

### 2.2.4 Boolean Optimizations for Neural Network Circuits

Approximate computing is a design paradigm that has proven to be an efficient resource saver in application level and consequently at the hardware level. A good amount of effort has been put in to reduce the NN's parameters. However, only a few works propose to optimize algorithms for logic synthesis that are driven by NN characteristics.

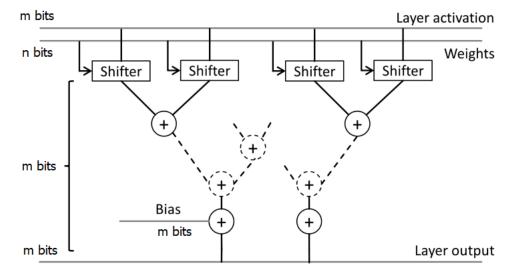

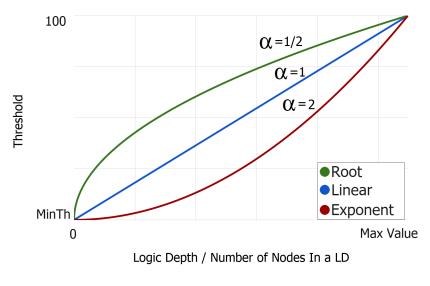

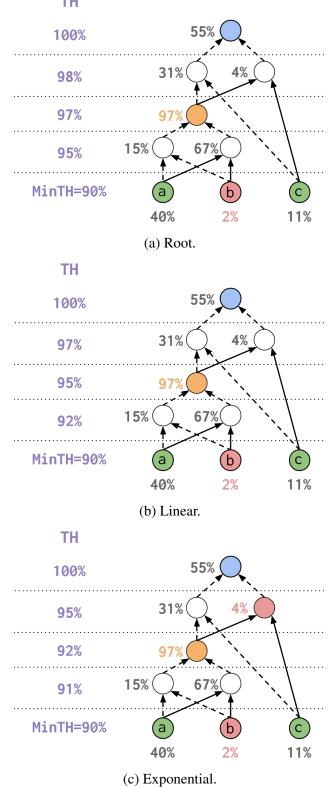

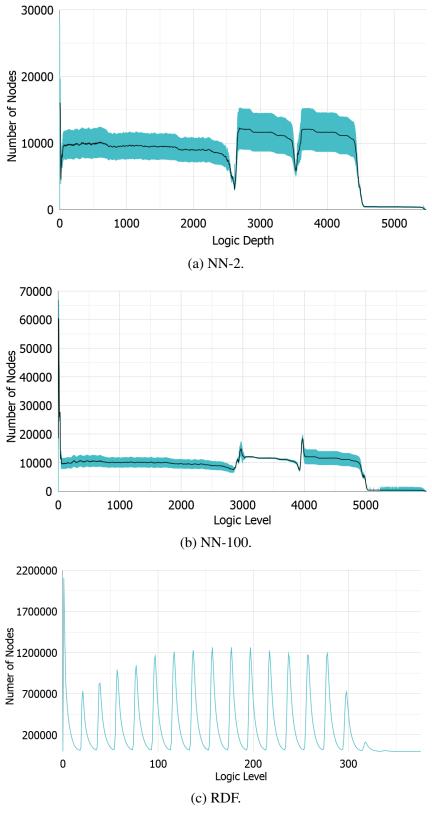

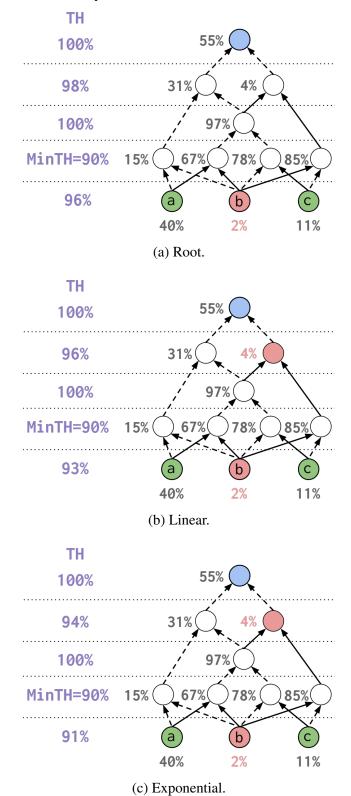

In reference (NAZEMI; PASANDI; PEDRAM, 2019), it is presented as a method to compact NNs implemented in FPGA. They propose a way to implement the logic of a neuron based on the input combinations by creating a truth table for the neuron, then limiting its exponential growth, where the NN's training set defines this limitation. With that, they can reduce the use of MAC operations. The digital implementation of the neurons in the NN is not done by realizing the dot product among weights and signals, but by synthesizing the logic representation of the neuron based on the training set. It is also implemented a shared logic when computing the neuron's combinational gate logic representation. Since neurons in the same layer may share the same inputs, their logic gate representation might also do. Results are shown based on NNs implemented with the use of MACs compared with their method, which uses fewer MACs, their method presents considerable savings in memory access due to fewer MACs required to implement the NN.