# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL ESCOLA DE ENGENHARIA PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA

# **JULIANO DE LIMA**

# METODOLOGIA PARA UTILIZAÇÃO DE CONTROLADORES PROGRAMÁVEIS STANDARD EM SISTEMAS DE SEGURANÇA

### **JULIANO DE LIMA**

# METODOLOGIA PARA UTILIZAÇÃO DE CONTROLADORES PROGRAMÁVEIS STANDARD EM SISTEMAS DE SEGURANÇA

Dissertação de mestrado apresentada ao Programa de Pós-Graduação em Engenharia Elétrica, da Universidade Federal do Rio Grande do Sul, como parte dos requisitos para a obtenção do título de Mestre em Engenharia Elétrica.

Área de concentração: Controle e Automação – Sistemas de Automação.

ORIENTADOR: Ivan Muller

Porto Alegre

### JULIANO DE LIMA

# METODOLOGIA PARA UTILIZAÇÃO DE CONTROLADORES PROGRAMÁVEIS STANDARD EM SISTEMAS DE SEGURANÇA

Esta dissertação foi julgada adequada para a obtenção do título de Mestre em Engenharia Elétrica e aprovada em sua forma final pelo Orientador e pela Banca Examinadora.

|                   | Orientador:                                                                                     |

|-------------------|-------------------------------------------------------------------------------------------------|

|                   | Prof. Dr. Ivan Muller, UFRGS                                                                    |

|                   | Doutor pela UFRGS- Porto Alegre, Brasil                                                         |

| Banca Examinadora | ı:                                                                                              |

|                   | Eckard, UFRGS<br>niversidade Federal do Rio Grande do Sul – Porto Alegre, Brasil                |

|                   | n Pignaton de Freitas, UFRGS<br>niversidade Federal do Rio Grande do Sul – Porto Alegre, Brasil |

|                   | elo Götz, UFRGS<br>niversität Paderborn – Paderborn, Alemanha                                   |

|                   | Coordenador do PPGEE:                                                                           |

|                   | Prof. Dr. João Manoel Gomes da Silva Junior                                                     |

Porto Alegre, Março de 2020.

# **DEDICATÓRIA**

Dedico este trabalho a todos que de certa forma contribuíram para que eu conseguisse concluir este grande projeto, em especial à Universidade Federal do Rio grande do Sul que me recebeu de portas abertas, aos professores que muito me ensinaram neste período, aos colegas e amigos que fiz nesta jornada e aos familiares que me deram todo apoio. Muito obrigado.

# **AGRADECIMENTOS**

Ao Programa de Pós-Graduação em Engenharia Elétrica, PPGEE, pela oportunidade de realização de trabalhos em minha área de pesquisa.

Aos professores do PPGEE pelos ensinamentos e pela oportunidade de ingresso ao programa.

Aos colegas de aula pelo auxílio nas tarefas desenvolvidas durante o curso e apoio na revisão deste trabalho.

Ao professor Ivan pela paciência, persistência e sabedoria na sua condução dos seus orientandos.

À minha esposa pela colaboração e disposição para que eu conseguisse estudar.

Aos meus filhos pelo estímulo, energia e inspiração para seguir no caminho.

## **RESUMO**

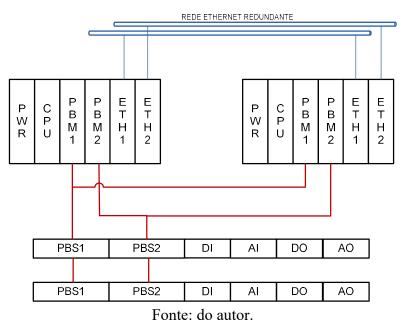

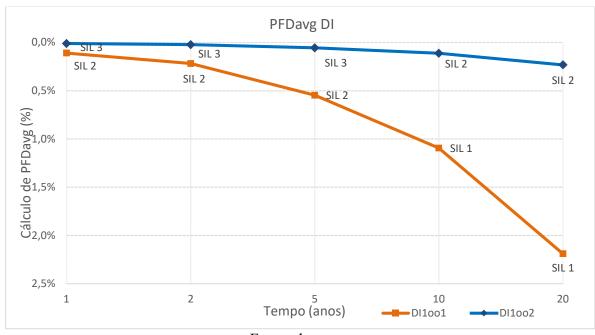

O uso de controladores programáveis dedicados à segurança de plantas industriais desempenha um papel fundamental em um Sistema Instrumentado de Segurança – SIS. Estes equipamentos são certificados de acordo com o Nível de Integridade de Segurança - SIL, classificados a partir de quatro níveis, onde as principais métricas para determinação destes níveis são: disponibilidade, probabilidade de falha na demanda e fator de redução de risco. O custo de uma plataforma certificada para Sistemas de segurança é muito elevado podendo inviabilizar um projeto onde a certificação pode não ser a exigência principal. Diante deste fato, este trabalho apresenta um estudo para utilização de controladores programáveis standard não certificados, para que sejam empregados em funções de segurança de processos industriais. Foram propostos estudos comparativos das principais métricas de confiabilidades entre os controladores standard e de segurança, onde cálculos de tempo médio entre falhas – MTBF, disponibilidade, probabilidade de falha na demanda e fração de falha segura são apresentados. De acordo com os dados apresentados por fabricantes de controladores standard, pode-se atingir métricas de segurança SIL a partir de aplicação de arranjos de arquiteturas e cálculos das métricas supracitadas. Conforme apresentado neste texto, uma plataforma de controlador standard formada por fonte, CPU e módulos de comunicação em um chassi e módulos de entrada e saída em um outro chassi montados em um arranjo de arquitetura 1001 resultou em métricas SIL 2 para intervalos de teste de cinco anos. A mesma plataforma formada por um sistema redundante do tipo Hot-Standby formado por fonte, CPU e módulos de comunicação montados em dois conjuntos distintos e módulos de I/O em arranjo 1002 resultaram métricas SIL 2 para intervalos de testes de vinte anos, intervalo médio utilizado para certificação SIL.

Palavras-chave: Safety Integrity Level, Disponibilidade, Probabilidade de Falhas, Segurança Funcional, Arquiteturas de alta disponibilidade, Tolerância a falhas.

### **ABSTRACT**

The use of programmable controllers dedicated to the safety of industrial plants plays a fundamental role in the Instrumented Safety System - SIS. This equipment is certified according to the Safety Integrity Level - SIL, classified from four levels, where the main measures to measure the levels are: availability, probability of failure in demand and risk reduction factor. The cost of a certified platform for Security Systems is very high, making unviable a project where certification may not be the main principle. Thus, this study proposes use a standard programmable controller where certifications are not required, it can be used in safety functions of industrial processes. Comparative studies of the main reliability metrics between standard and safety controllers were presented, where calculations of mean time between failures -MTBF, availability, probability of failure in demand and fraction of safe failure are indicated. According to the data presented by the manufacturers of standard controllers, SIL security metrics can be achieved through the application of architectural arrangements and calculations of the metrics already said. As defined in this text, a standard controller platform consisting in: power supply, CPU, communication and input and output modules in another chassis mounted in a 1001 architecture arrangement resulted in SIL 2 metrics for five-year tests. The same platform formed by a redundant system (Hot-Standby) type formed by power supply, CPU, communication modules and I / O modules composed in two different sets 1002 arrangement resulted in SIL 2 measurements for test intervals of twenty years, interval medium used for SIL certification

Keywords: Safety Integrity Level, Availability, Probability of Failure, Functional Safety, High Availability Architectures, Fault Tolerance.

# LISTA DE ILUSTRAÇÕES

| Figura 1 - Falhas prematuras em sistemas de automação.                                      | 19 |

|---------------------------------------------------------------------------------------------|----|

| Figura 2 - Comparativo e hierarquia de normas de segurança funcional                        | 22 |

| Figura 3 - Fluxograma do ciclo de vida do projeto de um EP                                  | 25 |

| Figura 4 - Exemplo de um SIS com uma SIF                                                    | 27 |

| Figura 5 - Hierarquia dos sistemas instrumentados de segurança                              |    |

| Figura 6 - Diagrama básico da CPU de um EP standard                                         | 29 |

| Figura 7 - Diagrama simplificado de um módulo de entradas digitais                          | 30 |

| Figura 8 - Diagrama simplificado de um módulo de saídas digitais                            | 30 |

| Figura 9 - Diagrama simplificado de um módulo de entradas analógicas                        | 31 |

| Figura 10 - Diagrama simplificado de um módulo de saídas analógicas                         | 32 |

| Figura 11 - Diagrama de blocos safety CPU.                                                  |    |

| Figura 12 - Diagrama de blocos módulo de entradas digitais.                                 | 34 |

| Figura 13 - Esquema de interligação de sensores nos módulos de entradas digitais            | 35 |

| Figura 14 - Diagrama de blocos módulo SDOM                                                  |    |

| Figura 15 - Exemplos de ligações de cargas no módulo SDOM                                   |    |

| Figura 16 - Diagrama de blocos módulo de EA.                                                |    |

| Figura 17 - Diagrama de blocos módulo de saídas analógicas                                  | 38 |

| Figura 18 - RBD de um controlador standard.                                                 |    |

| Figura 19 - Cálculo RBD paralelo.                                                           |    |

| Figura 20 - Arquitetura 1001 de um controlador                                              |    |

| Figura 21 - Arquitetura 100D de um controlador                                              |    |

| Figura 22 - Arquitetura 1002 de um controlador                                              |    |

| Figura 23 - Arquitetura 2002 de um controlador                                              |    |

| Figura 24 - Arquitetura 1002D de um controlador.                                            |    |

| Figura 25 - Arquitetura 2002D de um controlador                                             |    |

| Figura 26 - Arquitetura 2003 de um controlador                                              |    |

| Figura 27 - Fluxograma de cálculo de PFD.                                                   |    |

| Figura 28 - Método de cálculo RBD resultante.                                               | 56 |

| Figura 29 - Arquitetura típica de um sistema de controle de plataforma de petróleo          |    |

| Figura 30 - Controlador standard com arquitetura 1001.                                      |    |

| Figura 31 - Controlador standard com arquitetura 1002.                                      |    |

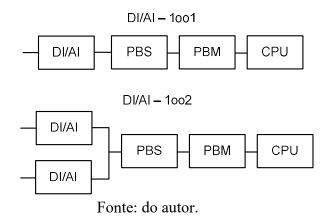

| Figura 32 - Diagrama RBD para circuitos DI/AI com arquitetura 1001 e 1002                   |    |

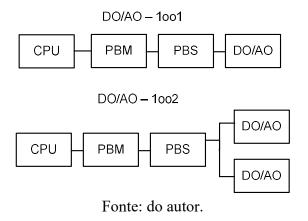

| Figura 33 - Diagrama RBD para circuitos DO/AO com arquitetura 1001 e 1002                   |    |

| Figura 34 - Gráfico PFD <sub>avg</sub> DI para intervalos de testes de 1, 2, 5 10 e 20 anos |    |

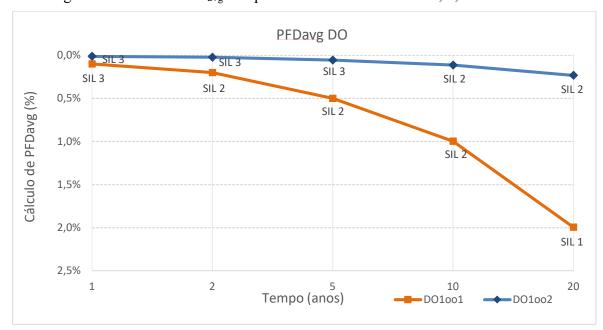

| Figura 35 - Gráfico PFD <sub>avg</sub> DO para intervalos de testes de 1, 2, 5 10 e 20 anos |    |

| Figura 36 - Gráfico PFD <sub>avg</sub> AI para intervalos de testes de 1, 2, 5 10 e 20 anos |    |

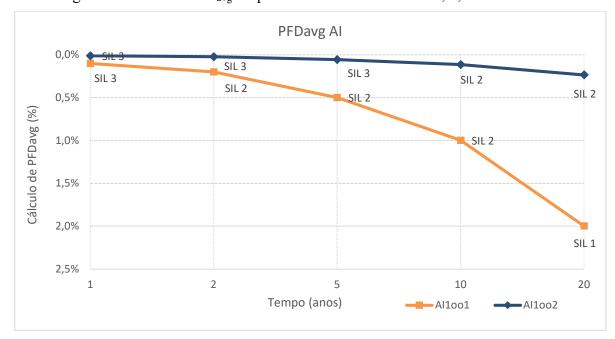

| Figura 37 - Gráfico PFD <sub>avg</sub> AO para intervalos de testes de 1, 2, 5 10 e 20 anos |    |

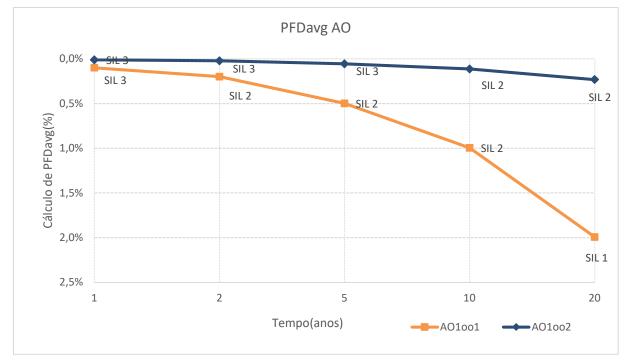

# LISTA DE TABELAS

| Tabela 1 - Divisão da IEC-61508.                                                  | 20 |

|-----------------------------------------------------------------------------------|----|

| Tabela 2 - Níveis de integridade e segurança – SIL.                               | 21 |

| Tabela 3 - Quadro resumo de arquiteturas EP SIL.                                  | 47 |

| Tabela 4 - Comparativo dos trabalhos relacionados                                 | 52 |

| Tabela 5 - Cobertura de diagnósticos e eficácia para diferentes elementos         | 59 |

| Tabela 6 - Lista de pontos de sistemas de segurança de uma plataforma de petróleo | 64 |

| Tabela 7 - Relação de valor do CLP standard com arquitetura 1001                  | 66 |

| Tabela 8 - Relação de valor do CLP standard com arquitetura 1002                  | 66 |

| Tabela 9 - Relação de valor do CLP SIL com arquitetura 1001D                      | 67 |

| Tabela 10 - Comparativo de custo CLP standard versus CLP SIL.                     | 67 |

| Tabela 11 - Memorial de cálculo dos módulos utilizados no estudo de caso          |    |

| Tabela 12 - PFD <sub>avg</sub> para DI arranjos 1001 e 1002                       | 70 |

| Tabela 13 - PFD <sub>avg</sub> para DO arranjos 1001 e 1002.                      | 71 |

| Tabela 14 - PFD <sub>avg</sub> para AI arranjos 1001 e 1002                       | 72 |

| Tabela 15 - PFD <sub>avg</sub> para AO arranjos 1001 e 1002.                      | 73 |

# LISTA DE ABREVIATURAS

ATEX Directive Appareils Destinés à Être Utilisés en Atmosphères Explosives

CE Conformité Européenne

**CPU Central Processing Unit**

DC Diagnostic Coverage

**DNV Det Nork Veritas**

EAC: Eurasian Union Conformity

**EPA Environmental Protection Agency**

E/E/EP Electrical/Electronic/Programmable Electronic

**ERP Enterprise Resource Planning**

IEC International Electrotechnical Commission

IED Intelligent Electronic Device

**HAZOP** Hazard and Operability Study

HSE Health and Safety Executive

LOPA Layer of Protection Analysis

MES Manufacturing Execution System

MooN M out of N channel architecture

MooND M out of N channel architecture with Diagnostic

MTBF Mean Time Between Failures

MTTF Mean Time to Fail

MRT Mean Repair Time

MTTFS Mean Time to Fail Safe

MTTR Mean Time to Repair

OSHA Ocupation Safety and Health Administration

PE Programmable Electronic

PFD Probability of Dangerous Failure on Demand

PFD<sub>avg</sub> Average Probability of dangerous Failure on Demand

PFH Average frequency of dangerous failure [h-1]

PTI Proof Test Interval

PLC Programmable Logic Controller

RBD: Reliability Block Diagram

RRF Risk Reduction Factor

SCADA Supervisory Control and Data Acquisition

SDIM Safety Digital Input Monitored

SDOM Safety Digital Output Monitored

SIF Safety Instrumented Function

SIL Safety Integrity Level

SIS Safety Instrumented System

SMCU Safety Microcontroller Unit

S-PLC Safety PLC

S-CPU Safety CPU

SRS Security Requirements specifications

SRCS Safety Related Control Systems

SFF Safe Failure Fraction

TCE Channel Equivalent Down Time

TGE System Equivalent Down Time

TMR Triple Modular Redundancy

**UL Underwriters Laboratories**

# LISTA DE SÍMBOLOS

| β ou CCF Common Cause Failure F | ou CCI | illion Cause Failule IX |

|---------------------------------|--------|-------------------------|

|---------------------------------|--------|-------------------------|

$\beta_d$  ou  $\text{CCF}_d$  Common Cause Failure Rate, Dangerous

λ Failure Rate

$\lambda_s$  Rate of Safe Failures

$\lambda_d$  Rate of Dangerous Failures

$\lambda_{dd}$  Dangerous, Detected Failure Rate

$\lambda_{du}$  Dangerous, Undetected Failure Rate

$\lambda_{su}$  Safe, Undetected Failure Rate

$\lambda_{\text{sd}}$  Safe, Detected Failure Rate

μ taxa de reparos

D disponibilidade

## LISTA DE NORMAS

EN/ISO 13849 Safety of Machinery – Safety-related Parts of Control Systems

EN 50126 Railway Applications – The Specification and Demostration of Reliability, Availability Maintainability and Safety (RAMS)

EN 50128 Railway Applications - Communication, Signalling and Processing systems - Software for Railway Control and Protection Systems

EN 50129 Railway applications – Communication, Signalling and Processing Systems – Safety Related Electronic Systems for Signalling

EN 54402 Electrical Apparatus for the Detection and Measurement of Combustible or Toxic Gases or Vapours or of Oxygen - Requirements on the Functional Safety of Gas Detection Systems

EN 50271 Electrical Apparatus for the Detection and Measurement of Combustible Gases, Toxic Gases or Oxygen - Requirements and Tests for Apparatus Using Software and/or Digital Technologies

IEC 61508 Functional Safety of electrical/Electronic/Programmable Electronic Safety-Raletade Systems

IEC 61511 Functional Safety – Safety Instrumented Systems for the Process Industry Sector IEC 62061 Safety of Machinery - Functional Safety of Electrical, Electronic and Programmable Electronic Control Systems

IEC 61513 Nuclear power plants - Instrumentation and control important to safety

IEC 61800 Adjustable speed electrical power drive systems

IEC-ACOS IEC Advisory Committee on Safety

EN 60079-X Electrical Apparatus for Explosive Gas Atmospheres

MIL-HDBK-217F Military Handbook, Reliability Prediction of Electronic Equipment

N 2595 Critérios de Projeto, Operação e Manutenção de Sistemas Instrumentados de Segurança em Unidades Industriais

# SUMÁRIO

| 1 INTRODUÇÃO                                         | 15 |

|------------------------------------------------------|----|

| 2 FUNDAMENTAÇÃO TEÓRICA                              | 18 |

| 2.1 SAFETY INTEGRITY LEVEL- SIL                      | 20 |

| 2.2 SAFETY IINSTRUMENTED SYSTEM - SIS                | 26 |

| 2.3 CARACTERÍSTICAS CONSTRUTIVAS DE UM EP STANDARD   | 28 |

| 2.3.1 CPU                                            | 29 |

| 2.3.2 Módulos de Entradas Digitais                   | 29 |

| 2.3.3 Módulos de Saídas Digitais                     |    |

| 2.3.4 Módulo de Entradas Ánalógicas                  | 31 |

| 2.3.5 Módulo de Saídas Analógicas                    | 32 |

| 2.4 CARACTERÍSTICAS DOS CONTROLADORES SIL            | 32 |

| 2.4.1 CPU SIL                                        | 33 |

| 2.4.2 Módulo de Entradas Digitais SIL                | 34 |

| 2.4.3 Módulo de Saídas Digitais SIL                  | 35 |

| 2.4.4 Módulo de Entradas Analógicas SIL              | 37 |

| 2.4.5 Módulo de Saídas Analógicas SIL                | 38 |

| 2.5 PRINCIPAIS DIFERENÇAS ENTRE EP STANDARD E EP SIL |    |

| 2.6 DIAGRAMA DE BLOCOS DE CONFIABILIDADE             | 39 |

| 2.7 ARQUITETURAS DE VOTAÇÃO                          | 41 |

| 3 TRABALHOS RELACIONADOS                             | 48 |

| 4 METODOLOGIA DE CÁLCULO DE CONFIABILIDADE           | 53 |

| 4.1 CÁLCULOS RBD                                     | 56 |

| 4.2 CÁLCULOS DE PROBABILIDADE DE FALHAS              | 57 |

| 5 ESTUDO DE CASO                                     | 62 |

| 5.1 LISTA DE PONTOS SIF                              | 63 |

| 5.2 ESTIMATIVA DE CUSTO DO SISTEMA DE SEGURANÇA      | 65 |

| 5.3 TESTES REALIZADOS                                | 67 |

| 6 CONCLUSÕES                                         | 75 |

# 1 INTRODUÇÃO

Segurança em processos industriais tem se tornado um requisito cada vez mais importante no cenário mundial, uma vez que acidentes graves em usinas nucleares, plantas petroquímicas, sistemas de transporte e armazenamento de combustíveis, por exemplo, causam grande impacto econômico, ambiental e pessoal. Estas causas têm se tornado intoleráveis aos órgãos competentes de cada país.

Normas específicas para aplicação e projeto de equipamentos dedicados a este fim foram desenvolvidas e têm sido aperfeiçoadas ao longo do tempo, como exemplo a IEC 61511, Safety Instrumented System - SIS e a IEC 61508 – Safety Integrity Level - SIL. A primeira norma citada descreve aplicações de sistemas de segurança voltados para indústria de processos e a segunda, conceitos e diretivas para desenvolvimento de equipamentos dedicados para aplicação em sistemas de segurança.

Controladores programáveis para sistemas de segurança, ou simplesmente *Electronic Programmable* (EP) conforme IEC-61508, são produtos desenvolvidos para executar lógicas de segurança de processos industriais, e são aplicados em medições de temperatura, nível, pressão, vazão, viscosidade entre outras variáveis de processos industriais, além da detecção de alarmes e comandos de *trip* (desligamento) dos processos em geral.

O ciclo de vida de projeto de um EP SIL consiste numa série de etapas e de uma documentação detalhada, devendo ser validada por algum órgão certificador, onde toda documentação deve passar por criteriosos processos de revisão a fim de garantir o sucesso da certificação do produto, tornando o processo lento e muito caro.

Por outro lado, controladores programáveis industriais não certificados, conhecidos na indústria como controladores de mercado ou controladores standard conforme designados neste trabalho, são equipamentos utilizados para controle do processo de máquinas e de plantas industriais, não sendo empregados em processos de segurança, não se abstendo de outras

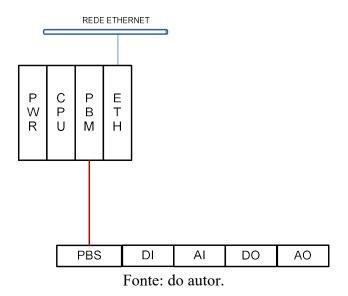

certificações e ou diretivas de qualidade e segurança, tais como, CE, UL, DNV, EAC entre outras. Os EPs standard são compostos de fontes, CPU, módulos de entrada e saída digitais e analógicas, conforme padronização da norma IEC 61131.

Em aplicações de missão crítica com controladores standard, arranjos especiais podem ser aplicados com o objetivo de atendimento dos requisitos das normas de segurança funcionais.

Conforme introduzido anteriormente, custo de uma plataforma certificada para sistemas de segurança é muito elevado podendo inviabilizar um projeto onde a certificação pode não ser a exigência principal. As normas referentes à segurança funcional são muito extensas e complexas, onde um projeto de um dispositivo certificado SIL pode levar muito tempo para ser concluído.

Diante destes fatos, este trabalho apresenta o estudo e o desenvolvimento de uma metodologia de projeto para utilização de controladores programáveis standard não certificados para que sejam empregados em funções de segurança de processos industriais, ou simplesmente utilizadas as mesmas técnicas para aplicações em processos de missão crítica. Esta metodologia resulta em arranjos e cálculos dos componentes a fim de atingir as mesmas métricas aplicadas nos equipamentos certificados. Este estudo pode ser aplicado em qualquer controlador standard de mercado que possua flexibilidade de arranjos de arquiteturas podendo popularizar a metodologia com objetivo de aumento de segurança funcional em processos críticos onde a certificação não foi exigida. A adoção desta metodologia pode contribuir para aumento de confiabilidade de máquinas e processos de automação mitigando o número de acidentes ocasionados por possíveis falhas de controladores programáveis e sistemas de instrumentação.

Como forma de validação desta dissertação, propõe-se um comparativo de atendimento às principais métricas de segurança entre controladores SIL e controladores programáveis standard, tanto ao atendimento de seus principais requisitos de segurança, quanto ao desempenho e confiabilidade necessária.

Através da forma de cálculo de redundância MooN e inclusão de taxas de falhas e cálculos de probabilidade de falha na demanda, um modelo de controlador standard de um fabricante brasileiro atingiu métricas de um controlador SIL2 para intervalo de testes de vinte anos. Para alcançar este objetivo, foi projetado um arranjo de arquitetura redundante nos chassis de fontes, CPUs e placas de comunicação e arquitetura 1002 para os módulos de aquisição de dados e saídas do sistema. Este trabalho está dividido da seguinte forma: No capítulo 1 é apresentada uma introdução do tema. No capítulo 2 é apresentada a fundamentação teórica, no capítulo 3 os trabalhos relacionados ao objetivo da dissertação. No capítulo 4 é descrita a metodologia adotada apresentando as principais formas de cálculo das métricas envolvidas em um projeto de EP SIL. No capítulo 5 é apresentado o estudo de caso e os resultados obtidos. Por fim o capítulo 6 apresenta a conclusão do trabalho e possíveis trabalhos futuros.

Este trabalho se diferencia dos demais por aproximar a metodologia de projeto dos controladores standard com os controladores de segurança comparando-os através de MTBF, disponibilidade, probabilidade de falhas, fator de redução de risco, fração de falhas seguras entre outras métricas não menos importantes. O trabalho propõe a aplicação dos controladores standard em funções de segurança onde certificações SIL não são exigidas, além disso a utilização de técnicas estudadas para emprego em sistemas de missão crítica com intuito de mitigação de possíveis falhas e melhoria de performance de segurança.

# 2 FUNDAMENTAÇÃO TEÓRICA

Inicialmente, sistemas de proteção de processos industriais eram projetados utilizando lógicas pneumáticas ou relés elétricos, uma vez que estes componentes tendem a falhar no modo desenergizado. À medida que os processos se tornaram mais complexos, lógicas fixas começaram a perder espaço devido à grande dimensão e retrabalho nas instalações, então deuse início à utilização de eletrônica de estado sólido. Atualmente utiliza-se lógica programável inclusive nos sistemas de proteção, devido ao grande esforço dos pesquisadores do setor para tornar estes produtos confiáveis, de acordo com as normas vigentes.

Tal evolução forçou a indústria e os órgãos competentes para que desenvolvessem regras para aplicação de sistemas voltados à segurança de processos, como a IEC-ACOS (IEC *Advisory Committee on Safety*), comitê especializado em segurança. A grande preocupação deveu-se aos problemas relacionados a acidentes em unidades industriais, provenientes de erros em todas as etapas de projeto, implantação e manutenção destas unidades.

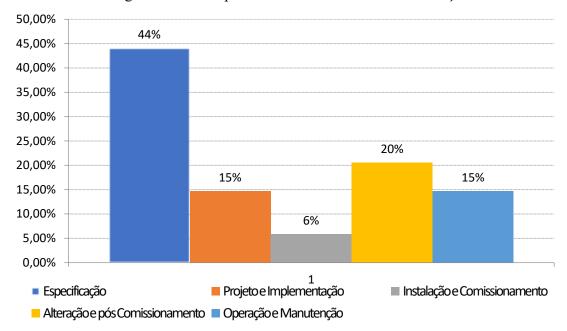

Conforme entidades como EPA (*Environmental Protection Agency*), OSHA (*Ocupation Safety and Health Administration*) e HSE (*Health and Safety Executive*) as principais causas de falhas em sistemas de automação estão relacionadas a erros de especificações de produtos e projetos, seguido por problemas relacionados com alterações após comissionamento, projeto e implementação de máquinas, equipamentos e sistemas, juntamente com erros de operação e manutenção, e, por último, problemas de instalação e comissionamento.

A Figura 1 quantifica os principais motivos de acidentes em unidades industriais durante ciclo de vida de projetos da automação.

Figura 1 - Falhas prematuras em sistemas de automação.

Fonte: HSE.

Segurança em sistemas de automação industrial estão sustentados por três divisões básicas:

Segurança Elétrica: consiste em garantir a redução de riscos operacionais, choques elétricos ao operador em caso de falha. Normas IEC 61131, UL, diretiva CE são algumas das normas vigentes.

Segurança Intrínseca: consiste no desenvolvimento de técnicas de proteção para utilização de equipamentos elétricos e eletrônicos em áreas perigosas com liberação de gases ou líquidos inflamáveis potencialmente explosivos com limitação de energia e temperatura de forma a garantir que não ocorrerá ignição do material inflamável. Diretivas ATEX e IECEx, são as principais normas utilizadas.

Segurança Funcional: aborda técnicas para garantir funcionamento conhecido, mesmo em caso de falha. A segurança funcional busca a redução da probabilidade de falha perigosa, onde as normas IEC 61508, IEC 61511, ISO-13849 (Safety of Machinery – Safety-related Parts of Control Systems) são as mais utilizadas.

#### 2.1 SAFETY INTEGRITY LEVEL- SIL

Basicamente, esta norma é uma padronização para especificação de requerimentos com o objetivo de atingir os níveis de integridade de segurança, e foi dividida em sete partes para melhor compreensão. A norma foi elaborada a partir da IEC (*International Electrotechnical Commission*) com o objetivo de orientar a gestão de todos os componentes dos sistemas de segurança relacionados abrangendo desde sensores e atuadores, até solucionadores de lógica para aplicações de segurança de determinado processo, levando em conta a pré determinação de variáveis para garantir um estado seguro de determinado equipamento, processo ou sistema.

A norma aplica-se a todo o ciclo de vida do sistema de segurança, desde o conceito, especificação, concepção, operação e utilização até a descontinuidade do produto ou sistema.

As três primeiras partes da norma correspondem ao desenvolvimento e aplicação do hardware e do software dos produtos E/E/EP (*Electrical/Electronic/Programmable Electronic*) e os demais capítulos servem de apoio para entendimento destas três primeiras. A tabela I ilustra a divisão da norma IEC 61508.

Tabela 1 - Divisão da IEC-61508.

| Norma Internacional IEC-61508 |                                                                         |  |  |

|-------------------------------|-------------------------------------------------------------------------|--|--|

| IEC-61508-1                   | Requisitos Globais                                                      |  |  |

| IEC-61508-2                   | Requisitos para sistemas E/E/EP ligados à segurança                     |  |  |

| IEC-61508-3                   | Requisitos de software                                                  |  |  |

| IEC-61508-4                   | Abreviaturas e definições de conceitos                                  |  |  |

| IEC-61508-5                   | Exemplos de processo de avaliação de níveis de integridade de segurança |  |  |

| IEC-61508-6                   | Diretrizes para a aplicação das partes IEC-61508-2 e IEC-61508-3        |  |  |

| IEC-61508-7                   | Visão global de técnicas e métricas utilizadas                          |  |  |

Os produtos voltados para área de segurança funcional são classificados entre quatro níveis de integridade, denominados de SIL1 a SIL4 onde a delimitação de cada nível está

relacionada como o grau de disponibilidade, probabilidade de falha na demanda (PFD) e fator de redução de risco (RRF), conforme tabela 2 abaixo:

Tabela 2 - Níveis de integridade e segurança – SIL.

| SIL | DISPONIBILIDADE | PFD         | RRF            |

|-----|-----------------|-------------|----------------|

| 4   | >99,99%         | <0,01%      | >10.000        |

| 3   | 99,90 a 99,99%  | 0,01 a 0,1% | 1.000 a 10.000 |

| 2   | 99,00 a 99,90%  | 0,1 a 1%    | 100 a 1.000    |

| 1   | 90,00 a 99,00%  | 1 a 10%     | 10 a 100       |

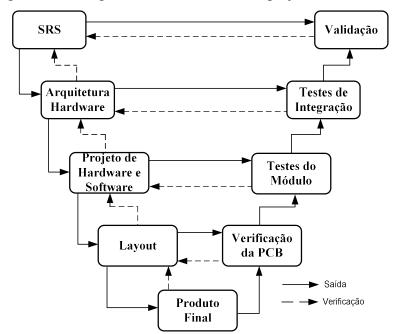

Para o desenvolvimento do produto certificado, é necessário obedecer ao ciclo de vida do projeto, também descrito na norma supracitada, sendo este o item primordial para o sucesso do projeto.

Existem divisões para cada tipo de aplicação, dentre elas, pode-se destacar: IEC-61511 voltada para sistemas instrumentados de segurança, IEC-62061 (Safety of Machinery: Functional Safety of Electrical, Electronic and Programmable Electronic Control Systems) direcionada para segurança de máquinas operatrizes, IEC-61513 (Nuclear power plants - Instrumentation and control important to safety) para operação e segurança de usinas nucleares de geração de energia elétrica, EN-50126 (Railway Applications – The Specification and Demostration of Reliability), EN-50128 (Railway Applications - Communication, Signalling and Processing systems - Software for Railway Control and Protection Systems) e EN-50129 (Railway applications – Communication, Signalling and Processing Systems – Safety Related Electronic Systems for Signalling) voltada para segurança funcional de sistemas de transportes ferroviários, EN-50402 (Electrical Apparatus for the Detection and Measurement of Combustible or Toxic Gases or Vapours or of Oxygen - Requirements on the Functional Safety of Gas Detection Systems) e EN-50271 (Electrical Apparatus for the Detection and Measurement of Combustible Gases, Toxic Gases or Oxygen - Requirements and Tests for Apparatus Using Software and/or Digital Technologies) específica para sensores de gás, EN

ISO-13849, direcionada para máquinas de baixa complexidade, IEC-61800 (*Adjustable speed electrical power drive systems*) requisitos de segurança funcional para sistemas de acionamento de potência e velocidade de motores elétricos, EN-60079-X (*Electrical Apparatus for Explosive Gas Atmospheres*) especificação de requisitos gerais para construção, ensaios e marcação de componentes elétricos destinados à atmosfera explosiva. A Figura 2 ilustra as principais normas de segurança e seus níveis de hierarquia.

IEC-61508

IEC-61511

IEC-62061

IEC-61513

EN-50126

EN-50128

EN-50129

EN-50402

EN/ISO-13849

IEC-61800

EN-60079-X

EN-50271

Figura 2 - Comparativo e hierarquia de normas de segurança funcional.

Fonte: do autor.

A classificação entre níveis de probabilidade de falhas e disponibilidade pode ser obtida de diversas formas, onde uma delas é feita a partir de cálculos de taxas de falhas dos componentes do produto. Outras técnicas são utilizadas, como análises de causa e consequência, árvore de falhas, análise por modelos de Markov, diagramas de blocos de confiabilidade, redes de Petri, métodos HAZOP, LOPA ou até mesmo a adoção de mais de uma técnica para resolução do problema.

Conceitualmente estas técnicas utilizam da mesma base para chegar aos resultados, neste caso, a classificação de falhas, a probabilidade de cada tipo de falha acontecer e medidas para mitigação do possível problema. Uma falha é considerada como um evento caracterizado por perda da capacidade de um dispositivo de não conseguir executar sua função, as falhas podem ser classificadas como:

Falhas aleatórias: quando ocorrem de maneira imprevisível, exemplo, defeitos de fabricação ou de instalação de determinado equipamento;

Falha de causa comum: ocorre em mais de um dispositivo ao mesmo tempo ou em um intervalo curto, exemplo, falta de energia elétrica, vibração, corrosão;

Falha na demanda: ocasionada quando o dispositivo deve ser acionado, tipo de falha ocasionada por falta de diagnóstico;

Falha oculta: só percebida quando se necessita do dispositivo ou o mesmo é testado;

Falha perigosa: potencial de impedir que uma função de segurança atue sob demanda;

Falha segura: pode causar o acionamento de um dispositivo de segurança sem a real necessidade.

Utilizando técnicas de estatística, a probabilidade de falha na demanda – PFD é a probabilidade de uma camada de proteção falhar em realizar sua função específica em resposta a uma demanda.

A Probabilidade média de falha na demanda - PFD $_{awg}$  é o indicador de confiabilidade de uma camada de proteção calculado pela probabilidade média em um dado intervalo de tempo que a mesma falhe quando demandada.

O fator de redução de risco – RFF é a medida de desempenho de uma camada de proteção dada pela razão entre os riscos sem e com a implementação desta camada de proteção.

A disponibilidade é a proporção de tempo no qual o equipamento ou o sistema trabalha sem falhas.

As definições acima são as principais métricas utilizadas para cálculos de confiabilidade de sistemas de segurança conforme IEC-61508.

O ciclo de vida de um projeto de EP SIL é um processo de engenharia que utiliza etapas específicas para garantir que o equipamento seja eficaz no seu principal objetivo, a redução de riscos, além de ser rentável ao longo de sua vida útil. Este processo é um ciclo contínuo que inicia a partir do projeto conceitual do produto e termina somente após a sua descontinuidade.

A primeira fase do ciclo de vida é a análise de riscos onde é estudada a necessidade de redução de riscos. Para tanto, utiliza-se de cálculos probabilísticos para verificação da integridade do projeto de segurança, definida como isenção de riscos inaceitáveis.

A fase de realização é iniciada após a identificação de todas as funções de segurança do produto. Um projeto conceitual deve ser desenvolvido escolhendo a tecnologia dos componentes, arranjo entre estes, como redundância de circuitos para aumento dos níveis de integridade de segurança. Ao final desta etapa, a arquitetura do hardware do produto deve ser concluída.

O desenvolvimento do hardware e do software inclui a etapa seguinte do processo, onde deve-se descrever todas as funções de cada circuito projetado tanto para o hardware quanto para o software com o objetivo de sustentar a etapa de validação do produto. Ao final desta etapa, os digramas elétricos e o desenvolvimento do software embarcado devem ser concluídos, e ferramentas dedicadas para projeto e simulações são utilizadas para sustentar esta tarefa. O layout do circuito deve ser desenvolvido após a validação do projeto de hardware e de software, após o desenvolvimento do layout de placa e mecânica do produto, este estará sujeito a um processo criterioso de testes para certificar que todo o processo de desenvolvimento foi concluído com êxito. Este processo deve seguir o modelo recomendado pela norma, chamado modelo V onde cada etapa passa por uma rigorosa fase de verificação, conforme Figura 3 abaixo.

Figura 3 - Fluxograma do ciclo de vida do projeto de um EP.

Fonte: do autor.

#### 2.2 SAFETY IINSTRUMENTED SYSTEM - SIS

Sistema Instrumentado de Segurança é o conjunto de funções instrumentadas de segurança – SIF (*Safety Instrumented Function*) de um determinado processo de segurança de uma planta industrial cuja função principal é levar este processo a um estado seguro em caso de falhas. Todos os componentes utilizados em um projeto de segurança fazem parte deste sistema. Os principais componentes de um SIS são:

Sensores: equipamentos responsáveis pela aquisição de dados do processo, classificados como digitais ou analógicos, podendo ser desde uma simples chave fim de curso ao um moderno sensor de temperatura, pressão ou um analisador de gás por exemplo.

Controladores programáveis: equipamentos eletrônicos programáveis que realizam a leitura dos sensores e processam todas informações para tomada de decisão do processo de segurança.

Atuadores: elementos de acionamento que ficam interligados aos controladores programáveis do processo, como exemplo, relés, sirenes, válvulas On/Off ou válvulas de controle, entre outros.

Software: denominado SCADA, é o sistema que realiza comunicação com os controladores programáveis e faz a interface entre operadores do processo e demais sistemas como, ERP (Enterprise Resource Planning), MES (Manufacturing Execution System), bancos de dados, sistemas de gestão, entre demais sistemas. Normalmente a camada de software de interface dos sistemas de segurança possui sua plataforma dedicada e isolada dos demais sistemas para garantir acesso restrito ao pessoal especializado, sendo que o resumo das ocorrências é enviado aos demais sistemas de uma unidade de produção.

A Figura 4 representa um SIS com uma função instrumentada de segurança – SIF composta por um transmissor e indicador de pressão, um controlador de segurança e uma válvula de segurança do tipo *shutdown*.

SENSOR

PIT

EP-SIL

LINHA DE ALTA PRESSÃO

VÁLVULA SHUTDOWN

Figura 4 - Exemplo de um SIS com uma SIF.

Fonte: do autor.

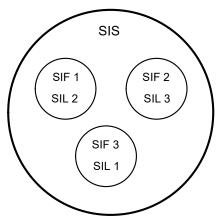

A Figura 5 representa a hierarquia de um SIS que executa três funções de segurança, uma com SIL 1, uma com SIL 2 e uma com SIL 3. Para que isto seja possível, os componentes de cada SIF devem ter no mínimo o valor SIL requerido de cada SIF e o SIS deve possuir o valor SIL da SIF de maior índice.

Figura 5 - Hierarquia dos sistemas instrumentados de segurança.

Fonte: do autor.

#### 2.3 CARACTERÍSTICAS CONSTRUTIVAS DE UM EP STANDARD

Controlador standard é um sistema de controle industrial de tempo real que executa um programa aplicativo armazenado em sua memória interna, pois deve funcionar independentemente do funcionamento de uma rede de comunicação como geralmente é projetado, garantido a continuidade do processo ao qual foi implementado. A programação deste equipamento é normatizada pela IEC-61131-3 e pode ser feita em até 6 linguagens de programação diferentes que podem ser utilizadas de forma mista no programa aplicativo, ou seja, pode ser programado em blocos de função para cada parte do programa, tornando mais organizado e de fácil entendimento para os demais usuários do sistema.

Como explicado anteriormente, este tipo de controlador é geralmente modular e dividido em blocos de entrada, CPU, fonte, módulos de comunicação e blocos de saída e são geralmente acoplados em um bastidor.

#### 2.3.1 CPU

Uma CPU de um controlador Standard é formada por uma unidade de processamento, memórias RAM e Flash, relógio de tempo real, portas de programação e comunicação e circuito de monitoramento denominado *watchdog*, conforme Figura 6.

PROCESSADOR WÓDULOS DE SAÍDA WÓDULOS DE SAÍDA WÓDULOS DE SAÍDA

Figura 6 - Diagrama básico da CPU de um EP standard.

Fonte: do autor.

Os módulos de entrada e saída do EP standard são compostos de entradas digitais e analógicas e saídas digitais, e analógicas, cujos sinais de leitura e acionamento são definidos pela norma IEC-61131.

#### 2.3.2 Módulos de Entradas Digitais

Módulos de entradas digitais normalmente são padronizados para sinais de campo de 24Vcc com capacidade de leitura geralmente de 8 ou 16 pontos de acordo com as especificações de cada fabricante. Estes módulos possuem um circuito de entrada com filtros, tratamento do sinal de entrada, acopladores ópticos para isolação do sinal de campo com o circuito digital, que por sua vez possui um circuito lógico geralmente utilizando um microcontrolador ou lógica programável do tipo EPLD ou similar, reguladores de tensão e circuito de interface do barramento de comunicação com a CPU conforme a Figura 7.

SENSORES DE CAMPO

SENSORES DE C

Figura 7 - Diagrama simplificado de um módulo de entradas digitais.

Fonte: do autor.

# 2.3.3 Módulos de Saídas Digitais

Os módulos de saídas digitais são compostos de conjuntos de saídas normalmente de 8 ou 16 pontos, possuem como elemento de acionamento das cargas externas transistores ou relés, de acordo com a aplicação final, e são formados por um circuito de interface de barramento e circuito digital similar ao módulo de entrada digital, conforme ilustrado na Figura 8.

ATUADORES DE CAMPO

Figura 8 - Diagrama simplificado de um módulo de saídas digitais.

Fonte: do autor.

## 2.3.4 Módulo de Entradas Analógicas

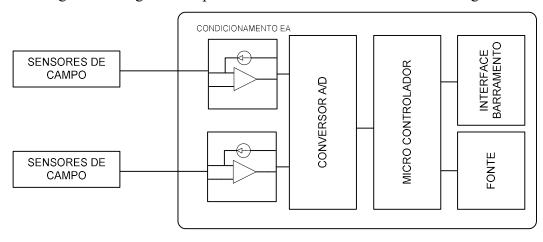

Os módulos de entradas analógicas são compostos por 4 ou 8 entradas e possuem os sinais de leitura padronizados com a norma IEC-61131. Geralmente os sensores analógicos emitem sinais de corrente elétrica padronizados em 4 a 20mA alimentados pelo próprio módulo de entrada analógica ou por fonte externa, sinais de tensão entre -10 a 10V, além de termopares, RTD e sensores resistivos em geral, de acordo com sua aplicação. Existe uma gama de elementos sensores analógicos muito grande, por este motivo a norma estabelece a padronização do condicionamento dos sinais destes sensores para garantir a aplicação de qualquer fabricante de controlador de mercado.

Internamente, os módulos de aquisição de dados analógicos são compostos por um circuito de condicionamento e isolação do sinal de entrada, conversores analógicos/digitais – AD e circuito lógico microcontrolado com interface de barramento e fonte ou regulador de tensão conforme demais módulos já apresentados. Neste caso um mesmo canal de leitura analógica pode ser capaz de realizar a leitura de qualquer sinal de entrada padrão, desde que seja interligado e configurado da maneira correta. A Figura 9 ilustra o diagrama simplificado de um módulo de entrada analógico.

Figura 9 - Diagrama simplificado de um módulo de entradas analógicas

Fonte: do autor.

## 2.3.5 Módulo de Saídas Analógicas

Os módulos de saídas analógicas são normalmente compostos por 4 canais de saída padronizados a partir da IEC-61131 (os módulos de saída analógicas são projetados com 4 canais devido ao padrão da indústria e a capacidade de layout da placa do equipamento). Geralmente os transmissores analógicos recebem sinais de corrente elétrica padronizados em 4 a 20mA, 0 a 20mA e sinais de tensão entre -10 a 10V.

Internamente são compostos por uma interface de barramento, um circuito lógico com o microcontrolador, conversores digital/analógico – DA e driver de tensão e corrente elétrica para acionamento dos atuadores. Um diagrama básico deste módulo é apresentado na Figura 10.

ATUADORES

CONVERSOR D/A

CONVERSOR D/A

ATUADORES

ATU

Figura 10 - Diagrama simplificado de um módulo de saídas analógicas.

Fonte: do autor.

#### 2.4 CARACTERÍSTICAS DOS CONTROLADORES SIL

Os controladores SIL são equipamentos eletrônicos desenvolvidos para segurança de processos industriais, da mesma forma que os controladores standard, possuem processamento e comunicação em tempo real, porém utilizam biblioteca de lógicas limitadas aos projetos de segurança, ou seja, utilizam de instruções reduzidas a cada procedimento com a finalidade de

não sobrecarregar os processadores, memória de aplicativo, memória RAM além de possuírem componentes duplicados em seu projeto. Em alguns casos ainda são utilizados componentes triplicados em sua arquitetura formando a arquitetura de votação 2003, ou TMR (*Triple Modular Redundancy*).

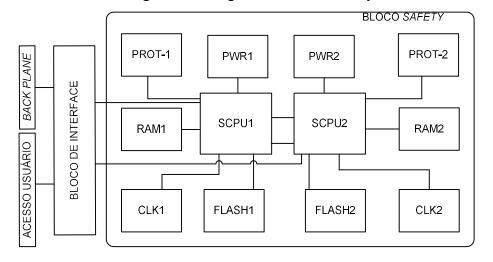

#### **2.4.1 CPU SIL**

A CPU SIL, também chamada de *safety* CPU ou SCPU, é responsável pela execução do software aplicativo do cliente, interface de comunicação com demais sistemas e processamento dos sinais dos módulos de aquisição. Tipicamente a arquitetura de hardware da SCPU é dividida em três blocos distintos, sendo: fonte de alimentação, unidade de processamento e interface, como mostrado na Figura 11. Os componentes do hardware de um produto SIL são rigorosamente selecionados, alguns fabricantes possuem componentes já certificados para este tipo de projeto, mesmo assim, a utilização destes componentes não garante a certificação do equipamento, técnicas de layout, cálculo de confiabilidade devem comprovar tal capacidade.

Figura 11 - Diagrama de blocos safety CPU.

Fonte: do autor.

## 2.4.2 Módulo de Entradas Digitais SIL

Os módulos de entradas digitais possuem três blocos distintos e isolados: entrada, processamento e interface.

O circuito de entrada possui limitadores de tensão e corrente elétrica, filtro e acoplamento óptico para a transformação do sinal físico em sinal lógico a ser processado em cada SMCU (*Safety Microcontroller Unit*). As entradas digitais devem ter o limite de tensão e corrente, conforme definido na IEC 61131-2

O processamento interno é realizado através de dois microcontroladores denominados SMCU, responsáveis por todas as entradas de leitura e tratamento dos sinais internos e externos. O software interno possui um algoritmo que garante a concordância das mensagens das SMCUs para CPU. Este tipo de módulo possui duas fontes de alimentação independentes, uma para cada SMCU que além de alimentar as SMCUs, realizam isolamento entre a interface de barramento e o circuito de circuito de monitoração de tensão. A Figura 12 ilustra o diagrama de blocos do modulo de entrada digital.

SENSORES DE CAMPO

SENSORES DE CAMPO

SENSORES DE CAMPO

SENSORES DE CAMPO

SMCU2

FONTE 2

CLOCK 2

FONTE 2

FONTE 1

Figura 12 - Diagrama de blocos módulo de entradas digitais.

Fonte: do autor.

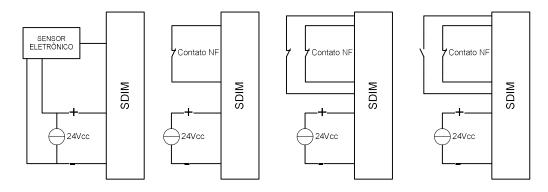

Os canais de entrada deste módulo possuem bornes de conexão que permitem diversos modos de ligação, seja um simples contato, um sensor alimentado por fonte externa,

configuração para arranjos de contatos paralelos ou série para configuração de sensores com arquiteturas 1001, 1002, 2003 entre outros. Para ambos arranjos é permitido o monitoramento de cada canal de entrada. A Figura 13 ilustra alguns esquemas de ligação dos sensores no módulo de entrada digital monitorado SDIM (*Safety Digital Input Monitored*).

Figura 13 - Esquema de interligação de sensores nos módulos de entradas digitais.

Fonte: do autor.

# 2.4.3 Módulo de Saídas Digitais SIL

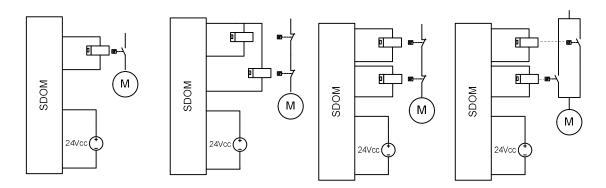

Os módulos de saída digital SIL ou simplesmente SDOM (*Safety Digital Output Monitored*) são dispositivos aplicados à sistemas de segurança, concebido a partir dos requisitos da norma IEC-61508 e dividido em três blocos distintos, interface de comunicação, processamento e bloco de saídas.

As saídas digitais são os circuitos que fornecem corrente para um atuador. Neste caso, onde o requisito é segurança, cada canal de saída possui um driver de fonte de corrente positivo e um driver de coletor de corrente negativo. Ambos os SMCUs controlam cada parte da saída, com sinais complementares.

O SMCU1 é o único microcontrolador que se comunica com o ETHMCU. O software interno deve garantir que ambas as SMCUs "concordem" com o telegrama que está sendo recebido. A Figura 14 apresenta o diagrama de blocos do módulo de saída digital.

ATUADORES DE CAMPO

ATUADO

Figura 14 - Diagrama de blocos módulo SDOM.

Fonte: do autor.

Os canais de saída deste módulo possuem bornes de conexão que permitem diversos modos de ligação, desde uma saída simples, até arranjos série ou paralelo de acordo com a aplicação. Cada canal possui um circuito de monitoramento de corrente elétrica e um algoritmo de teste para cada canal com intervalo de tempo configurável. A Figura 15 ilustra alguns esquemas de ligação das cargas no módulo de saída digital monitorado SDIM.

Figura 15 - Exemplos de ligações de cargas no módulo SDOM.

Fonte: do autor.

# 2.4.4 Módulo de Entradas Analógicas SIL

Os módulos de entradas analógicas são geralmente compostos por 4 canais e possuem os sinais de leitura padronizados com a norma IEC-61131, os sensores analógicos emitem sinais de corrente elétrica padronizados em 4 a 20mA alimentados pelo próprio módulo de entrada analógica ou por fonte externa, sinais de tensão entre -10 a 10V, além de entradas para termopares, RTD, e sensores resistivos, de acordo com sua aplicação.

Internamente, os módulos de aquisição de dados analógicos são compostos por um circuito de condicionamento e isolação do sinal de entrada, circuito de monitoramento dos canais de entrada, conversores analógicos/digitais – AD e duas unidades de processamento formada por processador, memória RAM, fonte e clock e a interface de barramento com conversor DC/DC. A Figura 16 ilustra o diagrama simplificado de um módulo de entrada analógico.

SENSORES DE CAMPO

SENSORES DE C

Figura 16 - Diagrama de blocos módulo de EA.

Fonte: do autor

# 2.4.5 Módulo de Saídas Analógicas SIL

Os módulos de saídas analógicas são normalmente compostos por 4 canais de saída padronizados a partir da IEC-61131. Geralmente os transmissores analógicos recebem sinais de corrente elétrica padronizados em 4 a 20mA, 0 a 20mA e sinais de tensão entre -10 a 10V.

São empregadas duas unidades de processamento formadas por processador, memória RAM, fonte e clock e a interface de barramento com conversor DC/DC. A Figura 17 ilustra o diagrama simplificado de um módulo de entrada analógico.

SENSORES DE CAMPO

SENSORES DE C

Figura 17 - Diagrama de blocos módulo de saídas analógicas.

Fonte: do autor.

### 2.5 PRINCIPAIS DIFERENÇAS ENTRE EP STANDARD E EP SIL

Um controlador programável consiste de uma arquitetura modular, onde os principais componentes são: bastidor, fonte, CPU, módulos de comunicação, módulos de aquisição de dados de sinais de campo e módulos de saída para controle de processo, constituídos de sinais digitais e analógicos padronizados por IEC-61131.

Sistemas dedicados à segurança funcional implicam na existência de uma série de técnicas para construção de hardware e software sustentadas por IEC-6508. Existe uma grande

diferença entre as duas soluções, em um controlador SIL, a segurança é prioridade, pois um EP SIL é projetado para atuar somente em caso de falha no processo, ao contrário dos controladores programáveis de processo onde exige-se muito do desempenho não desconsiderando a confiabilidade do sistema.

Quando se deseja que um controlador programável standard tenha características similares a um EP SIL, no ponto de vista das métricas de acordo com a tabela 2 sem comprometer o desempenho, existe a possibilidade de mesclar as técnicas construtivas conforme IEC-61131 e IEC-61508, tanto em hardware, quanto em software.

Como exemplo, o processador RM42L432 da *Texas Instruments* desenvolvido para SIL-3 possui arquitetura interna redundante e utiliza uma gama de diagnósticos embarcados no seu próprio firmware, garantindo um alto nível de confiabilidade. Desta forma, para aplicações de missão crítica com controladores programáveis Standard, são utilizadas técnicas similares, montando fontes, CPUs e até mesmo módulos de entrada e saída (I/O) em redundância. Para estes arranjos também é utilizada a técnica de aumento da gama de diagnóstico através de hardware e software no programa aplicativo. A elevação do custo da arquitetura redundante muitas vezes é inferior ao custo de desenvolvimento e certificação de equipamentos com selo SIL conforme a norma IEC-61508.

De acordo com IEC-61508 seção 6, diversos arranjos de interligação de componentes podem ser projetados para aumento de confiabilidade de um sistema. Estas técnicas podem ser adotadas em qualquer parte de uma malha de controle dos sistemas de segurança.

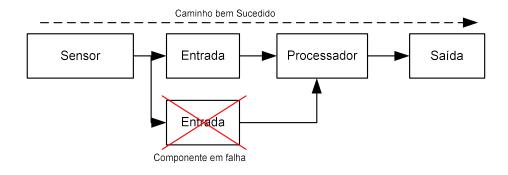

#### 2.6 DIAGRAMA DE BLOCOS DE CONFIABILIDADE

Conforme IEC 61508-6 anexo B e IEC 61131-6 o diagrama de blocos de confiabilidade RDB (*Reliability.Block Diagram*) é uma técnica utilizada para facilitar o cálculo de disponibilidade e probabilidade de falha de hardware de sistemas elétricos ou eletrônicos. A

técnica consiste em redesenhar cada módulo do sistema a ser calculado em formas de blocos, podendo ser representados em associações série, paralelo ou misto, seguindo um fluxo de acordo com sua interligação no sistema. No caso de leitura de um sinal, o fluxo ocorre do módulo de entrada até o elemento processador. Caso necessite-se uma sinalização, adicionam-se os componentes de sinalização, normalmente uma interface homem-máquina. No caso de um comando, adicionam-se os blocos que compõem a saída do sistema.

O RBD permite cálculo de confiabilidade de dois estados, sucesso ou falha, onde a resposta é bem sucedida caso seja possível encontrar um caminho de início a fim do fluxo não sendo obstruído por uma falha. Caso contrário, o caminho apresentou uma falha. Em sistemas redundantes, os componentes que são duplicados ou triplicados são tolerantes à falha de um ou mais módulos e demais componentes únicos não apresentam um caminho alternativo.

A Figura 18 ilustra um diagrama RBD com 2 canais de entrada duplicados e o restante dos componentes do sistema unitários.

Figura 18 - RBD de um controlador standard.

Fonte: IEC61508.

No exemplo da Figura 18 tem-se um sistema misto, onde os módulos de entrada estão em paralelo (realizando a leitura de um sensor através de um canal de cada módulo) e os demais componentes em série. Considerando os módulos de entrada do mesmo modelo, o primeiro

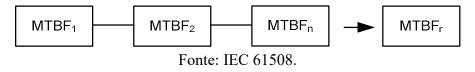

passo é calcular o resultado destes módulos em paralelo transformando-os em um componente com MTBF (*Mean Time Between Failures*) resultante e construindo então um circuito série para facilitar o cálculo. Neste cálculo, utiliza-se também o MTTR (*Mean Time to Repair*) que é o tempo médio de reparo, conforme Figura 19, o diagrama ilustra o MTBF resultante deste circuito paralelo. A forma de cálculo do MTBF resultante está descrita na Equação 1.

MTBF₁

MTTR

MTBF<sub>r</sub>

Figura 19 - Cálculo RBD paralelo.

Fonte: IEC 61508.

## 2.7 ARQUITETURAS DE VOTAÇÃO

Conforme IEC 61508-6 anexo B as arquiteturas de votação MooN (D) (M *out of* N), referem-se à capacidade de votação e redundância do sistema, onde N indica o número de canais redundantes que executam a função, enquanto M indica quantos desses canais têm de estar disponíveis para funcionamento. A letra D se refere às capacidades de diagnóstico, ou seja, cada canal tem capacidade de executar testes de diagnóstico regulares para verificar o seu correto funcionamento e utilizar esses diagnósticos para adaptar o votador de saída de forma que o estado de saída global possa ser dado pelo(s) outro(s) canal(is). Saliente-se que os testes de diagnóstico somente reportam as falhas encontradas e não devem mudar nenhum dos estados de votação de saída.

Na ausência da letra D, os diagnósticos são utilizados também, mas apenas para alertar a existência de falhas diagnosticáveis.

As principais arquiteturas MooN são denominadas 1001, 1001D, 1002, 2002, 1002D, 1003 e 2003.

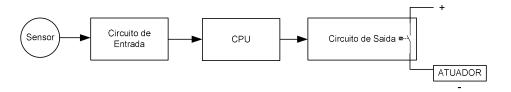

A arquitetura 1001 (diz-se "um-de-um") consiste em um arranjo onde existe apenas um componente de entrada, um elemento de processamento e um elemento de saída. Nesta arquitetura nenhuma tolerância a falhas é fornecida nem proteção do modo de falha. Os circuitos eletrônicos podem falhar com segurança (saídas desenergizadas, circuito aberto) ou perigosamente (saídas energizadas ou curto-circuito). A Figura 20 ilustra a arquitetura 1001.

Figura 20 - Arquitetura 1001 de um controlador.

Fonte: IEC 61508.

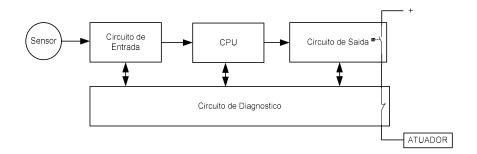

A arquitetura 10o1D é formada por um conjunto simples conforme a Figura 2, porém com um circuito de diagnóstico para o controlador. Neste caso, o circuito de diagnóstico implementa funções de segurança capazes de transformar uma falha perigosa em falha segura, por exemplo, a desenergização do circuito de saída. Como os efeitos dos diagnósticos on-line devem ser modelados, quatro categorias de falhas podem ser incluídas:  $\lambda_{DD}$  (*Dangerous, Detected Failure Rate*),  $\lambda_{DU}$  (*Dangerous, Undetected Failure Rate*),  $\lambda_{SD}$  (*Safe, Detected Failure Rate*), e  $\lambda_{SU}$  (*Safe, Undetected Failure Rate*). A Figura 21 ilustra a arquitetura 10o1D.

Figura 21 - Arquitetura 100D de um controlador.

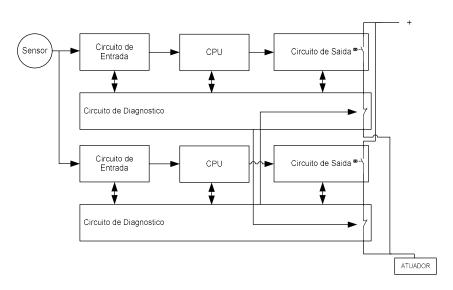

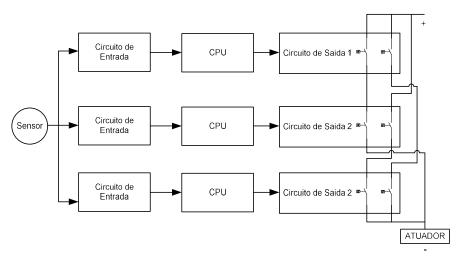

A arquitetura 1002 consiste em dois controladores conectados em paralelo, onde as funções de segurança são processadas de forma independente, onde, desta maneira, deve ocorrer falha nos dois equipamentos para que ocorra uma falha da função de segurança. Esta configuração oferece baixa probabilidade de falha na demanda, mas aumenta a probabilidade de falha segura.

As saídas das funções de segurança são interligadas em série para garantir a segurança do processo. A Figura 22 ilustra a arquitetura 1002.

Circuito de Entrada

CPU

Circuito de Saida CPU

Circuito de Saida ATUADOR

Figura 22 - Arquitetura 1002 de um controlador.

Fonte: IEC 61508.

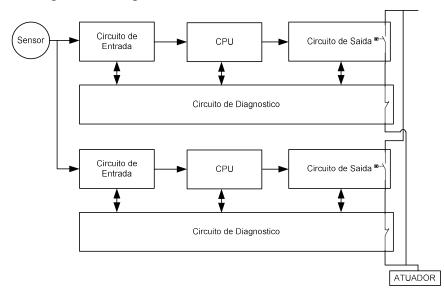

Arquitetura 2002 é um conjunto idêntico ao circuito 1002, porém com as saídas interligadas em paralelo. É utilizada em situações onde não seja desejável falhar com as saídas desenergizadas, e, neste caso, se uma falha ocorrer em um dos componentes de um conjunto, o

ATUADOR

outro que está ativo tem condições de assumir o controle. A Figura 23 representa a arquitetura 2002.

Circuito de Entrada

CPU

Circuito de Saida

CPU

Circuito de Saida

CPU

Circuito de Saida

CPU

Circuito de Saida

CPU

Figura 23 - Arquitetura 2002 de um controlador.

Fonte: IEC 61508.

A arquitetura 1002D consiste em dois conjuntos idênticos à arquitetura 1001D, onde o sensor é interligado e uma entrada de cada controlador, e suas saídas são respectivamente ligadas em série permitindo que uma unidade desligue a outra. A representação da arquitetura 1002D conforme Figura 24.

Figura 24 - Arquitetura 1002D de um controlador.

A arquitetura 2002D consiste num arranjo de dois conjuntos 1002D organizados de maneira semelhante ao sistema 2002. A solução 1001D protege o sistema contra falhas perigosas, onde, desta forma, duas unidades 100D em paralelo protegem o sistema contra desligamentos. Para esta solução ser confiável, os diagnósticos devem ser muito eficazes pois uma falha perigosa não detectada causará uma falha perigosa em todo o sistema. A Figura 25 ilustra a arquitetura 2002D.

Figura 25 - Arquitetura 2002D de um controlador.

Arquitetura 2003 é conhecida por tolerar falhas perigosas e falhas seguras (duas de três unidades devem estar em conformidade para o sistema operar) fornecendo alta disponibilidade. Duas saídas de cada unidade de controle são necessárias para cada circuito de saída, criando um sistema de votação onde o sistema acionará ou desligará a saída se no mínimo dois controladores forçarem este comando.

Uma análise detalhada do circuito de votação indica tolerância de uma falha de um dos modos de falha - perigoso (curto-circuito) ou seguro (circuito aberto). Quando uma unidade falha em circuito aberto, o sistema efetivamente se degrada para uma configuração de 1002. Se uma unidade falhar em curto-circuito, o sistema efetivamente se degrada para uma configuração 2002. Em ambos casos, o sistema permanece em operação. A arquitetura 2003 pode ser vista na Figura 26.

Figura 26 - Arquitetura 2003 de um controlador.

A Tabela 3 apresenta resumidamente as principais funcionalidades de cada arquitetura apresentada identificando seus objetivos.

Tabela 3 - Quadro resumo de arquiteturas EP SIL.

| ARQUITETURA | NUM.<br>UNIDADES | NUM.<br>SAÍDAS | OBJETIVO                                |

|-------------|------------------|----------------|-----------------------------------------|

| 1001        | 1                | 1              | Unidade Básica                          |

| 1002        | 2                | 2              | Segurança                               |

| 2002        | 2                | 2              | Disponibilidade                         |

| 1oo1D       | 1                | 2              | Segurança                               |

| 2003        | 3                | 6              | Segurança e Disponibilidade             |

| 2002D       | 2                | 4              | Segurança e Disponibilidade             |

| 1002D       | 2                | 4              | Segurança e Disponibilidade + segurança |

#### 3 TRABALHOS RELACIONADOS

A análise dos trabalhos relacionados tem como objetivo uma pesquisa de trabalhos acadêmicos de maior relevância publicados em periódicos e revistas da área de sistemas de segurança com controladores dedicados a este fim, no entanto, a literatura não promove comparativos destas aplicações com controladores programáveis standard.

Segundo (Ždánsky et al., 2012), as funções de segurança de um controlador dedicado podem ser alcançadas por um controlador padrão de mercado, porém, este não possui reação predefinida no caso de falha, o que pode resultar em um valor arbitrário na saída do sistema de controle. Neste trabalho foi realizado um estudo de arranjos de arquitetura de funções instrumentadas de segurança comparando a aplicação de SIF com CLP SIL e CLP standard. Também foi analisada a influência do fator humano na atuação de sistemas automatizados de segurança concluindo que este é o fator mais provável que a falha perigosa.

Conforme (Rástočný et al., 2012), Sistemas de Controle Relacionados à Segurança - SRCS podem comprometer o nível de integridade de segurança - SIL do Sistema Instrumentado de Segurança - SIS devido à combinação de diagnósticos embarcados no controlador e sua devida integração com os diagnósticos e interpretações do SRCS desenvolvidos no programa aplicativo. Sugere-se a implementação de diagnósticos dos componentes da malha, como, monitoração de contatos de sensores e contatores no programa aplicativo, e utilização de demais componentes desta malha de segurança com certificação SIL desejada.

Conforme (Safety Reference Manual 1756-RM001O-EN-P, 2018) controladores Standard da série Controllogix® Rockwell Automation podem alcançar nível SIL 2 em suas aplicações dependendo da maneira em que os módulos do sistema são arranjados. Neste documento também é apresentado o memorial de cálculo para atingimento do SIL desejado pelo conjunto. Boas práticas de instalações mecânicas e elétricas dos controladores e seus componentes também são reforçadas neste manual.

De acordo com (Georgies et al., 2016), circuitos de entrada e saída digitais monitorados aplicados em sistemas de missão crítica podem atingir SIL4 a partir do circuito projetado e dos recursos de diagnósticos desenvolvidos e medidos através da probabilidade de falha por hora - PFH. Circuitos de condicionamento de sinais de saída compatíveis com o tipo 2 da IEC-61131 incluindo sinais de teste e feedback de status para monitoramento de circuitos podem atingir valores suficientes para atingimento de SIL4.

Conforme (Bukoswki et al, 2009), funções instrumentadas de segurança – SIF podem sofrer alterações de resultado de probabilidade média de falha na demanda PFD<sub>avg</sub> (*Average Probability of dangerous Failure on Demand*) quando submetidos ao intervalo de testes de prova - PTI menor que 100% e completude menor que 100% pode sofrer degradação do nível SIL ao longo do tempo. O trabalho propõe uma correção destes resultados através da inserção de probabilidade de completude e da probabilidade de correção do intervalo de teste de prova.

De acordo com (Rástočný et al., 2016), o projeto de um SIS deve ser observado o dimensionamento das funções de segurança-SIF para garantir o tempo de atuação de uma determinada SIF quando demandada. Funções de segurança projetadas pelo usuário quando mau dimensionadas podem levar a degradação da segurança de todo o sistema.

Segundo (Sammarco, 2007), sistemas ESD (*Electronic Shutdown System*) aplicados em máquinas de mineração estão sendo realizados através de PLC (*Programmable Logic Controllers*), antes realizados através de fiação e lógica fixa (*Wardwired*). O trabalho compara a utilização dos sistemas ESD realizados através de *hardwired*, PLC e S-PLC (*Safety PLC*). Os testes realizados concluíram que ESD com *wardwired* atingiu SIL 2 com arquitetura 1001 e SIL 3 com arquitetura 1002. O ESD com a utilização de PLC atingiu apenas SIL 1 com arquitetura 1001 sendo o mesmo equipamento utilizado para o controle da máquina, enquanto o S-PLC independente do processo atingiu SIL 3 utilizando arquitetura 1002D.

De acordo com (Rástočný et al., 2017) controladores lógicos programáveis de segurança estão sendo utilizados para controle de processos devido aos requisitos de segurança em hardware por garantir uma reação segura em caso de detecção de falha e devido ao alto grau de diagnósticos por software que este tipo de equipamento proporciona. o trabalho analisou a influência dos parâmetros nativos no controlador de segurança combinados com os diagnósticos implementados no software aplicativo destes controladores para a cobertura dos sensores e atuadores da função de segurança e o comprometimento da integridade desta função de segurança devido à possíveis falhas de desenvolvimento do programa aplicativo.

Conforme (Torres et al., 2019) uma metodologia para avaliação de integridade de EP é proposto utilizando arquitetura de votação 2003 e análise através de modelo de Markov. A escolha por modelo Markov segundo Torres deve-se por considerar as taxas de falhas perigosas detectáveis, não detectáveis e aplicáveis em sistemas de baixa e alta demanda, onde cálculos estatísticos não realizam uma cobertura completa quanto apresentada pelo autor.

Segundo o autor, as normas IEC 61508, a IEC 61511 e a ISA TR 84.00.02 recomendaram diferentes métodos analíticos para quantificar a probabilidade de falha e o SIL necessário. Embora os padrões IEC e o relatório ISA sejam amplamente utilizados na indústria, esses padrões não fornecem uma abordagem abrangente dos métodos, nem especificam qual técnica deve ser aplicada com base nas características operacionais do sistema relacionado à segurança.

Embora o estudo comparativo tenha elencado lacunas no método utilizando equações simplificadas, o modelo de confiabilidade apresentado obteve mesmo resultado de desempenho (SIL2) em ambos os casos amostrados. O autor sugere ampliação do estudo utilizando através de falhas sistemáticas provenientes de erros de projetos, instalações e falhas de software.

Conforme (Torres et al., 2020) uma metodologia para avaliação de integridade de segurança de IEDS de proteção de rede elétrica é proposto através de modelo de Markov. O

artigo realiza comparação com método RBD alertando que o mesmo não contempla causas potenciais de falhas.

Torres realiza intervalos de teste de prova de um a cinco anos e verifica a degradação de SIL 3 para SIL 2 a partir de três anos de operação e reforça que o EP possui a maior influência no desempenho total do sistema composto por sensores, EP e atuadores.

Segundo Torres, em instalações industriais com arranjos de proteção, existem cenários de risco como consequência de qualquer aplicação incorreta mostrada neste documento. Um evento não controlado, particularmente no estudo de caso, uma falha de sobrecorrente nesses sistemas pode criar efeitos nocivos às pessoas, dispositivos e meio ambiente. A verificação SIL com IEDs sobre os arranjos de proteção fornece segurança e confiabilidade à operação de sistemas de energia industriais e comerciais em configurações complexas.

Este trabalho se diferencia dos demais por aproximar a metodologia de projeto dos controladores standard com os controladores de segurança comparando-os através de MTBF, disponibilidade, probabilidade de falhas, fator de redução de risco, fração de falhas seguras entre outras métricas não menos importantes. O trabalho propõe a aplicação dos controladores standard em funções de segurança onde certificações SIL não são exigidas, além disso a utilização de técnicas estudadas para emprego em sistemas de missão crítica com intuito de mitigação de possíveis falhas e melhoria de performance de segurança. Tornar esta metodologia mais popular pode significar a redução do índice de falhas em sitemas de automação de acordo com o gráfico da Figura 1.

A Tabela 4 - apresenta uma breve comparação entre os principais trabalhos relacionados.

Tabela 4 - Comparativo dos trabalhos relacionados.

| Autor          | Funções Segurança<br>CLP Std | Monitoramento sensores | Ciclo de Vida | Arq Votação | CLP SIL Processos | RBD |

|----------------|------------------------------|------------------------|---------------|-------------|-------------------|-----|

| Ždánsky, 2012  | X                            |                        |               |             |                   |     |

| Rástočný,2012  |                              | X                      |               |             |                   |     |

| Georgies,2016  |                              | X                      |               |             |                   |     |

| Rástočný, 2016 |                              |                        | X             |             |                   |     |

| Sammarco, 2007 | X                            |                        |               | X           |                   |     |

| Rástočný, 2017 |                              |                        |               | X           | X                 |     |

| Torres, 2019   |                              |                        |               | X           |                   |     |

| Torres, 2020   |                              |                        |               |             |                   | X   |

| Juliano, 2020  | X                            | X                      | X             | X           |                   | X   |

# 4 METODOLOGIA DE CÁLCULO DE CONFIABILIDADE

Pela avaliação das arquiteturas típicas dos EPs de segurança apresentadas na seção anterior, percebe-se que cada caso possui uma aplicação específica, seja ela relacionada com disponibilidade, tolerância à falhas ou fator de redução de riscos. Com base nestas arquiteturas, os controladores programáveis standard, que por sua concepção de projeto escalar, podem ser arranjados de formas similares aos EPs de segurança com o objetivo de atingirem métricas SIL.

Os controladores standard são tipificados por sua disponibilidade e não por sua tolerância a falhas como os controladores de segurança, porém, na prática o resultado é semelhante, a diferença está forma de cálculo que deve ser utilizada, apresentada nesta dissertação. Para obter os resultados em controladores standard, utiliza-se dos dados dos fabricantes que disponibilizam MTBF e Tempo Médio de Reparo - MTTR como as principais fontes de consulta. Em controladores de segurança utilizam-se taxas de falhas, análise através de árvore de falhas e Monte Carlo, dentre as principais técnicas.

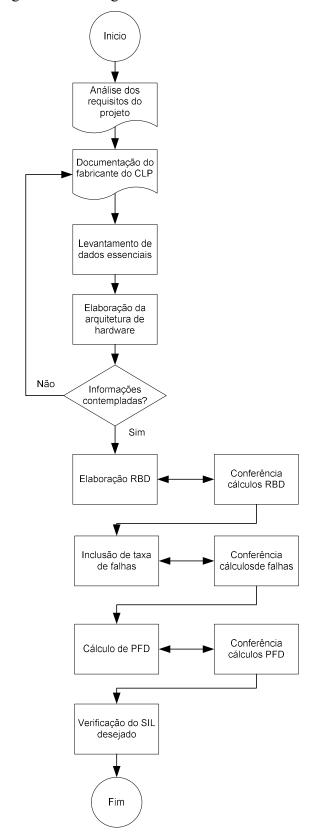

Conforme fluxograma de cálculo da Figura 27 abaixo, os métodos RBD e cálculos probabilísticos foram escolhidos para o desenvolvimento deste trabalho por conta da facilidade de compreensão e versatilidade de aplicação em qualquer linha de controladores standard com características modulares.

Figura 27 - Fluxograma de cálculo de PFD.

Fonte: do autor.

A primeira etapa do projeto é a leitura da especificação técnica do projeto do sistema instrumentado de segurança onde devem constar os requisitos técnicos necessários, relação das malhas das funções instrumentadas de segurança com as informações de SIL desejado em cada malha de segurança. Estas especificações geralmente são realizadas através do estudo HAZOP, parte-se do princípio de que este estudo já foi realizado, pois não faz parte do estudo deste trabalho.

De posse desta documentação deve ser estudada documentação do fornecedor do controlador para avaliar como este equipamento será instalado e sua flexibilidade de arranjos de arquiteturas conforme apresentado no item 2.7 deste trabalho. Os dados essenciais para preparação dos cálculos de confiabilidade são: MTBF de cada componente de hardware, MTTR e MRT do conjunto, informações do fabricante do controlador que possibilite a levantamento da cobertura de diagnósticos – DC da solução.

Para a elaboração da arquitetura deve-se observar a flexibilidade, características elétricas, mecânicas e boas práticas contidas nos manuais do fabricante possibilitando que alguma das arquiteturas de votação apresentadas possam ser implementadas.

Após e elaboração da arquitetura, deve-se verificar se todas informações obrigatórias estão contempladas e então deve-se projetar o diagrama de blocos de confiabilidade – RBD conforme item 4.1 deste trabalho.

Concluído o RBD e os cálculos de disponibilidade para a arquitetura desenvolvida a próxima etapa é a inclusão das taxas de falhas conforme item 4.2 deste trabalho. Importante salientar a tabela de cobertura de diagnósticos, conforme IEC 61508 apresentada na tabela 4, esta é uma análise quantitativa realizada a partir das características construtivas dos componentes e do projeto de layout do circuito eletrônico do produto estudado.

A última etapa após a verificação das taxas de falhas são os cálculos de probabilidade média de falha na demanda - PFDavg de acordo com a equações 14 a 17 para arquiteturas 1001

e 1002 objetos de estudo deste trabalho. A finalização dos cálculos de todos os luxos RBD exigem a comparação dos resultados obtidos com os requisitos solicitados nas especificações do projeto do sistema de segurança.

#### 4.1 CÁLCULOS RBD

Conforme Goble et al, algumas formas de cálculo de disponibilidade e tolerância a falhas são sugeridas, dentre elas, a técnica escolhida para o comparativo do controlador SIL com o controlador standard foi a RBD.

Conforme o item 2.4 o método RBD permite a simplificação dos componentes do sistema de forma que cada componente ou módulo seja associado à arquitetura a fim de garantir melhores métricas de confiabilidade do sistema.

Para componentes idênticos em paralelo, calcula-se o MTBF resultante a partir do MTBF e do MTTR fornecidos pelo fabricante do componente conforme Equação 1 abaixo:

$$MTBF_R = \frac{MTBF^2}{2 * MTTR} \tag{1}$$

Ou, de outra forma, calcula-se a partir das taxas de falhas, conforme Equação 2:

$$\lambda_R = 2 * \lambda^2 * MTTR \tag{2}$$

Calculando o MTBF do sistema em paralelo, tem-se um sistema em série conforme a Figura 27.

Figura 28 - Método de cálculo RBD resultante.

Para o caso de um sistema série, as equações de MBTF e taxa de falhas seguem abaixo com as equações 3 e 4 respectivamente:

$$MTBF_R = 1/(1/MTBF_1 + 1/MTBF_2 + 1/MTBF_n)$$

(3)

Do ponto de vista da taxa de falhas ( $\lambda$ ):

$$\lambda_R = \lambda_1 + \lambda_2 + \lambda_n \tag{4}$$

Existe uma forma de calcular sistemas redundantes genéricos, onde existem N equipamentos redundantes idênticos, dos quais M devem estar funcionando para que o sistema esteja em operação (1 <= M <= N). Este método é denominado redundância MooN, calculado a partir da Equação 5.

$$MooN = \frac{\lambda^{-1}}{(n-m)! \, m\left(\frac{n}{m}\right)} \, \left(\frac{\mu}{\lambda}\right)^{n-m} \tag{5}$$

Observa-se que:

- $\lambda = \text{taxa de falhas (falhas por hora)};$

- $\mu = \text{taxa de reparos};$

- D = disponibilidade (%);

A taxa de falhas deve ser calculada a partir da Equação 6.

$$\lambda = \frac{1}{MTBF} \tag{6}$$

A taxa da reparos é igual ao inverso do tempo médio para reparos conforme Figura 7

$$\mu = \frac{1}{MTTR} \tag{7}$$

A disponibilidade é calculada a partir da Equação 8.

$$D = \frac{MTBF_r}{(MTBF_R + MTTR)} * 100 \tag{8}$$

#### 4.2 CÁLCULOS DE PROBABILIDADE DE FALHAS

Para refinamento dos cálculos, foi incluída neste capítulo a forma de cálculo de probabilidade de falhas nos controladores standard para efeito comparativo das arquiteturas 1001 e 1002 nos controladores standard pesquisados.

De acordo com a norma IEC 61508 abaixo segue a forma de cálculo dos termos comuns às duas arquiteturas estudadas. Quando se deseja incluir taxas de falhas em controladores standard se utiliza na prática que metade da taxa de falhas é segura e a outra metade é perigosa, assim tem-se:

$\lambda$  - taxa de falhas;

$\lambda s$  - taxa de falhas segura;

$\lambda d$  – taxa de falhas perigosa;

A Equação 9 corresponde à taxa de falhas seguras:

$$\lambda s = \frac{\lambda}{2} \tag{9}$$

O cálculo de taxa de falhas perigosas é realizado através da Equação 10.

$$\lambda d = \frac{\lambda}{2} \tag{10}$$