# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SULINSTITUTOS DE INFORMÁTICA, FÍSICA, QUIMICA, ESCOLA DE ENGENHARIA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

| EED N A I | NDOIA  | V B D I W | BOEIRA |

|-----------|--------|-----------|--------|

| LENNA     | ハレい リケ | 31X D HWL | DULINA |

Study and Application of Direct RF Power Injection Methodology and Mitigation of Electromagnetic Interference in ADCs

Porto Alegre 2020

FERNANDO JARDIM BOEIRA

Study and Application of Direct RF Power Injection Methodology and Mitigation of

**Electromagnetic Interference in ADCs**

Dissertação apresentada ao programa de Pós-Graduação em

Microeletrônica da Universidade Federal do Rio Grande do Sul

como requisito parcial paraa obtenção do grau de Mestre em

Microeletrônica.

Orientador: Prof. Dr. Tiago R. Balen

Porto Alegre

2020

## CIP – CATALOGAÇÃO NA PUBLICAÇÃO

Boeira, Fernando Jardim

Study and Application of Methodology for Direct RF Injection and Mitigation of Electromagnetic Interference in ADCs [manuscrito] / Fernando Jardim Boeira. -2020.

82 f.:il.

Orientador: Tiago R. Balen.

Dissertação (Mestrado) — Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica. Porto Alegre, BR — RS, 2020.

1.DPI – Direct Power Injection. 2.IEC 62132-4. 3.Programmable System-on-Chip (PSoC). 4.Analog-to-digital converters. 5. Electromagnetic Interference. I. Balen, Tiago Roberto.

#### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos André Bulhões Vice-Reitor: Prof.<sup>a</sup> Patricia Pranke

Pró-Reitor de Ensino: Prof.ª Cíntia Inês Boll

Vice Pró-Reitor de Pós-Graduação: Júlio Otávio Jardim Barcellos

Diretora do Instituto de Informática: Prof.ª Carla Maria Dal Sasso Freitas

Coordenador do PGMICRO: Prof. Tiago Roberto Balen

Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

"Even if you have already taken a long walk, there is always a way to go." — SAINT AUGUSTINE

#### **ACKNOWLEDGEMENTS**

I thank my parents, Alvarino and Sueli, for their encouragement throughout my life.

Thanks to my family, Kelly, Arthur and Lucas. Kelly for all the dedication, support and understanding offered. Arthur and Lucas for being my propellers in the journey of improvement for our lives.

My special thank and acknowledgment to the advisor, prof. Dr. Tiago Roberto Balen, for welcoming me at the university, support and teachings provided during the master's course. Thanks also to the other professors I had during the course, for the teachings provided.

Thanks to colleague and friend M. Sc. Carlos Julio González Aguilera, for the partnership, support, discussions and shared knowledge.

I am grateful to the teachers and friends I met at UNISINOS: Feliciane Brehm, a great enthusiastic of this master's degree and Juliana Suzin, who provided all the necessary support for this professional formation. Thanks also to all the other colleagues from UNISINOS who contributed to this achievement.

Finally, I also thank the Federal University of Rio Grande do Sul, graduate program in microelectronics (PGMICRO) for providing this stage of my education and the accomplishment of this work.

#### **ABSTRACT**

There are many publications available in literature regarding the DPI (Direct Power Injection) technique for electronic systems, but few works specifically addressed for mixed-signal converters, which are components existent in almost all electronic devices. IEC 62132-4(International Electrotechnical Commission, 2006) and 62132-1(International Electrotechnical Commission, 2006) standards describe a method for measuring immunity of integrated circuits (IC) in the presence of conducted RF disturbances. This method ensures a high degree of repeatability and correlation of immunity measurements. Knowledge of the electromagnetic immunity of an IC allows the designer to decide if the system will need external protection, and how much effort should be directed to this solution. In this context, the purpose of this work is the study and application of the DPI methodology for injection of EMI in a mixed-signal programmable device, evaluating mitigation possibilities, with special focus on the analog-to-digital converters (ADCs). The main objective is to evaluate the impact of electromagnetic interference (EMI) on different converters (two Successive Approximation Register ADCs, operating with distinct sampling rate and a Sigma-Delta ADC) of the Cypress Semiconductor Programmable SoC (System-on-Chip), PSoC 5LP. Additionally a previously proposed fault tolerance methodology, based on triplication with hardware and time diversity is tested. Results show distinct behaviors of each converter to conducted EMI. Finally, the tested tolerance technique showed to be suitable to reduce error rate of such data acquisition system operating under EMI disturbance.

**Keywords**: DPI – Direct Power Injection. IEC 62132-4.Programmable System-on-Chip (PSoC). Analog-to-digital converters. Electromagnetic Interference.

#### **RESUMO**

Existem muitas publicações disponíveis na literatura sobre a técnica de DPI (Direct Power Injection ou injeção direta de energia) para sistemas eletrônicos, mas poucos trabalhos direcionados para conversores de sinais mistos, que são componentes existentes em quase todos os dispositivos eletrônicos. As normas IEC 62132-4 (IEC, 2006) e 62132-1 (IEC, 2006) descrevem um método para medir a imunidade de circuitos integrados (CI) na presença de distúrbios de RF conduzidos. Este método garante um alto grau de repetibilidade e correlação das medições da imunidade. O conhecimento da imunidade eletromagnética de um CI permite que o projetista decida se o sistema precisará de proteção externa e quanto esforço deve ser direcionado para esta solução. Nesse contexto, o objetivo deste trabalho é o estudo e aplicação da metodologia DPI para injeção de interferência eletromagnética em um dispositivo programável de sinal misto, avaliando as possibilidades de mitigação, com foco especial em conversores analógico-digitais (ADCs). O principal objetivo é avaliar o impacto da interferência eletromagnética em diferentes conversores (dois ADCs baseados em aproximação sucessiva, operando com taxa de amostragem distintas e um ADC do tipo Sigma-Delta) do SoC(System-on-Chip) programável da Cypress Semiconductor, PSoC 5LP. Além disso, é testada uma metodologia de tolerância a falhas proposta anteriormente, baseada em triplicação com diversidade de hardware e temporal. Os resultados mostram comportamentos distintos de cada conversor para a interferência eletromagnética conduzida. Finalmente, a técnica de tolerância testada mostrou-se adequada para reduzir a taxa de erros desse sistema de aquisição de dados operando sob perturbação eletromagnética.

**Keywords**: DPI - Injeção direta de potência. IEC 62132-4. Sistema em Chip Programável (PSoC). Conversores analógico-digital. Interferência Eletromagnética.

## LIST OF FIGURES

| Figure 2.1 – Microprocessor evolution                                                               | 20               |

|-----------------------------------------------------------------------------------------------------|------------------|

| Figure 2.2 – Global number of connected devices                                                     | 22               |

| Figure 2.3 – Trust model and EM information security threats                                        | 23               |

| Figure 2.4 – Examples of applications on the IoT market                                             |                  |

| Figure 2.5 – EMI Source Classification                                                              |                  |

| Figure 3.1 – Functions of the A/D Converter: sampling in time, quantizing in amplitude              | and linking to a |

| reference                                                                                           |                  |

| Figure 3.2 – Quantization process – MSB and LSB.                                                    |                  |

| Figure 3.3 – Common dynamic metrics: SNR, SINAD and SFDR.                                           | 31               |

| Figure 3.4 – ADC architectures, applications, resolution and sampling rates                         |                  |

| Figure $3.5 - \Sigma\Delta$ ADC Block Diagram.                                                      | 35               |

| Figure 3.6 – Conceptual $\Sigma\Delta$ ADC Modulator                                                | 36               |

| Figure 3.7 – Out-of-band noise rejection and decimation of a noise shaped signal                    | 37               |

| Figure 3.8 – Incorporating the quantizer in a feedback loop obtains noise shaping                   | 38               |

| Figure 3.9 – Simplified Schematic of an 8-bit SAR ADC                                               | 39               |

| Figure 3.10 – Basic Successive Approximation ADC                                                    | 40               |

| Figure 4.1 – PSoC overall block diagram                                                             | 42               |

| Figure 4.2 – PSoC 5LP Development KIT general view                                                  | 43               |

| Figure 5.1 – Arrangement of a direct injection test set-up                                          | 51               |

| Figure 5.2 – Example of the routing from the injection port to a pin of the DUT                     | 53               |

| Figure 5.3 – Flowchart of a test procedure                                                          | 54               |

| Figure 5.4 – SAR ADC Block Diagram                                                                  | 56               |

| Figure 5.5 – PSoC 5LP Voltage reference circuit schematic                                           |                  |

| Figure 5.6 – PSoC 5LP voltage reference circuit                                                     | 58               |

| Figure 5.7 – 100-pin TQFP Part Pinout                                                               | 59               |

| Figure 5.8 – Block diagram of test setup                                                            |                  |

| Figure 5.9 – Test setup and equipment                                                               | 60               |

| Figure 6.1 – Parameters and pins used to disturbance injection.                                     |                  |

| Figure $6.2$ – Conversion errors for EMI injected at VREF and input = $0 \text{ V}$                 |                  |

| Figure 6.3 –Conversion errors percent as function of input DC level                                 |                  |

| Figure $6.4 - \Sigma\Delta$ ADC conversion errors number as function of input DC level in different | *                |

| range                                                                                               |                  |

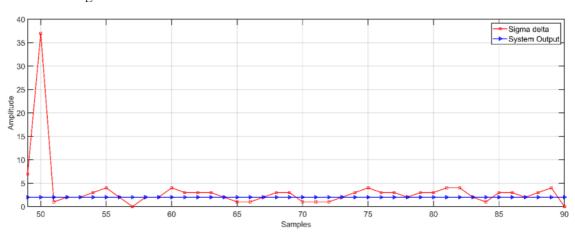

| Figure $6.5 - \Sigma\Delta$ conversion errors and healthy signal at system output                   |                  |

| Figure 6.6 – Another example of $\Sigma\Delta$ conversion errors and healthy signal at system outp  |                  |

| Figure $6.7 - \Sigma\Delta$ conversion errors – critical level                                      |                  |

| Figure 6.8 – Detailed visualization of the disturbance in the $\Sigma\Delta$ converter              |                  |

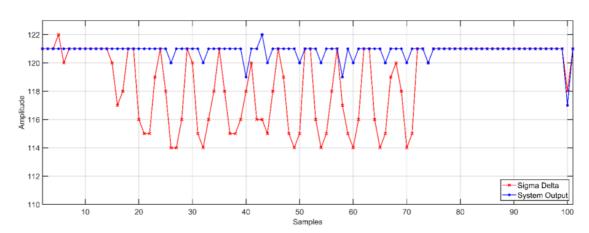

| Figure $6.9 - \Sigma\Delta$ conversion errors with the input at midscale                            |                  |

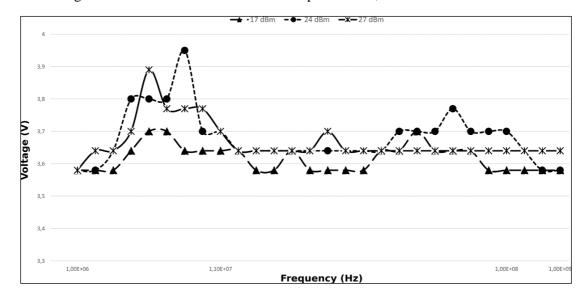

| Figure 6.10 – VDDA pin to inject EMI using DPI technique                                            |                  |

| Figure 6.11 – VDDA pin to EMI DPI                                                                   | 70               |

| Figure 6.12 – VDDA fluctuation when exposed to 17, 24 and 27 dBm EMI DPI                            | 602              |

## LIST OF TABLE

| Table 5.1 - Frequency step size versus frequency range | 55 |

|--------------------------------------------------------|----|

| Table 5.2 - Immunity Level Ranges                      | 55 |

#### LIST OF ABBREVIATIONS AND ACRONYMS

ADC Analog to Digital Converter

ABS Antilock Brake System

AE Auxiliary Equipment

CAGR Compound Annual Growth Rate

CIC Cascaded Integrator-Comb

CMOS Complementary Metal-Oxide-Semiconductor

DAS Data acquisition system

DAC Digital to Analog Converter

DMA Direct Memory Access

dB Decibel

DNL Differential Non-Linearity

DPI Direct Power Injection

DSP Digital Signal Processing (DSP)

DUT Device Under Test

EMC Electromagnetic Compatibility

EMI Electromagnetic Interference

ENOB Effective Number of Bits

HIS Hospital Information System

HF High Frequency

IC Integrated Circuit

IEC International Electrotechnical Commission

INL Integral Non-Linearity

IoT Internet of Things

ISM Industrial, Scientific and Medical Band

LPWAN Low Power Wide Area Networks

LSB Least Significant Bit

MS-DTMR Mixed-Signal Diversity Triple Modular Redundancy

MSB Most Significant Bit

NAD Noise and Distortion

OSR Oversampling Ratio

PCB Printed Circuit Board

PLD Programmable Logic Devices

PSoC Programmable System-on-Chip

RMS Root Mean Square

RF Radio Frequency

SAR Successive Approximations Register

SFDR Spurious Free Dynamic Range

SHA Sample-and-Hold

SINAD Signal Noise and Distortion

SNR Signal-to-Noise-Ratio

SoC System-on-Chip

THD Total Harmonic Distortion

TID Total Ionizing Dose

TMR Triple Modular Redundancy

UDB Universal Digital Blocks

VDDA Analog Power

VREF Reference Voltage

$\Sigma\Delta$  ADC Sigma-Delta Analog to Digital Converter

## **CONTENTS**

| 1. INTRODUCTION                                                                    | 13          |

|------------------------------------------------------------------------------------|-------------|

| 2. ELECTROMAGNETIC INTERFERENCE IN ELECTRONIC SYSTEMS                              | 17          |

| 2.1 Basic concepts                                                                 | 17          |

| 2.2 EMI/EMC history, trends and mitigation                                         | 18          |

| 2.2.1 Market Forecast concerning EMC                                               | 21          |

| 2.2.2 EMI on IoT systems                                                           | 21          |

| 2.3 EMI in Data Converters                                                         | 26          |

| 3. ANALOG-TO-DIGITAL CONVERTERS                                                    | 28          |

| 3.1 ADC Parameters and Characteristics                                             | 29          |

| 3.2 Dynamic and Static Parameters                                                  | 30          |

| 3.3 ADC Architectures                                                              | 33          |

| 3.4 Sigma-Delta Analog-to-Digital Converter ( $\Sigma\Delta$ ADC)                  | 34          |

| 3.5 Successive Approximation Register (SAR)                                        | 38          |

| 4. DEVICE AND DESIGN UNDER TEST (DUT)                                              | 41          |

| 4.1 Programmable SoC (PSoC 5LP) Technical Features                                 | 41          |

| 4.2 Data Acquisition System                                                        | 44          |

| 5. TEST SETUP                                                                      | 49          |

| 5.1 Requirements of IEC 62132-4                                                    | 49          |

| 5.2 Test Procedure                                                                 | 53          |

| 6. RESULTS AND DISCUSSIONS                                                         | 62          |

| 6.1 Injecting disturbance in VREF                                                  | 62          |

| 6.2 Injecting disturbance on VDDA (analog power supply):                           | 69          |

| 7. CONCLUSION                                                                      | 73          |

| REFERENCES                                                                         | 75          |

| APPENDIX A – INFRASTRUCTURE REQUIRED TO PERFORM THE TEST IEC62132-1 AND IEC62132-4 |             |

| APPENDIX B – ERRORS DATAS GATHERED WITH DIRECT POWER INJECTIO                      | N ON VREF82 |

| APPENDIX C – VOLTAGE FLUCTUATION AFTER DIRECT POWER INJECTION                      | I ON VDDA83 |

#### 1. INTRODUCTION

The electromagnetic interference (EMI) in electronic equipment has become more notable as technology evolves. People see with enthusiasm the evolution of electronic devices, mainly the wireless devices, but, unfortunately, the consequences of the pollution of frequency spectrum to the environment we live are not always considered.

The increasing use of electronic products leads this market to be fierce in terms of competitiveness, mainly for price and time-to-market constraints. This pressure often reflects in the work of system designers who are daily challenged to create innovative products that must cost less than the competitors, often within a tight schedule. However, for low cost products it is common some stages of the project to be skipped, such as functional tests that could recreate the actual use of the product in the field.

Along with the increasing demand for innovative electronic systems, a concern, that until then had not been considered so important, raised. However, it attracted more attention after the occurrence of a series of situations that brought risk of accidents to society as a whole. For example, during the early years of Antilock Brake System (ABS), Mercedes-Benz automobiles equipped with ABS had severe braking problems along a certain stretch of the German autobahn. The brakes where affected by a nearby radio transmitter as drivers applied them on the curved section of highway. The near term solution was to BUILD a mesh screen along the roadway to attenuate the EMI. This enabled the brakes to function properly when drivers applied them (NASA, 1995).

Thus, electromagnetic interference (EMI), which is a disturbance of electromagnetic origin that may cause performance degradation or affect the normal operation of a component, device and electronic systems, is being considered more often nowadays. EMI considers all the problems concerning the transfer of electromagnetic energy.

The interference may be intentional or accidental and may be of natural or artificial origin. According to Waes (2017), the earth's magnetic field is of natural origin and can cause interference in power systems by the influence of its force. Atmospheric discharges and winds are examples of natural causes of EMI.

The cost of maintaining an engineering area capable of dealing with electromagnetic interference issues is very high to some companies. This deficiency often causes unknown problems in products developed and commercialized by the company. This way, EMI may be

not properly treated due to the difficulties of solving the problem. As in many situations, especially in underdeveloped countries, electromagnetic interference is usually only dealt with when it arises and causes some damage, making the system more complex and more costly than if it had been planned at the beginning of the project. Nowadays a big challenge consist in to improve design methodologies and develop modeling techniques capable of providing simulations of circuit performance under EMI (JOVIC, 2010).

Another concept which will be addressed is Electromagnetic Compatibility (EMC), which is the ability of electronic equipment to function properly while immersed in an electromagnetic environment (IEC, 2016). The main topics of electromagnetic interference subject are: causes, effects and mitigation. The compatibility between electronic circuits should be achieved. Thus, an electronic system must work without impairing the operation of other devices, nor should it stop operating when installed/exposed to electromagnetic environments.

The motivation for study and research on EMI / EMC topicsis due to the limited knowledge and application of this topic in Brazil, the complexity of EMI understanding and, mainly, the demand for knowledge in this area.

In Brazil, there is no imposition for compliance with EMC standards for generalpurpose electronic products, although the recommendations presented by the International Electro technical Commission (IEC) serve as a reference. Nowadays, there is no comprehensive EMC / EMI standardization, the correct operation of electronic systems is very vulnerable to problems of electromagnetic interference due to the system topology itself, its interconnection cables and the configuration of the grounding system. Thus, the correct functioning of electrical and electronic products is compromised by the installation of new equipment in the vicinity, by the appearance of accidental connections, by the degradation of existing installations, among other factors. However, the National Telecommunications Agency (ANATEL), through Resolution No. 715 - Regulations for Conformity Assessment and Homologation of Telecommunications Products (ANATEL, 2019) now requires all national telecommunication equipment manufacturers to be compliant with specific EMC requirements - which reflect the technical specifications of the 2014/30/EU EMC Directive (COUNCIL OF EUROPEAN UNION, 2014). EMC requirements for biomedical equipment are also being adopted in Brazil, which (also) reflect the technical specifications of the EMC Directive.

The miniaturization of the electronic components is directly connected with technological innovation. Undoubtedly, electronic circuits became smaller while the systems

became more reliable. In this way, some areas such as medical equipment, automotive, and aerospace, for example, have taken advantage of this. One can imagine a cell phone in the 2000s and compare it to a mobile phone these days, the difference in size, functionality and cost is considerable. In this case, the processors have become faster, smaller and cheaper. This had been possible by the evolution in the microelectronics manufacturing process that allowed the transistors to become smaller and faster.

Reducing the size of the transistors increases the variability and consequently the probability of defects in nanoelectronic devices that, consequently, are more susceptible to environmental phenomena (CHENET, 2015). Thus, characterization of the susceptibility of integrated circuits (ICs) for electromagnetic disturbances is receiving special attention. This trend leads to the need for standardized measurement procedures that allow a comparative evaluation and analysis between different devices. The increasing technical development, on the other hand, has the consequence of increasing the complexity of the design of such systems, thus raising concerns regarding its reliability, performance and safety, especially with regard to its electromagnetic compatibility. It has become vital to prevent critical systems from malfunctioning because the consequences of these can be catastrophic. A possible way to overcome this problem is to use fault tolerance techniques in the design of such systems PRESTES, 2010).

The current study considers a previously proposed (by Chenet (2015))fault tolerance technique which is based on Triple Modular Redundancy (TMR) with diversity (DTMR) implementing a data acquisition system (DAS), prototyped in a PSoC. The objectives are, firstly, to evaluate the behavior of different architectures of data converters in the face of direct radio frequency (RF) power injection in their reference voltage and supply pins, and then to evaluate the effectiveness of the studied DTRM technique to mitigate EMI effects in this system.

Another important point considered for this study is that, today, most of the signal processing performed in electronic systems is digital, and the performance of the analog-to-digital converters (ADCs) present at the borders of the digital domain become very important (RAPUANO, 2005). To benefit from the Digital Signal Processing (DSP) advantages, an analog signal must be converted to a digital format, a task that is performed by an Analog-to-Digital Converter (A/D converter or ADC). The reverse procedure, that is, conversion from digital to analog domains, is performed by a Digital-to-Analog Converter (D/A Converter or DAC) (DORNELAS, 2018). Analog-to-Digital Converters (ADCs) are used in electronic

systems applied in large-scale to control, instrumentation and communication tasks that comprise mixed-signal interfaces.

In this work the Triple Modular Redundancy (TMR), a system-level fault tolerance technique, is considered. TMR and diversity are mainly used in critical applications where an error can result in harm for life or loss of high investment (CHENET, 2015). Throughout this textthe results of the impact of electromagnetic interference (EMI) on the three different converters of the Cypress Programmable SoC PSoC 5LP (CYPRESS SEMICONDUCTOR, 2013) is presented along with a discussion regarding the application of the methodology of redundancy with hardware diversity and its effectiveness to mitigate this type of interference in mixed-signal systems. Mainly, the standards IECs 62132-4(IEC, 2006) and 62132-1(IEC, 2006b) were followed to apply the Direct Power Injection (DPI) test to the PSoC device.

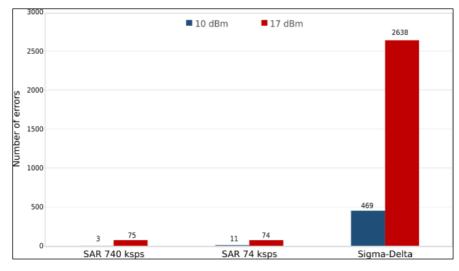

Therefore, this work contributes to the evaluation of the tolerance level and reliability of the converters and the voting system by injecting fault directly into the data converters. The main results show that the  $\Sigma\Delta$  ADC is more susceptible, in part due to its complex working principle and topology. Additionally, the applied tolerance technique is suitable to reduce the error rate of the overall system, as demonstrated in the rest of this text.

#### 2. ELECTROMAGNETIC INTERFERENCE IN ELECTRONIC SYSTEMS

At this moment, it is essential to understand some concepts about electromagnetic interference and how it happens. For the development of this research, it is also important a brief knowledge about the history of electromagnetic disturbances, as well as where the studies in this area are directed to. First of all, in order to better exemplify the possible effects, some interesting cases involving EMI will be presented.

#### 2.1 Basic concepts

Electromagnetic Interference is degradation in the performance of equipment or transmission channel or a system caused by an electromagnetic disturbance. It can be generated by spark-ignition in motor brushes, power circuit switching, inductive and resistive charge drives, relay drives, switches, circuit breakers, fluorescent lamps, heaters, automotive ignitions, atmospheric discharges and even electrostatic discharges between people and equipment, microwave equipment and mobile communication equipment. All of them can result in overvoltage, under voltage, surges, transients and other types of noise and interference (LAVARDA et al 2015).

The growing need for equipment to operate with different communication protocols, along with inadequate installations, allows the generation and emission of electromagnetic interference.

The occurrence of these disturbances is very common in industries and factories, where EMI is very frequent due to the greater use of machines and motors that generate transients in the electrical network. The biggest problem caused by EMI is the sporadic situations that gradually degrade the equipment and its components. According to Hanada et al. (2018), several problems can be generated by EMI, for example - in electronic equipment - we may have failures in communication between devices of network and/or computers, alarms generated without explanation, acting in relays that do not follow a logic and without command for this and, burnout of components and electronic circuits, among other effects. The presence of noise in the power supply is very common due to design errors in determining equipment and board grounding (FRÉMONT et al, 2012).

In general, at high frequencies, wires and PCB (Printed Circuit Board)paths are even closer to the behavior of an antenna, which helps us to understand why EMI emission

problems are aggravating in networks that operate at high speeds (PRESTES, 2010). Any electronic circuit is capable of generating some kind of magnetic field around it and its effect will depend on its amplitude and duration. Another typical example of how EMI can affect the behavior of an electronic component is a capacitor that is subject to a voltage peak higher than its specified nominal voltage (MANDRUCCOLO et al. 2010). It can cause the dielectric degradation (the thickness of the dielectric is limited by the capacitor's operating voltage, which must produce a potential gradient higher than the dielectric strength of the material), causing a malfunction and, in some cases, the burnout of the capacitor. Static electricity is an electrical charge in equilibrium that is generated primarily by the imbalance of electrons located under a surface or in the air of the environment. This imbalance of electrons thus generates an electric field that is capable of influencing other objects that are within a given distance. The charge level is affected by the type of material, contact speed and separation of the devices. When a not grounded object is electrostatically charged, an electric field associated with this charge is created around it and if an electronic device gets exposed to this field, electrostatic induction may occur. This can cause transfer of charges between the devices, which may result in a reduction of lifetime of the equipment, or even instantaneously damage it(CHENET et al. 2015).

#### 2.2 EMI/EMC history, trends and mitigation

Michael Faraday, near1843, demonstrated a zero electric field inside an electrified conductive surface. According to this experiment, the charges distribute homogeneously on the outside of this surface. This effect received the name of Faraday's Cage (MARCO, 2018). The German mathematician Carl Friedrich Gauss established the relation between the flows of the electric field through a closed surface with the electric charge that exists within the volume bounded by this surface, this is the principle of the electrostatic machine that was invented by the engineer Robert Jemison van de Graaff, around 1929 (MARCO, 2018). The knowledge of these effects has brought the possibility of preventing many problems caused by electromagnetic interference in several areas. In the case of vehicular applications, for example the meshes in electrical cables are responsible for shielding the transmission of important signals for the operation of the car.

The first known cases of electromagnetic interference occurred around 1930 in electric motors and electric railroads (PAUL, 2006). By 1950, the problem intensified with the emergence of the bipolar transistor, worsening between the 1960s and 1980s with the

invention of the integrated circuit and the microprocessor (PAUL, 2006). Thus, between 1960 and 1980, the main way to deal with EMI and power line transients issues was through grounding. In the 1970's, studies started to address PCB layout issues, in order to mitigate the effects of EMI in electronic equipment. However, the advances in this area were still very fast and even when a problem was solved, new equipment appeared in the market showing increased susceptibility to electromagnetic interference. Thus, in 1990 the studies began at the level of integrated circuit (MARDIGUIAN, 2004).

Some companies are highly concerned with EMI, as, for example, the automotive industry. With the arrival of autonomous vehicles, smart cities and as cars become more connected, sensors and other devices that emit EM signals will become increasingly present.

In the 2012 edition of IEEE International Symposium on Electromagnetic Compatibility the main theme was "trends in EMC engineering". Among the most discussed topic was the automotive industry, loss and absorbing materials, nanotechnology, high data rates and EMC rule checker software.

For Kruczkowski (2012), the automotive industry is in a period of aggressive innovation, adding modern features like Wi-Fi and radar. All of these emitters, combined with external interferers like cell towers, hot spots, and other vehicles, are potential sources of EMI to the processor-based systems that control all aspects of vehicle operation. In respect to materials science breakthroughs and how such advances can affect their area of expertise, composite materials with nanoparticles, nanotubes, or nanofiber for gaskets and shielding screens have already shown promissory. Nanowires have the potential to someday replace copper in high-density, high-speed interconnects; however, suitable approaches to signal integrity simulation and modeling are a necessity to avoid EMI when using such materials. Signal integrity has become a major concern for engineers because the demand for high-speed data transmission is greater.

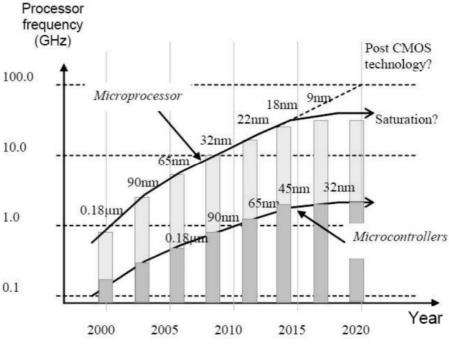

Miniaturization of transistors is very important for processor size reduction. This is why manufacturers are in a growing race to reduce the manufacturing size of their components. As already discussed, this miniaturization can have implications for EMC, mainly because the power supply reduction and frequency increase usually occur together with feature size reduction in technology scaling of integrated circuits. According to Jovic (2010), the time line of ICs performance is consistently rising, as can see observed in Figure 2.1.

Figure 2.1–Microprocessor evolution

Source: JOVIC (2010, p. 01).

The EMC industry is increasing relying on software simulation. With the speed in which new technologies emerge, the demand for EMI robust systems has increased very fast. The creation of standards, development of measurement and monitoring equipment and qualification of people has not accompanied the increasing diversity of characteristics in this area. Thus, development and use of software for simulation of EMI/EMC, is becoming an effective alternative to deal with this problem.

In relation to integrated circuits, it is important to consider that, internally, they have a thin layer of metal. In this frame are attached the semiconductor in the package process. Even though the lead frame is the largest component in an integrated circuit, at frequencies below 1 GHz, its presence is not considered as an antenna for receiving unwanted RF signals.

It is the cable harness and/or the traces of a printed circuit board which constitute efficient antennas. Thus, an IC receives the unwanted RF energy through the pins connected to the wires of such cables. Because of this, the electromagnetic immunity of an IC can be characterized by conducted RF disturbances (i.e. RF forward power) instead of field parameters as is usually the case in module and/or system testing (IEC 62132-4, 2006).

### 2.2.1 Market Forecast concerning EMC

Due to the importance and complexity of the subject, there are studies presenting detailed forecasts on investments that should be made in the area of EMC for the coming years. According to Global Market Insights(2017) EMI shielding materials market size should grow at a moderate rate from 2017 to 2024. The factors that are driving the EMI industry are increasing telecommunications infrastructure worldwide, increasing use of electronic devices in automobiles and tremendous growth of mobile wireless communications that is resulting in the need to shielding electronic equipment from interference by unwanted radio frequencies.

New generations of integrated electronic circuits with stacked & multi-chip package structures are more susceptible to interference that, besides affect performance of circuits, may also lead to data loss(JOVIC, 2010). The shielding market must be boosted by the EMI regulations. The area of defense/military has been important for the development of research of new technologies and, this should continue to happen in the coming years due to growing political and economic instability in many regions of the world. The aerospace industry is expected to continue growing and this includes space exploration. There is a forecast that 30,000 new passenger aircrafts will be needed in the next 20 years. Based on a survey conducted by the website Research and Market (2015), electromagnetic compatibility shielding market was valued at USD 3.51 billion in 2014 and estimated to grow at a CAGR (Compound Annual Growth Rate) of 6.09% during the forecast period of 2015-2020.

This shielding market can be divided according to the application: aerospace, automotive, defense and electronics. Different applications require distinct material. The main type of material includes aluminum, brass, nickel, silver, stainless steel, conductive carbon/graphite composites, metalized plastics and others.

The automotive market must be one of the main propellant for EMC concern. With the advent of self-driven cars, several new devices must be released, as well many other communication and safety standards.

#### 2.2.2EMI on IoT systems

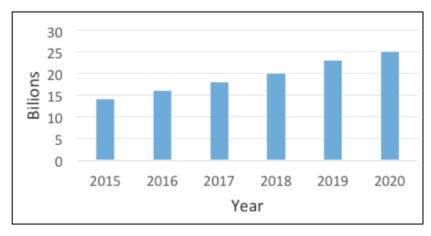

The interconnecting of physical devices embedded with electronics, sensors and network connectivity is called Internet of Things (IoT). According to Wiklundh (2017) and Stenumgaard (2017) the wireless part of global Internet traffic is expected to grow from approximately 50% today, to about 75% in 2020, and the first 5G products are expected to be

available in 2020. By 2025, the Internet of Things is projected to have an \$11 trillion impact on companies all around the world (WAES, VANKEIRSBILCK, PISSOORT and BOYDENS, 2017).

Figure 2.2- Global number of connected devices

Source: WIKLUNDH and STENUMGAARD (2017, p 01).

New services are being created, and using data gathered using devices like smart meters and surveillance cameras. These data are uploaded to servers through communication networks.

Another important area to be considered include medical field. For example, the medical telemetry systems used in hospitals can continuously acquire vital signs and transmit them to a staff station or administrative area. At a terminal in a staff station, staff members can observe multiple patients at the same time. A medical telemetry system connected to a hospital information system (HIS) is an example of critical IoT system (HANADA AND KUDOU, 2018).

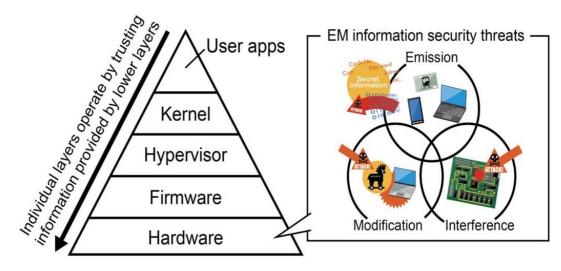

For Hayashi, Verbauwhede and Radasky (2018), IoT systems, may be divided in, at least, two layers. The upper layer – software – and lower layer – hardware. Thereby, to ensure reliability in IoT services it is very important to ensure that the hardware has a correct operation, because, in this layer, the data are gathered and transmitted. Figure 2.3 shows a system where each layer consists of terminals that operate by trusting the information coming from the layer below them. According to Waes et al. (2017), effects of EMI are observed in both hardware and software. In hardware, the effects of EMI can result in noise accumulating on traces and leading to false readings on inputs or distortion on outputs. As a result, software effects, such as jumps in the program execution and data corruption can be witnessed.

Figure 2.3 – Trust model and EM information security threats

Source: HAYASHI, VERBAUWHEDE and HADASKY (2018, p 01).

As already mentioned, automotive applications are continuously increasing complexity. Until 2025 it is expected that each car has more than one hundred microcontrollers with different functions.

More and more, those microcontrollers are used in a safety-critical environment, where a failure might result in injury, and in the worst case, even human deaths (WAES, VANKEIRSBILCK, PISSOORT and BOYDENS, 2017).

According to Fuqaha (2015, apud Dornelas 2018), the overall concept of the IoT is a network in which every domain-specific application is interacting with domain-independent services, whereas in each domain, sensors and actuators communicate directly with each other. In figure 2.4, some examples of this interconnectivity are depicted.

Figure 2.4 – Examples of applications on the IoT market

Source: AL-FUQAHA et al., (2015, apud DORNELAS, 2018, p 16).

Sources of Electromagnetic Interference in IoT Environment: Even though electronic products designed to operate in IoT environment are planned to comply with lower bands of the electromagnetic spectrum, the operating frequency, in some cases, may be particularly high. Some applications may operate up to 30 GHz (outdoor) and up to 90 GHz (indoor) WIKLUNDH et al. 2017. Nowadays, the majority EMI susceptibility tests are considering the frequencies up to 18 GHz. Therefore, it is possible to infer that, in the future, devices may suffer EMI from sources which are not considered in current compliance tests. Thus, for a wide range of new frequencies, both emission and immunity properties will be unknown. Furthermore, instruments and equipment for EMC testing will have to be further developed and modified to cope with the large extension of frequency bands (WIKLUNDH and STENUMGAARD, 2017).

The trend is that low power devices and components will dominate in IoT applications. For Wiklundh and Stenumgaard (2017), low power devices usually show lower signal-to-noise ratio (SNR) for the wireless connections. This means larger sensitivity to electromagnetic interference.

For medical applications, caution with distortions in electrical signals should be even greater as devices work by collecting and analyzing low amplitude signals. Considering the accuracy of medical application, some structural care should be observed, such as equipment installation location and the communication standards in which they operate. Wiklundh and Stenumgaard (2017) expose a great example: microwave therapy equipment and some heaters emit electromagnetic noise in the same frequency band as the ISM (Industry, Scientific and Medical) band, which is often used in the communication infrastructure of IoT. Although not specifically a medical device, microwave ovens are often installed in hospital wards. Careful planning of the location of the microwave equipment and careful installation of the IoT system can minimize the electromagnetic effect. In addition, IoT communication utilizes a wide variety of communication standards that must be taking in to account as a potential polluter of the EM spectrum. Currently, standards such as ZigBee, Bluetooth, IEEE802.11 series, and wireless LAN are used in the same environment. This all greatly increases the probability of EMC problems affecting the functioning of medical devices.

According to Hayashi, Verbauwhede and Radasky (2018) in IoT systems the electromagnetic vulnerability maybe divided in three categories:

Electromagnetic interference induced from devices operation—non intentional: It happens when the electronic devices are processing data, in normal operation. Electromagnetic interference is attributed to the radiated electromagnetic waves that vary with time according to data.

**Intentional electromagnetic interference:** Intentional electromagnetic interference is a threat that disables information and communication equipment by stopping functionality. This threat was usually carried out by military organizations. However, as time goes by, access to ordinary citizens is becoming possible.

**Intentional Modification of electronic circuits:** There are a lot of reasons that brings some manufacturers to make modifications on products. Amongst them is the cost reduction, which may bring loss of quality, potentially, turning the electronic devices more susceptible to EMI.

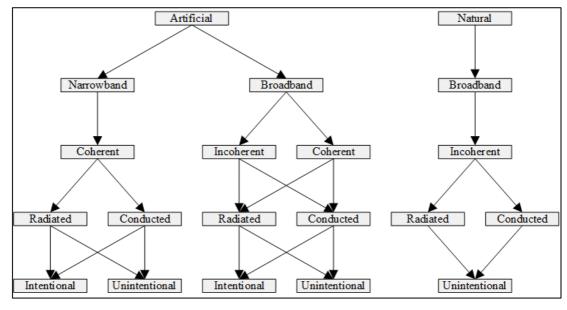

In the same way, Waes et al. (2017) classifies the electromagnetic interference in five categories according to the sources. The classification is shown in the figure 2.5.

Figure 2.5 – EMI Source Classification

Source: WAES, VANKEIRSBILCK, PISSORT AND BOYDENS (2018, p 02).

Artificial EMI is originating from manmade devices and infrastructure. Lightning on the other hand, is an example of natural EMI. Another classification considers the bandwidth of interfering signal: narrowband or broadband EMI. Broadband disruptions have a greater frequency range than the bandwidth of the device subjected to EMI. Electromagnetic disturbs can be also classified as coherent or incoherent: coherent EMI is defined as signals with a well-defined relationship between amplitude, frequency and phase. Regarding the propagating media, EMI can be considered as conducted or radiated: conducted EMI propagates through electrical conducting paths such as grounding planes or wires. All non-conductive EMI is classified as radiated. Finally, the last category considers whether or not the device is transmitting intentionally. Intentional radiating devices are emitting devices whose primary function is dependent on radiated emitters, such as communication, navigation and radar systems. Natural EMI events are by definition classified as unintentional. Restricted radiating devices only access the electromagnetic spectrum for a limited time, such as garages opening systems and wireless microphones.

#### 2.3 EMI in Data Converters

Previous research has been conducted into determining the susceptibility of analog voltage comparators (FIORI, 2012) and flash ADCs (KENNEDY, 2018) to EMI. According to Fiori (2012) when the input signals contain EMI and can cause false switching of the

output. It was observed that this effect was due to rectification of the EMI signal performed by non-linear devices causing unwanted perturbation of operating points of the transistors. This reflects in erroneous decision of bits during comparison leading to bit errors at the converter output.

MUSUMECI (2009) discusses if RFI can affect the  $\Sigma\Delta$  ADC operation, once the antialiasing filter could mitigate it. However, it is concluded that the  $\Sigma\Delta$  ADC operation can also be affected by substrate interference, which derives from digital core switching.

Kennedy (2018) presents some information about previous tests carried out on the internal structure of ADCs. For example, tests carried out on the analog voltage comparator showed that this block may be susceptible to EMI. The sample and hold phase uses a capacitor and a switche at the ADC inputs to sample and maintain the input voltage. Because of that, distortion caused by MOS switches due to the injected EMI has been investigated. Kennedy (2018) also comments about bulk CMOS processes suffering from substrate noise coupling due to the common substrate connection across the die. Undesirable responses in the circuit can be caused from EMI injected into the IC and propagated by the substrate.

Fiori (2012) addresses the topic of susceptibility of CMOS voltage comparators for radio frequency interference, in which some studies and tests were carried out on false commutations induced by the disturbances superimposed onto the nominal input signals. Fiori concluded that the RFI distortion occurs mainly at the comparator input stage, causing the comparator limit to change. Probably with this, the result of an AD conversion can be affected.

Kennedy (2018) focused his studies to verify the susceptibility of flash ADCs to electromagnetic interference concluding that supply port is immune to interference but the analog input and reference voltage input ports are susceptible to injected EMI.

#### **3.** ANALOG-TO-DIGITAL CONVERTERS

An analog signal is continuous in time, with continuous variations of its amplitude. The physical quantities such as velocity, pressure, temperature, electric current and voltage, are examples where analog variations occur. The analog-to-digital (ADC) conversion of signals is applied in control, instrumentation and communication systems, including those used in critical applications. AD and DA converters, depending on the needs of the system, perform the interface between the analog and digital world (AGUILERA, 2018).

Several errors may be introduced by sampling and quantization process that occurs in the task of converting an input analog signal. Additionally, the quantized and sampled signal is only meaningful when a relationship exists between the digital number range considered and a physical reference value (DORNELAS, 2018). Figure 3.1 shows the function involved in the conversion process, where an A / D converter transforms an analog signal, continuous in time, into a sampled signal, discrete in time, quantized within a finite number of integer values, determined by the characteristic resolution of the converter in bits.

a reference reference Digital amplitude value 101 100

D

С

f,

time

Figure 3.1 – Functions of the A/D Converter: sampling in time, quantizing in amplitude and linking to

011

010

001

000

Source: PELGROM (2010, p. 02).

Next subsections present the important characteristics and terminologies regarding ADCs, which are the main devices studied in this work.

#### 3.1 ADC Parameters and Characteristics

Some parameters are responsible for determine the performance and output accuracy of the ADC. Characteristics such as Signal-to-Noise-Ratio (SNR), Total Harmonic Distortion (THD), Signal to Noise and Distortion (SINAD), and Effective Number of Bits (ENOB) are explained below.

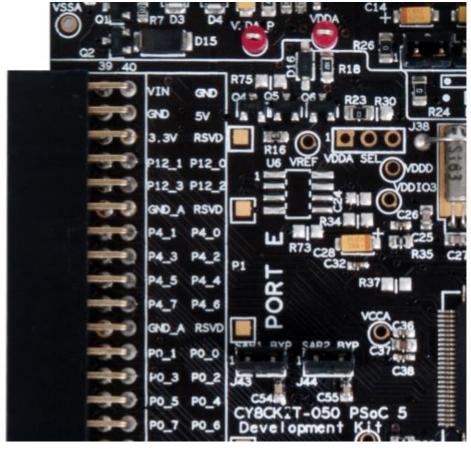

**Reference Voltage (VREF):** It is a standard voltage provided through external supply or generated from de ADC module. VREF is used such an indicator for Analog Input Voltage. The range of VREF varies among different devices and the respective device datasheet must be referred to know the exact or allowed values (ATMEL, 2016).

**Resolution:** it is the number of bits per conversion cycle that the converter is capable of processing. The resolution of an A/D converter (ADC) is specified in bits and determines how many distinct output codes (2<sup>n</sup>) the converter is capable of producing. Analog equivalent resolution is the smallest voltage increment corresponding to a 1 LSB (Least Significant Bit)change. This ADC specification determines the smallest analog input signal an ADC can resolve.

Sampling Rate and Bandwidth: The converter input receives the analog signal in continuous time and the ADC module needs to convert it to discrete digital values. These digital values are sampled from the analog signal. Sampling rate is defined as the number of samples acquired in one second (ATMEL, 2016). The maximum frequency supplied to the ADC of the input analog signal is the bandwidth. Nyquist theorem guides sampling rate and bandwidth parameters. According to this theorem, the sampling rate must be at least twice the bandwidth of the input signal (ATMEL, 2016).

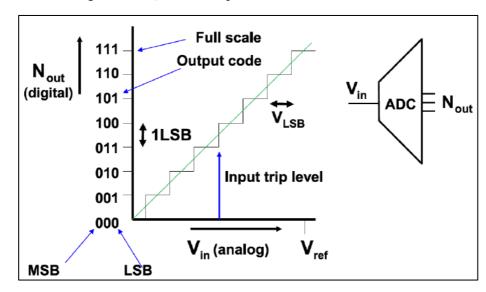

**Quantization:** In A/D Converters, the quantization process is performed after sampling and is also known as rounding (DORNELAS, 2018). Quantization is the process where the sampled analog input voltage will be replaced with an approximation from a finite set of discrete values (ATMEL, 2016). The converter dynamic range is divided into (ideally) equally-spaced quantized levels, each represented by analog amplitude (DORNELAS, 2018). The digital representation is done in binary numbers. The quantization level is a power of 2, 2<sup>N.</sup> The letter N represents the number of bits or resolution of the converter. Figure 3.2 shows

the most significant bit (MSB) and the least significant bit (LSB) in a quantization process. According to Pelgrom (2010), the Full Scale (FS) of the converter corresponds to the available analog dynamic range, Vrefp - Vrefn (typically Vrefn = 0).

Figure 3.2– Quantization process – MSB and LSB.

Source: PELGROM (2010, p. 175).

#### 3.2 Dynamic and Static Parameters

The basic purpose of an ADC is to transform an analog signal into an equivalent digital value. Characterization techniques of an analog-to-digital converter intend to achieve static and dynamic behavior of converters (FLORES, 2003; IEEE, 2010). Below, the main parameters for static and dynamic characterization of converters are detailed.

**Static Parameters:** Static errors are evaluated from the characteristic curve of the converter. This curve depends on its response to a ramp that goes through its entire scale (FLORES, 2003). The transfer function of the ADC is given by an N-bit line, and its actual characteristic curve will be formed by a uniform 2<sup>N</sup> levels.

**Differential Non-Linearity (DNL):** This parameter describes the deviation between two analog values corresponding to digital input values. A DNL error specification less or equal than 1 LSB ensures a monotonic transfer function without missing codes (AGUILERA,

2018). Non-linearity produces quantization steps with varying widths. For the case of a perfect ADC, the step width must be 1LSB. However, an ADC with DNL shows step widths which are not exactly 1LSB (ATMEL, 2016).

**Integral Non-Linearity (INL):** Integral non-linearity (INL) is defined as the maximum vertical difference between the actual and the ideal curve. It indicates the amount of deviation of the actual curve from the ideal transfer curve (ATMEL, 2016). INL can be interpreted as a sum of DNLs.

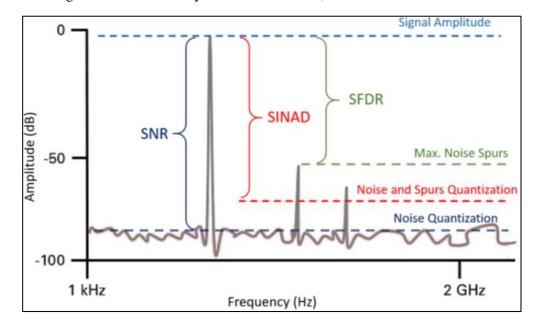

**Dynamic Parameters:** Dynamic errors are errors that occur when the signal is varying (RAPUNO, 2005) and may be associated to the above mentioned non-linearities. Dynamic parameters are used for ADC characterization and can be obtained with a sine excitation with known amplitude and phase, and evaluated the obtained spectrum of the converted signal (FLORES, 2003). In figure 3.3, some of the dynamic parameters ADCs may be observed. The following text will detail the dynamic parameters, such as Signal-to-Noise-Ratio (SNR), Total Harmonic Distortion (THD), Signal Noise and Distortion Ratio (SINAD), and Effective Number of Bits (ENOB).

Figure 3.3 – Common dynamic metrics: SNR, SINAD and SFDR.

Source: DORNELAS (2018, p. 32).

**Signal to Noise Ratio (SNR):** SNR is defined as the ratio of the output signal voltage level to the output noise level (ATMEL, 2016). It is possible to calculate SNR (dB) using this formula:

$$SNR(dB) = 20 \log \left( \frac{V_{RMS(Signal)}}{V_{RMS(Noise)}} \right)$$

(3.1)

In an ideal analog-to-digital converter the quantization error is distributed between -1/2 LSB and +1/2 LSB, and the Signal-to-quantization-noise ratio (SQNR) is calculated using this formula:

$$SNR = 6.02N + 1.76dB$$

(3.2)

The higher the value of SNR (dB), the better will be the performance of ADC.

**Signal-to-Noise and Distortion Ratio (SINAD):** Signal to noise and distortion (SINAD) is a combination of SNR and THD parameters (ATMEL, 2016). For Maloberti (2010, apud Aguilera 2018), SINAD is the relationship between the fundamental frequency and the frequency integration of all harmonic content obtained by spectral analysis of the converted signal, excluding the fundamental itself and the DC level. SINAD can be calculated with SNR and THD by:

$$SINAD = 10 \log 10 \left[ 10^{\frac{SNR}{10}} + 10^{\frac{THD}{10}} \right]$$

(3.3)

The higher the value of SINAD, the better will be the performance of ADC.

Total Harmonic Distortion (THD): When a sine wave is applied to a nonlinear ADC, the digitized output will contain harmonics of the input signal. The total harmonic distortion (THD) is the ratio, in percent or decibel, of the Root Mean Square (RMS) value of the harmonics to the RMS value of the component of the output signal at the input signal frequency (RAPUNO, 2005), considering a pure sine wave as input. The THD is a good metric for evaluating the correct functionality of data converters. This parameter is also correlated with DNL and INL. The THD is calculated in dB or as a percentage value (MALOBERTI, 2007; IEEE, 2010):

$$THD_{\%} = \left(\frac{\sqrt{V_2^2 + V_3^2 + \dots + V_N^2}}{V_1}\right) X \ 100\%$$

(3.4)

To achieve better performance, the THD value of an ADC should be as low as possible (ATMEL, 2016)

**Effective Number of Bits (ENOB):** The effective number of bits (ENOB) is a measure of accuracy and expresses the total of noise and distortion(NAD) relative to the full scale of the ADC. ENOB is another way of representing the signal to noise ratio and distortion (SINAD), in units of bits, and can be derived from the following formula (ATMEL, 2016):

$$ENOB = \frac{SINAD - 1.76}{6.02} \tag{3.5}$$

Ideally, the ENOB value should be as close as possible to the resolution of the ADC.

**Spurious Free Dynamic Range (SFDR):** is the ratio of the root-mean-square signal amplitude to the root-mean-square value of the highest spurious spectral component in the first Nyquist zone (MALOBERTI, 2007). The SFDR is important for communication systems.

#### 3.3 ADC Architectures

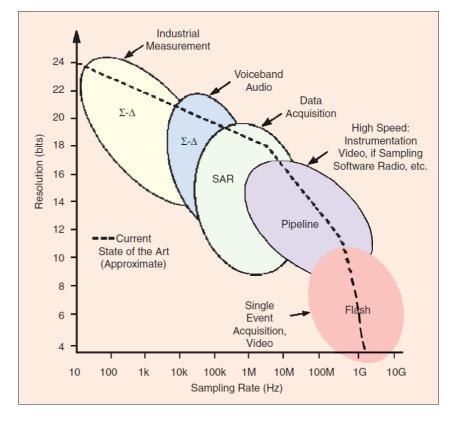

For Rapuano *et al* (2005), the ADC application can be characterized by five main market requirements - data acquisition, precision industrial measurement, voice band and audio, high speed and communication systems. Figure 3.4 shows the performance (resolution and sampling rate) related to different ADC architectures demanded for different applications.

Figure 3.4– ADC architectures, applications, resolution and sampling rates.

Source: RAPUANO et al (2005, p. 02).

The experimental part of this work considers the ADCs embedded in the Cypress Semiconductor Programmable SoC (System-on-Chip), PSoC 5LP, (CYPRESS SEMICONDUCTOR, 2013). Such PSoC comprises two architectures of ADCS – SAR and  $\Sigma\Delta$  for this reason, both architectures are detailed below.

#### 3.4 Sigma-Delta Analog-to-Digital Converter (ΣΔ ADC)

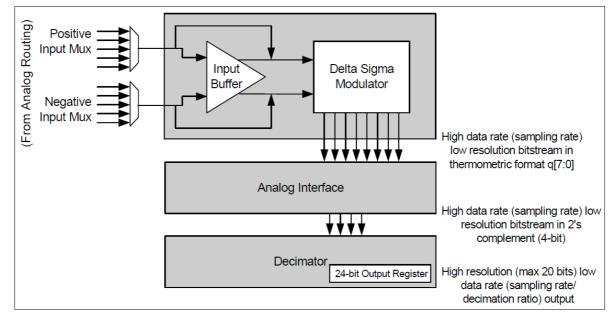

This converter has the following technical characteristics:  $100~\mu V$  offset, a gain error of  $\pm 0.1\%$ , integral nonlinearity (INL) of 1 LSB, differential nonlinearity (DNL) of 0.5 LSB, and signal-to-noise ratio (SNR) of 90 dB ( $\Sigma\Delta$  ADC) in 16-bit mode (PSoC 5LP Architecture TRM, 2017). It is possible to program this AD to work between 8 - to 20-bit resolution. It offers Internal and external reference options, differential/single ended inputs and the sample rate can be adjusted between up to 384 ksps. While the maximum clock that can be applied to the modulator is 6.144 MHz The  $\Sigma\Delta$  ADC from PSoC 5 uses the internal 1.024-V reference (default), but an external reference is allowed.

This  $\Sigma\Delta$  ADC is composed of three blocks: an input amplifier, a third order  $\Sigma\Delta$  modulator, and a decimator. The input amplifier provides a high impedance input and a user selectable input gain. The decimator block contains a 4 stage Cascaded Integrator Comb (CIC) decimation filter and a post processing unit. The CIC filter operates on the data samples directly from the modulator. The post-processing unit optionally performs gain, offset, and simple filter functions on the output of the CIC decimator filter (PSoC 5LP Delta Sigma Analog to Digital Converter, 2017). Figure 3.5 shows the PSoC5  $\Sigma\Delta$  ADC macro block diagram.

Figure  $3.5 - \Sigma\Delta$  ADC Block Diagram.

Source: PSoC 5LP Architecture TRM (2017, p. 377).

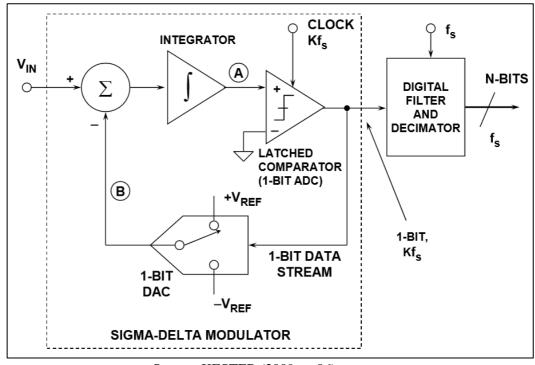

A conceptual1<sup>st</sup> order ADC modulator is shown in figure 3.6. The modulator consists in a closed loop system that constantly compares and samples the present analog input signal at the comparator positive side with the integrator voltage (KUMAR *et al*, 2016).

The ADC operates as follows: assume a dc input at VIN; the integrator is constantly ramping up or down at node A; the output of the comparator is fed back through an 1-bit DAC to the summing input at node B; the negative feedback loop from the comparator output, passing through the 1-bit DAC, back to the summing point, will force the average dc voltage at node B to be equal to VIN. This implies that the average DAC output voltage must be equal the input voltage VIN. The average DAC output voltage is controlled by the ones-density in the 1-bit data stream from the comparator output. As the input signal increases towards +V<sub>REF</sub>,

the number of "ones" in the serial bit stream increases, and the number of "zeros" decreases. Similarly, as the signal goes negative towards  $-V_{REF}$ , the number of "ones" in the serial bit stream decreases, and the number of "zeros" increases. From a very simplistic standpoint, this analysis shows that the average value of the input voltage is contained in the serial bit stream produced by the comparator output. The digital filter and decimator process the serial bit stream and produce the final output data (KESTER, 2009).

Figure 3.6 – Conceptual  $\Sigma\Delta$  ADC Modulator.

Source: KESTER (2009, p. 06).

To better understand the  $\Sigma\Delta$  ADC, fundamentals concepts of oversampling and noise shaping need to be known. These techniques bring improvement to ADC speed and resolution. According to Maloberti (2007), the advantage of oversampling is that the signal band occupies a small fraction of the Nyquist interval making it possible to use digital cancellation ontherelativelylargefractionofthequantizationnoisethatisoutsidetheband of interest. The use an ideal digital filter after the A/D conversion removes the noise from fB to fs/2 and significantly reduces the quantization noise power by a factor of fs/(2fB) leading to:

$$V^{2} = nB = \frac{\Delta^{2}}{12} \cdot \frac{2fB}{fs} = \frac{V_{ref}^{2}}{12.2^{2n}} \cdot \frac{1}{OSR}$$

(3.6)

where Vref is the reference voltage and n is the number of bits of the quantizer. The definition of the equivalent number of bits shows that an oversampling by OSR potentially improves the number of bits from n to:

$$ENOB = n + 0.5. log_2. (OSR)$$

(3.7)

Showing that every increase of the OSR by a factor four potentially improves the converter resolution by1-bit. For example, for gaining 5-bit resolution, it is necessary to use OSR = 1024, a high oversampling. Nevertheless, when oversampling is used to relax the anti-aliasing specifications, the additional benefit of obtaining extra bits is positive.

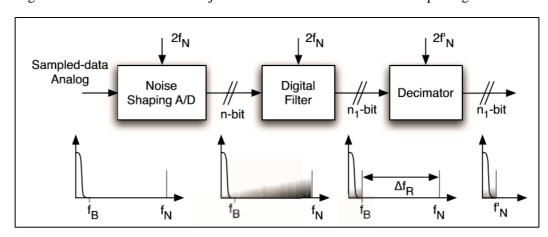

The oversampling method becomes more effective if the noise spectrum is lowered in the signal band, possibly at the expenses of an increase of the out-of-bandportion, thereby changing the white spectrum of the quantization noise into a shaped spectrum. Having more noise in high frequency regions is not problematic as the digital filter used after the ADC (Fig. 3.7) removes it. Incorporating the quantizer in a feedback loop as shownin Figure 3.8 gives rise to the desired in-band noise reduction, also called noise shaping.

Figure 3.7– Out-of-band noise rejection and decimation of a noise shaped signal.

Source: MALOBERTI (2007, p. 256).

Figure 3.8 – Incorporating the quantizer in a feedback loop obtains noise shaping

Source: MALOBERTI (2007, p. 257).

The scheme has a sampled data input that, after the processing block A(z), is converted into digital. For closing the loop it is necessary to generate the analog representation of the converted signal as done by the DAC. A second processing block A(z) is used before the subtracting element. The linear model of figure 3.8 (b) represents the quantization error with the additive noise  $\varepsilon_Q$  that is a second input of the circuit.

## 3.5 Successive Approximation Register (SAR)

The PSoC 5LP device has two successive approximation register analog-to-digital converters (SAR ADCs) in addition to the  $\Sigma\Delta$  ADC. The SAR ADC is designed for applications that require medium resolution and medium to high data rate. The ADC Successive Approximation Register (ADC\_SAR) component provides medium-speed (maximum 1-msps sampling) and medium-resolution (12 bits maximum) (PSoC 5LP ADC Successive Approximation Register, 2015). Other relevant features are an SNR about 70 dB and rail-to-rail input (0V to Vdda) (PSoC 5LP Architecture TRM, 2017).

This SAR ADC requires a low RMS jitter clock source. The maximum frequency of the clock source is 18 MHz. The maximum jitter on the sampling clock for 12-bit resolution is 32 ps RMS. The maximum input clock that can be applied to the SAR is 18 MHz and 1 MSPS sample rate (PSoC 5LP Architecture TRM, 2017).

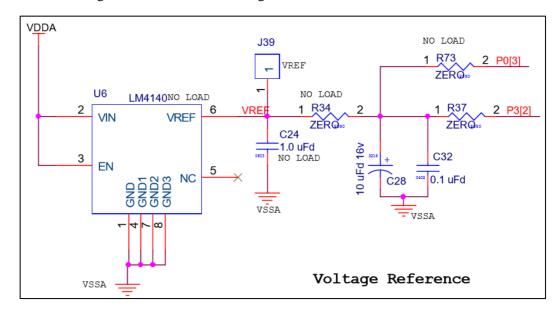

The SAR ADC requires a stable reference voltage between 1 V and Vdda (maximum 5.5 V). This can be set either as an internal or an external reference. The internal reference can be Vdda/2, 1.024V, 1.2V or the PSoC DAC's output voltage (PSoC 5LP Architecture TRM, 2017).

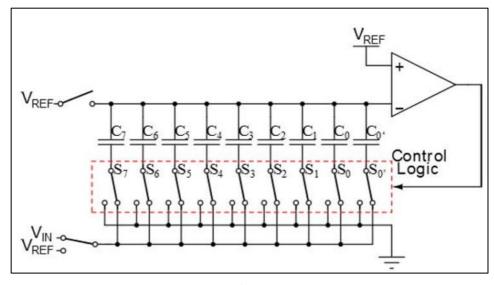

Figure 3.9 illustrates a simplified schematic of an 8-bit charge redistribution SAR ADC. This circuit consists of four main blocks: a capacitor array, a comparator, a set of switches, and the digital control logic for the switches. The capacitor array consists of N +1 binary-weighted capacitors, where N is the number of bits of the converter. Each bit is associated with one capacitor. The conversion is performed by a sequence of comparisons of the input signal with quantization levels generated by the reference voltage through the capacitive dividers formed by the switching scheme, converging to an equivalent digital representation. The code register, belonging to the digital control part of the converter, which also controls the state of the switches, will hold the final converted word after the charge redistribution phase (GONZÁLES, 2018).

Figure 3.9 – Simplified Schematic of an 8-bit SAR ADC.

Source: GONZÁLES (2018, p. 06).

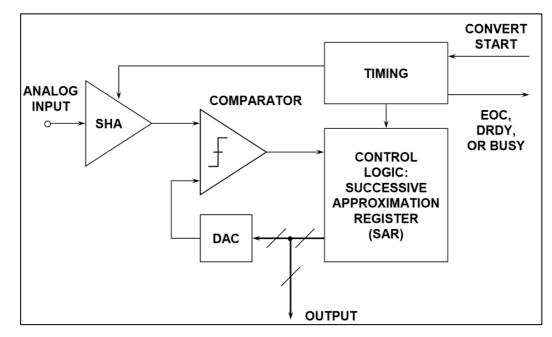

Figure 3.10 shows the SAR basic working. On the assertion of the CONVERT START command, the sample-and-hold (S&H) is placed in the hold mode, and the internal DAC is set to midscale. The comparator determines whether the S&H output is above or below the DAC output, and the result (bit 1, the most significant bit of the conversion) is stored in the successive approximation register (SAR). The DAC is then set either to ¼ scale or ¾ scale (depending on the value of bit 1), and the comparator makes the decision for bit 2 of the conversion. The result is stored in the register, and the process continues until all of the bit values have been determined. When all the bits have been set, tested, and reset or not as appropriate, the contents of the SAR correspond to the digital value of the analog input, and the conversion is complete (KULARATNA, 2008). Note that the acronym "SAR" actually stands for

Successive Approximation Register (the logic block that controls the conversion process), but is universally accepted as the acronym for the architecture itself (KESTER, 2009).

Figure 3.10– Basic Successive Approximation ADC

Source: KESTER (2009, p. 01).

### 4. DEVICE AND DESIGN UNDER TEST (DUT)

In this chapter, the device and the design on which tests were performed are presented. The DUT consists of a Data Acquisition System (DAS) programmed into a PSoC. The PSoC 5LP is a device that integrates configurable analog and digital peripherals, memory and microprocessor on a single chip (CYPRESS SEMICONDUCTOR, 2015). Besides that, the PSoC 5LP includes two Successive Approximation Register (SAR) ADCs and one  $\Sigma\Delta$  ADC which, in this work, reevaluated when exposed to electromagnetic interference (EMI).

Section 4.1 describes the main features of the PsoC 5LP, while section 4.2 addresses issues related to the implemented DAS.

## 4.1 Programmable SoC (PSoC 5LP) Technical Features

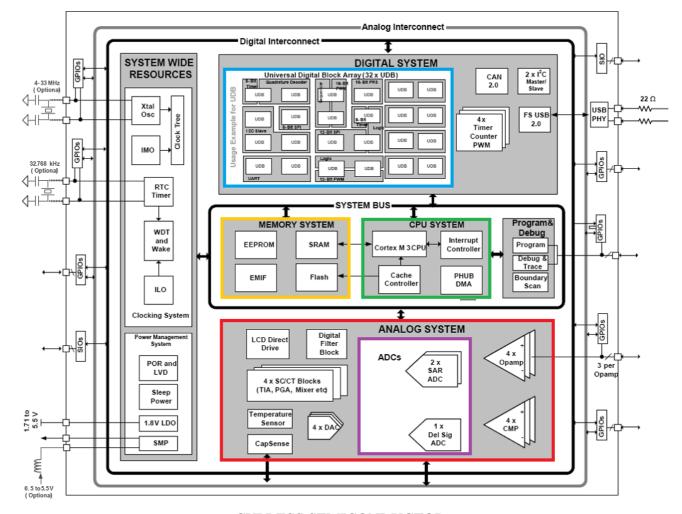

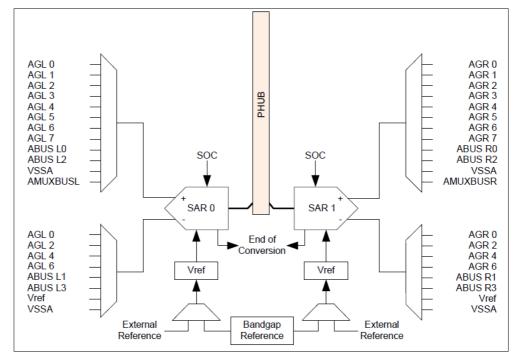

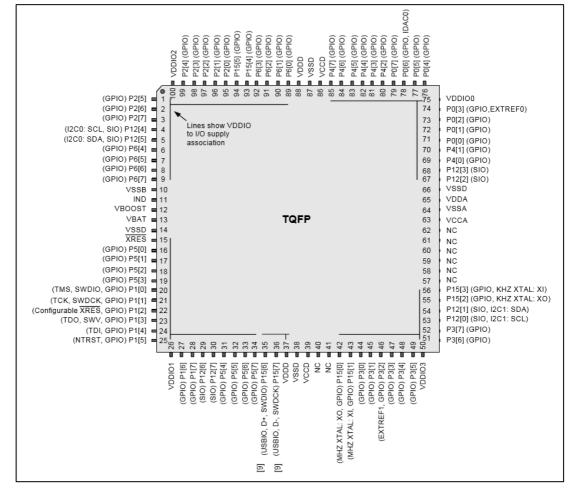

The DAS was implemented in a commercial, programmable, mixed-signal SoC called PSoC 5LP (CYPRESS SEMICONDUCTOR, 2013a), from Cypress Semiconductor. The architecture block diagram of this integrated circuit is shown in figure 4.1. The PSoC 5LP part number used is CY8C5588AXI-060. The device is manufactured in 130 nm CMOS technology and consists of a Cortex ARM CPU32-bit M3 (up to80 MHz clock), 256 KB Flash Memory, 64 KB SRAM Memory, 2 KB EEPROM, 24 channels of Direct Memory Access (DMA),digital peripherals as communication interfaces and, additionally, UDB-based(Universal Digital Blocks), Programmable Logic Devices (PLDs),which provide the implementation of various functions such as timers, counters and others.

Figure 4.1 – PSoC overall block diagram

Source: CYPRESS SEMICONDUCTOR(2018, p. 04).

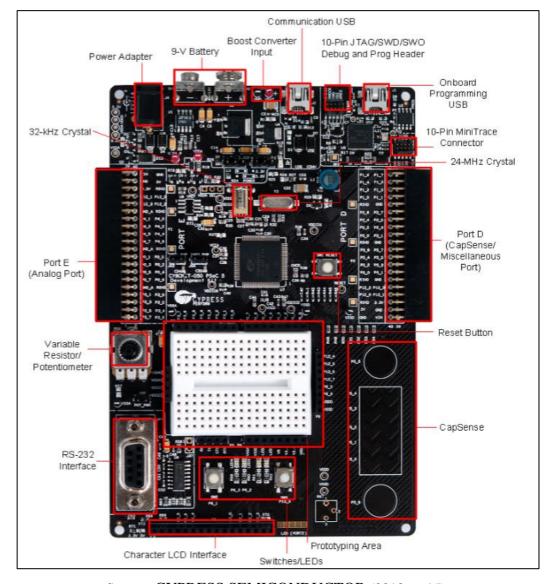

Fig. 4.2 shows PSoC 5LP development kit general details. The main technical features will be better detailed as follows.

Figure 4.2 – PSoC 5LP Development KIT general view

Source: CYPRESS SEMICONDUCTOR (2013, p. 15).

## **4.2 Data Acquisition System**

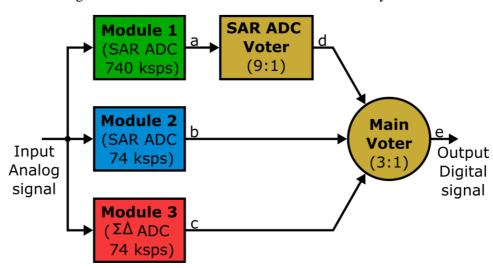

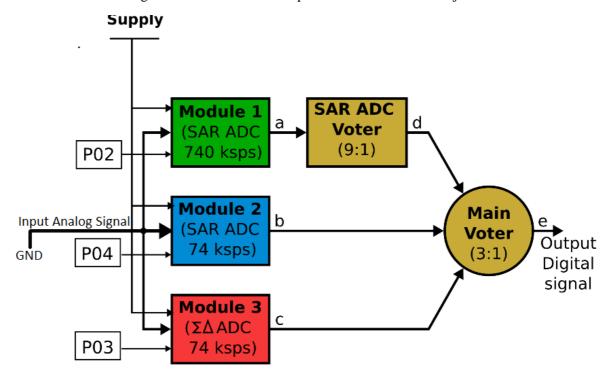

The current study considers a previously proposed System (CHENET et al. 2015) which is based on TMR with design diversity (DTMR) implementing a fault tolerant data acquisition system (DAS), prototyped in a PSoC. The objectives are, firstly, to evaluate the behavior of different architectures of data converters under direct radio frequency (RF) power injection in their reference voltage and supply pins, and then to evaluate the effectiveness of the studied DTRM technique to mitigate EMI effects in this system. The fault tolerant DASsimplified block diagram is shown in Figure 4.3.

Figure 4.3 – DAS scheme based on TMR and diversity

Source: CHENET (2015, p. 61).

The system is composed of three parallel converters: two Successive Approximation Register (SAR) ADCs and one  $\Sigma\Delta$  ADC architecture. These converters operate in different working frequencies; the first SARADC operates with a sampling rate of 740 ksps (kilo samples per second) and the other two converters (SAR – module 2 – and  $\Sigma\Delta$  ADC) work with a sampling rate of 74 ksps. This way a triple modular redundancy (TMR) approach is achieved. The use of different converter architectures constitutes the spatial (or hardware) diversity, and the different sampling rates constitute the temporal diversity (CHENET, 2015). Within the implementation of the system, it is necessary to build a voting structure: a temporal SAR ADC voter to vote upon the oversampled words generated by the SAR operating at 740 ksps and a main voter who conducts the voting between the SAR ADC voter output and the other two converters. The ADC SAR voting is done bit-by-bit considering 9-out-of-10 samples generated by the ADC (one is discarded to have an odd number); performing also the

coarse synchronization of the system (its output throughput is then 74 ksps). In the end, after the voting, the digital output of the system is obtained. The whole voting system is implemented in software.

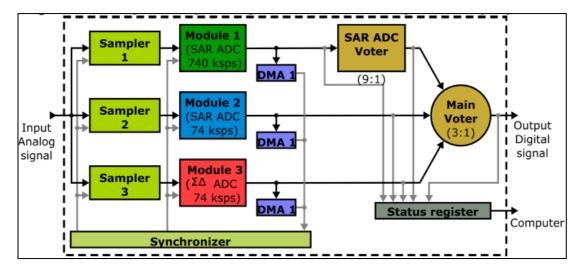

Figure 4.4 shows in detail the full implementation of DAS on PSoC 5LP. Beyond analog-to-digital converters and voters initially planned, the implementation demands samplers (sample-and-hold blocks), direct memory access (DMA) units and a fine-synchronizer, to cope with the different latencies of the converters.

Figure 4.4 – Detailed implementation of DAS into the PSoC 5LP

Source: AGUILERA (2018, p. 41).

The adopted scheme consists in one individual sample-and-hold for each ADC, triggered by a synchronizer circuit, as shown in figure 4.4. The first advantage of this scheme is that it provides an extra redundancy, as using a single sampler could generate an incorrect response of the system in the case of an error affecting this block. The second advantage of the is that the impedance seen by the sampler output is higher than in a scheme with three ADCs connected in a single block. This way the samplers can maintain the sampled data for a higher period of time. The ADCs were implemented with prebuilt components of the PSoC 5LP. They were set to 8-bit resolution, internal clock source, internal reference voltage, and analog input in common and in the range 0 to 2,048 V.

The basic voting concept adopted in the implementation of the main voter and the ADC SAR voter was the majority voting. The majority voting has the disadvantage of loss in accuracy when applied to mixed-signal systems due to the need of a threshold for the

construction of a tolerance window, which allows the majority to be determined when the data to be voted on is approximate, but not exactly the same as in most digital systems.

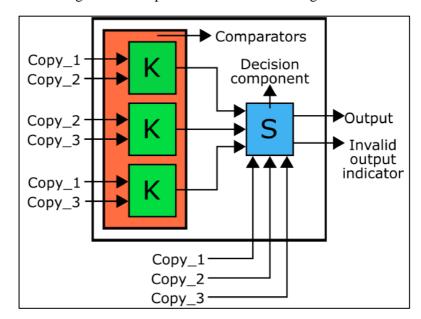

The implementation of majority voting in the digital domain can be done by following the bit-by-bit voting or word voting concepts (CHENET, 2015). The word voter adopted in this system, as illustrated in figure 4.5, consists of three comparators and one decision element. The comparators perform mutual subtractions between the outputs of the three redundant copies (comprising all possible combinations), producing three error signals. Based on these error signals, the decision element selects the correct value for the voter's output.

Figure 4.5 – Representation of word voting scheme

Source: CHENET (2018, p. 05).

The software (C language code) used to program this voter is shown in figure 4.6. The tolerance window has been set to 4 decimal units and an indication (main\_voter\_error\_det) is generated in the case an error is detected.

Figure 4.6 – Software code generated to implement the main word voter algorithm

```

void main voter()

2

error1 = abs (SAR_ADC_voter_data - module2Data[1]);

3

4

error2 = abs (module2Data[1] - module3Data[1]);

error3 = abs (module3Data[1] - SAR ADC voter data);

5

6

7

if (error1 <= 4)

system output = SAR ADC voter data;

9

else if (error2 <= 4)

system output = module2Data[1];

10

11

else if (error3 <= 4)

system output = module3Data[1];

12

13

else

system output = 0;

14

15

16

if ((error1 > 4) || (error2 > 4) || (error3 > 4))

main_voter_error_det = 1;

17

18

```

Source: CHENET (2015, p. 66).

As illustrated in figure 4.7, bit-by-bit voting consists of a counter and a decision element for each bit position, as well as a word assembler. The number of 'ones' of each bit position between all words is counted and this information is taken to the decision element, which votes (if the bit is zero or one)based on the number of counted 'ones'. Subsequently, each of these voted bits is submitted to the word assembler, whose generates the output word. The advantage of bit-by-bit voter is that it is easier to implement in the case of many voting inputs (as is the case of this block: 9 inputs).

Copy\_x\_bit\_1

Copy\_x\_bit\_1

Copy\_x\_bit\_2

Copy\_x\_bit\_7

S

Bits Decision counter component

Word Assembly

Outpu

Figure 4.7 – Representation of bit-by-bit voting scheme

Source: AGUILERA (2018, p. 43).

The software (C language code) used to program this voter is shown in figure 4.8. If at any bit position different logical states are detected between words, an indication (SAR\_ADC\_voter\_error\_det) is generated.

Figure 4.8 – Software code generated to implemented the main bit-by-bit voter algorithm

```

void SAR_ADC_voter()

2

3

bits = 0;

4

SAR_ADC_voter_data = 0;

5

for (i = 0; i < 8; i++)

6

bit_counter[i] = 0;

7

for (i = 0; i < 8; i++)

8

10

for (j = 1; j < 10; j++)

11

12

bits = (module1Data[j] & mask[i]) != 0;

13

if (bits == 1)

14

bit_counter[i] = bit_counter[i] + 1;

15

16

}

17

for (i = 0; i < 8; i++)

18

19

20

if (bit_counter[i] > 4)

21

SAR_ADC_voter_data = SAR_ADC_voter_data + mask[i];

22

23

24

bigger = module1Data[1];

25

smaller = module1Data[1];

26

for (pointer = 2; pointer < 10; pointer++)</pre>

27

28

if (bigger < module1Data[pointer])</pre>

29

bigger = module1Data[pointer];

30

if (smaller > module1Data[pointer])

31

smaller = module1Data[pointer];

32

33

error = bigger - smaller;

34

if (error > 4)

35

SAR_ADC_voter_error_det = 1;

36

```

Source: CHENET (2015, p. 67).

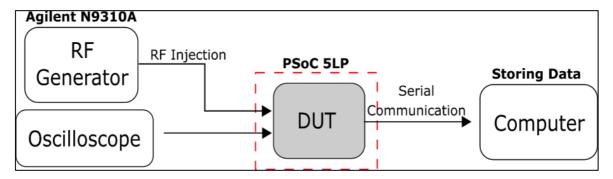

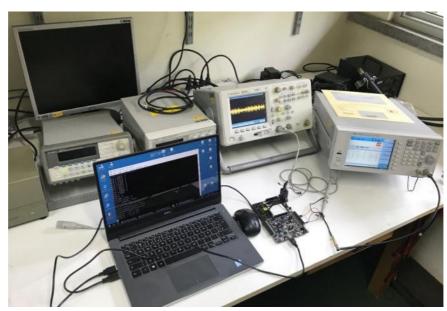

#### 5. TEST SETUP

The main objective of this study is to evaluate the impact of conducted electromagnetic interference (EMI) on the three different converters of the Cypress Semiconductor Programmable SoC (System-on-Chip) system (PSoC 5LP) PSoC (CYPRESS SEMICONDUCTOR, 2013) and discuss whether the methodology of redundancy with hardware diversity is effective for this type of interference.

To make it possible, a study of the IEC standards 62132-4 (IEC, 2006) and 62132-1 (IEC, 2006) was done, together with a study of the PSoC 5LP device. These standards describe a method for measuring immunity of integrated circuits (IC) in the presence of conducted RF disturbances. This method ensures a high degree of repeatability and correlation of immunity measurements. Besides that, it establishes a common base for the evaluation of semiconductor devices used in equipment functioning in an environment subject to unwanted radio frequency electromagnetic waves.

A major challenge that eventually became one of the main contributions of this work was to propose a setup of tests that were both real and feasible using the available laboratory infrastructure at UFRGS.

Throughout the text of this chapter there will be notes specifying some points that could not be followed as the norm, but it is important to emphasize that the results can be used in a comparative way, since they were obtained with this same setup.

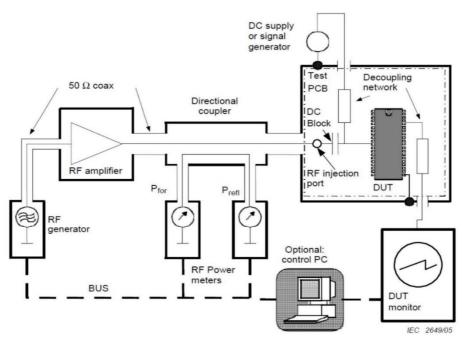

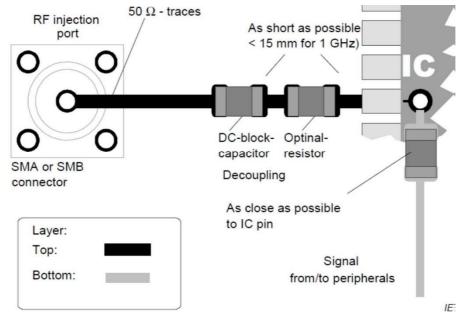

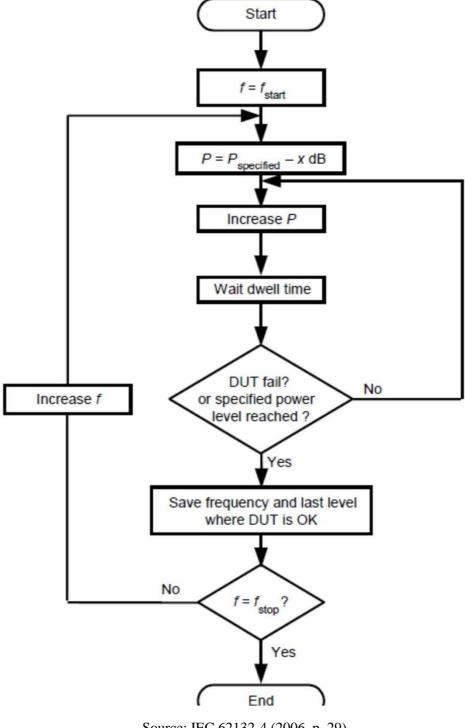

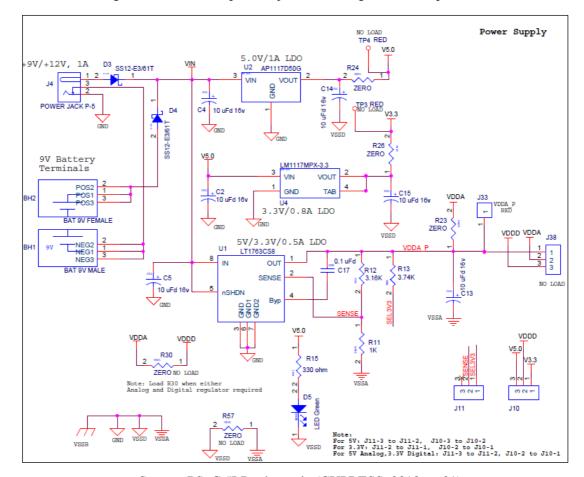

## 5.1 Requirements of IEC 62132-4

This part of IEC 62132 describes a method to measure the immunity of integrated circuits (IC) in the presence of conducted RF disturbances, e.g. resulting from radiated RF disturbances.

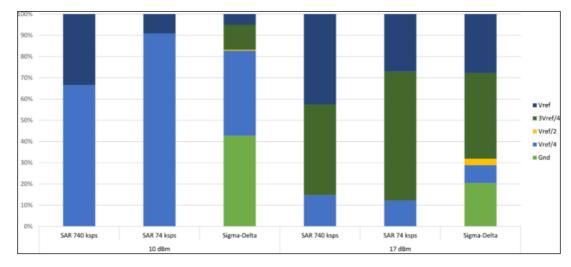

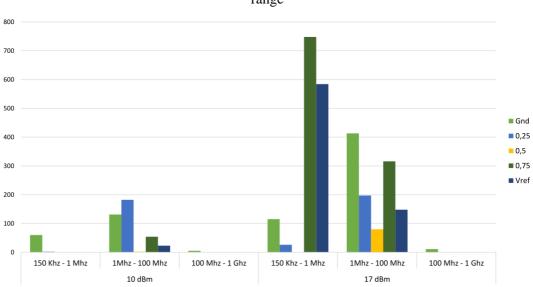

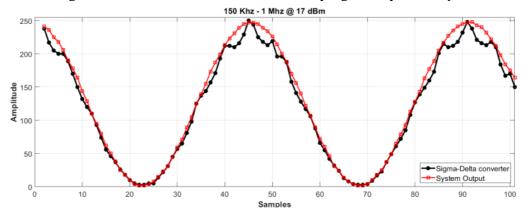

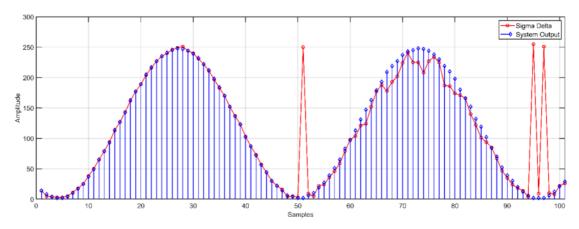

The minimum electromagnetic immunity level required for an IC depends on the maximum permitted level of RF disturbance to which an electronic system can be submitted. The value of the immunity level is dependent on system and application specific parameters. To determine the immunity performance of an IC, a simple measurement procedure, and a measurement setup in which resonances are avoided, is required to guarantee a high degree of repeatability (IEC 62132-4, 2006).