#### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

#### FERNANDO FERNANDES DOS SANTOS

# Understanding and Improving GPUs' Reliability Combining Beam Experiments with Fault Simulation

Thesis presented in partial fulfillment of the requirements for the degree of Doctor of Computer Science

Advisor: Prof. Dr. Paolo Rech Coadvisor: Prof. Dr. Luigi Carro

Porto Alegre December 2021

#### **CIP** — **CATALOGING-IN-PUBLICATION**

dos Santos, Fernando Fernandes

Understanding and Improving GPUs' Reliability Combining Beam Experiments with Fault Simulation / Fernando Fernandes dos Santos. – Porto Alegre: PPGC da UFRGS, 2021.

134 f.: il.

Thesis (Ph.D.) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação, Porto Alegre, BR–RS, 2021. Advisor: Paolo Rech; Coadvisor: Luigi Carro.

1. GPUs. 2. Reliability. 3. High Performance Computing. 4. Safety critical systems. I. Rech, Paolo. II. Carro, Luigi. III. Título.

#### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos André Bulhões

Vice-Reitora: Prof. Patricia Helena Lucas Pranke

Pró-Reitor de Pós-Graduação: Prof. Júlio Otávio Jardim Barcelos

Diretora do Instituto de Informática: Prof. Carla Maria Dal Sasso Freitas

Coordenador do PPGC: Prof. Claudio Rosito Jung

Bibliotecário-chefe do Instituto de Informática: Alexsander Borges Ribeiro

#### **ABSTRACT**

Graphics Processing Units (GPUs) have moved from being dedicated devices for multimedia and gaming applications to general-purpose accelerators, employed in High Performance Computing (HPC) and safety-critical applications, such as autonomous vehicles. This market shift led to a burst in the GPU's computing capabilities and efficiency, significant improvements in the programming frameworks and performance evaluation tools, and a sudden concern about their hardware reliability.

In order to evaluate the GPU reliability, researchers expose a device to a neutron beam and perform fault injection to simulate the fault propagation. While beam experiments provide a very realistic error rate of the device, it lacks fault propagation visibility. Contrarily, fault injection allows the complete visibility of the fault propagation, but the fault simulation and the error model are often limited to user-accessible resources and may lead to unrealistic results. Consequently, a methodology to accurately estimate the error rate of a device is necessary to answer two of the fundamental open questions in GPU reliability evaluation: (1) whether fault simulation provides representative results and can be used to predict the Failure In Time (FIT) rates of codes running on GPUs. (2) are the single and double bit-flip accurate error models to simulate faults on a GPU.

This thesis presents a novel FIT estimation approach to predict the NVIDIA GPUs' error rate. The proposed FIT estimation is achieved by comparing and combining high-energy neutron beam experiments that account for more than 13 million natural terrestrial exposure years, an extensive architectural-level fault simulation (using SASSIFI and NVBitFI), and detailed application-level profiling, requiring more than 1,000 GPU hours. Results show that, in most cases, the estimated Silent Data Corruption (SDC) rate is sufficiently close (differences lower than  $5\times$ ) to the experimentally measured SDC rates. The knowledge from the FIT estimation is then used to present a new error model based on the relative error in opposition to single/double bit flip. The relative error is based on a new method that extracts the relative error differences from a fault injection at the Register-Transfer Level (RTL).

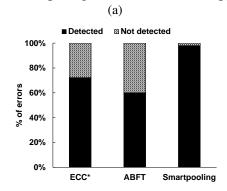

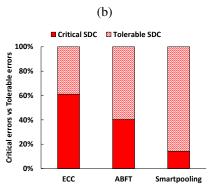

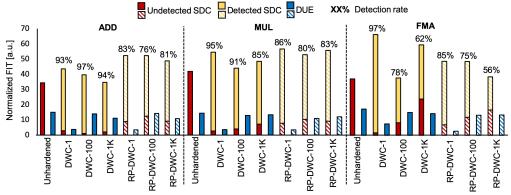

Using the experimental, architectural, and algorithmic analysis, this work presents also two novel hardening solutions for HPC and safety-critical applications: (1) Reduced Precision Duplication With Comparison (RP-DWC). RP-DWC's primary goal is to lower the overhead of Duplication With Comparison (DWC) by executing the redundant copy in reduced precision. RP-DWC achieves an excellent coverage (up to 86%) with

minimal overheads (as low as 0.1% time and 24% energy consumption overhead). (2) Dedicated software solutions for hardening Convolutional Neural Networks (CNNs). The Algorithm-Based Fault Tolerance (ABFT) employed to the matrix multiplication (the core of the CNNs) can correct more than 60% of the critical SDCs in a CNN, while re-designing the CNN's max pool layers leads to a detection up to 98% of SDCs. Additionally, this work is the first to evaluate the CNNs' error rate and CNNs' hardening efficiency on neutron beam experiments.

Keywords: GPUs. Reliability. High Performance Computing. safety critical systems.

## Entendendo e Melhorando a Confiabilidade das GPUs Combinando Experimentos com Feixe e Injeção de Falhas

#### **RESUMO**

Graphics Processing Units (GPUs) passaram de dispositivos dedicados a aplicações multimidia e gaming, para se tornarem aceleradores de propósito geral usados em High Performance Computing (HPC) e aplicações críticas como carros autônomos. Tal mudança no mercado das GPUs levou a um aumento nas capacidades computacionais, eficiência energética, melhoras nas ferramentas de programação e de análise de performance, e também um aumento na preocupação com a confiabilidade do hardware das GPUs.

Com o objetivo de avaliar a confiabilidade das GPUs, pesquisadores expõe o dispositivo a um feixe de nêutrons e realizam injeções de falhas para simular a propagação das falhas. Se por um lado experimentos de radiação provêm uma taxa de falhas realista, por outro lado eles não permitem visualizar a propagação das falhas no hardware e na aplicação. Contrariamente, a injeção de falhas permite a completa visualização da propagação de uma falha injetada, porém, na maioria das vezes os modelos de falhas são por sua vez limitados ao que o pesquisador consegue acessar e modificar, o que pode levar a resultados não realísticos. Consequentemente, uma metodologia para estimar com precisão a taxa de falhas de um dispositivo é necessária para responder duas questões fundamentais na avaliação da confiabilidade das GPUs: Se a injeção de falhas consegue prover resultados representativos que podem ser usados para estimar a taxa Failure In Time (FIT) de códigos executando em GPUs, e se os modelos de falhas que consideram a modificação de um único bit ou dois bits são modelos acurados para simular falhas em uma GPU. Sendo assim, essa tese propõe uma nova metodologia para estimar a taxa Failure In Time de GPUs NVIDIA. A metodologia proposta é possível através da comparação e combinação dos resultados de experimentos de radiação realizados em um feixe de nêutrons de alta energia, que correspondem por mais de 13 milhões de anos de exposição no fluxo terrestre natural, e extensivos experimentos utilizando simulação de falhas (usando SASSIFI e NVBITFI), e profiling de aplicações que requerem mais de 1,000 horas de GPU. Os resultados mostram que, para a maioria dos casos, as taxas de Silent Data Corruptions (SDCs) estimadas são suficientemente perto (diferenças menores que  $5\times$ ) das estimadas experimentalmente nos testes de radiação. O conhecimento extraído da estimação do FIT é então usado para propor um novo modelo de falhas em oposição ao bit flip único ou

duplo. O modelo de falhas proposto é baseado no erro relativo extraído de injeção de falhas em *Register Transfer Level* (RTL) comparando as diferenças observadas na saída das injeções.

Usando uma análise experimental, arquitetural, e algorítmica, esse trabalho apresenta também duas novas soluções de tolerância a falhas para HPC e aplicações críticas. A primeira solução proposta é a *Reduced Precision Duplication With Comparison* (RP-DWC), onde o principal objetivo é diminuir a sobrecarga causada pela *Duplication With Comparison* (DWC) executando a cópia redundante em uma precisão reduzida. A técnica RP-DWC consegue uma taxa de detecção excelente, 86%, com sobrecarga mínima, podendo chegar aumento de tempo de execução mínimos de 0.1%, e em alguns casos somente 24% de aumento no consumo de energia. O segundo tipo de solução proposta é voltado para *Convolutional Neural Network*, onde duas modificações foram apresentadas. A técnica já conhecida, *Algorithm Based Fault Tolerance* (ABFT) empregada as multiplicações de matrizes (maior parte do processamento das CNNs) conseguem corrigir mais de 60% dos SDCs críticos em uma CNN, enquanto recriando camadas especificas de uma CNN, *maxpool*, foi capaz de detectar 98% dos SDC. Adicionalmente, esse trabalho também é o primeiro a validar a taxa FIT de CNNs, como também a eficiência de tolerância a falhas aplicadas a uma CNN em experimentos de radiação.

**Palavras-chave:** GPUs, confiabilidade, Computação de Alta Performance, sistemas críticos.

#### LIST OF ABBREVIATIONS AND ACRONYMS

ABFT Algorithm-Based Fault Tolerance

AVF Architecture Vulnerability Factor

BFS Breadth-first search

CCL Connected Component Labeling

CFD Computational Fluid Dynamics

CNN Convolutional Neural Network

COTS Commercial Of The Shelf

CUDA Compute Unified Device Architecture

DMR Double Modular Redundancy

DUE Detected Unrecoverable Error

DWC Duplication With Comparison

ECC Error Correction Code

EPL Expected Precision Loss

FIT Failure In Time

GPU Graphics Processing Unit

HPC High Performance Computing

IOV Instruction Output Value model

IPC Instructions Per Cycle

ISA Instruction Set Architecture

LUD LU Decomposition

MWBF Mean Work Between Failures

MxM Matrix Multiplication

NW Needleman-Wunsch

RP-DWC Reduced Precision Duplication With Comparison

RTL Register-Transfer Level

SASS Source And Assembly

SDC Silent Data Corruption

SECDED Single Error Correction Double Error Detection

SM Streaming Multiprocessor

TMR Triple Modular Redundancy

TRE Tolerated Relative Error

YOLO You Only Look Once

#### LIST OF FIGURES

| Figure 2.1 | Abstract view of fault injection and propagation                          | 21               |

|------------|---------------------------------------------------------------------------|------------------|

| Figure 2.2 | The images per second and performance per Watt achieved for NVIDIA        |                  |

| Tegra      | X1 and Intel i7.                                                          | 24               |

| Figure 2.3 | An example of a CNN's architecture                                        | 26               |

|            |                                                                           |                  |

|            | Instruction type per code for Kepler and Volta                            |                  |

| Figure 3.2 | Beam experiment setup at ChipIR                                           | 37               |

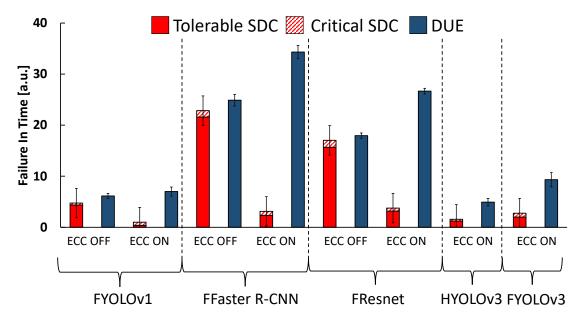

| Figure 4.1 | Normalized FIT rates for CNNs on Kepler and Volta architectures           | 42               |

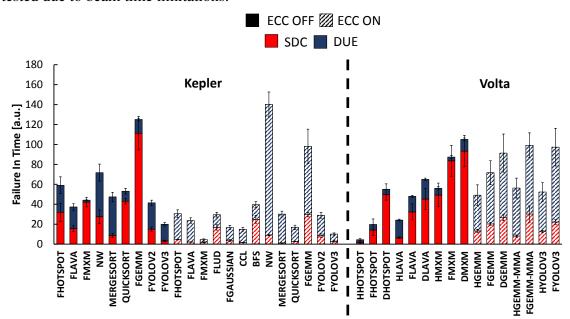

|            | Normalized FIT rates for Kepler and Volta.                                |                  |

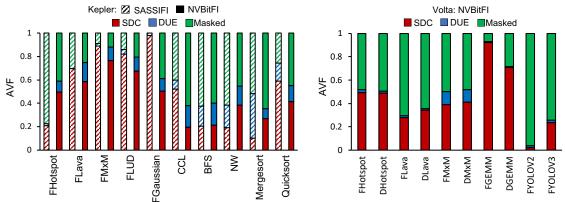

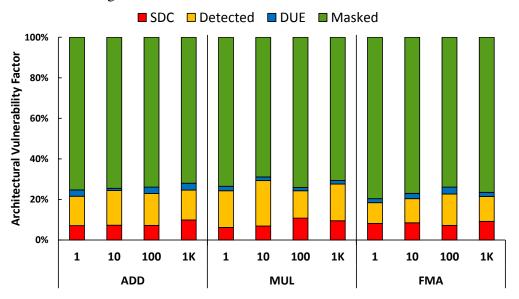

| Figure 4.3 | Architectural Vulnerability Factor for Kepler and Volta.                  | 47               |

| Figure 5.1 | SDCs spatial distribution in GEMM                                         | 53               |

| _          | YOLOv1 fault tolerance efficacy.                                          |                  |

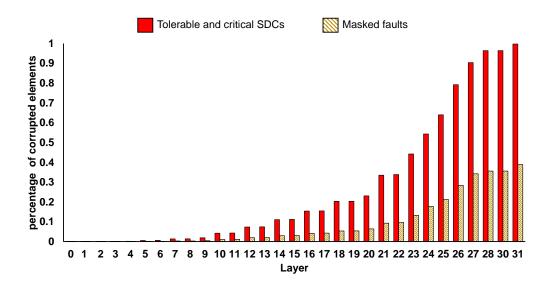

| _          | Average percentage of corrupted elements at the output of each layer      |                  |

|            | AVF results for the micro-benchmarks                                      |                  |

|            | Normalized beam data for DWC methods                                      |                  |

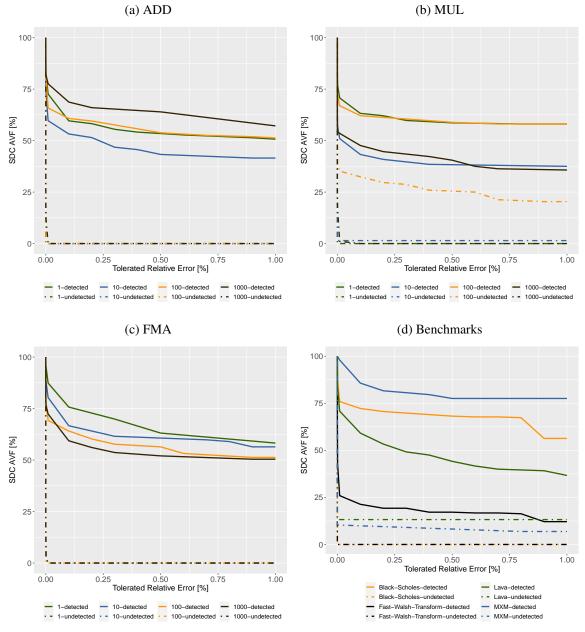

| -          | TRE for RP-DWC errors.                                                    |                  |

| E 6 1      | Micro handrandra avangimental EIT notas                                   | 76               |

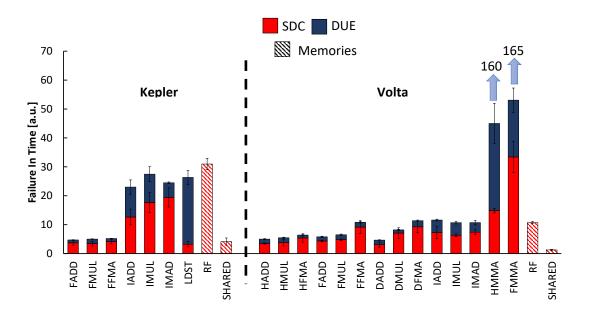

|            | Micro-benchmarks experimental FIT rates                                   | / 0              |

| _          | ted with fault injection.                                                 | 90               |

|            | Comparison between the DUE FIT rate measured with the beam and            | 80               |

|            | ted with fault injection.                                                 | 82               |

|            | Detailed DUE sources for Kepler and Volta GPUs.                           |                  |

|            | Code size and execution time relative to default NVCC compilation for     | 04               |

|            | ns 10.2 and 11.3                                                          | 88               |

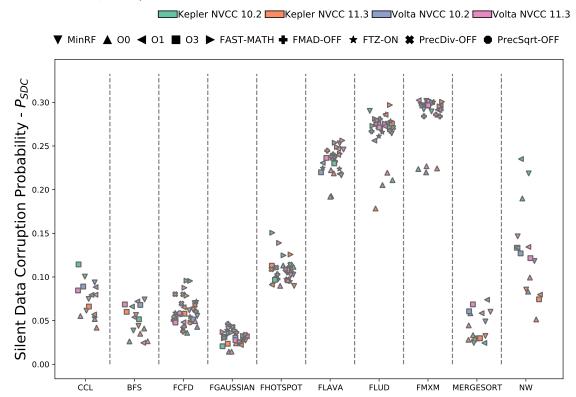

|            | Silent Data Corruption Probability ( $P_{(SDC)}$ ) distribution           |                  |

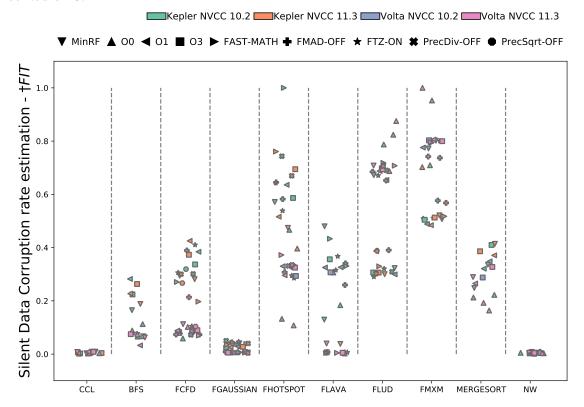

|            | SDC rate estimation († $FIT$ ) distribution.                              |                  |

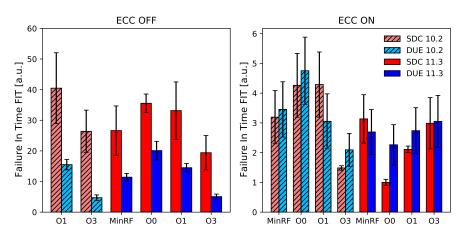

|            | Error rate for FMXM compiled with different configurations.               |                  |

| riguic 0.6 | Error rate for r wixiw complica with different configurations.            | J <del>. T</del> |

| Figure 7.1 | Scheme of the proposed two-level fault simulation framework               | 97               |

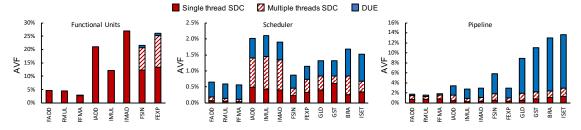

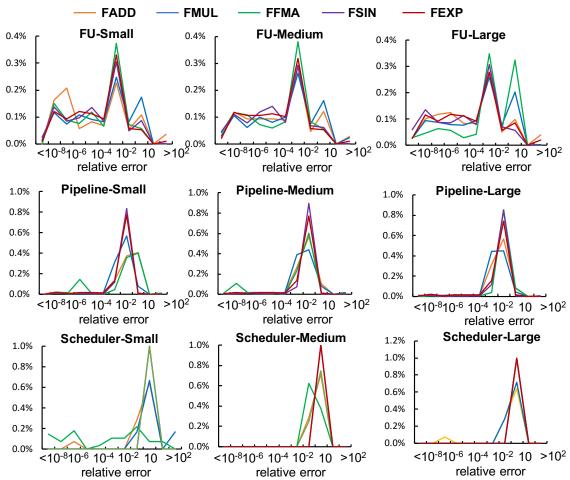

| Figure 7.2 | AVF of the injections at RTL level on the functional units                | .101             |

| Figure 7.3 | Distribution of the fault syndrome from the RTL fault injection for float |                  |

| instruc    | ctions                                                                    | .103             |

| Figure 7.4 | Distribution of the fault syndrome from the RTL fault injection for in-   |                  |

| teger i    | nstructions                                                               | .104             |

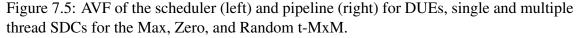

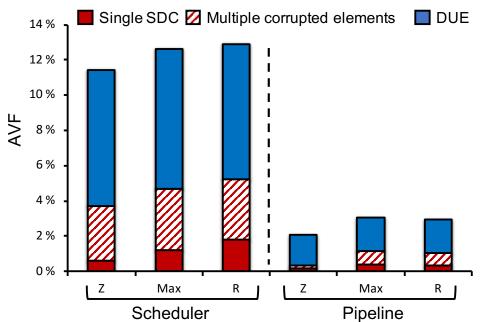

| Figure 7.5 | AVF of the scheduler (left) and pipeline (right) for DUEs, single and     |                  |

|            | ole thread SDCs for the Max, Zero, and Random t-MxM                       |                  |

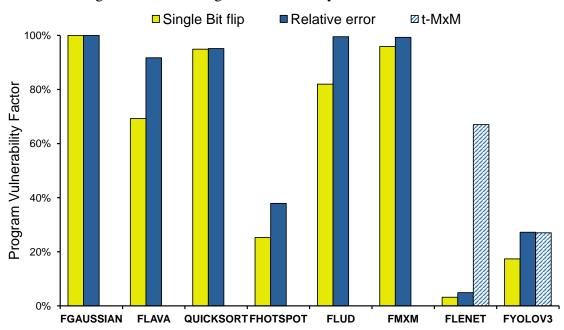

| Figure 7.6 | SDC Program Vulnerability Factor for HPC codes                            | .108             |

#### LIST OF TABLES

| Table 3.1 Codes used for reliability evaluation on Kepler.                                                                    | 33  |

|-------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 3.2 Codes used for reliability evaluation on Volta                                                                      | 33  |

| Table 3.3 Summarized micro-benchmarks details.                                                                                | 36  |

| Table 3.4 Evaluated modules, sizes and instructions used per module                                                           | 40  |

| Table 5.1 Error detection and overhead (Fault Injection).                                                                     | 64  |

| Table 6.1 NVCC Ratio between NVCC 10.2 and 11.3. When the ratio is higher than 1, NVCC 10.2 FIT rate is higher than NVCC 11.3 | 94  |

| Table 6.2 Ratio between the estimated SDC FIT rate and the SDC FIT rate obtained from beam experiments.                       |     |

| Table 7.1 Distribution of the multiple patterns (single corrupted elements are not listed) observed with t-MxM.               | 107 |

### CONTENTS

| 1 INTRODUCTION                                                            | 13 |

|---------------------------------------------------------------------------|----|

| 1.1 Motivation                                                            | 15 |

| 1.2 Goals and organization                                                |    |

| 2 BACKGROUND AND RELATED WORK                                             | 18 |

| 2.1 Radiation Effects on Computing Devices                                | 18 |

| 2.2 Reliability evaluation                                                | 19 |

| 2.3 Fault tolerance in artificial neural networks                         | 22 |

| 2.3.1 The performance of CNNs on GPUs                                     | 23 |

| 2.4 Mixed precision and error criticality                                 | 26 |

| 2.4.1 SDC criticality                                                     |    |

| 3 METRICS AND EVALUATION METHODOLOGY                                      | 29 |

| 3.1 Devices                                                               | 29 |

| 3.2 Tested Codes                                                          |    |

| 3.3 Synthetic Micro Benchmarks implementation                             | 34 |

| 3.4 Beam Experiment Setup                                                 |    |

| 3.5 Fault Simulation Frameworks                                           |    |

| 3.5.1 Software level fault injection                                      |    |

| 3.5.2 RTL level fault injection                                           |    |

| 4 GPU RELIABILITY EVALUATION                                              |    |

| 4.1 Evaluating CNNs reliability                                           |    |

| 4.2 GPU FIT rate                                                          |    |

| 4.3 Architectural Vulnerability Factor                                    |    |

| 4.4 Discussion on GPU reliability                                         |    |

| 5 HARDENING TECHNIQUES                                                    |    |

| 5.1 Available hardening techniques for GPUs                               |    |

| 5.2 Fault Tolerance for CNNs                                              |    |

| 5.2.1 GEMM ABFT                                                           |    |

| 5.2.2 Reliable Max-pooling                                                |    |

| 5.3 Reduced Precision Duplication With Comparison                         |    |

| 5.3.1 Overview of the Implementation                                      |    |

| 5.3.2 Granularity of the Approach                                         |    |

| 5.3.3 Architectural Vulneratibility Factor                                |    |

| 5.3.4 Error Detection                                                     |    |

| 5.3.5 Overhead                                                            |    |

| 5.3.6 Neutron Beam Experiments                                            |    |

| 5.3.7 Detected vs Undetected Errors                                       |    |

| 5.3.8 Impact of Undetected Errors in HPC and Safety-Critical Applications |    |

| 6 FAILURE IN TIME ESTIMATION                                              |    |

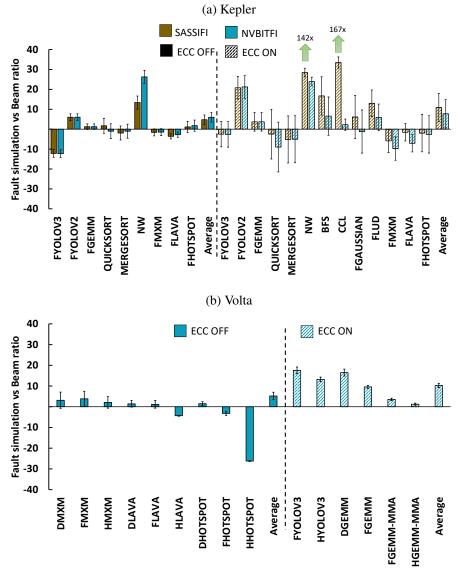

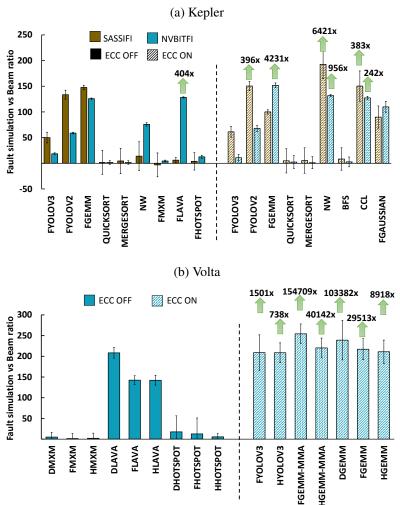

| 6.1 FIT rate prediction through fault simulation                          |    |

| 6.2 Profiling kernel dynamic instructions                                 |    |

| 6.3 Synthetic Micro benchmarks                                            |    |

| 6.3.1 Micro-benchmarks profile and error rate                             |    |

| 6.4 Beam vs Fault injection                                               |    |

| 6.4.1 SDC                                                                 |    |

| 6.4.2 DUE                                                                 |    |

| 6.4.2.1 DUE source                                                        | 83 |

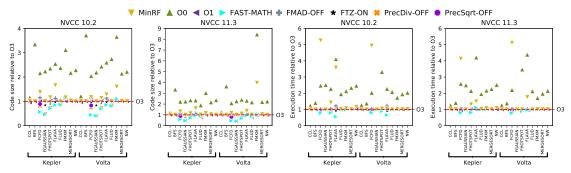

| 6.5 Case Study: Measuring the Compiler Impact on Reliability with SDC rate | 0.1 |

|----------------------------------------------------------------------------|-----|

| estimation                                                                 |     |

| 6.5.1 Optimization flags and compilers                                     | .86 |

| 6.5.2 Preliminary analysis: Dynamic instructions profiling                 | .87 |

| 6.5.3 SDC probability                                                      | .89 |

| 6.5.4 SDC rate estimation                                                  |     |

| 6.5.5 Validation through beam experiments                                  |     |

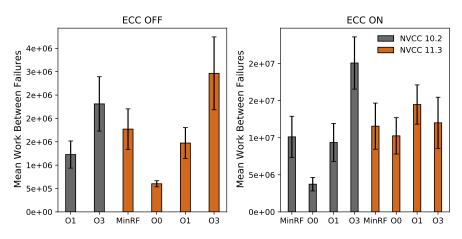

| 6.5.6 Mean Workload Between Failures                                       | .95 |

| 6.6 Considerations on FIT estimation                                       | .96 |

| 7 IMPROVED FAULT SIMULATION ERROR MODEL                                    | .97 |

| 7.1 Overview of the Idea                                                   | .97 |

| 7.1.1 Contributions and Limitations                                        |     |

| 7.2 RTL fault injection results                                            | 100 |

| 7.2.1 Fault Syndrome                                                       | 102 |

| 7.2.2 Tiled MxM errors distribution                                        |     |

| 7.3 HPC Applications Evaluation                                            | 108 |

| 8 CONCLUSIONS                                                              |     |

| 8.1 Summary of contributions                                               |     |

| 8.2 Future work                                                            |     |

| 8.3 Conclusions                                                            |     |

| REFERENCES                                                                 |     |

| APPENDIX A — RESUMO EXPANDIDO                                              |     |

| APPENDIX B — PUBLICATIONS                                                  |     |

#### 1 INTRODUCTION

Graphics Processing Units (GPUs) have evolved from supporting hardware for user applications and graphics rendering to general-purpose accelerators extensively employed in High Performance Computing (HPC) and safety-critical applications such as autonomous vehicles and aerospace markets. The highly parallel architecture of GPUs, in fact, perfectly fits the computational characteristic of most HPC codes and is incredibly efficient in executing matrix multiplication, which is the computing core of Convolutional Neural Networks (CNNs) used to detect objects in autonomous vehicles. The most recent GPU architecture advances, such as tensor core and mixed-precision functional units, move toward improving the architecture performances and software flexibility for HPC and deep learning applications.

Consequently, GPU vendors have been working on many architecture modifications to improve the GPUs reliability while maintaining high performances (HARI; ADVE; NAEIMI, 2012; RECH et al., 2014; WADDEN et al., 2014a; HARI et al., 2021). The researchers have proposed hardening at different levels of the GPU hardware/software, such as in the memory cell (RECH et al., 2014), Error Correction Code (ECC) (HARI; ADVE; NAEIMI, 2012), Redundant Multithreading execution (WADDEN et al., 2014a), and Algorithm Based Fault Tolerance for deep learning applications (HARI et al., 2021). Additionally, GPU vendors are working on the design of platforms compliant with strict automotive reliability standards as the ISO26262 (ISO, 2011; NVIDIA, 2018). As shown in Section 5.2, this thesis demonstrates that it is possible to detect 98% of the SDCs with a software-level hardening technique for CNNs executing on a GPU.

The research community has been carefully studying GPU reliability with both fault-injection (Wei et al., 2014; Hari et al., 2017; TSELONIS; GIZOPOULOS, 2016; TSAI et al., 2021), and beam experiments (Goncalves de Oliveira et al., 2016; SULLI-VAN et al., 2021). Beam experiments provide a very realistic analysis but lack visibility. As errors are observed only when they manifest at the program/chip output, it is impossible to associate observed behaviors with their source of the fault (without specialized hardware for observability) and identify the most vulnerable GPUs' resources. In opposition, fault simulation provides complete visibility of the fault propagation and allows a detailed analysis of the propagation through the micro-architecture (i.e., the Architecture Vulnerability Factor (AVF)). This methodology enables identifying the resources or code portions that, once corrupted, are more likely to affect the computation. However, faults

usually can be injected only on a subset of the available resources, and the adopted fault-model risks to be unrealistic if not tuned with experiments.

The comparison between beam experiments and fault simulation is an essential missing piece in the GPU reliability evaluation puzzle that this research intends to find. Unfortunately, it is still mostly unclear whether a reliability evaluation based only on fault simulation is realistic. Evaluating the effectiveness of many error mitigation techniques requires fault-injection experiments. However, data based on fault simulations alone does not imply that the method will be useful in the field. This thesis investigates and compares the programs' Failure In Time (FIT) rates measured with beam experiments that count for more than  $13 * 10^6$  years of natural exposure with the failure rates estimated from 400,000 fault injections using SASSIFI (Hari et al., 2017) and NVBitFI (TSAI et al., 2021), evaluating at which level and under which assumptions fault simulation can provide a realistic reliability evaluation for GPUs. Through beam experiments, this research presents the FIT rates of the main functional units (including mixed-precision and tensor core), register file, and shared memory of Kepler and Volta GPUs. The FIT rates of 15 representative codes for HPC and safety-critical applications, including three CNNs, are also presented. Some codes have been executed using different data types (integer, float-, single-, or half-precision) to understand the impact of mixed-precision on code's reliability.

Based on the data obtained from the beam experiments, profiling, and fault injection, this thesis proposes a multi-level fault simulation methodology to improve the GPU error model. The new fault injection method consists of performing fault injection at Register-Transfer Level (RTL) main structures and propagating the fault *syndrome* at the software level. The proposed method can join the accuracy of the RTL simulations with the performance of software fault injection. Then, for the first time, it is possible not only to unveil the effects of faults on otherwise hidden GPU resources but also to propose **a more detailed fault model** to be used in the reliability evaluation of complex codes. This information is essential, as it helps researchers focus on designing a hardening solution to a subset of critical resources.

The NVIDIA mixed-precision architectures are extremely interesting for the HPC and safety-critical markets. On GPUs, good object detection accuracy can be achieved through neural network representing data in half-precision float point (16 bits) or even in short integer (8 bits) (COURBARIAUX; BENGIO; DAVID, 2014; GUPTA et al., 2015). Several HPC applications could also be executed in reduced-precision, significantly im-

proving the computing efficiency (BREUER, 2005; PUENTE et al., 2014). As reliability is a primary concern for both safety-critical and HPC applications, it is mandatory to understand if and how mixed-precision influences the reliability of devices and codes. To take advantage of mixed-precision GPU hardware, this work moves a step forward in the performance efficiency of Duplication With Comparison (DWC) by presenting **Reduced Precision Duplication With Comparison (RP-DWC)**, an improvement over the traditional DWC approach, which consists of executing the replica in a lower precision. The results show that RP-DWC achieves an excellent coverage (up to 86%) with minimal overheads. The time overhead can be as low as 0.1%, while the energy consumption overhead can be as low as 24%.

In this thesis, two generations of NVIDIA GPUs are evaluated, Kepler and Volta. The two GPUs architectures have almost 10 years of release difference, which is as an interesting case study to understand where the architectural improvements can benefit the GPU reliability. Additionally, for both architectures and most codes, experiments are presented with Error Correction Code (ECC) enabled and disabled to evaluate the efficacy of GPUs built-in reliability solutions and distinguish between the contribution of logic and memory faults to the codes error rate.

#### 1.1 Motivation

This thesis is about understanding and improving the GPU reliability by combining the knowledge extracted from beam experiments, fault simulation, and profiling. Currently, the difference between the data from the fault simulators and the error rates from radiation experiments is one of the most significant issues for GPU reliability analysis. This is the primary motivation of this research. In order to better characterize the investigation developed in this work, the following topics are also covered in this thesis:

The reliability of machine learning on GPUs: CNNs algorithms can exploit GPU's ability to support data and thread-level parallelism. However, researchers have been overly focused on the performance while neglecting other critical aspects, particularly reliability. While performance is vital in these applications, reliability needs to be paramount. It is not possible to tradeoff performance for reliability in safety-critical applications.

The reliability of mixed-precision GPUs: While it has been shown that mixed-precision operations are very beneficial in terms of computing and power efficiency, their

impact on the devices and applications reliability has not been thoroughly investigated yet.

#### 1.2 Goals and organization

By performing multiple levels of fault injection, beam experiments, RTL, and software fault simulation, this work proposes a systematic and quantitative analysis of the error rate on NVIDIA GPUs. The main contributions of this work are:

- Combining beam experiments and fault simulation to deeply understand GPUs' reliability. This research also presents a comparison between the GPU's FIT rate measured with beam experiments with the FIT rate predicted using fault simulation and kernel profiling. This study provides essential information to ensure that fault simulation provides a realistic reliability evaluation.

- This work advances GPU reliability by characterizing how microarchitecture vulnerabilities in a GPU can undermine a CNN's reliability. Most previous works focused on HPC application reliability on a GPU.

- A new approach of hardening is proposed for mixed-precision architectures. This thesis goes a step forward in the performance efficiency of DWC by presenting Reduced-Precision DWC (RP-DWC), an improvement over the traditional DWC approach, which consists of executing the replica in a lower precision.

- For the first time for GPUs, a fine grain *RTL fault injection* (using FlexGripPlus) is combined with the flexibility and efficiency of *software fault injection in real GPUs*. With the RTL analysis, this research gathers the syndrome induced by faults in the micro-instruction output value, and produces an accurate fault model for the most common machine operations. As all GPU modules are accessible in the RTL model, presenting a reliability characterization that considers most GPU resources is possible.

The remainder of the document is organized as follows. Chapter 2 gives a background on the reliability of electronic devices and a short introduction of GPU's uses on machine learning and its impact on reliability. Chapter 3 presents some error rate concepts, the radiation tests setup, the fault simulators tools, and other artifacts used in this work, such as devices and codes. Chapter 4 presents the reliability evaluation using beam experiments and software fault simulation. New software fault tolerance techniques are

presented in Chapter 5. A methodology to estimate the FIT rate based on profiling and beam experiments is presented in Chapter 6. Chapter 7 presents the new fault injection methodology. Chapter 8 summarizes the main achievements and concludes this research.

#### 2 BACKGROUND AND RELATED WORK

This chapter presents the background and the related work in radiation effects in computing devices, Graphics Processing Unit (GPU) reliability, Convolutional Neural Networks (CNNs), error rate estimation, and mixed-precision architectures necessary for this research.

#### 2.1 Radiation Effects on Computing Devices

Galactic cosmic rays, interacting with the terrestrial atmosphere, trigger a flux of high-energy particles, mainly neutrons, that reach the ground. The natural flux of high-energy neutrons at sea level has been estimated to be about  $13 \ neutrons/((cm^2) \times h)$  (JEDEC, 2006). A terrestrial neutron strike may perturb a transistor's state, generating bit-flips in memory or current spikes in logic circuits that, if latched, lead to an error (BUCHNER et al., 1997; MAHATME et al., 2011).

Neutron-induced events are typically *soft* errors in the sense that the device is not permanently damaged. A new write operation will correctly store the value on the struck memory cell, and a new operation using the struck logic gate will provide the correct result. Soft errors are the worst kind of errors since they are harder to detect and are transient. Given the shrinking dimensions of transistors, the pursuit of lower power consumption, and the integration of several resources in a single chip, the probability of neutron-induced faults, in both memory and logic resources, has increased significantly (BAUMANN, 2005; SRIDHARAN et al., 2015). On a GPU, a soft error leads to three different main outcomes:

- 1. **No effect** on the program output, i.e., the fault is masked, the corrupted data is not used, or the circuit functionality is not affected;

- 2. A **Silent Data Corruption (SDC)** is an incorrect program output. The application finishes correctly, but its output does not contain correct data;

- 3. **Multiple Data Corruption** is an SDC caused by multiple errors in a GPU. For instance, an error in the Streaming Multiprocessor (SM) scheduler can corrupt the output of multiple threads;

- 4. A **Detected Unrecoverable Error (DUE)** is a detected but uncorrectable event, a crash, or device reboot that make the system abort abruptly.

Given a particle flux, the error rate of code being executed on a microprocessor depends on both the memory/logic sensitivity (BAUMANN, 2005; NOH et al., 2015), the number of resources adopted for computation, and on the probabilities for the fault to be propagated through the hardware design (the microarchitecture) and the program (MUKHERJEE et al., 2003; SRIDHARAN; KAELI, 2010).

Modern parallel computing architectures such as GPUs have some inherent reliability weaknesses (WUNDERLICH; BRAUN; HALDER, 2013; GOMEZ et al., 2014; Goncalves de Oliveira et al., 2016). A single particle-induced fault in the scheduler or shared memory is likely to affect the correctness of several parallel threads or kernels, leading to the corruption of multiple output values (RECH et al., 2013). Additionally, a single corrupted thread could feed thousands of future parallel threads with erroneous data, again leading to multiple errors (LI et al., 2016). Previous studies have already evaluated the reliability of FPGA, GPUs, and Xeon Phi running various codes through radiation experiments (BAUMANN, 2005; QUINN et al., 2005; OLIVEIRA et al., 2017c) or fault simulation (FANG et al., 2014; KALIORAKIS et al., 2015; LU et al., 2015; Hari et al., 2017; OLIVEIRA et al., 2017a; TSAI et al., 2021). By the time this work was done, this is the first research that combines beam experiments and fault simulation and compares the GPU's FIT rate measured with beam experiments with the FIT rate predicted using fault simulation and kernel profiling. This study provides essential information to ensure that fault simulation provides a realistic reliability evaluation.

#### 2.2 Reliability evaluation

The error rate of computing devices, including GPUs, running specific applications has already been measured through-beam experiments in previous work (BAU-MANN, 2005; ZIEGLER; PUCHNER, 2010; SEIFERT; ZHU; MASSENGILL, 2002; NGUYEN et al., 2005; CONSTANTINESCU, 2002; OLIVEIRA et al., 2017b; SULLI-VAN et al., 2021). By exposing the device running a code to an accelerated particle beam, it is possible to induce transient faults in the hardware and, counting the manifestations of errors at the output, measure the realistic error rate. While providing the realistic error rate, beam experiments jointly consider all the factors that influence the device error rate, impeding the distinction of each factor's contribution and making it challenging to identify the most vulnerable parts of the system. Additionally, beam experiments are performed on a silicon prototype or the final Commercial Of The Shelf (COTS) prod-

uct, making any modification to the project, including improving the device reliability, extremely expensive.

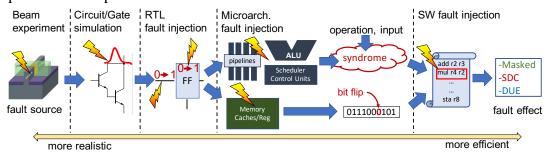

Fault simulation, contrarily, is used to understand the probability for a fault to propagate, generating an error. Figure 2.1 illustrates a view of the available fault injection methodologies across different levels of abstractions. Each evaluation methodology has some benefits and limitations, which are summarized next:

- Circuit or Gate Level Simulations induce analog current spikes or digital faults in the lowest abstraction level that still allows to track fault propagation (not available with beam tests). There are two main issues with the level of details required to perform this analysis on GPUs: (1) a circuit, or gate-level description of GPUs is not publicly available and, even if it was, (2) the time required to evaluate the whole circuit would definitely be excessive (the characterization of a small circuit takes weeks (Kochte et al., 2010)).

- Register-Transfer Level (RTL) fault injection accesses all resources (flip flops and signals) and provides a more realistic fault model, given the proximity of the RTL description with the actual implementation of the final hardware (Ejlali et al., 2003; SUBASI et al., 2018; CONDIA et al., 2020). However, the time required to inject a statistically significant number of faults makes RTL injections impractical. The massive amount of modules and units in a GPU and the complexity of modern HPC and safety-critical applications exacerbate the time needed to have an exhaustive RTL fault injection (hundreds of hours for small codes), making it unfeasible.

- Micro-architecture fault injection provides a higher fault coverage than software fault injection as faults can, in principle, be injected in most modules. A preliminary work, based on Multi2Sim (Ubal et al., 2012) GPU description, presented micro-architectural fault injection data. However, most micro-architectural analysis is limited to just memories (KALIORAKIS et al., 2015; TSELONIS; GIZOPOULOS, 2016; Vallero; Gizopoulos; Di Carlo, 2017; YANG et al., 2021b). One of the issues of micro-architectural fault injection in GPUs is that the description of some modules (including the scheduler and pipelines) is behavioral. Thus, their implementation is not necessarily similar to the realistic one.

- **Software fault injection** is performed at the highest level of abstraction and, on GPUs, it was proved efficient and helpful in identifying those instructions or code portions that, once corrupted, are more likely to affect computation (Wei et al.,

- 2014; FANG et al., 2014; Hari et al., 2017; YANG et al., 2021a; TSAI et al., 2021). However, the analysis is limited as faults can be injected only on that subset of visible resources to the programmer. Unfortunately, critical resources for highly parallel devices (i.e., hardware scheduler, threads control units, etc.) are not accessible to the programmer and cannot be characterized via high-level fault injection.

- Hybrid or combined fault injections at different levels of abstraction have been adopted to increase the efficiency of the reliability evaluation without jeopardizing its accuracy. Some studies have proposed to use a detailed RTL fault injection in specific portions of the circuit and a fast fault simulation in others (Ejlali et al., 2003; SARTOR; BECKER; BECK, 2019). Recent works combined an extremely detailed gate-level fault injection in tandem with a faster (but still impracticable for complex devices) RTL evaluation (Kochte et al., 2010; NIMARA et al., 2016). Cho et al. used high-level simulation (not using real hardware), triggering a RTL model when the fault needs to be injected (Cho et al., 2015). Subasi et al. focus on RTL injection to provide a more detailed fault model but limited to embedded processors ALU (SUBASI et al., 2018). While this work takes inspiration from the two-level fault injection concept, none of these works address GPUs (nor parallel devices in general), but mainly embedded processors, with a completely different complexity scenario. Additionally, none of the previous works provide, as this work does, a fault model database that could be used in future evaluations (SANTOS et al., 2021).

Figure 2.1: Abstract view of fault injection and propagation. Reliability evaluations closer to the fault source (i.e., the silicon implementation) are more realistic by extremely costly. Evaluations closer to the fault manifestation at the output are more efficient but risk to be unrealistic. Single or double bit-flips injections at software level, for instance, accurately simulate memory faults, only. Faults in other resources have a syndrome that depends on operation and input value.

In an effort to improve the analysis made using fault simulation, the concept of SDC probability is proposed by some works (YIM et al., 2011; FENG et al., 2010; LI;

PATTABIRAMAN, 2018; PALAZZI et al., 2019; ANWER et al., 2020). The SDC probability is the AVF normalized by the instruction probability to be sampled from the code's instructions. The SDC probability is a metric that connects the AVF (fault propagation) and the *instruction profiling* of the application to determine the dependence of the AVF on the instruction distribution. However, the SDC probability still lacks information on the hardware sensitivity, which still presents as a model limitation.

Recent studies (Chatzidimitriou et al., 2019; Serrano-Cases et al., 2020) tried to predict application SDC rate using micro-architectural fault injection on ARM CPUs. For GPUs, only one study (HARI et al., 2020) attempted to predict the error rate at low- and application-level. The low-level implementation considered beam experiments, and application-level analysis employed fault injection. The results show that the SDC prediction is plausible. However, the paper did not provide insights into the impact of hidden GPU resources (parallelism management) on the SDC rate or identifying the code/architecture characteristics/metrics that significantly impact GPUs. It focussed on only one GPU architecture with a single ECC setting and did not study sensitivity to compiler versions. This work is the first to demonstrate that analyzing multiple GPU architectures and compiler versions are crucial for application failure rate analysis, and investigating with both the ECC models reveals new insights.

#### 2.3 Fault tolerance in artificial neural networks

Prior works, from the late 1990's, have shown that ANNs are highly tolerant to transient faults (ALIPPI; PIURI; SAMI, 1995; BETTOLA; PIURI, 1998; PIURI, 2001; DISTANTE; PIURI, 1991; PHATAK; KOREN, 1995; DISTANTE et al., 1991; NETI; SCHNEIDER; YOUNG, 1992). Software fault injection was performed at different levels of abstraction to understand the vulnerability of various networks. Unfortunately, GPUs tend to propagate a single fault to multiple output elements, a behavior not studied in previous research. Additionally, as the structure and topology of neural networks have significantly evolved in recent years, most prior results cannot be easily extended to today's deep learning complex frameworks. Specifically, neural networks for object detection have the peculiarity of using convolution to extract features from the data (LE-CUN et al., 1998), a class of computations where reliability has not been deeply studied to date. A study on CNN reliability, executed on dedicated accelerators, is presented by Li et al. (LI et al., 2017), showing that each layer and flip-flop has a different injec-

tion sensitivity. The authors also identify which flip-flops to harden to increase the CNN reliability.

This work significantly advances the knowledge on CNNs reliability by considering realistic error models (provided by beam experiments) and understanding the propagation of errors injected in memory elements and computing resources. This thesis considers and compares three commercially available frameworks and three different GPU architectures. Finally, hardening strategies proposed in this work do not require costly hardware modifications and are experimentally proven to be very useful and efficient.

Given the results of previous studies, it is possible to expect that the fault-tolerance of neural networks will be dominated by subsequent filtering operations. This was suggested through the study of the mathematical algorithms present in general neural paradigms, and by evaluating specific implementations (DISTANTE; PIURI, 1991; DISTANTE et al., 1991; NETI; SCHNEIDER; YOUNG, 1992; ALIPPI; PIURI; SAMI, 1995; PIURI, 2001).

Prior work has also considered how to improve the reliability of neural networks. Most of the available solutions rely on partial or full duplication (or even triplication) of operations (PHATAK; KOREN, 1995). Some solutions require specific hardware modifications (BETTOLA; PIURI, 1998; LI et al., 2017). These approaches are less than ideal for real-time object detection, a task commonly performed in automotive applications, due to processing overhead and added costs.

Some studies have used fault injection during network training (SEQUIN; CLAY, 1990; BOLT, 1992; KULAKOV; ZWOLINSKI; REEVE, 2015). Once the neuron values are adjusted to support errors, the network can maintain the correct classification, even if a fault happens. The main limitation of this approach is that it is hard to inject a representative set of faults. The fault model set, unfortunately, is determined by the network dimension. For deep CNNs, injecting a statistically significant set of fault models is a considerable amount of work, infeasible for most frameworks.

#### 2.3.1 The performance of CNNs on GPUs

In 1989, a new algorithm in machine learning proposed by LeCun *et. Al* placed a breakthrough for image recognition in AI (LeCun et al., 1989). The authors proposed a machine learning method called CNN to detect handwritten digits, which achieved more than 98% of accuracy (LECUN et al., 1998). Since then, machine learning methods

have increased their accuracy and complexity. However, with deeper neural networks and the increasing number of classification method parameters, machine learning became costly in performance for that time processors. Only in 2009, the machine learning methods were implemented using GPUs (RAINA; MADHAVAN; NG, 2009) with a single NVIDIA GPU Raina *et. Al* achieved more than 72× speedup over a dual-core CPU. Ever since, the machine learning algorithms get lots of improvement on NVIDIA GPUs in terms of performance and power consumption (CHETLUR et al., 2014; KRIZHEVSKY, 2014). Nowadays, the standard COTS platform to train and execute machine learning algorithms is through NVIDIA GPUs (GAWANDE et al., 2018).

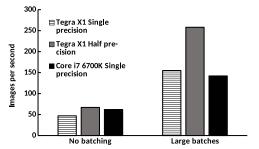

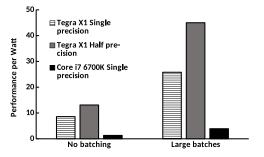

As an example of how NVIDIA overpower the rivals in the deep learning market, figure 2.2 shows a result adapted from (NVIDIA, 2015b). Two platforms are evaluated, an embedded NVIDIA GPU, Tegra X1, and a general-purpose CPU, Intel i7 6700K, running AlexNet Convolutional Neural Network object classification. For Tegra X1, the results are shown for two float precisions, single and half (i.e., FP32 and FP16), without losing classification accuracy. The batch sizes are plotted for *No batching* (batch size equals to 1) and *Large batches* (batch size equals to 128 for Tegra X1 and 48 for Intel i7). The batch size defines the number of samples seen before updating the neural network model in the training process. For images per second result, Intel i7 is only better than Tegra X1 using a batch size of 1, while for large batches, Tegra X1 outperforms Intel i7 for single and half precision. If the power consumption is taken into the analysis, Tegra X1 half precision exceeds Intel i7 up to 6.6× without batching and 11.5× with large batches. Today, NVIDIA GPUs are the most used commercial device for Deep Learning researchers. Consequently, this work evaluated the NVIDIA GPU reliability running three of the most accurate CNN when this work is done, YOLO, Faster R-CNN, and Resnet.

Figure 2.2: The images per second and performance per Watt achieved for NVIDIA Tegra X1 and Intel i7 6700K. Adapted from (NVIDIA, 2015b)

(a) Images per second processed in the inference (b) The ratio between performance and power process.

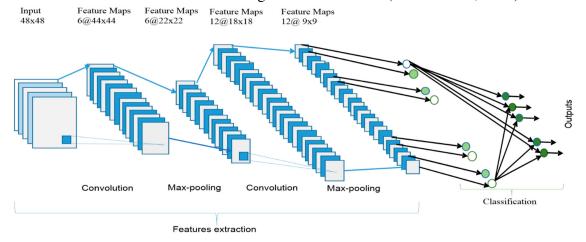

Convolutional Neural Networks (CNNs) are one of the most efficient ways to perform image classification (CIREGAN; MEIER; SCHMIDHUBER, 2012), segmentation (CIRESAN et al., 2012), and object detection (REDMON et al., 2015; Mao et al., 2018; REN et al., 2015; GKIOXARI; MALIK; JOHNSON, 2019). Prior work has adopted CNNs for real-time object detection, showing excellent results (ANGELOVA et al., 2015; RIBEIRO et al., 2016; REDMON; FARHADI, 2018). Figure 2.3 shows an example of how CNNs works, most of them are composed of two stages: Feature extraction and classification (ALOM et al., 2019).

One of the basic steps when using CNNs for object detection is convolution. A kernel filter is convolved with a matrix to extract specific features of the image. The kernel filter slides over the input matrix, multiplying and accumulating products at every position of the input with every position of the kernel. This process can be mapped to a matrix multiplication operation. Each block is reorganized as a row of matrix A, and the filter kernel is replicated as columns of a matrix B. Convolution is then computed as AxB. Other methods consider convolutional algorithms or Fast Fourier Transforms. However, they are less efficient than GEMM-based convolutions (CHETLUR et al., 2014; MATH-IEU; HENAFF; LECUN, 2013). As GPUs are highly efficient for accelerating matrix multiplication, they are an excellent target for CNNs. Specific processors can be designed for CNN, achieving significant performance and low power consumption (LUO et al., 2017; JOUPPI et al., 2017). However, the design of dedicated processors is exceptionally costly and less than ideal for embedded applications.

A CNN has several layers that perform convolution on a raw image or feature map (i.e., the output of an upstream convolutional layer). This work considers three modern frameworks: i.) You Only Look Once (YOLO) versions, one, two and three (REDMON et al., 2015; REDMON; FARHADI, 2016; REDMON; FARHADI, 2018), ii.) a 2) a Faster Region-based Convolution Neural Network (Faster R-CNN) (REN et al., 2015), and iii.) a Residual Network (Resnet) (HE et al., 2016). **YOLO** is based on *Darknet*, which is an open-source CNN used for object classification and detection written in C and Compute Unified Device Architecture (CUDA) (REDMON et al., 2015). **Faster R-CNN** is written in C++ and Python, based on Caffe's (JIA et al., 2014) deep learning framework. **ResNet** is a CNN for classification based on the Torch7 deep learning framework (COLLOBERT; KAVUKCUOGLU; FARABET, 2011). ResNet only performs object classification, while YOLO and Faster R-CNN also provide detection (i.e., bounding boxes that highlight the classified objects in the frame). However, the networks pipeline and operation performed

are similar once all the CNNs share the same structure. There are other differences between YOLO, Faster R-CNN, and ResNet that are likely to impact their reliability as demonstrated in (Santos et al., 2019).

The GPU microarchitecture can propagate a single fault to affect several output elements, and this behavior significantly impacts CNN reliability. This work demonstrates in Chapter 4.1 that, unfortunately, ECC is insufficient to ensure high reliability in CNNs, as it does not reduce the number of critical errors. Chapter 5 presents more efficient hardening techniques that can improve the fault-tolerance on CNNs.

Figure 2.3: An example of a CNN's architecture, most of CNNs are split into two stages feature extraction and classification. Figure extracted from (ALOM et al., 2019).

#### 2.4 Mixed precision and error criticality

In recent years major hardware vendors are making available devices that enable the execution of operations in mixed-precision. The market needs for more efficient architectures and applications in terms of execution time and power consumption pushed the adoption of approximate computing in a growing number of applications. Consequently, the demand for mixed-precision platforms increased since they are extremely interesting for the HPC and safety-critical markets.

Some applications do not require the full precision provided by IEEE754's double or single precisions (STRZODKA; GODDEKE, 2006). As the float point functional units area grows quadratically as the precision increase, using double and single-precision data even if lower precision is sufficient would add unnecessary overhead to the application (GODDEKE; STRZODKA; TUREK, 2007). Previous studies have shown significant performance improvement using mixed precision on HPC (GODDEKE; STR-

ZODKA; TUREK, 2007; CLARK et al., 2010), Deep Learning (COURBARIAUX; BENGIO; DAVID, 2014; VENKATESH; NURVITADHI; MARR, 2017), physics simulation (GRAND; GöTZ; WALKER, 2013), and approximate computing (HO et al., 2017; MICIKEVICIUS et al., 2017).

Mixed-precision architectures can be used in low power devices (TONG; NA-GLE; RUTENBAR, 2000), FPGAs (MINHAS; BAYLISS; CONSTANTINIDES, 2014), GPUs (NVIDIA, 2017; MINHAS; BAYLISS; CONSTANTINIDES, 2014), general purpose CPUs (LOMONT, 2011), etc. The architecture is said to be mixed precision if it has support for at least two of the five float point arithmetics defined by the IEEE 754 (16, 32, 64, 128, and 256 bits) (IEEE, 2008). Modern devices such as NVIDIA GPUs, Intel accelerators, and FPGAs, have support for half, single, and double precisions (MINHAS; BAYLISS; CONSTANTINIDES, 2014; NVIDIA, 2017; INTEL, 2016). Nevertheless, other architectures support different precisions, such as 8 bits operations (GUPTA et al., 2015).

Many fields can benefit from float point mixed-precision arithmetic, such as Neural Networks, image processing, HPC, etc (CLARK et al., 2010; HWANG; SUNG, 2014; COURBARIAUX; BENGIO; DAVID, 2014). Recently, efforts have been to improve the performance of mixed-precision applications on modern devices. Most recent research does not cover how mixed-precision arithmetics impact the device or application reliability. This work also covers different precision reliability on Volta architecture.

#### 2.4.1 SDC criticality

SDCs are not always critical, as some output errors can be tolerated. For instance, if the corruption affects only the least significant positions of the mantissa of a float point number, the results could still be inside float point operations' inherent variance. Some physical simulations accept as correct values in a range that can be as high as 4% for wave simulations (PUENTE et al., 2014; OLIVEIRA et al., 2017b). Additionally, approximate computing is gaining interest in various HPC applications (BREUER, 2005; NVIDIA, 2017). If the presence of SDCs does not impact the application output, SDCs could be considered tolerable. Moreover, the output of most neural-networks-based object detection frameworks is a vector of *tensors* containing the probability of eligible objects. Objects identified with a sufficiently high probability are classified and eventually detected. Transient faults that modify the probability without altering an object's rank or

change the coordinates of low-probability objects are not considered critical. Intuitively, the reduction of data and operation precision is likely to increase the criticality of transient errors, as demonstrated in a recent study (SANTOS et al., 2019).

#### 3 METRICS AND EVALUATION METHODOLOGY

This chapter describes the devices and codes characterized, the metrics adopted for the reliability evaluation, and how they are measured for GPUs.

#### 3.1 Devices

**Devices:** For this work, two NVIDIA GPU micro-architectures, Kepler (Tesla K40c) and Volta (Titan V and Tesla V100), are considered. NVIDIA Kepler micro-architecture, designed in 2013, was one of the most popular GPUs for HPC. Kepler introduces significant changes compared to previous micro-architectures, such as introducing dynamic kernel parallelism and launching concurrent kernels in the same GPU. The tested NVIDIA K40 (**Kepler**) is built with the *Kepler* ISA and fabricated in a 28nm TSMC standard CMOS technology. This model has 2880 CUDA cores divided in 15 Streaming Multiprocessors (SMs). Each K40 SM has 64K registers, 64KB of L1/shared memory, 1.5MB of L2 cache, and 6GB GDDR5 memory. Single Error Correction Double Error Detection (SECDED) Error Correcting Code (ECC) protects the register file, shared memory, and caches while read-only data cache is parity protected. K40 is used with both the ECC enabled and disabled to evaluate the register file error rate's impact on the prediction.

Titan V and Tesla V100 (**Volta**) are designed with the Volta micro-architecture and built with TSMC FinFET 12nm. Volta GPUs feature hardware acceleration for three IEEE754 float point precisions: double, float, and half. Each of the 80 Volta SMs has 64 FP32 cores, 64 INT32 cores, 32 FP64 cores (HO; WONG, 2017; NVIDIA, 2018). Volta also includes eight *tensor cores*, i.e., specific hardware that performs the Matrix Multiplication and Accumulate (MMA) operation on 4x4 matrices. While the V100 operates at 1246MHz as a base clock, Titan V operates at 1200MHz. Tesla V100 has 16GB of HBM2 RAM, and Titan V has 12GB of HBM2 RAM. Finally, only the V100 has SECDED ECC on the main memories.

It is worth noting this evaluation considers errors occurring in the GPU core, not in the main memory. That is, injecting faults in the main memory is not studied. For Kepler, the beam spot is sufficiently small (2cm of diameter) to not hit the onboard DDR when ECC is disabled. For Volta, as HBM2 memories are on top of the chip when ECC is disabled, all the global memory accesses are made through Triple Modular Redundancy

(TMR). The choice of not considering main memory reliability that has already been extensively studied (Saeng-Hwan Kim et al., 2007; Chen et al., 2016) is dictated by the fact that bitflips in it would mask effects in the GPU core.

#### 3.2 Tested Codes

Twelve representative codes listed in Table 3.1 (Kepler) and Table 3.2 (Volta) are chosen for this work. A set of codes that comes from broad domains, from HPC to deep learning. As a side contribution, this work measures which are the codes that are more vulnerable or reliable. Additionally, all the codes, data, and tools used in this work are available on GitHub to allow reproducibility. The radiation experiments setup tools and codes are available in (SANTOS et al., 2014). The data extracted on CNNs and discussed in Chapter 4.1 is available in (SANTOS et al., 2018). FIT prediction, discussed in Chapter 6, data is available in (SANTOS et al., 2021). Finally, the data for RTL/Software fault injections and the new error model discussed on Chapter 7 are available at (SANTOS et al., 2021).

A detailed description of the chosen benchmarks are as follows:

- 1. Connected Component Labeling (CCL) is a labeling algorithm that is commonly used for object detection. CCL scans the image in parallel in a row-wise fashion to find contiguous pixels using child threads through dynamic parallelism in the same row that belong to the same label. Then, CCL merges the components previously found and updates the respective labels using child threads through dynamic parallelism (UKIDAVE et al., 2015).

- 2. **Breadth-first search** (**BFS**) is a search in graphs algorithm that is widely used in GPS Navigation Systems. BFS kernel searches an undirected and unweighted graph to find the minimum edges reaching all vertexes of the graph. The chosen BFS algorithm uses each thread to represent each vertex of the graph them store the results of visited vertices in an array of indexes, and another array to keep the costs (HARISH; NARAYANAN, 2007). BFS is a well-known example of a not well-suitable algorithm for GPUs since each thread has a very irregular memory access pattern.

- 3. **Lava** simulates particle interactions in a large 3D space. It calculates the particle's potential and relocation in a large 3D space due to mutual forces between

- them (CHE et al., 2009). Lava kernel computation is mostly dot-products with float point data. Each thread performs one particle's interactions with all particles in neighboring boxes. Lava is representative of Multi-physics Particle Dynamics Code applications which solve a series of ordinary differential equations using Finite Difference Methods (SZAFARYN et al., 2010).

- 4. **Hotspot** estimates a processor temperature using an architectural floor plan and simulated power measurements (CHE et al., 2009). The computation is represented by a grid, where each output cell represents the average temperature value of the corresponding area of the chip. Hotspot is a 2D stencil highly parallelizable code that achieves a high occupancy level. Hotspot is representative of stencil solvers, used in applications from geophysics to molecular dynamics (PUENTE et al., 2014; BIYIKLI; YANG; TO, 2014) and intensely studied by the community (NGUYEN et al., 2010).

- 5. **Gaussian** elimination is a linear algebra algorithm that solves a system of equations and computes the result for all of the variables in a linear system, row-by-row (CHE et al., 2009).

- 6. LU Decomposition (LUD) is a linear algebra method that calculates solutions for a square system of linear equations. LUD kernel factors a matrix as the product of a lower triangular matrix and an upper triangular matrix. LUD is representative of highly CPU-bound codes (CHE et al., 2009). Additionally, this application has many row-wise/column-wise interdependencies, significant inter-thread sharing, and row/column dependencies.

- 7. Needleman–Wunsch (NW) is a bioinformatics algorithm that aligns DNA sequences. Possible pairs of sequences are organized in a 2D integer matrix, then NW deduces the optimal alignment by finding the maximum path in the matrix. NW uses smaller problems to solve the original problem (CHE et al., 2009), which leads the NW kernel to have many control flow instructions.

- 8. **Matrix Multiplication (MxM)** is an essential tool for HPC and is also one reason for GPUs' success in CNNs training and execution. For this reason, this study pays particular attention to this algorithm and test both the naive version (*MxM*) and the optimized version that digest data in the most suitable way for GPUs as General Matrix Multiplication (*GEMM*). The GEMM version considered is part of the NVIDIA CUBLAS libraries, which is to be highly efficient, has a dedicated kernel code for each group of size, precision, and device configuration.

- 9. **Mergesort** is a divide and conquer sorting algorithm of  $O(n \log n)$  complexity. CUDA toolkit Mergesort sorts divided arrays with Bitonic sorting algorithm. Then the final step organizes the data segments previously ordered. CUDA toolkit Mergesort creates an array of indexes for each input element. If an element on input data is changed, its index is moved along (NVIDIA, 2015a). Sorting algorithms have a high memory device utilization as also lots of control flow instructions.

- 10. Quicksort is one of the most known sorting algorithms. CUDA toolkit implementation chooses a random pivot between the two split segments, then each element in the segment vector is sorted relative to the pivot. CUDA toolkit Quicksort uses Cuda Dynamic Parallelism, which allows the main kernel to create child kernels reducing the host-GPU communications overhead (NVIDIA, 2015a).

- 11. **CFD Solver** is an unstructured grid solver for Computational Fluid Dynamics (CFD) (CHE et al., 2009). CFD is a type of numerical algorithms commonly used to solve problems that involve fluids. The algorithm used in this work solves an Euler equation for compressible flow.

- 12. You Only Look Once (YOLO) is an open-source high accurate real-time CNN-based object detection framework for automotive applications (REDMON; FARHADI, 2018). This work uses three versions of YOLO, version one, two, and three. The newer version of YOLO is always different from the former one. For instance, they all differ in the layer numbers, YOLOv1 has 31 layers, YOLOv2 has 32 layers, and YOLOv3 has 106 layers (REDMON et al., 2015; REDMON; FARHADI, 2016; REDMON; FARHADI, 2018). The differences between the versions are mainly upgrades in the original algorithms that improved the object detection's accuracy and performance. In this work, all YOLO versions are tested with Caltech dataset (DOLLÁR et al., 2012). Exceptionally, YOLOv3 is executed in single and half precision on NVIDIA Volta. It is worth noting that, to focus only on mixed-precision operation effects on CNN reliability, YOLOv3 is not retrained. The weights of the single-precision version are converted to half-precision precision.

This work also discusses if the code reliability characteristic is due to the resources' sensitivity, the number of resources used for computation, or the probability of propagating faults (AVF). Tables 3.1 and 3.2 also list the amount of shared memory and the average number of registers used for computation together with the execution time. They also include the IPC and occupancy metrics used to consider the GPU parallel

management in the FIT rate prediction (details in Section 6.2).

Table 3.1: Codes used for reliability evaluation on Kepler.

| Benchmark    | Precision | SHARED (KB) | RF (AVG) | Execution Time [s] | IPC  | Occupancy |

|--------------|-----------|-------------|----------|--------------------|------|-----------|

| CCL          | Integer   | 0.12        | 33.1     | 1.19               | 0.14 | 0.11      |

| BFS          | Integer   | 0           | 20.3     | 0.27               | 1.22 | 0.81      |

| Lava         | Float     | 7.04        | 37       | 2.43               | 4.12 | 0.57      |

| Hotspot      | Float     | 3           | 23       | 1.7                | 3.89 | 0.94      |

| Gaussian     | Float     | 0           | 13.9     | 0.27               | 0.51 | 0.34      |

| LUD          | Float     | 8.61        | 26.1     | 1.44               | 0.58 | 0.37      |

| NW           | Integer   | 8.26        | 32       | 0.33               | 0.2  | 0.08      |

| MXM          | Float     | 8           | 25       | 0.38               | 1.5  | 1         |

| GEMM         | Float     | 31.01       | 247.8    | 0.07               | 4.94 | 0.19      |

| Mergesort    | Integer   | 2.51        | 15.4     | 0.75               | 2.11 | 0.97      |

| Quicksort    | Integer   | 0.32        | 26.1     | 1.81               | 1.97 | 0.96      |

| Yolov2       | Float     | 8.02        | 96.2     | 0.1                | 2.84 | 0.59      |

| Yolov3       | Float     | 9.07        | 99.6     | 0.44               | 3.11 | 0.65      |

| Faster R-CNN | Float     | 5.4         | 67.7     | 0.09               | 2.40 | 0.58      |

| Resnet       | Float     | 1.9         | 63.9     | 0.03               | 1.54 | 0.49      |

Table 3.2: Codes used for reliability evaluation on Volta.

| Benchmark | Precision | SHARED (KB) | RF (AVG) | Execution Time | IPC  | Occupancy |

|-----------|-----------|-------------|----------|----------------|------|-----------|

|           | Half      | 8           | 255      | 0.31           | 0.26 | 0.1       |

| Lava      | Float     | 8           | 255      | 0.56           | 0.12 | 0.1       |

|           | Double    | 16          | 254      | 1.07           | 0.07 | 0.1       |

|           | Half      | 16          | 26       | 0.44           | 0.48 | 0.94      |

| Hotspot   | Float     | 32          | 27       | 0.65           | 0.32 | 0.95      |

|           | Double    | 64          | 30       | 1.3            | 0.18 | 0.96      |

|           | Half      | 0           | 27       | 1.17           | 2.84 | 1         |

| MXM       | Float     | 0           | 25       | 1.97           | 2.62 | 1         |

|           | Double    | 0           | 29       | 2.4            | 2.3  | 1         |

|           | Half      | 64          | 127      | 0.4            | 2.34 | 0.25      |

| GEMM      | Float     | 64          | 134      | 0.77           | 2.36 | 0.13      |

|           | Double    | 64          | 234      | 1.3            | 1.22 | 0.13      |

|           | Half      | 21.52       | 69.0     | 0.4            | 1.23 | 0.7       |

| Yolov3    | Float     | 34.18       | 122      | 0.46           | 1.74 | 0.7       |

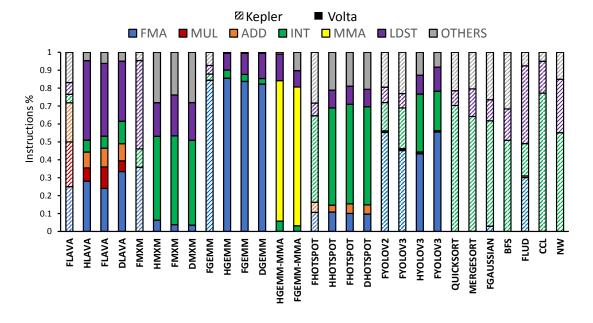

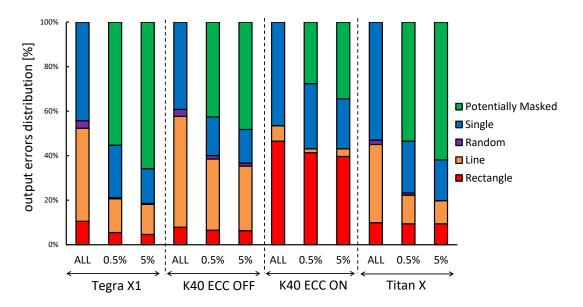

The dynamic instructions are profiled for each code listed in Table 3.1 and 3.2 using NVPROF and NSIGHT-COMPUTE, respectively. Profiling the codes provide insights into the micro-instructions that significantly contribute to the benchmark execution. Figure 3.1 shows, in percentage, the micro-instructions that compose each code. Each float point code has the precision made explicit in the first letter of its name, D for double-precision (64 bits), F for single-precision (32 bits), and H for half-precision (16 bits). That is, *HHOTSPOT* is Hotspot executed in half-precision, *DGEMM* is GEMM executed in double-precision. Codes that only operate with INT32 data do not have their names modified.

The instructions in the kernel profile are divided into two classes: (1) the arithmetic instructions commonly used on the benchmarks (i.e., FMA, MUL, ADD, INT, MMA), and the primary instruction used for data movement (LDST). (2) "OTHERS" are the ones that have a minor contribution to the final benchmark. (i.e., transcendental functions, branch, inter-thread communication, thread barrier, NOP, and atomic directives). The FIT rate of only the former set of instructions is measured through beam experiments, as they are the most likely to be corrupted and the most common in a wide range of codes. Testing all the micro-instructions would be unfeasible due to beam time restrictions (more than 20 different micro-instructions types in the NVIDIA ISA). Nevertheless, as further demonstrated in Chapter 6, even considering a (large but not exhaustive) subset of instructions allows a reasonable estimation of the code's FIT rates. The information provided by the profile tools is required to map how the application uses the GPU's resources. Thus, a detailed profile is crucial for a correct FIT prediction. Figure 3.1 shows that the arithmetic instructions dominate the composition of chosen benchmarks, information that will be useful later in this work.

Figure 3.1: Instruction type per code for Kepler and Volta.

#### 3.3 Synthetic Micro Benchmarks implementation

This section describes the implementation of the microbenchmarks used in this work. Microbenchmarks are a set of synthetic applications designed to stress specific

components of the GPU architecture. Using microbenchmarks, it is possible to evaluate the error rate of a particular resource. Table 3.3 shows the main characteristics of each microbenchmark. The microbenchmarks are tuned to stress mostly the unit that is being evaluated. That is, in each microbenchmark composition, 99% of the instructions is the one that is being assessed. For example, 99% of the FADD microbenchmark is FP32 ADD instructions. In sequence, each microbenchmark is explained in detail.

RF and SHARED micro-benchmarks measure the FIT rate of the Register File and Shared Memory, respectively (L1 cache has the same technology as Shared Memory). Each thread per SM that writes a known pattern in all accessible registers or shared memory (255 registers per thread and 48KB of static shared memory among all SM threads) and, after a pre-defined time, read-backs the values counting bit-flips. The microbenchmark instantiates the lowest possible number of threads to reduce the probability of having errors in other resources besides the memories. The time between a write and a read should be long enough to ensure that the setup/read-back time is negligible and short enough to prevent more than one neutron from generating faults. This latter constrain is necessary to detect eventual Multiple Bit Upsets (MBUs, more than one bit corrupted in a single word). The exposure time is heuristically set to 1s. It is anticipable that, for RF, the MBU rate is lower than 2% and, for SHARED, is lower than 0.9%.

LDST performs a sequence of memory movements on the global memory (Load followed by Store) with ECC enabled. The LDST kernel reads a memory region from global memory that contains a unique pattern and stores it in another global memory location. Each kernel consists of 4M threads, each performing  $2^{10}$  memory movements. In total, this micro-benchmark allocates 2GB of memory. The host CPU setup compares the expected pattern on the output memory and counts the number of corruptions. CPU verification time is not considered for FIT calculation.

A group of specific micro-benchmarks was created to evaluate the arithmetic functional units. Each thread in **FMA** (Fused Multiply and Add), **ADD** (Addition), **MUL** (Multiplication), and **MAD** (Integer Multiply and Accumulate) micro-benchmarks executes  $10^8$  operations, while **MMA** performs  $10^7$  16x16 (the matrix is sliced into 4x4 smaller matrices, see Table 3.3) matrix multiplications (with FP16 on HMMA or FP32 casted to FP16 for FMMA). A lower of operations MMA was chosen to keep the exposure time, and so the statistic, similar to the other micro-benchmarks. The inputs are pre-defined and have been randomly generated off-line, ensuring to avoid overflow. The integer and float versions of the micro-benchmarks have been tested on the Kepler and

Table 3.3: Summarized micro-benchmarks details. The information present on the table for the latency is extracted from (JIA et al., 2018; ARAFA et al., 2019). On Volta, the FP16 corresponds to two operations performed in the same hardware (x2). Kepler supports FP64 instruction. However, as Kepler FP64 instructions are not used in this work, they are not listed.

|                 |        | Instruction latency (cycles) |         |      | Operand |                       |

|-----------------|--------|------------------------------|---------|------|---------|-----------------------|

|                 |        | INT32                        | FP16    | FP32 | FP64    | description           |

| Addition        | Kepler | 9                            | _       | 9    | _       | 2 input registers     |

| (ADD)           | Volta  | 4                            | 6(x2)   | 4    | 8       | + 1 output register   |

| Multiply        | Kepler | 9                            | _       | 9    | _       | 2 input registers     |

| (MUL)           | Volta  | 4                            | 6(x2)   | 4    | 8       | + 1 output register   |

| Multiply and    | Kepler | 9                            | _       | 9    | _       | 3 input registers     |

| Add (FMA/MAD)   | Volta  | 4                            | 6(x2)   | 4    | 8       | + 1 output register   |

| Shared memory   | Kepler | 26 - 55                      |         |      |         | Thread Block load     |

| (SHARED)        | Volta  | 18 - 49                      |         | _    |         | followed by store     |

| Matrix Multiply |        |                              | 4x4     |      |         | A warp of threads     |

| and Accumulate  | Volta  | _                            | matrix  | _    | _       | perform 16x16         |

| (MMA)           |        |                              | 1 cycle |      |         | matrix multiply       |

| Load Followed   |        |                              |         |      |         | 4 Bytes load followed |

| by Store (LDST) | Kepler | 331 - 382                    | _       | _    | _       | by 4 Bytes store      |

| by Store (LDS1) |        |                              |         |      |         | on global memory      |

| Register File   | Kepler |                              |         |      |         | 255 loads followed    |

| (RF)            | and    |                              | _       |      |         | by 255 stores         |

| (KI)            | Volta  |                              |         |      |         | by 233 stores         |

the integer (INT32), double (FP64), float (FP32), and half (FP16) versions of the microbenchmarks on the Volta. The number of instantiated threads is tuned to occupy all the GPU's available functional units (3,840 threads for Kepler, 20,480 threads for Volta). The micro-benchmarks can be easily adaptable to any GPU.

#### 3.4 Beam Experiment Setup

Beam experiments are the most effective way to measure the Failure In Time (FIT) rate of code running on a computing device. By dividing the number of observed errors by the received particles fluence  $\eta$  ( $neutrons/cm^2$ ) it is possible to calculate the cross section:

$$\sigma[cm^2] = \frac{\#errors}{\eta} \tag{3.1}$$

The fluence is obtained by multiplying the average neutron flux provided by the test facility  $(neutrons/(cm^2 \cdot s))$  by the effective execution time. The cross-section  $(cm^2)$  represents the circuit area that will generate an output error if hit by a particle. The higher

the number of computation resources, the higher the cross-section, and the higher the probability for an impinging particle to generate an error.