# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

RAFAEL BILLIG TONETTO

# A Reliability- and Variation-Aware Methodology for Improved Processor Designs for the Edge Computing Domain

Thesis presented in partial fulfillment of the requirements for the degree of Doctor of Computer Science

Advisor: Prof. Dr. Gabriel Nazar Co-advisor: Prof. Dr. Antonio Carlos Schneider Beck Filho

Porto Alegre September 2023 Billig Tonetto, Rafael

A Reliability- and Variation-Aware Methodology for Improved Processor Designs for the Edge Computing Domain / Rafael Billig Tonetto. – Porto Alegre: PPGC da UFRGS, 2023.

120 f.: il.

Thesis (Ph.D.) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação, Porto Alegre, BR– RS, 2023. Advisor: Gabriel Nazar; Co-advisor: Antonio Carlos Schneider Beck Filho.

1. Heterogeneous systems. 2. Reliability. 3. Near-threshold voltage. 4. Process variation. I. Nazar, Gabriel. II. Schneider Beck Filho, Antonio Carlos. III. Título.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL Reitor: Prof. Carlos André Bulhões Vice-Reitora: Prof<sup>a</sup>. Patricia Pranke Pró-Reitor de Pós-Graduação: Prof. Júlio Otávio Jardim Barcellos Diretora do Instituto de Informática: Prof<sup>a</sup>. Carla Maria Dal Sasso Freitas Coordenador do PPGC: Prof. Claudio Rosito Jung Bibliotecário-chefe do Instituto de Informática: Alexsander Borges Ribeiro

## AGRADECIMENTOS

Primeiramente, gostaria de agradecer a todos os membros da minha família, meus pais Cláudio e Rejane, e meus irmãos André e Daniela, por todo o apoio oferecido, gratuitamente, ao longo dos meus  $100000_2$  anos de vida. Em especial, gostaria de agradecer aos meus orientadores, Caco e Gabriel Nazar, pelo apoio, paciência e feedbacks providos ao longo dos últimos sete anos de trabalho, desde o mestrado até o final deste programa de doutorado. É sempre um privilégio trabalhar com pessoas que estão à nossa frente.

### ABSTRACT

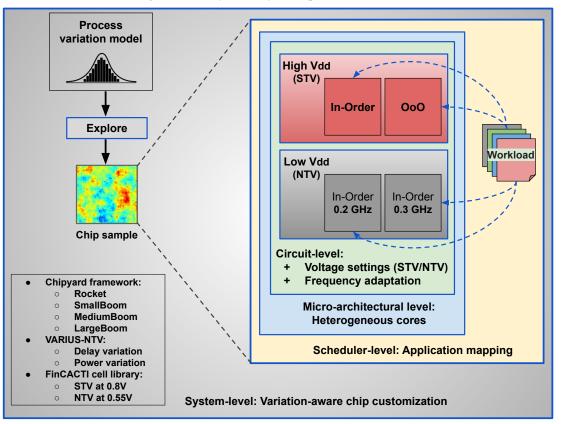

Technology scaling has been successfully improving the performance of current microprocessors primarily due to the reduced node size that enables increased transistor integration, allowing for the design and widespread adoption of high-performance and highly heterogeneous chips. However, despite the slowdown of Moore's Law, the improved transistor integration is accompanied by complex technological challenges and trade-offs that must be addressed. In particular, smaller technology nodes impose increased reliability, power density, and process variation issues that penalize performance, energy efficiency, and yield. Additionally, overcoming such challenges is especially tricky for devices operating at the edge due to the limited power budgets and battery dependency. This thesis, then, proposes a set of methodologies to improve non-functional requirements for heterogeneous chips targeting edge-based applications subject to power, reliability, and process variation constraints. First, we leverage the application and microarchitectural heterogeneity of cores and propose a low-cost learning method for reliability-oriented mappings that provide near-to-optimal Mean Workload to Failure (MWTF) of heterogeneous chips. With the prediction-based mappings, we achieve MWTF as close as 5.6% to the oracle in a low overhead and transparent fashion. Secondly, aiming to improve powerconstrained edge devices' performance and energy efficiency, we propose a design-time strategy for chip customization with Near-Threshold Voltage (NTV). Here, we develop an efficient method to allocate NTV and conventional cores in the same die. In this setup, only an optimal subset of the cores are set to operate at NTV, leaving the remaining cores at conventional voltage settings, attenuating the frequency degradation overheads of NTV. Finally, as NTV comes at the cost of exacerbated process variations, we propose a two-step methodology to address delay and power variations on heterogeneous chips. At design time, we augment our chip composition strategy with parameter variation models and develop a statistical and variation-aware design space exploration for heterogeneous chip composition. At the post-design phase, we propose an efficient frequency adaptation mechanism to further cope with unseen parameter variations and improve either performance or yield. We show that under strict power and process variation restrictions, our proposal improves performance by an average of 3.4 times compared to standard NTV approaches and 12% when compared to chips at conventional voltage levels.

**Keywords:** Heterogeneous systems. Reliability. Near-threshold voltage. Process variation.

# Uma Metodologia Visando Melhoria de Confiabilidade e Variação de Processos em Processadores no Domínio da Computação na Borda

#### **RESUMO**

A escalabilidade tecnológica tem melhorado com sucesso o desempenho dos microprocessadores atuais, principalmente devido ao tamanho reduzido dos circuitos que permite uma maior integração de transistores, possibilitando o projeto e a adoção generalizada de chips altamente heterogêneos e de alto desempenho. No entanto, apesar da desaceleração da Lei de Moore, a alta integração de transistores é acompanhada por desafios tecnológicos e trade-offs difíceis de serem enfrentados. Em especial, transistores menores impõem problemas de confiabilidade, densidade de potência e variabilidade de processo que penalizam o desempenho, a eficiência energética e o yield quando não são adequadamente abordados. Superar esses desafios é especialmente difícil para dispositivos que operam em ambientes de borda devido aos limites de potência e à dependência de baterias. Nesta tese, propomos uma metodologia abrangente para melhorar os requisitos não funcionais de chips heterogêneos destinados a aplicações de borda sujeitas a restrições de potência, confiabilidade e variabilidade de processo. Primeiro, aproveitamos a heterogeneidade de aplicações e de microarquitetura dos núcleos de processadores e propomos um método de aprendizado de baixo custo para mapeamentos orientados à confiabilidade que fornecem um tempo médio de carga até a falha (MWTF, na sigla em inglês) próximo ao ideal para chips heterogêneos. Com os mapeamentos baseados em previsão, alcançamos um MWTF tão próximo quanto 5,6% do oráculo com baixo custo e de forma transparente. Em segundo lugar, com o objetivo de melhorar o desempenho e a eficiência energética de dispositivos de borda com restrição de potência, propomos uma estratégia de configuração de chips em tempo de projeto com uso de Tensão Próxima do Limiar (NTV). Desenvolvemos uma estratégia eficiente para alocar núcleos tanto NTV quanto convencionais no mesmo chip. Nessa configuração, apenas um subconjunto ótimo dos núcleos opera com NTV, deixando os demais núcleos com configurações convencionais de tensão, reduzindo assim as perdas de frequência decorrentes do uso de NTV. Por fim, como o uso de NTV acarreta variabilidades de processo exacerbadas, propomos uma metodologia em duas etapas para lidar com variabilidades de frequência e potência em chips heterogêneos. No momento do projeto, aprimoramos nossa estratégia anterior de composição de chips com modelos de variabilidade de parâmetros e desenvolvemos uma exploração estatística e ciente da variabilidade do espaço de design para a composição de chips heterogêneos. Na fase pós-projeto, implementamos um mecanismo eficiente de adaptação de frequência para lidar com variabilidade de parâmetros não previsíveis e melhorar o desempenho ou o yield. Mostramos que, sob restrições estritas de potência e variabilidade de processo, nossa proposta melhora o desempenho, em média, em 3,4 vezes em comparação com abordagens padrão de NTV e em 12% em comparação com chips em níveis convencionais de tensão.

**Palavras-chave:** Sistemas heterogêneos. Confiabilidade. Tensão próxima ao limiar. Variabilidade de processos.

# LIST OF FIGURES

| Figure 1.1 Processor trend data up until the year of 2021.                                                                                              | 13  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 1.2 Thesis outline. The contributions of this thesis are highlighted in red                                                                      | 18  |

| Figure 2.1 The NMOS transistor                                                                                                                          | 22  |

| Figure 2.2 Potential reduction in the energy required per operation for different                                                                       |     |

| supply voltage levels, and the corresponding impact in the transistor delay                                                                             | 26  |

| Figure 2.3 Frequency spread (right axis) as a function of $V_{dd}/V_{th}$ variation                                                                     |     |

| Figure 2.4 An Alpha (single-ISA) heterogeneous chip                                                                                                     |     |

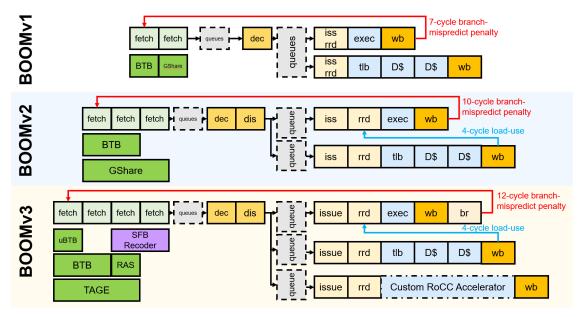

| Figure 2.5 Evolution of the BOOM processor organization.                                                                                                |     |

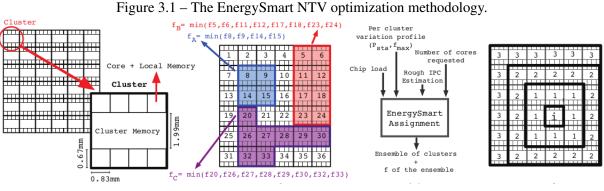

| Figure 3.1 The EnergySmart NTV optimization methodology                                                                                                 | 38  |

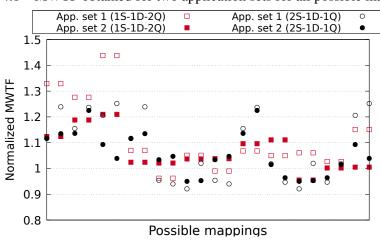

| Figure 4.1 MWTF obtained for two application sets for all possible mappings                                                                             | 45  |

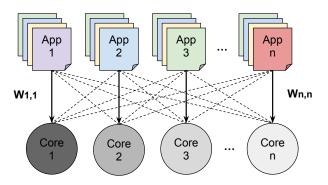

| Figure 4.2 Assignment graph of application mappings aiming to maximize the                                                                              |     |

| overall MWTF                                                                                                                                            | 46  |

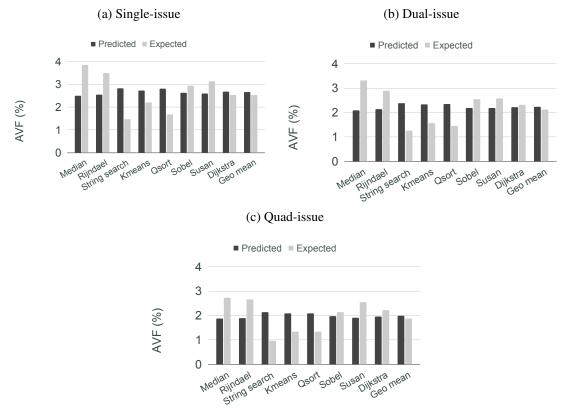

| Figure 4.3 The predicted AVF estimation by the neural network compared to the                                                                           |     |

| expected values estimated with fault injection                                                                                                          | 48  |

| Figure 4.4 The predicted AVF estimation by the neural network compared to the                                                                           |     |

| expected values estimated with fault injection                                                                                                          | 52  |

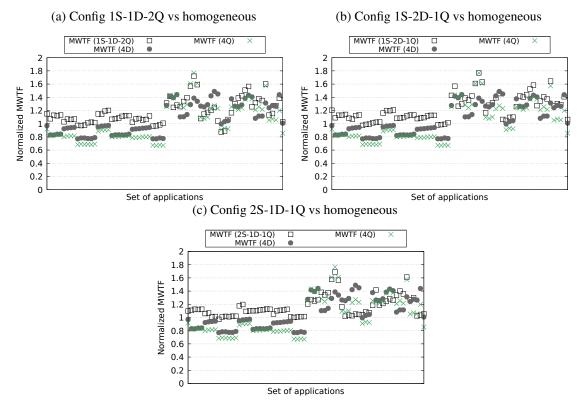

| Figure 4.5 Configuration 1S-1D-2Q                                                                                                                       | 53  |

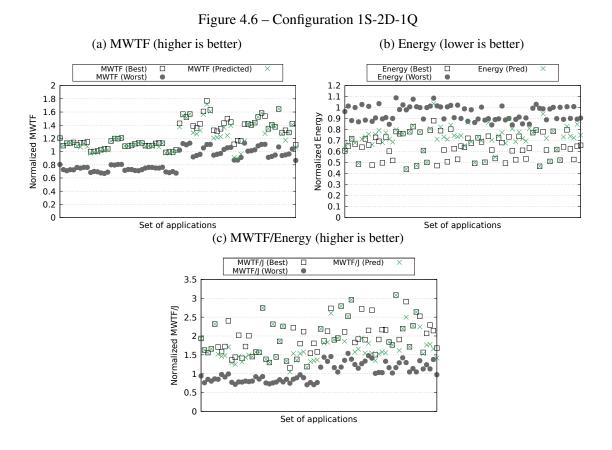

| Figure 4.6 Configuration 1S-2D-1Q                                                                                                                       | 54  |

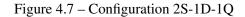

| Figure 4.7 Configuration 2S-1D-1Q                                                                                                                       | 54  |

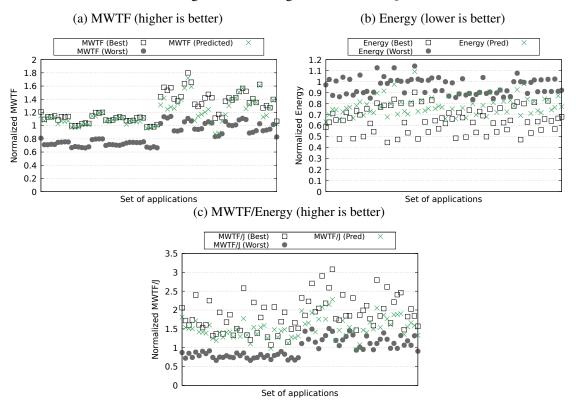

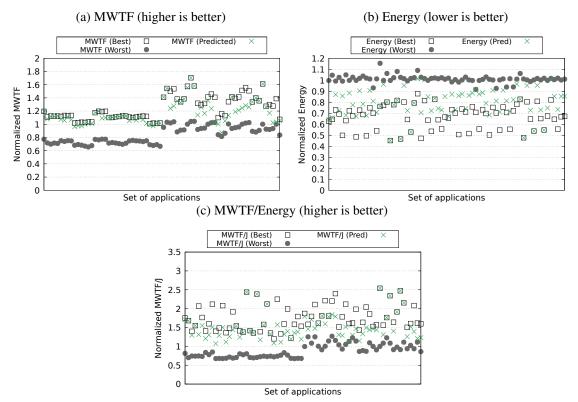

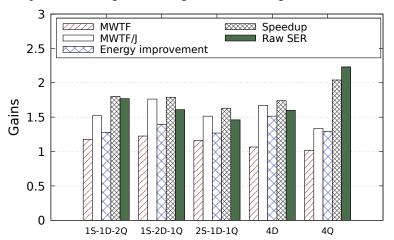

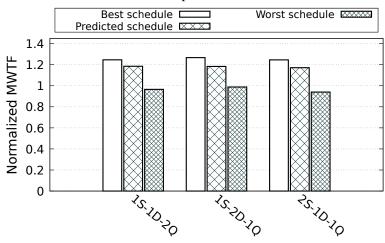

| Figure 4.8 Average MWTF gains for all application sets for the three mapping cases.                                                                     | .55 |

| Figure 4.9 Comparison of the three different heterogeneous configurations (using                                                                        |     |

| the predicted mappings) against two homogeneous ones.                                                                                                   | 56  |

| Figure 4.10 Comparison (average values) against two homogeneous architectures                                                                           |     |

| (4D and 4Q).                                                                                                                                            | 56  |

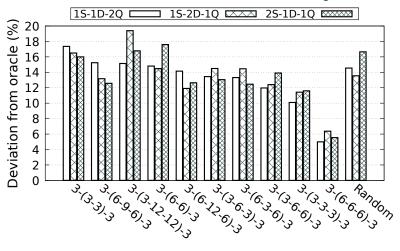

| Figure 4.11 MWTF deviation from oracle for different ANN configurations (lower                                                                          |     |

| is better)                                                                                                                                              | 58  |

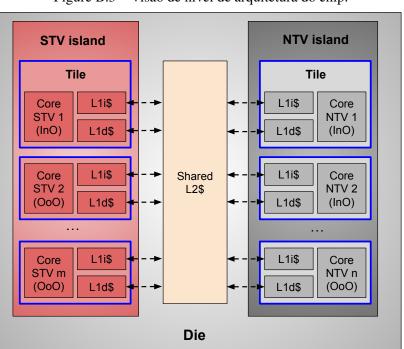

| Figure 5.1 Architecture-level view of the chip                                                                                                          | 59  |

| Figure 5.2 Assignment graph of application mappings aiming to maximize the                                                                              |     |

| overall MIPS.                                                                                                                                           | 61  |

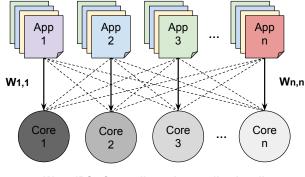

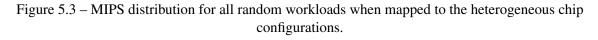

| Figure 5.3 MIPS distribution for all random workloads when mapped to the het-                                                                           |     |

| erogeneous chip configurations                                                                                                                          | 65  |

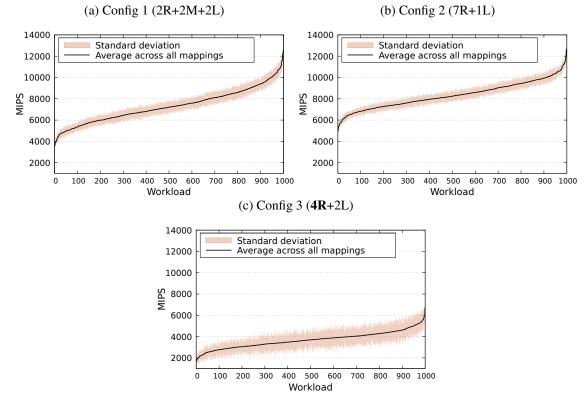

| Figure 5.4 MIPS distribution for the two workloads with the lowest (lowest var)                                                                         |     |

| and highest (highest var) degree of MIPS variation across all mappings to                                                                               |     |

| heterogeneous chips.                                                                                                                                    | 66  |

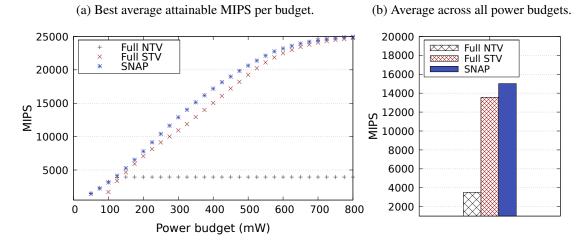

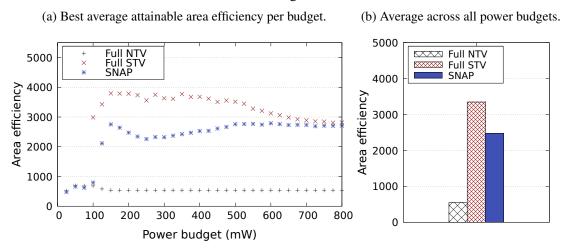

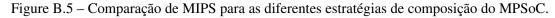

| Figure 5.5 MIPS comparison for the different MPSoC composition strategies                                                                               |     |

| Figure 5.6 Area efficiency $(MIPS/mm^2)$ comparison for the different MPSoC                                                                             |     |

| composition strategies                                                                                                                                  | 69  |

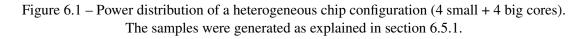

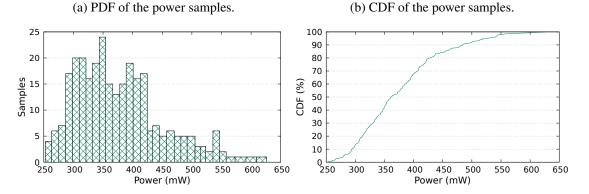

| Figure 6.1 Dower distribution of a betargaphague abin configuration (A small + A                                                                        |     |

| Figure 6.1 Power distribution of a heterogeneous chip configuration (4 small + 4 big cores). The samples were constructed as explained in section 6.5.1 | 70  |

| big cores). The samples were generated as explained in section 6.5.1                                                                                    |     |

| Figure 6.2 System layers explored in this thesis.                                                                                                       |     |

| Figure 6.3 Abstract workflow of this thesis.                                                                                                            |     |

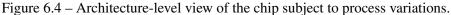

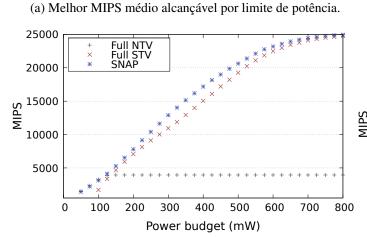

| Figure 6.4 Architecture-level view of the chip subject to process variations                                                                            |     |

| Figure 6.5 Design time chip exploration workflow                                                                                                        |     |

| Figure 6.6 The goals of frequency scaling.                                                                                                              | 80  |

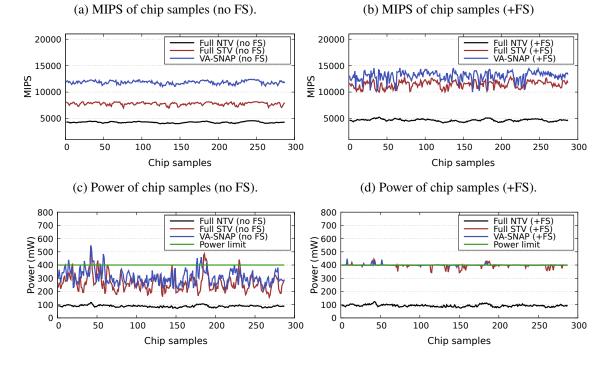

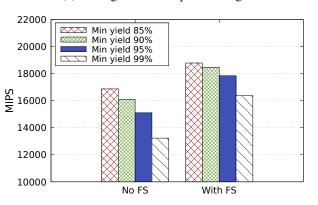

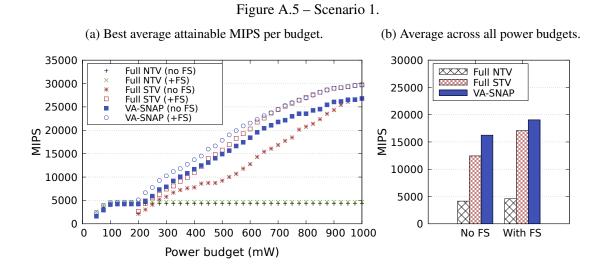

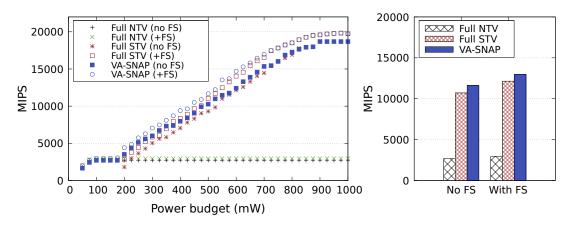

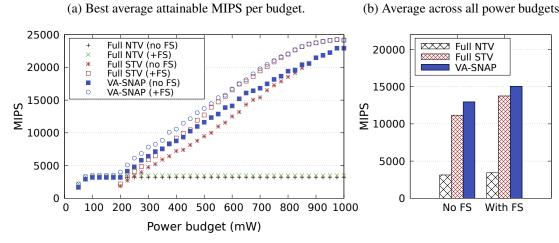

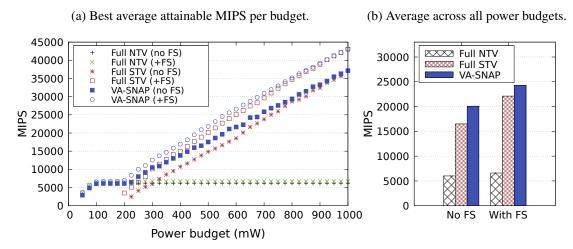

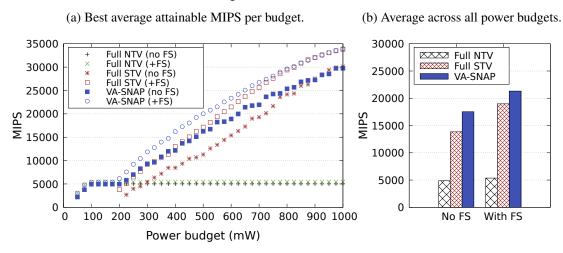

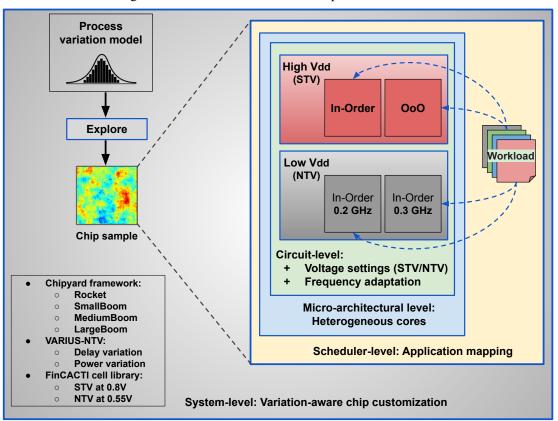

| Figure 6.7 N | MIPS comparison for the different MPSoC composition strategies         | 86  |

|--------------|------------------------------------------------------------------------|-----|

| Figure 6.8 N | MIPS and power samples for optimized chips aiming a power limit of     |     |

| 400m         | W, with and without FS                                                 | 88  |

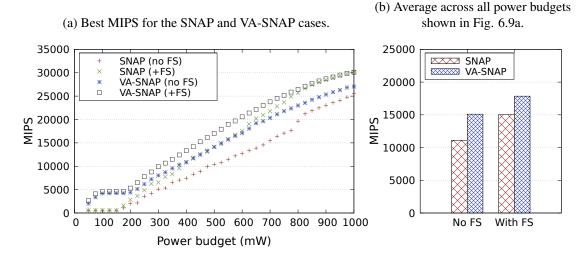

| Figure 6.9 A | Average best achievable MIPS for the variation aware (VA-SNAP) and     |     |

| unawa        | re (SNAP) designs, with and without frequency scaling                  | 88  |

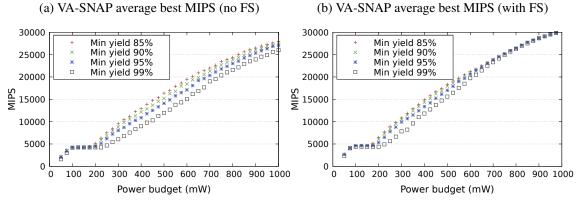

| Figure 6.10  | Best attainable MIPS for various yield requirements for the variation- |     |

|              | VA-SNAP case                                                           | 89  |

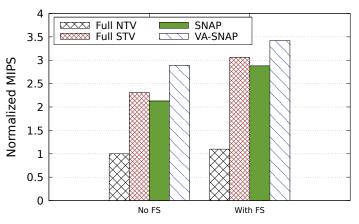

| Figure 6.11  | MIPS performance of all evaluated methods, normalized to the Full      |     |

| NTV (        | (No FS) case                                                           | 90  |

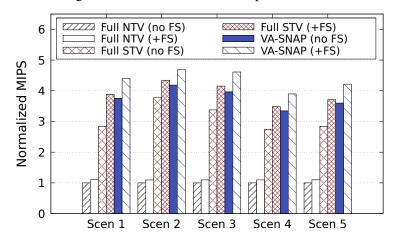

| Figure 6.12  | Normalized MIPS per each scenario                                      | 91  |

| Figure A.1   | SmallBoom configuration file (Chisel/Scala code)                       | 106 |

| Figure A.2   | Medium configuration file (Chisel/Scala code).                         | 107 |

| 0            | LargeBoom configuration file (Chisel/Scala code)                       | 108 |

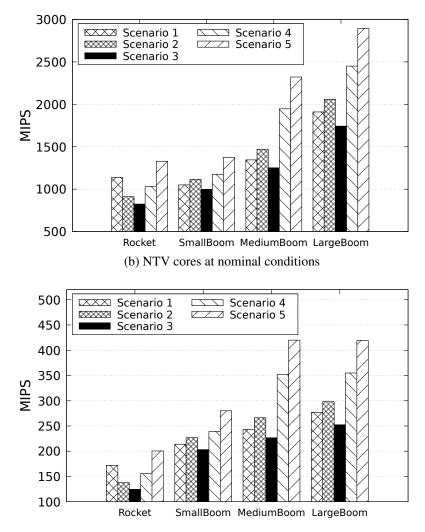

| Figure A.4   | Per-core attainable MIPS for each scenario explored in Chapter 6 (Tab. |     |

| 6.2)         |                                                                        | 109 |

| U            | Scenario 1                                                             |     |

| U            | Scenario 2                                                             |     |

| 0            | Scenario 3                                                             |     |

| Figure A.8   | Scenario 4                                                             | 111 |

|              | Scenario 5                                                             |     |

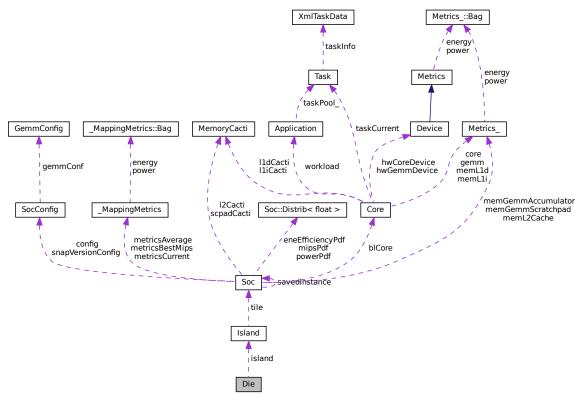

| Figure A.10  | Class diagram of the source code.                                      | 112 |

| 0            | Visão geral desta tese. As contribuições principais estão marcadas em  |     |

|              | lho                                                                    | 114 |

| -            | Ganhos médios de MWTF para todos os conjuntos de aplicações nos        |     |

|              | asos de mapeamento                                                     |     |

|              | Visão de nível de arquitetura do chip                                  | 116 |

| e            | O mapeamento de aplicações visa maximizar o MIPS total (milhões de     |     |

|              | ções por segundo)                                                      | 117 |

|              | Comparação de MIPS para as diferentes estratégias de composição do     |     |

|              | С                                                                      |     |

| e            | Camadas do sistema exploradas nesta tese                               | 118 |

| -            | Comparação de MIPS para as diferentes estratégias de composição de     |     |

| MPSo         | С                                                                      | 119 |

# LIST OF TABLES

| Table 1.1 The optimization requirements tackled in this work with the associated hampering factors, and the proposed (combination) of solutions tackling each constraint.                                                                         | 15 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 2.1 Some examples of popular commercial heterogeneous MPSoCs from<br>three leading smartphone companies.                                                                                                                                    | 29 |

| Table 3.1 Previews works on addressing varying optimization goals                                                                                                                                                                                 | 40 |

| Table 4.1 Explored core configurations.                                                                                                                                                                                                           | 44 |

| Table 4.2 Area $(mm^2)$ and approximate normalized flip-flop raw SER (based on the number of flip-flops) of the explored chips                                                                                                                    | 51 |

| Table 4.3 Percentage of application sets that maximize a given metric when prediction based mapping is applied to each evaluated chip configuration. Example: 62.8% of the application sets achieve the highest MWTF with configuration 1S-2D1-Q. |    |

| Table 5.1 Explored core configurations. The power and frequency shown are under<br>nominal conditions.                                                                                                                                            |    |

| Table 5.2 Suite of edge-applicable tasks adopted in this work.                                                                                                                                                                                    | 64 |

| Table 5.3 The three evaluated chip cases. Four NTV rocket cores ( <b>4R</b> ) are considered in Config 3. All other cores are at STV                                                                                                              | 65 |

| Table 5.4 Mapping distribution characterization, for each configuration, for the two         workloads with the lowest and highest variation across mappings                                                                                      |    |

| Table 6.1 Explored processor configurations. The power and frequency shown are<br>under nominal conditions.                                                                                                                                       | 84 |

| Table 6.2 Application scenarios explored in this work.                                                                                                                                                                                            |    |

| Table 6.3 Best average achievable MIPS for varying yield requirements (averageacross all power budgets). Gains are the geometric mean of all gains, across all                                                                                    |    |

| budgets, provided by frequency scaling                                                                                                                                                                                                            | 87 |

| Table 6.4 MIPS gains of VA-SNAP (+FS), per scenario, against all other chip de-<br>sign cases.                                                                                                                                                    | 01 |

| 51511 Cases.                                                                                                                                                                                                                                      | ノ1 |

## LIST OF ABBREVIATIONS AND ACRONYMS

- ANN Artificial Neural Network

- AVF Architectural Vulnerability Factor

- DMR Dual Modular Redundancy

- DSE Design Space Exploration

- DSP Digital Signal Processor

- DVFS Dynamic Voltage and Frequency Scaling

- ECC Error Correcting Code

- GPU Graphics Processing Unit

- ILP Instruction-Level Parallelism

- ISA Instruction Set Architecture

- MPSoC Multiprocessor System on a Chip

- MWTF Mean Workload to Failure

- NTC Near-Threshold Computing

- NTV Near-Threshold Voltage

- RMT Redundant Multi-Threading

- RTL Register-Transfer Level

- SDC Silent Data Corruption

- SER Soft Error Rate

- SEU Single-Event Upset

- STC Super-Threshold Computing

- STV Super-Threshold Voltage

- TDP Thermal Design Power

- TMR Triple Modular Redundancy

- VLSI Very Large-Scale Integration

# CONTENTS

| 1 INTRODUCTION                                                                                                             | 13                                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| 1.1 Challenges Addressed in this Thesis                                                                                    | 14                                                                                                                       |

| 1.2 Contributions of this Thesis                                                                                           | 17                                                                                                                       |

| 1.2.1 Contribution 1: Reliability-Oriented Mapping Solutions                                                               | 17                                                                                                                       |

| 1.2.2 Contribution 2: Efficient use of NTV for Improved Performance and Energy                                             |                                                                                                                          |

| Efficiency                                                                                                                 |                                                                                                                          |

| 1.2.3 Contribution 3: Addressing Process Variations                                                                        |                                                                                                                          |

| 1.3 Structure of this Document                                                                                             |                                                                                                                          |

| 2 BACKGROUND                                                                                                               |                                                                                                                          |

| 2.1 Sources of Power Consumption and Optimization Methods                                                                  |                                                                                                                          |

| 2.2 Radiation-Induced Soft Errors and Fault Tolerance Concepts                                                             |                                                                                                                          |

| 2.3 Near-Threshold Voltage Computing                                                                                       |                                                                                                                          |

| 2.3.1 Timing Failures                                                                                                      |                                                                                                                          |

| 2.4 State-of-the-Art Heterogeneous Architectures                                                                           |                                                                                                                          |

| 2.5 The Chipyard Framework                                                                                                 |                                                                                                                          |

| 2.5.1 The BOOM and Rocket Cores                                                                                            |                                                                                                                          |

| 3 RELATED WORK                                                                                                             |                                                                                                                          |

| 3.1 Related Works on Addressing Soft Errors Reliability                                                                    |                                                                                                                          |

| 3.1.1 Redundancy-based Fault Tolerance Approaches                                                                          |                                                                                                                          |

| <ul><li>3.1.2 Mapping-based Fault Tolerance Approaches</li><li>3.2 Related Works on Process Variation Mitigation</li></ul> |                                                                                                                          |

| 3.3 Contextualizing this Thesis with Respect to Previous Works                                                             |                                                                                                                          |

| 4 APPLICATION MAPPING APPROACHES TO IMPROVE RELIABILITY                                                                    | 40                                                                                                                       |

| AND PERFORMANCE OF HETEROGENEOUS SYSTEMS                                                                                   | 42                                                                                                                       |

|                                                                                                                            |                                                                                                                          |

| 4.1 Improving MWTF with Application Mapping                                                                                | 42                                                                                                                       |

| <b>4.1 Improving MWTF with Application Mapping</b>                                                                         |                                                                                                                          |

| 4.1.1 Motivation and Background                                                                                            | 44                                                                                                                       |

|                                                                                                                            | 44<br><b>46</b>                                                                                                          |

| <ul> <li>4.1.1 Motivation and Background</li> <li>4.2 Adaptive Mapping</li></ul>                                           | 44<br><b>46</b><br>46                                                                                                    |

| <ul> <li>4.1.1 Motivation and Background</li></ul>                                                                         | 44<br>46<br>50                                                                                                           |

| <ul> <li>4.1.1 Motivation and Background</li> <li>4.2 Adaptive Mapping</li></ul>                                           | 44<br>46<br>50<br>53                                                                                                     |

| <ul> <li>4.1.1 Motivation and Background</li></ul>                                                                         | 44<br>46<br>50<br>53<br>53                                                                                               |

| <ul> <li>4.1.1 Motivation and Background</li></ul>                                                                         | 44<br>46<br>50<br>53<br>53                                                                                               |

| <ul> <li>4.1.1 Motivation and Background.</li> <li>4.2 Adaptive Mapping</li></ul>                                          | 44<br>46<br>50<br>53<br>53<br>55<br>56                                                                                   |

| <ul> <li>4.1.1 Motivation and Background</li></ul>                                                                         | 44<br>46<br>50<br>53<br>55<br>56<br>57                                                                                   |

| <ul> <li>4.1.1 Motivation and Background.</li> <li>4.2 Adaptive Mapping</li></ul>                                          | 44<br>46<br>50<br>53<br>55<br>56<br>57<br>58                                                                             |

| <ul> <li>4.1.1 Motivation and Background</li></ul>                                                                         | 44<br>46<br>50<br>53<br>55<br>56<br>57<br>58<br><b>DN</b>                                                                |

| <ul> <li>4.1.1 Motivation and Background</li></ul>                                                                         | 44<br>46<br>50<br>53<br>53<br>55<br>56<br>57<br>58<br>DN<br>59<br>59                                                     |

| <ul> <li>4.1.1 Motivation and Background</li></ul>                                                                         | 44<br>46<br>50<br>53<br>53<br>55<br>56<br>57<br>58<br>DN<br>59<br>59<br>60                                               |

| <ul> <li>4.1.1 Motivation and Background</li></ul>                                                                         | 44<br>46<br>50<br>53<br>53<br>55<br>56<br>57<br>58<br><b>DN</b><br>59<br>59<br>60                                        |

| <ul> <li>4.1.1 Motivation and Background</li></ul>                                                                         | 44<br>46<br>50<br>53<br>53<br>55<br>56<br>57<br>58<br><b>DN</b><br>59<br>59<br>60<br>61                                  |

| <ul> <li>4.1.1 Motivation and Background.</li> <li>4.2 Adaptive Mapping</li></ul>                                          | 44<br>46<br>50<br>53<br>53<br>55<br>56<br>57<br>58<br>DN<br>59<br>60<br>60<br>61<br>63                                   |

| <ul> <li>4.1.1 Motivation and Background</li></ul>                                                                         | 44<br>46<br>50<br>53<br>53<br>55<br>56<br>57<br>58<br>DN<br>59<br>60<br>63<br>63                                         |

| <ul> <li>4.1.1 Motivation and Background</li></ul>                                                                         | 44<br>46<br>50<br>53<br>53<br>55<br>56<br>57<br>58<br><b>DN</b><br>59<br><b>59</b><br><b>60</b><br><b>61</b><br>63<br>63 |

| <ul> <li>4.1.1 Motivation and Background</li></ul>                                                                         | 44<br>46<br>50<br>53<br>53<br>55<br>56<br>57<br>58<br><b>DN</b><br>59<br>60<br>61<br>63<br>65<br>65                      |

| <ul> <li>4.1.1 Motivation and Background</li></ul>                                                                         | 44<br>46<br>50<br>53<br>53<br>55<br>56<br>57<br>58<br><b>DN</b><br>59<br>60<br>63<br>63<br>65<br>65                      |

| 6 A VARIATION-AWARE METHODOLOGY FOR IMPROVED PROCES-                  |      |

|-----------------------------------------------------------------------|------|

| SOR DESIGNS FOR THE EDGE COMPUTING DOMAIN                             | 70   |

| 6.1 Motivational Analysis                                             | 70   |

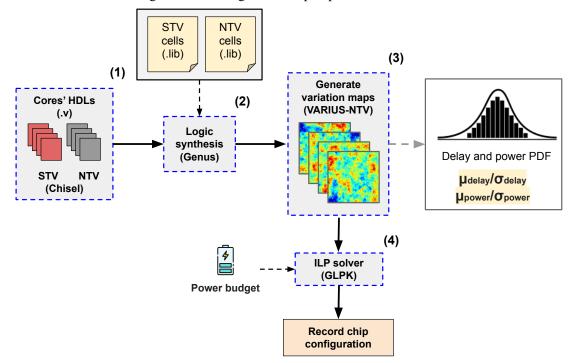

| 6.2 Variation-Aware Proposal                                          | 71   |

| 6.3 Approach Overview                                                 | 73   |

| 6.3.1 Proposed Flow of Optimization                                   | 73   |

| 6.3.2 Chip Architecture Exploration Scope                             | 73   |

| 6.3.3 Modeling and Addressing Parameter Variations                    | 74   |

| 6.4 Variation-Aware Design- and Post-Design time Optimization         | 77   |

| 6.4.1 Design-time and Variation-Aware Chip Customization              | 77   |

| 6.4.2 Post-Design and Variation-Aware Frequency Scaling               | 80   |

| 6.4.3 Putting It All Together: Variation-Aware Exploration Algorithm  | 82   |

| 6.5 The Proposal's Evaluation                                         | 83   |

| 6.5.1 Experimental Methodology                                        |      |

| 6.5.2 Results                                                         |      |

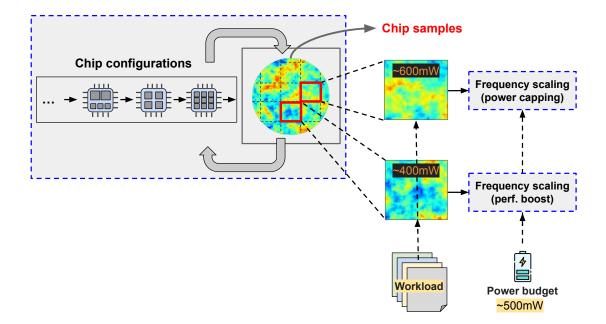

| 6.5.2.1 Variation-Aware VA-SNAP Approach and Frequency Scaling        | 86   |

| 6.5.2.2 Case Study                                                    | 87   |

| 6.5.2.3 Variation-aware versus Variation-unaware Approaches           | 89   |

| 6.5.2.4 MIPS for Minimum Yield Requirements                           | 89   |

| 6.5.2.5 Overall Gains Evaluation                                      |      |

| 6.5.2.6 Per-Scenario Results                                          | 91   |

| 7 CONCLUSIONS                                                         |      |

| 7.1 Addressing Reliability                                            | 92   |

| 7.2 Improving Performance and Energy Efficiency with NTV Edge Devices | 93   |

| 7.3 Addressing Process Variations with NTV Edge Devices               | 93   |

| 7.4 Future Work                                                       | 94   |

| 7.5 List of Published Papers                                          |      |

| 7.5.1 Main Publications                                               | 96   |

| 7.5.2 Publications as a Collaborator                                  | 96   |

| REFERENCES                                                            | 97   |

| APPENDIX A IMPLEMENTATION DETAILS AND PER-SCENARIO EVA                | L-   |

| UATION                                                                | 106  |

| A.1 Detailed Configurations of the Explored Cores                     |      |

| A.2 Per-Scenario VA-SNAP Evaluation                                   | 109  |

| A.3 Class Diagram of the Architecture                                 | .112 |

| APPENDIX B — UMA METODOLOGIA VISANDO O APRIMORAMENTO                  |      |

| DE PROCESSADORES RESTRITOS À VARIAÇÃO DE PROCES-                      |      |

| SOS E APLICÁVEIS À COMPUTAÇÃO DE BORDA                                |      |

| B.1 Parte 1: Otimização de Confiabilidade                             |      |

| B.2 Parte 2: Otimização de Desempenho e Eficiência Energética         |      |

| B.3 Parte 3: Abordando Variabilidade de Processos                     |      |

#### **1 INTRODUCTION**

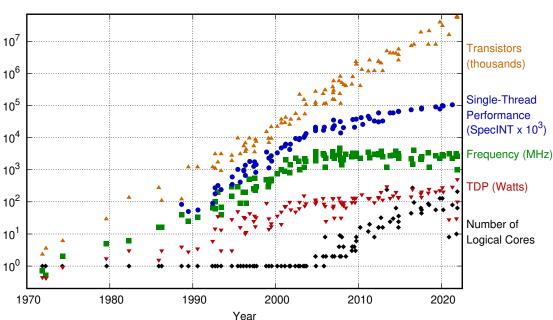

The progressive improvements in technology scaling and the associated increased transistor integration have resulted in the emergence of a myriad of heterogeneous chip designs to accommodate the performance demands of a diverse domain of complex applications. Such integration trends are shown in Fig. 1.1, which characterizes the evolution of microprocessors up until the year 2021 (data obtained from (RUPP, 2021)). Despite the slowdown of Moore's Law, there has been continuous and exponential integration of transistors over the decades. On the other hand, no significant frequency improvements have been achieved since around 2005, which resulted in roughly the stagnation of single-threaded performance and, as a consequence, the emergence of the multicore paradigm and the urge for more hardware specialization in the form of domain-specific architectures (HENNESSY; PATTERSON, 2019).

Specially, such technological progress has enabled the emergence of heterogeneous multicores applicable to the *edge computing* domain (Shi et al., 2016; Wu et al., 2019). In this computing environment, applications are executed by edge devices that operate near the network's edge. In general, edge devices can be any form of processing engine between the end user and the cloud (e.g., a device operating near a data sensor

Figure 1.1 – Processor trend data up until the year of 2021.

Original data up to the year 2010 collected and plotted by M. Horowitz, F. Labonte, O. Shacham, K. Olukotun, L. Hammond, and C. Batten New plot and data collected for 2010-2021 by K. Rupp

#### Source: (RUPP, 2021)

that provides the input data to the device). Executing applications (or parts of them) at the edge is compelling for latency-critical operations since it allows for improved performance and even energy efficiency since edge-based execution avoids offloading input data to remote servers that usually rely on unpredictable network latency, mainly due to uncertain server-side performance caused by CPU load variance and queuing (Wang et al., 2020; LI; ZHOU; CHEN, 2018; KANG et al., 2017).

In addition to the hardware-side amelioration of commodity microprocessors, the growing commercial interests of both hardware and software industries have resulted in the proliferation of many newer and more performance-demanding applications. Usually, applications tend to be considerably heterogeneous due to the high number of different domains they span. For example, up to July 2023, Google Play alone has over 2.6 million published Android applications spanning across several distinct categories such as enter-tainment, education, business, online shopping, and many others (STATISTICS, 2023). This further paves the way for the adoption of *heterogeneous systems*, where state-of-the-art power/performance optimization strategies often harness from *software heterogene-ity* by adopting *hardware heterogeneity* across different layers of the system (e.g., from circuit- to system-level), in which the combination of both hardware and software heterogeneity can be explored to improve key metrics (e.g., performance, power, energy, reliability, etc.) by leveraging application-to-core affinities and mapping applications to the most suitable core.

However, despite the progressive improvements in computing systems, many edgeside optimization challenges are still associated with transistor downscaling. Among others, some important and challenging constraints are (1) radiation-induced soft errors, (2) the chip-specific power envelope and the associated power wall issues, and (3) transistorlevel process variation. When not addressed, such constraints hinder many (functional and non-functional) essential requirements of microprocessors, such as reliability, performance, energy efficiency, and yield. This thesis, then, aims at optimizing such requirements of heterogeneous chips subject to the three constraints mentioned above.

#### 1.1 Challenges Addressed in this Thesis

We illustrate the optimization requirements addressed in this thesis, their associated hampering factors, and the proposed solutions in Tab. 1.1. We justify addressing the considered hampering factors in the domain of heterogeneous multicores as follows:

| Requirement             | Hampering factors                                                   | Proposed solutions<br>Reliability-oriented<br>application mapping                                         |  |

|-------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--|

| Reliability             | Single-event upsets                                                 |                                                                                                           |  |

| Energy efficiency       | Power wall                                                          | Efficient use of NTV +<br>Frequency adaptation                                                            |  |

|                         | Process variation                                                   | DSE with heterogeneous cores +<br>Frequency adaptation                                                    |  |

|                         | Power wall Efficient use of NTV -<br>Frequency adaptation           |                                                                                                           |  |

| Performance             | Process variation DSE with heterogeneous co<br>Frequency adaptation |                                                                                                           |  |

|                         | Domain-specific power limits                                        | DSE with heterogeneous cores +<br>Efficient use of NTV +<br>Application mapping +<br>Frequency adaptation |  |

| Yield Process variation |                                                                     | DSE with heterogeneous cores +<br>Frequency adaptation                                                    |  |

Table 1.1 – The optimization requirements tackled in this work with the associated hampering factors, and the proposed (combination) of solutions tackling each constraint.

**Radiation-induced faults.** The diminishing sizes of transistors and the associated reduced voltage of contemporary microprocessors historically pose reliability challenges that arise from radiation-induced faults - frequently in the form of Single-Event Upsets (or SEUs) - that can cause malfunction in mission-critical applications (MITRA et al., 2014; HENKEL et al., 2013). Additionally, while past reliability research has focused mostly on single cores or homogeneous multicore systems, the limitations in Instruction-Level Parallelism (ILP) have led to the adoption of heterogeneous multicore architectures, such as the big.LITTLE and DynamIQ (ARM, 2021) architectures to meet the demands for more task-level throughput. *We make the case that reliability research on heterogeneous multicores is mostly an unexplored topic, and we provide an efficient and low-cost reliability-oriented application mapping optimization methodology for this domain.*

**Power Wall.** The current transistor scaling approaches do not provide simultaneous improvements in feature size and voltage  $(V_{dd})$  because the threshold voltage has not been scaled at the same pace as the transistor's dimension to keep the leakage current under control (Borkar et al., 2003; Horowitz et al., 2005; Bohr, 2007). Hence,  $V_{dd}$  does not scale linearly across different technology generations as it has been kept roughly constant for over one decade and, consequently, power density tends to increase for smaller technology nodes (Bohr, 2007). This trend, then, introduces the phenomenon known as *the* end of Dennard's scaling (Esmaeilzadeh et al., 2011), which claims that voltage should scale linearly with transistors' dimensions and, consequently, power density would stay roughly constant over the generations (Dennard et al., 1974). This contrasts with the actual observed trend of increased power density. In essence, this power wall phenomenon implies that frequency cannot be further improved reliably due to the stagnation of  $V_{dd}$ , leading single-core performance to stagnate. One approach to mitigate the power wall issues is the adoption of low voltage designs based on Near-Threshold Voltage (NTV) (Dreslinski et al., 2010), which consists in setting  $V_{dd}$  to a point close to the threshold voltage. While this comes at the cost of frequency degradation and exacerbated process variations, NTV can improve energy efficiency and throughput under a power envelope when used smartly. We adopt power-aware and efficient use of NTV, reliably at low frequency, to mitigate power wall issues.

**Domain-specific power limits.** In addition to the power wall issues imposed by circuit-level constraints, executing compute-demanding applications on edge devices is challenging to achieve at low power limits. Usually, system-level power envelopes are imposed by Thermal Design Power (TDP) constraints (e.g., due to the limited cooling capabilities) or battery dependence, which demands high energy efficiency. Thus, more aggressive solutions for multicore optimization may be necessary to accommodate such restrictive requirements if high performance is needed for this domain. *We propose an efficient Design Space Exploration (DSE) methodology in both the microarchitectural and voltage settings layer and propose a special NTV optimization method to improve performance with minimal power slacks under a power limit. Although NTV degrades frequency, our strategy reclaims performance by efficiently increasing the number of cores under a power envelope.*

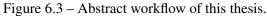

**Process variation.** Unfortunately, NTV optimization comes at the cost of exacerbated process variations (Kaul et al., 2012; Karpuzcu et al., 2012) that must be tackled before chip deployment. Process variations are raised by fabrication effects (e.g., due to lithography imperfections), which lead to delay and static power deviations from the intended design goals (KARPUZCU; KIM; TORRELLAS, 2013; Kaul et al., 2012; PINCK-NEY et al., 2012). If no countermeasures are taken, such unwanted parameter fluctuations can hinder performance (e.g., if variation affects the critical path, effectively hampering achievable frequency), power, and energy efficiency (PINCKNEY et al., 2012). Specially, variation-induced power overheads beyond the required power limits can degrade yield, as a fraction of the assembled chips will not comply with the application requirements, possibly having to be discarded due to excessive leakage (Borkar et al., 2003). We augment our DSE methodology with process variation models and propose a combination of design-time and post-design-time approaches to provide chip designs to mitigate the discussed variation issues.

#### **1.2** Contributions of this Thesis

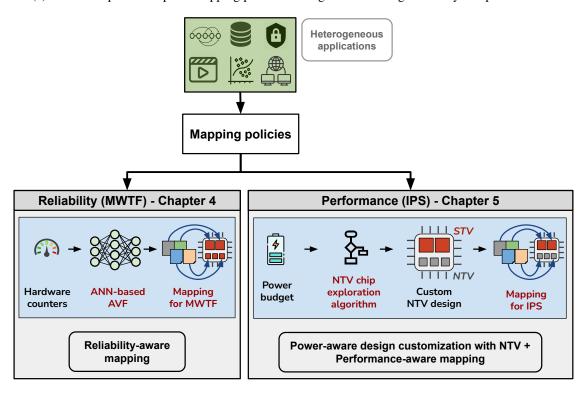

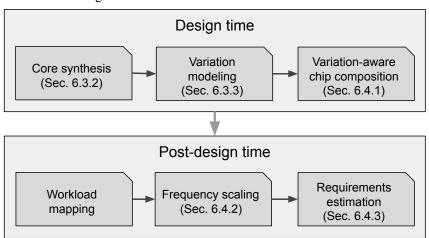

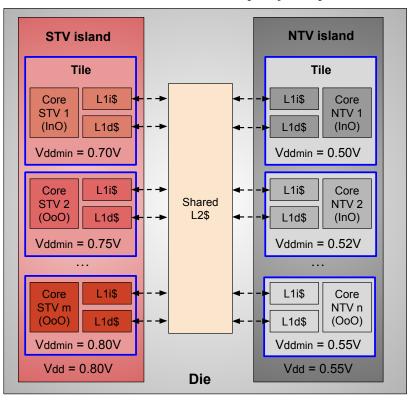

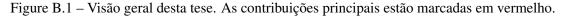

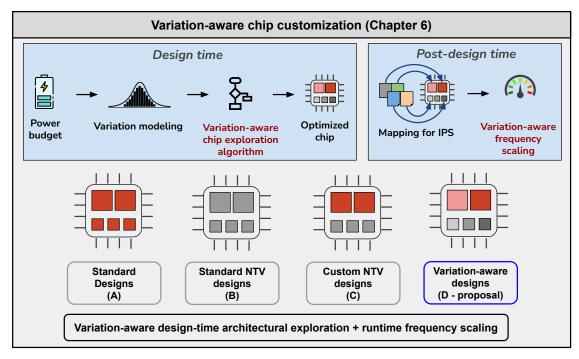

An outline of this thesis's workflow and contributions is shown in Fig. 1.2. The thesis is divided into three phases addressing different concerns in the scope of heterogeneous multicores for the edge domain. First, in Chapter 4, we propose a transparent mapping solution aiming at improving reliability in the context of heterogeneous multicores. Secondly, in Chapter 5, we propose a design methodology to improve performance and energy efficiency, under strict power limits, of heterogeneous multicores applicable to low-power edge scenarios. Finally, in Chapter 6, we augment our chip design methodology to address process variations and propose a two-step approach (design- and post-design time) that provides customized and more efficient chips that improve performance, energy efficiency, and yield under a power envelope and process variation contexts. The contributions are described in the following sections.

#### **1.2.1 Contribution 1: Reliability-Oriented Mapping Solutions**

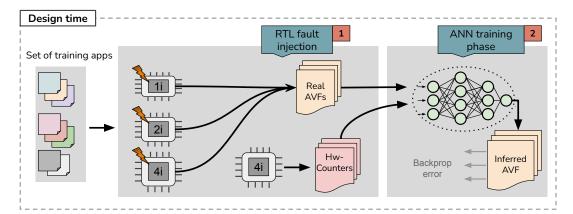

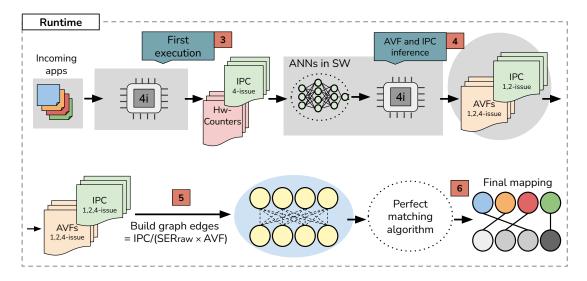

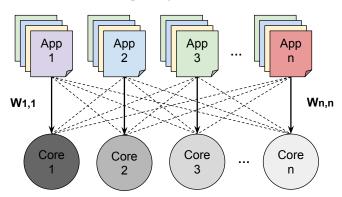

In this part, we leverage core-level heterogeneity from microarchitectural resources to perform proper workload mappings to the most suitable core type to maximize reliability. This is shown in Fig. 1.2a (left block). Our proposal consists in adopting a learningbased and automatic solution for efficient mappings to maximize the reliability of the system in terms of Mean Workload to Failure (MWTF) on heterogeneous multicores. Here, we perform runtime monitoring of application-dependent core pipeline utilization with hardware counters and train an Artificial Neural Network (ANN) to estimate the core's Architectural Vulnerability Factors (or AVF) from the hardware counters' data. We then perform near-to-optimal AVF-oriented application mappings to heterogeneous cores aiming at maximizing the chip-level system's MWTF;

Figure 1.2 – Thesis outline. The contributions of this thesis are highlighted in red. (a) In the first part we explore mapping policies aiming at maximizing reliability and performance.

(b) The second part aims to compose energy efficient and variation-aware chip designs with NTV.

# **1.2.2** Contribution 2: Efficient use of NTV for Improved Performance and Energy Efficiency

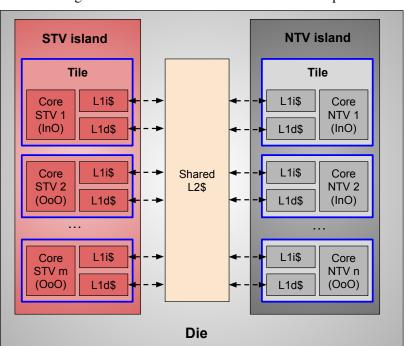

In the second part, in Fig. 1.2a (right block), we propose an efficient DSE methodology for composing micro-architecturally heterogeneous multicores under a domainspecific power envelope. We additionally propose a method for selective NTV, where only an efficiently selected set of the cores that compose the chip operate at NTV. This results in a chip comprising two voltage islands, accommodating both NTV and conventional core designs in the same die, with improved energy efficiency and performance under a power limit. At runtime, we combine the chip customization method with runtime application mappings to increase task-level instruction throughput. This renders chips with maximized Instructions Per Second (IPS) and minimal power slacks under the power envelope.

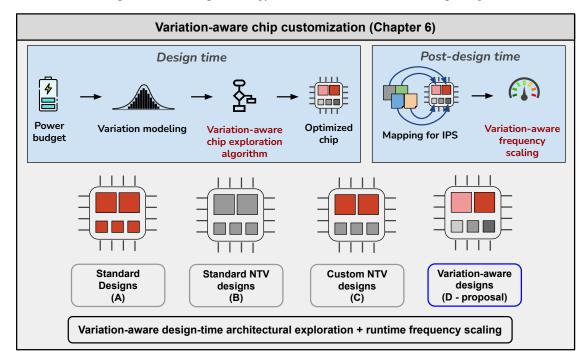

#### **1.2.3 Contribution 3: Addressing Process Variations**

In this part of the thesis, we augment our DSE methodology for partial NTV and propose a variation-aware chip exploration methodology to compose power-constrained chips subject to process variation scenarios. This part is shown in Fig. 1.2b. First, we propose a sampling-based and variation-aware strategy during the design stage to select optimized chip configurations with variation-aware and selective NTV. Secondly, we propose a frequency adaptation mechanism in the post-design time to further cope with variations. Combining both design- and post-design steps provides IPS-optimized and power-aware configurations while maintaining minimum yield requirements.

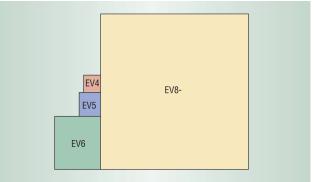

Our procedure relies on exploring heterogeneous multicore designs with varying microarchitecture cores. For example, a combination of performance-oriented cores plus low-power cores results in improved chip-level energy efficiency. Four abstract heterogeneous chip design cases are shown in Fig. 1.2b (the A-D designs, bottom part). The designs are (**A**) standard designs that rely on a single (conventional) and safe voltage setting suitable for frequencies at the Giga-Hertz level; (**B**) conventional NTV designs that allocate a single NTV voltage level to all cores in the chip, at low frequencies at the Mega-Hertz level; (**C**) custom architectures that efficiently combines both STV and NTV cores in the same chip; and (**D**), our proposed variation-aware chip composed of STV and NTV cores.

This contribution consists of providing customized chip configurations following the **D** paradigm, as it is suitable to improve performance and energy efficiency at lowpower scenarios while maintaining minimum yield requirements under process variations constraints.

## 1.3 Structure of this Document

This work is structured as follows:

- Chapter 2: Provides background information on microprocessor reliability, Near-Threshold Computing, and its associated process variation challenges. We also briefly discuss the emergence and importance of heterogeneous systems and the toolchain adopted to develop this work;

- Chapter 3: Highlights previous works on microprocessor reliability improvement proposals, as well as previous approaches to mitigate process variations in the context of NTV and conventional designs;

- Chapter 4: Details our proposal for improved reliability on heterogeneous systems;

- Chapter 5: Details our NTV proposal for improved performance and energy efficiency of low-power heterogeneous systems applicable to the edge;

- Chapter 6: Details our approach for variation-aware and low-power chip designs applicable to the edge;

- Chapter 7: Highlights the main conclusions of the chapters 4, 5, and 6;

- Appendix A: Provides details on the explored core configurations and the evaluated application scenarios;

- Appendix B: Summarizes this work in Portuguese (required).

### **2 BACKGROUND**

This chapter provides background information on key concepts such as basics on transistor behavior and sources of power dissipation (Sec. 2.1), NTV and the associated process variations and reliability issues (Sec. 2.3), current state-of-the-art heterogeneous systems (Sec. 2.4) as well as a brief discussion on an open source framework (*Chipyard*) we adopted to explore heterogeneous systems design (Sec. 2.5).

#### 2.1 Sources of Power Consumption and Optimization Methods

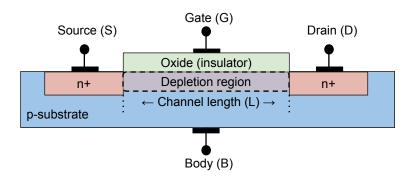

The Complementary Metal Oxide Semiconductor (CMOS) technology is the building block for the implementation of digital logic. The CMOS logic relies on a specific arrangement of Metal-Oxide-Semiconductor Field Effect Transistor (MOSFET) to construct logic gates. Such transistors are considered the most widely manufactured device in history (HANDY, 2014) mainly due to their low power consumption and scalability properties. As an example, Fig. 2.1 depicts the high-level view of an NMOS transistor, which consists of three main terminals: source (S), gate (G), and drain (D). Different modes of operation are achieved depending on the relationship between the voltages applied to the terminals and the threshold voltage ( $V_{th}$ ). Three regions of operation are possible:

- Sub-threshold region: when V<sub>gs</sub> < V<sub>th</sub> and hence there is no channel formed between source and drain. Even though the transistor is considered off in this region, there is drain-to-source *leakage* current (I<sub>ds</sub>) flowing according to Eq. 2.1 (RABAEY, 1995).

- Linear region: when  $V_{gs} > V_{th}$  and  $V_{ds} < V_{gs} V_{th}$ . A channel is formed between the source and drain (depletion region). In this region, the I<sub>ds</sub> current depends on the drain voltage, and the transistor behaves like a resistor that can be controlled by  $V_{gs}$ .

- Saturation region: when  $V_{gs} > V_{th}$  and  $V_{ds} > V_{gs} V_{th}$ . A channel is formed between the source and drain (depletion region), but the I<sub>ds</sub> current saturates and does not depend on the drain voltage.

Notice in Eq. 2.1 that in the sub-threshold region, the leakage current depends exponentially on  $V_{ds}$ ,  $V_{gs}$ ,  $V_{th}$  and the thermal voltage (V<sub>T</sub>). The leakage current is also sensitive to transistors' parameters, such as the gate length (L), width (W), and tempera-

ture.

$$I_{ds} = I_0 \frac{W}{L} e^{\frac{V_{gs} - V_{th}}{nV_T}} (1 - e^{-\frac{V_{ds}}{V_T}}), V_T \propto Temp$$

(2.1)

The gate delay can be modeled in high-level as shown in Eq. 2.2 (RABAEY, 1995), which is the time taken for a signal to propagate from the gate input to its output. For a CMOS inverter, for example, the delay is defined as the time the output takes to reach  $V_{dd}/2$  (low to high - LH) after the input reaches  $V_{dd}/2$  (high to low - HL).

$$t_{p,LH} \approx kC \frac{V_{dd}}{I_{ds}^{PMOS}}, t_{p,HL} \approx kC \frac{V_{dd}}{I_{ds}^{NMOS}}$$

(2.2)

In the equation, k is a fitting parameter, and C is the gate output capacitance. The gate delay determines the maximum frequency (f) for the gate.

Logic gates dissipate static and dynamic power. Dynamic power dissipation is caused by input transitions that lead the gate outputs to toggle, and is calculated as  $P_{dyn} = Cf\alpha V_{dd}^2$ , where  $\alpha$  is the application-dependent switching activity (i.e., probability of state transition). Static power happens due to leakage current, which can be expressed as  $P_{leak} = I_{leak}V_{dd}$ , where  $I_{leak}$  is determined by Eq. 2.1. The total power consumption for generic gates can then be expressed as  $P = P_{dyn} + P_{leak}$ , which influences the energy and energy efficiency of the circuit for a given performance target.

Optimizing power consumption is essential to increase both energy and thermal efficiency, which is relevant for cloud servers, desktop computers, and edge devices. However, keeping low power consumption for edge devices is crucial due to 1) battery dependence (needs energy efficiency) and 2) restricted temperature (needs thermal efficiency), which raises cooling challenges for portable devices, for instance. Over the years, many low-power and/or energy efficiency optimization strategies have been proposed across different layers, such as clock or power gating (PEDRAM, 1996), Dynamic

Voltage and Frequency Scaling (DVFS) (BURD et al., 2000; SEMERARO et al., 2002), approximate computing at various distinct layers (MITTAL, 2016), aggressive voltage underscaling with NTV (Kaul et al., 2012), and system-level strategies such as the adoption of application-specific accelerators and heterogeneous cores such as the ARM's DynamIQ (ARM, 2021).

In this work, we explore optimization strategies by adopting NTV applied to heterogeneous systems. We justify the adoption of NTV due to its increased energy efficiency improvements and also as an aggressive power capping method. When compared to conventional STV designs, NTV provides improved energy efficiency as the most energyefficient voltage point is known to be close to the transistor's threshold voltage (Dreslinski et al., 2010; Markovic et al., 2010); thus, NTV provides more aggressive power reduction and increased energy efficiency when compared to standard DVFS approaches at conventional voltage levels, e.g., (Dighe et al., 2011; RAGHUNATHAN et al., 2013; Teodorescu; Torrellas, 2008), mostly because NTV is suited to reduce both dynamic and static power dissipation.

Moreover, given the widespread and firm adoption of heterogeneous systems in commercial devices, we also consider NTV in conjunction with proper application mapping to better exploit the heterogeneity of cores and applications so that better applicationto-core affinities are exploited to increase performance further. The next section briefly introduces NTV concepts and the associated design challenges.

#### 2.2 Radiation-Induced Soft Errors and Fault Tolerance Concepts

Radiation-induced soft errors, mostly in the form of Single-Event Upset (SEU), may occur when energized particles (e.g., from cosmic rays or alpha particles from decaying materials) hit a transistor and flips the value of the stored bit (flip-flops or SRAM cells) (MITRA et al., 2014; HENKEL et al., 2013). The soft error rate is strongly dependent on the transistor's critical charge (the minimum charge required to invert the bit state), which in turn depends on  $V_{dd}$  (JAHINUZZAMAN; SHARIFKHANI; SACHDEV, 2009).

To measure the susceptibility of application failures due to soft errors, the authors in (MUKHERJEE et al., 2003) have introduced the concept of Architectural Vulnerability Factor (AVF) as the conditional probability of system failure given that a bit-flip occurred in the microprocessor. The AVF depends on the fraction of bits in the processor that are required for the correct execution of the application, called Architectural Correct Execution bits (or ACE bits). The fraction of ACE bits is directly related to the degree of useful *occupancy* of each internal structure in the processor's pipeline, which is determined by complex correlations between several microarchitectural factors and applications' characteristics that can change the residence times of useful bits in the structures (MUKHERJEE et al., 2003; WALCOTT; HUMPHREYS; GURUMURTHI, 2007). For instance, a microprocessor with good branch prediction accuracy and too much memory stalls due to cache misses will tend to fill up the processor's internal structures with useful data, increasing the occupancy (or degree of utilization) of the structures and consequently making it more vulnerable to bit-flips.

Standard resiliency analysis to investigate fault tolerance levels requires measuring the processor's AVF, which is determined by estimating the fraction of ACE bits in the processor's pipeline for distinct applications. A common approach to identify the fraction of ACE bits in processors is termed *ACE analysis*, which consists in monitoring the application's instruction trace and gathering instruction-level metrics (such as ISA register utilization) with high-level simulators. This method, however, is well-known for providing overly pessimistic vulnerability factors (WANG; MAHESRI; PATEL, 2007; GEORGE et al., 2010). In order to avoid the limitations of ACE analysis or the adoption of highlevel simulations that do not provide hardware details, we measure the AVF through fault injections at RTL, gathering more realistic (and less conservative) AVF estimations.

The raw Soft Error Rate (SER) of a system is the rate of raw/total soft errors experienced by the chip (e.g., how many bits are flipped per unit of time in the circuit), and it is commonly expressed as the raw FIT rate (Failures in Time) - the number of raw errors experienced in 1 billion hours of operation. This error rate depends on manufacturing parameters (e.g., transistor sensitivity due to the critical charge and voltage of operation), environmental conditions (e.g., radiation due to proximity to alpha-decaying materials or space applications exposed to high levels of cosmic rays), and silicon area exposed to soft errors. Therefore, SER is proportional to the core's area and the circuit technology. Notice that the raw SER does not determine the frequency of errors that lead to actual failures, as most of such errors are masked at different layers such as circuit-level, microarchitecturallevel, or even application-level masking factors. The *effective* SER is the rate of errors that actually lead to system failures, which is measured by *derating* the raw SER by the AVF/derating factor ( $SER_{effective} = SER_{raw} \times AVF$ ).

While the AVF is a satisfactory metric for estimating the probability of failures in

the presence of bit-flips in the processor, more than such a metric is needed to evaluate the fault tolerance of heterogeneous systems in which application mapping strategies influence both AVF and performance. For example, larger cores may execute the workload faster, but they also have higher SER (due to larger area) and application-dependent AVF. The AVF metric does not capture all information on the effects of resilience across different application mappings because mappings affect both AVF and performance. Hence, only considering the AVF as a vulnerability metric in the context of heterogeneous cores with varying performance will likely be misleading in this scenario. To account for that, the resilience metric we consider in this work is the Mean Workload to Failure (MWTF) (REIS et al., 2005), defined in Eq. 2.3, because it accounts for both the AVF and workload execution time, which are affected by application mapping. Higher MWTF means more computation is completed before the next system failure, which can be achieved by adopting proper mapping solutions to heterogeneous cores.

$$MWTF = \frac{amount \ of \ workloads \ computed}{number \ of \ errors \ encountered}$$

$$= (SER_{raw} \times AVF \times execution \ time)^{-1}$$

(2.3)

#### 2.3 Near-Threshold Voltage Computing

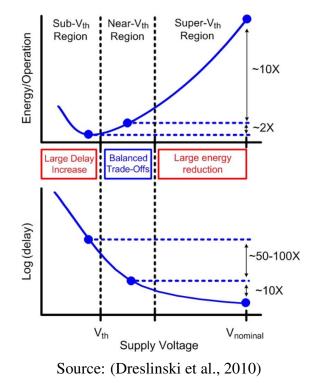

Near-Threshold Voltage (NTV), in contrast to the conventional Super-Threshold Voltage (STV), consists in operating the circuit at a voltage very close to the threshold voltage level ( $V_{th}$ ) to achieve aggressive power reduction at the cost of frequency degradation (Dreslinski et al., 2010; Chang et al., 2010; Markovic et al., 2010). NTV provides reduced dynamic power dissipation due to the quadratic dependence on  $V_{dd}$  and reduced static power dissipation (linearly or exponentially, depending on the transistors' region of operation).

Ideally, the NTV power reduction is aggressive enough to cover the frequency degradation, which is usually achieved by increasing the chip-level parallelism under a power envelope. For instance, by increasing the number of cores, or processing elements in general, NTV designs provide improved energy efficiency, as shown in Fig. 2.2. However, the energy efficiency gains stop at some point near the sub-threshold region because at this point the drain-to-source current depends exponentially on  $V_{dd}$ , which brings about orders of magnitude of frequency degradation due to the increased transistor delay.

Figure 2.2 – Potential reduction in the energy required per operation for different supply voltage levels, and the corresponding impact in the transistor delay.

Unfortunately, a secondary and unwanted effect of NTV is the increased susceptibility to parametric variations (i.e., deviations from the nominal values) that arises due to Process Variations (PV). PV is already a known issue at STV (Bowman; Duvall; Meindl, 2002; Fu; Li; Fortes, 2009; Dighe et al., 2011). At NTV, however, PV effects become more pronounced, up to 20 times higher when compared to conventional STV regime (Markovic et al., 2010).

Process variations (die-to-die and within-die variations) manifest mostly through deviations in the transistors'  $V_{th}$  and effective channel length ( $L_{eff}$ ), which are mostly attributed to design-time effects such as *systematic effects* (due to lithographic imperfections) and *random effects* (due to variable doping concentrations). At runtime, PV can also be affected by aging, voltage, and temperature (Bowman; Duvall; Meindl, 2002; Fu; Li; Fortes, 2009; Karpuzcu et al., 2012; Karpuzcu et al., 2013). Consequently, parametric variations affect both transistor's delay and leakage current, possibly shifting the optimal voltage point, the voltage point that yields the best energy efficiency, to a value higher than the ideal/PV-free circuit (PINCKNEY et al., 2012).

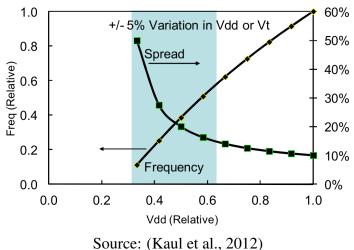

For a circuit operating at NTV, a small variation in the supply voltage results in a large change in the transistor delay, hence influencing the frequency of operation. Fig. 2.3 depicts the relative frequency of operation and frequency variation (measured by dividing

Figure 2.3 – Frequency spread (right axis) as a function of  $V_{dd}/V_{th}$  variation.

the standard deviation of frequency by the average frequency of sampled circuits in a die, or  $\sigma/\mu$ ) as a function of supply voltage. Near the NTV region, even a small variation in supply voltage or  $V_{th}$  may result in up to 50%

To further elucidate why variation is accentuated at NTV, an accurate model for current and delay near the threshold region is necessary. For that, current and delay formulas for the NTV region are derived according to the *EKV model* (ENZ; KRUMME-NACHER; VITTOZ, 1995; Markovic et al., 2010), according to the Eq. 2.4 and 2.5, respectively, which cover all regions of operation.

$$I = \frac{\mu}{L_{eff}} \times n \times vt^2 \times ln^2 (e^{\frac{V_{gs} - V_{th}}{2 \times n \times vt}} + 1)$$

(2.4)

$$delay_{gate} \propto \frac{V_{dd} \times L_{eff}}{\mu \times n \times vt^2 \times ln^2 (e^{\frac{V_{gs} - V_{th}}{2 \times n \times vt}} + 1)}$$

(2.5)

In the equations above,  $\mu$  represents the carrier mobility, vt is the thermal voltage, and n is a process-dependent parameter that relies on sub-threshold characteristics.

The equations show the strong dependence of the gate delay on both  $V_{th}$  and  $L_{eff}$ . For a multicore setting with variations in such parameters, for example, if a given design decision relies on the slowest core to determine the frequency of operation, which is a conventional design strategy while not addressing the variation issues, then the core-tocore delay variations translate into different  $V_{opt}$  points for different cores. Therefore, corner-based optimizations, in which the slowest core determines the frequency, yield a sub-optimal energy efficiency solution (Zhai et al., 2007; Karpuzcu et al., 2013) as different cores have different optimal voltage settings. We elucidate other approaches to address process variation in Sec. 3.2.

#### **2.3.1 Timing Failures**

Timing failures occur in both combinational and sequential circuits. If a combinational path is too slow to process the inputs for the designed clock frequency (due to unaddressed variation issues), timing failures may arise in the output of the circuit due to timing violations (i.e., the frequency of operation is too high for the combinational (variation-afflicted) path) (Ernst et al., 2004). Secondly, sequential circuits with conventional 6T SRAMs cells, for example, variations can cause both read, write and hold failures due to the tight timing margins of operation because the access transistors of such cells impose conflicting timing requirements (for read and write operations) as such cells are designed to be small to achieve high bit density (Karpuzcu et al., 2012).

#### 2.4 State-of-the-Art Heterogeneous Architectures

The need to improve compute performance under restricted power budgets has raised many architectural challenges, and the emergence of heterogeneous systems is one leading way to address such issues. Single-ISA heterogeneous (or asymmetric) systems are any form of multi-core MPSoC composed of cores with varying microarchitectural properties, but all implementing a unique Instruction Set Architecture (ISA) specification. Fig. 2.4 depicts a high-level view of a multi-core processor comprising different cores implementing the Alpha ISA. Such architectures were first proposed aiming at reduced power consumption (KUMAR et al., 2003), and later to improve multi-threaded or

Figure 2.4 – An Alpha (single-ISA) heterogeneous chip.

Source: (KUMAR et al., 2005)

| sinartphone companies. |                                                              |                                                                            |                                               |

|------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------|

|                        | Apple<br>A14 Bionic                                          | Qualcomm<br>Snapdragon 865                                                 | Samsung<br>Exynos 990                         |

| Cores                  | 2x Firestorm<br>(Big cores)<br>4x Icestorm<br>(Little cores) | 1x Cortex A77 @ 3.1GHz<br>3x Cortex-A77 @ 2.4GHz<br>4x Cortex-A55 @ 1.8GHz | 2x Mongoose<br>2x Cortex-A76<br>4x Cortex-A55 |

| GPU                    | 4 core (Apple in-house design)                               | Adreno 650                                                                 | Mali-G77<br>11 cores                          |

| AI DSP                 | 16-core Neural Engine                                        | Hexagon 698 DSP +<br>Tensor Accelerator                                    | Dual-core NPU +<br>DSP                        |

| Process                | 5nm                                                          | 7nm EUV                                                                    | 7nm EUV                                       |

|                        |                                                              |                                                                            |                                               |

Table 2.1 – Some examples of popular commercial heterogeneous MPSoCs from three leading smartphone companies.

Source: (Triggs, Robert, 2021)

multi-program workload performance (KUMAR et al., 2004; KUMAR et al., 2005). The critical insight of such architectures is that application heterogeneity can be leveraged by providing the opportunity to effectively match application characteristics to the best core for a given requirement (e.g., performance or power). An example is mapping high-ILP applications to larger cores (with higher achievable IPC), and low-ILP applications to smaller cores that provide better energy efficiency.

Such architectures' effectiveness has led companies to move from the traditional homogeneous multicore settings to heterogeneous multicores. Specifically, the most no-table technology companies like Samsung, Qualcomm, and Apple rely on heterogeneous MPSoCs to better accommodate application performance while keeping acceptable power consumption. For example, Samsung and Qualcomm rely on the ARM's DynamIQ technology (ARM, 2021) for the Exynos and Snapdragon MPSoCs series, respectively, which represent most MPSoCs used in mobile phones. Tab. 2.1 showcases three examples of commercial chipsets from Apple, Qualcomm, and Samsung. Most modern chips are highly heterogeneous systems composed of a cluster of different core configurations, Graphics Processing Unit (GPU), Digital Signal Processor (DSP), and a dedicated AI engine for emerging ML applications (most commonly for neural networks).

The ARM's big.LITTLE architecture was the first implemented in a commercial mobile MPSoC, which later evolved to the more flexible and efficient DynamIQ technology (ARM, 2021). Among others, DynamIQ incorporates key architectural innovations such as:

• Flexible configurations of up to eight cores. Standard configurations include up

to three different cores (big, medium, and small cores) to meet both performance, energy, and thermal efficiency goals of diverging applications;

- All cores reside in a single cluster with a coherent and shared memory. This facilitates task migration between cores through the shared memory and reduces memory traffic of shared data between different cores, increasing the performance and energy efficiency;

- Independent voltage and frequency domains for each core to tune power/performance, allowing for fine-grained DVFS to scale performance and power up or down, according to the tasks' needs;

- Enhanced power features that reduce the latency to transition between power states (i.e., ON, OFF, and SLEEP states supported by the Cortex-A series);

- An Energy Aware Scheduler (EAS) that provides fast and efficient task migration to facilitate the software-to-core mapping, providing more intelligent power and performance management.