# A New Adaptive Analog Test and Diagnosis System

Érika F. Cota, Marcelo Negreiros, Luigi Carro, and Marcelo Lubaszewski

Abstract—This paper presents a low-cost analog test system with diagnosis capabilities. The tester is able to detect faults in any linear circuit by learning a reference circuit behavior in a first step, and comparing this behavior against the output of the circuit under test in a second step. For a faulty circuit, a third step takes place to locate the fault. The diagnosis method consists on injecting probable faults in a mathematical model of the circuit, and later comparing its output with the output of the real faulty circuit. This system has been successfully applied to a case study, a biquad filter. Soft, large, and hard deviations on components, as well as faults in operational amplifiers, were considered. Experimental results have proven the feasibility and efficiency of the proposed test and diagnosis system.

Index Terms—Adaptive filters, adaptive systems, analog system fault diagnosis, circuit testing, testing.

#### I. INTRODUCTION

▶ HE market for analog and mixed-signal circuits continues to grow very fast. Although many challenges still exist regarding design aspects, testing these devices has proven to be a major bottleneck in electronics production. The main problems to test an analog device come from poor observability and controllability of nodes, from the inherent complexity of these circuits and from the lack of a common design feature that could be used in a generic test method. Different searching processes exist today that aim at identifying those test stimuli that can minimize testing time, maximize fault coverage, or both. For example, sensitivity analysis is used in [1] in order to find the input frequencies that maximize the error output for every kind of fault in a component (soft, large, and hard faults). If diagnosis is not a concern, the individual frequency subsets can be merged together, in such a way that a smaller set of test stimuli is obtained. [2] also applies sensitivity analysis to analog circuits, but generates a minimal subset of input-parameter pairs that simultaneously maximizes fault detection and fault diagnosis. Other existing test generation techniques are ad-hoc methods, thus devoted to specific circuit classes (see, for example, [3]).

Besides testing, fault diagnosis becomes especially important for prototype debugging, and is also useful during the circuit lifetime, whenever repair is possible. Nevertheless, the analog diagnosis problem can be very hard to solve, since many faults may produce an identical behavior at the circuit outputs. In terms of analog diagnosis, existing tools follow two basic approaches [4]: Simulation Before Test (SBT) and Simulation After Test (SAT). In the SBT method, the design is analyzed before testing, and the output of a faulty circuit is

Manuscript received May 26, 1999; revised November 25, 1999.

The authors are with the Electrical Engineering Department-Universidade Federal do Rio Grande do Sul, CEP 90035-190, Porto Alegre RS, Brazil (e-mail: luba@iee.ufrgs.br; negreiro@iee.ufrgs.br).

Publisher Item Identifier S 0018-9456(00)02422-0.

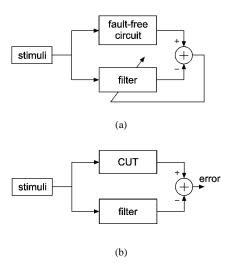

Fig. 1. Adaptive tester. (a) Learning phase. (b) Testing phase.

stored in a fault dictionary. Thus, if a fault is detected, it can be located by matching the actual result against the dictionary. For instance, [5] proposes a tool based on the SBT method. In the SAT approach, on the other hand, a mathematical analysis is only performed after a fault is detected. Conventional SAT approaches make this mathematical analysis based on diagnosis equations [4].

Within this context, this work faces the problem of efficiently testing and diagnosing faults in analog circuits. Its main goal is to achieve high fault coverages and low test application times, while keeping the cost of automatic test equipments affordable. In this paper, a complete test and diagnosis system for linear analog circuits is presented, that is based on adaptive algorithms.

### II. ADAPTIVE TESTER

In the proposed approach, the output of the circuit under test (CUT) is observed and compared to the expected output. Although the CUT is analog, the comparison is developed in the digital domain by means of an adaptive filter [6]-[8] (Fig. 1). The filter duplicates the behavior of the analog circuit during a learning phase [Fig. 1(a)], creating a circuit model. This model may also be constructed based on the design, using filter coefficients generated by any mathematical tool (Matlab, Mathcad, etc). The comparison is made during the testing phase [Fig. 1(b)], where the filter is used as the reference circuit and the error signal is measured. This error signal increases if the two systems are different. A threshold can be defined for an acceptable mismatch [9]. Note that in the first step (learning phase), the filter is trained with white noise. Since this kind of stimulus comprises all frequencies in a range, a specific set of frequencies is not necessary during testing time. It is worth mentioning that not only component faults, but also faults in

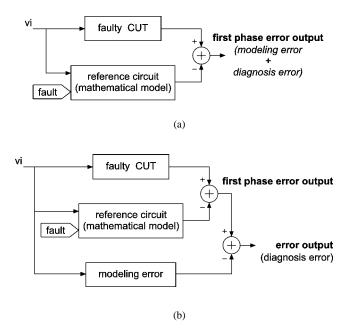

Fig. 2. Diagnosis Model. (a) Fundamentals of the diagnosis method (b) Practical diagnosis scheme.

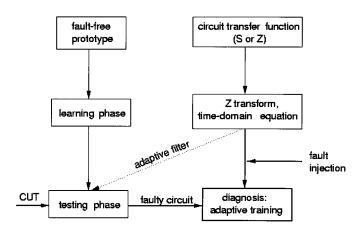

Fig. 3. Complete test and diagnosis system.

operational amplifiers (opamps) can be checked. Any deviation from the opamp ideal function will be recorded as another pole-zero signature in the s or z domains. Any fault present in the operational amplifier will change this analog signature and, as a consequence, will be detected [9].

#### III. ADAPTIVE DIAGNOSIS

The diagnosis procedure in use, shown in Fig. 2, belongs to the class of SAT (simulation after test) methods for analog circuits. As denoted in Fig. 3, after a fault is detected, a third step is added to the adaptive tester, aiming at the identification of the faulty component (*adaptive training*). The basic diagnosis mechanism [Fig. 2(a)] consists on injecting faults into a *reference circuit* (fault-free mathematical model) and on comparing its output against the output of the faulty CUT. When a match is found, then a component which may have caused the failure is identified. The tester proposed in this paper implements this mechanism also in the digital domain, where fault injection can be easily achieved in a fast and economical way.

The mathematical model is a Z-transform, obtained automatically from the circuit transfer function [10]. The Z-transform brings the analog circuit to the digital domain, where fault injection can be easily accomplished. For example, changing the nominal value of a capacitor by 10% can be achieved by simply modifying the coefficients of the digital filter in Fig. 1. The idea is then to inject faults in the Z-transform domain and evaluate the difference to the behavior of the circuit under test [Fig. 2(a)].

When the fault injected into the mathematical model is the same fault that affects the real circuit, then the two circuits will present a very close behavior. Therefore, when the error output in Fig. 2(a) is minimal, a possible fault location is identified, since the algorithm is tracking the components into which faults are injected.

It was noticed, however, that there is an intrinsic difference between the real circuit and its mathematical model. This difference varies according to the fault, and it exists even for a fault-free circuit and the ideal model. One of the reasons for this disagreement is that the physical circuit uses non-ideal components, like resistors with 5% tolerance and capacitors with 10% tolerance, for example. Moreover, the A/D converter used to bring information from the analog to the digital world also introduces some phase distortion. Because of this, a new step is necessary before the diagnosis phase takes place. It consists on learning the difference between the real and the ideal circuits by using another adaptive filter, [Fig. 2(b)].

At first, a learning procedure must be performed for the fault-free circuit, in order to generate the modeling error. This is the error component associated to the differences between the fault-free circuit model and the real world implementation. This error is obtained in a scheme like Fig. 1(b) where the CUT is a fault-free real circuit implementation. When comparing the faulty circuit with its model a first phase error output comes out [Fig. 2(a)]. This signal embodies both the modeling error and the difference between the faulty circuit and the mathematical model into which the fault was injected (diagnosis error). Then, in order to have only the information about the injected fault, modeling error must be subtracted from this first result in the real procedure [Fig. 2(b)]. Now, when the mathematical model has the same fault as the faulty CUT, diagnosis error is very close to zero, making the first phase error output very close to modeling error. This way, when error output value is minimal in Fig. 2(b), the fault is located. Fig. 3 shows the complete test and diagnosis system.

### IV. PRACTICAL EXPERIMENTS

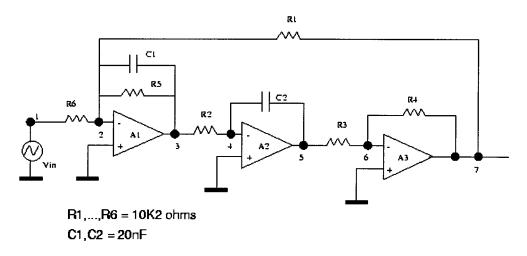

In order to illustrate the versatility of the proposed methodology, several fault detection and fault diagnosis experiments were carried out using a biquad. The biquad filter is shown in Fig. 4, and was built using discrete components.

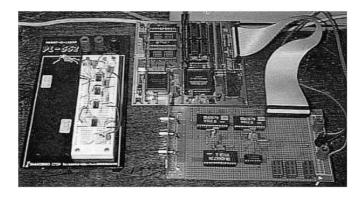

In the adaptive tester, a PC embedding a DSP board with an analog interface (16 bits resolution, with reconstruction filters) has been used as the test signal generator, and a TMSC25 board with an A/D converter (14 bits) was the front-end testing system. A sampling frequency of 8 KHz per channel and a 48 taps Least Mean Square adaptive filter were used for this specific example.

Fig. 4. Biquad filter.

Fig. 5. Input signal, modeling error signal (fault-free circuit) and error output signal (for a 10% change in C2).

The C25 board samples the input and the output of the circuit. Since the analog interface has a multiplexed A/D converter, data is not sampled simultaneously. The output signal is generated from the C25 board using an 8-bit D/A converter. Note that all calculations used fixed-point arithmetic (16 bits).

### A. Fault Detection

In the case of the biquad, the proposed test methodology has proven very efficient, since even small component deviations could be detected. One should also mention that the test is inherently simple and fast: there is neither the need to predetermine a set of input frequencies, nor to check more than one test parameter, like gain, phase of intermediate nodes.

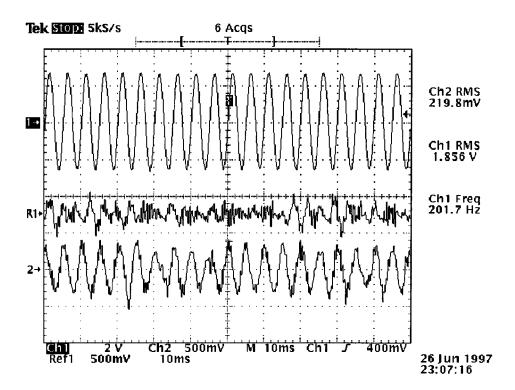

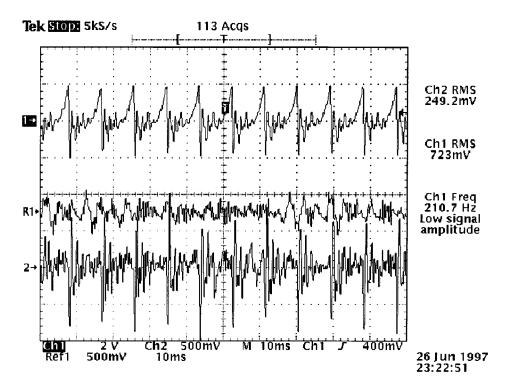

Fig. 5 shows the response of the system to a soft deviation (10%) of C2. In this case, the tester was trained using white noise, and the CUT tested with a sine wave test stimulus with arbitrarily values for frequency and amplitude. This example shows that any input frequency is able to detect faults, although the sensitivity of the error output can be smaller for some of them. Fig. 6 presents the response of the tester to a large fault (50% deviation) in C2. In this example, the testing signal is a voice signal, just to show the versatility of the method. Although some different input stimuli can be used during testing time, for test purposes the best input signal is white noise. The presence of all frequencies in this signal garantees the detection of a larger set of faults when compared to a pure sine wave single-frequency input.

Fig. 6. Input signal, modeling error signal (fault-free circuit) and error output signal (for a 50% deviation in C2).

TABLE I

TYPE OF FAULTS

AND DIAGNOSIS SUCCESS RATIO

| Component faults   | Diagnosis success ratio |

|--------------------|-------------------------|

| Soft (1%,5%,10%)   | 70.83%                  |

| Large (50%)        | 100%                    |

| Hard (short, open) | 50%                     |

| Altogether         | 71.43%                  |

#### B. Fault Diagnosis

In the diagnosis experiments, the *faulty CUT* of Fig. 2(a) was in fact replaced by the practical results obtained from the adaptive testing of the real circuit.

Table I summarizes the results obtained from MATLAB implementation of the algorithm, considering data extracted from the biquad filter. This table shows the diagnosis success ratio, that is, the percentage of fault experiments for which the diagnosis procedure has correctly found the faulty component. Forty-two different faults, among soft, large and hard deviations, were considered: 1%, 5%, 10%, and 50% component deviations, and all those component shorts and opens that did not saturate the CUT. Catastrophic faults leading to saturation make diagnosis impossible using the procedure described in the previous session. It is important to notice that the test engineer should define what is the accepted tolerance at the error output, since some circuits may have differences of a few percent between them and still be considered to be working correctly.

The results in Table I can be analysed as follows: similarly to previous approaches based on neural networks [11], [12], a very high success ratio was obtained for large component deviations. Unlike [11], the success ratios for soft and hard fault diagnosis have drastically dropped. This is mainly due to the

fact that we are measuring a single test parameter, the output voltage. In [11], four different test parameters are considered, thus a straight comparison would be unfair.

Additionally, the biquad transfer function was modified to make it possible to change the gain of the operational amplifiers. This way, faults that affect this parameter could be injected into the circuit model. Three large gain deviations were injected into the second operational amplifier of the CUT. Gains of 50, 100, and 1000 were considered, instead of an infinity gain (ideal case). All of them were successfully detected and located by the test and diagnosis system. This is another important contribution of this work, since operational amplifiers, although hard to test, are in general considered as black-boxes in existing test systems.

## V. CONCLUDING REMARKS

This paper has presented a low cost and efficient analog tester. This tester is based on a DSP board and on software tools used to detect faults and locate faulty components. The testing method is very robust, ensuring the detection of faults that range from minor component variations to large circuit changes caused by shorts or opens. The test methodology can be applied to any linear analog circuit that can be described by a transfer function in the s or in the s-plane.

This work has also presented an alternative diagnosis method for analog circuit testing. The method is based on adaptive testing and on fault injection into a mathematical model of the CUT. Its ability of classifying component faults is comparable to existing methods based on neural networks. Its main advantages are the extremely low time required for learning and diagnosing, and the location of faults even in operational amplifiers.

Fig. 7. Prototype of the test system.

A prototype was implemented and is shown in Fig. 7. The first results are very promising, although diagnosis of hard faults needs further investigation. Additionally, experimental results performed using a tester prototype have demonstrated that a low cost and time-efficient implementation can be achieved for both the fault detection and the fault diagnosis procedures.

#### REFERENCES

- [1] M. Slamani and B. Kaminska, "Multifrequency analysis of faults in analog circuits," *IEEE Design Test Comput.*, pp. 70–80, Summer 1995.

- [2] E. F. Cota, M. Lubaszewski, and E. Domênico, "A frequency-domain tool for test and diagnosis on analog circuits," *J. Brazilian Comput. Soc.*, *Special Issue on Fault-Tolerant Computing*, vol. 4, no. 2, pp. 5–15, Nov. 1997.

- [3] P. Caunegre and C. Abraham, "Fault simulation for mixed-signal systems," J. Electron. Testing: Theory Applicat., vol. 8, no. 2, pp. 143–152, Apr. 1996.

- [4] R. W. Liu, Testing and Diagnosis of Analog Circuits and Systems. New York: Van Nostrand, 1991.

- [5] S. Mir, M. Lubaszewski, and B. Courtois, "Fault-based ATPG for linear analog circuits with minimal size multifrequency test sets," *J. Electron. Testing: Theory Applicat.*, vol. 9, no. 1/2, pp. 43–57, Aug./Oct. 1996.

- [6] S. Haykin, Adaptive Filter Theory, 2nd. ed. Englewood Cliffs, NJ: Prentice-Hall, 1991, p. 854.

- [7] B. Widrow and S. D. Stearns, *Adaptive Signal Processing*. Englewood Cliffs, NJ: Prentice-Hall, 1985, p. 474.

- [8] J. G. Proakis and D. G. Manolakis, Introduction to Digital Signal Processing. New York: Macmillan, 1988, p. 944.

- [9] L. Carro and M. Negreiros, "Efficient analog test methodology based on adaptive algorithms," in *Proc. ACM/IEEE Design Automation Conf.*. Los Alamitos, CA: IEEE Computer Soc. Press, June 1998, pp. 32–37.

- [10] C.-T. Chen, System and Signal Analysis. Philadelphia, PA: Saunders, 1994, p. 705.

- [11] Z. R. Yang, M. Z. Zwolinski, and C. D. Chalk, "Fault detection and classification in analog integrated circuits using Robust heteroscedastic probabilistic neural networks," in *Proc. 4th Int. Mixed-Signal Testing Workshop*, June 1998, pp. 41–46.

- [12] R. Spina and S. Upadhyaya, "Linear circuit fault diagnosis using neuromorphic analysers," *IEEE Trans. Circuits Syst. II*, vol. 44, pp. 188–196, Mar. 1997.

Érika F. Cota received the computer science degree from Universidade Federal de Minas Gerais (UFMG), Brazil, in 1994 and the M.Sc. degree from Universidade Federal do Rio Grande do Sul (UFRGS), Brazil, in 1997, where she is currently pursuing the Ph.D. degree in the Computer Science Department.

From 1997 to 1999, she was with the Electrical Engineering Department at UFRGS as an Associate Researcher in the Prototyping and Testing Laboratory. Her main research topics are high level testing, de-

sign for testability, and test automation.

**Marcelo Negreiros** was born in Porto Alegre, Brazil, on Oct. 27, 1969. He received the electrical engineering degree in 1992 and the M.S. degree in engineering in 1994, both from the Federal University of Rio Grande do Sul (UFRGS), Brazil.

Since then, he has been working in the Electrical Engineering Department at UFRGS as an Associate Researcher in the Signal Processing Lab. (LaPSI). His areas of interest include digital signal processing, adaptive systems, and speech processing.

**Luigi Carro** was born in Porto Alegre, Brazil, in 1962. He received the electrical engineering degree, the M.Sc. degree, and the Ph.D. degree in computer science from Universidade Federal do Rio Grando do Sul (UFRGS), Brazil, in 1985, 1989, and 1996, respectively.

From 1989 to 1991, he was with ST-Microelectronics, Agrate, Italy, in the R&D group. He is presently a Lecturer at the Electrical Engineering Department of UFRGS, in charge of Digital Systems Design disciplines at the graduate and undergraduate

level. His primary research interests include mixed-signal design, digital signal processing, and fast system prototyping.

Marcelo Lubaszewski received the electrical engineering and the M.Sc. degrees from Universidade Federal do Rio Grande do Sul (UFRGS), Brazil, in 1986 and 1990 respectively. In 1994, he received the Ph.D. degree from the Institut National Polytechnique de Grenoble, France.

He is presently the Co-Head of the Electrical Engineering Department of UFRGS, where he lectures on microprocessor-based systems and on VLSI design and test. His primary research interests include mixed-signal and microsystems testing, synthesis for

testability, self-checking and fault-tolerant systems, and computer-aided testing. He has published over 100 technical papers in these topics.

Dr. Lubaszewski has served as General Chair or Program Chair of SBCCI, Symposium on Integrated Circuits and Systems Design, and of LATW, Latin American Test Workshop. He has also served as a member of the Organizing or the Program Committee of the VLSI Conference, the Mixed-Signal Testing Workshop, the Asian Test Symposium and the European Test Workshop.