## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

#### LEANDRO MAX DE LIMA SILVA

Implementação Física de Arquiteturas de Hardware para a Decodificação de Vídeo Digital Segundo o Padrão H.264/AVC

> Dissertação apresentada como requisito parcial para a obtenção do grau de Mestre em Ciência da Computação

Prof. Dr. Sergio Bampi Orientador

## CIP – CATALOGAÇÃO NA PUBLICAÇÃO

Silva, Leandro Max de Lima

Implementação Física de Arquiteturas de Hardware para a Decodificação de Vídeo Digital Segundo o Padrão H.264/AVC / Leandro Max de Lima Silva — Porto Alegre: Programa de Pós-Graduação em Computação, 2010.

136 f.:il.

Dissertação (mestrado) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação. Porto Alegre, BR – RS, 2010. Orientador: Sergio Bampi.

1.Fluxo ASIC (*standard-cells*). 2.Projeto de Circuitos Integrados Digitais. 3.Padrão H.264/AVC. 4.Codificação de Vídeo. 5.Microeletrônica. I. Bampi, Sergio. II. Título.

### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos Alexandre Netto

Vice-Reitor: Prof. Rui Vicente Oppermann

Pró-Reitor de Pós-Graduação: Prof. Aldo Bolten Lucion Diretor do Instituto de Informática: Prof. Flávio Rech Wagner

Coordenador do PPGC: Prof. Álvaro Freitas Moreira

Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

"The difference between a successful person and others is not a lack of strength, not a lack of knowledge, but rather a lack of will."

- Vincent T. Lombardi

"Knowing is not enough, we must apply. Willing is not enough, we must do."

- Johann von Goethe

"Perseverance is a great element of success. If you knock long enough and loud enough at the gate, you are sure to wake up somebody."

- Henry W. Longfellow

"To have striven, to have made the effort, to have been true to certain ideals - this alone is worth the struggle."

- William Penn

## **AGRADECIMENTOS**

Ingressar em um curso de mestrado não é uma tarefa fácil, e muito menos é concluílo. Para realizar esta conquista é necessário adquirir conhecimento, dedicar-se bastante, ter determinação e persistência para solucionar os problemas que aparentam ser insolúveis, e além de tudo isso, é necessário ter ajuda e colaboração de muitas pessoas. Assim, gostaria de aproveitar a oportunidade para agradecer a todos que de alguma forma contribuíram para com a minha formação e conclusão deste trabalho.

Primeiramente, quero agradecer à minha família, meus avôs, tios, meu irmão Fagner e principalmente aos meus pais, Cícero e Djanira, por terem sido sempre os maiores incentivadores em meus estudos e estarem sempre me apoiando em tudo que faço. Muito obrigado a vocês!

Gostaria de agradecer também à minha namorada, Paula Bodanese, e à sua família: Paulo, Solange e Bianca, por todo o apoio que me deram na cidade de Porto Alegre. À Paula, agradeço por todo o amor, carinho, amizade, atenção e compreensão durante o período de mestrado, em que o tempo era sempre curto e em que, muitas vezes, tive que abrir mão de ficar mais tempo com ela para poder estudar para uma prova, escrever um artigo ou executar uma das muitas atividades realizadas no decorrer do curso. Muito obrigado, linda!

Ao meu orientador, professor Dr. Sergio Bampi, pela aceitação como meu orientador de mestrado, por todas as conversas, conselhos, atenção despendida, confiança e principalmente apoio em diversas decisões tomadas no decorrer do mestrado. Obrigado, professor.

A todos os colegas e amigos(as) feitos durante o período de graduação na Universidade Federal de Campina Grande (UFCG). Entre eles: Henza Rafaela, Pedro Alysson, Vinícius Marques, Tomás de Barros, Halley Freitas e em especial aos camaradas George Silveira, Gustavo Antunes e Raphael Mattos, pela pareceria em tantas festas, forrós no parque do povo e conversas aleatórias em mesa de bar, atividades estas de convívio social que considero importantes para se ter uma visão crítica além das fronteiras da universidade e, consequentemente, poder lidar melhor com os vários tipos de adversidades que podem surgir sempre que se faz uma mudança na vida, como mudar de cidade, estado, iniciar um curso de mestrado e assim por diante.

Aos colegas do Laboratório de Arquiteturas Dedicadas (LAD-UFCG), em especial ao professor Elmar Melcher, pela ajuda na formação do conhecimento que me possibilitou enveredar por esta área de microeletrônica em que estou concluindo o mestrado.

Aos amigos e companheiros de moradia que fiz em Porto Alegre: Rômulo Calado, Flávio Santos, Rafael Cantalice, Alexandre Amaral, Alexandre Melo, William Alves,

Thiago Ló, Rogério Silva, Paulo Eduardo e Jair Fajardo, pela parceria nos churrascos e incontáveis baladas nos arredores da Cidade Baixa, as quais ajudavam a manter equilibrado o nível de *stress* adquirido durante a semana, quando as coisas não iam muito bem e a conclusão do trabalho parecia cada vez mais distante.

Gostaria de dizer muito obrigado aos integrantes do laboratório "lab215": Bruno Zatt, Cláudio Diniz, Vagner Rosa, Dieison Deprá, Leandro Zanetti, Marcelo Porto, Roger Porto, Fábio Ramos, Guilherme Mauch, Thaísa Leal, Débora Matos, Cristiano Thiele, André Martins, Guilherme Corrêa, Miklécio Costa e Franco Valdez, pela receptividade, churrascos, todo o apoio, troca de idéias e colaborações em diversos trabalhos ao longo do mestrado.

Também ao professor Altamiro Susin e aos integrantes do Laboratório de Processamento de Sinais e Imagens (LaPSI), em especial ao Alexsandro Bonatto e ao André Borin, pela colaboração direta com meu trabalho e ajuda na solução de diversos problemas encontrados durante o desenvolvimento.

A todos os colegas do curso de Formação de Projetistas de Circuitos Integrado (CI-Brasil/Cadence), pelas diversas dicas sobre engenharia e microeletrônica em sala de aula e pelas conversas sobre mercado de trabalho, economia, política e assuntos gerais às sextas-feiras, sempre quando apreciávamos um bom *chopp* no bar Pinguim ao final de uma semana puxada de treinamento. Um agradecimento especial aos colegas Marcos Hervé e Fábio Walter, com quem trabalhei diretamente em um dos times de desenvolvimento no treinamento e com quem tive a oportunidade de aprender bastante.

Aos funcionários do Núcleo de Suporte e Treinamento em EDA da UFRGS, o NSCAD, em especial ao Carlos Dorst e à Tatiana Costa, por todo o auxílio e suporte com as ferramentas que precisei utilizar nos servidores da UFRGS durante o mestrado.

A toda equipe do Instituto de Informática (INF) e do Programa de Pós-Graduação em Computação (PPGC) da Universidade Federal do Rio Grande do Sul (UFRGS), pelas palestras, infraestrutura, biblioteca, instalações gerais e boa vontade por parte dos funcionários.

Não poderia deixar de agradecer aos órgãos de fomento à pesquisa CNPq, FINEP e FAURGS, pelo auxílio financeiro recebido, sem o qual eu não teria como me manter estudando em regime de dedicação exclusiva ao longo deste trabalho.

Por fim, mas não menos importante, gostaria de agradecer a todos que não foram citados, mas que direta ou indiretamente contribuíram para o início e conclusão deste trabalho de mestrado.

A todos vocês, o meu muito obrigado!

# **SUMÁRIO**

| LISTA DE ABREVIATURAS E SIGLAS                                                                                                                                    | 11 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| LISTA DE FIGURAS                                                                                                                                                  | 15 |

| LISTA DE TABELAS                                                                                                                                                  | 17 |

| RESUMO                                                                                                                                                            | 19 |

| ABSTRACT                                                                                                                                                          | 21 |

| 1 INTRODUÇÃO                                                                                                                                                      | 23 |

| 1.1 Motivação e Objetivos                                                                                                                                         | 24 |

| 2 O PADRÃO H.264/AVC                                                                                                                                              | 27 |

| 2.1 Conceitos Básicos sobre Codificação de Vídeo                                                                                                                  | 27 |

| 2.2 Introdução ao Padrão H.264/AVC                                                                                                                                | 29 |

| 2.2.1 Histórico                                                                                                                                                   |    |

| 2.2.2 Perfis e Níveis                                                                                                                                             |    |

| 2.2.3 Visão Geral do Decodificador                                                                                                                                |    |

| 2.3 Módulos de um Decodificador H.264/AVC                                                                                                                         |    |

| 2.3.1 O Módulo de Decodificação de Entropia                                                                                                                       |    |

| <ul> <li>2.3.2 O Módulo de Quantização Inversa (Q<sup>-1</sup>)</li> <li>2.3.3 O Módulo de Transformadas Inversas (T<sup>-1</sup>)</li> </ul>                     | 34 |

| 2.3.4 O Módulo de Predição Intra-quadro (Intra)                                                                                                                   |    |

| 2.3.5 O Módulo de Compensação de Movimento (MC)                                                                                                                   |    |

| 2.3.5.1 Arquitetura do Módulo de Compensação de Movimento (MC)                                                                                                    |    |

| 2.3.6 O Módulo Filtro Redutor de Efeito de Bloco (Filtro)                                                                                                         |    |

| 2.3.6.1 Arquitetura do Filtro Redutor de Efeito de Bloco                                                                                                          |    |

| 3 DECODIFICADOR H.264 INTRA-ONLY                                                                                                                                  | 43 |

| 3.1 Visão Geral do Decodificador H.264 Intra-only                                                                                                                 |    |

| 3.2 O Módulo Parser (Decodificação de Entropia)                                                                                                                   |    |

| <ul> <li>3.3 O Módulo de Predição Intra-Quadro (Intra)</li> <li>3.4 O Módulo de Quantização e Transformadas Inversas (Q<sup>-1</sup> e T<sup>-1</sup>)</li> </ul> | 46 |

| 3.4 O Módulo de Quantização e Transformadas Inversas (Q <sup>-1</sup> e T <sup>-1</sup> )                                                                         | 46 |

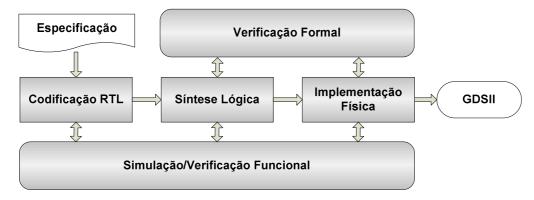

| 4 METODOLOGIA DE IMPLEMENTAÇÃO ASIC                                                                                                                               | 47 |

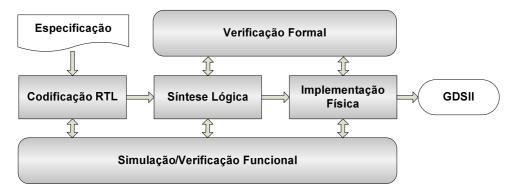

| 4.1 Metodologia de Projeto Standard-cells                                                                                                                         | 47 |

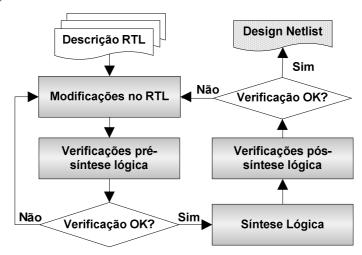

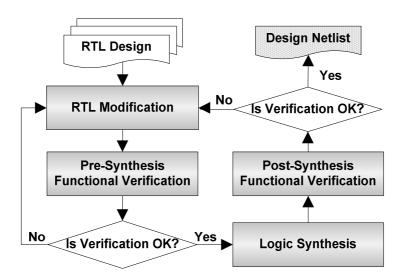

| 4.2 Modificações no RTL Visando Síntese Standard-cells                                                                                                            | 49 |

| 4.3 Metodologia de Verificação                                                                                                                                    | 52 |

| 4.5.1 Verificação Funcional                                               | 52             |

|---------------------------------------------------------------------------|----------------|

| 4.5.2 Verificação Formal                                                  |                |

| 4.4 Etapa de Síntese Lógica                                               |                |

| 4.5 Implementação Física                                                  |                |

| 5 RESULTADOS E COMPARAÇÕES                                                | 59             |

| 5.1 Arquitetura do Filtro Redutor de Efeito de Bloco (Filtro)             | 59             |

| 5.1.1 O Sub-módulo <i>Edge Filter</i>                                     |                |

| 5.1.2 O Módulo Filtro Redutor de Efeito de Bloco (Filtro)                 | 60             |

| 5.2 Arquiteturas para Compensação de Movimento (MC)                       | 63             |

| 5.1.3 O Sub-módulo Preditor de Vetores de Movimento (MVP)                 | 63             |

| 5.2.1 Arquitetura para Compensação de Movimento (MC) Perfil A             | <i>Main</i> 64 |

| 5.2.2 Arquitetura para Compensação de Movimento Perfil High 4             | :2:2 66        |

| 5.3 O Decodificador H.264 Intra-only                                      | 70             |

| 6 CONCLUSÕES E TRABALHOS FUTUROS                                          | 75             |

| 6.1 Trabalhos Futuros                                                     | 76             |

| REFERÊNCIAS                                                               | 77             |

| APÊNDICE TUTORIAL SOBRE FLUXO DE PROJETO ASICIRCUITOS INTEGRADOS DIGITAIS | C PARA         |

## LISTA DE ABREVIATURAS E SIGLAS

ABC Arithmetic Binary Coding

ASIC Application-Specific Integrated Circuit

AVC Advanced Video Coding

B Bi-predictive

BITSTREAM Sequência de bits do vídeo codificado

BRAM Block RAM

bS Boundary Strength

CABAC Context-Based Adaptive Binary Arithmetic Coding

CAD Computer-Aided Design

CAVLC Context-Based Adaptive Variable Length Coding

CAVLD Context-Based Adaptive Variable Length Decoding

Cb Chrominance blue

CI Circuito Integrado

CIF Common Intermediate Format

CODEC Codificador/Decodificador

CMOS Complementary Metal Oxide Semiconductor

CMP Chemical Mechanical Planarization

Cr Chrominance red

CTS Clock Tree Synthesis

DCT Discrete Cosine Transform

DFM Design for Manufacturability

DFT Design for Testability

DPCM Differential Pulse Code Modulation

DRC Design Rule Check

DS Diamond Search

DUV Design under Verification

DVD Digital Versatile Disk

EDA Electronic Design Automation

EDK Embedded Development Kit

FIFO First In First Out

FPGA Field Programmable Gate Array

FRExt Fidelity Range Extensions

FSM Finite State Machine

GB Gigabytes

GDSII Graphic Design System II

GUI Graphical User Interface

H422P *High 4:2:2 Profile* H444P *High 4:4:4 Profile*

HDL Hardware Description LanguageHDTV High Definition Digital Television

High Definition

Hi 10P High 10 Profile

HP High Profile

HW Hardware

I Inter

HD

IBM International Business Machines

IDCT Inverse Discrete Cosine Transform

IDE Integrated Development Environment

IEEE Institute of Electric and Electronics Engineers

INTER Inter Prediction

INTRA Intra Prediction

IP Intellectual Property

ISE Xilinx Integrated Software Environment

ISO International Organization for Standardization

ITU-T International Telecommunication Union - Telecommunication

JVT Joint Video Team

LAD Laboratório de Arquiteturas Dedicadas da UFCG

LEC Logical Equivalence Check

LEF Library Exchange Format

LIB Abbreviation of Library

LUT Look-up-Table

LVS Layout versus Schematic

MB Macrobloco

MC Motion Compensation

ME Motion Estimation

MDD Model Driven Design

ML Metal Layer

MP3 MPEG-1/2 Audio Layer 3

MPEG Moving Picture Experts Group

MV Motion Vector

MVPr Motion Vector Prediction

NAL Network Abstraction Layer

NDA Non Disclosure Agreement

P Predictive

PAL-M Sistema de TV Brasileiro anterior ao SBTVD

PC Personal Computer

PCB Printed Circuit Board

PDA Personal Digital Assistant

Pel Pel Subsampling

PLE Physical Layout Estimation

POC Picture Order Count

PSNR Peak Signal-to-Noise Ratio

Q Quantization

Q<sup>-1</sup> Inverse Quantization

QCIF Quarter Common Intermediate Format

QP Quantization Parameter

Qstep Quantization Step

RAM Random Access Memory

RC Resistência e Capacitância

RGB Red, Green, Blue ROM Read Only Memory

RTL Register Transfer Level

SAD Sum of Absolute Differences

SAIF Switching Activity Interchange Format

SBTVD Sistema Brasileiro de Televisão Digital

SDTV Standard Definition Television

SCA Side Channel Attack

SDC Synopsys Design Constraints

SDF Standard Delay Format

SI Signal Integrity

SI Switching I

SoC System on Chip

SP Switching P

SPEF Standard Parasitic Exchange Format

SRAM Static Random Access Memory

SW Software

T Transform

T<sup>-1</sup> Inverse Transform

TCF Toggle Count File

TCL Tool Command Language

TSMC Taiwan Semiconductor Manufacturing Company

TV Televisão

UFCG Universidade Federal de Campina Grande UFRGS Universidade Federal do Rio Grande do Sul

UMC United Microelectronics Corporation

UML Unified Modeling Language

USB Universal Serial Bus

V2P Virtex 2 Pro

VCD Value Change Dump

VCEG Video Coding Experts Group

VDD Positive supply voltage of a Field Effect Transistor

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrated Circuit

VLC Variable Length Coding

VLSI Very Large Scale Integration

VSS Negative supply voltage of a Field Effect Transistor

VT Threshold Voltage

WLM Wire Load Model

Y Luminance

YCbCr Luminance, Chrominance Blue, Chrominance Red

# LISTA DE FIGURAS

| Figura 1.1: Diagrama de blocos de um decodificador H.264/AVC (AGOSTINI, 2007)                   | 24 |

|-------------------------------------------------------------------------------------------------|----|

| Figura 3.1: Diagrama de blocos do decodificador H.264 intra-only.                               | 25 |

| Figura 2.1: Diagrama em blocos de um codificador H.264/AVC (AGOSTINI, 2007)                     | 29 |

| Figura 2.2: Composição de um slice (PORTO, 2008).                                               | 31 |

| Figura 2.3: Perfis Baseline, Main, Extended e High do H.264/AVC (AGOSTINI, 2007)                | 32 |

| Figura 2.4: Detalhamento dos perfis High do H.264/AVC (ZATT, 2008)                              | 32 |

| Figura 2.5: Diagrama de blocos de um decodificador H.264/AVC (AGOSTINI, 2007)                   |    |

| Figura 2.6: Nove modos da predição intra-quadro para blocos de luminância 4x4 (AGOSTINI, 2007). |    |

| Figura 2.7: Utilização de múltiplos quadros de referência (AGOSTINI, 2007)                      |    |

| Figura 2.8: Arquitetura para compensação de movimento HP422-MoCHA (ZATT, 2008a)                 | 37 |

| Figura 2.9: Arquitetura do módulo Preditor de Vetores de Movimento (ZATT, 2007)                 | 38 |

| Figura 2.10: Arquitetura do módulo de acesso à memória do MC (ZATT, 2007)                       |    |

| Figura 2.11: Sequência de processamento de bordas no filtro. (ROSA, 2010)                       |    |

| Figura 2.12: Convenção de nomes para pixels ao redor das bordas. (ROSA, 2010)                   | 40 |

| Figura 2.13: Arquitetura do módulo edge filter (ROSA, 2010)                                     |    |

| Figura 2.14: Arquitetura do filtro redutor de efeito de bloco (ROSA, 2010)                      |    |

| Figura 3.1: Diagrama de blocos do decodificador H.264 intra-only.                               |    |

| Figura 3.2: Vídeo Parkun HD 720p sendo decodificado em FPGA (BONATTO, 2010)                     |    |

| Figura 3.3: Diagrama de blocos do sub-módulo parser e decodificação de entropia                 |    |

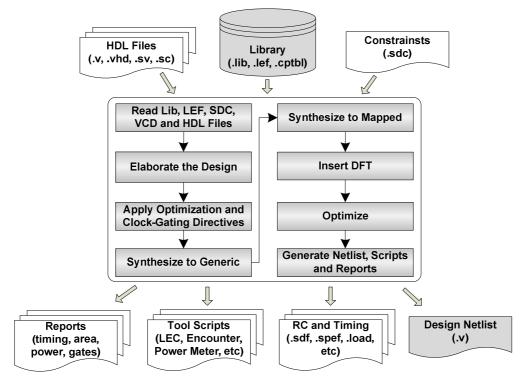

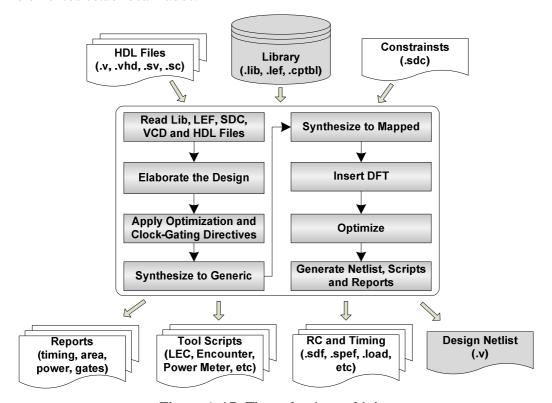

| Figura 4.1: Fluxo de projeto ASIC (standard-cells).                                             |    |

| Figura 4.2: Fluxograma de decisão para realizar modificações no código RTL                      |    |

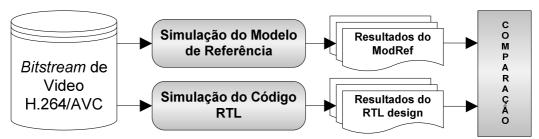

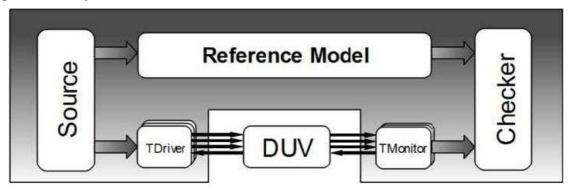

| Figura 4.3: Fluxo para verificação funcional                                                    | 52 |

| Figura 4.4: Fluxo de síntese lógica                                                             |    |

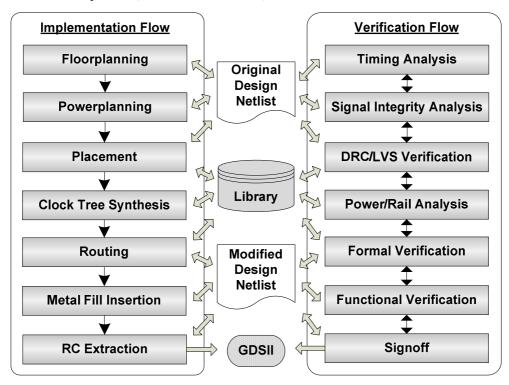

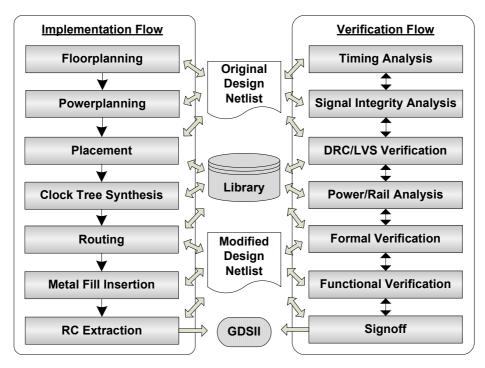

| Figura 4.5: Fluxo de implementação física                                                       |    |

| Figura 5.1: Leiaute do Edge Filter.                                                             |    |

| Figura 5.2: Leiaute do módulo filtro redutor de efeito de bloco                                 |    |

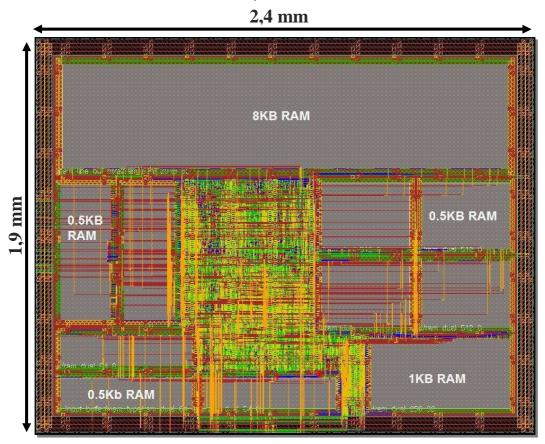

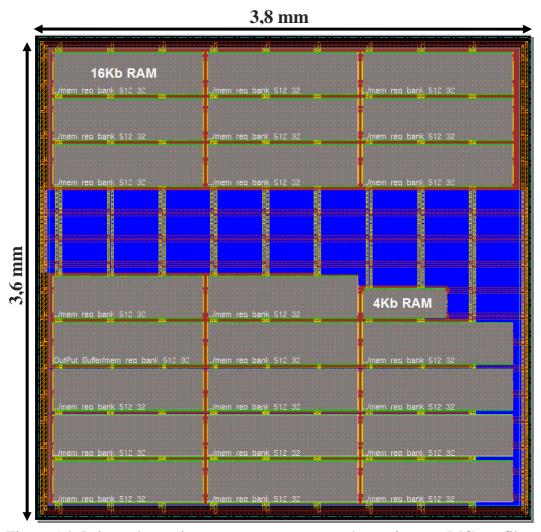

| Figura 5.4: Leiaute da arquitetura para compensação de movimento (MC) perfil Main               |    |

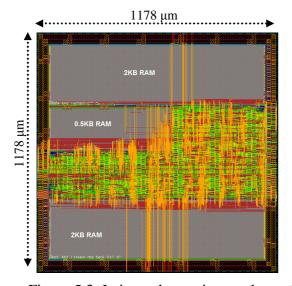

| Figura 5.5: Leiaute do módulo de MC HP422-MoCHA perfil High 4:2:2                               |    |

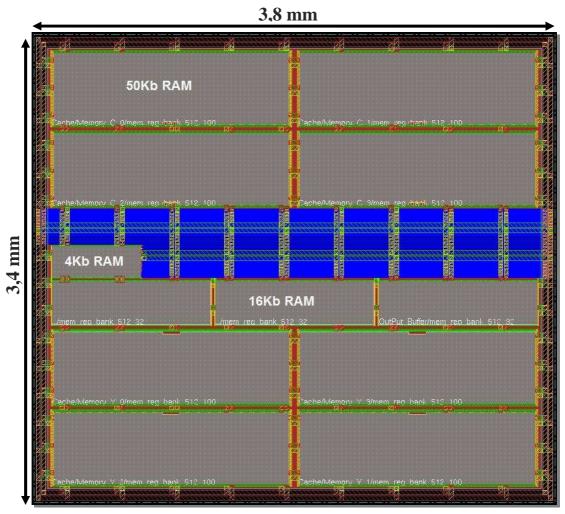

| Figura 5.7: Leiaute do decodificador H.264 intra-only                                           |    |

| Figura 5.8: Área ocupada por cada sub-módulo do decodificador H.264 intra-only                  |    |

| Figura A.1: Fluxo de projeto ASIC                                                               | 85 |

| Figura A.2: Exemplo de scripts de configuração de ferramentas                                   |    |

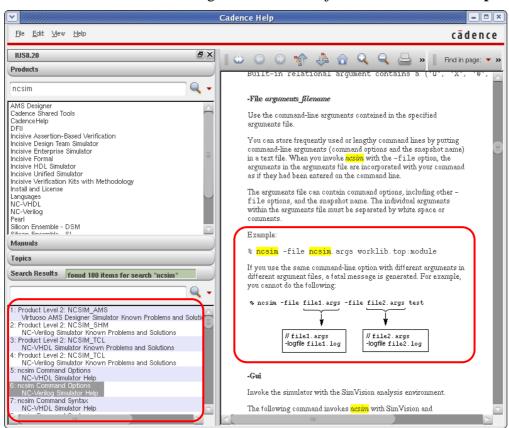

| Figura A.3: Janela inicial da ferramenta cdnshelp                                               | 89 |

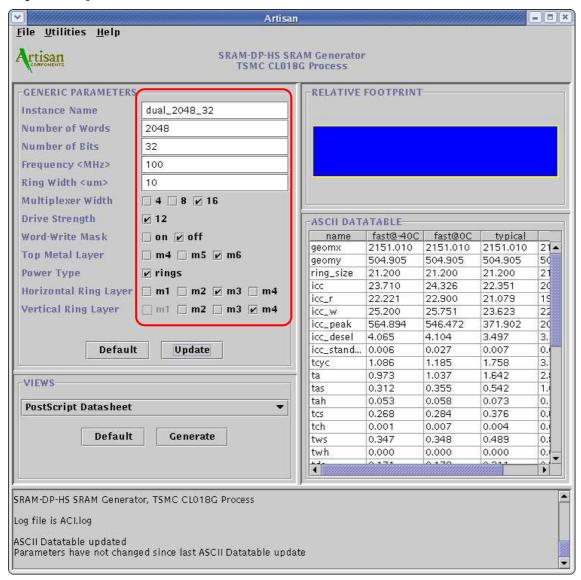

| Figura A.4: Janela do gerador de memória da Artisan.                                            | 90 |

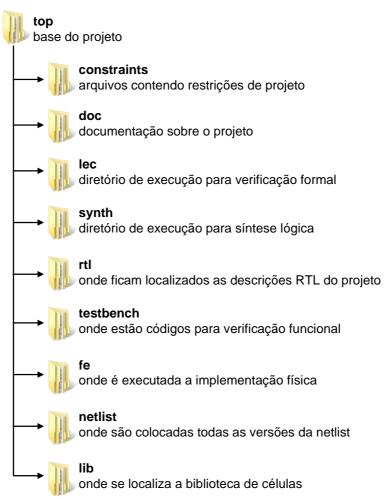

| Figura A.5: Modelo de estrutura de diretórios de projeto                                        |    |

| Figura A.6: Exemplo de makefile para automatização de simulação                                 |    |

| Figura A.7: Ambiente de verificação da metodologia VeriSC (SILVEIRA, 2009)                      |    |

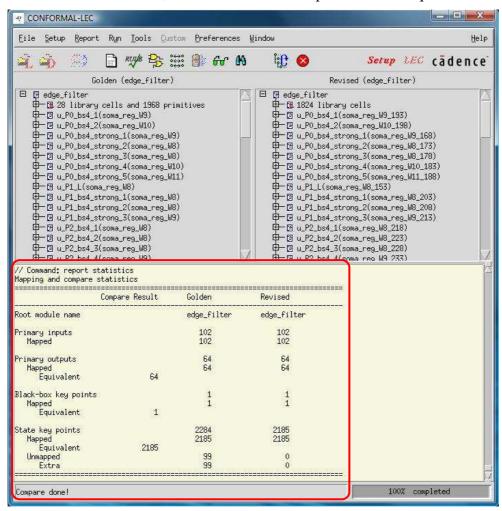

| Figura A.8: Verificação de equivalência utilizando a ferramenta LEC                             |    |

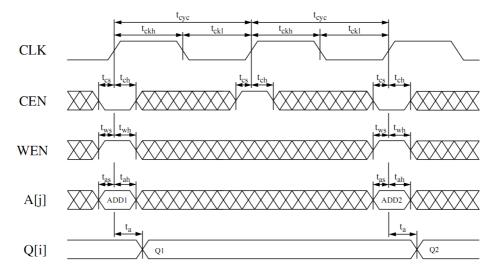

| Figura A.9: Diagrama de tempo para memória ASIC                                                 |    |

| Figura A.10: Descrição de memória como array de std_logic_vector                                |    |

| Figura A.11: Exemplo de uso de memória single-port para ASIC                                    |    |

| Figura A.12: Abstração de memória como array de registradoress                                  |    |

| Figura A.13: Exemplo de uso de memória dual-port para ASIC                                      |    |

| Figura A.14: Indexação dinâmica de bits em um std_logic_vector                                  |    |

| Figura A.15: Indexação estática de bits em um std_logic_vector                                  |    |

| Figura A.16: Fluxograma de decisão para mudanças no RTL.                                        |    |

|                                                                                                 |    |

| Figura A.17: Fluxo de síntese lógica                                           | 104 |

|--------------------------------------------------------------------------------|-----|

| Figura A.18: Exemplo de arquivo SDF                                            | 115 |

| Figura A.19: Exemplo de arquivo sdf_cmd_file para backannotation               | 116 |

| Figura A.20: Fluxo de implementação física                                     | 117 |

| Figura A.21: Modelo de wrapper para inclusão de PADs em netlist                |     |

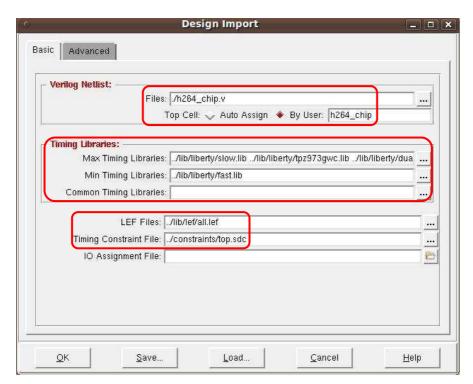

| Figura A.22: Modelo de arquivo de configuração para a ferramenta Encounter     | 119 |

| Figura A.23: Aba para carregamento de projeto no Encounter                     |     |

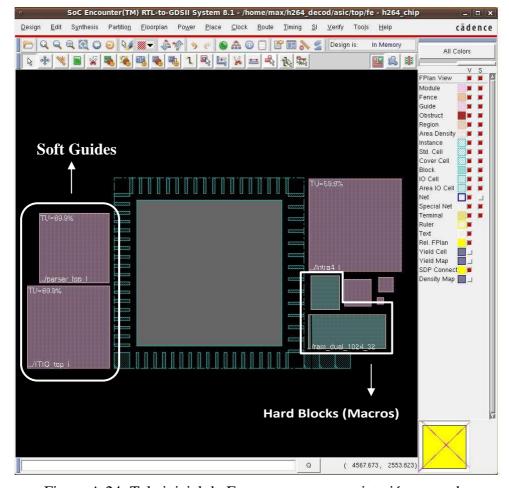

| Figura A.24: Tela inicial do Encounter com o projeto já carregado              | 120 |

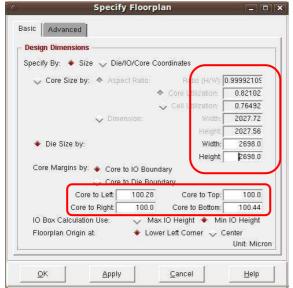

| Figura A.25: Especificação de dimensões do leiaute                             | 121 |

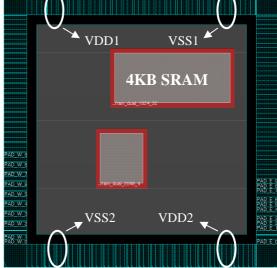

| Figura A.26: Floorplan de macros e PADs                                        | 121 |

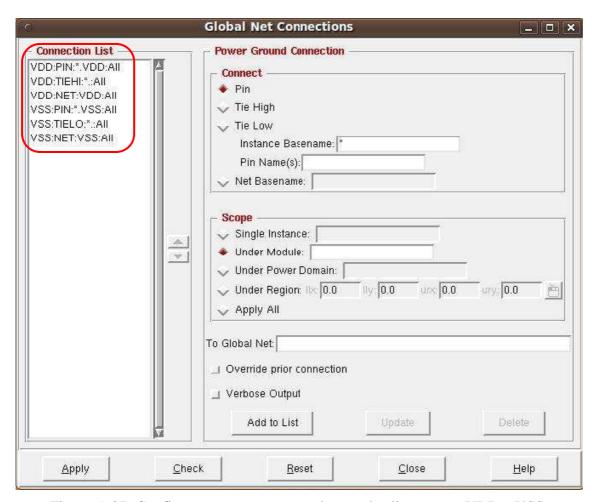

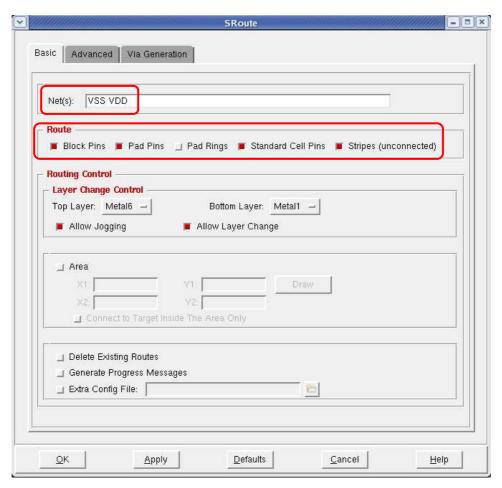

| Figura A.27: Configuração para conexão de nets de alimentação VDD e VSS        | 122 |

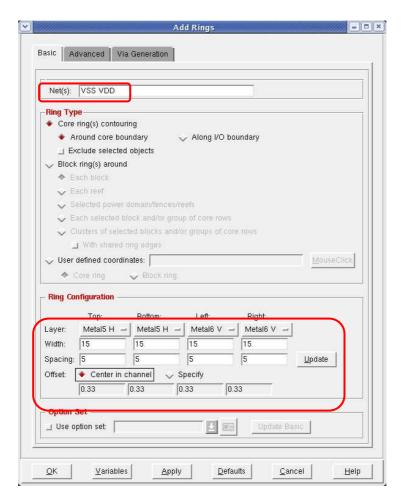

| Figura A.28: Configuração de rings de alimentação para VDD e VSS               | 123 |

| Figura A.29: Janela para conexão de power das std-cells, PADs e macros         |     |

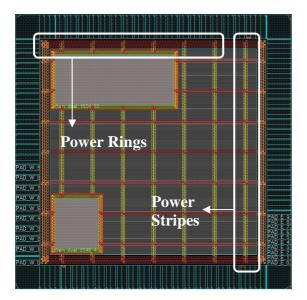

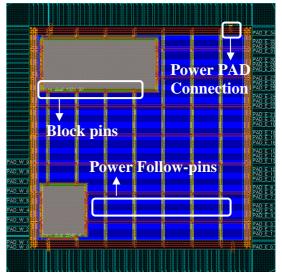

| Figura A.30: Ilustração do rings e stripes de power                            | 124 |

| Figura A.31: Ilustração das nets para ligação de power das std-cells           | 124 |

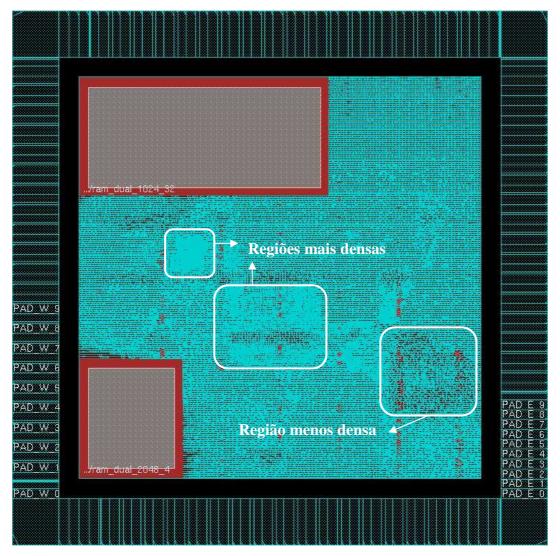

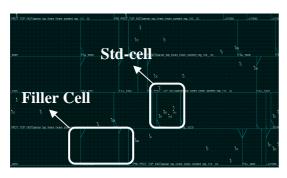

| Figura A.32: Circuito após a etapa de posicionamento                           | 125 |

| Figura A.33: Relatório do comando checkPlace                                   | 126 |

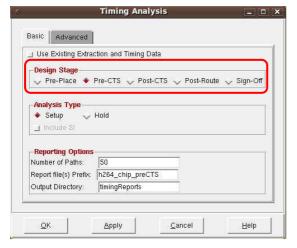

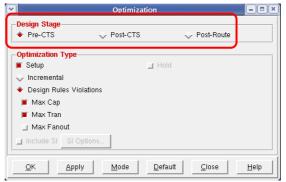

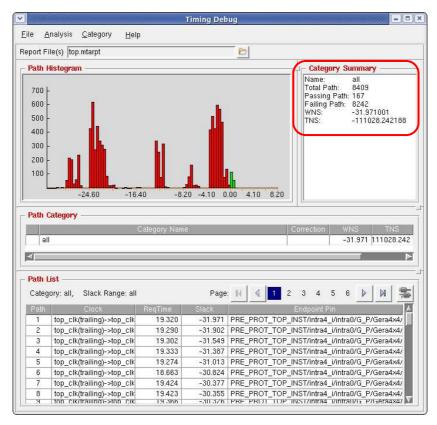

| Figura A.34: Tela para execução da etapa de timing analysis                    | 126 |

| Figura A.35: Tela para execução de otimizações de timing                       | 126 |

| Figura A.36: Timing Analysis com alguns caminhos desrespeitando as constraints |     |

| Figura A.37: Resultado de análise de timing sem violações                      | 127 |

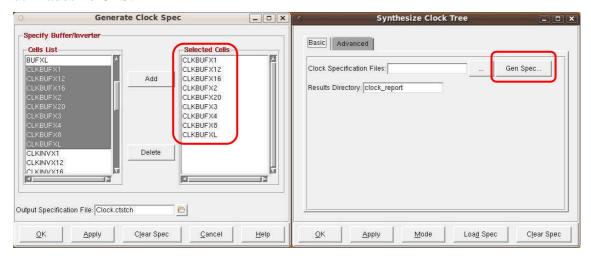

| Figura A.38: Janela para geração do Clock.ctstch e execução do CTS             | 128 |

| Figura A.39: Arquivo Clock.ctstch para clock tree synthesis (CTS)              |     |

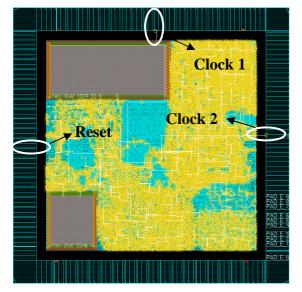

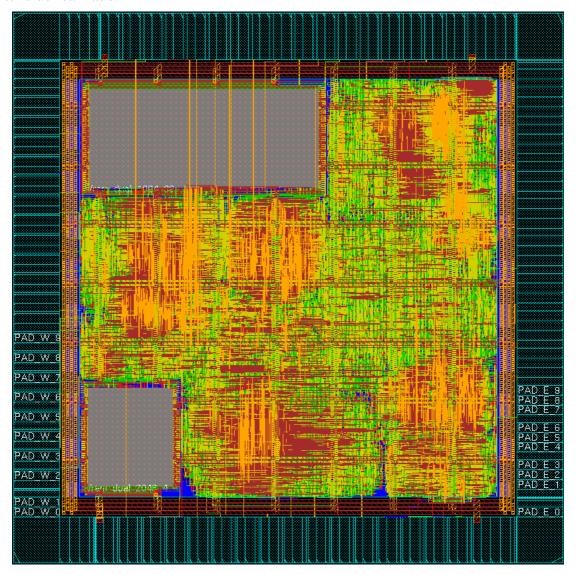

| Figura A.40: Ilustração da árvore de relógio no circuito                       |     |

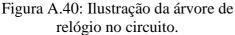

| Figura A.41: Ilustração das regiões de maior e menor atraso de relógio         | 129 |

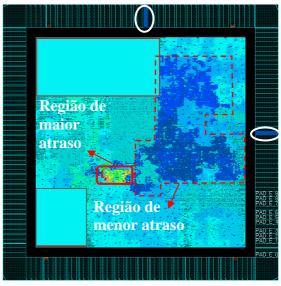

| Figura A.42: Leiaute do circuito totalmente roteado                            |     |

| Figura A.43: Ilustração do leiaute após a inserção de filler cells             | 131 |

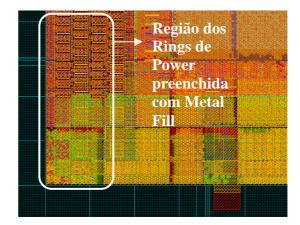

| Figura A.44: Ilustração do leiaute após a inserção de metal                    |     |

| Figura A.45: Modelo de script para inserção de metal fill                      | 132 |

| Figura A.46: Trecho de um relatório de verificação de DRC                      | 133 |

| Figura A.47: Trecho de relatório de verificação de LVS                         |     |

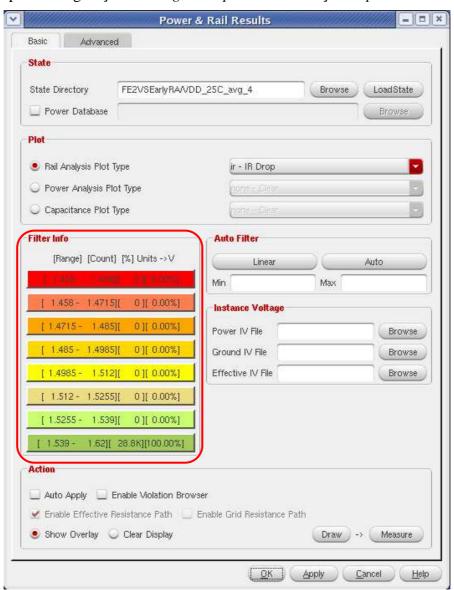

| Figura A.48: Exemplo de configuração de Rail Analysis para VDD                 | 134 |

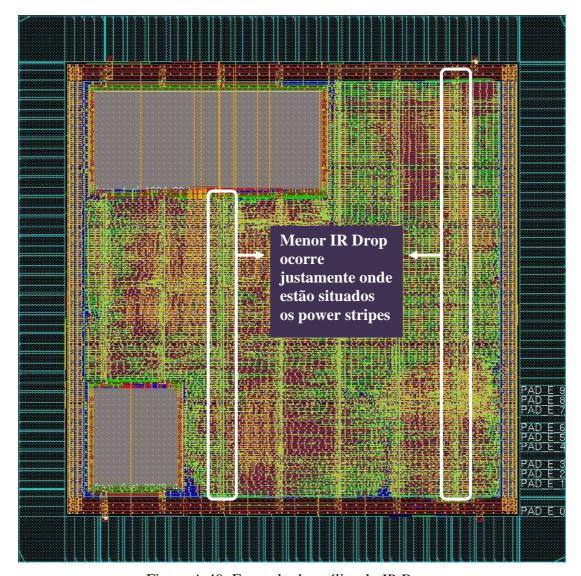

| Figura A.49: Exemplo de análise de IR Drop.                                    |     |

# LISTA DE TABELAS

| Tabela 2.1: Relação entre QP e Qstep                                                | 34 |

|-------------------------------------------------------------------------------------|----|

| Tabela 2.2: Resultados de síntese FPGA para MoCHA e HP422-MoCHA                     |    |

| Tabela 2.3: Resultados de síntese do filtro para FPGA                               |    |

| Tabela 3.1: Resultados de síntese para FPGA Xilinx Virtex 2 Pro                     |    |

| Tabela 5.1: Características do Edge Filter                                          | 59 |

| Tabela 5.2: Características do filtro redutor de efeito de bloco                    | 60 |

| Tabela 5.3: Detalhamento em gates e memória dos sub-módulos do filtro               |    |

| Tabela 5.4: Comparação do filtro com trabalhos descritos na literatura              |    |

| Tabela 5.5: Características do MVP                                                  |    |

| Tabela 5.6: Comparação entre arquiteturas do MVP                                    | 64 |

| Tabela 5.7: Características do MC perfil Main                                       | 65 |

| Tabela 5.8: Características do MC HP422-MoCHA perfil High 4:2:2                     | 66 |

| Tabela 5.9: Detalhamento dos sub-módulos do MC HP422-MoCHA perfil High 4:2:2        | 67 |

| Tabela 5.10: Comparação do MC com trabalhos descritos na literatura                 | 69 |

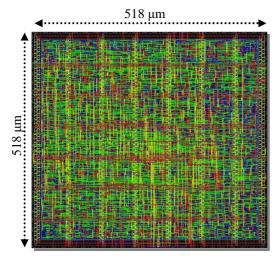

| Tabela 5.11: Características do decodificador H.264 intra-only                      | 71 |

| Tabela 5.12: Detalhamento de memória e gates do decodificador intra-only            | 72 |

| Tabela 5.13: Comparação do decodificador com implementações descritas na literatura |    |

| Tabela A.1: Tabela de verificações de signoff                                       |    |

## **RESUMO**

Recentemente, o Brasil adotou o padrão SBTVD (Sistema Brasileiro de TV Digital) para transmissão de TV digital. Este utiliza o CODEC (codificador e decodificador) de vídeo H.264/AVC, que é considerado o estado-da-arte no contexto de compressão de vídeo digital. Esta transição para o SBTVD requer o desenvolvimento de tecnologia para transmissão, recepção e decodificação de sinais, assim, o projeto Rede H.264 SBTVD foi iniciado e tem como um dos objetivos a produção de componentes de hardware para construção de um set-top box SoC (System on Chip) compatível com o SBTVD. No sentido de produzir IPs (Intellectual Property) para codificação e decodificação de vídeo digital segundo o padrão H.264/AVC, várias arquiteturas de hardware vêm sendo desenvolvidas no âmbito do projeto. Assim, o objetivo deste trabalho consiste na realização da implementação física em ASIC (Application-Specific Integrated Circuit) de algumas destas arquiteturas de hardware para decodificação de vídeo H.264/AVC, entre elas as arquiteturas parser e decodificação de entropia, predição intra-quadro e, por fim, quantização e transformadas inversas, que juntas formam uma versão funcional de um decodificador de vídeo H.264 chamado de decodificador intra-only. Além destas, também foi fisicamente implementada uma arquitetura para o módulo filtro redutor de efeito de bloco e arquiteturas para os perfis Main e High de um compensador de movimentos. Nesta dissertação de mestrado, é apresentada a metodologia de implementação standard-cells (ASIC) utilizada, assim como uma descrição detalhada de cada passo executado para se chegar ao leiaute de cada uma das arquiteturas. Também são apresentados os resultados das implementações e realizadas algumas comparações com outras implementações de arquiteturas descritas na literatura. A implementação do filtro possui 43,9K portas lógicas (equivalent-gates), 42mW de potência e possui a menor quantidade de memória interna, 12,375KB SRAM, quando comparada com outras implementações para a mesma resolução de vídeo, 1920x1080@30fps. As implementações para os perfis Main e High do compensador de movimento apresentam a melhor relação entre a quantidade de ciclos de relógio necessária para interpolar um macrobloco (MB), 304 ciclos/MB, e a quantidade de equivalent-gates de cada implementação, 98K e 102K, respectivamente. Já a implementação do decodificador H.264 intra-only possui 5KB SRAM, 11,4mW de potência e apresenta a menor quantidade de equivalent-gates, 150K, comparado com outras implementações de decodificadores H.264 com características similares.

**Palavras-Chave:** Fluxo ASIC (*standard-cells*), Projeto de Circuitos Integrados Digitais, Padrão H.264/AVC, Decodificação de Vídeo, Microeletrônica.

# Physical Implementation of Hardware Architectures for Video Decoding According to the H.264/AVC Standard

## **ABSTRACT**

Recently Brazil has adopted the SBTVD (Brazilian Digital Television System) for digital TV transmission. It uses the H.264/AVC video CODEC (coder and decoder), which is considered the state of the art in the context of digital video compression. This transition to the SBTVD standard requires the development of technology for transmitting, receiving and decoding signals, so a project called Rede H.264 was initiated with the objective of producing cutting edge hardware components to build a set-top box SoC (System on Chip) compatible with the SBTVD. In order to produce IPs (Intellectual Property) for encoding and decoding digital video according to the H.264/AVC standard, many hardware architectures have been developed under the project. Therefore, the objective of this work is to carry out the physical implementation flow for ASIC (Application-Specific Integrated Circuit) in some of these hardware architectures for H.264/AVC video decoding, including the architectures parser and entropy decoding, intra-prediction and inverse quantization and transforms, which together compound a working version of an H.264 video decoder called intra-only. Besides these architectures, it is also physically implemented an architecture for a deblocking filter module and architectures for motion compensation according the Main and High profiles. This master thesis presents the standard-cells (ASIC) implementation as well as a detailed description of each step necessary to outcome the layouts of each of the architecture. It also presents the results of the implementations and comparisons with other works in the literature. The implementation of the filter has 43.9K gates (equivalent-gates), 42mW of power consumption and it demands the least amount of internal memory, 12.375KB SRAM, when compared with other implementations for the same video resolution, 1920x1080@30fps. The implementations for the Main and High profiles of the motion compensator have the best relationship between the amount of required clock cycles to interpolate a macroblock (MB), 304 cycles/MB, and the equivalent-gate count of each implementation, 98K and 102K, respectively. Also, the implementation of the H.264 intra-only decoder has 5KB SRAM, 11.4 mW of power consumption and it has the least equivalent-gate count, 150K, compared with other implementations of H.264 decoders which have similar features.

Keywords: ASIC (standard-cells) Implementation Flow, Integrated Circuits Design, Video Compression, H.264/AVC Video Coding and Decoding Standard, Microelectronics.

## 1 INTRODUÇÃO

A compressão de vídeos digitais vem sendo bastante pesquisada atualmente devido à sua relevância em aplicações para determinados dispositivos eletrônicos com recursos de multimídia complexos, como computador pessoal e portátil, aparelho celular, televisão digital de alta resolução (HDTV), DVD *players*, câmeras e filmadoras digitais portáteis, entre muitos outros. A compressão de vídeo é essencial para aplicações que utilizam vídeos digitais devido ao elevado volume de informações contidas nestes e que precisam ser armazenadas ou transmitidas por um meio físico.

Para um vídeo com resolução de 720x480 pixels a 30 quadros por segundo (usado em televisão digital com definição normal – SDTV e em DVDs), utilizando 24 bits por pixel, a taxa necessária para a transmissão sem compressão seria aproximadamente 249 milhões de bits por segundo (249 Mbps). Para armazenar uma sequência de curta duração, com 10 minutos, seriam necessários quase 19 bilhões de bytes (19GB). Para vídeos com resolução de 1920x1080 pixels a 30 quadros por segundo (usado em televisão digital com alta definição ou HDTV), com 24 bits por pixel, a taxa de transmissão sobe para 1,5 bilhões de bits por segundo (1,5 Gbps) e seriam necessários 112 bilhões de bytes (112 GB) para armazenar um vídeo com 10 minutos de duração.

Vários padrões foram desenvolvidos agregando técnicas a algoritmos no sentido de reduzir a quantidade de informações em um vídeo digital, principalmente explorando suas redundâncias. O padrão H.264/AVC (*Advanced Video Coding* - Codificação de Vídeo Avançada) (ITU-T, 2005) é um deles. Ele é considerado o estado-da-arte em termos de compressão de vídeo, introduzindo um conjunto de ferramentas inovadoras em relação a padrões anteriores. A eficiência em compressão do padrão H.264/AVC pode ser de até duas vezes em relação ao padrão MPEG-2 (ITU-T, 1994), ao preço de um aumento na complexidade de aproximadamente quatro vezes (WIEGAND, 2003).

Devido à grande complexidade do padrão, a maioria dos processadores de propósito geral executando um decodificador H.264/AVC implementado em software não atingem desempenho suficiente para decodificar vídeo de alta resolução em tempo real a uma taxa de 30 quadros por segundo. Isto se torna ainda mais crítico quando se deseja decodificar vídeo em sistemas embarcados, pois, além do desempenho, restrições no consumo de potência e área do circuito integrado também são importantes. Isto praticamente inviabiliza a decodificação de vídeo puramente em software. Assim, surge a necessidade de implementação de decodificadores de vídeos H.264/AVC em hardware.

O processo de decodificação de vídeo segundo o padrão H.264/AVC é dividido em vários módulos/etapas em que para cada uma delas pode ser projetada uma arquitetura de hardware correspondente. Estas etapas são definidas como *parser* e decodificação de

entropia, quantização e transformadas inversas, predição intra-quadro, predição interquadros (compensação de movimentos) e filtro redutor de efeito de bloco.

## 1.1 Motivação e Objetivos

Atualmente, o Brasil vem passando por uma transição no sistema de transmissão de TV, passando do padrão PAL-M para o padrão SBTVD (Sistema Brasileiro de TV Digital) (SBTVD, 2007), que é baseado no sistema de TV japonês, porém, com um CODEC (codificador e decodificador) de vídeo melhorado em relação ao utilizado no padrão japonês. O sistema de TV digital brasileiro pretende utilizar o padrão para decodificação de vídeo H.264/AVC, enquanto o sistema japonês utiliza o MPEG-2.

Esta transição para o SBTVD requer o desenvolvimento de tecnologia para transmissão, recepção e decodificação de sinais, assim, o projeto Rede H.264 SBTVD (REDE-H264, 2010) foi iniciado e tem como um dos objetivos a produção de IPs (*Intellectual Property*) para construção de um *set-top box* SoC (*System on Chip*) compatível com o SBTVD. No sentido de produzir tecnologia para codificação e decodificação de vídeo digital segundo o padrão H.264/AVC, várias arquiteturas de hardware vêm sendo desenvolvidas no âmbito do projeto.

Para o decodificador H.264/AVC, já foram projetadas em HDL as arquiteturas para os módulos *parser* e decodificador de entropia (PEREIRA, 2009), quantização e transformadas inversas (AGOSTINI, 2006), predição intra-quadro (STAEHLER, 2006) e filtro redutor de efeito de bloco (ROSA, 2009). Uma arquitetura para o módulo de compensação de movimentos perfil *Main* foi desenvolvida em (AZEVEDO, 2007) e uma extensão dela para o perfil *High* 4:2:2 foi desenvolvida em (ZATT, 2008a). Todas elas estão ilustradas na Figura 1.1.

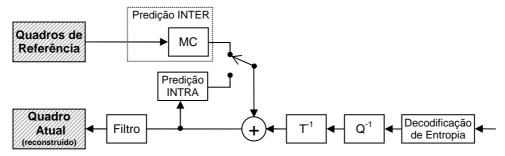

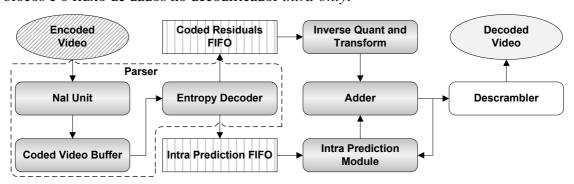

Figura 1.1: Diagrama de blocos de um decodificador H.264/AVC (AGOSTINI, 2007).

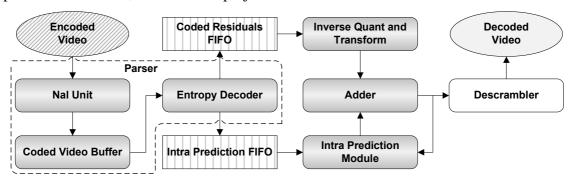

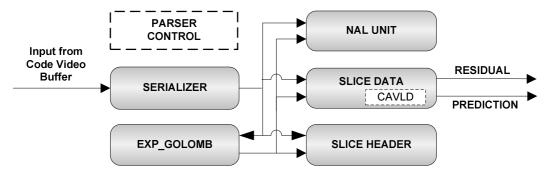

Entre estas arquiteturas desenvolvidas, no trabalho de (PEREIRA, 2006), as arquiteturas *parser* e decodificação de entropia, quantização e transformadas inversas e predição intra-quadro foram integradas gerando um decodificador de vídeo H.264, porém as arquiteturas para predição inter-quadros e filtro redutor de efeito de bloco não foram integrados. Devido à falta do módulo de predição inter-quadros, este decodificador foi chamado de H.264 *intra-only*, que é

Todas essas arquiteturas desenvolvidas foram projetadas utilizando a linguagem VHDL, validadas através de simulação e prototipadas em placas com dispositivos de FPGA (*Field Programmable Gate Array*). Entretanto, nenhuma delas havia sido sintetizada para *standard-cells* (*std-cells*) com o intuito de realizar a implementação física para geração de *hard* IPs (*Intellectual Property*), que são elementos de hardware pré-projetados e disponíveis para uso em leiautes. O decodificador H.264 também não

havia sido implementado em ASIC (*Application-Specific Integrated Circuit*). Dessa forma, havia a necessidade de realizar a implementação física de todas estas arquiteturas em ASIC para extração de resultados de potência, quantidade de portas lógicas, área, etc, com o intuito de posteriormente avaliar a viabilidade de utilização delas na prototipação de um circuito integrado (*chip*) decodificador de vídeo digital segundo o padrão H.264/AVC, resultante do projeto H.264 SBTVD.

Figura 3.1: Diagrama de blocos do decodificador H.264 *intra-only*.

Assim, o objetivo deste trabalho de mestrado consiste na realização da implementação física (ASIC) das arquiteturas de hardware *parser* e decodificação de entropia, quantização e transformadas inversas e predição intra-quadro descritas anteriormente. Elas juntas formam uma versão funcional de um decodificador de vídeo H.264, chamado de H.264 *intra-only*. Além destas, também é objetivo do trabalho implementar em ASIC, a arquitetura para o filtro redutor de efeito de bloco e as arquiteturas para os perfis *Main* e *High* do módulo compensação de movimento, comparando as implementações físicas de todas estas arquiteturas com trabalhos descritos na literatura, para avaliação da utilização delas em um decodificador de vídeo segundo o padrão H.264/AVC adequado para integração em um *set-top box* SoC (*System on Chip*) compatível com o SBTVD.

Nesta dissertação, é apresentada a metodologia de implementação ASIC utilizada, assim como uma descrição detalhada de cada passo executado para se chegar ao leiaute de cada uma das arquiteturas. Também são apresentados os resultados das implementações, comparando-os com outros resultados de implementações descritas na literatura, e analisando assim a viabilidade de utilização delas para prototipação de um circuito integrado para decodificação de vídeo segundo o padrão H.264/AVC.

O restante do trabalho está organizado da seguinte maneira. O Capítulo 2 apresenta resumidamente o padrão para decodificação de vídeo H.264/AVC, com uma breve descrição de cada uma de suas etapas. O Capítulo 3 apresenta a arquitetura do decodificador H.264 *intra-only* e discorre sobre as arquiteturas que o compõem. O Capítulo 4 apresenta a metodologia de projeto *standard-cells* utilizada neste trabalho. Nela, também são encontrados alguns comentários e observações a respeito das dificuldades encontradas ao longo da implementação física das arquiteturas em ASIC. O Capítulo 5 apresenta os resultados obtidos para cada arquitetura, assim como algumas comparações com trabalhos encontrados na literatura. O Capítulo 6 discorre sobre as conclusões e considerações gerais do trabalho. Alguns pontos a serem ainda tratados em trabalhos futuros são também apresentados. Por fim, é apresentado um apêndice intitulado Fluxo de Projeto ASIC para Circuitos Integrados Digitais, que contém uma descrição detalhada da metodologia de implementação utilizada neste trabalho.

## 2 O PADRÃO H.264/AVC

Este capítulo apresenta, de forma resumida, os conceitos básicos sobre compressão de vídeo e dá uma visão geral sobre o padrão para decodificação de vídeo digital H.264/AVC. Aqui é apresentado o funcionamento geral de cada um dos módulos em um decodificador H.264/AVC. São também apresentadas arquiteturas de hardware para os módulos de compensação de movimento, perfis *Main* e *High*, e para o filtro redutor de efeito de bloco, implementadas em ASIC neste trabalho. As arquiteturas que formam o decodificador H.264 *intra-only* são apresentadas no Capítulo 3.

Informações mais detalhadas sobre os conceitos de codificação de vídeo, sobre o padrão H.264/AVC e uma comparação detalhada deste com outros padrões podem ser consultadas no trabalho de doutorado de Agostini (AGOSTINI, 2007), assim como em (SULLIVAN, 2005; RICHARDSON, 2003).

## 2.1 Conceitos Básicos sobre Codificação de Vídeo

Um sistema para representar cores é chamado de espaço de cores, e a definição do espaço de cores a ser utilizado para representar um vídeo é essencial para a eficiência da codificação deste vídeo. São vários os espaços de cores usados para representar imagens digitais, tais como: RGB, HSI e YCbCr (SHI, 1999). O RGB (*red*, *green e blue*) representa, em três matrizes distintas, as três cores primárias captadas pelo sistema visual humano: vermelho, verde e azul. No espaço de cores YCbCr, as três componentes utilizadas são luminância (Y), que define a intensidade luminosa ou o brilho; crominância azul (Cb) e crominância vermelha (Cr) (BHASKARAN, 1997).

Os componentes R, G e B possuem um elevado grau de correlação, o que não é desejável do ponto de vista da compressão de vídeos. Por isso, a compressão é aplicada para espaços de cores do tipo luminância e crominância, como o YCbCr (RICHARDSON, 2002). Outra vantagem do espaço de cor YCbCr sobre o espaço RGB é que, no espaço YCbCr, a informação de cor está completamente separada da informação de brilho. Deste modo, estas informações podem ser tratadas de forma diferenciada pelos codificadores de imagens estáticas e de vídeos (AGOSTINI, 2007).

A compressão de vídeo utiliza uma série de técnicas, estratégias e algoritmos que exploram a redundância de informações nos vídeos. Estas técnicas podem ser basicamente resumidas em duas categorias: remoção de informações redundantes, ou seja, em que não há perdas na qualidade do vídeo durante a compressão; e a remoção de informações que não são perceptíveis aos olhos. Nesta última, há perda de informação durante a compressão do vídeo.

Os principais tipos de redundância explorados são:

- **Redundância Espacial -** conhecida também como redundância intra-quadro, está relacionada à correlação de pixels em uma mesma imagem. Assim, através de algoritmos de predição intra-quadro, é possível utilizar pixels já processados para prever seus vizinhos;

- Redundância Temporal conhecida também como redundância interquadros, vem da relação entre os vários quadros consequentes em um mesmo vídeo. Os algoritmos de predição temporal se baseiam em quadros previamente processados para prever como é o quadro atualmente sendo processado;

- Redundância Entrópica vem da relação entre determinados símbolos codificados e a quantidade de bits utilizada para representá-lo. Existem algoritmos responsáveis por reduzir a quantidade de bits utilizada para representar os símbolos de maior ocorrência sem perdas de informação;

As principais técnicas baseadas em perdas são:

- Subamostragem redução da taxa de amostragem dos componentes de crominância em relação aos componentes de luminância (RICHARDSON, 2002). Como os olhos humanos são muito mais sensíveis à informação de luminância, a idéia é utilizar uma maior resolução para o componente de luminância (mais amostras) e menores para os componentes de crominância (AGOSTINI, 2007). Assim, existem 3 tipos de subamostragem: 4:4:4, o 4:2:2 e o 4:2:0. No formato 4:4:4, para cada quatro amostras de luminância (Y), existem quatro amostras de crominância azul (Cb) e quatro amostras de crominância vermelha (Cr). Por isso, os três componentes de cor possuem a mesma resolução, existe uma amostra de cada elemento de cor para cada pixel da imagem e, assim, a subamostragem não é aplicada. No formato 4:2:2, para cada quatro amostras de Y na direção horizontal, existem apenas duas amostras de Cb e duas amostras de Cr. Neste caso, as amostras de crominância possuem a mesma resolução vertical das amostras de luminância, mas possuem metade da resolução horizontal. No formato 4:2:0, para cada quatro amostras de Y, existe apenas uma amostra de Cb e uma amostra de Cr. Neste caso, as amostras de crominância possuem metade da resolução horizontal e metade da resolução vertical, com relação às amostras de luminância (AGOSTINI, 2007);

- Transformadas e Quantização Os olhos humanos têm maior perceptividade para mudanças suaves em vídeos do que para texturas detalhadas. O termo frequência espacial determina a taxa com que os pixels mudam de um lugar para outro. Neste contexto, altas frequências espaciais significam uma grande diferença entre as posições vizinhas de pixels, ao passo que baixa frequência espacial significa modificações mais suaves. A aplicação de transformadas sobre uma determinada área é uma operação sem perdas de informação que recebe como entrada uma matriz de pixels e produz a frequência espacial dessa matriz. A aplicação da quantização é uma

operação com perdas que descarta as partes da imagem que são menos perceptíveis aos olhos. (PEREIRA, 2009).

## 2.2 Introdução ao Padrão H.264/AVC

Para compressão de vídeo, o padrão H.264/AVC, assim como os outros padrões para codificação de vídeo, utiliza os pixels vizinhos (redundância espacial) ou quadros já codificados (redundância temporal) para predizer como é o quadro atualmente sendo processado. Em um quadro sendo codificado, a predição intra-quadro procura achar qual a combinação de pixels vizinhos disponíveis produz a melhor configuração para o bloco de imagem sendo atualmente codificado, ao passo que a predição inter-quadros procura em alguns quadros já codificados para tentar achar o mais similar possível ao que está sendo atualmente codificado. Ambas as predições produzem uma estimativa, e como a estimativa não é perfeita, há uma diferença entre ela e a imagem, o que se chama de resíduo.

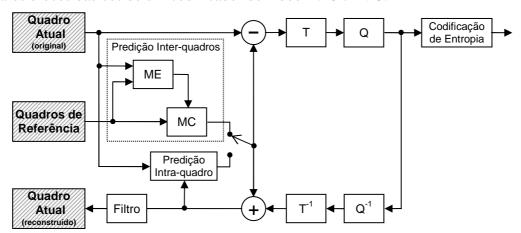

O resíduo gerado pela predição intra-quadro ou inter-quadros é transformado do domínio espacial para o domínio de frequências. Com a informação do resíduo neste domínio, um passo de quantização reduz as frequências diferentes com pesos diferentes. Os dados de predição e resíduo são enviados para um codificador de entropia para que este reduza o número de *bits* da informação a ser enviada ou armazenada. A Figura 2.1 ilustra os blocos básicos de um codificador de vídeo H.264/AVC.

Figura 2.1: Diagrama em blocos de um codificador H.264/AVC (AGOSTINI, 2007)

O codificador é dividido nos seguintes módulos: predição intra-quadro; predição inter-quadros, esta dividida nas etapas de estimação de movimentos (ME) e compensação de movimentos (MC); transformadas diretas (T); quantização direta (Q); e codificação de entropia.

Um decodificador de vídeo não tem acesso aos quadros originais que servem de referência durante a decodificação, tendo acesso apenas aos quadros codificados, ou seja, aos quadros com perdas, após a quantização realizada durante o processo de codificação. Assim, o codificador também deve ser capaz de decodificar os quadros recém codificados para utilizá-los como quadros de referência durante as predições, pois é necessário que o quadro de referência utilizado no codificador seja igual ao quadro de referência no decodificador. Assim, um codificador também possui alguns módulos do processo de decodificação, para poder gerar os quadros de referência

reconstruídos a partir dos quadros recém codificados. Estes módulos para decodificação de vídeo são: quantização inversa (T<sup>-1</sup>) e transformada inversa (Q<sup>-1</sup>), para reconstrução do resíduo codificado, a ser somado com um quadro de referência para reconstrução do quadro. O módulo filtro redutor de efeito de bloco (Filtro) do processo de decodificação também é adicionado ao codificador. A função deles é suavizar o efeito de bloco do quadro reconstruído antes de ele ser usado para fazer a predição de um novo macrobloco, utilizando predição do tipo inter-quadros.

#### 2.2.1 Histórico

Em 1990, o ITU-T (*International Telecommunication Union - Telecommunication*) (ITU-T, 2010a) publicou o padrão H.261 (ITU-T, 1990), estabelecendo assim as ferramentas básicas para os CODECS (codificador e decodificador) atuais. Depois do H.261, outros padrões foram publicados nos anos seguintes: O MPEG (*Motion Picture Experts Group*) da ISO (*International Organization for Standardization*) (ISO/IEC, 2010) publicou o MPEG-1 (ISO/IEC, 1993) e depois o MPEG-2, que foi padronizado como H.262 (ITU-T, 1994). O H.262/MPEG-2 obteve grande sucesso e se tornou mais popular que outros padrões como ITU-T H.263 e ISO MPEG4 Parte 2.

Em 2001, o ITU-T e ISO se juntaram e criaram o JVT (*Joint Video Team*) (ITU-T, 2010b) com o intuito de elaborar um novo CODEC de alto desempenho, aprovado em 2003 (ITU-T, 2003) com uma extensão 2005 (ITU-T, 2005). Este CODEC é chamado de MPEG4 Parte 10 (nome dado pelo ISO) e H.264 (nome dado pelo ITU-T). Este padrão possui ferramentas/técnicas que proporcionam um desempenho consideravelmente maior que os padrões anteriores, chegando a duplicar a taxa de compressão em relação ao padrão mais eficiente até então, que era o MPEG-2. Softwares de referência também estão disponíveis para testar o padrão (PEREIRA, 2009).

## 2.2.2 Perfis e Níveis

O padrão H.264/AVC é dividido em perfis e níveis que suportam diferentes tipos de funções para diferentes tipos de aplicações. Perfis estão relacionados ao conjunto de características que um CODEC utiliza para codificar um vídeo, enquanto níveis estão relacionados aos requisitos de processamento e memória. Os níveis definem, por exemplo, a máxima resolução e taxas de transferência.

No padrão H.264/AVC, as imagens são formadas por quadros de vídeo progressivo ou por campos para codificação entrelaçada. Quando um vídeo entrelaçado é utilizado, as imagens são divididas em dois campos, um contendo as linhas impares e outro contendo as pares. Os quadros decodificados podem ser utilizados como referência para predição dos quadros seguintes. Eles são organizados em duas listas, chamadas de lista 0 e lista 1.

O espaço de cores utilizado pelo H.264/AVC é o YCbCr, geralmente fazendo uso de subamostragem. Há diferentes características dependendo do tipo de perfil e nível utilizado. Uma imagem codificada é dividida em blocos chamados macroblocos (MB), compostos de 16x16 amostras de luminância e as correspondentes amostras de crominância, dependendo do perfil. Os macroblocos podem ainda ser divididos em blocos menores, dependendo do tipo de codificação utilizada (AGOSTINI, 2007).

Os macroblocos podem ser classificados em três tipos:

- 1. **Macrobloco tipo I (intra)** utiliza predição intra-quadro com área de predição de 16x16 ou 4x4 sub-blocos.

- 2. **Macrobloco tipo P (preditivo)** utiliza predição inter-quadros por meio de quadros de referência previamente codificados e armazenados na lista 0. Este tipo de macrobloco pode ser dividido em partições de tamanhos 16x16, 16x8, 8x16 e 8x8. Este último pode ser também subdividido em partições de sub-macrobloco de 8x4, 4x8 e 4x4.

- 3. **Macrobloco tipo B (bi-preditivo)** assim como os macroblocos do tipo P, um macrobloco tipo B também utiliza predição inter-quadros e pode ser subdividido da mesma forma, porém, este suporta também múltiplas referências, podendo assim utilizar quadros da lista 0 como da lista 1.

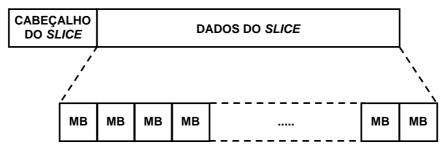

Em um quadro, os macroblocos são agrupados em um ou mais *slices*, que podem ser do tipo I, P, B, SP (*Switching P*) ou SI (*Switching I*). *Slices* do tipo I podem somente ter macroblocos do tipo I, *slices* do tipo P podem ter macroblocos do tipo I e P, e *slices* do tipo B podem ser os três tipo de macroblocos, I, P e B. *Slices* dos tipos SP e SI são análogos aos *slices* I e P, porém, usados em situações específicas de troca de contexto para aplicações de *streaming* vídeo (DINIZ, 2009). A Figura 2.2 ilustra a composição de um *slice*, destacando os MBs que o compõem.

Figura 2.2: Composição de um *slice* (PORTO, 2008).

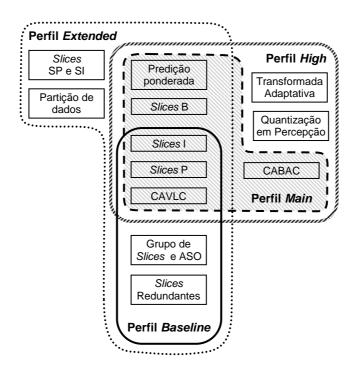

Na primeira versão do H.264/AVC, três perfis foram definidos: *Baseline*, *Main* e *Extended*. Depois, para dar suporte a vídeos de alta qualidade, uma extensão ao padrão foi criada, chamada de FRExt (*Fidelity Range Extensions*) (ITU-T, 2004; ITU-T, 2005). A FRExt produziu um grupo de quatro novos perfis chamados coletivamente de perfis *High* (SULLIVAN, 2004). A Figura 2.3 apresenta a divisão dos perfis.

O perfil *Baseline* suporta apenas macroblocos dos tipos I e P, e codificação de entropia com códigos de comprimento de palavra variável adaptativos ao contexto (CAVLC). O perfil *Main* introduz o suporte a macroblocos do tipo B, codificação de entropia utilizando codificação aritmética adaptativa ao contexto (CABAC) e vídeos entrelaçados. Estas duas últimas características não são suportadas no perfil *Extended*, entretanto, este suporta *slices* dos tipos SP e SI. Os perfis *High* foram um conjunto de quatro perfis com uma função comum: eles introduzem o tamanho de bloco adaptativo para a transformada (4x4 e 8x8), matrizes de quantização baseadas em percepção e uma representação sem perdas de regiões em específicas do conteúdo do vídeo (SULLIVAN, 2004).

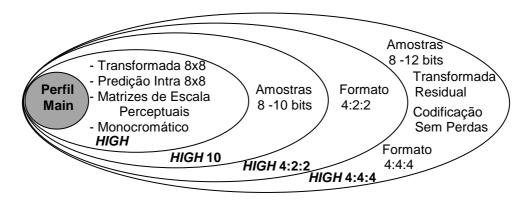

O perfil *High* (HP) inclui vídeos com 8 bits por amostra e com relação de cores 4:2:0. O perfil *High* 10 (Hi10P) suporta vídeos com 10 bits por amostra, também com uma relação de cores 4:2:0. O perfil *High* 4:2:2 (H422P) inclui suporte à relação de cor 4:2:2 e vídeos a 10 bits por amostra. Finalmente, o perfil *High* 4:4:4 (H444P) dá suporte à relação de cores 4:4:4 (ou seja, sem nenhuma subamostragem), suporte a vídeos com até 12 bits por amostra e, adicionalmente, suporta a codificação sem perdas em determinadas regiões do vídeo (AGOSTINI, 2007). A Figura 2.4 ilustra a relação entre esses perfis.

Figura 2.3: Perfis Baseline, Main, Extended e High do H.264/AVC (AGOSTINI, 2007).

Figura 2.4: Detalhamento dos perfis *High* do H.264/AVC (ZATT, 2008).

Além da divisão em diversos perfis, o padrão H.264/AVC também define 16 diferentes níveis em função da taxa de processamento e da quantidade de memória necessária para cada implementação. Com a definição do nível utilizado, é possível

deduzir o número máximo de quadros de referência e a máxima taxa de bits que pode ser utilizada (SULLIVAN, 2004).

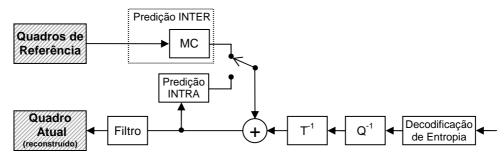

#### 2.2.3 Visão Geral do Decodificador

O processo de decodificação segundo o padrão H.264/AVC pode ser dividido nas seguintes etapas: decodificação de entropia, quantização inversa (Q<sup>-1</sup>), transformada inversa (T<sup>-1</sup>), predição intra-quadro (INTRA), predição inter-quadros (compensação de movimento - MC) e filtro redutor de efeito de bloco (Filtro) (RICHARDSON, 2003). Cada uma dessas etapas pode ser desenvolvida como um módulo separado em hardware. A Figura 2.5 ilustra como estas etapas são integradas no fluxo de decodificação de vídeo.

Figura 2.5: Diagrama de blocos de um decodificador H.264/AVC (AGOSTINI, 2007).

O decodificador recebe um *bitstream* de vídeo comprimido na entrada e extrai os elementos sintáticos para predição intra-quadro e inter-quadros, assim como as informações de resíduos, que são decodificadas utilizando códigos binários de tamanho fixo ou variável no módulo de decodificação de entropia, e processados pelos blocos de quantização e transformadas inversas (Q<sup>-1</sup> e T<sup>-1</sup>). Utilizando a informação decodificada a partir do *bitstream*, o decodificador cria um bloco de predição, utilizando o modo intra-quadro ou inter-quadros. O módulo de compensação de movimento (MC) em hardware é responsável pela reconstrução do quadro atualmente sendo decodificado a partir de quadros de referência. A predição intra-quadro reconstrói cada bloco de imagem a partir de seus vizinhos em um mesmo quadro.

### 2.3 Módulos de um Decodificador H.264/AVC

As próximas seções descrevem de forma breve os módulos para decodificação de vídeo segundo o padrão H.264/AVC, ilustrados na Figura 2.5 e correspondentes a cada uma das arquiteturas implementadas em ASIC neste trabalho. Informações detalhadas sobre cada um destes módulos podem ser encontradas em (AGOSTINI, 2007).

### 2.3.1 O Módulo de Decodificação de Entropia

O módulo *parser*, que inclui o decodificador de entropia, é o módulo responsável pela decodificação dos pacotes NAL (*Network Abstraction Layer*) recebidos no *bitstream*, que contém elementos de configuração ou *slices* de vídeo. Os parâmetros recebidos são basicamente codificados utilizando codificação Exp-Golomb (*Exponencial* Golomb) (SILVA, 2007). Inteiros de tamanho pré-determinado e, dependendo do perfil utilizado, podem ser codificados utilizando VLC (*Variable Length Coding*) ou ABC (*Arithmetic Binary Coding*).

O padrão H.264 utiliza tanto VLC quanto ABC, porém, não ambos ao mesmo tempo. Quando um algoritmo VLC é selecionado, as informações de resíduos provenientes da etapa de transformação e quantização são codificadas utilizando codificação CAVLC (Context-Based Adaptive Variable Length Coding) (RICHARDSON, 2003). Quando a codificação ABC é selecionada, é utilizado codificação CABAC (Context-Based Adaptative Binary Arithmetic Coding). Este último não é suportado nos perfis Baseline e Extended, e apresenta maior complexidade que o CAVLC, porém apresenta também maior eficiência, gerando assim um compromisso entre complexidade e eficiência (AGOSTINI, 2007).

No decodificador, o módulo de decodificação de entropia realiza as operações inversas da codificação feita com estes algoritmos no codificador, e os algoritmos CABAC e CAVLC são chamados de CABAD (*Context-Based Adaptative Binary Arithmetic Decoding*) e CALVD (*Context-Based Adaptive Variable Length Decoding*), respectivamente (DEPRÁ, 2009; PEREIRA, 2009).

Mais informações sobre codificação e decodificação Exp-Golomb, CABAC e CAVLC podem ser encontradas em (DEPRÁ, 2009; AGOSTINI, 2007).

## 2.3.2 O Módulo de Quantização Inversa (Q<sup>-1</sup>)

O módulo de quantização inversa está presente tanto nos codificadores como nos decodificadores. Ela realiza a correção de escala nas informações que passaram pelas transformadas diretas na codificação. Como na etapa de quantização na codificação ocorrem perdas, os resíduos obtidos após esta etapa de quantização inversa não são os mesmos que eram antes da etapa de quantização no codificador. Em cada bloco 4x4, a amostra superior esquerda é chamada de elemento DC. Os outros elementos são chamados de elementos AC. Após a operação de quantização inversa, o módulo de transformadas inversas (T-1) pode realizar a operação de IDCT (*Inverse Discrete Cosine Transform*) sobre os dados (PEREIRA, 2009). Este fluxo de operações pode ser visto na Figura 2.5.

O algoritmo de quantização inversa (Q<sup>-1</sup>) consiste na multiplicação das entradas por uma constante, a adição dos resultados por outra constante e finalmente o deslocamento da adição por outra constante. Estas constantes são influenciadas diretamente pelo parâmetro de quantização (QP), que é uma entrada externa que informa ao módulo Q<sup>-1</sup> qual é o passo de quantização (Qstep) que foi utilizado na codificação. Os Qsteps utilizados na quantização inversa são os mesmos utilizados durante a quantização direta (Q).

O QP pode variar de 0 a 51, e para cada QP, existe um Qstep. Os primeiros seis valores de Qstep, relativos aos seis primeiros QP, são definidos pelo padrão, como está apresentado na Tabela 3.4. Os demais Qsteps podem ser derivados dos seis primeiros, pois o Qstep dobra de valor a cada variação de 6 no valor do QP. Então o Qstep<sub>(6)</sub> é igual Qstep<sub>(0)</sub>  $\times$  2. As fórmulas para o cálculo da quantização inversa podem ser encontrados em (AGOSTINI, 2007).

Tabela 2.1: Relação entre QP e Ostep

| QP    | 0     | 1      | 2      | 3     | 4 | 5     | 6    | <br>12  |

|-------|-------|--------|--------|-------|---|-------|------|---------|

| Qstep | 0,625 | 0,6875 | 0,8125 | 0,875 | 1 | 1,125 | 1,25 | <br>2,5 |

Fonte: AGOSTINI, 2007. p. 58.

## 2.3.3 O Módulo de Transformadas Inversas (T<sup>-1</sup>)

O módulo de transformadas inversas (T¹) está presente tanto nos codificadores quanto nos decodificadores. As transformadas inversas realizam exatamente a operação oposta das transformadas diretas (T) no processo de codificação, ou seja, convertem as informações de resíduos do domínio de frequências para o domínio espacial, para que estas sejam adicionadas aos resultados de predição. As operações das transformadas inversas são muito semelhantes às operações das transformadas diretas. Transformadas chamadas de Hadamard 2x2 e Hadamard 4x4 são calculadas diretamente sobre os coeficientes DC provenientes da etapa de quantização, antes da etapa de quantização inversa. Depois destas operações, os coeficientes são entregues à etapa de quantização inversa para só então serem processados pela etapa de DCT 2-D inversa (IDCT 2-D) (DINIZ, 2009). As fórmulas para o cálculo das transformadas podem ser encontradas em (AGOSTINI, 2007).

## 2.3.4 O Módulo de Predição Intra-quadro (Intra)

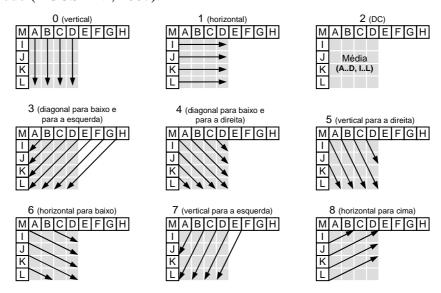

O módulo de predição intra-quadro é responsável pela predição de um quadro de saída baseado em valores previamente codificados do *slice* atual dos pixels acima e à esquerda do bloco a ser codificado. Este tipo de predição é utilizado em macroblocos do tipo I. Para amostras de luminância, o tamanho do bloco para predição pode ser de 16x16 ou 4x4. Há 9 diferentes modos de predição de blocos 4x4 são utilizados e 4 modos quando blocos 16x16 são utilizados.

A Figura 2.6 apresenta os nove tipos diferentes de codificação no modo intra-quadro para blocos 4x4 de luminância. Os modos 0 e 1 fazem uma simples extrapolação (uma cópia) dos pixels das bordas verticais ou horizontais para todas as posições do bloco. O modo DC (2) faz uma média entre as amostras das bordas e copia o resultado para todas as posições do bloco. Os demais modos (3 a 8) fazem uma média ponderada das amostras das bordas, de acordo com a direção da seta na Figura 2.6.

A predição da crominância é realizada diretamente sobre blocos 8x8 e utiliza 4 modos distintos de predição, mas os dois componentes de crominância utilizam sempre o mesmo modo (AGOSTINI, 2007).

Figura 2.6: Nove modos da predição intra-quadro para blocos de luminância 4x4 (AGOSTINI, 2007).

Durante a decodificação de vídeo, o módulo *parser* passa para a predição intraquadro as informações de tamanho de bloco e tipo de predição escolhida pelo codificador. A predição intra-quadro gera na saída informações que deverão ser somadas com os resíduos do processo de codificação.

#### 2.3.5 O Módulo de Compensação de Movimento (MC)

O módulo de compensação de movimento faz parte da predição inter-quadros, que é composta pela compensação de movimento (MC) e pela estimativa de movimento (ME), este último apenas presente no codificador de vídeo. Ambos juntos, MC e ME, apresentam a maior complexidade em um codificador de vídeo. A predição inter-quadros é parte que demanda maior poder computacional em um CODEC H.264/AVC, consumindo mais de 50% do tempo de processamento em um decodificador e 80% em um codificador (ZATT, 2008b).

Como todos os módulos presentes nos processos de codificação e decodificação, o módulo de compensação de movimento trabalha sobre as regiões dos quadros, chamadas de macroblocos (MB), sobre os blocos de 16x16 amostras de luminância e sobre as amostras de crominância associadas a estas. A compensação de movimento opera adicionando um MB já predito (de um quadro de referência) às amostras de resíduos com o intuito de reconstruir o MB atual (ZATT, 2008b).

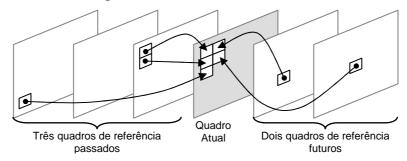

Muitos detalhes sobre a operação da compensação de movimento são descritos no padrão H.264/AVC. Entre algumas das funções do MC no decodificador, se destacam o tratamento de múltiplos tamanhos de partições de macroblocos e a utilização de múltiplos quadros de referência anteriores e posteriores, armazenados nas listas 0 e 1. A Figura 2.7 ilustra a utilização destas duas listas para armazenamento de quadros de referência, de onde podem ser pesquisados os macroblocos para predição do macrobloco sendo atualmente processado.

Figura 2.7: Utilização de múltiplos quadros de referência (AGOSTINI, 2007).

#### 2.3.5.1 Arquitetura do Módulo de Compensação de Movimento (MC)

Em (AZEVEDO, 2007), é apresentada uma arquitetura para compensação de movimento de acordo com o perfil *Main* do H.264/AVC, chamada de MoCHA. Em (ZATT, 2008a; ZATT, 2008b) é apresentada uma arquitetura para compensação de movimento do H.264/AVC, desenvolvida para atingir desempenho capaz de decodificar, em tempo real, vídeos com resolução HD1080p (1920x1080 pixels) a 30 quadros por segundo. Esta arquitetura foi chamada de HP422-MoCHA (*High Profile* 4:2:2 MoCHA), e é uma extensão feita sobre a arquitetura MoCHA (AZEVEDO, 2007)

original, tornando-a capaz de suportar as ferramentas do perfil *High 4:2:2* do padrão H.264/AVC. O suporte ao perfil *High 4:2:2* visa atender ao padrão SBTVD, adotado no Brasil como padrão de televisão digital (ZATT, 2008a).

A seguir, são apresentados os principais componentes da arquitetura MoCHA e sua extensão para o perfil *High* 4:2:2, a HP422-MoCHA. Maiores detalhes arquiteturais sobre máquinas de estados e detalhes de implementação em VHDL podem ser consultados em (AZEVEDO, 2007; ZATT, 2008a).

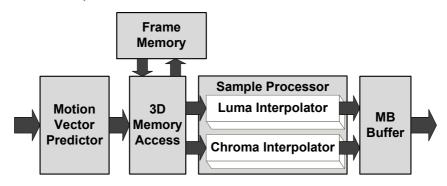

A Figura 2.8 apresenta a arquitetura do HP422-MoCHA, desenvolvida em um *pipeline* hierárquico e o mais elevado nível da hierarquia é formado por três módulos principais: o preditor de vetores de movimento (*Motion Vector Predictor* - MVP), acesso à memória (*3D Frame Memory Access* - 3D-FMA) e processamento de amostras (*Sample Processor* - SP).

Figura 2.8: Arquitetura para compensação de movimento HP422-MoCHA (ZATT, 2008a).

A compensação de movimento reconstrói o quadro atual utilizando como referências as regiões de quadros previamente decodificados. As regiões de referência são indicadas por vetores de movimento (*Motion Vector* – MV). Estes MVs são calculados por meio de um processo chamado de predição de vetores de movimento (*Motion Vector Prediction* – MVPr).

O primeiro bloco, o preditor de movimentos (*Motion Vector Predictor*-MVP), foi desenvolvido para trabalhar com o filtro de compensação apresentado em (AZEVEDO, 2007) com o objetivo de implementar um módulo de compensação de movimentos para o perfil *Main* do H.264/AVC. A frequência de 100 MHz foi determinada para que o módulo fosse capaz de decodificar vídeos com resolução HD1080p e subamostragem 4:2:0, fornecendo uma amostra processada a cada ciclo de relógio. Para a subamostragem utilizada, há 256 amostras de luminância e 128 amostras de crominância em um macrobloco. Assim, o preditor de movimentos pode utilizar até 384 ciclos de relógio para processar um macrobloco sem que o desempenho seja limitado.

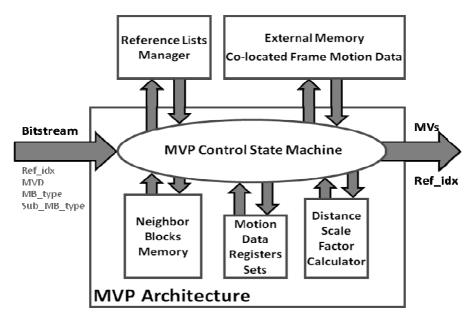

A arquitetura de hardware desenvolvida para o MVP é composta de três unidades: *Neighbor Blocks Memory, Motion Data Registers Sets* e *MVP Control State Machine*. Adicionalmente, uma arquitetura desenvolvida para cálculo de *Distance Scale Factor* foi desenvolvida com o intuito de suportar a predição direta temporal (ZATT, 2008). Esta arquitetura está ilustrada na Figura 2.9.

Figura 2.9: Arquitetura do módulo Preditor de Vetores de Movimento (ZATT, 2007).

O módulo de compensação de movimento do H.264/AVC demanda uma grande largura de banda para gerenciamento de dados na memória, que aumenta bastante quando considerado o perfil *High* 4:2:2. Esta largura de banda é extremamente sensível ao aumento da resolução de vídeo, pois quando vídeos de alta resolução (HDTV) são processados, a largura de banda necessária para o gerenciamento de dados em memória é um dos gargalos de um decodificador.

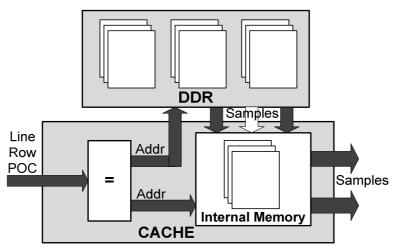

Portanto, com o intuito de garantir o melhor desempenho possível em relação à manipulação de dados em memória no módulo de compensação de movimentos, foi projetada a arquitetura para o bloco de acesso à memória (3D Frame Memory Access), que é indexada por tags compostas utilizando posições verticais e horizontais de uma determinada área em um quadro de referência. O número do quadro de referência sendo manipulado também é utilizado e corresponde à ordem temporal dele na sequência de vídeo sendo chamado de POC (Picture Order Count) (ZATT, 2008). A Figura 2.10 apresenta um diagrama de blocos da arquitetura 3D Frame Memory Access.

Figura 2.10: Arquitetura do módulo de acesso à memória do MC (ZATT, 2007).

O módulo de processamento de amostras (*Sample Processor-SP*) executa as transformações nas amostras, durante a compensação de movimentos. Na arquitetura do SP, o processamento de amostras de luminância e crominância ocorre em paralelo, porém, crominância azuis e vermelhas são processadas serialmente pela parte operativa de crominância. Esta estratégia é necessária para atingir o *throughput* para decodificação de vídeos HD1080p, em tempo real, sem a necessidade de recursos de hardware adicionais. Para lidar com a complexidade intrínseca do controle de blocos de tamanhos diferentes, foi utilizada a abordagem de quebrar todos os blocos no menor tamanho de bloco possível. Na parte operativa de luminância, os dados são processados em amostras de 4x4, enquanto que na de crominância, em matrizes de 2x2 e 4x2, utilizando subamostragem de 4:2:0 ou 4:2:2, respectivamente. Para subamostragens de 4:0:0, a parte operativa de crominância fica aguardando (ZATT, 2008).

A Tabela 2.2 apresenta os resultados de síntese para FPGA obtidos em (AZEVEDO, 2007; ZATT, 2008a) para as arquiteturas MoCHA e HP422-MoCHA, respectivamente. Para obtenção destes resultados, foi utilizado o dispositivo de FPGA Virtex II Pro (XC2VP30-7) como alvo de síntese de ambas as prototipações.

|             | MVP   | MA    | SP    | MoCHA<br>Main 4:2:0 | HP422-<br>MoCHA | Increase % |

|-------------|-------|-------|-------|---------------------|-----------------|------------|

| Slices      | 3,494 | 951   | 5,511 | 8,465               | 10,530          | 24%        |

| Flip Flops  | 3,358 | 723   | 5,904 | 5,671               | 6,313           | 11%        |

| LUTs        | 5,961 | 1,175 | 6,742 | 10,835              | 13,894          | 28%        |

| BRAM        | 3     | 24    | 0     | 21                  | 27              | 28%        |

| Multipliers | 0     | 0     | 8     | 12                  | 12              | 0%         |

Tabela 2.2: Resultados de síntese FPGA para MoCHA e HP422-MoCHA

Fonte: ZATT, 2008a. p. 75.

#### 2.3.6 O Módulo Filtro Redutor de Efeito de Bloco (Filtro)

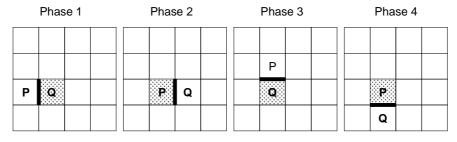

Como imagens são processadas em blocos, segundo o padrão H.264/AVC, é possível que nos blocos reconstruídos, haja efeitos de bloco em suas bordas, devido à forma como estes foram processados. Para reduzir este efeito, um filtro redutor de efeito de bloco é aplicado nas bordas dos blocos no final do processo de decodificação, ou seja, o objetivo do filtro é suavizar o efeito de bloco do quadro reconstruído antes que ele seja utilizado como quadro de referência para fazer a predição de um novo macrobloco do tipo inter-quadros. Este filtro produz um efeito significante na qualidade subjetiva do vídeo reconstruído (PEREIRA, 2009). Para cada bloco, as quatro bordas distintas são filtradas separadamente, na sequência apresentada na Figura 2.11.

Figura 2.11: Sequência de processamento de bordas no filtro. (ROSA, 2010).

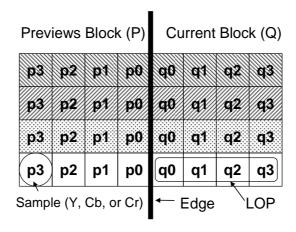

Para cada borda de bloco, o filtro é aplicado aos valores de pixels perpendiculares à borda. A convenção de nomes para os pixels ao redor das bordas é mostrada na Figura 2.12. Tanto os pixels do bloco atualmente sendo processado (bloco Q), quanto os do bloco passado (bloco P), podem sofrer modificações. Os que já tiverem sido modificados por outro estágio de filtragem podem ser modificados novamente em uma operação subseqüente. O algoritmo para filtragem é adaptativo, assim, o *boundary strength* (bS), parâmetro que define a força de filtragem, é calculado levando em consideração os seguintes elementos: os valores dos pixels, as posições deles dentro do macrobloco, o tipo de predição aplicada (inter ou intra), os vetores de predição (predição inter) e o QP. O bS pode assumir cinco valores diferentes, variando de 0 (sem filtragem) a 4 (filtragem máxima), dependendo do contexto e localização da borda (ROSA, 2010).

Figura 2.12: Convenção de nomes para pixels ao redor das bordas. (ROSA, 2010).

#### 2.3.6.1 Arquitetura do Filtro Redutor de Efeito de Bloco

Em (ROSA, 2010), é apresentada uma arquitetura de hardware para o módulo filtro redutor de efeito de bloco, que pode ser utilizada em um CODEC H.264/AVC. Esta implementação foi projetada para atingir ou superar os requisitos necessários para processamento de vídeos com resolução HDTV (1920x1080 a 30fps) de acordo com o perfil *Main* do H.264/AVC.

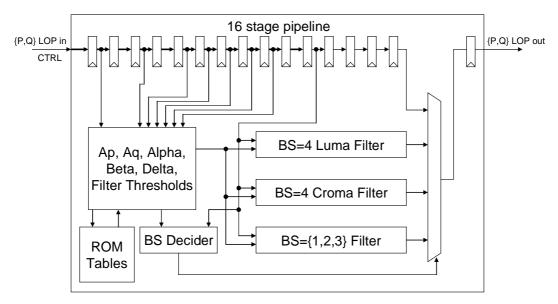

O filtro é subdividido em alguns sub-módulos, sendo o mais importante deles chamado de *edge filter*. Este é responsável por toda a funcionalidade de filtragem. O restante dos módulos executa apenas operações de controle de sequência e memória. A arquitetura do *edge filter* recebe como entrada um LOP (*Line Of Pixels* – Figura 2.13) por ciclo de relógio para blocos Q e P e produz LOPs filtrados Q' e P'. Utilizando esse esquema, uma borda de bloco inteira pode ser enviada ao *edge filter* a cada quarto ciclos de relógio.

A arquitetura do sub-módulo *edge\_filter* é apresentada na Figura 2.13. Ela é implementada utilizando um *pipeline* de 16 estágios, assim, as amostras filtradas só estão disponíveis na saída após 16 ciclos do momento em que são recebidas.

Figura 2.13: Arquitetura do módulo edge filter (ROSA, 2010).

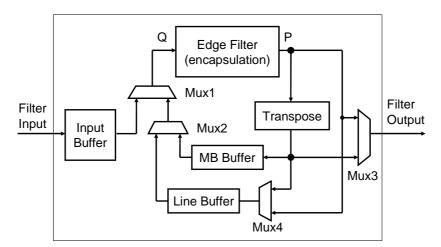

A Figura 2.14 ilustra toda a arquitetura do filtro redutor de efeito de bloco, em que podem ser vistas as interconexões do módulo *edge filter* com os demais. O módulo *transpose* é utilizado para converter amostras do bloco alinhadas verticalmente para amostras alinhadas de forma horizontal, permitindo que estas possam ser processadas pelo *edge filter*. O módulo *input buffer* é necessário para o reordenamento dos blocos, uma vez que estes são enviados para processamento em uma ordem diferente da que devem ser processados. Os módulos MB *buffer* e *line buffer* são utilizados para armazenar blocos e determinadas informações sobre eles (QP, tipo do bloco, *offset* de filtragem, estado), que não são completamente filtradas. Para detalhes sobre a implementação de todos os módulos, o trabalho de (ROSA, 2010) pode ser consultado.

Figura 2.14: Arquitetura do filtro redutor de efeito de bloco (ROSA, 2010).

A Tabela 2.3 apresenta os resultados obtidos no trabalho de (ROSA, 2009) para o número de LUTs (*Look-up-Table*) e BRAMs (*Block RAM*) utilizados na síntese desta arquitetura para os dispositivos de FPGA Virtex II Pro (XC2VP30) e Xilinx Virtex-5 (XC5VLX30).

Tabela 2.3: Resultados de síntese do filtro para FPGA

| FPGA Device  | XC2VP30          | XC5VLX30         |

|--------------|------------------|------------------|

| LUTs         | 4008/27392 (14%) | 4275/19200 (21%) |

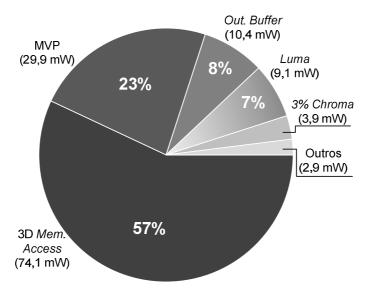

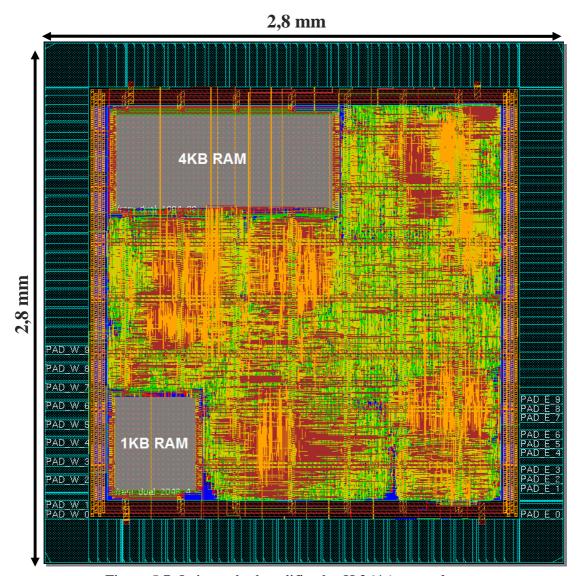

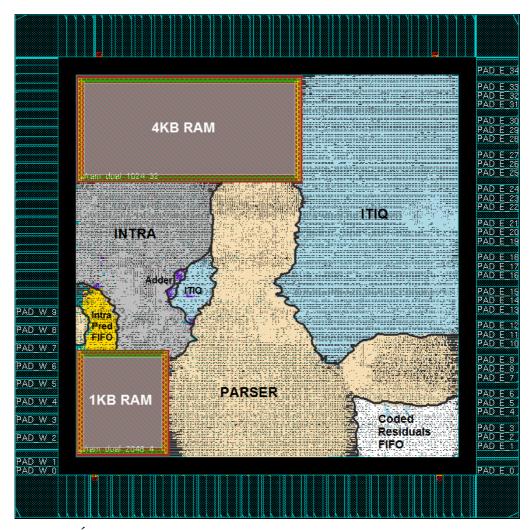

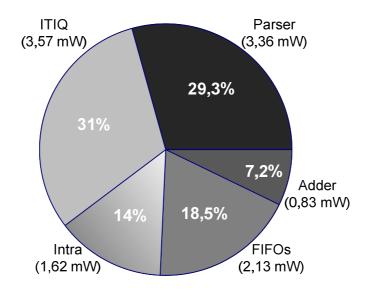

| <b>BRAMs</b> | 20/136 (14%)     | 7/32 (21%)       |