### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

RENATO DONIZETE PERALTA

# Satisfiability-Based Covering of AIGs Using KL-cuts

Thesis presented in partial fulfillment of the requirements for the degree of Doctor of Microeletronics

Advisor: Prof. Dr. André Inácio Reis

Porto Alegre July 2024 Peralta, Renato Donizete

Satisfiability-Based Covering of AIGs Using KL-cuts / Renato Donizete Peralta. – Porto Alegre: PGMICRO da UFRGS, 2024.

120 f.: il.

Thesis (Ph.D.) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica, Porto Alegre, BR–RS, 2024. Advisor: André Inácio Reis.

1. And-inverter graph. 2. Electronic design automation. 3. Cuts in AIGs. 4. KL-cuts. 5. Logic synthesis. 6. Very-largescale integration. 7. Satisfiability. I. Reis, André Inácio. II. Título.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL Reitor: Prof. André Bulhões Mendes Vice-Reitora: Prof<sup>a</sup>. Patricia Pranke Pró-Reitor de Pós-Graduação: Prof<sup>a</sup>. Júlio Otávio Jardim Barcellos Diretora do Instituto de Informática: Prof<sup>a</sup>. Carla Maria Dal Sasso Freitas Coordenador do PGMICRO: Prof. Cláudio Radtke Bibliotecário-chefe do Instituto de Informática: Alexsander Borges Ribeiro

### ABSTRACT

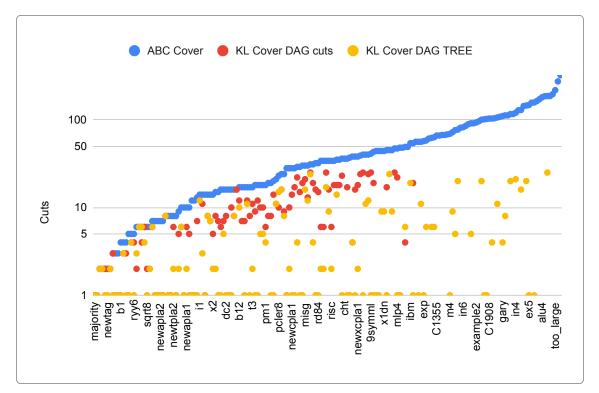

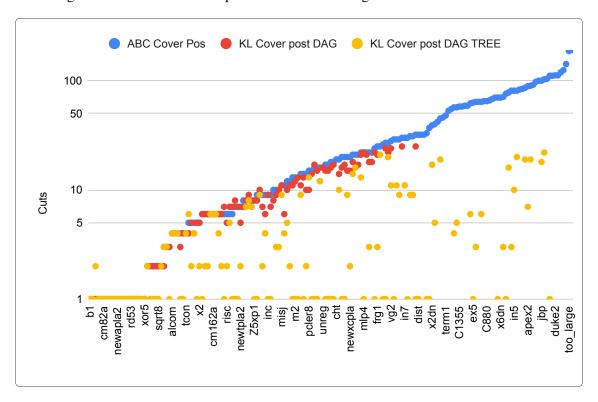

The rapid advancement of Very-large-scale integration (VLSI) silicon integration has revolutionized the electronics industry, enabling the integration of billions of transistors into a single integrated circuit. This complexity necessitates the use of Electronic Design Automation (EDA) tools for VLSI design. These tools automate various tasks, with the design process typically divided into logic synthesis and physical design stages. Logic synthesis involves capturing the initial logic description and generating a netlist of interconnected cell instances, while physical design focuses on placing and routing these instances to create a circuit layout ready for fabrication. Over the past two decades, logic synthesis has heavily relied on the And-Inverter-Graph (AIG) data structure for its scalability and result quality. This thesis introduces a contribution to logic synthesis based on AIGs, specifically focusing on computing AIG covers with KL-cuts, where both the number of inputs (K) and outputs (L) are controlled. While previous work has proposed the use of KL-cuts in synthesis flow, efficient algorithms for covering AIGs with KL-cuts have been lacking. This thesis addresses this issue by presenting an algorithm to optimize this task. Additionally, a detailed review of AIG cut types is provided. Existing synthesis methodologies often lack efficient algorithms for AIG covering with KL-cuts, necessitating the development of optimized solutions. In this thesis are proposed two novel contributions to logic synthesis using AIGs, focusing on KL-cut computation to enhance synthesis efficiency. The first contribution introduces a novel method for expanding single-output cuts into KL-cuts. The second contribution presents a satisfiability-based approach for generating AIG covers using KL-cuts. Experimental results validate the effectiveness of these contributions. The proposed cut expansion method achieved a 1.25x speedup compared to the MFFW method. Furthermore, the proposed approach successfully generated KL-cut covers with a reduction: 49.01% compared to K-cuts from ABC and 7.51% compared to multi-output covers derived from post-processing of ABC results. Keywords: And-inverter graph. electronic design automation. cuts in AIGs. KL-cuts. logic synthesis. very-large-scale integration. satisfiability.

### Cobertura de AIGs Baseada em Satisfatibilidade Usando KL-cuts

#### **RESUMO**

O rápido avanço da integração de silício em Integração em Larga Escala (VLSI) revolucionou a indústria de eletrônicos, permitindo a integração de bilhões de transistores em um único circuito integrado. Essa complexidade exige o uso de ferramentas de Automação de Projeto Eletrônico (EDA) para o design de VLSI. Essas ferramentas automatizam várias tarefas, com o processo de design tipicamente dividido em etapas de síntese lógica e design físico. A síntese lógica envolve capturar a descrição lógica inicial e gerar uma lista de interconexões entre instâncias de células, enquanto o design físico se concentra na colocação e roteamento dessas instâncias para criar um layout de circuito pronto para a fabricação. Nas últimas duas décadas, a síntese lógica tem dependido fortemente da estrutura de dados And-Inverter-Graph (AIG) devido à sua escalabilidade e qualidade dos resultados. Esta tese apresenta uma contribuição para a síntese lógica baseada em AIGs, especificamente focando no cálculo de coberturas de AIG com KL-cuts, onde tanto o número de entradas (K) quanto de saídas (L) são controlados. Embora trabalhos anteriores tenham proposto o uso de KL-cuts em fluxos de síntese, algoritmos eficientes para cobrir AIGs com KL-cuts têm sido escassos. Esta tese aborda essa questão apresentando um algoritmo para otimizar essa tarefa. Além disso, é forne uma revisão detalhada dos tipos de cortes em AIGs. Metodologias de síntese existentes frequentemente carecem de algoritmos eficientes para cobertura de AIG com KL-cuts, exigindo o desenvolvimento de soluções otimizadas. Nesta tese, são propostas duas contribuições inovadoras para a síntese lógica usando AIGs, com foco no cálculo de KL-cuts para melhorar a eficiência da síntese. A primeira contribuição introduz um método inovador para expandir cortes de saída única em KL-cuts. A segunda contribuição apresenta uma abordagem baseada em satisfatibilidade para gerar coberturas de AIG usando KL-cuts. Resultados experimentais validam a eficácia dessas contribuições. O método de expansão de cortes proposto alcançou uma aceleração de 1,25 vezes em comparação com o método MFFW. Além disso, a abordagem proposta gerou com sucesso coberturas KL-cut com uma redução de 49,01% em comparação com K-cuts do ABC e 7,51% em comparação com coberturas multi-saídas derivadas do pós-processamento dos resultados do ABC.

**Palavras-chave:** Grafo and-inverter, automação de projeto eletrônico, cortes em AIGs, KL-cuts, síntese lógica, integração em larga escala, satisfatibilidade.

### LIST OF ABBREVIATIONS AND ACRONYMS

- AIG And-Inverter Graph

- ASIC Application-Specific Integrated Circuit

- BDD Binary Decision Diagram

- EDA Electronic Design Automation

- FFC Fanout-Free Cone

- FFW Fanout-Free Window

- FPGA Field-Programmable Gate Array

- LUT Look-Up Table

- MFFC Maximum Fanout-Free Cone

- MFFW Maximum Fanout-Free Window

- PI Primary Input

- PO Primary Output

- SAT Satisfiability

- TT Truth Table

- SOP Sum of Products

- TFI Transitive Fanin

- TFO Transitive Fanout

- VLSI Very-large-scale Integration

- IC Integrated Circuit

- MtM More than Ten Million Benchmark

# LIST OF FIGURES

| Figure 3.1 ROBDD representing a Full Adder with inputs a, b, and cin                        | 21 |

|---------------------------------------------------------------------------------------------|----|

| Figure 3.2 Example of an AIG representing a two-input full adder                            | 22 |

| Figure 3.3 Transitive fanin and transitive fanout of node 12.                               |    |

| Figure 3.4 AIG elements.                                                                    |    |

| Figure 3.5 Rewriting method in AIG.                                                         | 27 |

| Figure 3.6 Example of a K-cut                                                               |    |

| Figure 3.7 Example of a valid cover with non-superposed cuts.                               |    |

| Figure 3.8 Example of an invalid cover with non-superposed cuts.                            |    |

| Figure 3.9 Example of a valid cover with superposed cuts                                    |    |

| Figure 3.10 Example of an invalid cover with superposed cuts                                |    |

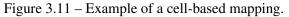

| Figure 3.11 Example of a cell-based mapping                                                 |    |

| Figure 3.12 Example of FPGA-based mapping.                                                  |    |

| Figure 4.1 <i>K</i> -cut example                                                            | 36 |

| Figure 4.2 Side-outputs of the $cut_1$ and $cut_3$ . The blue arrow illustrates the K-cut's |    |

| output and the red arrow illustrates the side edges                                         | 37 |

| Figure 4.3 KL-cut in AIG.                                                                   | 38 |

| Figure 4.4 Example of <i>L</i> -cut crossing the TFO of <i>K</i> -cuts                      | 39 |

| Figure 4.5 KL-cut cover in AIG. The blue arrows represent the KL-cuts outputs               |    |

| Figure 4.6 Example of a not valid <i>KL</i> -cut for $L = 2$ .                              | 41 |

| Figure 4.7 Example of when a K-cut is a KL-cut with $L = 1$                                 |    |

| Figure 4.8 Circuit partitioned into KL-cuts.                                                |    |

| Figure 4.9 Points of view of a <i>1L</i> -cut                                               |    |

| Figure 4.10 $1 \times 1 (m \times n)$ Window for node N.                                    |    |

| Figure 4.11 Fanin cone of the node 10                                                       |    |

| Figure 4.12 Fanout cone of the node 8                                                       |    |

| Figure 4.13 All Fanout-Free Cones of node 5                                                 |    |

| Figure 4.14 MFFC                                                                            |    |

| Figure 4.15 MFFW                                                                            |    |

| Figure 5.1 Backcut example                                                                  | 62 |

| Figure 5.2 Martinello's algorithm.                                                          | 64 |

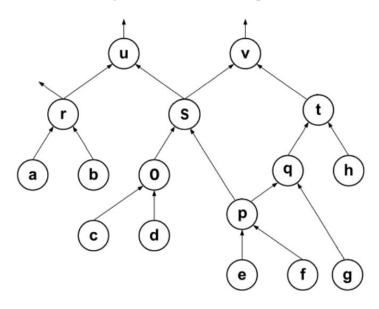

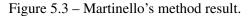

| Figure 5.3 Martinello's method result.                                                      | 65 |

| Figure 5.4 <i>addInsts()</i> function illustration                                          | 67 |

| Figure 5.5 Machado's algorithm.                                                             | 68 |

| Figure 5.6 Machado's algorithm result.                                                      | 68 |

| Figure 5.7 MFFW expansion.                                                                  | 70 |

| Figure 5.8 Example of an AIG covered using only K-cut, with K equals 3.                     | 72 |

| Figure 5.9 Another cover using K-cuts with k equals 3                                       |    |

| Figure 5.10 Cover example using $KL$ -cuts with $K$ equals 3 e $L$ equals 2                 | 73 |

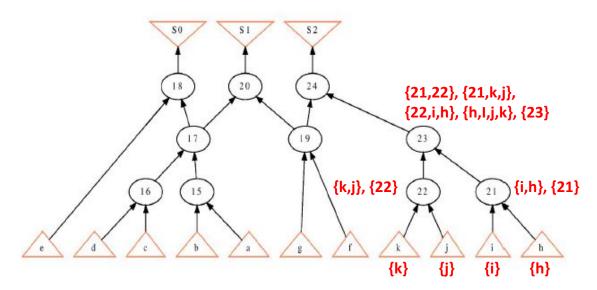

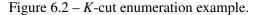

| Figure 6.1 <i>K</i> -cut enumeration example                                                |    |

| Figure 6.2 K-cut enumeration example                                                        |    |

| Figure 6.3 Example of cuts K generated with K=3 for a given AIG.                            | 79 |

| Figure 6.4 Result of the markSupport() method at a piece of the circuit                     |    |

| Figure 6.5 Intersection of the fanins support list                                          | 83 |

| Figure 6.6 Identifying the outputs of the cut $C_1$ .                                       | 85 |

| Figure 6.7 AIG example for SAT formulation.                                                 | 87 |

|                                                                                             |    |

| Figure 6.8 CNF encoding for only one cut for node 18                              | 89   |

|-----------------------------------------------------------------------------------|------|

| Figure 6.9 BDD for Cuts With Unit Costs.                                          |      |

| Figure 6.10 BDD for solutions with up to 2 Cuts.                                  |      |

| Figure 6.11 ROBDD for solutions with up to 2 Cuts                                 |      |

| Figure 6.12 BDD for a problem involving four cuts with different costs. Each ter- |      |

| minal node shows the total cost of each combination of cuts                       | 94   |

| Figure 6.13 BDD for a problem involving four cuts, showing combinations of cuts   |      |

| that meet the maximum predefined cost of 2                                        | 95   |

| Figure 6.14 ROBDD for the problem with different costs for the cuts               | 95   |

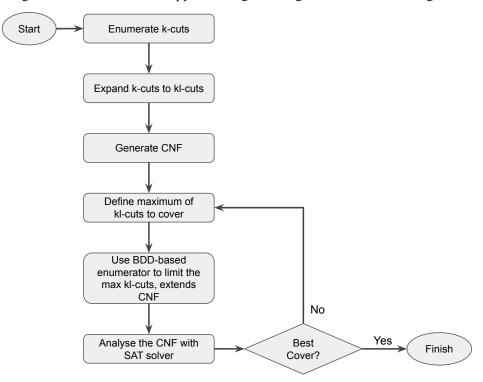

| Figure 6.15 Flowchart of approach to generating minimum cover using SAT           | 97   |

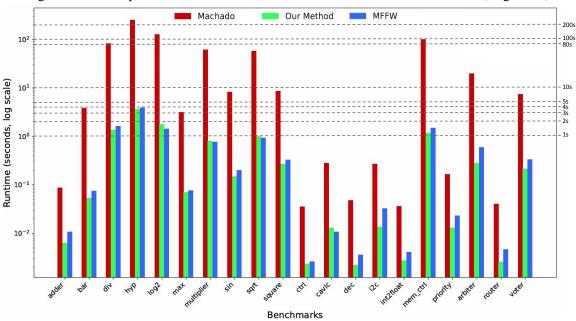

| Eigure 7.1 Comparison of Buntimes for Machada, Our Mathad, and MEEW (Log          |      |

| Figure 7.1 Comparison of Runtimes for Machado, Our Method, and MFFW (Log          | 101  |

| Scale)                                                                            | .101 |

| Figure 7.2 Comparison of Cover Size Using Single-Output Cuts (from ABC) vs.       | 104  |

| Multi-Output Cuts (with <i>KL-cuts</i> )                                          |      |

| Figure 7.3 Cover Size Comparison of Results of Figure 7.2 after the Post-Process  | .105 |

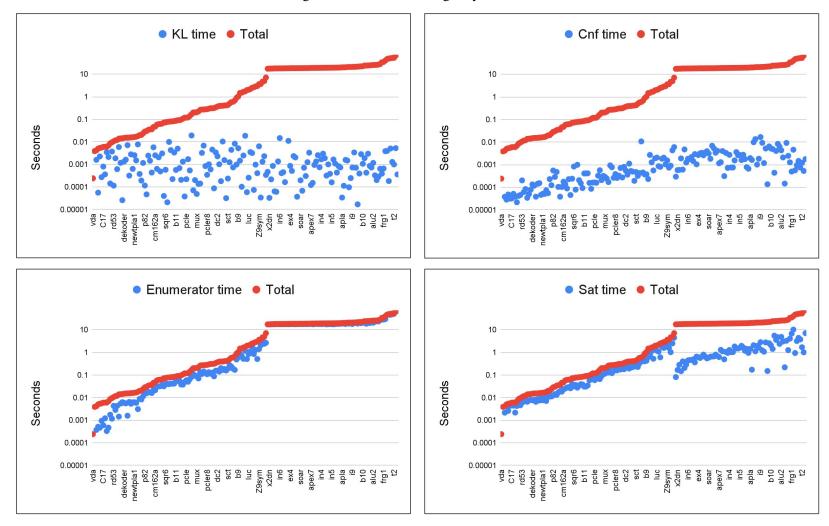

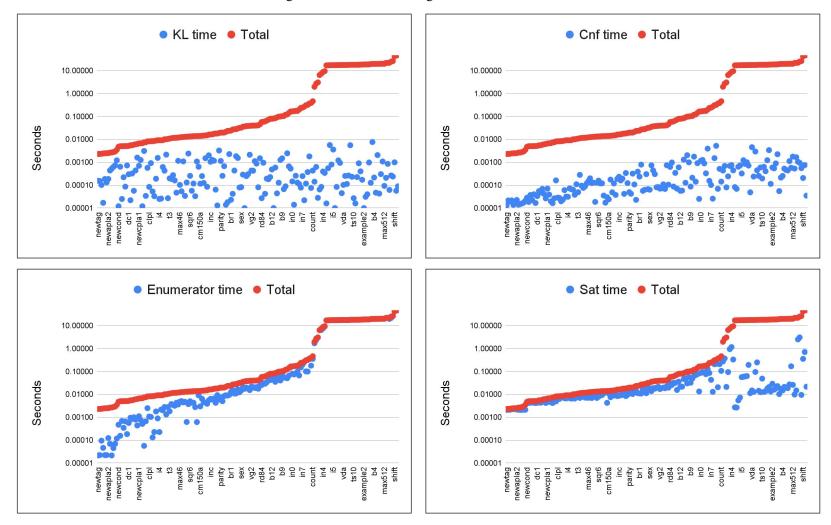

| Figure 7.4 Runtime using only DAG cuts.                                           | .107 |

| Figure 7.5 Runtime using DAG and TREE cuts.                                       | .109 |

|                                                                                   |      |

|                                                                                   |      |

## LIST OF TABLES

| Table 3.1 | Truth table of a full adder.                                      | 18  |

|-----------|-------------------------------------------------------------------|-----|

| Table 5.1 | All k-cuts for the AIG of Figure 3.2                              | 55  |

| Table 5.2 | K-cuts and Backcuts of Figure 5.1.                                | 63  |

| Table 5.3 | Summary of the coverage results using k-cuts and kl-cuts.         | 74  |

| Table 6.1 | Cortes K de três entradas, e seus custos, do AIG da Figura 6.3    | 81  |

| Table 6.2 | Result of the Methods mark_support() and forward() in the AIG 6.3 | 84  |

| Table 6.3 | KL-cuts used for SAT formulation                                  | 87  |

|           | Runtime comparison in milliseconds.                               |     |

| Table 7.2 | Cover without optimization for EPFL circuits                      | 111 |

|           | Clause size and runtime                                           |     |

# LIST OF ALGORITHMS

| 6.1 | KL-Cuts enumeration Algorithm.            | .80 |

|-----|-------------------------------------------|-----|

| 6.2 | Prepare KL-Cuts Algorithm                 | .80 |

| 6.3 | Mark Support Algorithm                    | .81 |

| 6.4 | Forward KL-Cuts Algorithm.                | .83 |

| 6.5 | Define KL-Cuts outputs Algorithm.         | .84 |

| A.1 | KL-Cuts enumeration Algorithm (Complete)1 | 120 |

# CONTENTS

| 1 INTRODUCTION                                                  |     |

|-----------------------------------------------------------------|-----|

| 2 MOTIVATION FOR KL CUTS                                        | 15  |

| 2.1 About This Chapter                                          |     |

| 2.2 KL-cuts and multi-output LUTs                               | .15 |

| 2.3 KL-cuts and multi-output cells in a library                 | 15  |

| 2.4 <i>KL</i> -cuts as a partitioning method                    | 16  |

| 2.5 Contributions of this chapter                               | 16  |

| 3 BASIC CONCEPTS                                                |     |

| 3.1 About this chapter                                          | 17  |

| 3.2 Boolean functions and their representation                  |     |

| 3.2.1 Historical evolution of Boolean functions representations | 17  |

| 3.2.2 Truth tables                                              |     |

| 3.2.3 Sum of Products                                           | 19  |

| 3.2.4 Binary Decision Diagrams                                  |     |

| 3.2.5 And-Inverter Graphs                                       |     |

| 3.3 Physical Implementation Technologies                        |     |

| 3.3.1 ASICs                                                     |     |

| 3.3.1.1 Cell Library                                            |     |

| 3.3.1.2 Library-based Design specificities                      |     |

| 3.3.2 FPGAs                                                     |     |

| 3.3.2.1 Look-up Tables - LUTs                                   |     |

| 3.3.2.2 LUT-based Design specificities                          |     |

| 3.4 AIGs-based synthesis                                        |     |

| 3.4.1 Cuts in AIGs                                              |     |

| 3.4.2 Covers of an AIG                                          |     |

| 3.5 Technology Mapping                                          |     |

| 3.5.1 Mapping to cell-based ASICs                               |     |

| 3.5.2 Mapping to FPGAs                                          |     |

| 3.5.3 Cost Functions                                            |     |

| 3.5.3.1 Area                                                    |     |

| 3.5.3.2 Delay                                                   |     |

| 3.5.3.3 Power                                                   |     |

| 3.5.3.4 Design Constraints                                      |     |

| 3.6 The EPFL Benchmarks                                         |     |

| 3.7 Contributions of this chapter                               |     |

| 4 A TAXONOMY OF AIG CUTS                                        |     |

| 4.1 About this Chapter                                          |     |

| 4.2 Structural Differences Among Different Types of Cuts        |     |

| 4.2.1 <i>K</i> -cut                                             |     |

| 4.2.2 <i>KL</i> -cut                                            |     |

| 4.2.2.1 <i>IL</i> -cut                                          |     |

| 4.2.3 Windowing                                                 |     |

| 4.2.3.1 Fanin Cone                                              |     |

| 4.2.3.2 Fanout Cone                                             |     |

| 4.2.3.3 Fanout-Free Cone                                        |     |

| 4.2.3.4 Maximum Fanout-Free Cone                                |     |

| 4.2.3.5 Maximum Fanout-Free Window                              |     |

| 4.2.4 Structural differences between MFFW and KL-cuts           | 51  |

| 4.3 Non-structural types of cuts                                 |     |

|------------------------------------------------------------------|-----|

| 4.3.1 Factor Cuts                                                | .51 |

| 4.3.2 Priority Cuts                                              | .52 |

| 4.4 Windowing vs. Covering                                       | .52 |

| 4.4.1 Windowing with MFFW                                        | .52 |

| 4.4.2 Covering with <i>KL</i> -cuts                              |     |

| 4.4.3 Windowing with <i>KL</i> -cuts                             | .53 |

| 4.4.4 Covering with <i>KL</i> -cuts and 1L-cuts                  | .53 |

| 4.5 Contributions of this chapter                                | .53 |

| 5 LITERATURE REVIEW.                                             |     |

| 5.1 About this chapter                                           | .54 |

| 5.2 Cuts in AIGs - a historical overview                         | .54 |

| 5.2.1 <i>K</i> -cuts                                             | .54 |

| 5.2.1.1 Enumerating all K cuts                                   | .54 |

| 5.2.1.2 Enumerating factor cuts                                  |     |

| 5.2.1.2.1 Complete Cut Factorization                             |     |

| 5.2.1.2.1.1 Tree Cuts - (Local Cuts)                             |     |

| 5.2.1.2.1.2 Reduced Cuts - (Global Cuts)                         |     |

| 5.2.1.2.2 Partial Cut Factorization                              |     |

| 5.2.1.2.2.1 Leaf-dag Cuts - (Local Cuts)                         |     |

| 5.2.1.2.2.2 Dag Cuts - (Global Cuts)                             |     |

| 5.2.1.3 Enumerating priority cuts                                |     |

| 5.2.1.4 Cut signature                                            |     |

| 5.2.2 <i>KL</i> -cuts                                            |     |

| 5.2.2.1 Martinello's Enumeration Method                          |     |

| 5.2.2.2 Machado's Enumeration Method                             |     |

| 5.2.2.2.1 IWLS23 Best Paper Method                               |     |

| 5.2.2.3 Optimization Without Coverage                            |     |

| 5.3 Flow Based on Logic Calculation and Signal Distribution      |     |

| 5.3.1 KL-cuts For Logic Calculation                              |     |

| 5.3.2 1L-cuts For Signal Distribution                            |     |

| 5.4 Comparative Summary Between Covering With K-cuts and KL-cuts |     |

|                                                                  | .74 |

| 6 PROPOSED METHOD                                                | .75 |

| 6.1 About This Chapter                                           | .75 |

| 6.1.1 <i>K</i> -cut Enumeration                                  |     |

| 6.1.2 Cut Signature                                              | .77 |

| 6.2 Expanding K-cuts to KL-cuts                                  |     |

| 6.3 Covering an AIG with <i>KL</i> -cuts                         |     |

| 6.3.1 Satisfiability formulation for a valid cover               |     |

| 6.3.1.1 Rule 1                                                   |     |

| 6.3.1.2 Rule 2                                                   |     |

| 6.3.1.3 Rule 3                                                   | .89 |

| 6.3.1.4 Rule 4                                                   |     |

| 6.3.2 Satisfiability formulation for a minimum cover             |     |

| 6.3.3 Approach Using BDDs for Cost Constraint Solutions          |     |

| 6.4 Our Method Overview                                          |     |

| 6.5 Contributions of This Chapter                                |     |

| 7 RESULTS AND DISCUSSIONS                                        | .98 |

| 7.1 About this chapter                                           | .98 |

| 7.2 <i>KL</i> -cut enumeration performance                       | .98 |

| 7.3 Covering with <i>KL</i> -cuts        |     |

|------------------------------------------|-----|

| 7.3.1 Exact Cover Size                   |     |

| 7.3.1.1 Cover Size                       |     |

| 7.3.1.2 Cover Runtime                    |     |

| 7.3.2 Cover Without Optimization         | 110 |

| 7.4 Contributions of this chapter        |     |

| 8 CONCLUSION                             | 114 |

| REFERENCES                               |     |

| APPENDIX A — ALGORITHM WITH OPTMIZATIONS |     |

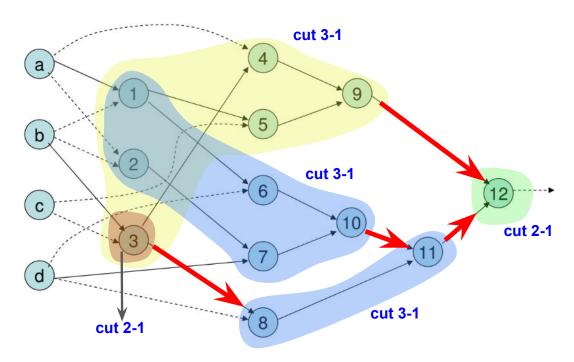

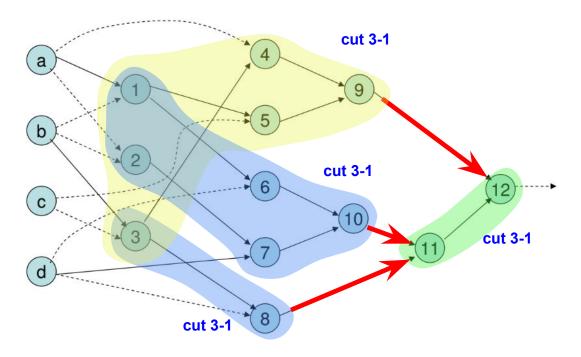

### **1 INTRODUCTION**

The evolution of VLSI silicon integration has led the electronics industry to a present situation where the number of devices in a single integrated circuit can be of the order of billions of transistors. The complexity of large VLSI design must rely then on computer-aided design tools commonly known as Electronic Design Automation (EDA) tools.

Due to the complexity of design flows, the research on EDA focuses generally on small specialized topics. Design flows are generally very complex encompassing a variety of tasks performed by a variety of tools. In a very naive way, the design of integrated circuits can be divided into logic synthesis and physical design. The logic synthesis happens in the front end of the design flow and the goal of logic synthesis can be stated as to capture the initial logic description and generate a netlist of interconnected cell instances that implement the desired logic. The physical design happens in the back end of the design flow and the goal of physical design can be stated as using the netlist generated by the logic synthesis to place and route the cell instances to produce a circuit layout that is ready for fabrication. It must be said that current commercial design flows can estimate placement and floorplanning in the early steps of the design flow, still during logic synthesis, and consider the effect introduced by placement and routing parasitics.

The field of logic synthesis has in the last two decades relied on the AIG data structure. This is done mostly due to scalability reasons while preserving result quality. The logic synthesis using AIGs is based on the concept of AIG cuts. There are several types of cuts in AIGs, so this will be discussed in more detail later in this thesis. The most used type of cut in AIG is the *K*-cut, which can be roughly defined as a sub-graph with K inputs rooted in an output node. *K*-cuts were initially introduced to map Field-Programmable Gate Array (FPGA) circuits composed of K-input look-up tables. However, *K*-cuts later become an important part of AIG-based logic synthesis not necessarily tied to FPGAs.

This thesis presents a contribution to logic synthesis based on AIGs. The contribution is focused on computing AIG covers with *KL*-cuts, where not only the number of inputs K but also the number of outputs L is controlled in the *KL*-cut subgraph. *KL*-cuts were introduced by Martinello (MARTINELLO et al., 2010) and later Prof. André Reis (REIS; MATOS, 2018) proposed an approach to use *KL*-cuts in a synthesis flow based on logic computation and signal distribution. However, the proposal of the logic computation and signal distribution design flow did not provide an efficient algorithm to cover an AIG with KL cuts. In this thesis, we provide an efficient algorithm for this task, as described in chapter 6. We propose: (1) an efficient method to enumerate *KL*-cuts, (2) a method to generate CNF formulas to obtain the cover of an AIG with *KL*-cuts using satisfiability (SAT), and (3) a BDD-based algorithm to generate maximum cost clauses for problems that will be solved with SAT.

Chapter 3 introduces the basic concepts used in this thesis. For people with familiarity with logic synthesis, this chapter can be partially or completely skipped, with the reader searching only for the necessary concepts from the chapter.

Chapter 4 presents a complete overview of different types of AIG cuts in the literature. This chapter is a contribution in itself, as a comparative review with the level of completeness and detail presented here is not available in previous works.

Chapter 5 discusses prior works in a chronological way. It is a bibliographical review that presents the historical evolution of AIG-based logic synthesis. The focus is to present the evolution of AIG based logic synthesis.

Chapter 6 introduces the contributions of this thesis, where the proposed methods and the steps taken to obtain a cover using *KL*-cuts are presented.

Chapter 7 presents the obtained results and discusses their significance. One point that is important to highlight is that the algorithm for enumerating *KL*-cuts is significantly more efficient in terms of execution time when compared to the method of (MACHADO et al., 2012), and slightly more efficient on average than the method of (TANG et al., 2023). Another point is the reduction in the number of cuts needed to cover circuits when using multi-output cuts, such as *KL*-cuts.

Finally, Chapter 8 concludes this work, discussing the contributions and limitations. Future works are also outlined, in the context of a design flow based on logic computation and signal distribution.

### **2 MOTIVATION FOR KL CUTS**

#### **2.1 About This Chapter**

This chapter presents the motivation for *KL*-cuts. *KL*-cuts can be useful on at least three different contexts. Notice that the use in different contexts also happens for the more common *K*-cuts that can be used in independent logic optimization, FPGA mapping, as well as cell-based mapping for ASICs. The different contexts for using *KL*-cuts are discussed in the next subsections.

#### 2.2 KL-cuts and multi-output LUTs

The first and more obvious application of *KL*-cuts is for FPGAs with multiple output LUTs. In a very similar way that *K*-cuts can be used to map a circuit for FPGAs based on single output LUTs, the mapping for FPGAs with LUTs with L outputs can be done through a cover based on KL cuts. One interesting research question would be to map a circuit for an FPGA with single output 4-LUTs and compare it with a mapping to an FPGA with 4-2-cuts. In the best case, the number of LUts would be divided by 2. However, not all the pairs of 4-cuts can be packed into 4-2-cuts as the inputs may differ. Additionally, it is possible to compare the dedicated *KL*-cut covering method proposed in this thesis against a method that covers a circuit with *K*-cuts and then packs the compatible cuts into the same KL-Lut when this is possible. This is one type of experiment investigated in this thesis.

### 2.3 KL-cuts and multi-output cells in a library

A second application of *KL*-cuts is for ASIC mapping targeting a library with (some) multiple-output cells. A recent publication on technology mapping using multi-output library cells (CALVINO; MICHELI, 2023) discusses *KL*-cuts as an alternative to the method they introduced. However, they use cut signatures as they target only full-adder cells where the outputs depend exactly on the same set of inputs, which results in equal cut signatures. The use of *KL*-cuts could help to match cells with outputs depending on a slightly different set of inputs. However, we will not investigate this type of approach

in detail, as for ASIC synthesis of ASICs the different outputs will probably require different sizes and the logical match of a cell would not be sufficient to produce a match that is adequate to the timing requirements.

### 2.4 KL-cuts as a partitioning method

A third application of *KL*-cuts is in a method to bring physical awareness starting at technology-independent logic synthesis (REIS; MATOS, 2018). The authors propose a design flow based on (local) logic computation and signal distribution. The local logic computation is done inside *KL*-cuts, meaning that the *KL*-cuts will be used to pack independent portions of the circuit that will be placed locally. In this way, the routing among cells inside a same *KL*-cut is local, using short wires and low metal levels. This means that the *KL*-cuts in (REIS; MATOS, 2018) can be seen as partitions composed of several cells inside the *KL*-cuts as opposed against a *KL*-cut that is a match to a single library cell as in (CALVINO; MICHELI, 2023). The *KL*-cuts can be viewed as physical partitions. As a consequence, the routing among different *KL*-cuts tends to be global, using long wires and high metal levels. The authors (REIS; MATOS, 2018) proposed the design flow with these characteristics, but a scalable algorithm to compute *KL*-cuts and cover a circuit was not provided. The original algorithm for *KL*-cuts (MARTINELLO et al., 2010) also lacks scalability. This way, a scalable *KL*-cut covering algorithm is missing.

#### 2.5 Contributions of this chapter

This chapter presented the motivation for developing a *KL*-cut computation and covering algorithm. The use of *KL*-cuts can be applied in three distinct contexts proposed by different authors. At the same time an efficient scalable algorithm for *KL*-cuts has not yet been proposed.

Finally, we reckon that this chapter presents the motivation in a way that is suitable for those already knowledgeable in logic synthesis. We hope that it motivates those that are not yet fully knowledgeable in logic synthesis to keep reading the thesis so that the motivation is further clarified when the underlying concepts are presented further in the text. For those initiating in logic synthesis, perhaps re-reading this chapter after finishing the thesis will bring a renewed appreciation of the contributions.

### **3 BASIC CONCEPTS**

#### **3.1** About this chapter

This chapter will present the basic concepts essential for understanding this work. This section provides the necessary basis for subsequent discussions and analyses. This chapter can be potentially skipped by those knowledgeable about the field of logic synthesis.

#### 3.2 Boolean functions and their representation

The Boolean domain is defined by the set  $B = \{0, 1\}$ . In other words, this set contains only the elements 1 or 0; and a variable defined in the Boolean domain can only assume the values 0 or 1. For instance, if a variable x is a Boolean variable, it can only assume the values 0 or 1. The value 1 is sometimes interpreted (named, referred or labeled) as the true value. Similarly, the value 0 is called the false value.

A (single input) Boolean function is a mapping from a Boolean set of size N, called a domain, to another set of the size of 1, also a Boolean domain called an image, this is defined as  $F : B^n \to B$ . Therefore, a Boolean function associates a combination of input values, of size N, with an output of 0 or 1. Normally the term Boolean function refers to a single output Boolean function. However, most functions of practical interest are multiple output functions. A multiple output Boolean function is a mapping from a Boolean set of size N, called a domain, to another set of size M, also a Boolean domain called an image, this is defined as  $F : B^n \to B^m$ .

There are different ways to represent Boolean functions, each with its characteristics and limitations. Next, some of the main representations of Boolean functions that were widely used during the evolution of the circuit design area will be presented.

#### 3.2.1 Historical evolution of Boolean functions representations

As predicted by Gordon Moore in 1965 (MOORE, 1965), the density of transistors in integrated circuits, and consequently, the processing capacity of computers, is expected to double approximately every two years. As the size of circuits grew over time, it was increasingly necessary to use more optimized ways to represent Boolean functions. This motivated the creation of new data structures to represent Boolean functions in order to keep up with the growth of Boolean functions.

EDA started with the design of the first computers and modern data structures were not yet known, as the first computers did not have the necessary resources to support them. So the evolution of EDA data structures goes in hand with the evolution of computers, as larger computers need and at the same time support smarter and more efficient data structures to design the next generation of computers. In the following sections, we will present some of the most popular ways to represent Boolean functions.

#### 3.2.2 Truth tables

The truth table (TT) was the first way to represent Boolean functions in the very early days of EDA, from the late 50's to 70's. In this representation, each combination of input values is associated with a corresponding output value (MICHELI, 1994). Consequently, it is considered canonical, possessing a unique representation under a fixed order of the input variables. Table 3.1 shows a truth table for a full adder, which is a 3-input, 2-output Boolean function denoted as  $B^3 \rightarrow B^2$  function.

| A | В | $\mathbf{C}_{\mathbf{in}}$ | Sum | $\mathbf{C}_{\mathbf{out}}$ |

|---|---|----------------------------|-----|-----------------------------|

| 0 | 0 | 0                          | 0   | 0                           |

| 0 | 0 | 1                          | 1   | 0                           |

| 0 | 1 | 0                          | 1   | 0                           |

| 0 | 1 | 1                          | 0   | 1                           |

| 1 | 0 | 0                          | 1   | 0                           |

| 1 | 0 | 1                          | 0   | 1                           |

| 1 | 1 | 0                          | 0   | 1                           |

| 1 | 1 | 1                          | 1   | 1                           |

Table 3.1 – Truth table of a full adder.

Each row of the truth table represents a combination of input values to the function, which has one or more associated outputs. For example, row 2 of the truth table 3.1 has the input combination (A=0, B=0,  $C_{in}$ =1), which produces the outputs  $Sum = 1, C_{out} = 0.$

It is important to notice that, as the number of inputs grows, the size of the truth table increases exponentially with the number n of inputs. The number of different input combinations is  $2^n$ , where n is the number of inputs to the function (CRAMA; HAMMER, 2011). For instance, the full adder has a truth table with eight combinations for the three inputs A, B, and  $C_{in}$ , as shown in Table 3.1.

#### **3.2.3 Sum of Products**

A Sum of Products (SOP) was one of the most popular Boolean representations from the early 70's to 90's, is an equation described by the sum of all input combinations (Products) that produce the value 1 as the output of the function. SOP can be considered one of the simplest ways to describe a Boolean function using equations because an SOP is composed only of the sum of the function's minterms, which is a two-level format (WAGNER; REIS; RIBAS, 2006). For example, the function represented by the truth table 3.1 has the following SOPs:

•

$$Sum = (\overline{A} \cdot \overline{B} \cdot C_{in}) + (\overline{A} \cdot B \cdot \overline{C_{in}}) + (A \cdot \overline{B} \cdot \overline{C_{in}}) + (A \cdot B \cdot C_{in});$$

•

$$C_{out} = (\overline{A} \cdot B \cdot C_{in}) + (A \cdot B \cdot C_{in}) + (A \cdot \overline{B} \cdot C_{in}) + (A \cdot B \cdot \overline{C_{in}});$$

This form of Boolean function representation has been and continues to be used by tools such as Espresso (BRAYTON et al., 1982), a heuristic two-level logic minimizer. The SOP representation has also been and is still used by tools like MIS (BRAY-TON et al., 1987), a multilevel logic synthesis and minimization system responsible for popularizing multilevel synthesis based on the manipulation of factored forms, and SIS (SENTOVICH et al., 1992), a tool for synthesis and optimization of sequential circuits, responsible for adding sequential circuit handling to the MIS algorithms.

Similarly to the TT, the SOP is also considered canonical, thus providing a unique representation of the Boolean function (WAGNER; REIS; RIBAS, 2006). However, as with the TT, the size of the SOP can increase significantly with the number of inputs grows. Due to these limitations, new approaches have been proposed, where methods based on data structures have become prominent, as will be discussed in the following sections.

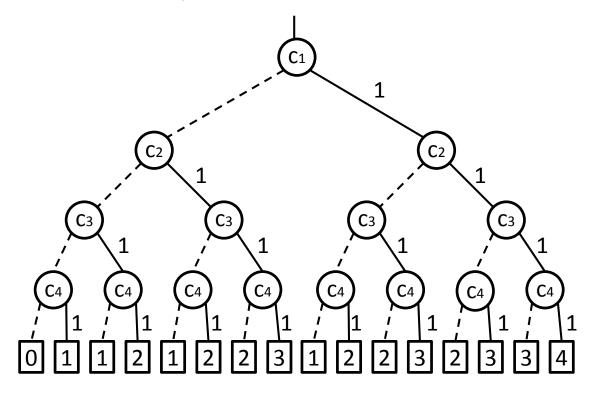

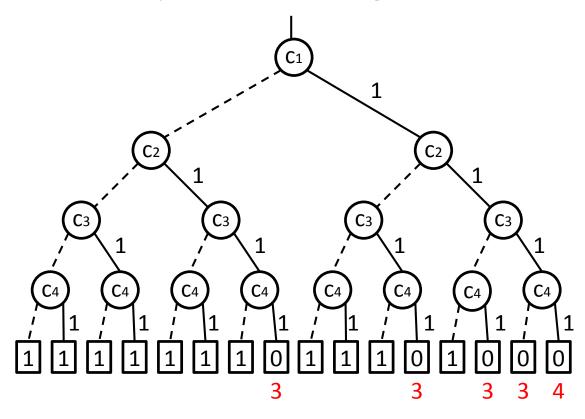

### **3.2.4 Binary Decision Diagrams**

Binary Decision Diagrams (BDDs) were an important tool in the field of formal verification and optimization of logic circuits, from the late 80's to the mid 2000's. The BDD structure is based on the Shannon Expansion (SHANNON, 1949), each node in the BDD has a generic decision variable dv that is used to decide between two other nodes that represent sub-functions where the decision variable dv has a fixed value dv = 0 (negative cofactor sub-function) or dv = 1 (positive cofactor sub-function). Technically, the two sub-functions that are pointed by a BDD node with decision variable dv do not depend on the variable dv, as the variable dv has already been decided to dv = 0 (for the negative cofactor sub-function) or dv = 1 (for the positive cofactor sub-function).

BDDs can be traced to the work by (LEE, 1959) and (AKERS, 1978), but they become widely used after the seminal work of (BRYANT, 1986), which introduced Reduced Ordered BDDs (ROBDDs), their canonical properties and algorithms to manipulate functions. ROBDDs constitute an optimized variant of BDDs, proposed to enhance efficiency in the representation and manipulation of Boolean functions. By eliminating duplicate nodes (i.e. nodes representing the same logic function) and imposing restrictions on the ordering of BDD variables, ROBDDs provide a compact and effective representation.

The defining characteristics of ROBDDs are i) variable ordering and ii) node irredundancy. Variable ordering means that a fixed order is imposed on the function's input variables, where all paths from the root node to a terminal node follow the same sequence of variables, even when some variables are not present in a specific path. Node irredundancy means that ROBDDs do not have i) nodes that do not make decisions and ii) redundant sub-graphs representing the same Boolean function. Also, (BRYANT, 1986) has shown that due to these characteristics, ROBDDs are canonical and unique structures for equivalent functions.

Figure 3.1 illustrates a ROBDD example of the Boolean function depicted in Table 3.1. The decision variables for each level are represented on the left, as the ROBDD is ordered and all the nodes in a given level share the same decision variable. The values inside the nodes are keys used in a hash table to guarantee that nodes are not duplicated, as it is usual in the strong canonical form of ROBDDs (BRACE; RUDELL; BRYANT, 1990). The solid lines represent the positive cofactors dv = 1, while the dotted lines represent the negative cofactors dv = 0 for each node. As shown, every path in the BDD leads to one of the terminal nodes, determining the output value generated by the Boolean

function.

Figure 3.1 – ROBDD representing a Full Adder with inputs *a*, *b*, and *cin*.

The tools SIS (SENTOVICH et al., 1992), VIS (BRAYTON et al., 1996), and MV-SIS (CHAI et al., 2003) use BDDs in their respective methodologies. SIS employs BDDs to represent and manipulate sequential circuits, facilitating optimization and formal property verification. Although VIS does not use BDDs as its primary form of representation, BDDs are employed in processes such as Equivalence checking and Simulation for advanced formal verification. On the other hand, MVSIS deals with multivalued logic and uses methods based on BDDs.

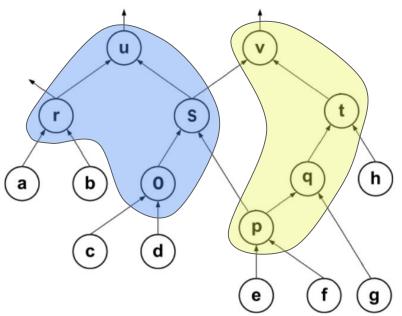

### 3.2.5 And-Inverter Graphs

In the beginning of the 2000's, it became clear that ROBDDs would not scale to support EDA aiming large circuits, and AIGs began to gain traction as the main data structure in logic synthesis through the use of AIGs in ABC. This way, AIGs became an essential structural representation in the domain of computer engineering and computer science. Their efficiency and scalability make them a valuable tool for representing complex Boolean functions.

An AIG is a directed acyclic graph composed of primary inputs (PIs), primary outputs (POs), and internal nodes that represent the AND2 function. Variable inversions

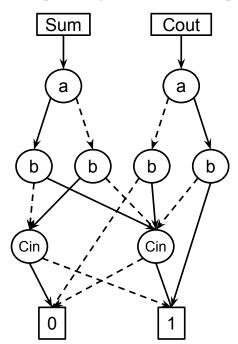

are represented in the arcs, that may be labeled as inverters. Figure 3.2 shows the AIG of a full adder. In this AIG example, the PIs are *a*, *b*, and *Cin*, the outputs are *Sum* and *Cout*, and the nodes numbered six to twelve are AND2 nodes.

Figure 3.2 – Example of an AIG representing a two-input full adder.

Source: Adapted from (CIESIELSKI et al., 2019).

The dotted and solid lines represent the complemented (inverted) and uncomplemented (non-inverted) edges, respectively, used to describe whether the function accessed by the edge is inverted or not. Internal nodes are 2-input ANDs that have exactly two inputs, called *fanins* of the node. The output of a node  $nd_i$  that is input to another node  $nd_j$ is called *fanout* of  $nd_i$  (MISHCHENKO; BRAYTON, 2005).

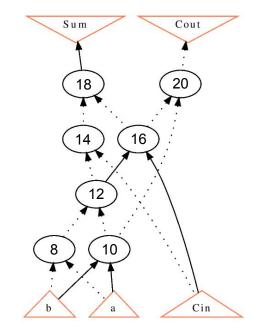

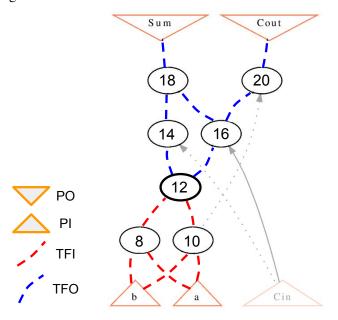

An AIG node  $nd_i$  is commonly associated with an integer identificator *i*. Given two nodes  $nd_i$  and  $nd_j$ , where i < j, there is a topological partial order between node  $nd_i$ and node  $nd_j$ , such that node  $nd_i$  has precedence over (i.e. appears before) node  $nd_j$ . As a consequence of the partial order, when there is a path between the nodes  $nd_i$  and  $nd_j$ , the node  $nd_i$  is in *fanin* transitive (TFI) of node  $nd_j$ . Conversely, node  $nd_j$  is in the transitive *fanout* (TFO) of node  $nd_i$  (MISHCHENKO; CHATTERJEE; BRAYTON, 2006a). These elements are illustrated in Figure 3.3. For instance, nodes  $nd_{14}$ ,  $nd_{16}$ ,  $nd_{18}$  and  $nd_{20}$  are in the transitive fanout of node  $nd_{12}$ . Additionally,  $nd_8$  and  $nd_{10}$  are in the transitive fanout or transitive fanin of each other because there is no directed path from one to the other, as they are parallel nodes in the graph.

Figure 3.3 – Transitive fanin and transitive fanout of node 12.

Even though the AIG is a graph representation, this data structure can be manipulated as an array. Figure 3.4 illustrates the AIG from Figure 3.2 represented by an array. In this representation approach, each node is indexed by an even integer number, and stored at the position  $(Aig\_index)/2$ . When a node is accessed through an odd Aig index, this means that the inverted function from the node is required instead, and the correspondent node is also accessible through  $((Aig\_index)/2)$ . For example, node 12 is stored at position 6, and its fanins are nodes 8 and 10 (in Figure 3.2), however, both fanins are complemented, thus in the integer array AIG representation these nodes are indexed by the values 9 (inverted 8) and 11 (inverted 10). Finally, position 0 is reserved for the constant zero (and its complement 1), to distinguish it from other PIs, its fanins are marked with "-".

Figure 3.4 – AIG elements.

| Array index | 0 | 1 | 2 | 3 | 4 | 5  | 6  | 7  | 8  | 9  | 10 |

|-------------|---|---|---|---|---|----|----|----|----|----|----|

| Aig index   | 0 | 2 | 4 | 6 | 8 | 10 | 12 | 14 | 16 | 18 | 20 |

| Fanin_1     | - | 2 | 4 | 6 | 5 | 4  | 11 | 13 | 12 | 17 | 17 |

| Fanin_2     | - | 2 | 4 | 6 | 3 | 2  | 9  | 7  | 6  | 15 | 11 |

In the remainder of this work, some examples of AIGs can have nodes with odd indexes. This is justified because the ABC tool (BRAYTON; MISHCHENKO, 2010)

used to create the examples uses odd indexes for the nodes to generate the figures, even if internally the nodes have even integer identifiers.

Currently, AIGs are one of the main data structures used by the ABC tool (BRAY-TON; MISHCHENKO, 2010), one of the most important *open-source* logic synthesis tools. The ABC tool provides state-of-the-art combinational and sequential circuit synthesis algorithms.

#### **3.3 Physical Implementation Technologies**

The ultimate goal of EDA tools is to produce a real-world circuit design. To produce such a real-life design, a target implementation technology should be adopted. The main technologies are ASICs and FPGAs, which are discussed in the following subsections.

### **3.3.1 ASICs**

Application-Specific Integrated Circuit (ASIC) is a type of integrated circuit (IC) that is designed for a specific purpose or application, as opposed to general-purpose ICs like microprocessors or memory chips. ASICs are custom-built to perform a particular function or set of functions, making them highly efficient and specialized for the intended task.

The key advantages of ASICs include high performance, low power consumption, and optimized functionality for the targeted application. However, the development of ASICs can be costly and time-consuming, and once manufactured, they are typically not reprogrammable for different tasks. This contrasts with general-purpose processors, which can be reprogrammed to perform a wide range of tasks.

### 3.3.1.1 Cell Library

A cell library, in the context of integrated circuit (IC) design, is a collection of predefined and characterized building blocks or cells that can be used to create custom integrated circuits. Each cell within the library represents a fundamental functional unit, such as logic gates, flip-flops, multiplexers, and other digital or analog components. These cells are designed, characterized, and tested to meet specific performance and electrical

criteria.

The purpose of a cell library is to provide designers with a set of standardized building blocks that they can use to assemble custom ICs quickly and efficiently. Instead of designing every component from scratch, designers can select cells from the library that match their requirements and integrate them into their overall chip design. This modular approach helps streamline the design process, reduce development time, and ensure consistency in the manufactured ICs.

### 3.3.1.2 Library-based Design specificities

Each cell from a library implements a function with a given cost. That means that specific sub-functions, implemented by different cells, will have different costs.

### 3.3.2 FPGAs

A FPGA is a configurable hardware integrated circuit that can be programmed or configured by the user or designer after manufacturing. Unlike the ASICs, which are custom-designed for a specific application and have a fixed functionality, FPGAs offer flexibility and reconfigurability to implement different designs. This makes FPGAs wellsuited for prototyping, development, and applications where adaptability to changing requirements is crucial.

FPGAs have gained significant attention in modern computing, owing to their versatility, rapid deployment capabilities, and cost-effectiveness. With short time-to-market and field programmability, FPGAs have become pivotal in diverse computing environments, from data centers to edge computing applications (FAN; WU, 2023; CONG; DING, 1993).

The FPGA architecture comprises programmable logic blocks, interconnections, and I/O pads. The Look-Up Table (LUT)-based architecture dominates the existing programmable chip industry. LUTs are discussed in the next subsection.

#### 3.3.2.1 Look-up Tables - LUTs

The fundamental programmable logic element is the K-input LUT (K-LUT), a versatile element that can implement any combinational logic function up to K inputs. The specific implementation of the LUT architecture is determined by the target size (maximum number of inputs) to be supported (CHEN; CONG, 2004; CHEN; CONG, 2001). Notice that the LUT architecture does not necessarily need to be based on a table structure, and the specific implementations are generally proprietary. For instance, Vranesic (ZILIC; VRANESIC, 1996) proposes LUT architectures derived from BDDs.

### 3.3.2.2 LUT-based Design specificities

Each LUT in a given FPGA architecture implements several different functions with the same given cost (the cost of the LUT, not the configured function). That means that different sub-functions, implemented by identical LUTs, will have equal costs.

### **3.4 AIGs-based synthesis**

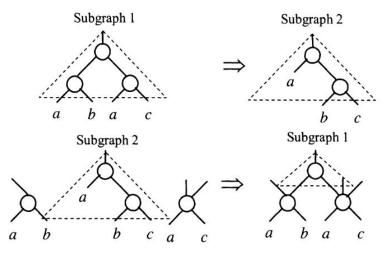

Modern logic synthesis is strongly based on AIG rewriting. The concept of AIG rewriting can be explained with the help of Figure 3.5. The figure presents two examples of AIG rewriting, one in the upper part and one in the bottom part. The AIG rewriting depends on the context of the complete AIG.

In the upper part of the figure, it is illustrated that a subgraph 1 (with equation (ab) \* (ac)) can be substituted by a subgraph 2 (with equation (a) \* (bc)) in an AIG such that the number of nodes in the subgraph is reduced from 3 nodes to 2 nodes. This way, there is a reduction of one node in the circuit implementation.

In the bottom part of the figure, the dependence of the complete AIG context is illustrated. In this example, subgraph 2 (with equation (a) \* (bc)) is substituted by subgraph 1 (with equation (ab) \* (ac)) in an AIG such that the total number of nodes in the AIG is reduced from 4 nodes to 3 nodes. This way, there is a reduction of one node in the circuit implementation. Notice that this optimization is viable due to the context of the complete AIG, where the nodes with equations ab and ac previously exist in the AIG and do not need to be created.

Several different approaches in the literature are based in AIG rewriting. Examples of AIG based synthesis include (PAN; LIN, 1998), (CONG; DING, 1999), and (NETO et al., 2022).

Figure 3.5 – Rewriting method in AIG.

Source: (MISHCHENKO; CHATTERJEE; BRAYTON, 2006a).

### 3.4.1 Cuts in AIGs

A cut in a Boolean network, denoted as C, is an important concept utilized in logic synthesis and optimization. It consists of a pair  $\{r, \{l_0, \ldots, l_i\}\}$ , comprising a root node and a set of nodes called leaves. For each path from a PI to the root of C, it must traverse at least one of its leaves (MISHCHENKO; CHATTERJEE; BRAYTON, 2006a; MISHCHENKO; BRAYTON; CHATTERJEE, 2008).

The size of a cut C consists of the number of leaf nodes that compose it and is denoted as |C|, and a trivial node cut consists only of the node itself, called self-cut (MISHCHENKO; CHATTERJEE; BRAYTON, 2006a; MISHCHENKO; BRAYTON; CHAT-TERJEE, 2008). The procedure to enumerate the cuts with K or less inputs will be shown in section 5.2.

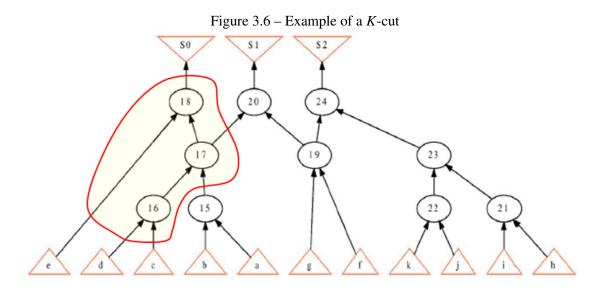

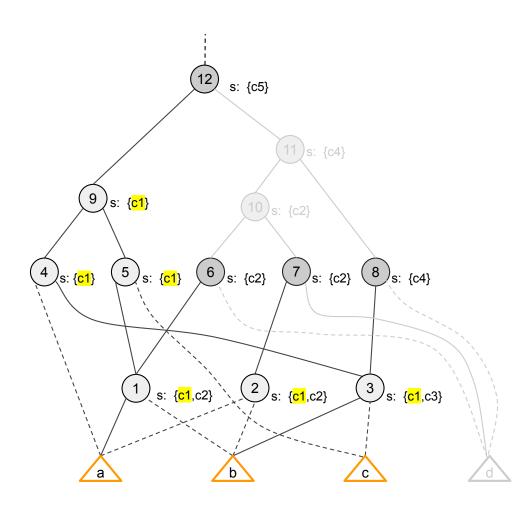

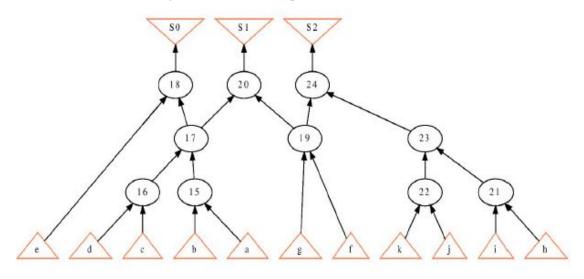

Figure 3.6 provides an example of a 4-cut in an AIG. Notice that only one 4-cut is shown for simplicity, but several different cuts may be possible for each node of this AIG. The section 5.2.1.1 will provide a complete explanation of how to generate all *K*-cuts for a given AIG. Figure 3.6, shows a 4-cut with leaves the nodes  $\{e, d, c, 15\}$  and root the node 18. The meaning of this 4-cut is that the Boolean function rooted in node 18 can be expressed as a function of the variables representing the Boolean function rooted in nodes  $\{e, d, c, 15\}$ . Indeed,  $n_{18} = e \cdot d \cdot c \cdot n_{15}$ .

It is possible to say that the 4-cut  $\{e, d, c, 15\}$  rooted on node 18 covers nodes 16, 17 and 18. This has to be understood as the fact that the inputs  $\{e, d, c, 15\}$  are sufficient

to compute the function of node 18 and nodes 16 and 17 are not necessary to this end. However, nodes 16 and 17 are still necessary to compute the function in node 20 as node 17 is an input for node 20.

### 3.4.2 Covers of an AIG

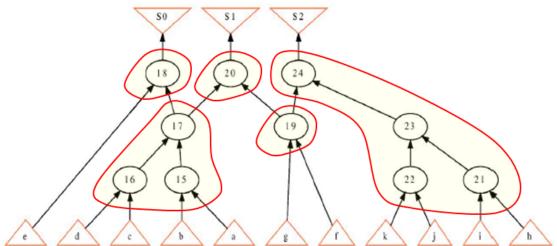

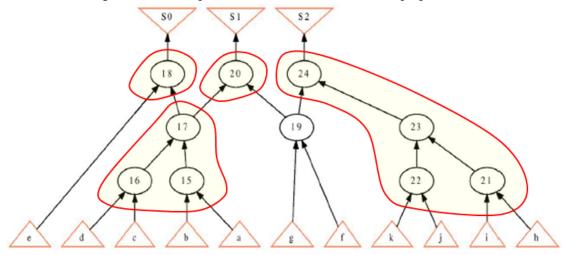

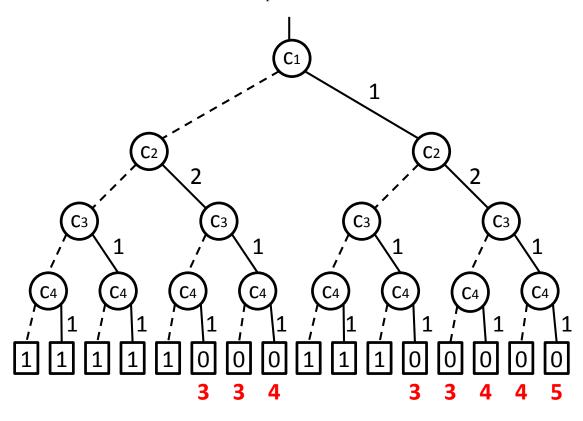

A cover of an AIG is a set of cuts such that the set of Boolean functions corresponding to each cut jointly implements the Boolean function of the complete AIG. In the following, we will see some examples of valid and invalid covers of an AIG.

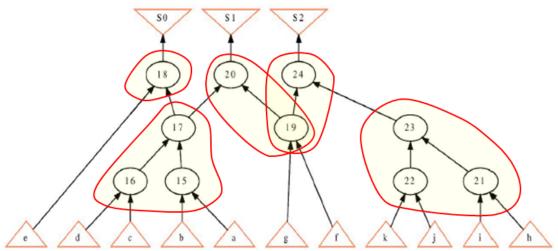

Figure 3.7 – Example of a valid cover with non-superposed cuts.

Figure 3.7 presents a valid cover of an AIG with non-superposed cuts. The cover is composed of five distinct cuts and there is no superposition of cuts. That means that each AIG node is covered by only one cut. There is no AIG node belonging to more

than one cut. Notice that the Boolean functions for nodes 15, 16, 21, 22, and 23 were not explicitly implemented as the nodes are internal to cuts. This is not a problem as the nodes are not used as inputs to any other cuts.

Figure 3.8 – Example of an invalid cover with non-superposed cuts.

Figure 3.8 illustrates an invalid cover of an AIG with non-superposed cuts. The cover is composed of four distinct cuts and there is no superposition of cuts. That means that each AIG node is covered at most by only one cut. There is no AIG node belonging to more than one cut. However, node 19 is not covered by any cut and it is an input for nodes 20 and 24. This way, this is not a valid cover as the Boolean function corresponding to node 19 is necessary and it was not implemented.

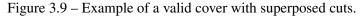

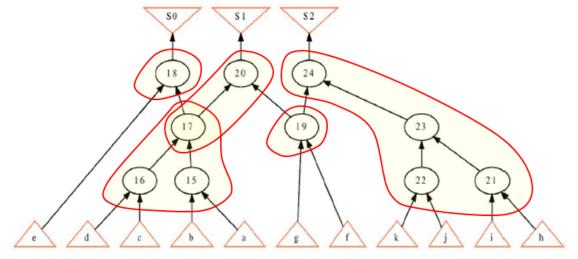

Figure 3.9 shows a valid cover of an AIG with superposed cuts. The cover is composed of five distinct cuts and there is a superposition of cuts between the cuts rooted in nodes 20 and 24. This happens because node 19 is covered by the two cuts. Consequently, there is an AIG node belonging to more than one cut, resulting in the superposition of cuts. Notice that the Boolean functions for nodes 15, 16, 19, 21 and 22 were not explicitly implemented as the nodes are internal to cuts. This is not a problem as the nodes are not used as inputs to any other cuts.

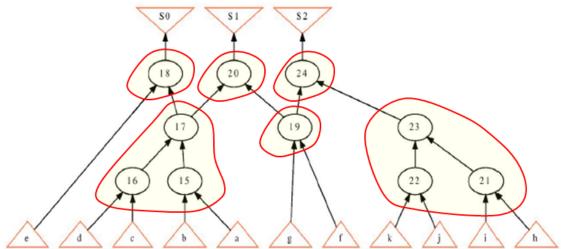

Figure 3.10 – Example of an invalid cover with superposed cuts.

Figure 3.10 presents an invalid cover of an AIG with superposed cuts. The cover is composed of five distinct cuts and there is a superposition of cuts between the cuts rooted in nodes 17 and 20. This happens because node 17 is covered by the two cuts. Consequently, there is an AIG node belonging to more than one cut, resulting in the superposition of cuts. However, the cut rooted in node 20 has the nodes 15 and 16 as inputs and those do not have any cut rooted on them. This way, this is not a valid cover as the Boolean function corresponding to nodes 15 and 16 are necessary and they were not implemented.

### **3.5 Technology Mapping**

Technology mapping is an important step in the digital circuit integrated design flow. This step is responsible for transforming the description of a technology-independent circuit to a set of primitives defined in a given technology. For cell-based designs, the primitives are cells from the target library. In the case of field programmable gate arrays (FPGAs), the primitives are normally K-input LUTs. Before mapping, the Boolean network is represented as a specific type of graph, normally called a subject graph. AIGs are commonly used as subject graphs.

Similarly to a cover of an AIG, a mapping can also be defined as a set of cuts,

but with more restrictive properties. A mapping of an AIG is a set of cuts such that *i*) the set of Boolean functions corresponding to each cut jointly implements the Boolean function of the complete AIG; *ii*) the Boolean function of each cut can be implemented by a physical element of the target technology; and, *iii*) an overall technology-dependent cost is optimized. In the next sub-sections we will discuss mapping to cell-based designs and FPGAs.

#### 3.5.1 Mapping to cell-based ASICs

Mapping to cell-based ASICs is the process of transforming a high-level electronic design description into a configuration that can be implemented on a specific type of ASIC known as a cell-based ASIC. This process involves selecting appropriate standard cells from the library to implement different parts of the design.

Figure 3.11 illustrates an ASIC mapping considering a cell library with AND cells up to 4 inputs (i.e. a five input AND is not present in the library). Cell-based mapping tends to avoid superposition as the duplication of nodes due to superposition leads to duplication of logic, with an adverse impact on area costs.

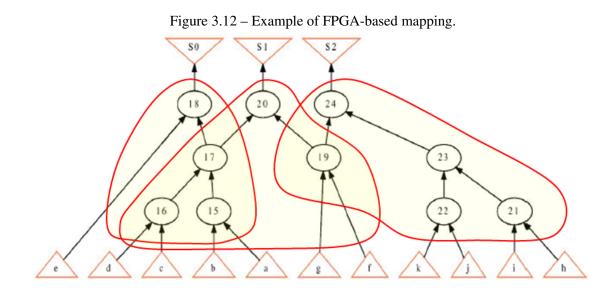

### 3.5.2 Mapping to FPGAs

In the case of FPGA as target technologies, the physical elements used to implement the circuit are LUTs. Figure 3.12 shows an FPGA mapping considering LUTs up to 6 inputs (i.e. every Boolean function is feasible with a single 6-input LUT). FPGA-based mapping tends to extensively use superposition as the duplication of nodes due to superposition does not imply in duplication of logic. Indeed, the more logic is packed in a sigle LUT, the better the usage of the LUT.

In the example of Figure 3.12, four nodes are duplicated to allow the implementation of the circuit with only 3 LUTs, one for each output. Three 6-input LUTs are used even if output S0 has only five inputs. The outputs S1 and S2 make full use of a 6-input LUT each.

### 3.5.3 Cost Functions

During technology mapping an overall technology-dependent cost is optimized. In the following, we discuss first-order estimators for cost functions.

### 3.5.3.1 Area

Area in technology-independent optimization is estimated by counting the number of AIG nodes. The number of AIG nodes, when used for relative comparisons, has good correspondence with the final area of cell-based and FPGA implementations. Area in cell-based implementations is obtained by adding the areas of individual cell instances. Area in FPGA-based implementations is obtained by adding the number of used LUTs.

#### *3.5.3.2 Delay*

The first-order estimator for delay in a circuit is the number of elements in the longest path. In the case of FPGA designs, unit delay can be used as all elements are LUTs of the same type. In the case of cell-based designs, the individual delay of cells from the library must be considered, as different types of cells have different associated delays.

### 3.5.3.3 Power

Power is highly correlated to area, so that area is sometimes used as a first-order estimator. When different Vt options are available for cells, Vt assignment can be made after place and route.

#### 3.5.3.4 Design Constraints

Real-life design optimizations perform a trade-off among different cost functions. To express design intent and direct these trade-offs in the right direction, design constraints are used. Design constraints are commonly expressed in SDC format.

### **3.6 The EPFL Benchmarks**

The EPFL Combinational Benchmark Suite (AMARÚ; GAILLARDON; MICHELI, 2015) is a set of benchmarks proposed to evaluate the performance of academic and commercial logic optimization and synthesis tools. It is composed of 23 combinational circuits divided into three main categories: Arithmetic, Random/Control, and *More than ten Million gates* (MtM). Each circuit is distributed in different formats, including Verilog, VHDL, BLIF, and AIGER.

This set of *benchmarks* has been widely used to validate several works, due to providing a nice variety of circuits. Furthermore, are provided a set of circuits with more than one million AND2 nodes when represented in AIG form. It is a relatively expressive size, making these *benchmarks* a good choice to test the scalability of the proposed methods.

# 3.7 Contributions of this chapter

In this chapter, we have presented the main definitions necessary for an understanding of this work. The main concepts concerning AIG based logic synthesis were presented.

### **4 A TAXONOMY OF AIG CUTS**

#### 4.1 About this Chapter

This chapter presents a taxonomy for AIG cuts. We discuss the differences among various types of cuts in AIGs, in order to establish a language that allows the reader to understand different types of cuts, their inner workings and the motivation for their use. This discussion is made from two distinct points of view.

Section 4.2 discusses cuts from a structural standpoint. For instance, questions addressed in section 4.2 include the structural differences between *K*-cuts and *KL*-cuts. Are they always structurally different? Can a given cut be classified as a *K*-cut and as a *KL*-cut at the same time? The structural discussion does not consider the algorithms used to generate the cuts.

### 4.2 Structural Differences Among Different Types of Cuts

Beginning with the structural properties of cuts, with a focus on understanding their definitions and characteristics, this approach enables us to differentiate the various types of cuts and alternative techniques employed for identifying subregions within the graph.

### 4.2.1 K-cut

Let  $K \in \mathbb{N}^*$ , a cut is considered k-feasible if its size is less than K ( $|C| \leq K$ ), defining what is known as a k-cut. Therefore, a cut is said to be K-feasible if its number of inputs is up to K inputs (MISHCHENKO; CHATTERJEE; BRAYTON, 2006b; MISHCHENKO; BRAYTON; CHATTERJEE, 2008).

Structurally, a k-cut is the same as the conventional cut, comprising a list of leaf nodes and a single root node, with the only distinction being the imposed limitation on its size. In this category of cuts, only those with a size not exceeding K are retained, while those surpassing K are discarded (CONG; DING, 1996). This approach aims to reduce the number of cuts, thereby enhancing efficiency.

In other words, a K-cut defines a region in the graph that represents the logic

function of n, using at most K variables. It is a useful tool in technology mapping, especially when targeting FPGAs, which are composed of LUTs that can implement any logic function up to a fixed number of inputs.

*K*-cuts are widely used in logic synthesis, serving to optimize circuits through logic optimization, and also used in technology mapping for both FPGA and ASIC contexts, where the *K*-cuts are replaced by LUTs, for FPGA, or by a standard cell, for ASICs context. The *K*-cuts define regions within the circuit where optimization and mapping techniques are applied.

This type of cut plays an important role in logic synthesis by optimizing circuits through logic optimization such as (MISHCHENKO; CHATTERJEE; BRAYTON, 2006a) where some *K*-cuts are selected and replaced by others with smaller precomputed subgraphs. Moreover, the *K*-cuts are used in technology mapping for both FPGA and ASIC contexts, where the *K*-cuts delineate specific regions within the circuit, which are subsequently replaced by LUTs in FPGA implementations or standard cells in ASICs implementations.

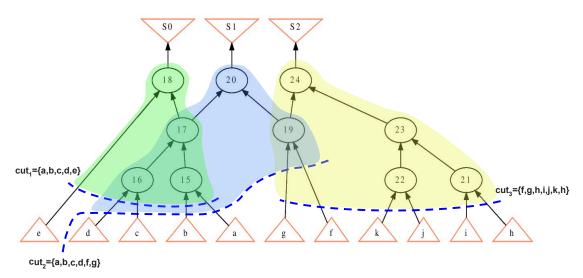

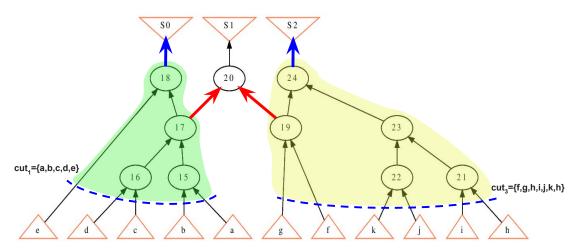

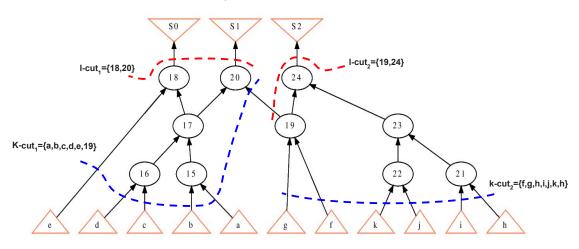

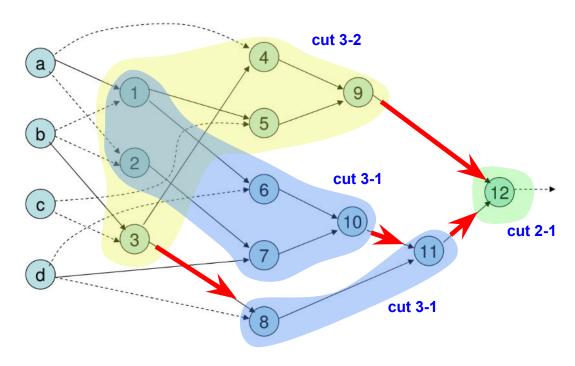

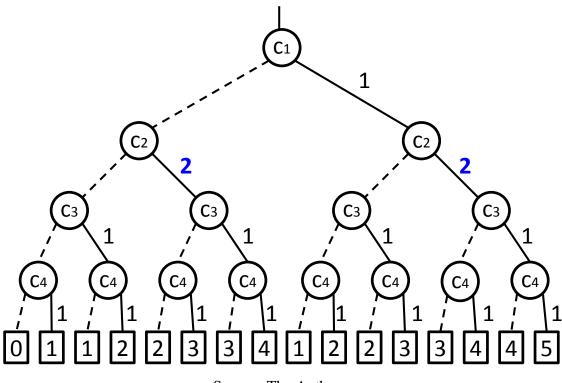

To illustrate the K-cut, Figure 4.1 provides an example of an AIG with three cuts,  $c_1 = \{a, b, c, d, e\}$ ,  $c_2 = \{a, b, c, d, f, g\}$ , and  $c_3 = \{f, g, h, i, j, k\}$ , considering K = 5, we have that the cut  $c_3$  is not a K-cut because this cut has as the leaves the set  $\{f, g, h, i, j, k\}$  that is composed of six leaves ( $|c_3| = 6$ ), thus this cut is not a k-feasible cut. In summary, a K-cut is structurally the same as the conventional cut and only has a restriction on the number of leaves.

Figure 4.1 - K-cut example.

The cuts shown in Figure 4.1 generate the best cover for this AIG, considering a mapping to LUTs using K-cuts with K = 6, this result was obeyed using the "if -K 6"

command in ABC (BRAYTON; MISHCHENKO, 2010). In this example, some nodes belong to more than one *K*-cut, this occurs because the *K*-cut can have only one output, and in this case to obtain the smaller number of LUTs, it is necessary to duplicate some nodes.

A *K*-cut is a type of cut where its structure has only one output. In this type of cut, there may be side-outputs, which are not considered in the cut. Therefore, the subgraph represented by the *K*-cut can have additional interconnection points with the remaining graph (REIS, 2018).

For example, in Figure 4.2, two *K*-cuts,  $cut_1$  and  $cut_2$ , are illustrated, which have as outputs the nodes 18 and 24 (blue arrows), respectively. However, as highlighted with the red arrows,  $cut_1$  has the side-output from node 17 to node 20, and  $cut_3$  has the sideoutput from node 19 to node 20, which are not considered outputs of these *K*-cuts. Consequently, *K*-cuts cannot fully isolate such logic from the rest of the circuit.

Figure 4.2 – Side-outputs of the  $cut_1$  and  $cut_3$ . The blue arrow illustrates the *K*-cut's output and the red arrow illustrates the side edges.

The following equations correspond to the *K*-cuts illustrated in Figure 4.2:  $18 = a \cdot b \cdot c \cdot d \cdot e$  for  $cut_1$  and  $24 = f \cdot g \cdot h \cdot i \cdot j \cdot k$  for  $cut_2$ . In these examples, the remaining nodes, including nodes 17 and 19, do not have equations because they are not the outputs of any cut.

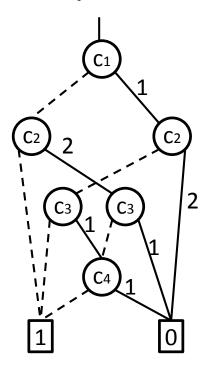

## 4.2.2 KL-cut

Since *K*-cut is limited in terms of the number of outputs, which can not have more than one output, the *KL*-cut arises as an alternative to the *K*-cut limitation. Proposed by

(MARTINELLO et al., 2010), the *KL*-cut is a variation of traditional *K*-cuts which allows the identification of subgraphs with more than only one output.

As the *K*-cuts, the *KL*-cut follows the same definition of a *K*-feasible cut, having up to *K* leaves nodes. However, *KL*-cuts provide more flexibility in terms of the number of outputs, in this structure the number of outputs is not fixed to only one output, the *KL*-cut can have up to *L* outputs. Thus, the *KL*-cut is also a *L*-feasible cut if the cut has up to *L* outputs.

Structurally, a *KL*-cut is very similar to a *K*-cut, these two types of cuts are exactly equal in terms of the leaf nodes. The main distinction between *K*- and *KL*-cuts is the number of outputs that each type can represent.

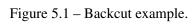

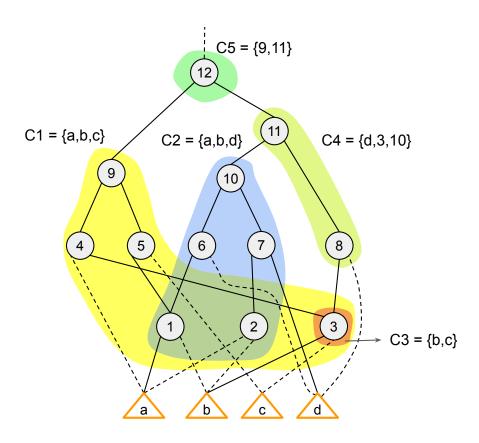

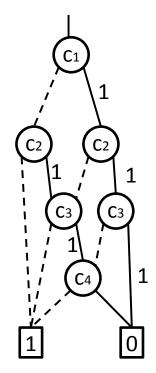

To demonstrate a *KL*-cut, first it is necessary to present the *L*-cut. A *L*-cut is a *backcut*, present in (MARTINELLO et al., 2010), which is quite similar to a cut, that is cut at some edges in the subject graph, however, instead of being a cut at the fanins of a node, which are the inputs of the cut, a *L*-cut is a cut at the fanouts. Figure 4.3 shows an AIG where one can identify two *K*-cuts, described by the blue dashed lines, and two *L*-cuts, described by the red dashed line.

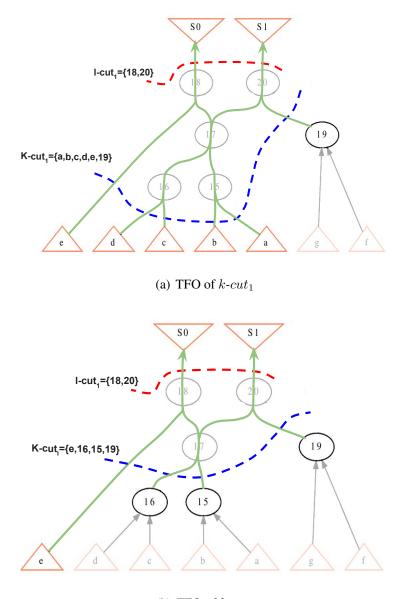

An *L*-cut can be associated with more than one *K*-cut. As an example, Figure 4.4 illustrates two distinct *K*-cuts, *K*-cut<sub>1</sub> and *K*-cut<sub>2</sub>, associated with the same the *L*-cut<sub>1</sub>. The *backcut L*-cut<sub>1</sub> is associated with both *K*-cut<sub>1</sub> and *K*-cut<sub>2</sub> because the *L*-cut<sub>1</sub> intercepts all TFOs (the solid green arrows) from the leaves of *K*-cut<sub>1</sub> and *K*-cut<sub>1</sub>, Figure 4.4(a) and Figure 4.4(b) respectively.

Figure 4.4 – Example of *L*-cut crossing the TFO of *K*-cuts

(b) TFO of k- $cut_i$

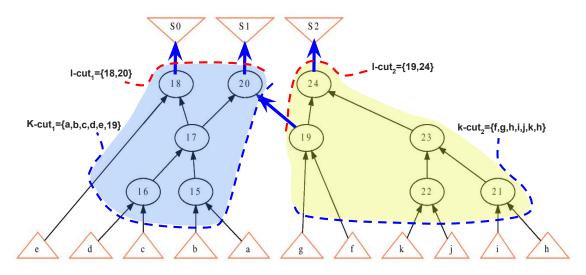

Like a *K*-cut, a *KL*-cut covers a set of nodes in the AIG, the distinction between these two types of cuts is that *KL*-cut covers a subcircuit with up to *L* outputs. Figure 4.5 illustrates the same AIG example from section 4.2.1 covered with *KL*-cuts. In this example are shown two *KL*-cuts which are  $\{\{a, b, c, d, e, 19\}, \{18, 20\}\}$  resultant of *K*-cut<sub>1</sub> and *L*-cut<sub>1</sub>, and *KL*-cut  $\{\{f, g, i, j, k, h\}, \{19, 24\}\}$  resultant of *K*-cut<sub>2</sub> and *L*-cut<sub>2</sub>,

Figure 4.5 – KL-cut cover in AIG. The blue arrows represent the KL-cuts outputs.

A KL-feasible cut is defined as:

$$\{\{l\}, \{o\}\} \mid l \in \text{Leaves}, o \in \text{Outputs}, |l| \le K, |o| \le L$$

$$(4.1)$$

Therefore, the *KL*-cuts showed in Figure 4.5 are *KL*-feasible for K = 6 and L = 2, where both cuts have no more than six inputs and two outputs. Any cut that exceeds these two values, is not a *KL*-feasible cut and, thus, is not a *KL*-cut.

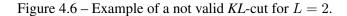

However, not every sub-circuit with more than one output is necessarily a KL-cut. For instance, Figure 4.6 depicts a cut that is not a KL-cut for L = 2, where the blue arrows represent the outputs. This cut might be mistaken for a KL-cut with two inputs. However, despite having the correct number of outputs (two in this case), there is a sideoutput from node 17 to node 18, violating the fundamental property of a KL-cut, which dictates that every fanout from the sub-circuit must be an output of the KL-cut to qualify as such. Therefore, for a cut to be classified as a KL-cut, it must not only be K-feasible and L-feasible but also can not have side-outputs.

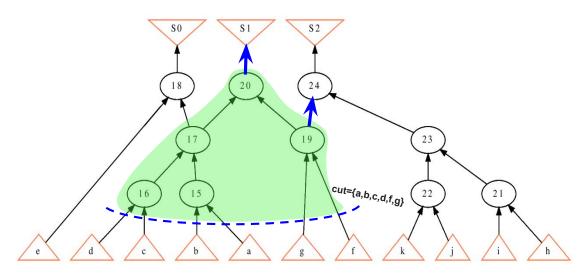

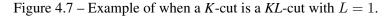

Continuing the discussion on the distinctions between K-cuts and KL-cuts, another question arises: Is a K-cut considered a KL-cut when L = 1? To address this query, Figure 4.7 illustrates two K-cuts, K-cut<sub>1</sub> and K-cut<sub>2</sub>, with outputs 20 and 23 respectively. With K = 6, both cuts qualify as K-cuts since they possess only one output, indicated by the blue arrows, and respect the number of inputs limit.

However, as depicted in Figure 4.7, only K- $cut_2$  satisfies the criteria for a KL-cut with L = 1 since it lacks side-outputs. In contrast, K- $cut_1$  fails to meet the requirements of a KL-cut due to its two side-outputs from nodes 17 and 19. This example highlights that the presence of only one output is insufficient to classify a K-cut as a KL-cut with L = 1; rather, the absence of side-outputs is necessary for a K-cut to be also considered a KL-cut.

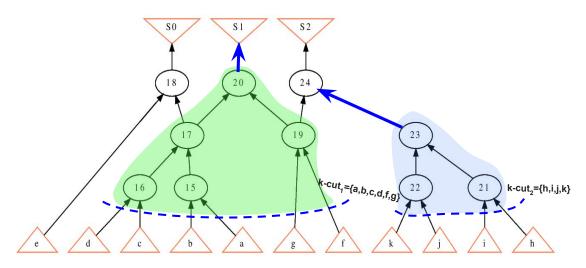

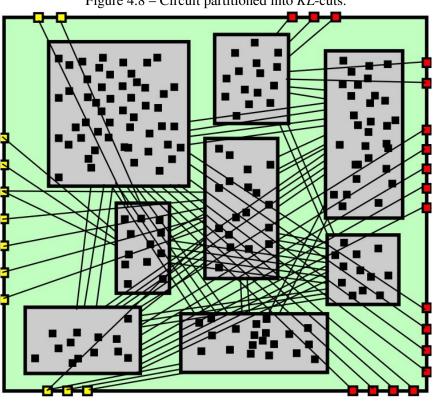

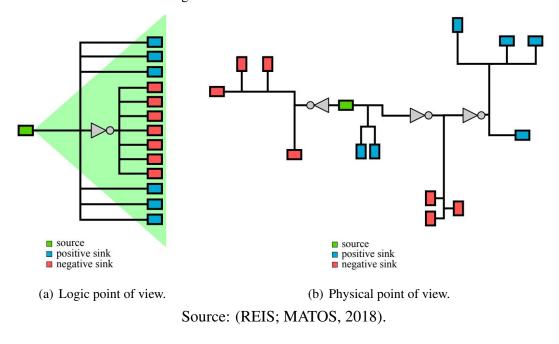

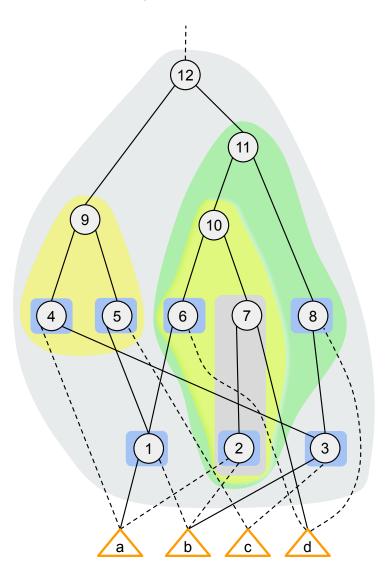

When a circuit is positioned into KL-cuts, blocks, as shown in Figure 4.8, the outputs from each block, and the PIs, are connected to other input blocks. This illustrated example is a bad-quality circuit because the blocks' positions imply long wires to connect the blocks and POs (REIS; MATOS, 2018).

Figure 4.8 – Circuit partitioned into KL-cuts.

Source: (REIS; MATOS, 2018).

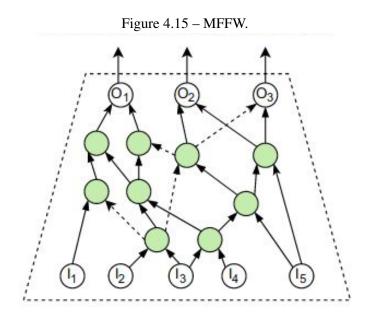

While the KL-cuts act as node containers in the AIG, there is another type of cut used to signal distribution called 1L-cuts, that is a KL-cut with the fixed number of inputs K = 1. The *IL*-cut is useful to make the placement of the *KL*-cuts in the circuit aiming to improve its quality (REIS; MATOS, 2018).

# 4.2.2.1 1L-cut

A 1L-cut is a specialized type of cut that has up to L outputs while being restricted to only one input. Unlike the previously discussed cuts, which are employed in identifying and representing circuit components known as logical blocks, the 1L-cut serves a purpose in routing, where routing involves the distribution of signals between these logical blocks (REIS, 2018). The 1L-cut structure is shown in Figure 4.9.

Figure 4.9 – Points of view of a 1L-cut.

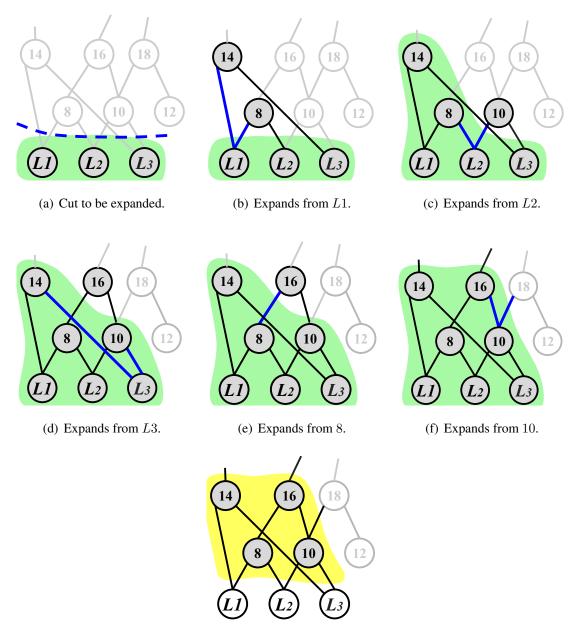

### 4.2.3 Windowing

The concept of windowing was introduced in (MISHCHENKO; WANG; KAM, 2003). The technique of defining windows consists of identifying regions around some nodes in the AIG. Delimiting such regions on the circuit, it is possible to apply local optimizations inside each window separately.

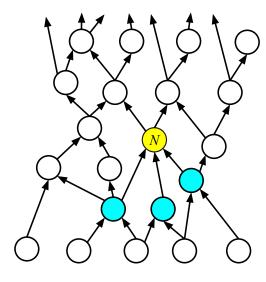

A window is constructed around a node N of the graph. To achieve this, a maximum distance limit is defined from the node both in the direction of its fanout and in the direction of its fanin. These values are defined by m and n, respectively.

Figure 4.10 illustrates, at a high level, the identification of nodes in the neighborhood of N. First, are identified the nodes that are at a distance n from the node N (Figure 4.10(a)). Next, are identified the nodes that are at a distance m from the node N (Figure 4.10(b)).

Subsequently, the nodes in reconvergent paths are identified (Figure 4.10(c)). Finally, the set of nodes obtained in the previous steps defines the window around the node N, where the nodes O are the outputs of the window and the nodes L are the inputs of the window (Figure 4.10(d)).

(a) Nodes on the fanin which are distance-m.

(b) Nodes on the fanout which are distance-n..

(c) Nodes on reconvergent paths.(d) Resulting Window of N.Source: Adapted from (MISHCHENKO; BRAYTON, 2005).

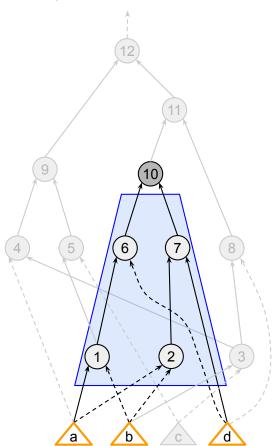

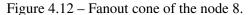

# 4.2.3.1 Fanin Cone

A node's fanin cone, also known as the TFI cone, refers to the set of nodes accessible through its incoming edges. In this way, the fanin cone of a node n includes the node n itself and all nodes in the TFI of n, including the PIs (MISHCHENKO; CHATTERJEE; BRAYTON, 2006a). In other words, the fanin cone is the set of nodes that produce the logic for the node n.

Figure 4.11 illustrates the fanin cone of the node 10. As depicted, this fanin cone

is composed of nodes 1, 2, 6, and 7, which collectively provide the logic utilized by node 10.

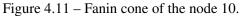

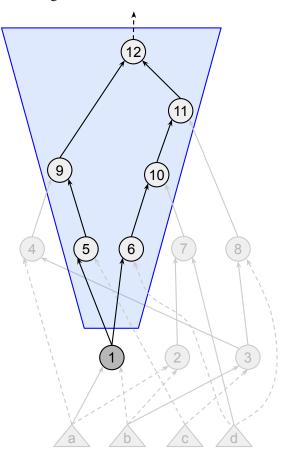

## 4.2.3.2 Fanout Cone

Similarly to the Fanin Cone, the fanout cone encompasses the nodes accessible through its outgoing edges (MISHCHENKO; CHATTERJEE; BRAYTON, 2006b). The TFO cone of node  $nd_j$  includes the node  $nd_j$  itself and all nodes that are in the TFO of  $nd_j$ , including the POs (MISHCHENKO; CHATTERJEE; BRAYTON, 2006a).

Figure 4.12 illustrates the fanout cone of node *1*, comprised of nodes *5*, *6*, *9*, *10*, *11*, and *12*. These nodes, accessible from the fanouts of node *1*, collectively represent the portion of the circuit influenced by node *1*.

## 4.2.3.3 Fanout-Free Cone

A Fanout-Free Cone (FFC) centered at node n constitutes a subgraph structure where node n is the root. In the FFC, each node, excluding the root, has outgoing edges directed solely towards the root node, creating a cone-like topology within the graph. In a straight way, each path from an input of the FFC converges to the root node of the FFC (CONG; DING, 1996).

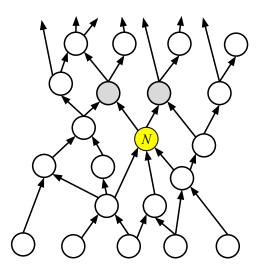

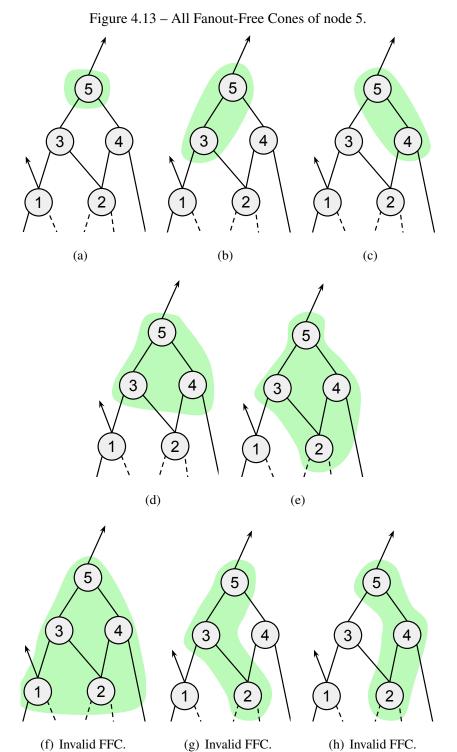

An AIG node can comprise various FFCs, as depicted in Figure 4.13. In this illustration, the FFCs of node 5 are highlighted in green shading. Figures 4.13(a) through 4.13(e) depict five examples of FCCs for node 5, wherein only node 5, the root, has an output outside the FFC, thus illustrating FFCs of node 5.

However, in Figure 4.13(f), node 1 has an outgoing edge outside the shaded area. Since the root node in this example is node 5, this set of nodes does not constitute an FFC for node 5. Similar instances are illustrated in Figures 4.13(g) and 4.13(h), where node 2 has an outgoing edge outside the shaded area. Therefore, these three figures provide examples of node sets that do not form FFCs for node 5.

Given that all logic generated within the FFC is solely utilized within the cone itself, the FFC offers the ability to completely isolate the logic contained within the cone from the remainder of the graph. The FFC contains the logic used only by its root node.

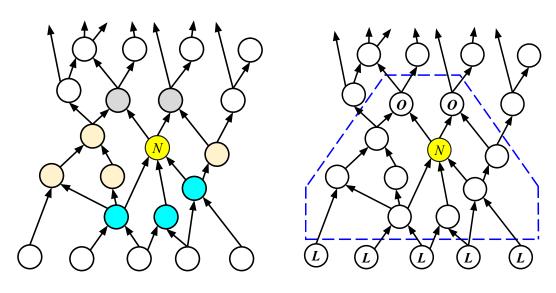

### 4.2.3.4 Maximum Fanout-Free Cone

The Maximum Fanout-Free Cone (MFFC) of a node in a circuit refers to a subset of its fanin cone that contains only nodes such that every path from these nodes to the POs passes through the node itself. In simpler terms, the MFFC of a node encompasses all the logic exclusively utilized by that node. When a node is either removed or substituted within the circuit, the logic contained within its MFFC can also be safely removed, as it is no longer necessary for the circuit's functionality (MISHCHENKO et al., 2007; CALVINO et al., 2022).

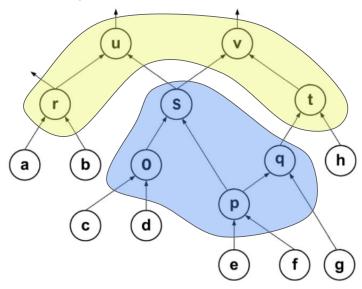

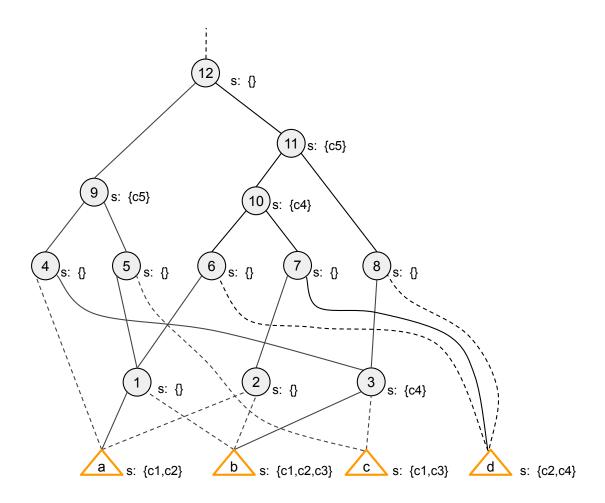

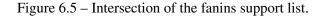

The MFFC encompasses every FFC rooted at node n. Additionally, an MFFC can be further characterized as follows: for a given node w, if the output of node w is within the MFFC(v), then node w itself is also within the MFFC(v). In other words, output(w) $\subseteq MFFC(v) \Rightarrow w \in MFFC(v)$ . This characterization is based on the work by Cong and Ding (CONG; DING, 1996).