## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL PÓS GRADUAÇÃO EM CIÊNCIA DE COMPUTAÇÃO

CV2D - Operador de Convolução para Processamento de Imagens em Tempo Real

por

João C. Netto

Dissertação submetida como requisisto parcial para a obtenção do grau de Mestre em Ciência da Computação

Prof. Tiaraju Vasconcellos Wagner Orientador

Porto Alegre, Dezembro de 1989

## Catalogação na Fonte

Netto, João Cesar

CV2D - Operador de convolução para processamento de imagens em tempo real. Porto Alegre, PGCC - UFRGS, 1989

1v.

Diss. (mestr. ci. comp.) UFRGS - PGCC, Porto Alegre, BR-RS, 1989.

Dissertação: Processamento de Imagens: Processamento de Sinais:

Convolução: Arquiteturas Sistólicas.

"Senhor que queres que eu faça?" São Francisco de Assis

#### AGRADE CIME NT 05

Agradecimentos à Universidade Federal do Rio Grande do Sul que proporciona e incentiva a pesquisa mesmo com os poucos recursos destinados a este fim pelo governo federal. À Université Catholique de Louvain que, através de um convênio de cooperação, possibilitou o projeto e implementação do protótipo do circuito CV2D. Também aos órgãos financiadores públicos, CNPq e CAPES, e particulares, IBM, pelo apoio financeiro na forma de bolsa de mestrado, permitindo a dedicação ao trabalho.

Aos meus pais, que sem o esforço na orientação, formação, amizade e sacrifício financeiro não existiria este trabalho. A minha namorada, pela sua paciência, presença e amor e também pela inumerável quantidade de cartas durante minha ausência.

Fica o agradecimento a todos meus professores, pelos conhecimentos transmitidos e estímulo científico e intelectual. Em especial ao companheiro e orientador Tiaraju Wagner, que aceitou enfrentar junto este trabalho e pelas horas de bate-papo sempre produtivas e também ao prof. Philippe Navaux por sua intervenção junto a CAPES no processo de estágio no exterior. Ao prof. Raul Weber pelo auxílio na utilização dos MACs e paciência na conversão de formatos.

Ao "gurú" e amigo Altamiro Suzim, por suas sugestões e perguntas e por mostrar, através de suas atitudes, o comportamento do espírito científico e o entusiasmo de acreditar nas pessoas.

Ao pessoal que fica atrás da cortina, bibliotecárias, secretárias, telefonistas, recepcionistas e faxineiras, que acompanharam este trabalho desde o seu início e forneceram a infraestrutura para sua realização.

Ao time da engenharia, 1985, sempre dispostos a realizar os projetos mais impossíveis: Ricardo Telichevesky, Fernando Belmonte, Eduardo Todt, Régis Huf, Carlos Prolo, Luigi Carro, Cirano Silveira e aos demais que estiveram juntos.

Ao amigo e sócio Alexandre Caríssimi, pela amizade e batalhas enfrentadas juntos. Também por aquelas "broncas" deixadas como herança e pelo seu aprendizado e parceria de chimarrão.

Aos amigos belgas, Frank Vos e André Vandelmelbrok, pela acolhida no país estrangeiro, disponibilidade de tempo e principalmente pela amizade e paciência nos diálogos em francês. Também ao belgo-brasileiro Ricardo Jacobi com quem tive oportunidade de trocar muitas idéias durante os seis meses que convivemos em Louvain.

Muitas pessoas contribuiram, direta ou indiretamente, na realização deste trabalho, sem as quais este não chegaria ao fim e citar todas as pessoas que comigo participaram dos últimos três anos seria impossível. Fica no entanto o agradecimento ao longo da convivência da vida.

De forma especial agradeço a Deus, pelo magnífico dom da vida e pelas pessoas que passaram em meu caminho.

# SUMáRIO

| GLOSSáRIO                                   | 9  |

|---------------------------------------------|----|

| LISTA DE ABREVIATURAS                       | 15 |

| LISTA DE FIGURAS                            | 17 |

| RESUMO                                      | 19 |

| ABSTRACT                                    | 21 |

| 1 INTRODUÇÃO                                | 23 |

| 1.1 Conceitos Básicos                       | 23 |

| 1.2 <u>Escopo e Organização do Texto</u>    | 26 |

| 2 SINAL DE VÍDEO                            | 29 |

| 2.1 Modelo de Imagem                        | 29 |

| 2.2 <u>Caracterização do Sinal de Vídeo</u> | 31 |

| 2.2.1 Características                       |    |

| 2.2.2 Fundamentos de Cor                    | 36 |

| 2.2.3 Padrões                               | 37 |

| 2.2.4 Degradações                           |    |

| 2.3 <u>Vídeo Digital</u>                    | 46 |

| 2.3.1 Amostragem e Quantização              | 46 |

| 2.3.2 Efeitos da Digitalização              | 48 |

| 2.4 Exibição de Imagens                     |    |

| 2.5 <u>Conclusão</u>                        |    |

| 3 PROCESSAMENTO DE IMAGENS                  |    |

| 3.1 <u>Componentes de um Sistema IP</u>     |    |

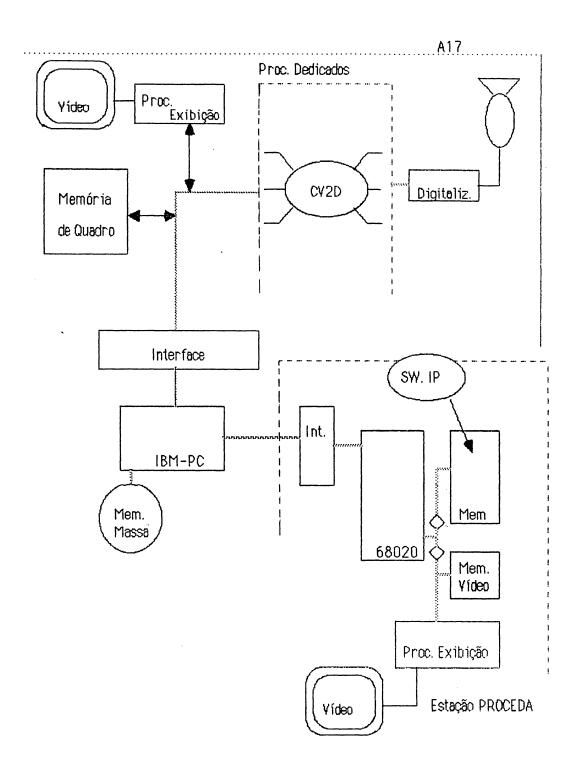

| 3.2 <u>Sistema A17</u>                      |    |

| 3.3 <u>Convolução Bidimensional</u>         | 71 |

| 3.4 <u>Conclusão</u>                        |    |

| 4 ARQUITETURA DE CONVOLUÇÃO                 |    |

| 4.1 Concepção e Mapeamento de Arquiteturas  |    |

| 4.2 <u>Materialização do Algoritmo</u>      |    |

| 4.2.1 Método de Choen & Johnson             |    |

| 4.3 <u>Frentes de Onda</u>                  |    |

| 4.4 Fluxo de Dados                          |    |

| 4.5 <u>Conclusão</u>                        |    |

| 5 CV2D                                      |    |

| 5 1 Descrição Geral                         | 91 |

| 5.2 CV2D - Descrição Funcional              |      |

|---------------------------------------------|------|

| 5.3 <u>Descrição Operacional</u>            |      |

| 5.4 Particionamento                         |      |

| 5.4.1 Unidade de Convolução                 |      |

| 5.4.1.1. Elementos de Processamento         | 104  |

| 5.4.1.2 Sincronização                       | 105  |

| 5.4.1.3 Unidades de Ajuste de Fase          | 106  |

| 5.4.2 Unidade de Deslocamento               | 106  |

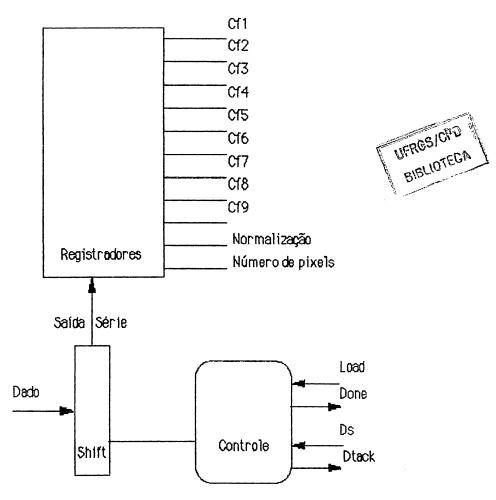

| 5.4.3 Unidade de Programação                | 106  |

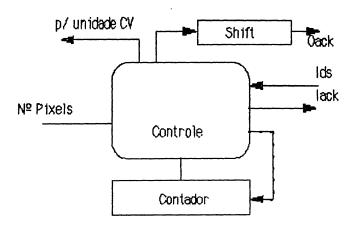

| 5.4.4 Unidade de Sincronização              | 108  |

| 5.5 <u>Detalhes</u>                         | 108  |

| 6 IMPLEMENTAÇÃO                             | ,111 |

| 6.1 <u>Síntese do Fluxo de Dados</u>        | 112  |

| 6.1.1 Cadeia de Processadores               | 112  |

| 6.1.2 Registradores de Deslocamento         | 114  |

| 6.1.3 Unidade de Deslocamento               | 114  |

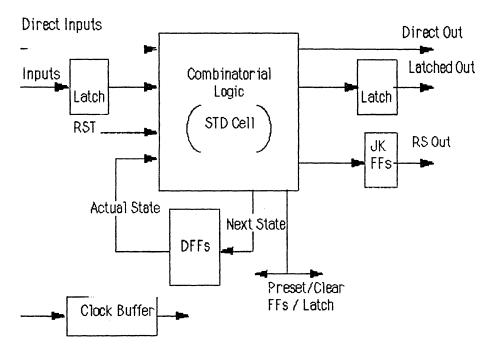

| 6.2 <u>Síntese das Máquinas de Controle</u> | 114  |

| 6.3 <u>Posicionamento e Interconexão</u>    |      |

| 6.4 <u>Testes</u>                           | 117  |

| 7 CONCLUSÕES                                | 121  |

| 7.1 Condições de Desenvolvimento do Projeto | 122  |

| 7.2 Melhorias                               | 123  |

| 7.2.1 Testabilidade                         | 124  |

| 7.3 Resultados                              | 126  |

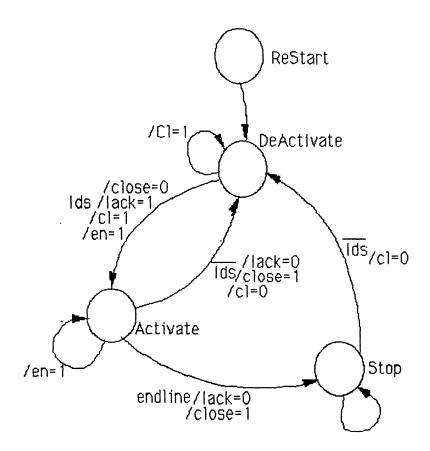

| ANEXO 1 - Diagramas de Estado               | 131  |

| ANEXO 2 - Distribuição de PADs              |      |

| ANEXO 3 - Informações Preliminares          |      |

| REFERÊNCIAS BIBLIOGRÁFICAS                  |      |

#### **GLOSSáRIO**

Ad hoc

Técnica de projeto que segue, fundamentalmente, a experiência do projetista.

Aliasing

Erro originado pela utilização de uma taxa de amostragem inferior à necessária para o sinal.

Caracteriza-se pela impossibilidade da recontrução do sinal original.

And

- Operador lógico 'E'

Arrays

Conjunto de processadores, semelhantes ou não, que trabalham em conjunto na execução de um algoritmo.

Barrel shifter

Elemento combinacional que realiza um deslocamento de um determinado número de bits em uma palavra.

Bit slice

Unidade funcional de um bit que pode ser multiplicada para compor uma uma unidade de vários bits.

Blurring

Degradação caracterizada pela perda de definição das bordas da Imagem. É causada pela atenuação das componentes de alta frequência.

Broadcast

Tipo de transmissão de televisão. Caracteriza-se por usar o ar como meio de propagação, permitindo que qualquer aparelho receba a informação.

Buffer

Componente de um sistema empregado como área temporária para o armazenamento de dados.

Checker board

Efeito de tabuleiro de xadrez. É o mesmo que pixellation.

Clock

- Relógio. Base de tempo para os sistemas digitais.

Cross Colour

Efeito de degradação de uma imagem colorida devido a superposição da crominância e da luminância no início da banda de frequência da crominância. Cross Luminance - Efeito de degradação de uma imagem colorida devido a superposição da crominância e da luminância no final da banda de frequência da luminância. Data flow Modelo computacional onde o controle da máquina é orientado pelo fluxo dos dados. Delay Tempo de propagação de um sinal elétrico, ou atraso imposto à transferência de um dado. Dot pitch - O mesmo que pitch. Filter Operação de filtragem. Flicker - Efeito de piscamento da imagem devido a baixa frequência de varredura vertical. - Panta baixa. Disposição dos blocos funcionais em um Floor plan circuito integrado. Frame Grabber - Dispositivo capaz de digitalizar e armazenar um quadro de imagem de TV. Frame Quadro de uma imagem de TV. Seus limites são dados por uma varredura vertical completa. Handshake Protocolo de comunicação entre duas máquinas. Entrada. Input Kerne1

- Máscara ou núcleo de uma operação de convolução. Matriz de constantes que definem os coeficientes de uma operação bidimensional de mácara.

Keying

Capacidade de adicionar planos de texto em planos gráficos.

Layout

- Desenho da disposição física dos elementos de um circuito integrado e de suas interconexões.

Layout custom

Layout realizado pelo próprio projetista, desenhado sem o auxílio das ferramentas automáticas do sistema de CAD utilizado.

Lentgh () - Indica o tamanho do argumento parentizado. Line ficlker - Efeito de piscamento local, que afeta apenas uma linha. Look-up-tables - Tabelas que fornecem o valor de saída indexado pelo seu valor de entrada. Net list - Lista dos componentes de um sistema e de suas interconexões. Not Operador lógico de negação. Or - Operador lógico 'OU' - Saída. Output Overflow Estouro de representação numérica. Pan Deslocamento da janela de exibição de uma imagem na direção horizontal, dentro de seu universo. Phosphor spacing - Espaçamento entre os elementos de fósforo de um tubo de Imagem. Picture Elements - Pixels. Menor elemento de imagem. Seu conjunto forma um quadro de imagem digital. - Espaçamento dos pontos de fósforo de uma mesma Pitch cor em um tubo de imagem. Pixellation - Efeito de tabuleiro de xadrez. A imagem é vista como um conjunto de quadrados que definem seus objetos. - Tamanho do pixel. Dimensão do elemento de imagem, Pixel size

Tamanho do pixel. Dimensão do elemento de imagem, que, quando colorida, é composto pelos três pontos de cor.

Placement

Posicionamento dos blocos funcionais em um circuito integrado.

Reset

Sinal de inicialização de um equipamento ou bloco funcional. Retimming - Técnica que consiste em modificar a temporização do sistema a fim de melhorar seu desempenho. - Desenho das linhas de interconexão dos elementos de Routing um sistema. Row processor - Processador de linha. Nome dado ao conjunto de elementos de processamento que tratam os pixels de uma determinada linha da imagem. Salt-and-peeper - Ruído caracterizado por pontos pretos e brancos na tela, causados por interferência elétrica no sinal de vídeo. Scanning - Processo de conversão de uma cena em um sinal elétrico, através de um feixe de elétrons que se desloca, ao mesmo tempo, nas direções horizontal e vertical. Scan Motré - Efeito de batimento em áreas da imagem que são iluminadas uniformemente. Caracteriza-se linhas horizontais nas áreas de mesma luminosidade. Scrool Deslocamento da janela de exibição de uma imagem na direção vertical, dentro de seu universo.

Sharpening

Processo de enriquecimento de imagem que reforça as altas frequências. Seu objetivo é realçar o contorno dos objetos de uma imagem.

Skew

Atraso colocado a fim de ajustar a temporização dos dados.

Slices

- Fatias. Conjunto funcional que pode ser replicado para formar unidades maiores.

Sliced floor plan

- Planta baixa de um circuito integrado que caracteriza-se por todos os blocos possuirem forma tetragonal ( quatro lados ).

Smoothing

Processo de enriquecimento de imagem que atenua as altas frequências. Seu objetivo é a redução de ruído.

Speckly, efeito

- Degradação em forma de manchas, que aparece em imagens geradas por fontes de luz coerentes.

Spot size

Tamanho da malha ou grade que existe nos tubos de imagem. A função desta malha é de colimar o feixe de elétrons.

Standard cells

Técnica de implementação semi-dedicada de circuitos integrados. Caracteriza-se por possuir blocos funcionais que possuem mesma altura, possibilitando sua justaposição.

Sync

Pulso de sincronismo existente no sinal de vídeo fornecido por uma câmera de TV.

Throughput

- Taxa de saída de dados de um processador.

Twin tub

Tecnologia de fabricaçãode circuitos integrados que utiliza poço 'P' e 'N'.

Vídeo Moiré

Efeito que causa o aparecimento de faixas verticais estreitas, com distância múltipla do espaçamento das trilhas de fósforo.

Wavefronts

- Frentes de onda. Representam a movimentação dos dados em relação ao tempo.

#### LISTA DE ABREVIATURAS

ALU - Arithmetic Logic Unit ( Unidade Lógica e Aritmética )

ASIC - Application Specific Integrated Circuit ( Circuito Integrado Dedicado )

BB - Bounding Box

CAD - Computer Aided Design ( Projeto Auxiliado por Computador)

CAPES - Coordenadoria de Aperfeiçoamento de Pessoal e Ensino Superior

CC - Chip Compiler

CCD - Charged Coupled Device (Dispositivo de Acoplamento de Carga)

Cl - Circuito Integrado

CNPq - Conselho Nacional de Pesquisa

CPGCC - Curso de Pós Graduação em Ciência da Computação

CRT - Cathode Rays Tube (Tubo de Raios Catódicos)

DPC - Data Path Compiler

DSP - Digital Signal Processing (Processamento Digital de Sinais)

f | - Frequência de linha; frequência de varredura horizontal

fs - Frequência de amostragem

IP - Image Processing ( Processamento de Imagens )

LFSR - Linear Feedback Shift Register

LS - Logic Syntetizer

MIPS - Milhões de operações por segundo

NTSC - National Television Standards Commites

PE - Processing Element (Elemento de Processamento)

RMS - Root Mean Square (Valor médio quadrático)

SAW - Surface Acoustic Waves (Ondas Acusticas de Superfície)

SM - State Machine Compiler

UFRGS - Universidade Federal do Rio Grande do Sul

# LISTA DE FIGURAS

| Fig. | 1.1 | Elementos de um Sistemas de Processamento Digital de   |     |

|------|-----|--------------------------------------------------------|-----|

|      |     | Imagens                                                | 24  |

| Fig. | 2.1 | Modelo de Formação da Imagem                           | 31  |

| Fig. | 2.2 | Sinais de Sincronismo                                  | 35  |

| Fig. | 2.3 | Formato RS170                                          | 39  |

| Fig. | 2.4 | Níveis de quantização e Aplicações                     | 48  |

| Fig. | 2:5 | Razão de Visualização                                  | 49  |

| Fig. | 2.6 | Dot Pitch Pv e Ph                                      | 52  |

| Fig. | 2.7 | índice de Modulação (m) e Razão de Contraste (c)       | 53  |

| Fig. | 2.8 | Relação entre SpotSize- DotPitch- PixelSize            | 55  |

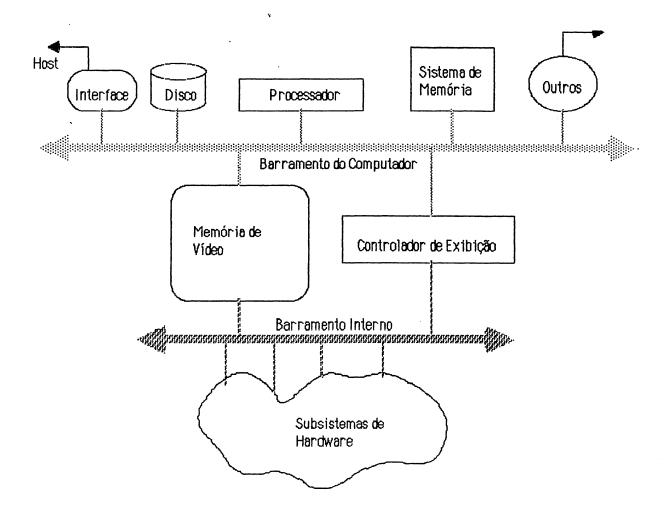

| Fig. | 3:1 | Classificação hierárquica dos algoritmos IP            | 60  |

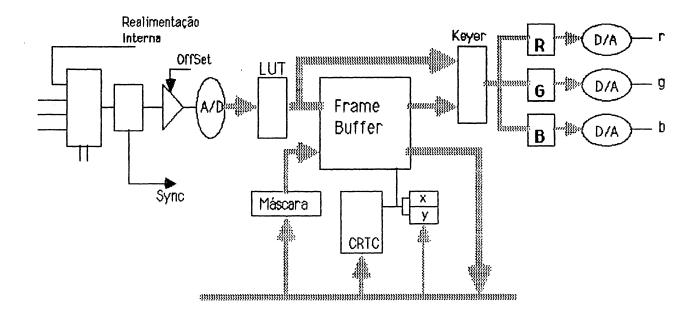

| Fig. | 3.2 | Arquitetura com Barramento Interno                     | 63  |

| Fig. | 3.3 | Digitalizador de Vídeo PIP                             | 64  |

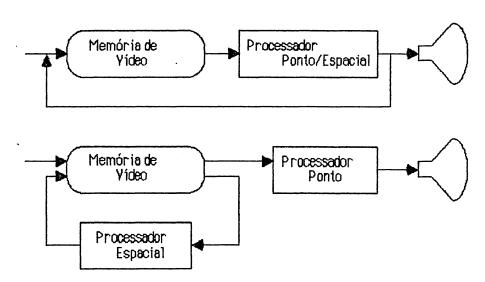

| Fig. | 3.4 | Configurações de Processadores Especializados de Vídeo | 65  |

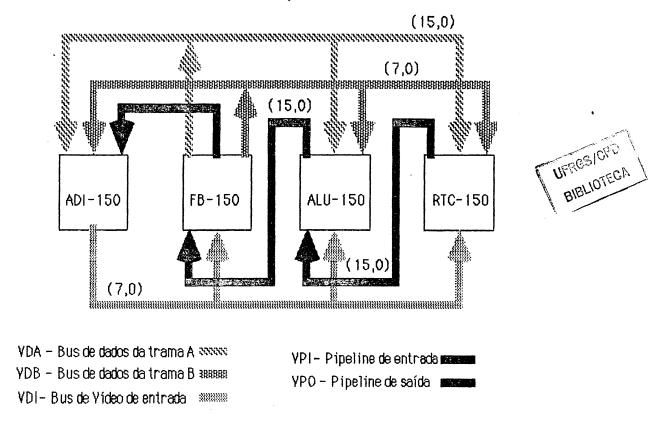

| Fig. | 3.5 | Arquitetura do Sistema Série 150                       | 67  |

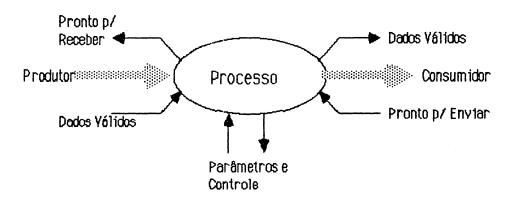

| Fig. | 3.6 | Modelo de Processo no Sistema A17                      | 69  |

| Fig. | 4.1 | Representação Gráfica do Elemento de Delay             | 84  |

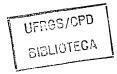

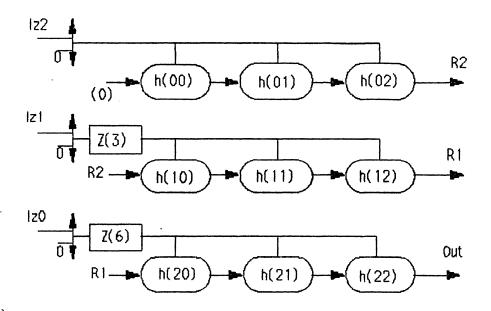

| Fig. | 4.2 | Implementação das Redes de Convolução                  | 86  |

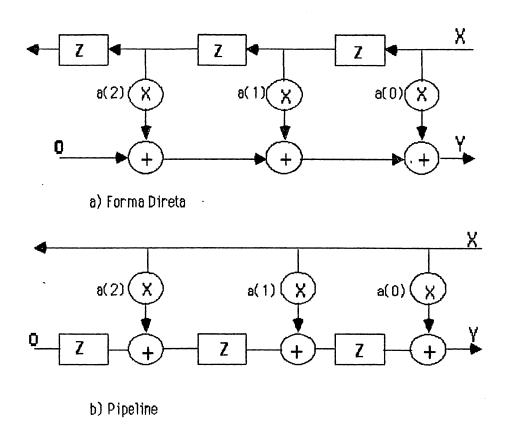

| Fig. | 4.3 | Implementação da Convolução Bidimensional              | 89  |

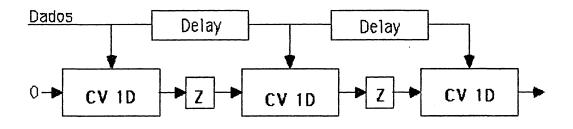

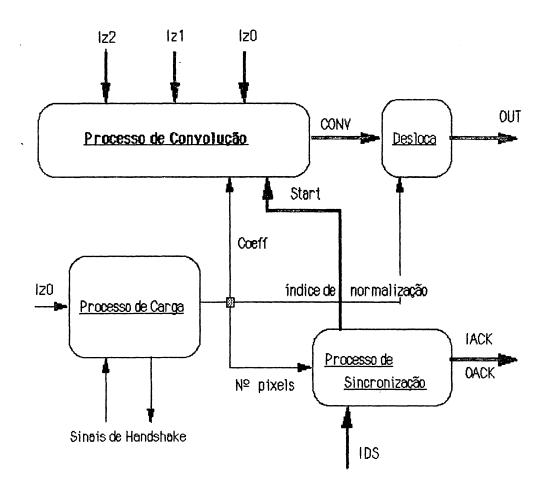

| Fig. | 5.1 | Modelo do Ambiente de Funcionamento do CV2D            | 94  |

| F1g. | 5.2 | Diagrama em Blocos                                     |     |

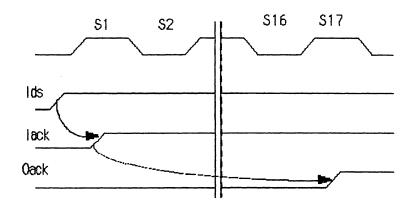

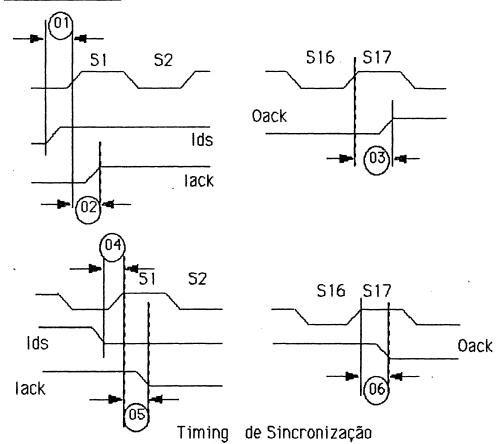

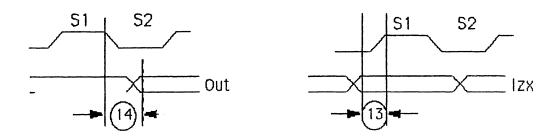

| Fig. | 5.3 | Forma de Onda de Sincronização                         |     |

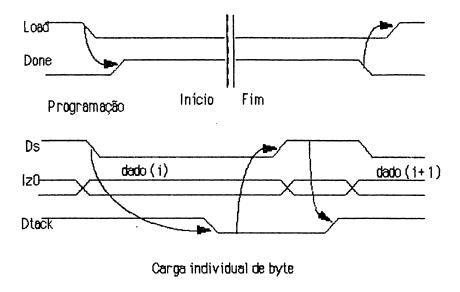

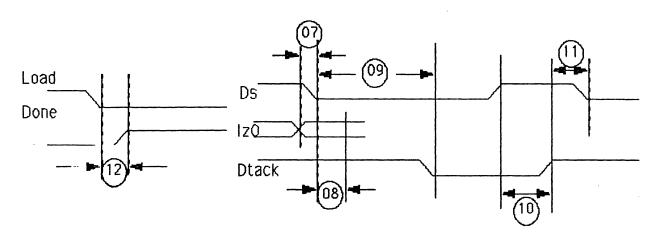

| Fig. | 5.4 | Formas de Onda de Programação                          |     |

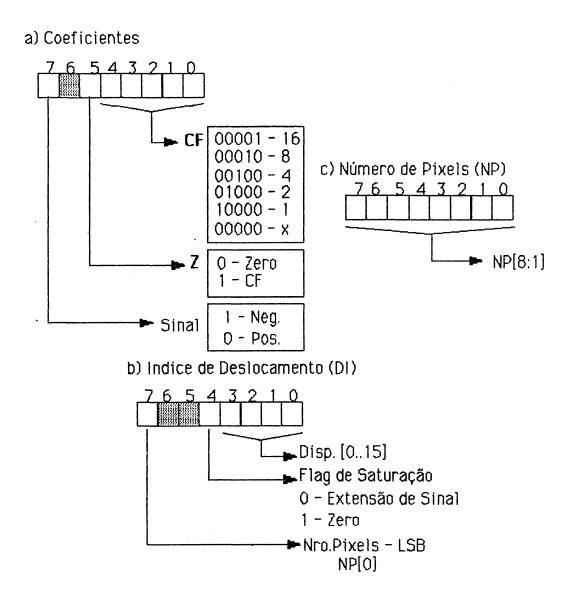

| •    | 5.5 | Parâmetros de Programação                              | 100 |

| Fig. | 5.6 | Formato dos Parâmetros de Programação                  | 101 |

| •    |     | Efeito do Indice de Deslocamento                       |     |

| Fig. | 5.8 | Unidade de Convolução                                  | 104 |

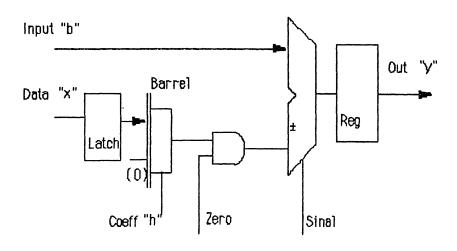

| Fig. | 5.9 | Arquitetura do Elemento de Processamento               | 105 |

| _    |     | Unidade de Programação                                 |     |

| _    |     | Unidade de Sincronização                               |     |

| •    |     | Caminho Crítico                                        |     |

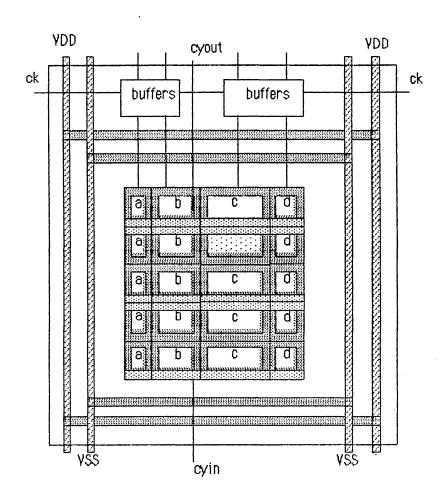

|      |     | Layout gerado pelo DPC                                 |     |

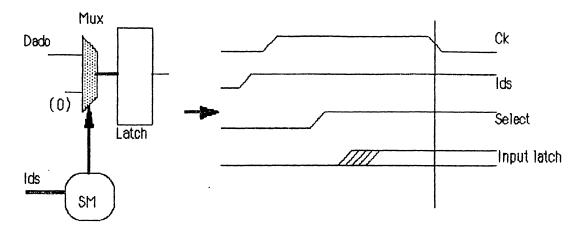

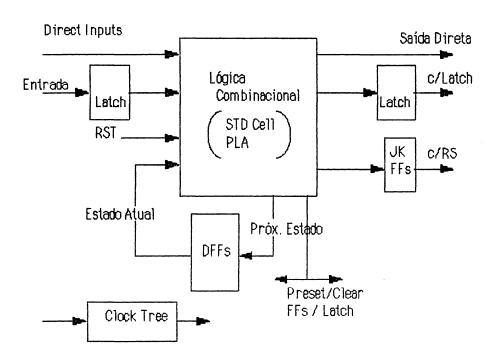

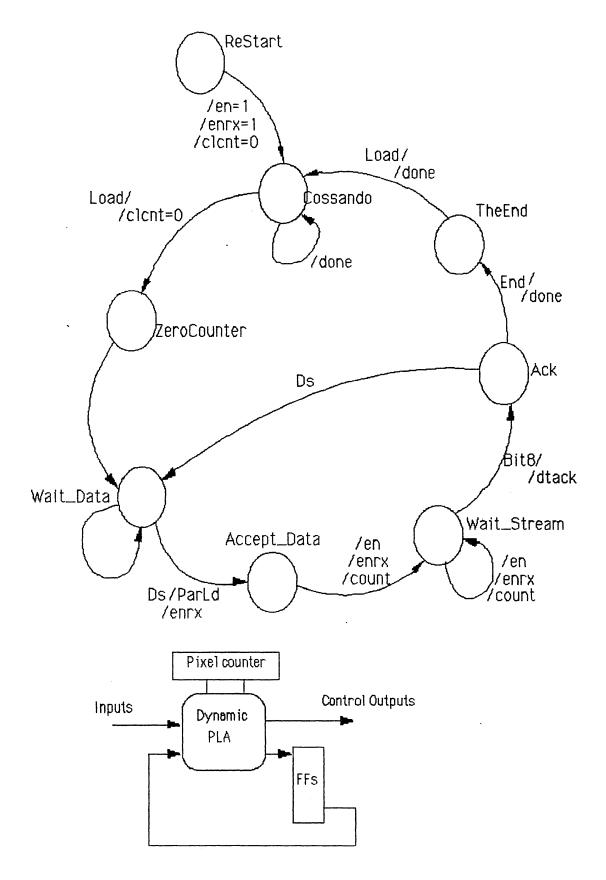

| _    |     | Arquitetura Alvo das Máquinas de Estado                |     |

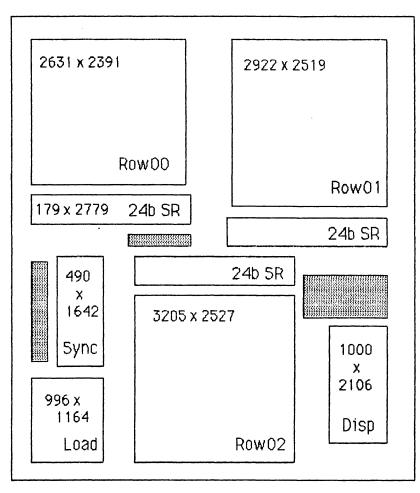

| Fig. | 6.3 | CV2D - Planta Baixa                                    | 117 |

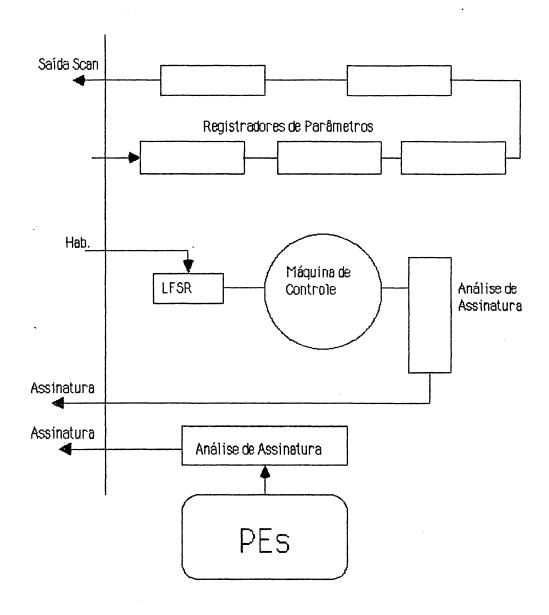

| Fig. | 7.1 | Estruturas de Teste | 126 |

|------|-----|---------------------|-----|

| Fig. | 7.2 | Arquitetura PGCC    | 129 |

#### **RESUMO**

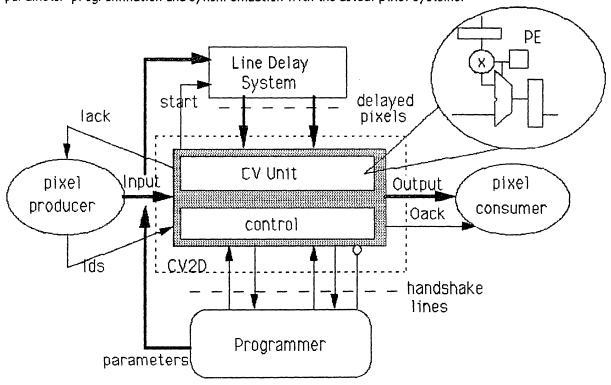

Este trabalho descreve a concepção de um circuito integrado dedicado (ASIC), destinado a realizar a operação de convolução sobre imagens em tempo real. São analisadas as características do sinal de vídeo e algumas propostas de sistemas de processamento de imagens (IP). É caracterizado um ambiente de IP assim como o projeto de um operador de convolução chamado CV2D.

O CV2D calcula, à taxa de pixel, a convolução bidimensional sobre imagens quantizadas em 8 bits/pixel e até 512 pixels/linha. O circuito foi projetado para ser uma interface em sistemas de processamento de imagens, podendo realizar ou filtragem linear ou convolução sobre uma sequência de pixels. O processo de convolução necessita de duas linhas de varredura anteriores e o armazenamento destes dados é realizado através de um sistema de *Line Delay*, atualmente implementado fora do componente.

#### **ABSTRACT**

This work describes the design of an Aplication Specific Integrated Circuit (ASIC) dedicated to perform the real time convolution over monochromatic images. The video signal characteristics and some alternatives for image processing (IP) systems are considered. An IP environment is characterized and the design of a convolution operator called CV2D is presented.

The CV2D computes, at pixel rate, the bidimensional convolution over 8 bits/pixel quantized images up to 512 pixels/line. The chip was designed to be an interface for Image processing systems performing linear filtering or convolution processing of a pixel stream. The convolution process needs two delayed lines and the storage of these lines is performed by means of a line delay circuit, actually implemented out of the chip.

# 1 INTRODUÇÃO

" Pois a dúvida agrada-me não menos que o saber. " Dante (1265-1321). Inferno.

Dentro do vasto domínio de aplicações na área de tratamento de sinais, ênfase especial é dada ao ramo de processamento digital de sinais (DSP). Esta área foi fortemente impulsionada pelo aumento dos recursos computacionais disponíveis e pelo avanço e integração das técnicas digitais. A teoria matemática, ferramenta que sustenta o desenvolvimento desta matéria, encontra-se na bibliografia relacionada ao assunto, onde pode-se citar [OPP 75], [RAB 75], [OPP 78], [EDE 89] e outros.

As aplicações em DSP compreendem a realização de filtros digitais, sistemas de controle lineares e não lineares, sistemas de comunicação, radares convencionais e de abertura sintética e processamento de imagens entre outras. Uma visão deste campo é dada em [OPP 78] e [SAL 77]. As aplicações em filtragem digital vêm de longo tempo e hoje utilizam tanto técnicas puramente digitais como capacitores chaveados e SAW (Surface Acoustic Waves) para sua implementação. Referências são encontradas em [JAC 68], [HAM 77], [PEL 76] e [GRE 87].

Uma das áreas que tem merecido atenção dos pesquisadores é a classe de processamento digital de imagens, que objetiva desde a melhoria da qualidade de imagem para visualização até a implementação de máquinas de visão artificial, capazes de reconhecer e manipular objetos. Aplicações em robótica, transmissão de imagens e biomédica são frequentemente objeto de publicação.

#### 1.1 Conceitos Básicos

A expressão "imagem monocromática", ou simplesmente "imagem", refere-se à função de intensidade bidimensional f(x,y), onde x e

y são as coordenadas espaciais e o valor da função é proporcional ao brilho (ou tom de cinza) da imagem neste ponto. "Imagem digital" é uma função imagem que foi discretizada nas duas coordenadas espaciais e no brilho. Pode-se considerar uma imagem digital como uma matriz na qual os índices de linha e coluna identificam espacialmente um ponto da imagem na matriz e o valor deste corresponde ao brilho. Os componentes desta matriz são chamados de elementos de imagem ou pixels ( picture elements ). A dimensão da imagem está relacionada com a aplicação a que se destina e é limitada pela resolução do sensor.

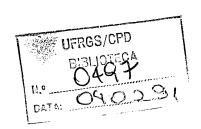

Os componentes de um sistema simples de processamento de Imagens pode ser visto na figura 1.1.

Figura 1.1 Elementos de um Sistemas de Processamento Digital de Imagens

A partir da figura identifica-se que um processador de imagens é formado por um conjunto de módulos que realizam quatro funções básicas: Aquisição, Armazenamento, Processamento básico do sinal e exibição [GON 87].

Tipicamente um módulo de aquisição possui um sensor e um digitalizador, que converte o sinal gerado em uma representação digital. Quando este módulo é capaz de digitalizar uma imagem de TV no tempo de um quadro, recebe o nome de "Frame Grabber". Digitalizador é o dispositivo que converte uma imagem na sua representação numérica, manipulável pelos computadores digitais. Embora a bibliografia cite vários tipos de

tipos de sensores como "flying spot scanners", "image dissectors", "microdensitometers" entre outros [PRA 78], [GON 87], [EKS 84], este trabalho considera apenas os sensores do tipo câmera de TV. Esta opção deve-se à facilidade de obtenção deste sensor, capacidade de exibição imediata da imagem captada em um monitor de vídeo bem como a aquisição de imagens móveis.

O módulo de armazenamento, chamado também de "Frame Buffer", é uma memória capaz de armazenar uma imagem completa. Uma variação na forma de endereçamento desta memória permite realizar zoom (aproximação) instantâneo na imagem, bem como "scroll" (deslocamento vertical) e "pan" (deslocamento horizontal), da mesma forma como é feito nos atuais controladores de vídeo com capacidade gráfica.

O módulo de processamento realiza operações aritméticas e lógicas. Estes processadores variam desde microcomputadores [MAT 87] até componentes especializados, ASICs, que realizam a computação dos dados [RUE 87], [RUE 89]. Este tipo de processador especializado é projetado especialmente para ser rápido e, muitas vezes, realiza o processamento dos pixels em paralelo.

A função do módulo de exibição é realizar a conversão da imagem de sua forma numérica em um sinal de vídeo analógico e exibí-lo em um monitor de TV ou outro dispositivo que traduza a informação em uma forma perceptível ao olho humano. Neste texto serão considerados apenas os vídeos, em especial os CRTs (*Cathode Rays Tubes*) que são os mais comuns e permitem a visualização de imagens móveis. Sistemas em hardware podem ser colocados a fim de realizar transformações na escala de tons, inserção de gráficos e planos alfanuméricos e tratamento de pseudo-cores.

Os demais elementos que aparecem na figura 1.1 são um computador e um dispositivo de memória de grande capacidade. O computador pode ser utilizado para controle ou processamento de mais alto nível e sua memória de massa para armazenamento das imagens ou dos resultados do processamento realizado.

## 1.2 Escopo e Organização do Texto

O presente trabalho descreve a concepção e implementação de um processador integrado e especializado, que realiza o processo de convolução bidimensional. Este componente foi projetado para ser utilizado em tarefas de processamento de imagens monocromáticas em tempo real, onde tempo real significa que o cálculo dos resultados é realizado na mesma taxa da geração das imagens do sensor. Este componente implementa uma das funções do processador de imagens da figura 1.1, e pode ser utilizado em sistemas de identificação e visualização. Com este processador de convolução é possível implementar filtros de eliminação de ruído, reforço de contorno, cálculo de gradientes e outras operações comuns em processamento de imagens.

O processo de concepção de um sistema compreende as seguintes fases:

- \* Compreensão e limitação da função a ser realizada pelo sistema; (Especificação)

- \* Detalhamento do sistema determinando os pontos críticos, em velocidade e complexidade; (Refinamento)

- \* Avaliação das diversas formas de realização e a viabilidade da aplicação a que se destina;

- \* Projeto e implementação utilizando ferramentas de CAD que viabilizem a avaliação e realização das etapas acima.

- \* Fabricação e teste do sistema.

Os capítulos a seguir abordam cada um destes tópicos, com maior enfase na implementação do circuito.

No capítulo 2, SINAL de VÍDEO, é feita a caracterização do sinal a ser processado e introduz parâmetros básicos de vídeo digital: bits/pixel e pixels/linha. São citadas algumas degradações provenientes dos sensores e do processo de discretização. Finalmente são descritos alguns parâmetros qualitativos dos sistemas de exibição baseados em CRTs.

O tópico de PROCESSAMENTO de IMAGENS, capítulo 3, apresenta uma classificação dos algoritmos utilizados em IP (*Image Processing* ). Faz-se a apresentação do algorítmo de convolução bidimensional, extensamente utilizado em processamento de imagens,e discute-se as condições de contorno da equação. Neste mesmo capítulo são caracterizados os componentes básicos e o modelo de sistema de processamento de imagens a ser utilizado.

O capitulo 4, ARQUITETURAS DE CONVOLUÇÃO, dedica-se a discutir os conceitos arquiteturais utilizados para definição da arquitetura alvo utilizada.

No capítulo 5, CV2D, é apresentada a arquitetura implementada e a descrição dos blocos funcionais que compõem o circuito.

No título IMPLEMENTAÇÃO, capítulo 6, descreve-se brevemente as ferramentas de CAD utilizadas para o projeto do CV2D e o resultado da aplicação destas na concepção do circuito.

Finalmente no capítulo 7 são apresentados os resultados e CONCLUSÕES. São dadas também sugestões de melhorias para o circuito, avaliação da testabilidade e um sumário das características do circuito.

UFROS/CPD DIBLICITEGA

# 2 SINAL DE VÍDEO

Este capítulo apresenta o modelo de imagem que será utilizado ao longo do texto. É caracterizado o sinal a ser processado, sua geração, limitações e eventuais degradações. São abordados os aspectos de digitalização do sinal de vídeo, concluindo com a escolha do número de pixels/linha e do número de bits/pixel utilizados no sistema. É discutida também a representação de imagens monocromáticas a partir de sinais de cor. Tal relação pode ser utilizada no tratamento de pseudo-cores [HAL 79]. Ainda neste capítulo são tecidas considerações sobre a exibição de imagens em CRTs a fim de completar a cadeia do sinal: Formação e Geração, Aquisição, Tratamento e Exibição.

## 2.1 Modelo de Imagem

O termo imagem refere-se à função bidimensional de intensidade luminosa, descrita por **f(x,y)**, onde o valor de f nas coordenadas **(x,y)** fornece a intensidade ou brilho deste ponto de imagem. As imagens que percebemos consistem da luz refletida dos objetos de uma cena e cada um dos pontos da imagem contém a contribuição de luminosidade de todos os outros pontos vizinhos. Sendo a luz uma forma de energia, os valores de f estão nos limites:

$$0 < f_{xy} < \infty$$

A função f(x,y) pode ser caracterizada por duas componentes [PRA 78], [OPP 78], [GON 87]. A primeira é a quantidade de luz incidente sobre a cena observada e a segunda traduz a quantidade de luz refletida pelos elementos da cena. Estas componentes são chamadas de iluminação e refletância, representadas pelas funções i(x,y) e r(x,y) respectivamente. O produto destas funções define a imagem f(x,y).

$$f_{xy} = r_{xy} * i_{xy}$$

Neste contexto a refletância é uma característica dos objetos da cena e tem seus limites entre a absorção total (zero) e a reflexão total (um) da luz incidente. A intensidade de uma imagem monocromática, chamada de tons ou níveis de cinza, normalmente é colocada no intervalo [O,L]. Estes limites representam o preto (O) e o brilho máximo possível para um elemento de imagem (L).

As imagens reais possuem propriedades de vizinhança, significando que um ponto (x,y) no plano de imagem [OPP 78] não corresponde apenas ao ponto (x',y') no plano do objeto, mas também é função da energia radiante dos infinitos vizinhos deste ponto. A imagem g(x,y) corresponde à distribuição de energia de um objeto e o somatório das contribuições infinitesimais de seus vizinhos. Assumindo linearidade nos processos pelos quais a energia radiante se acumula no plano de imagem, a formação de um quadro pode ser descrita, após alguma manipulação algébrica, pela equação abaixo. Esta representa um sistema linear de duas dimensões e invariante no deslocamento.

$$g_{xy} = \int_{-\infty}^{+\infty} \int_{-\infty}^{+\infty} h_{x-x_1, y-y_1} f_{x_1 y_1} \partial x_1 \partial x_1$$

É claro que a influência de um determinado ponto diminui nos pontos mais afastados deste. Isto permite restringir a influência de um determinado elemento em seus vizinhos sem perda significativa de informação para um posterior processamento.

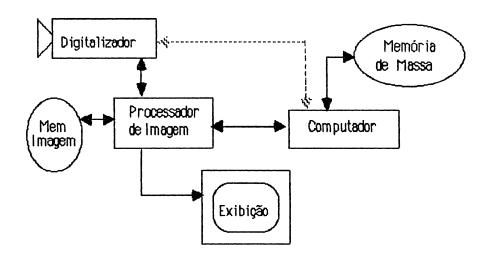

Os processos de formação da imagem e seu sensoriamento podem ser idealizados no blocodiagrama da figura 2.1. Neste modelo foi incluida uma fonte de ruído aditivo e uma função de tranferência que modela outras degradações possíveis no sinal de vídeo gerado.

Figura 2.1 Modelo de Formação da Imagem

## 2.2 Caracterização do Sinal de Vídeo

Para uma boa compreensão dos métodos utilizados em processamento digital de imagens e suas limitações é necessário conhecer o sinal a ser processado. A seguir são dadas as principais características do sinal fornecido pelas cāmeras de video.

#### 2.2.1 Características

O objetivo de uma câmera de vídeo é converter uma cena que está em frente ao sensor em um sinal elétrico. Este sinal possui apenas um valor a cada instante de tempo, ou seja, uma função de uma variável ou um sinal unidimensional. No entanto a imagem é uma função de duas dimensões, como descrito anteriormente, que ao mesmo tempo possui valores diferentes para cada posição do quadro.

Um método de converter a imagem de duas dimensões em um sinal elétrico é chamado de varredura ou *scanning*. O processo de varredura consiste em um ponto sensor que desloca-se rapidamente sobre a imagem, com velocidade suficiente para realizar a captura completa da imagem antes desta modificar-se muito. Durante o movimento do ponto sensor, a saída elétrica varia em resposta ao brilho ou a cor da imagem sob o ponto de sensoriamento. O sinal elétrico proveniente deste sensor apresenta a imagem como uma série de valores separados no tempo. Este sinal será chamado de sinal de vídeo.

Normalmente a cena é explorada pela combinação de dois movimentos ortogonais do ponto sensor. Assim a varredura inicia no canto superior esquerdo e prossegue horizontalmente através da imagem, formando a chamada linha de varredura. Ao mesmo tempo o ponto sensor é movido verticalmente para baixo a uma velocidade muito menor do que o seu movimento horizontal. Quando o lado direito da imagem é atingido, o ponto de varredura retorna ao lado esquerdo. Devido a este movimento vertical o ponto estará, após retornar ao lado esquerdo, um pouco abaixo do lugar de partida da primeira linha. O processo de varredura prossegue através da próxima linha e sucessivamente até ser percorrida a última linha. Durante a linha percorrida, a saída do sensor representa a intensidade luminosa de cada ponto. No período de retorno do ponto ( conhecido como tempo de apagamento ou retraço ) o valor é colocado em zero (ou nível de apagamento). Este apagamento vertical e horizontal é originalmente dedicado a fornecer o tempo necessário para o retraço do feixe das câmeras e CRTs, porém, devido ao fato de não conterem informações de imagem, aproveita-se este tempo, no caso de transmissão de TV, para enviar outras informações, como videotexto, dados e sinais de correção. O sinal de uma varredura completa é uma sequência de linhas separadas por intervalos de apagamento. Este conjunto de linhas de varredura é chamado quadro ou *frame* . Um importante parâmetro na varredura é a relação de aspecto. Esta é a razão do comprimento de uma linha de varredura horizontal pela distância coberta verticalmente no quadro. A relação de aspecto pode ser vista como a relação largura vs altura de um frame. Em televisão a relação de aspecto padrão é 4:3 e em outros sistemas, como em cinema, pode-se chegar a razões de 1:1 e, modernamente, até 2:1.

Se o sinal obtido for utilizado para modular a intensidade de um feixe de elétrons em um CRT, com o mesmo padrão de varredura do sensor, a imagem original será reproduzida. Desta forma o sinal elétrico enviado ao monitor deve conter alguma informação adicional para garantir que a varredura do monitor mantenha sincronismo com o sensor. Esta informação é chamada de pulsos de sincronismo (SYNC), incluida dentro do próprio sinal de vídeo durante o tempo de apagamento ou enviada separadamente.

Resolução é a medida da fidelidade de reprodução dos detalhes de um quadro real através do sinal de vídeo gerado. A capacidade de variação do sinal está vinculada a dois fatores:

- Intensidade luminosa necessária para sensibilizar o dispositivo e

- área sensível do ponto explorador.

A diferenca entre o valor máximo e mínimo de luminosidade capaz de estimular o sensor é chamada de faixa dinâmica. O tamanho do ponto sensor determina a resolução horizontal, onde um ponto menor dará uma major resolução na imagem capturada, que reflete-se na capacidade de reproduzir detalhes finos. Uma das formas de testar a resolução horizontal de uma sistema é colocar linhas verticais pouco espaçadas em frente a câmera. Se a área do ponto sensor for menor que o espaço entre as linhas, estas serão reproduzidas, caso contrário a saída produzida será um sinal correspondente a intensidade média entre o brilho das linhas e do intervalo entre as mesmas. Em sistemas de televisão [GRO 79] a resolução é medida pela contagem de linhas verticais pretas e brancas consecutivas capazes de serem reproduzidas. Resolução de 400 a 500 linhas são valores comuns em câmeras industriais vidicon, chegando a valores bem maiores em equipamentos especializados. Em dispositivos que utilizam um arranjo de pontos sensores, chamados matriciais, a resolução horizontal depende do tamanho do ponto e do número de sensores em cada linha da matriz.

É importante notar que nas transições abruptas de luminosidadde o sensor sempre produz sinais elétricos de alta frequência, sendo importante que os circuitos utilizados para processamento e transmissão destes sinais possuam a largura de banda adequada para suportar tais frequências. Em [LUT 89] encontramos, por exemplo, que para transmissão de televisão é necessária uma banda de 1Mhz para cada 80 linhas de resolução horizontal. Este parâmetro é importante na utilização de um sensor que possua no mínimo uma capacidade de resolução e largura de banda igual à desejada na computação digital, evitando processos de estimação de pixels em tempo de amostragem.

A resolução vertical depende do número de linhas de varredura utilizadas em um quadro, ou do número de pontos verticais no caso de um sensor matricial. Quanto maior o número de linhas, maior a resolução vertical. Por exemplo os sistemas de TV utilizam valores de 525 linhas (americano e japonês) e 625 linhas (europeu). Destas um pequeno número (em torno de 40 linhas) são utilizadas para apagamento vertical. Novos sistemas de TV de alta resolução amplia estes valores para 1000 a 1200 linhas, com relação de aspecto de 5:3 ou mesmo 16:9 [LEW 88]

A taxa de quadros exibidas no tempo deve ser suficiente para produzir um efeito de continuidade em imagens móveis. Em sistemas de transmissão padrão, taxas de 25 ou 30 quadros/s são utilizadas. Estes números,embora suficientes para representar imagens móveis, não são altos o suficiente para evitar flicker (efeito de piscamento da imagem). Desta forma procura-se atender taxas superiores a 50 quadros/s, que, apesar de reduzir o flicker apresenta resultados satisfatórios. Com esta taxa de atualização, preservando a mesma resolução horizontal é necessário um aumento nas frequências de varredura horizontal e vertical, que provoca um significativo aumento na largura de banda necessária para o sistema. A teledifusão comercial evita este problema através do uso de técnicas de entrelaçamento.

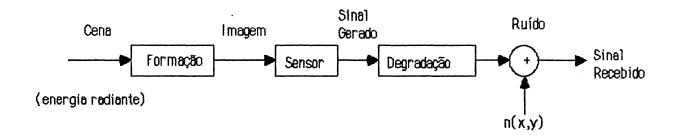

Entrelaçamento, em televisão, significa que mais do que uma varredura vertical produz um quadro. Sistemas de televisão usam entrelaçamento 2:1. Assim uma varredura vertical exibe as linhas impares e outra exibe as linhas pares, chamados campos pares e impares do quadro exibido. Com uma taxa de 30 campos por segundo a taxa de varredura vertical equivale a 60 quadros/s. Baseado no fato que o olho humano não percebe piscamento em pequenos objetos nesta frequência, a taxa de 30 campos/s é suficiente e a imagem total é aparentemente regenerada a uma

taxa de 60 quadros/s (*frames/s*). Desta forma, cada campo par inicia imediatamente após um retraço vertical e os campos impares 1/2 linha após. Durante o tempo de apagamento vertical existem os sinais de sincronização horizontal e pulsos de equalização que mantém a relação de frequências do dispositivo de exibição e o entrelaçamento correto. A figura 2.2 mostra o formato completo do sinal, indicando o início dos campos pares e impares e os pulsos de equalização.

Figura 2.2 Sinais de Sincronismo

Nos sensores do tipo câmera, a imagem é oticamente focalizada em uma superfície bidimensional. Esta superfície fotosensível recolhe a luz proveniente de todos os pontos da imagem, de maneira contínua, gerando uma carga elétrica correspondente a cada ponto da imagem focalizada nesta superfície. Esta carga é convertida em um valor de tensão que compõe o sinal de video.

Existem duas grandes classes destes dispositivos, que diferem na forma de armazenamento e tranferência de carga. Tubos a vácuo (vidicon, staticom, plumbicom) [GRO 79] coletam a carga em uma superfície especial depositada no fundo do tubo. Um feixe de elétrons faz a varredura e gera o sinal de vídeo correspondente a carga armazenada. O segundo tipo de dispositivo é o de estado sólido, onde a carga é gerada em uma área de silício que é superposta a uma matriz de componentes que transferem ordenadamente esta, cadenciada pelos sinais de sincronismo. Estes dispositivos são conhecidos como CCD (Charged Coupled Devices).

Com o mesmo princípio alguns sensores utilizam as propriedades de armazenamento de carga utilizadas nas RAMs dinâmicas ('Optics DRAMs") [AWC 87a], [AWC 87b], [AWC 87c].

#### 2.2.2 Fundamentos de Cor

Devido à estrutura do olho humano, todas as cores podem ser vistas como uma combinação variável das três chamadas cores primárias: Vermelho (R), Verde (G) e Azul (B). Estas cores primárias podem ser somadas para produzir as secundárias: Magenta (R+B), Cian (G+B) e Amarelo (R+G). Misturando as três primárias ou cada uma das secundárias com a cor primária oposta, na intensidade correta, a luz branca é produzida.

Existe diferença entre cores primárias de luz e cores primárias de pigmentos ou corantes. Nos corantes, a cor primária é definida como absorção de uma das cores primárias e reflexão das outras duas [GON 87], [GRO 79]. O sistema de cores em televisão é um exemplo de coloração de natureza aditiva e portanto composta com as cores primárias RGB. As características utilizadas para distinguir uma cor de outra são o BRILHO, MATIZ e SATURAÇÃO.

Brilho refere-se à intensidade e o Matiz é um atributo associado ao comprimento de onda dominante nas ondas luminosas ( a percepção de uma cor não se restringe a um comprimento de onda fixo e sim a uma faixa do espectro visível). Assim o matiz representa a cor dominante recebida pelo observador. Quando se chama um objeto de azul, laranja ou amarelo, está sendo estabelecido seu matiz. A saturação refere-se a pureza relativa, ou quantidade de luz branca misturada ao matiz. O espectro puro é definido como completamente saturado e o grau de saturação é inversamente proporcional à quantidade de luz branca adicionada. O conjunto de matiz e saturação é chamada de cromaticidade e, portanto, uma cor pode ser caracterizada pelo seu brilho e cromaticidade. A quantidade de R, G, B necessária para formar uma determinada cor é chamada de valores "tristimulus" e denotados por X,Y e Z respectivamente. Uma cor é então especificada por seus coeficientes tricromáticos, definidos como:

$$x = \frac{x}{x+y+z} \quad y = \frac{y}{x+y+z}$$

$$z = \frac{z}{x+y+z} \quad x+y+z=1$$

Na criação da tecnologia de vídeo colorido, procurou-se manter compatibilidade com os receptores de TV monocromáticos e a mesma largura de banda para transmissão. Para atender tal requisito, o sinal de vídeo colorido é codificado em dois sinais distintos [GRO 79], [EDE 89]:

- a) O sinal Y, luminância, que contém o sincronismo e a informação de brilho, compatível com os sistemas preto e branco.

- b) O sinal de croma C, que carrega a informação de cor (matiz e saturação).

Para não haver redundância, a croma é composta apenas pelos sinais "diferença de cor" (R-Y) e (B-Y), modulados em fase e amplitude sobre uma subportadora de 3.58Mhz. Fica função do sistema de exibição ou recepção recuperar o sinal G (cor verde). De acordo com a sensação de brilho de cada cor ao olho humano, foi estabelecida a relação algébrica entre o sinal Y e os sinais de cor:

$$y = 0.3R + 0.59G + 0.11B$$

#### 2.2.3 Padrões

Vários comitês desenvolveram padrões para câmeras de vídeo. Estes, primeiramente desenvolvidos para aplicações em televisão, incluem o RS170, CCIR625 e RS343. Estes padrões satisfazem uma tecnologia

antiga, baseada em sinais monocromáticos. Assim, relacionado a esta origem, estes possuem algumas limitações, como:

- . Largura de banda apropriada para difusão, o que limita a resolução;

- . O formato entrelaçado representa um obstáculo para aquisição de imagens em alta velocidade;

- Não existe "reset" vertical assíncrono. Desta forma uma imagem não pode ser gatilhada por eventos externos.

Para sistemas que necessitam alto desempenho não existem padrões definidos. Existem sistemas de aquisição de imagens que atendem os requisitos de alta definição e interface digital não enterlaçada.

Os padrões são conceitualmente semelhantes entre si na sua implementação, produzindo imagens enterlaçadas em 2:1 com resolução variada. Será apresentada a seguir uma visão superficial dos padrões mais utilizados. Mesmo as câmeras CCD de alta resolução fornecem sinais compatíveis aos formatos descritos, variando apenas as frequências, para permitir o não entrelaçamento.

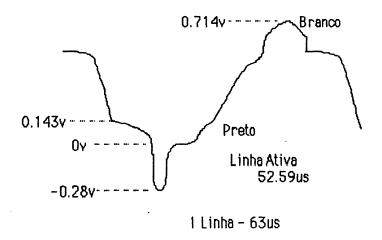

O R5170 define a temporização e a específicação de voltagem para sinais de vídeo preto e branco. Posterioremente a codificação de sinais de diferença de cor com luminância e sinais de sincronismo conduziu a um padrão de televisão colorida, o NTSC ("National Television Standards Commites"). O quadro R5170 é composto de 525 linhas de varredura horizontal, separadas em dois campos, par e ímpar. Durante o campo par, 262.5 linhas são fornecidas em 1/60s. As 262.5 linhas ímpares são fornecidas nos próximos 16.7ms. A cada 33.3ms, ou 1/30s, um quadro completo é atualizado. Como um tempo de 9 linhas é necessário para o intervalo de sincronismo vertical e 11 linhas são utilizadas no apagamento, a janela de vídeo fica reduzida a 242.5 linhas ativas em cada campo. Logo a resolução vertical efetiva é de apenas 485 linhas. A figura 2.3 llustra o formato típico R5170 para um determinado campo.

262.5 linhas

9 linhas de sincronismo vertical

11 linhas de apagamento

total: 242.5 linhas ativas/campo

resolução vertical efetiva: 485 linhas/quadro

Figura 2.3 Formato RS170

A resolução horizontal efetiva é limitada pela largura de banda do amplificador de vídeo da câmera. Muitas câmeras RS170 possuem resolução de 300a 400 pixels/linha com sinais de temporização horizontal e vertical inseridos nos dados analógicos de vídeo. Conforme a figura, o envelope de vídeo possui limites de -0.28V a 0.714V, ou seja, em torno de 1Vpp. Os dados de vídeo iniciam em um pedestal de 0.143V, que corresponde ao valor de um ponto preto na imagem e um ponto completamente branco possui um valor de 0.714V. Os sinais no intervalo entre 0.143 e 0.0V são utilizados para indicar apagamento horizontal e vertical. Os sinais negativos correspondem aos pulsos de sincronização.

O CCIR625, 625 linhas, é similar ao padrão RS170, porém com diferenças na taxa de quadro e largura de banda de vídeo. Por possuir mais linhas ativas, uma resolução maior é alcançada. Em sistemas de imagens isto significa que um quadro de 512x512 pode ser capturado, uma vez que

possui 575 linhas ativas, em oposição as 480 linhas do RS170. No entanto a frequência de quadro é de 50 Hz, o que pode fazer diferença na captura de imagens rápidas. Além disso a natureza dos quadros pode causar um batimento de frequências espaciais, introduzido quando os objetos em foco estão sob iluminação fluorescente alimentadas pela rede de 60 Hz. Em conjunto com o desenvolvimento deste padrão foi criado um sistema de codificação de cor: o sistema de alternância da fase da linha (Phase Alternation Line system PAL). Neste, a cor é codificada pela fase do sinal de 3.58MHz em relação a uma referência. A fase de uma das componentes de cor é alternada linha a linha, tornando média qualquer distorção de cor. Este tipo de codificação reduz os erros de fase ao longo do processo de transmissão, dispensando o ajuste de cor existente nos receptores NTSC.

Em busca de um padrão com melhor resolução que o RS170, mantendo o fator de entrelaçamento 2:1, a EIA desenvolveu o RS343. Devido a melhor resolução e uma taxa de quadro mais alta, os sistemas que empregam RS343 utilizam principalmente câmeras VIDICON. Para este padrão existem diferentes versões, de 675 a 1023 linhas/frame e com um número de linhas ativas entre 624 e 943 respectivamente, todos com entrelaçamento 2:1. O padrão RS343 mais popular é o de 875 linhas. Não existe padronização de cor desenvolvido para este sistema.

Câmeras com sensor CCD fazem parte de um conjunto de interfaces não padronizadas. Estas podem conter até 1320x1035 pontos sensíveis a luz, cada um com uma área de 6.8 µm² e espaçamento de 6.8 µ de centro a centro. Como 100% da área do sensor é sensível à luz, os efeitos de aliasing podem ser reduzidos. Uma das características deste tipo de sensor é a de possuir um conversor A/D no mesmo sistema. O conversor, geralmente de 8 bits, produz um sinal digital, neste caso em 256 tons, eliminando degradações de amplificadores, condicionadores de sinais e cabos de transmissão.

Outros sensores do tipo câmeras com interface não padronizada podem ser encontrados em [AMO 88] que sumariza alguns tipos de câmeras e suas principais características.

## 2.2.4 Degradações

Em todo sistema, alguns efeitos indesejáveis podem ocorrer por diversos motivos. Algumas destas degradações são comentadas a seguir.

A forma mais comum de ruído em sistemas de varredura é conhecido como *snow* . A presença destas manchas é devido à excessiva quantidade de ruído branco (uniformemente distruibuído na banda passante) sobre o sinal. Este pode ser modelado como ruído aditivo, sendo o sinal (v) representado como v= v'+ r, onde o ruído (r) e o sinal imagem (v') não são correlatos. Este tipo de ruído é observado quando a relação sinal/ruído cai abaixo dos 40 dB. Esta degradação pode ser introduzida nos vários caminhos de transmissão, seja em cabos ou nos sistemas de teledifusão (broadcast ). Outros tipos de ruído manifestam-se diferentemente. Em alguns casos o nível de ruído depende da intensidade do sinal de imagem. Se o ruído for, por exemplo, proporcional ao sinal de vídeo, isto é, v = v'+rv', temos v= v'(1+r) ≈ v'r, que representa um ruído não correlato porém multiplicativo. Outros exemplos são os ruídos de baixa frequência que aparecem como linhas horizontais no quadro. No caso de sinal de vídeo com informação de cor, devido à estreita faixa do canal de crominância e a superposição no final da faixa de luminância, os efeitos de *cross-colour*e cross-luminanc&requentemente aparecem.

Imagens geradas por fonte de luz coerente, como imagens de radar infravermelho [EKS 84] podem apresentar ruídos que se manifestam como manchas, chamadas de efeito *speckly*. Imagens transmitidas em um canal ruídoso ou sob interferência de ruído elétrico podem apresentar pontos pretos e brancos espalhados na imagem. Este tipo de efeito é conhecido como *salt-and-pepper*. O ruído tipo "chuvisco", também visualizado como pontos pretos e brancos ao longo da imagem, é resultado de transições de alta frequência com tempo de duração considerável e característica de distribuição aleatória.

Para os ruídos de alta frequência, um filtro passa baixas pode ser colocado, desde que não ocorra perda significativa de resolução. Em [ODG 81] encontramos que para uma imagem de 512 x 512, uma largura de

banda de 7Mhz para o sistema de exibição e suficiente para que não haja degradações pela perda de altas frequências.

As distorções devido à perda de alta frequência, afetam a percepção das transições. Este tipo de degradação pode ser introduzido devido a perda de foco nas lentes, movimento ou turbulência atmosférica, ou pela limitação da banda de passagem do sinal. Este tipo de degradação é chamada de *blurring* ou ainda de ruido de convolução. A perda na amplitude e, no caso de sinais coloridos, o deslocamento de fase nas frequências próximas a frequência horizontal faz com que o quadro fique borrado, normalmente à direita. Uma série de outros efeitos eletrônicos, de natureza unidimensional, podem ocorrer bem como degradações devido a deficiências geométricas e de iluminação. Alguns destes tópicos são analisados em [ODG 81], abrangendo *shading*, fator gamma, aberrações óticas nas lentes e a variação inerente aos componentes analógicos utilizados no equipamento sensor.

Quando quadros sucessivos possuem variações abruptas de iluminação, a visualização pode ser prejudicada. Uma técnica utilizada em receptores de TV, a fim de minimizar este efeito, é realizar uma variação lenta na amplitude do sinal de vídeo, de acordo com a intensidade dos quadros anteriores, uma espécie de integral da luminosidade em um período de tempo.

Vários tipos de interferência, chamadas de interferência coerente, podem surgir dentro do sinal de vídeo proveniente de outras fontes. Um exemplo é a interferência de RF (radio frequência), que depende da relação de frequências entre o sinal interferente, a subportadora de cor e as frequências de varredura. Outros exemplos são encontrados em [LUT 89], como as barras horizontais que variam em posição e tamanho de acordo com o som, relacionadas ao sinal de áudio, ou a ondulação de 120Hz proveniente da tensão de alimentação. A interferência de fontes coerentes é muito mais visível que a interferência aleatória ou ruído, pois cria algum tipo de padrão que é repetido na mesma posição ou com lento deslocamento.

Alguns tipos de degradação podem ser modelados matematicamente, o que permite aplicar transformações na imagem que compensem ou atenuem os efeitos de acordo com o modelo utilizado. Este

tipo de enfoque é utilizado em algumas técnicas de enriquecimento de imagens e é a base de toda a área de restauração de imagens [EKS 84], [AND 77]. A seguir são dados dois exemplos simples de modelos. O primeiro modela o borramento ou *blurring* e é utilizado nos processos de reforço de contorno ou *sharpening*. O exemplo subsequente introduz um modelo de ruido aditivo e algumas considerações do processo de *smoothing*.

O borramento, ou *bluring*, traduz-se em perda de definição, ou seja, redução da capacidade de delimitar o contorno entre várias regiões da imagem. Este é, em sua essência, uma média ou uma integração, onde as altas frequências são atenuadas. É intuitivo que o efeito possa ser corrigido com operadores diferenciais. Se uma imagem possui ruído e é borrada, as técnicas de sharpening devem considerar que o ruído geralmente contém consideráveis componentes de alta frequência espacial. Logo as técnicas devem ser restritas a imagens onde a relação sinal ruído é grande ou onde a redução de ruído já foi realizada, caso contrário os efeitos de ruido de alta frequência serão enfatizados. No sentido de salientar as características de borramento com orientação espacial arbitrária, um operador espacial isotrópico, isto é invariante na rotação, se faz necessário. Esta limitação é usada para derivar algumas propriedades que tais operadores devem possuir. Um dos operadores diferenciais isotrópicos mais utilizados é alguma forma de Laplaciano. O Laplaciano de uma imagem f pode ser representado como:

$$\nabla^2 f = \frac{\partial^2 f}{\partial x^2} + \frac{\partial^2 f}{\partial y^2}$$

Assumindo que o *blurring* é consequência de um processo modelado fundamentalmente como uma difusão, temos:

$$\frac{\partial g}{\partial t} = k \nabla^2 g$$

onde g é uma função de (x,y,t) e k>0.

Em t=0, g(x,y,0) é a imagem sem degradação f(x,y).

Em t>0 pode-se representar a imagem borrada g(x,y,t) como uma série de Taylor,

$$g_{x,y,t} = g_{x,y,0} + t \frac{\partial g_{x,y,t}}{\partial t} + \frac{t^2}{2} \frac{\partial^2 g_{x,y,t}}{\partial t^2} + \dots$$

Se considerarmos apenas os termos lineares, temos:

$$g_{x,y,0} \to f$$

$$\frac{\partial g}{\partial t} \to k \nabla^2 g$$

$$f = g - kt \nabla^2 g$$

Assim temos um mecanismo de primeira ordem para restaurar a imagem. É claro que o processo de difusão não é o fundamento de todos os fenômenos de *blurring*, porém existem métodos baseados no Laplaciano, expresso de forma discreta. Este mesmo operador diferencial pode ser encarado como um filtro de altas frequências espaciais e calculado através de um operador de convolução.

O *smoothing* está esssencialmente ligado à remoção de ruído. Muitos métodos baseados em processos lineares para *smoothing* resultam em um grau inaceitável de borramento da imagem. Minimizar as condições de borramento implica em realizar otimizações globais para alguma "função custo" definida adequadamente. Na prática as operações locais são utilizadas, explorando o grau de liberdade oferecido nos problemas reais [OFF 85].

Uma imagem pode ser afetada, como citado anteriormente, por ruído de diferentes fontes, incluindo o ruído do sensor, ruído de quantização e ruído de canal. Este ruído pode ser ainda sistemático ou aleatório, sendo o primeiro facilmente tratável com técnicas de Fourier. O ruído em uma imagem possui, usualmente, componentes de alta frequência espacial em relação a imagem considerada. Assim um filtro espacial passa-baixa pode ser efetivo, embora não haja distinção entre imagem e ruído. Para obter-se uma maior eficiência, requer-se um conhecimento específico do modelo do ruído a ser tratado.

É fácil ver porque técnicas que utilizam cálculo de média reduzem ruído. Se **s(1)** representa um pixel livre de ruído e **n(1)** é o ruído correspondente, o cálculo da média fica:

$$\frac{S_1+\ldots+S_j+\ldots+S_N}{N}+\frac{P_1+\ldots+P_j+\ldots+P_N}{N}$$

O segundo termo da soma é uma variável aleatória com média zero e desvio padrão s/√(N), onde n é o ruído RMS para um único pixel. Desta forma, tomando-se a média sobre um número de cópias independentes de uma dada imagem, a redução do ruído sem blurring é obtida (filtragem temporal). Se uma única imagem é disponível, então o ruído pode ser reduzido por uma média local, mas apenas se o ruído da imagem possui granularidade mais fina que os detalhes da mesma.

Os limites espaciais do processo de média local dependem da quantidade de redução de ruído desejada. Por exemplo, no caso anterior, a redução de um fator  ${\bf N}$  envolve uma média sobre  ${\bf N}^2$  pixels. Uma extensão das mesmas idéias , leva a média ponderada, com pesos que minimizem a média sobre detalhes de linhas e transições. Para isto deve-se usar um meio de localizar tais detalhes, implicita ou explicitamente.

# 2.3 Vídeo Digital

A fim de realizar o tratamento digital de imagens é necessário representá-la através de um padrão de bits. Na transformação de um sinal de vídeo analógico para sua forma digital, vários aspectos devem ser observados nos processos de quantização e amostragem, bem como os efeitos destes parâmetros sobre as imagens.

### 2.3.1 Amostragem e Quantização

O processo de converter sinais contínuos no tempo em um conjunto de valores discretos no tempo, é chamado de amostragem e a etapa de transformar a amplitude dos sinais em valores discretos é dita quantização. No caso de imagens, a função imagem f(x,y) deve ser digitalizada nas coordenadas espaciais (x,y), chamada amostragem do sinal, e a intensidade (valor da função) deve ser convertida em vários tons de cinza, chamada de quantização.

Os processos de amostragem são inúmeros, sendo o mais simples a chamada amostragem uniforme [GON 87] onde uma imagem f(x,y) contínua é convertida em amostras igualmente espaçadas na forma de uma matriz MxN. Nesta matriz cada elemento é um valor discreto que corresponde a intensidade luminosa do ponto. Nestes casos uma prática comum é que os valores de M e N sejam potências de 2 e muitas vezes fazse M=N. A amostragem não uniforme pode melhorar a aparência da imagem, através de um processo adaptativo que depende das características da mesma. Em geral uma amostragem com menor granularidade é utilizada na vizinhança de uma transição e amostras mais espaçadas em regiões de luminosidade constante da imagem. Uma discussão ampla sobre os processos de amostragem uniforme e não uniforme utilizando matriz de pontos ou baseados em representação da imagem pelos coeficientes de uma função ortonormal pode ser encontrada em [PRA 78], [ROS 82], [HAL 79] e [MAS 84].

A aplicação do teorema da amostragem no caso bidimensional resulta que, uma função bidimensional f(x,y) pode ser teoricamente reconstruida se o intervalo da amostragem seguir as equações abaixo:

$$\Delta X \le \frac{1}{2W_0} \qquad \Delta Y \le \frac{1}{2W_v}$$

onde  $2W_{\mathbf{U}}$  e  $2W_{\mathbf{V}}$  representa a largura da função na direções  $\mathbf{u}$  e  $\mathbf{v}$  no domínio frequência. Porém quando a  $\mathbf{f}(\mathbf{x},\mathbf{y})$  é espacialmente limitada por uma janela  $\mathbf{h}(\mathbf{x},\mathbf{y})$ , a transformada da função amostrada é distorcida pela convolução da  $\mathbf{H}(\mathbf{u},\mathbf{v})$  com  $\mathbf{S}(\mathbf{u},\mathbf{v}) * \mathbf{F}(\mathbf{u},\mathbf{v})$  onde  $\mathbf{S}(\mathbf{u},\mathbf{v})$  é a transformada de Fourier da matriz de impulsos de amostragem, e  $\mathbf{F}$  é a transformada de Fourier de  $\mathbf{f}(\mathbf{x},\mathbf{y})$ . Esta distorção origina-se do fato das imagens serem espacialmente limitadas e impede a reconstrução completa das imagens a partir de suas amostras.

Da mesma maneira a quantização pode ser uniforme e não uniforme [GON 87], [PRA 78], [ROS 82], [HAL 79] e [MAS 84]. Quantização uniforme significa que os níveis de discretização são igualmente espaçados entre 0 e L (valor máximo) na escala de tons. Normalmente o número de níveis também é feito uma potência de dois, que no caso de dois níveis passa a se chamar de binarização.

Uma classe de algoritmos baseia-se na quantidade de tons possíveis na representação da imagem. Alguns destes processos convertem representações de tons de cinza em uma imagem binária a fim de aumentar a velocidade de processamneto. Entretanto a informação dos tons de cinza pode representar variações na iluminação, ponto de vista, propriedades de reflexão e permitir processos de medição quantitativos em uma imagem amostrada. No caso de imagens binárias, o limiar de quantização pode ser varável, variando de quadro a quadro ou localmente conforme a região da imagem. O quadro da figura 2.4, extraído de [SIL 87], mostra algumas aplicações e o método de quantização utilizado.

|               | Limiar     | Intensidade de<br>Luz Variável | Superficie<br>Contraste Var. | lluminação<br>Não Uniforme | Quantização<br>Espacial |

|---------------|------------|--------------------------------|------------------------------|----------------------------|-------------------------|

| Binarização   |            |                                |                              |                            | Lopusidi                |

|               | Automático | •                              | •                            |                            |                         |

|               | Local      | ●.                             | •                            | •                          |                         |

| Tons de Cinza |            | •                              | •                            | •                          | •                       |

Figura 2.4 Níveis de quantização e Aplicações

Para imagens em tons de cinza pode-se utilizar poucos níveis em transições abruptas e uma escala completa em regiões de lenta variação de luminosidade a fim de evitar falso contorno. Outra idéia similar é calcular a frequência de ocorrência dos níveis desejados e colocar níveis de quantização próximos na área de interesse e mais afastados nas outras áreas. A dificuldade de generalização destes métodos é que estes implicam em determinadas qualidades da imagem e um conhecimento prévio da mesma.

# 2.3.2 Efeitos da Digitalização

A bibliografia mostra a derivação de critérios de quantização ótima, que vişa minimizar o erro entre a imagem original e a imagem quantizada. Este erro é referenciado como erro de quantização e no caso de quantização uniforme estes critérios não são significativos. Na prática o número de linhas, ou a resolução vertical é dada pela câmera utilizada, já que o sinal de vídeo é fornecido linha a linha pelo dispositivo de captura.

Uma vez que a resolução vertical é limitada, resta ainda determinar a resolução horizontal, composta por duas figuras de mérito: número de pixel/linha e número de bits/pixel. Quanto maior estes dois valores, maior a resolução da imagem digitalizada que se aproximará da imagem original. É evidente que estes parâmetros estão limitados na capacidade dos sensores, como visto anteriormente, bem como na

na capacidade de memória de armazenamento de imagens. O número de bits necessários para armazenar uma imagem digitalizada, fazendo M pixels/linha, N linhas e b bits/pixel é:

#### $Mem = M \times N \times b$ bits

Estes dois parâmetros e a taxa de amostragem devem ser observados para evitar distorção na imagem. Estes efeitos de distorção são conhecidos como falso contorno, *aliasing* e *pixellation*.

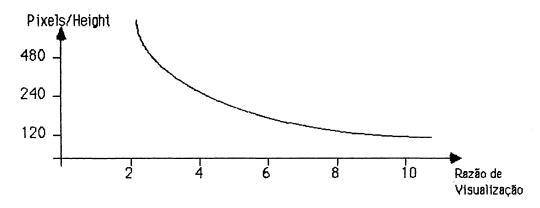

Pixellation é o efeito visual de uma baixa resolução; é também chamado de checker-boardou efeito de tabuleiro de xadrez. Este manifesta-se por uma aparência de blocos que formam a imagem. O grau de visibilidade depende da distância de visualização da imagem reproduzida. A relação entre a distância e o número de amostras de um quadro é a razão de visualização. Esta é a distância entre o observador e o dispositivo de exibição em múltiplos da altura do quadro. O gráfico da figura 2.5 mostra a relação necessária para uma boa visualização [LUT 89]. O gráfico assume que os pixels são quadrados (um pixel pode ocupar mais que uma linha de varredura).

Figura 2.5 Razão de Visualização

A literatura apresenta um valor mínimo de 256 pixels/linha para imagens provenientes de uma câmera de TV. Resolução de 512 pixels é apontada como boa resolução e o ganho em qualidade de visualização não é

significativo com imagens digitalizadas com 1024 pixels/linha, no caso de imagens de TV.

O número de bits/pixel determina o número de tons ou cores possíveis para representação das imagens. Um fator importante a ser observado é que uma boa relação sinal/ruído em um sistema de vídeo é de 46dB, o qual produz 3% de ruído pico a pico. O número de níveis necessário para reproduzir um sinal com ruído é, no mínimo, igual ao ruído pico a pico. Esta condição resulta em 33 níveis para um sistema de 46dB de sinal/ruído. O fenômeno chamado de falso contorno ocorre porque níveis analógicos caem entre dois limiares de quantização e são colocados com o mesmo valor digital. Qualquer parte da imagem que variar lentamente será convertida em degraus quando quantizada. Considerando este efeito, uma quantização de 8bpp (bits por pixel) evita o problema de falso contorno [LUT 89], [EKS 84]. Não existe muita vantagem em utilizar mais do que 8 bits em um sinal que será exibido para visualização a menos que algum processo não linear, como a correção gamma, seja realizada após a digitalização. Um número maior de bits pode ser necessário se o sinal for processado para outras aplicações que não a de simples visualização.

Aliasing é o erro causado pela amostragem de uma imagem que contém componentes acima do limite de Nyquist para a taxa de amostragem já discutida anteriormente. Limite de Nyquist significa que a faixa de frequência ocupada pelo sinal deve ser menor ou igual à metade da frequência de amostragem. No momento da exibição, quando a imagem é convertida em dados analógicos e exibida no monitor, a largura de banda do sistema deve ser no mínimo igual ao limite de Nyquist para a taxa de amostragem utilizada. É claro que sempre ocorrerá algum tipo de suavização em transições abruptas, porém apenas na direção horizontal.

Outros tipos de efeitos de degradação podem ocorrer devido a natureza dos processadores digitais e da imagem amostrada. Por exemplo, a quantização pode introduzir ruído randômico, modelado com ruído aditivo [AND 77] e, para uma imagem ruidosa, uma técnica de binarização pode introduzir o já citado ruído do tipo salt-and-pepper. Como se trabalha com palavras de largura finita, erros podem ser introduzidos nas transformações de domínio devido a precisão limitada dos processadores digitais.

# 2.4 Exibição de Imagens

Dispositivos de exibição são aqueles que convertem uma imagem de sua representação numérica para uma forma perceptível ao olho humano. Nos sistemas baseados em CRTs, as posições horizontal e vertical do pixels são convertidas em tensões que são utilizadas para direcionar um feixe de elétrons [GRO 79]. A cada ponto direcionado a intensidade do feixe produz um elemento de imagem. Esta intensidade é modulada por uma tensão proporcional ao valor do pixel exibido.

Um sistema de exibição de dados digitais possui algumas características diferentes dos sistemas convencionais de TV. Estes aspectos podem ser considerados a fim de compreender a limitação de resolução e fidelidade destes equipamentos. Tais considerações podem ser encontradas em [PHI 85].

Devido ao fato que a distância de observação é, na maioria das vezes, muito menor que em sistemas de televisão o entrelaçamento não é recomendado, já que pode introduzir piscamento local ou *line flicker*. A percepção de contorno em um quadro é uma interação de três parâmetros: tamanho da malha (*spot size*), espaçamento do fósforo (*phosphor spacing*) e tamanho do pixel (*pixel size*). O espaçamento de ponto é também chamado de *pitch*. Quando o quadro possui mais de uma cor ativa localmente, erros de convergência afetarão a percepção do contorno. Além destes erros, a falta de foco (defocalização) influi na identificação de detalhes finos da imagem.

O tamanho da malha e espaçamento (pitch) são figuras características do tubo (CRT) ao passo que o número e tamanho dos pixels é determinado pelo controle de vídeo do computador e pela área de varredura.

Spot size (SS) é o diâmetro do feixe de elétrons medido no ponto onde sua intensidade cai a 50%. O SS visual é o diâmetro onde a intensidade cai a 5% e é em torno de 2x o spot size físico.

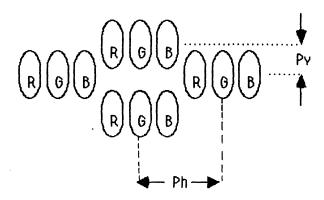

Dotpitch (DP) é um parâmetro geométrico do tubo e representa a distância entre os pontos de fósforo de mesma cor. Suas componentes

componentes ortogonais são chamadas de Pv e Ph, como mostrada na figura 2.6.

Figura 2.6 Dot Pitch Pv e Ph

Para tecnologia com uma máscara de trilhas a teoría é a mesma que para máscara de pontos [PHI 85], exceto que a primeira não possui pontos de fósforo, que atuam como uma amostragem espacial na imagem de vídeo projetada.

É conhecido que todos os caracteres, alfanuméricos ou gráficos, exibidos por computadores digitais são formados por uma matriz de pixels. Estes pixels, gerados pelo sistema controlador de vídeo do computador não são parâmetros do tubo. O tamanho do pixel depende ainda da velocidade de varredura horizontal e da distância de linha (vertical). Em aplicações gráficas, a fim de evitar distorção, são preferidos pixels quadrados. A iteração entre os parâmetros supracitados pode ser caracterizado nas relações *spot size vs. dot pitch spot size vs. pixel size* e *dot pitch vs. pixel size* e *dot pitch vs. pixel size* e

### \* Spot Sizevs. Dot Pitch

O tamanho da malha (*spot size* ) deve prevenir modulação de intensidade, caso contrário a luminosidade dependerá, aleatoriamente, da posição do spot relativamente ao espaço entre pontos. Desta forma o *pitch* deve ser menor que o *spot size*

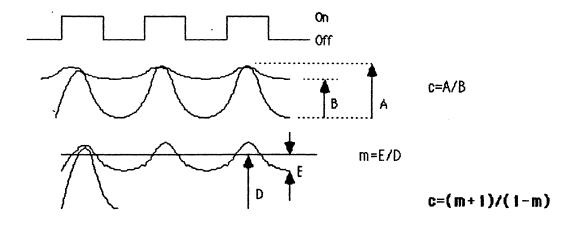

### \* Spot Sizevs Pixel Size

Esta interação é considerada em termos de índice de modulação (m) e razão de contraste (c). Os dois valores descrevem o mesmo fenômeno, que pode ser visto na figura 2.7.

Figura 2.7 índice de Modulação (m) e Razão de Contraste (c)

A partir das expressões pode-se verificar, por exemplo, que um indice de modulação de 10% (-20dB) é equivalente a uma razão de contraste de 1.22. Para um padrão *on-off-on* exibido, 2 pixels vizinhos serão misturados. Pixels adjacentes em estado *on* (ligados) devem ser misturados para obter-se uma imagem homogênea. Assim o tamanho de pixels deve ser menor que o *spot size*

### \* Dot Pitchvs. Pixel Size

Existem dois aspectos na relação entre o dot pitch e o tamanho do pixel. São eles o padrão de Moiré e o teorema de Shannon. Estes fenômenos ocorrem devido ao fato que a máscara de sombra do tubo atua como um filtro de amostragem espacial. Se o tamanho do pixel for quase igual ou múltiplo de Ph ou Pv, padrões de batimento espacial podem ocorrer na tela. O padrão de batimento em áreas iluminadas uniformemente são

chamados de " scan Moiré", onde a distância da linha é quase igual ou múltiplo do espaçamento das trilhas verticais. O padrão de batimento em quadros que possuem faixas estreitas é chamado de vídeo Moiré, onde o espaçamento de faixas é quase igual ou múltiplo do espaço das trilhas horizontais. Deve-se assim evitar um tamanho vertical de pixel (distância de linha) perto de 1,2,3,... vezes Pv e um tamanho horizontal múltiplo inteiro de Ph.

O teorema de Shannon para sinais amostrados diz que a largura de banda ocupada pelo sinal deve ser menor do que a metade da frequência de amostragem, caso contrário os detalhes finos serão perdidos. Transferindo o teorema para a máscara de sombra do tubo, vem que a distância mínima de pixel em um padrão *on-off-on* deve ser maior que 2 *pitches*. Podemos representar esta última afirmativa nas inequações abaixo.

# Altura pixel > Pv Largura pixel > Ph

Na prática no mínimo 25% [PHI 85] deve ser adicionado ao tamanho do pixel para reduzir os efeitos de aliasing. Em aplicações de imagem esta regra pode ser violada, já que normalmente os quadros exibem regularidades que se extendem por mais do que um pixel. O "efeito escada" ao longo de linhas inclinadas pode ser reduzido ou mesmo eliminado quando utilizado pixels "sub-Shannon" (em tamanho). A figura 2.8 mostra a relação entre os parâmetros discutidos acima.

podem ser consideradas como sinais unidimensionais. Desta forma, conforme o enfoque dado ao tratamento e ao modelo de degradação usado, os algoritmos podem operar apenas com linhas, conjunto de linhas ou conjunto de quadros. Aqueles que trabalham a nível de linhas são referenciados como filtros horizontais e aqueles que tratam conjunto de linhas valem-se das propriedades de vizinhança dos pixels, herdada do modelo bidimensional de imagem. Na maioria das referências o tratamento bidimensional é realizado. Em alguns casos o sinal de transmissão de TV pode ser tratado de forma unidimensional, como encontrado em [EDE 89] e [PHI 86]. Outra técnica é utilizar a filtragem temporal, aproveitando a correlação entre quadros. Neste tipo de técnica são extraidos parâmetros de um quadro para processamento dos próximos quadros. É claro que para imagêns móveis deve existir um detector de movimento que iniba os procedimentos de filtragem para grandes variações do quadro [EDE 89].

Além do número de pixels/linha a escolha da frequência de amostragem deve levar em conta sua relação com a frequência de linha. Esta relação torna-se importante na medida que é necessário utilizar componentes de armazenamento de linhas e quadros, que devem estar sincronizados com a frequência de amostragem. Se a taxa de amostragem, denotada por f<sub>S</sub> for um múltiplo inteiro da frequência de linha f<sub>1</sub>, evita-se o problema de sincronização do relógio a cada início de linha, caso contrário a posição dos pixels amostrados poderão variar de quadro para quadro, causando um efeito de piscamento nas transições, quando da captura de imagens contínuas.

Com base nos tópicos abordados neste capítulo foram escolhidos os valores dos parâmetros de nº pixels/linha e nº bits/pixel para o modelo de sistema utilizado ao longo do trabalho.

Quantização Uniforme 512 pixels/linha 8 bits/pixel (bpp)- 256 tons fs = M\*f], comMinteiro Por exemplo para o pdrão RS170 temos:

Frequência de linha: 15Khz

Tempo de linha ativa: **54 us**

Frequência mínima: 1/(54/512)= 9.48Mhz

Frequência de amostragem = 9.48Mhz (632\*f1)

# 3 PROCESSAMENTO DE IMAGENS

Processamento de imagem consiste em qualquer operação que transforme uma representação de uma imagem em outra, a qual pode ser utilizada para visualizar algum detalhe específico, descrever um conjunto de objetos ou representar uma forma compacta de armazenamento desta imagem. Os algoritmos do processamento de imagens podem ser agrupados de acordo com o objetivo ao qual se destinam. Procedimentos para enriquecimento, restauração, codificação e transmissão de imagens já existem há algum tempo e hoje servem de núcleo para novas técnicas de visão computadorizada, que buscam a compreensão de imagens em cenas tri-dimensionais, modelando o comportamento do sistema de visualização humano.

Existem duas possíveis fontes de imagem: as capturadas através de sensores e as sintetizadas por algum método computacional. O tratamento de dados provenientes de sensores trabalha com cenas reais, procurando fidelidade ao quadro capturado ou extração de caracteristicas e informações.

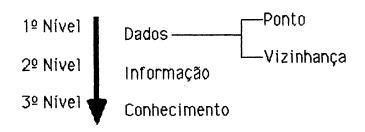

As técnicas de IP podem ser independentes do contexto, muitas vezes chamados de processamento de baixo nível, ou dependentes do contexto (orientada ao objetivo), também chamadas de processamento de alto nível. Os algoritmos usados podem ser classificados hierarquicamente em níveis de processamento. No nível mais baixo de processamento, o qual inclui muitos dos algoritmos convencionais de IP, a imagem é considerada como um conjunto de pixels, sem referência a estrutura ou objetos contidos na imagem. Estas operações atuam sobre a imagem, pixel a pixel, amostrada e organizada em uma matriz bidimensional. Exemplos destas operações são filtros, operadores de smoothing, codificação de imagens e transformação cosseno. Em procedimentos como enriquecimento de imagens, onde um dos fatores é a qualidade subjetiva dos dados, técnicas são empregadas, bem como tratamento estatístico dos dados. AD HOC Uma revisão de algumas técnicas pode ser encontrada em [OFF 85], [BAR 87], [DVO 88], [AMO 88].

Para tarefas mais complexas não basta tratar a imagem como um conjunto de pontos amostrados. O próximo nível de processamento consiste em extrair e manipular informações contidas na imagem. Estas informações podem ser descritas em termos de estruturas como bordas, limites, texturas ou formas que constituem objetos. Outra maneira de obtenção de tais dados é utilizar métodos de decomposição estatística da imagem.

Um terceiro nível de processamento atende tarefas mais complexas, em aplicações onde algum grau de interpretação e entendimento se faz necessário e, por conseguinte, incluem a utilização do conhecimento sobre o domínio utilizado. Tarefas que utilizam sistemas de inteligência são, por exemplo, descrição de cenas ou modelagem 3-D. Entretanto mesmo com estas tarefas que incluem um conhecimento significativo sobre a imagem, o nível mais baixo de processamento é ainda necessário. Esta afirmação é devido ao fato que sistemas baseados no conhecimento necessitam de um conjunto de qualidades confiáveis para trabalhar, função do processamento de baixo nível sobre as imagens. A figura 3.1 mostra a classificação hierárquica dos algoritmos de processamento de imagens, que resume-se em 3 níveis. Esta classificação é didática e alguns algoritmos caminham sobre todos os níveis, não restringindo-se a um nível particular.

Figura 3.1 Classificação hierárquica dos algoritmos IP