# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

## FÁBIO LUÍS LIVI RAMOS

# Arquitetura para o Algoritmo CAVLC de Codificação de Entropia segundo o Padrão H.264/AVC

Dissertação apresentada como requisito parcial para a obtenção do grau de Mestre em Ciência da Computação

Prof. Dr. Sergio Bampi Orientador

# CIP – CATALOGAÇÃO NA PUBLICAÇÃO

#### Ramos, Fábio Luís Livi

Arquitetura para o Algoritmo CAVLC de Codificação de Entropia segundo o Padrão H.264/AVC / Fábio Luís Livi Ramos – Porto Alegre: Programa de Pós-Graduação em Computação, 2010.

99 f.:il.

Dissertação (mestrado) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação. Porto Alegre, BR – RS, 2010. Orientador: Sergio Bampi;

1.CAVLC. 2.Compressão de Vídeo 3.H.264/AVC 4.Arquiteturas de Hardware. I. Bampi, Sergio. II.Título.

## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos Alexandre Netto

Vice-Reitor: Prof. Rui Vicente Oppermann

Pró-Reitor de Pós-Graduação: Prof. Aldo Bolten Lucion Diretor do Instituto de Informática: Prof. Flávio Rech Wagner

Coordenador do PPGC: Prof. Álvaro Freitas Moreira

Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

## **AGRADECIMENTOS**

Primeiramente gostaria de agradecer a minha família, meus pais Gregório e Rosa, e minha irmã Renata. Sem eles, não seria o que sou hoje, além de eu hoje perceber profundamente o quão difícil pode ser criar e educar um filho nos dias de hoje. Obrigado a eles pelo amor, carinho, apoio, compressão durante todos esses anos. Sou muito feliz por poder ser parte da minha família e agradeço profundamente tudo que puderam me oferecer para eu chegar onde cheguei! Amo vocês!

Gostaria de agradecer a minha namorada Betina, e a família dela, Carmo , Leoni e Fernanda, pelo apoio durante esses últimos quase dois anos. Todos foram muito importantes para que eu conseguisse fechar esta etapa da minha caminhada, sendo para mim como uma segunda família! Obrigado gatinha por tudo!! Te amo! Você é uma pessoal essencial e muito importante para mim!

Gostaria também de agradecer aos meus amigos, os quais estamos juntos faz muitos anos. Ao pessoal do Colégio Militar: Souza, Santos Rocha, Gra, Nascimento, Coimbra, Quinto, Pontel, Luiz e Cláudio, obrigado pela amizade inigualável desde a época do colégio, obrigado pelo carinho e companheirismo esses anos todos. Ao pessoal da Engenharia da Computação: Bruno, Osvaldo, Kunz, Giancarlo, Schenkel, Gordo, Jonas, Nondillo e Hugsy, obrigado pela amizade e parceria durante esses anos desde o começo da graduação, obrigado também pelas já legendárias idas a praia de Imbé. A todos meu muito obrigado pela amizade, vocês são parte essencial na minha vida.

Ao pessoal do Lab 215, muitos dos quais tenho como verdadeiros amigos hoje: Cláudio, Marcelo, Dieison, Roger, Guilherme Mauch, Thaísa, Vágner, Debóra, Zanetti, Alemão, Miklécio, Guilherme, Franco e Gustavo. Obrigado pelos ótimos momentos durante essa etapa do mestrado, tanto pelos momentos técnicos quanto nossas discussões filosóficas e churrascos do Lab. Obrigado!

Obrigado também ao pessoal da FGV: Bibiana, Flávio, Paulista, Natan e Fernando, pela aventura que foi passar por lá e a amizade que continuou mesmo após o fim do curso.

Ficam aqui também meus agradecimentos ao pessoal do CEITEC, lugar que estou nos últimos meses trabalhando e fui muito bem recebido. Ficam aqui meus agradecimentos especiais ao Wagston, Hervé, Kindel, Rohde, Cyrille, João, Janaína, Fred e Palma.

Meus agradecimentos também ficam ao professor Sergio Bampi, que me aceitou como seu aluno no mestrado e me orientou nesse tempo todo. Obrigado pelos ensinamentos e pela competência, além da grande humanidade no trato com seus alunos e também pela compreensão quando fiz a seleção para o CEITEC.

Gostaria de agradecer também aos professores do PPGC, funcionários, CNPq e a todos que de uma forma ou outra contribuíram com essa conquista aqui apresentada. Ficam também os meus agradecimentos as pessoas que passaram pela minha vida e de alguma forma deixaram alguma contribuição na minha essência.

Por fim, mas não menos importante, gostaria de agradecer a vida, por ter me dado a oportunidade de viver e provar para mim mesmo mais uma vez que fui capaz de mais uma grande conquista, além de ter me apresentado todas essas pessoas maravilhosas que citei anteriormente nessa seção, e por mostrar que sou uma pessoa muito feliz por tudo que já tenho!

Obrigado a todos, de verdade!!

# **SUMÁRIO**

| LIST       | A DE ABREVIATURAS E SIGLAS                      | 7  |

|------------|-------------------------------------------------|----|

| LIST       | A DE FIGURAS                                    | 9  |

|            | A DE TABELAS                                    |    |

|            | J <b>MO</b>                                     |    |

|            | TRACT                                           |    |

| 1 I        | NTRODUÇÃO                                       | 15 |

|            | CONCEITOS DE COMPRESSÃO DE VÍDEO E O PADRÃO DE  |    |

|            | IFICAÇÃO H.264/AVC                              |    |

| 2.1        | Conceitos de Compressão de Vídeo Digital        |    |

| 2.2        | Padrão de Codificação de Vídeo H.264/AVC        |    |

| 2.2.1      | Perfis e Níveis do Padrão H.264/AVC             |    |

| 2.2.2      | Codec H.264/AVC                                 |    |

| 2.3        | Conclusão                                       |    |

| 3          | CODIFICAÇÃO DE ENTROPIA CAVLC                   |    |

| 3.1        | Algoritmo CAVLC                                 |    |

| 3.1.1      | Ordenamento Ziguezague                          |    |

| 3.1.2      | Estatísticas dos Coeficientes                   | 35 |

| 3.1.3      | Elementos Sintáticos                            |    |

| 3.1.4      | Montagem do Bitstream                           | 39 |

| 3.2        | Revisões de Trabalhos Encontrados na Literatura |    |

| 3.2.1      | Trabalho de Chen et al                          |    |

| 3.2.2      | Trabalho de Chien et al                         | 40 |

| 3.2.3      | Trabalho de Yi et al                            | 41 |

| 3.2.4      | Trabalho de Tsai et al                          | 41 |

| 3.2.5      | Trabalho de Han et al                           |    |

| 3.2.6      | Trabalho de Lee et al                           | 42 |

| 3.3        | Conclusão                                       |    |

| 4 A        | ARQUITETURA DESENVOLVIDA PARA O ALGORTIMO CAVLC |    |

| <b>4.1</b> | Buffer de Entrada                               |    |

| 4.1.1      | DPRAM                                           |    |

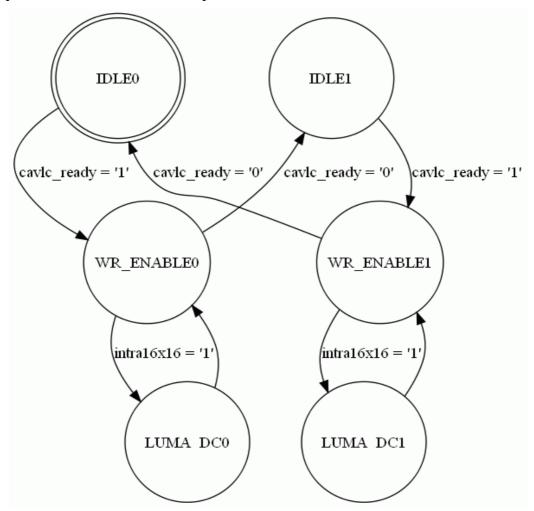

| 4.1.2      | Máquinas de Estados de Escrita                  |    |

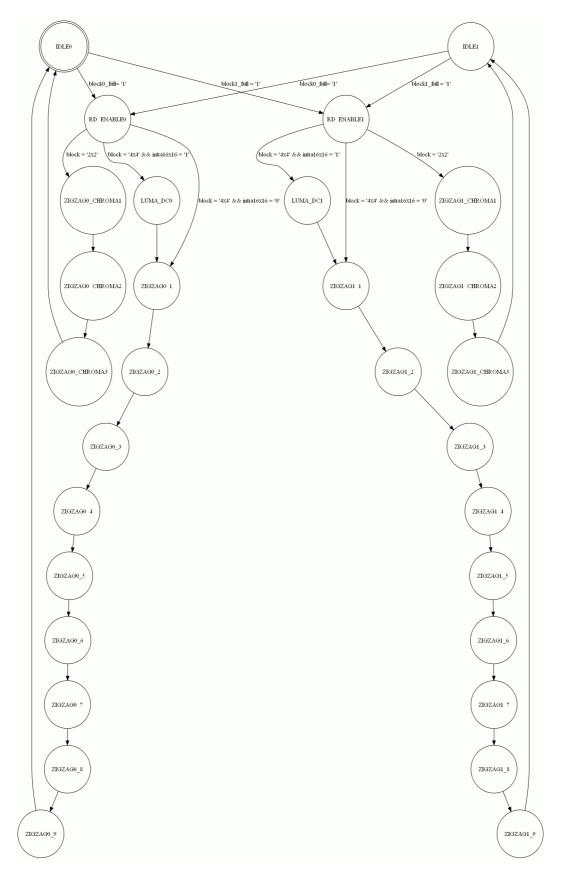

| 4.1.3      | Máquina de Estados de Leitura                   |    |

| 4.1.4      | Topo do Buffer                                  | 50 |

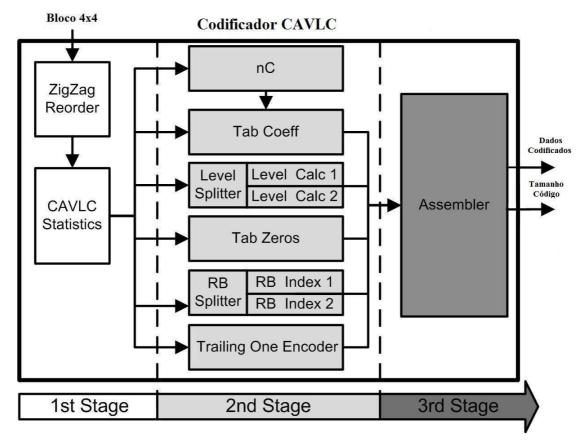

| 4.2        | Componente CAVLC                                | 52 |

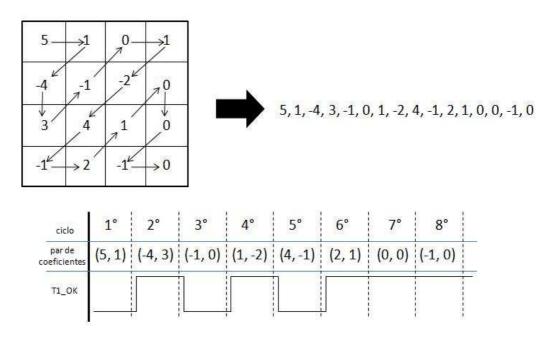

| 4.2.1      | Estágio de Scan                                 |    |

| 4.2.2      | Estágio de Codificação                          |    |

| 4.2.3      | Estágio de Montagem                             |    |

| 4.2.4      | Máquina de Estados do Componente CAVLC          | 80 |

| 4.3 | Conclusão                                                  | 84 |

|-----|------------------------------------------------------------|----|

| 5   | RESULTADOS E COMPARAÇÕES DA ARQUITETURA                    |    |

| DE  | SENVOLVIDA                                                 | 85 |

| 5.1 | Resultados de Síntese e Comparações com o Componente CAVLC |    |

| Des | senvolvido                                                 | 85 |

| 5.2 | Conclusão                                                  | 89 |

| 6   | CONCLUSÃO E TRABALHOS FUTUROS                              | 90 |

| RE  | FERÊNCIAS                                                  | 92 |

|     | ÊNDICE AMBIENTE DE VALIDAÇÃO                               |    |

## LISTA DE ABREVIATURAS E SIGLAS

AC Alternating Current

ASIC Application Specific Integrated Circuit

AVC Advanced Video Coding

CABAC Context-Based Adaptive Bynary Arithmetic Coding

CAVLC Context-Based Adaptive Variable Length Coding

Cb Chrominance Blue

CBP Coded Block Pattern

Codec Codificador/Decodificador

Cr Chrominance Red

DC Direct Current

DCT Discrete Cosine Transform

DPRAM Dual Port Random Access Memory

FPGA Field Programmable Gate Array

FRExt Fidelity Range Extensions

FSM Finite State Machine

HD High Definition

HDL Hardware Description Language

HDTV High Definition Digital Television

I4MB Modo de Predição Intra 4x4I16MB Modo de Predição Intra 16x16

IDCT Inverse Discrete Cosine Transform

IEC International Electrotechnical Commission

ISO International Organization for Standardization

ITU International Telecommunication Union

JVT Joint Video Team

LUT Look Up Table

MC Motion Compensation

ME Motion Estimation

MPEG Motion Pictures Experts Group

QCIF Quarter Commom Intermediate Format

QP Quantization Parameter

RGB Red, Green, Blue

SI Switch-I SP Switch-P

TSMC Taiwan Semiconductors Manufacturing Company

TV Televisão

MC Brasil

UFRGS Universidade Federal do Rio Grande do Sul

VCEG Video Coding Experts Group

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrated Circuits

Y Luminance

YCbCr Luminance, Chrominance Blue, Chrominance Red

# LISTA DE FIGURAS

| Figura 2.1: Relação entre os perfis <i>Baseline</i> , <i>Main</i> , <i>Extended</i> e <i>High</i> | . 20 |

|---------------------------------------------------------------------------------------------------|------|

| Figura 2.2: Relação entre os perfis FRExt                                                         | . 20 |

| Figura 2.3: Diagrama de Blocos do Codificador H.264/AVC                                           | . 22 |

| Figura 2.4: Diagrama de Blocos do Decodificador H.264/AVC                                         | . 22 |

| Figura 2.5: Cálculo de um vetor de movimento                                                      | . 23 |

| Figura 2.6: Divisões possíveis para um macrobloco                                                 | . 23 |

| Figura 2.7: Divisões do sub-macrobloco 8x8                                                        | . 23 |

| Figura 2.8: Amostras a serem usadas no cálculo da predição Intra para um bloco 4x4                | . 24 |

| Figura 2.9: Os nove modos de predição Intra-quadros para macroblocos I4MB                         | . 25 |

| Figura 2.10: Os quatro modos de predição Intra-quadros para macroblocos I16MB                     | . 25 |

| Figura 2.11: Aplicação dos modos Intra sobre um quadro de vídeo exemplo                           | . 26 |

| Figura 2.12:Resultado da predição Intra. Quadro original à esquerda e quadro de                   |      |

| resíduos à direita                                                                                | . 26 |

| Figura 2.13: Bloco 4x4 ao sofrer processo de transformada: à esquerda o bloco origin              | nal  |

| e à direita após o processo                                                                       | . 27 |

| Figura 2.14: Bloco 4x4 ao sofrer processo de quantização: à esquerda bloco após sof               | rer  |

| a transformada e à direita após a quantização                                                     | . 29 |

| Figura 2.15: À esquerda imagem sofrendo o feito de bloco; à direita a imagem ao pas               | ssar |

| pelo filtro de deblocagem                                                                         |      |

| Figura 3.1: Ordem Duplo Z de entrega de blocos dentro de um macrobloco                            | . 34 |

| Figura 3.2: Ordenamento Ziguezague de um bloco 4x4                                                | . 34 |

| Figura 3.3: Estatísticas do bloco 4x4                                                             | . 36 |

| Figura 3.4: Coeficientes não-zero numerados para estatísticas de Run Before e Zeros               |      |

| Left                                                                                              | . 36 |

| Figura 3.5: Cálculo de <i>nC</i> para alguns blocos dentro de macroblocos                         | . 37 |

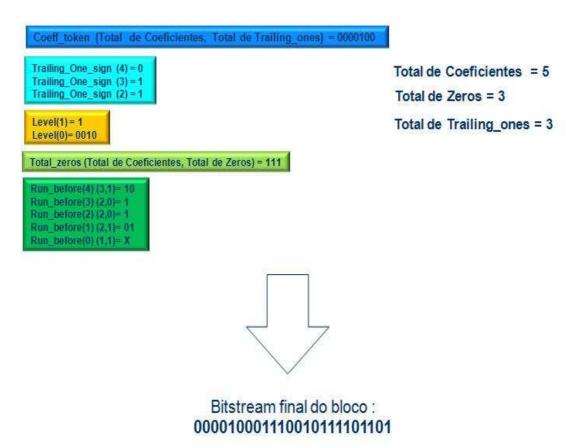

| Figura 3.6: Montagem do bitstream final para o bloco exemplo                                      | . 39 |

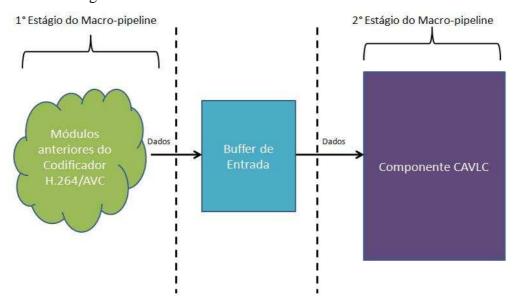

| Figura 4.1: Buffer de Entrada e Componente CAVLC                                                  | . 44 |

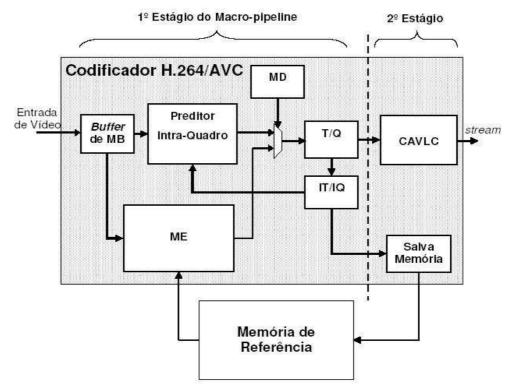

| Figura 4.2: Componentes do Macro-pipeline de um Codificador H.264/AVC                             | . 45 |

| Figura 4.3: Organização da DPRAM do <i>Buffer</i> de entrada                                      | . 46 |

| Figura 4.4: Máquina de Estados de Escrita do Buffer.                                              | . 48 |

| Figura 4.5: Máquina de Estados de Leitura do Buffer                                               | . 51 |

| Figura 4.6: Estágios e blocos do Macro-pipeline do componente CAVLC                               | . 53 |

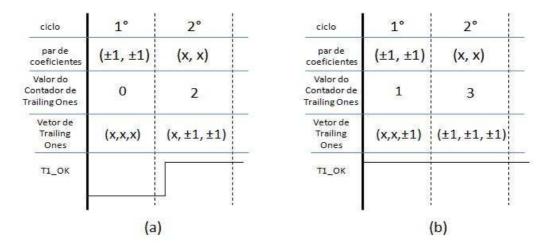

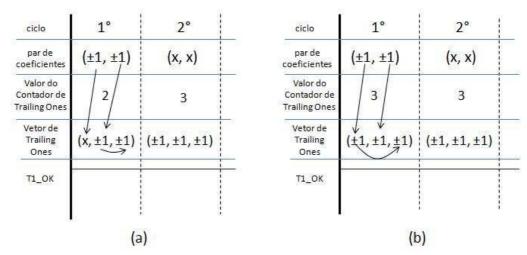

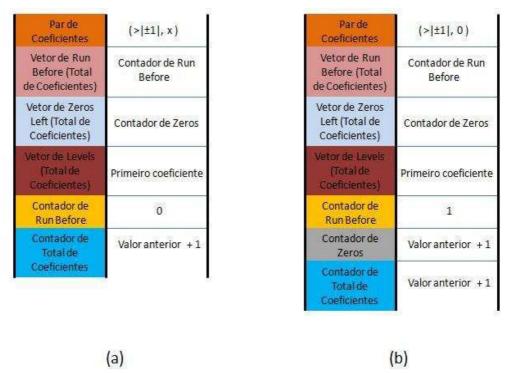

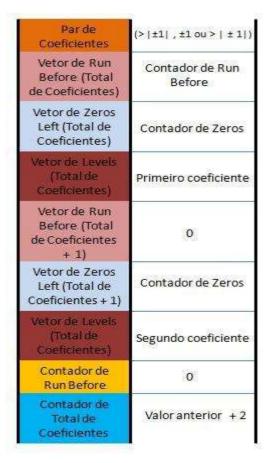

| Figura 4.7: Blocos 4x4 exemplo para comportamento do sinal T1_ok                                  | . 55 |

| Figura 4.8: Comportamente do vetor de Trailing Ones.                                              | . 55 |

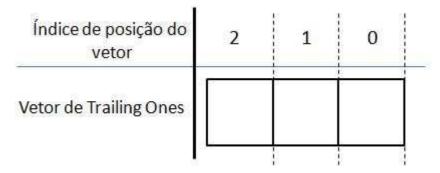

| Figura 4.9: Vetor de <i>Trailing Ones</i> com índice de cada posição                              | . 56 |

| Figura 4.10: Comportamento dos contadores caso dois coeficientes com valor zero                   |      |

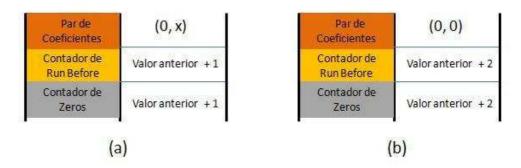

| tenham ocorrido                                                                                   | . 56 |

|                                                                                                   |      |

| Figura 4.11: Comportamento dos vetores e contadores de estatísticas quando o primeiro              |

|----------------------------------------------------------------------------------------------------|

| coeficiente é zero                                                                                 |

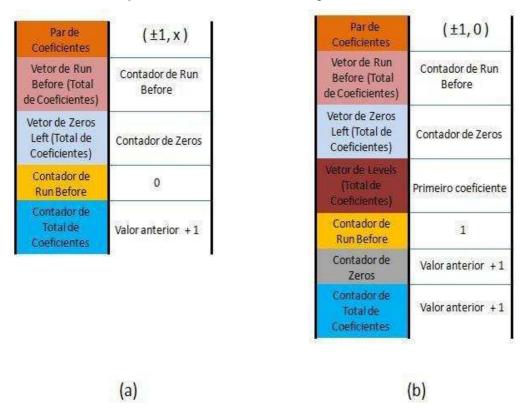

| Figura 4.12: Comportamento do contador de <i>Trailing Ones</i> quando o primeiro                   |

| coeficiente possui valor zero e o segundo possui valor maior que  ±1                               |

| Figura 4.13: Comportamento dos vetores e contadores de estatísticas quando o primeiro              |

| coeficiente é $\pm 1$                                                                              |

| Figura 4.14: Comportamento do contador de <i>Trailing Ones</i> quando dois coeficientes            |

| acontecem com valor ±1, sendo (a) o contador de <i>Trailing Ones</i> com valor 0 e (b) o           |

| contador de Trailing Ones com valor 1                                                              |

| Figura 4.15: Comportamento do contador <i>Trailing Ones</i> quando dois coeficientes               |

| acontecem com valor ±1, sendo (a) o contador de <i>Trailing Ones</i> com valor 2 e (b) o           |

| contador de <i>Trailing Ones</i> com valor 3                                                       |

| Figura 4.16: Comportamento do contador <i>Trailing Ones</i> quando o primeiro coeficiente          |

| possui valor $\pm 1$ e o segundo um valor maior que $ \pm 1 $                                      |

| Figura 4.17: Comportamento dos vetores e contadores de estatísticas quando o primeiro              |

| coeficiente é ±1 e o segundo é diferente de zero                                                   |

| Figura 4.18: Comportamento do contador de <i>Trailing Ones</i> quando o primeiro                   |

| coeficiente possui valor maior que  ±1  e o segundo possui valor zero                              |

| Figura 4.19: Comportamento dos vetores e contadores de estatística quando o primeiro               |

| coeficiente é maior que  ±1  e o segundo não importa (a) ou é zero (b)                             |

| Figura 4.20: Comportamento do contador <i>Trailing Ones</i> quando o primeiro coeficiente          |

| possui valor maior que $ \pm 1 $ e o segundo valor $\pm 1$                                         |

| Figura 4.21: Comportamento do contador <i>Trailing Ones</i> quando os dois coeficientes            |

| possuem valor maior que  ±1                                                                        |

| Figura 4.22: Comportamento dos vetores e contadores de estatísticas quando o primeiro              |

| coeficiente é maior que  ±1  e o segundo é diferente de zero                                       |

| Figura 4.23: Estatísticas finais do estágio de <i>Scan</i> : (a) os coeficientes dos vetores e (b) |

| os valores dos contadores                                                                          |

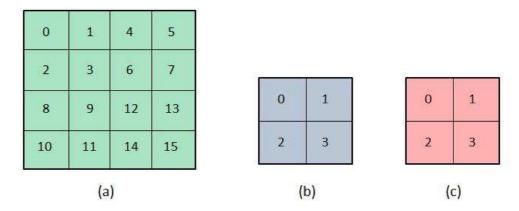

| Figura 4.24: Registradores do Total de Coeficientes de cada bloco, sendo (a) para Luma             |

| e (b) e (c) para Chroma <i>Blue</i> e <i>Red</i>                                                   |

| Figura 4.25: Registradores de Aresta vertical para macroblocos 4x4                                 |

| Figura 4.26: Registradores para coeficientes de Chroma: (a) para aresta vertical azul; (b)         |

| para aresta vertical vermelha                                                                      |

| Figura 4.27: Vetor de 270 registradores para total de coeficientes entre blocos de linhas          |

| diferentes no mesmo <i>Slice</i>                                                                   |

| Figura 4.28: Vetor de 135 registradores para total de coeficientes entre blocos de linhas          |

| diferentes no mesmo <i>Slice</i> para Chroma Blue (a) e Chroma Red (b)                             |

| Figura 4.29: <i>Pipeline</i> de processamento dos <i>Levels</i>                                    |

|                                                                                                    |

| Figura 4.30: Máscaras para o cálculo dos <i>Levels</i>                                             |

|                                                                                                    |

| Figura 4.32: Lógica para cálculo do código e tamanho de <i>Levels</i> para <i>Value</i> 0          |

|                                                                                                    |

| Figura 4.33: Lógica para cálculo do código e tamanho de <i>Levels</i> para <i>Value</i> 1 até 6 77 |

| Figura 4.34: Lógica de montagem para dois elementos sintáticos no componente                       |

| Assembler                                                                                          |

| Figura 4.35: Lógica de montagem para um elemento sintático no componente                           |

| Assembler                                                                                          |

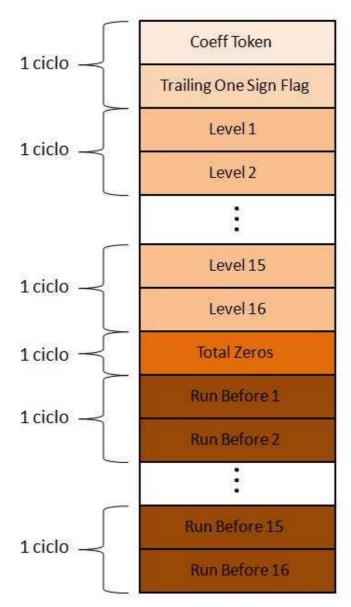

| Figura 4.36: Ordem dos elementos sintáticos alocados no <i>bitstream</i>                           |

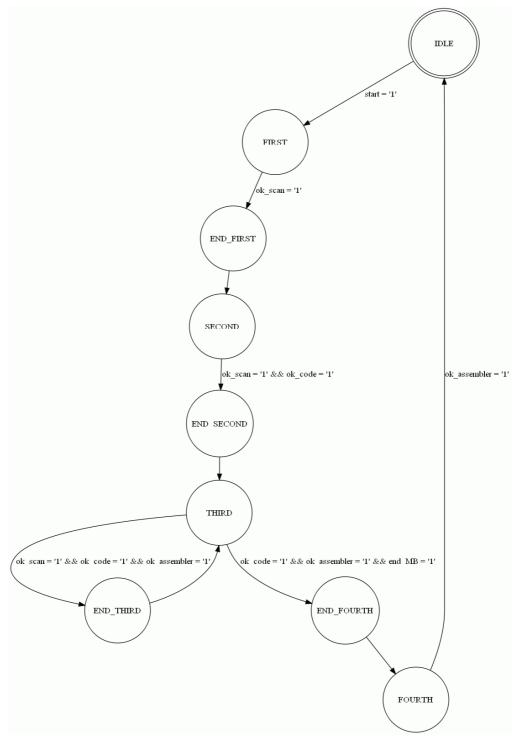

| Figura 4.37: Máquina de Estados do Componente CAVLC                                                |

|                                                                                                    |

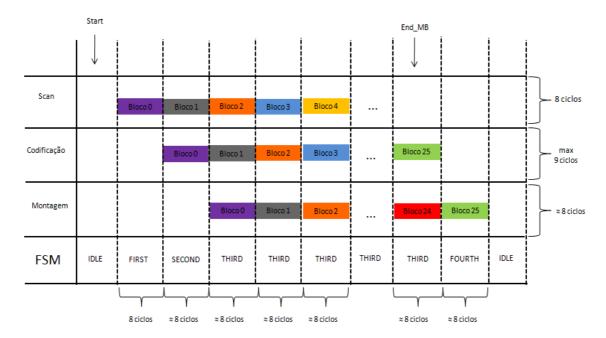

| Figura 4 | .38: Tem | porização | dos Estágios | s do <i>Macro</i> - | <i>pipeline</i> e d | a FSM | 84 |

|----------|----------|-----------|--------------|---------------------|---------------------|-------|----|

| 0        |          | 1         |              |                     | I I                 |       |    |

# LISTA DE TABELAS

| Tabela 2.1: Níveis do padrão H.264/AVC                                           | 21 |

|----------------------------------------------------------------------------------|----|

| Tabela 2.2: Códigos Exp-Golomb                                                   | 31 |

| Tabela 4.1: Relação entre os valores <i>Value</i> e <i>Threshold</i>             | 73 |

| Tabela 4.2: Relação entre os valores <i>Value</i> e <i>Thres_N</i>               | 77 |

| Tabela 5.1: Resultados de Síntese para FPGA Xilinx Virtex 5                      | 85 |

| Tabela 5.2: Número Médio de Ciclos usados para processar um Macrobloco pelas     |    |

| Seqüências de Vídeo Teste                                                        | 86 |

| Tabela 5.3: Comparações de Ciclos e Freqüência com trabalhos da literatura       | 86 |

| Tabela 5.4: Comparações de Tecnologia, Área e uso do Montador com os trabalhos o | da |

| literatura                                                                       | 88 |

|                                                                                  |    |

#### **RESUMO**

A codificação de vídeo digital depende de uma série de etapas para ser alcançada a compressão de dados necessária para, então, o vídeo ser enviado ou armazenado em um meio. Existe uma série de padrões que se propõe a isso e dentre eles, o que apresenta o melhor desempenho em termos de compressão de dados e qualidade de vídeo até o presente momento é o H.264/AVC.

Considerando então o padrão H.264/AVC, uma das etapas do seu processamento é a codificação de entropia, sendo que um dos algoritmos usados para esse fim é o CAVLC (Context-Based Adaptive Variable Length Coding). Esta técnica faz uso de uma série de características onde o código gerado pela seqüência de vídeo processada tende a assumir, para, então, gerar códigos menores para padrões do vídeo que tendem a aparecer mais freqüentemente em detrimento a padrões que são mais raros, fazendo para isso uso de código de comprimento variável que depende do contexto atual em que cada porção do código está sendo processada.

Baseado nisso, este trabalho apresenta uma arquitetura para o algoritmo CAVLC segundo o padrão H.264/AVC, onde foi inserida uma nova técnica para diminuir o gargalo na etapa inicial do algoritmo, além de usar técnicas já conhecidas na literatura para diminuir os ciclos necessários para o processamento do componente, fazendo com que a arquitetura aqui apresentada tenha um ganho em relação aos demais trabalhos da literatura encontrados e comparados.

Esse trabalho está inserido no esforço do grupo de TV Digital da UFRGS e pretende-se que, no futuro, esse módulo seja integrado aos demais módulos desenvolvidos no grupo para formar um codificador H.264/AVC completo.

# Architecture for the CAVLC Entropy Encoding Algorithm According the H.264/AVC Standard

#### **ABSTRACT**

The digital video encoding depends on different phases to reach the necessary data compression, so the video can be transmitted through or stored in the medium. There are a variety of compression standards that are designed to that purpose and, among them, the one that has the best performance currently is the H.264/AVC.

Considering the H.264/AVC standard, one of the processing stages is the entropy encoding. CAVLC (*Context-Based Adaptive Variable Length Coding*) is one of the algorithms that can be used for that end. It can use many of the code particularities, generated by the video sequence being processed. This way, CAVLC can generate codes with less bits for portions of the video sequence that occur more often, and codes with more bits for rarer patterns of the video sequence, using variable code lengths that depend on the current context for each portion of the code being processed.

Based on this, the present work presents a VLSI hardware architecture for the CAVLC algorithm, according to the H.264/AVC standard. The architecture introduces a new technique to decrease the bottleneck at the initial stage of the algorithm and, furthermore, well-known techniques already tested in works found in the literature, were also implemented, to save processing cycles at the other stages of the component. The present architecture is then able to achieve gains compared to the other works found in the literature.

This work is inserted into the effort of the Digital TV Group at UFRGS and it is intended to be integrated with the others developed by the group to make a complete H.264/AVC encoder.

**Keywords:** CAVLC, Video Compression, H.264/AVC, Hardware Architectures.

# 1 INTRODUÇÃO

A compressão de vídeo digital tem sido uma das principais áreas de pesquisa nos últimos anos, em grande parte devido a suas inúmeras aplicações, desde pequenos celulares até telas de cinema de alta fidelidade. Como é de se esperar, o aumento na capacidade de comprimir informações de vídeo de padrões de vídeo mais atuais não vem sem um aumento na complexidade dos algoritmos usados para esse fim.

Muitos padrões para codificação de vídeo foram criados e usados ao longo dos últimos anos, com destaque para o MPEG-2 que, durante cerca de 10 anos, foi o padrão adotado na grande maioria das aplicações que envolviam vídeo digital.

Em 2003, da união dos esforços de especialistas do VCEG da ITU-T (ITU-T, 2010) e de especialistas do MPEG da ISO/IEC (ISO/IEC, 2010), sob o nome de JVT- *Joint Video Team* (ITU-T, 2003), surgiu o padrão que viria a aumentar a capacidade de compressão de vídeo em relação aos demais padrões já existentes: o H.264/AVC.

O padrão H.264/AVC possuía uma capacidade de compressão de vídeo que alcançava até duas vezes a taxa que o MPEG-2 conseguia (esse que, até então, era o padrão mais poderoso de compressão de vídeo) (KAMACI, 2003). Não obstante, essa considerável melhoria em relação ao MPEG-2 trouxe também um aumento na complexidade computacional na ordem de até 8 vezes em relação ao MPEG-2 (SUNNA, 2005).

O H.264/AVC, em sua primeira versão, apresentava três diferentes perfis originais: *Baseline*, *Extended* e *Main*. Na seqüência, buscando melhorar o padrão para aplicações de alta fidelidade, como cinemas, foram gerados mais 4 perfis, todos esses agrupados como perfis *High* (denominados também como *Fidelity Range Extensions* -FRExt) (ITU-T, 2004).

Apesar das grandes vantagens apresentadas pelo padrão, devido a também alta taxa de complexidade computacional advinda dessa melhoria do H.264/AVC, se tornou inviável que codificadores em software seguindo o padrão conseguissem processar vídeos em tempo real para HDTV (para a tecnologia presente), isso se considerando usar as ferramentas de mais alta complexidade do padrão. Assim sendo, uma grande gama de esforços, tanto da indústria quanto do meio acadêmico ao redor do mundo foi iniciada a fim de se achar soluções de implementação para o codec H.264/AVC usando hardware e assim esperando-se que com uma arquitetura dedicada, o *codec* possa alcançar taxas de processamento em tempo real para vídeos HD, além de reduzir consumo e aplicações para sistemas embarcados.

Falando um pouco mais sobre aplicações que o padrão se propõe a resolver, as aplicações voltadas para transmissão de TV Digital se encaixam perfeitamente com a capacidade que o H.264/AVC apresenta para alcançar as altas taxas de compressão

necessárias. É visível o esforço para gerar produtos voltados para transmissão de TV Digital, como *set-top Boxes*, *SoC*s, etc, voltados para essa aplicação (RAMOS, 2008).

Dentro desse escopo, o presente trabalho está inserido no contexto da construção de um codificador seguindo o padrão H.264/AVC. Esse codec está também inserido no esforço que o grupo de TV Digital da UFRGS está realizando para a implementação do Sistema Brasileiro de Televisão Digital (SBTVD). O codificador H.264/AVC que o grupo de pesquisa está se propondo a implementar é capaz de processar vídeos em alta definição (1920x1080) a taxas de 30 quadros por segundo.

Assim sendo, o trabalho aqui proposto pretende implementar e validar um codificador de entropia CAVLC (*Context-Based Variable Lenght Coding*), sendo o CAVLC uma das ferramentas de inovação do padrão H.264/AVC que são usadas dentro do codificador do padrão. O CAVLC consegue tirar proveito de certos padrões constantes que o código tende a apresentar ao longo do processamento e, assim, comprimir mais ainda a representação dos bits que forma o código de vídeo.

Esse trabalho se propõe a apresentar uma arquitetura para o CAVLC em hardware, usando linguagem de descrição de hardware VHDL, que consiga suportar vídeos em alta definição (1920 x1080) a taxas de tempo real (30 fps). Em um contexto maior, o CAVLC foi implementado pensando-se na sua futura integração com o preditor Intra Quadros e o Loop de Transformadas e Quantização do grupo de pesquisa da TV Digital da UFRGS e da UFPel (DINIZ, 2009) (SAMPAIO,2009). Assim sendo, foi também pensada uma estrutura de *Buffer* intermediário entre os demais módulos e o CAVLC para interface entre eles.

Nesse trabalho, foram propostas melhorias não encontradas até então na literatura para processar o algoritmo CAVLC em hardware, como, por exemplo, processar dois coeficientes ao mesmo tempo no primeiro estágio do processamento, além de algumas melhorias, como processar em paralelo alguns elementos sintáticos do CAVLC ao invés de apenas um deles.

O texto dessa dissertação está assim organizado: no capítulo 2 será apresentada uma visão geral sobre os conceitos de compressão de vídeo digital e sobre o padrão H.264/AVC, focado mais no codificador do padrão e em alguns aspectos importantes a serem considerados na codificação de entropia CAVLC. No capítulo 3, será apresentado mais especificamente o algoritmo de entropia CAVLC e os trabalhos encontrados na literatura sobre o assunto. No capítulo 4, será mostrado a arquitetura de hardware do *Buffer* intermediário e do componente que implementa o algoritmo CAVLC. No capítulo 5 serão apresentados os resultados e as comparações deste trabalho com outros encontrados na literatura. O capítulo 6 conclui essa dissertação e discute prováveis trabalhos futuros de investigação e desenvolvimento seguindo o escopo desse texto.

# 2 CONCEITOS DE COMPRESSÃO DE VÍDEO E O PADRÃO DE CODIFICAÇÃO H.264/AVC

Esse capítulo apresentará alguns conceitos importantes para codificação de vídeo digital, as quais serão fundamentais para o entendimento do CAVLC, e, além disso, apresentará uma introdução ao padrão H.264/AVC de compressão de vídeo digital, sendo esse o padrão onde o escopo do presente trabalho está inserido.

## 2.1 Conceitos de Compressão de Vídeo Digital

Um vídeo digital corresponde a uma seqüência de imagens estáticas sendo mostradas ao espectador uma após a outra a uma taxa que gere a sensação de movimento real. Cada imagem dessas é formada por centenas ou milhares de *pixels*. Já cada *pixel* pode ser formado por uma ou mais componentes (como no caso mais comum, as componentes RGB - *Red*, *Green* e *Blue*). A menor unidade dentro de uma imagem são as amostras para cada uma dessas componentes de cor, de acordo com o espaço de cores da imagem processada.

A compressão de um vídeo é, então, basicamente a busca e a eliminação por redundâncias entre essas amostras, que se pode dar entre uma das três formas seguintes:

- Redundância espacial: semelhanças que são encontradas em *pixels* dentro de uma mesma imagem.

- Redundância temporal: semelhanças encontradas em *pixels* entre imagens diferentes.

- Redundância entrópica: probabilidade de certos símbolos sempre acontecerem ou acontecerem geralmente de determinada forma, que possibilite sua representação de uma forma mais compacta.

Além dessas três, podemos considerar a redundância visual subjetiva do ser humano, onde determinadas componentes são menos sensíveis a variações ao olho humano, podendo ser representadas também de forma mais compacta (GONZALEZ, 2003).

Considerando já o escopo do padrão H.264/AVC, cada pixel de imagem do vídeo é representado no espaço de cores YCbCr, onde Y corresponde à luminância, Cb à crominância azul e Cr à crominância vermelha (MIANO, 1999). Essa forma de representação apresenta algumas vantagens em relação a tradicional forma RGB, pois no espaço de cores YCbCr cada componente possui um grau de correlação com as demais muito menor que em relação ao RGB (RICHARDSON, 2003), fazendo com que possa haver paralelização e divisão do processamento de cada uma delas para a compressão de vídeo.

Além disso, voltando ao tema de redundância visual subjetiva, o olho humano é muito mais sensível a variações de luminância do que em relação aos componentes de crominância, isso devido ao maior número de bastonetes (células do olho humano responsáveis pela detecção do nível de luminosidade da visão) em relação ao número de cones (células do olho humano responsáveis pela detecção dos níveis de cores da visão) (GONZALEZ, 2003). Assim sendo, é possível haver uma sub-representação dos componentes de crominância em relação ao de luminância, sem que o espectador perceba perda de qualidade no vídeo que ele está vendo.

Um exemplo do que foi dito no parágrafo anterior é a sub-amostragem de componentes do espaço de cor. Por exemplo, pode-se considerar que para cada conjunto de 4 amostras Y, tem-se o mesmo número de amostras Cr e Cb. Nesse exemplo não existe sub-amostragem, pois todos os *pixels* possuem a mesma quantidade de amostras para cada componente (essa forma de representação recebe a nomenclatura 4:4:4). Agora, considerando outro exemplo, onde para cada 4 amostras da componente Y, tem-se 1 de Cr e 1 de Cb, tem-se uma redução significativa no número de dados para representar uma mesma imagem (50%) (AGOSTINI, 2007) e essa sub-amostagem (cuja nomenclatura é 4:2:0) não faz o vídeo ter perdas significativas ao olho humano, pelo motivo apresentado no parágrafo anterior.

A redundância entrópica, que é o foco desse trabalho, visto que o CAVLC é um codificador de entropia, funciona considerando que os símbolos que são mais freqüentes possuem códigos menores. Já os que são mais raros, têm códigos maiores. Assim, há uma compressão na representação final da sequência de bits.

Ainda um último conceito importante dentro do escopo de codificação de vídeo é o de codificação com perdas (*lossy*) e sem perdas (*lossless*). Existem tipos de codificação onde o código final, ao ser reconstruído, não possuirá a mesma representação de dados como o formato original, mas, espera-se que essa perda de dados não represente perda significativa de qualidade subjetiva dos dados originais. Já em uma codificação sem perdas, os dados originais são reconstruídos, após a codificação, e apresentam o mesmo formato que anteriormente. No caso específico do CAVLC, ele é um codificador de entropia *lossless*, mas o conceito de *lossy* é importante, pois alguns componentes dentro do codificador H.264/AVC possuem perdas e eles estão dentro do fluxo de dados anterior ao CAVLC.

Na próxima seção, será apresentada uma introdução ao padrão H.264/AVC, além de uma pequena explicação sobre os módulos que compõem seu *codec*, dando ênfase aos módulos que possuem relação direta com o CAVLC e aos conceitos apresentados nessa seção.

# 2.2 Padrão para Codificação de Vídeo H.264/AVC

O padrão H.264/AVC surgiu da união do grupo de codificação de vídeo da ITU-T (VCEG -Video Coding Experts Group) (ITU-T, 2008) e do grupo de imagens em movimento da ISO/IEC (MPEG- Motion Picture Experts Group) (ISO/IEC, 2010), sob o nome de JVT (Joint Video Team) (ITU-T, 2010) em 2003 (ITU-T, 2003). Essa primeira versão do padrão contemplava três Perfis diferentes, que serão explicitados mais adiante nesse texto: Baseline, Main e Extended.

Já em 2005, buscando aplicações de nível mais profissional e de mais alta qualidade, foram incorporados ao padrão mais quatro perfis, todos agrupado sob a nomenclatura de

perfis *High* (ITU-T, 2005). Esse adendo é conhecido como *Fidelity Range Extensions* (FRExt) (ITU-T,2004).

A maior estrutura que não possui dependências com as demais dentro do padrão H.264/AVC é o chamado *Slice*. Cada imagem dentro de um vídeo pode ser composta por um ou mais *Slices* (PURI, 2004). Os *Slices* podem ser de cinco tipos diferentes, definidos pelo padrão: I (intra), P (preditivo), B (bi-preditivo) SI (*Switch* Intra) e SP (*Switch* Preditivo). Cada tipo de *Slice* corresponde a um determinado tipo de codificação entre espacial ou temporal: os *slices* I são relacionados à codificação Intraquadros, já os *slices* P e B são relacionados à predição Inter-quadros ou Intra-quadros, no caso dos *slices* P. Já os *slices* SI e SP são tipos especiais usados apenas no perfil *Extented* do padrão para situações onde a mudança no fluxo de bits (como, por exemplo, situações de *fast-forward* num vídeo) (ITU-T, 2003).

Cada *Slice* é formado por seqüências de macroblocos. Os chamados macroblocos são sequências de 16x16 de amostras das componentes de cor. No caso do padrão H.264/AVC, para os três perfis originais (*Baseline*, *Main* e *Extended*), havia a sub-amostragem 4:2:0 e, assim, sendo, para cada macrobloco de luminância 16x16 tem-se um macrobloco 4x4 para a crominância azul (Cb) e um macrobloco 4x4 para a crominância vermelha (Cr). No adendo FRExt, os novos perfis *High* podiam sofrer sub-amostragem diferentes, como a 4:2:2 e a 4:4:4, mas essas fogem ao escopo desse trabalho.

O tipo de cada macrobloco está atrelado ao tipo do *slice* ao qual ele pertence: *slices* tipo I podem conter apenas macroblocos tipo I; *slices* tipo P podem conter macroblocos do tipo P e I; *slices* tipo B podem conter macroblocos do tipo B e I; e os *slices* do tipo SI e SP são análogos aos do tipo I e P, respectivamente. Macroblocos do tipo I usam codificação intra-quadros, ou seja, usando apenas amostras dentro do mesmo quadro ao qual pertecem. Macroblocos do tipo P e B usam codificação inter-quadros, sendo que os do tipo P usam apenas um quadro como referência e os do tipo B usam até dois quadros (ITU-T, 2003).

#### 2.2.1 Perfis e Níveis do Padrão H.264/AVC

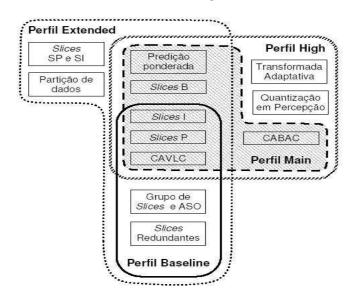

O padrão H.264/AVC, em sua primeira versão, possuía três perfis originais: *Baseline*, *Main* e *Extended* (ITU-T, 2003). Para cada perfil, existe um grupo de funcionalidades e aplicações que melhor se adequa a cada um, de acordo com suas especificações.

O perfil *Baseline* se adequa a aplicações como videotelefonia, videoconferência e vídeo sem fio. É o perfil mais simples dos criados, voltado para aplicações que não exijam tanta qualidade. Suporta predição tanto intra quanto inter-quadros (usando apenas *slices* tipo I e P) e codificação de entropia CAVLC. O perfil *Main* é voltado a aplicações mais robustas, como transmissão de televisão e armazenamento de vídeo. Possui como adendos em relação ao *Baseline*, o suporte a vídeo entrelaçado, *slices* tipo B, predição ponderada e codificação de entropia CABAC. Já o perfil *Extended*, voltado para aplicações de *streaming* de vídeo possui habilidades especiais em relação ao chaveamento de fluxo de dados (*slices* tipo SI e SP) e algumas funcionalidades para melhorar a resiliência a erros, usando particionamento de dados, embora ele não possua os adendos do perfil *Main* em relação ao perfil *Baseline* (ITU-T, 2003).

É importante citar que todos os perfis acima citados possuem duas semelhanças entre si, que é a sub amostragem 4:2:0 no espaço de cores YCbCr e amostras de 8 bits de largura.

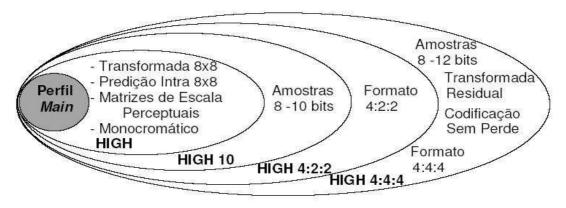

Mais tarde, como já foi dito nesse texto, foram adicionados os quatro perfis FRExt ao padrão. Eles são conhecidos coletivamente como perfis *High* (SULLIVAN, 2004). Esses perfis são voltados para aplicações profissionais com resoluções mais elevadas e exigência de alta fidelidade de imagem. O primeiro deles, nomeado simplesmente como *High*, além de já possuir todas as funcionalidades do perfil *Main*, possui também predição intra-quadros e transformadas 8x8. Permite, também, suporte para imagens monocromáticas, ou seja, sub-amostragem 4:0:0. O Perfil *High 10*, além das funcionalidades do *High*, ainda permite que a largura de representação para cada amostra tenha 9 ou 10 bits. O *High 4:2:2*, além das funcionalidades do anterior, também agrega a possibilidade de sub-amostragem de cores 4:2:2. Por fim, o *High 4:4:4*, além de todas as funcionalidades dos anteriores, também permite tamanho de amostras de 11 e 12 bits, vídeos sem sub-amostragem (4:4:4), transformada residual de cores (conversão do RGB para YCgCo) e opção de codificação sem perdas. Nas figuras 2.1 e 2.2 estão resumidas as funcionalidades para cada perfil de acordo com o perfil imediatamente anterior, desde o *Baseline* até o *High*.

Figura 2.1: Relação entre os perfis *Baseline*, *Main*, *Extended* e *High* (AGOSTINI, 2007).

Figura 2.2: Relação entre os perfis *FRExt* (ZATT, 2008).

Além dos perfis, o padrão define, também, 16 níveis, que variam de acordo com a taxa de processamento para cada perfil acima mencionado. A especificação de cada nível pode ser visto na tabela 2.1.

Tabela 2.1: Níveis do padrão H.264/AVC.

| Nível | Máximo de<br>Macrobloco/s | Tamanho<br>Máximo de<br>Frame<br>(macroblocos) | Máximo<br>Bitrate-<br>Baseline,<br>Extended<br>e Main | Máximo<br>Bitrate<br>High | Máximo<br>Bitrate<br>High 10 | Máximo<br>Bitrate<br>High<br>4:2:2 e<br>4:4:4 | Resolução<br>Máxima @ Taxa<br>de Frame                                                                        |

|-------|---------------------------|------------------------------------------------|-------------------------------------------------------|---------------------------|------------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| 1     | 1485                      | 99                                             | 64 Kbits/s                                            | 80 Kbits/s                | 192 Kbits/s                  | 256 Kbits/s                                   | 128x96@30.9 (8)<br>176x144@15.0 (4)                                                                           |

| 1b    | 1485                      | 99                                             | 128 Kbits/s                                           | 160<br>Kbits/s            | 384 Kbits/s                  | 512 Kbits/s                                   | 128x96@30.9 (8)<br>176x144@15.0 (4)                                                                           |

| 1.1   | 3000                      | 396                                            | 192 Kbits/s                                           | 240<br>Kbits/s            | 576 Kbits/s                  | 768 Kbits/s                                   | 176x144@30.3 (9)<br>320x240@10.0 (3)<br>352x288@7.5 (2)                                                       |

| 1.2   | 6000                      | 396                                            | 384 Kbits/s                                           | 480<br>Kbits/s            | 1152<br>Kbits/s              | 1536<br>Kbits/s                               | 320x240@20.0 (7)<br>352x288@15.2 (6)                                                                          |

| 1.3   | 11880                     | 396                                            | 768 Kbits/s                                           | 960<br>Kbits/s            | 2304<br>Kbits/s              | 3072<br>Kbits/s                               | 320x240@36.0 (7)<br>352x288@30.0 (6)                                                                          |

| 2     | 11880                     | 396                                            | 2 Mbits/s                                             | 2.5<br>Mbits/s            | 6 Mbits/s                    | 8 Mbits/s                                     | 320x240@36.0 (7)<br>352x288@30.0 (6)                                                                          |

| 2.1   | 19800                     | 792                                            | 4 Mbits/s                                             | 5 Mbits/s                 | 12 Mbits/s                   | 16 Mbits/s                                    | 352x480@30.0 (7)<br>352x576@25.0 (6)                                                                          |

| 2.2   | 20250                     | 1620                                           | 4 Mbits/s                                             | 5 Mbits/s                 | 12 Mbits/s                   | 16 Mbits/s                                    | 352x480@30.7(10)<br>352x576@25.6 (7)<br>720x480@15.0 (6)<br>720x576@12.5 (5)                                  |

| 3     | 40500                     | 1620                                           | 10 Mbits/s                                            | 12.5<br>Mbits/s           | 30 Mbits/s                   | 40 Mbits/s                                    | 352x480@61.4 (12)<br>352x576@51.1 (10)<br>720x480@30.0 (6)<br>720x576@25.0 (5)                                |

| 3.1   | 108000                    | 3600                                           | 14 Mbits/s                                            | 17.5<br>Mbits/s           | 42 Mbits/s                   | 56 Mbits/s                                    | 720x480@80.0 (13)<br>720x576@66.7 (11)<br>1280x720@30.0 (5)                                                   |

| 3.2   | 216000                    | 5120                                           | 20 Mbits/s                                            | 25 Mbits/s                | 60 Mbits/s                   | 80 Mbits/s                                    | 1280x720@60.0 (5)<br>1280x1024@42.2 (4)                                                                       |

| 4     | 245760                    | 8192                                           | 20 Mbits/s                                            | 25 Mbits/s                | 60 Mbits/s                   | 80 Mbits/s                                    | 1280x720@68.3 (9)<br>1920x1080@30.1 (4)<br>2048x1024@30.0 (4)                                                 |

| 4.1   | 245760                    | 8192                                           | 50 Mbits/s                                            | 50 Mbits/s                | 150<br>Mbits/s               | 200<br>Mbits/s                                | 1280x720@68.3 (9)<br>1920x1080@30.1 (4)<br>2048x1024@30.0 (4)                                                 |

| 4.2   | 522240                    | 8704                                           | 50 Mbits/s                                            | 50 Mbits/s                | 150<br>Mbits/s               | 200<br>Mbits/s                                | 1920x1080@64.0 (4)<br>2048x1080@60.0 (4)                                                                      |

| 5     | 589824                    | 22080                                          | 135 Mbits/s                                           | 168.75<br>Mbits/s         | 405<br>Mbits/s               | 540<br>Mbits/s                                | 1920x1080@72.3 (13)<br>2048x1024@72.0 (13)<br>2048x1080@67.8 (12)<br>2560x1920@30.7 (5)<br>3680x1536@26.7 (5) |

| 5.1   | 983040                    | 36864                                          | 240 Mbits/s                                           | 300<br>Mbits/s            | 720<br>Mbits/s               | 960<br>Mbits/s                                | 1920x1080@120.5 (16)<br>4096x2048@30.0 (5)<br>4096x2304@26.7 (5)                                              |

#### 2.2.2 Codec H.264/AVC

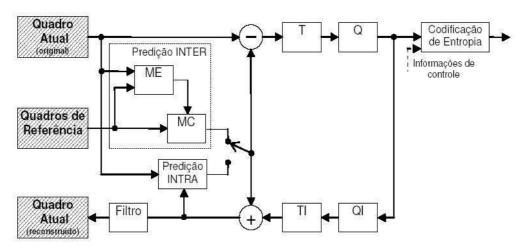

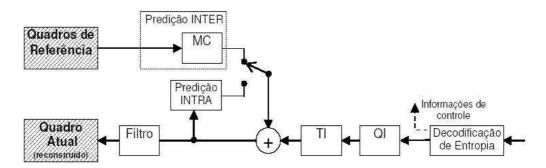

O codec do padrão H.264/AVC é formado por diversos módulos, onde cada um é responsável por uma funcionalidade para comprimir/descomprimir o vídeo digital a ser processado. Como já foi dito anteriormente, a codificação de vídeo nada mais é que a busca por redundâncias entre os quadros processados, fazendo assim com que a informação redundante seja processada e mandada adiante no fluxo de uma forma mais compacta, gerando mais informações de vídeo com a menor taxa de bits possíveis e mantendo a qualidade dentro do esperado. As figuras 2.3 e 2.4 mostram os principais blocos do codificador e decodificador do padrão H.264/AVC e, na sequência, haverá uma breve explicação sobre os módulos que compõe o codec, dando uma ênfase maior àqueles que pertencem ao fluxo de dados do CAVLC.

Figura 2.3: Diagrama de Blocos do Codificador H.264/AVC (AGOSTINI, 2007).

Figura 2.4: Diagrama de Blocos do Decodificador H.264/AVC (AGOSTINI, 2007).

É importante notar que o decodificador está replicado dentro do próprio codificador, pois este precisa, durante o fluxo de codificação, reconstruir os quadros a serem usados como referência para a Inter-predição, que será visto a seguir.

#### 2.2.2.1 Estimação de Movimento (ME)

A predição Inter-quadros, é responsável pela busca de redundâncias temporais entre o quadro atual e demais quadros já processados no fluxo de um vídeo. Existem dois sub-blocos, cada um responsável por uma funcionalidade da predição Inter: a Estimação de Movimento (ME) e a Compensação de Movimento (MC). Importante ressaltar que são esses os blocos que garantem as maiores fontes de ganho no padrão H.264/AVC (WIEGANG, 2003) (RICHARDSON, 2003).

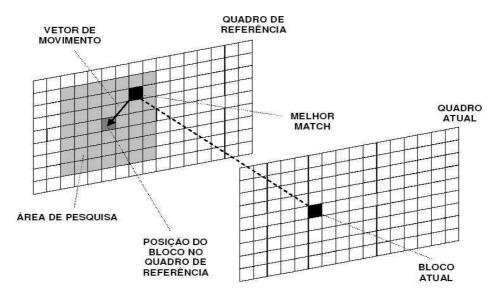

Falando primeiramente da ME (presente apenas no codificador), esse sub-bloco é o que apresenta a maior complexidade dentre todos os blocos do padrão (PURI, 2004). Sua funcionalidade é buscar dentro de um macrobloco (tipo P ou B) que está sendo processado, o macrobloco de *pixels* que mais se assemelha a esse, dentre um ou mais quadros já processados no fluxo de dados. Pode fazer uso de uma série de algoritmos a fim de usar o melhor casamento, como pode ser visto em (PORTOa, 2008) e (PORTOb, 2008). Assim que a melhor possibilidade de macrobloco é encontrada, é calculado um vetor de movimento, que indica o deslocamento da posição desse bloco no quadro de referência de onde ele foi tirado. Esse processo está explicitado na figura 2.5.

Figura 2.5: Cálculo de um vetor de movimento (PORTO, 2008).

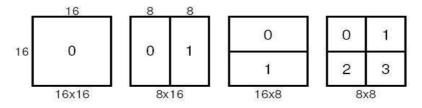

Outra inovação que merece destaque nesse módulo é a possibilidade de terem-se blocos de tamanhos variáveis. Assim sendo, é possível se ter o melhor casamento variando de acordo com o tamanho do macrobloco escolhido para se calcular o vetor de movimento. Os tamanhos de bloco podem ser de 16x16, 8x16, 16x8 e 8x8. Quando o bloco assume o valor de 8x8, ele ainda pode ser subdivido em outras partições (8x8, 8x4, 4x8 e 4x4) (RICHARDSON, 2003). Para cada partição de macrobloco ou submacrobloco, ter-se-á então um vetor de movimento específico a ser calculado. As figuras 2.6 e 2.7 explicitam os tamanhos variáveis de bloco e sub-blocos.

Figura 2.6: Divisões possíveis para um macrobloco (AGOSTINI, 2007).

Figura 2.7: Divisões do sub-macrobloco 8x8 (AGOSTINI, 2007).

#### 2.2.2.2 Compensação de Movimento (MC)

O bloco de Compensação de Movimento trabalha de forma complementar ao bloco de Estimação de Movimento apresentado anteriormente. Sua função é, a partir do vetor de movimento calculado pela ME, copiar os blocos que possuem melhor casamento entre quadros já processados para montar o quadro predito e, assim. subtrair desse quadro o quadro atual para gerar os resíduos que serão enviados para a etapa de transformada. O processo de MC está presente tanto no codificador quanto no decodificador do padrão. Mais informações desse módulo fogem ao escopo dessa dissertação, mas podem ser encontradas em (ZATT,2008) e (AZEVEDO, 2006).

#### 2.2.2.3 Predição Intra-quadros

Esse módulo é o responsável pela detecção de redundâncias espaciais entre os macroblocos que estão sendo processados (tipo I). Para o cálculo das redundâncias, são usados como referência os *pixels* imediatamente acima e a esquerda do bloco que está sendo processado atualmente. A predição Intra quadros está presente tanto na codificação quanto na decodificação do padrão H.264/AVC.

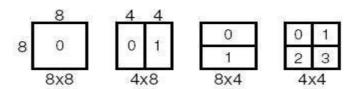

A predição Intra Quadros pode tanto ser aplicada em blocos de *pixels* de luminância e crominância 4x4 (macroblocos I4MB) ou de luminância 16x16 (macroblocos I16MB). Para os macroblocos I4MB existem nove diferentes modos para o cálculo da predição, enquanto que para os macroblocos I16MB existem quatro modos (RICHARDSON, 2003).

A Figura 2.8 apresenta de forma visual os *pixels* vizinhos a um bloco 4x4 genérico, que serão usados para o cálculo de sua predição Intra. As amostras acima e a esquerda, nomeadas com as letras de A até M, foram já calculadas e reconstruídas antes do processamento do bloco atual na figura.

| М | Α | В | С | D | Е  | F | G | Н |

|---|---|---|---|---|----|---|---|---|

|   | а | b | С | d |    |   |   |   |

| J | е | f | g | h | 0  |   |   |   |

| K | i | j | k | 1 | G. |   |   |   |

| L | m | n | 0 | р | 0  |   |   |   |

Figura 2.8: Amostras a serem usadas no cálculo da predição Intra para um bloco 4x4 (AGOSTINI, 2007).

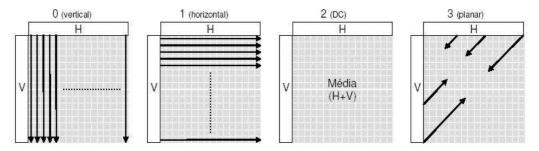

A Figura 2.9 apresenta os nove modos de cálculo para macroblocos I4MB. Os modos 0 e 1 fazem uma extrapolação dos valores acima e a esquerda do bloco atual, respectivamente, e replica os valores para as linhas ou colunas do bloco atual, exatamente no sentindo mostrado na figura 2.9. O modo 2 faz uma média entre os valores referências das bordas e copia esse valor para todas as posições do bloco atual. Já os demais modos, de 3 até 8, fazem uma média ponderada das amostras das bordas e alocam esses valores para o bloco atual, de acordo com o sentido das flechas mostrados também na figura 2.9 (ITU-T, 2003).

Figura 2.9: Os nove modos de predição Intra-quadros para macroblocos I4MB (AGOSTINI, 2007).

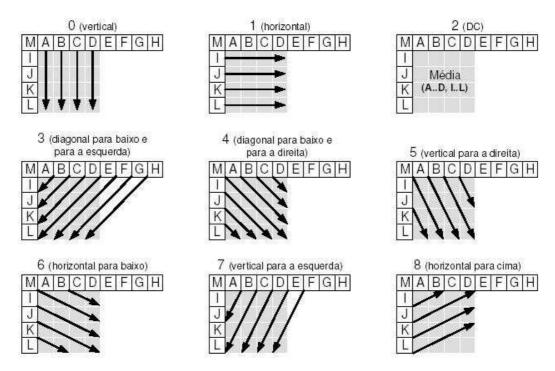

Já no caso em que a Intra-predição opta pelo modo onde teremos os macroblocos completos para serem preditos os I16MB, ter-se-á então quatro possíveis modos de predição, como mostrados na figura 2.10. Os modos 0 e 1 replicam os valores de referência acima e a esquerda respectivamente para todas a posições respectivas no macrobloco que está sendo predito, como visto na figura 2.12. O modo 2 faz uma média dos valores de referência das bordas e copia esse valor para todas as posições do macrobloco atual. Já o modo 3 aplica uma função linear usando as amostras acima e a esquerda para o cálculo dos valores preditos a serem usados em cada posição do macrobloco processado. A fórmula para esse cálculo foge ao escopo desse texto, mas pode ser encontrada com maiores detalhes em (DINIZ, 2009).

Figura 2.10: Os quatro modos de predição Intra-quadros para macroblocos I16MB (AGOSTINI, 2007).

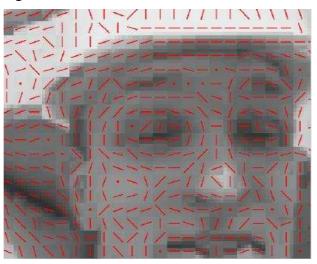

Como um exemplo mais visual, pode-se ver as figuras 2.11 e 2.12, onde um quadro da seqüência de vídeo *Foreman* QCIF foi usado e as linhas representam o sentido dos modos usados para cada macrobloco ou bloco da figura, que foram mostrados nas duas figuras anteriores desse texto. Por fim, na figura 2.12, tem-se o resultado final para um quadro completo da predição Intra-quadros, tendo como saída os resíduos gerados. Esse

exemplo é importante para notar-se como, mais adiante, irá funcionar a codificação de entropia CAVLC, que age sobre esses resíduos.

Figura 2.11: Aplicação dos modos Intra sobre um quadro de vídeo exemplo (DINIZ, 2009).

Figura 2.12: Resultado da predição Intra. Quadro original à esquerda e quadro de resíduos à direita (DINIZ, 2009).

#### 2.2.2.4 Transformadas e Transformadas Inversas

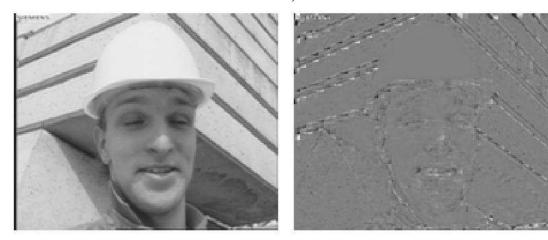

As transformadas são responsáveis por processar os resíduos gerados na predição e reorganizar os dados de uma forma que eles assumam um comportamento onde as redundâncias entrópicas dos dados serão melhor destacadas (no caso, elas estão presentes apenas no codificador). Como exemplo disso, pode-se ver a figura 2.13, onde de um bloco 4x4 retirado de uma amostra da imagem 2.12 original, tem-se, de um lado, o bloco original e, do outro, o bloco após a sofrer a transformada. Como pode ser observado, os dados de mais alta freqüência acabam por serem zerados, fazendo com que os valores diferentes de zero tendam a se concentrar no canto superior esquerdo do bloco (baixas freqüências). Isso será importante mais adiante para o aproveitamento do algoritmo CAVLC.

As transformadas podem ser de três tipos: *Hadamard* para blocos 4x4 DC formados quando há a predição Intra 16x16; *Hadamard* para bloco 2x2 formados por coeficientes

DC de crominância; e Transformada inteira baseada na DCT-2 (*Discrete Cosine Transform*) para os demais blocos 4x4.

Figura 2.13: Bloco 4x4 ao sofrer processo de transformada: à esquerdas o bloco original e à direita após o processo.

A título de informação, em (1) temos a fórmula da DCT-2D aplicada aos blocos 4x4 de AC de luminância e crominância, onde  $\mathbf{X}$  é a matriz 4x4 de entrada,  $\mathbf{C}_{\mathbf{f}}$  é a matriz FDCT inteira em uma dimensão,  $\mathbf{C}_{\mathbf{f}}$  é a transposta da matriz DCT,  $\mathbf{E}_{\mathbf{f}}$  é a matriz de fatores de escala, o símbolo  $\otimes$  é uma multiplicação escalar e  $\mathbf{a}$  e  $\mathbf{b}$  são constantes definidas em (2).

$$Y = C_f X C_f^T \otimes E_f = \begin{bmatrix} 1 & 1 & 1 & 1 \\ 2 & 1 & -1 & -2 \\ 1 & -1 & -1 & 1 \\ 1 & -2 & 2 & -1 \end{bmatrix} \begin{bmatrix} X & \begin{bmatrix} 1 & 2 & 1 & 1 \\ 1 & 1 & -1 & -2 \\ 1 & -1 & -1 & 2 \\ 1 & -2 & 2 & -1 \end{bmatrix} \otimes \begin{bmatrix} a^2 & \frac{ab}{2} & a^2 & \frac{ab}{2} \\ \frac{ab}{2} & \frac{b^2}{4} & \frac{ab}{2} & \frac{b^2}{4} \\ a^2 & \frac{ab}{2} & a^2 & \frac{ab}{2} \\ \frac{ab}{2} & \frac{b^2}{4} & \frac{ab}{2} & \frac{b^2}{4} \end{bmatrix}$$

$$a = \frac{1}{2}, \qquad b = \sqrt{\frac{2}{5}}$$

$$(2)$$

Já em (3), tem-se a transformada *Hadamard* 4x4 que é aplicada ao bloco DC de luminância, após ele sofrer a DCT-2D mostrada em (1), quando ocorre o modo Intra 16x16 (macroblocos I16MB). **W**D é o bloco de resíduos DC após sofrer a DCT-2D e **Y**D é o resultado da *Hadamard*.

Por fim em (4) tem-se a *Hadamard* 2x2 usado nos blocos DC de crominância, onde **W**<sub>D</sub> são os blocos DC e **W**<sub>QD</sub> representa o resultado da *Hadamard* 2x2.

$$W_{QD} = \begin{pmatrix} \begin{bmatrix} 1 & 1 \\ 1 & -1 \end{bmatrix} \begin{bmatrix} W_D \end{bmatrix} \begin{bmatrix} 1 & 1 \\ 1 & -1 \end{bmatrix}$$

(4)

Já no caso das transformadas inversas, presentes tanto no codificador como no decodificador, seu propósito é reverter o processo gerado pelas transformadas acima apresentadas.

Em (5), temos a IDCT-2D, aplicada sobre os blocos 4x4 análogos aos que sofreram o processo de transformada normal, explicada antes nesse texto. Assim, temos que  $\mathbf{X}$  é matriz de entrada,  $\mathbf{C}$ i é matriz IDCT inteira em uma dimensão  $\mathbf{C}$ i é a transposta da IDCT,  $\mathbf{E}$ i é matriz de escala. Da mesma forma que em (1), o símbolo  $\otimes$  representa uma multiplicação escalar e  $\mathbf{a}$  e  $\mathbf{b}$  possuem os mesmos valores que em (2).

Em (6), é apresentado o cálculo para a transformada inversa da *Hadamard* 4x4, usada em blocos DC de luminância, quando o modo Intra 16x16 ocorre. A única diferença em relação a (3) é que (6) não possui divisão por dois.

Já o cálculo da inversa da *Hadamard* 2x2, aplicada aos blocos DC de crominância, possui a mesma fórmula apresentada em (4).

#### 2.2.2.5 Quantização e Quantização Inversa

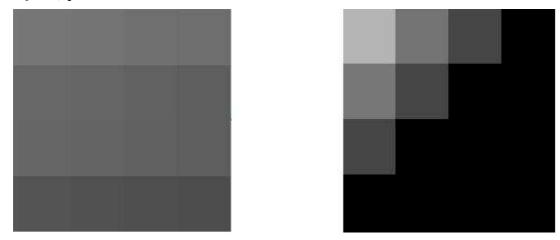

Os coeficientes, após passarem pelo processo de transformada, sofrem uma quantização escalar, determinada por um parâmetro *QP* (*Quantization Parameter*) (RICHARDSON, 2003). Nesse bloco ocorre a única codificação com perdas no processo do H.264/AVC e ele se encontra presente apenas no codificador do padrão.

Os resíduos, após sofrerem o processo de transformada, assumem, dentro dos blocos, um aspecto como o que foi mostrado na figura 2.13. Ao sofrerem o processo de quantização, muitos dos valores que estavam próximos a zero tendem a ser zerados e os demais tem seu valor diminuído em função do *QP*. Assim, como pode ser visto na figura 2.14, os blocos assumem um aspecto onde tendem a ter apenas no canto superior esquerdo (baixas freqüências) valores não-zero (o que, mais uma vez está sendo frisado, será importante para o algoritmo CAVLC).

Figura 2.14: Bloco 4x4 ao sofrer processo de quantização: à esquerda o bloco após sofrer a transformada e à direita após a quantização.

Já a quantização inversa, presente tanto no codificador como no decodificador, reverte o processo gerado pela quantização. Como a quantização normal insere perdas (devido aos coeficientes que são zerados e, assim, não sendo possível recuperar seu valor original) o resultado da quantização inversa pode gerar deformações nos quadros reconstruídos; no entanto, existe um módulo especializado em tratar dessa situação, que será apresentado na seqüência.

#### 2.2.2.6 Filtro Redutor de Efeito de Bloco

Esse filtro atua sobre o efeito de blocagem que acaba por acontecer quando, por exemplo, é aplicado um *QP* muito elevado nos macroblocos, suavizando assim esse efeito num quadro antes que ele seja armazenado para ser usado como futura referência, ou antes de ele ser exibido. Na figura 2.15 tem-se um exemplo de uma imagem que, devido ao passo de quantização elevado, sofreu um efeito de bloco e, ao lado, o resultado desse quadro após passar por um filtro redutor do efeito de bloco.

Uma novidade nesse filtro é a capacidade que ele tem em detectar uma aresta normal da imagem em relação a um efeito de bloco gerado devido ao alto passo de quantização aplicado. O filtro possui 5 forças para filtragem (desde a força 0, onde não há filtragem, até a força 4, filtragem máxima). Para mais informações sobre o filtro de deblocagem, consultar (ROSA, 2009).

Figura 2.15: À esquerda imagem sofrendo o efeito de bloco; à direita, imagem ao passar pelo filtro de deblocagem (ROSA, 2009).

#### 2.2.2.7 Codificação de Entropia

A codificação de entropia compacta os dados gerados nos processos anteriores da codificação usando de comportamentos constantes que tendem a acontecer no código e, assim, usar disso para representar os dados de forma menor. Pode-se utilizar três métodos para esse fim: utilizando o algoritmo *Exp-Golomb*, códigos de comprimentos variáveis (VLC - *Variable Length Coding*) e códigos binários aritméticos (BAC - *Binary Arithmetic Coding*). Como o foco dessa dissertação é um dos algoritmos para codificação de entropia (o CAVLC - *Context Adaptive Variable Length Coding*), será apresentada uma breve explanação do funcionamento e da aplicação no fluxo de dados dos demais algoritmos envolvidos na codificação de entropia: O *Exp-Golomb* e o CABAC.

O *Exp-Golomb* atua como codificador de entropia sobre as informações geradas no processo de codificação como: os vetores de movimento da Inter-predição, tipo de macrobloco, parâmetro de quantização, entre outros, como pode ser visto em (RICHARDSON, 2003). É importante frisar que a codificação *Exp-Golomb* é complementar à CAVLC, visto que essa última atua apenas sobre os resíduos da Intra Predição e a primeira sobre todas as demais informações geradas no processo de codificação.

A codificação *Exp-Golomb* (SOLOMON, 2000) segue as fórmulas abaixo especificadas. Em (7). tem-se o código gerado para cada elemento:

$$C\acute{o}digo = \begin{bmatrix} M \ zeros \end{bmatrix} \begin{bmatrix} 1 \end{bmatrix} \begin{bmatrix} INFO \end{bmatrix}$$

<sup>(7)</sup>

M corresponde ao número de zeros que antecede o primeiro valor 1 no código. *M* é definido em (8) como sendo:

$$M = \lfloor \log_2 \cdot (num \rfloor cod + 1) \rfloor$$

(8)

Onde *num\_cod* corresponde ao número do código. Já o campo *INFO* possui M bits e indica qual tipo de elemento está presente naquele código. *INFO* é definido em (9):

$$INFO = num\_cod + 1 - 2^{M}$$

<sup>(9)</sup>

Na tabela 2.2, temos os primeiros códigos para o algoritmo *Exp-Golomb* para exemplificar as fórmulas acima mencionadas:

Tabela 2.2: Códigos *Exp-Golomb*.

| num_cod | Código |

|---------|--------|

| 0       | 1      |

| 1       | 010    |

| 2       | 011    |

| 3       | 00100  |

| 4       | 00101  |

| 5       | 00110  |

| •••     |        |

O outro algoritmo, além do CAVLC e do *Exp-Golomb*, é o CABAC. Este algoritmo atua sobre todos os elementos sintáticos produzidos nas etapas anteriores da codificação, podendo substituir tanto o CAVLC quanto o *Exp-Golomb*, pois desempenha a função dos dois juntos. O CABAC, presente nos perfis *Main* e *High* do padrão, faz com que o ganho na compactação do código comparado ao CAVLC alcance em torno de 9% a 15% ao custo de uma maior complexidade para a codificação de entropia (MARPE, 2003).

O princípio básico do algoritmo consiste dos seguintes passos:

- Binarização: O algoritmo utiliza apenas decisões binárias, baseadas nos valores 0 ou 1 (codificação aritmética binária). Caso o símbolo não possua um valor binário, ele é binarizado, onde cada posição de um dígito binário é chamada de bin. O algoritmo segue os próximos passos para todos os bins.

- Seleção de modelos probabilísticos: Modelo de contexto consiste de um modelo probabilístico para um ou mais bins do símbolo que sofreu a binarização. Essa escolha depende do contexto, ou seja, depende dos modelos disponíveis e de estatísticas de símbolos que recentemente foram codificados. O modelo de contexto armazena as probabilidades de cada bin ser 0 ou 1 e no caso do H.264/AVC, são usados até 398 contextos diferentes (MARPE, 2003; ITU-T, 2005).

- Codificação Aritmética: o codificador aritmético codifica o bin atual usando o modelo probabilístico escolhido. As sub-faixas de valores que cada bin pode assumir, respeitando as regras da codificação aritmética, correspondem a '0' ou '1'.

- Atualização de probabilidades: o modelo probabilístico usado é atualizado de acordo com o valor do bin que foi codificado, ou seja, de acordo com o contexto atual o modelo selecionado é incrementado para o valor do bin atual (se for 0, a

ocorrência de zeros é incrementada no modelo, se for 1, a ocorrência de uns no modelo é incrementada). Para mais informações a respeito do algoritmo CABAC, consultar (DEPRA, 2009).

## 2.3 Conclusão

Neste trabalho de dissertação será focado o desenvolvimento de arquiteturas que realizam a codificação de entropia CAVLC (*Context Adaptive Variable Length Coding*). Para a compreensão do contexto geral, é importante ter presente que o objetivo deste trabalho é contribuir para o desenvolvimento de um codificador H.264/AVC em hardware. Neste capítulo, as principais características que devem ser suportadas por este codificador, em seus diferentes perfis e níveis, foram apresentadas, assim como os principais módulos dentro do *codec* do padrão, alguns dos quais sua compreensão será importante, pois eles estão dentro do fluxo de dados anterior a codificação de entropia CAVLC.

# 3 CODIFICAÇÃO DE ENTROPIA CAVLC

O algoritmo CAVLC (*Context Adaptive Variable Lenght Coding*) consiste em uma das formas de codificação de entropia presentes no padrão H.264/AVC, como já anteriormente citado. Sua lógica deriva do fato que símbolos que aparecem mais vezes durante o fluxo de codificação de determinado vídeo acabam por receber códigos menores, enquanto os símbolos menos freqüentes tendem por receber códigos maiores, assim gerando um ganho de compactação no vídeo, devido ao código de comprimento variável (RICHARDSON, 2003).

Os elementos a serem codificados pelo CAVLC também dependem do contexto para sua codificação (*Context Based*). Isso quer dizer que os códigos desses elementos sofrem influência direta de elementos já codificados durante o fluxo CAVLC.

Nesse capítulo será apresentado o algoritmo CAVLC de forma detalhada, além dos trabalhos encontrados na literatura que apresentam o estado-da-arte em relação a codificação de entropia mencionada.

## 3.1 Algoritmo CAVLC

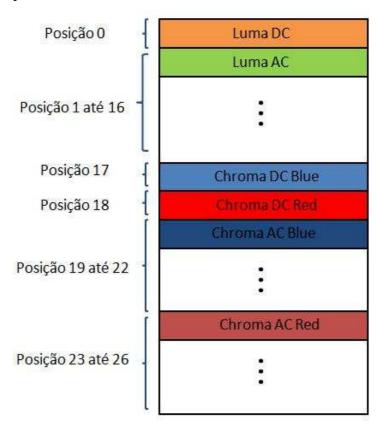

A unidade básica do algoritmo consiste de macroblocos constituídos de blocos de resíduos que podem ser de tamanho 2x2 ou 4x4. Esses blocos são, ainda, divididos em blocos de luminância (Luma) ou blocos de crominância (Chroma) Azul ou Vermelha (espaço de cores YCbCr). Cada um deles ainda pode ser dividido em blocos DC ou AC.

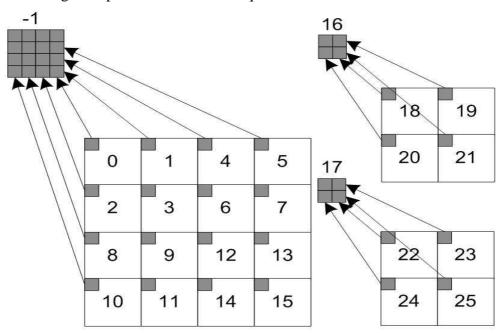

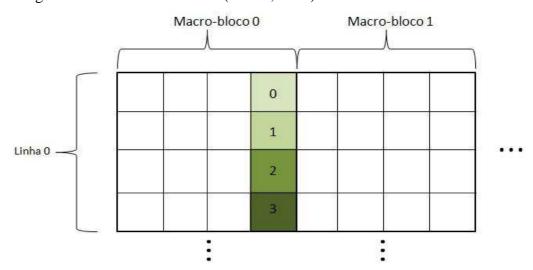

Na figura 3.1 podem-se observar as especificações acima mencionadas. Os blocos são enviados ao CAVLC na ordem mostrada na figura (Duplo Z), começando no bloco - 1 ou no bloco 0 e seguindo em ordem crescente até o bloco 25.

Os blocos 0 até 15 correspondem aos blocos Luma AC. Já o bloco -1 somente ocorre no modo de predição Intra 16x16 (ITU-T, 2003) e ele recebe, como valores, os coeficientes DC de todos os blocos Luma AC, como mostrado na figura 3.1. Quando o bloco Luma DC ocorrer, os blocos Luma AC terão apenas 15 coeficientes, visto que seus coeficientes DC já estão alocados dentro do bloco -1.

Os blocos 16 até o 25 correspondem aos blocos Chroma, sendo o bloco 16 o Chroma DC para a componente Azul e o bloco 17 o Chroma DC para a componente Vermelha. Já os blocos 18 até 21 correspondem aos Chroma AC Azuis e os blocos 22 até 25 os Chroma AC Vermelhos. Analogamente ao caso Luma DC, os blocos 16 e 17 contêm os coeficientes DC dos respectivos blocos AC. Visto que o CAVLC trabalha com sub-amostragem de 4:2:0, os macroblocos de crominância tem metade das dimensões dos macroblocos de luminância. Assim sendo, como se pode notar na figura, os blocos Chroma DC possuem dimensões 2x2. Também é importante ressaltar que, ao contrário

do caso dos Lumas, os Chromas DC sempre ocorrem, independentemente do modo predição Intra escolhido (ITU-T, 2003).

A partir da entrega dos blocos pela ordem duplo Z, como mostrado na figura citada, o CAVLC segue os passos descritos na seqüência.

Figura 3.1: Ordem Duplo-Z de entrega de blocos dentro de um macrobloco.

## 3.1.1 Ordenamento Ziguezague

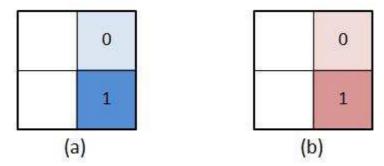

Após os processos citados anteriormente, os resíduos passam por um processo de reordenamento antes de serem propriamente codificados pelo CAVLC. Esse processo é denominado de Ziguezague, devido ao sentido que ele assume dentro dos blocos de resíduo.

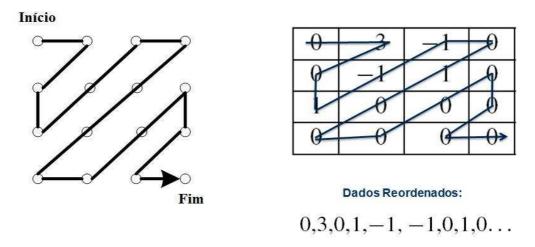

Na figura 3.2 pode-se observar um exemplo de um bloco 4x4 de coeficientes e o sentido que o ordenamento Ziguezague assume dentro dele para a passagem dos valores ao codificador de entropia.

Figura 3.2: Ordenamento Ziguezague de um bloco 4x4.

#### 3.1.2 Estatísticas dos Coeficientes

A partir do ordenamento Ziguezague, os coeficientes agora serão classificados de acordo com o seu comportamento dentro de cada bloco. Os coeficientes dentro de cada bloco a partir de agora receberam a nomenclatura de coeficientes e as características que eles apresentam serão denominadas estatísticas.

Considerando o exemplo apresentado na figura 3.2, tem-se um bloco 4x4 com 16 amostras sofrendo um ordenamento ziguezague, indicando a ordem de entrada dos dados no CAVLC. As estatísticas são assim divididas:

- *Total de Coeficientes*: corresponde ao total de coeficientes no bloco que possuem valor não-zero, independentemente do seu valor absoluto;

- Levels: corresponde ao valor de todos os coeficientes que possuem valor nãozero dentro de um bloco, exceto as que possuem valor ±1;

- *Total de Levels*: corresponde ao total de coeficientes cujo valor é não-zero dentro de um bloco, exceto as possuem valor ±1;

- *Trailing Ones*: corresponde aos coeficientes não-zero cujos valores podem ser ±1 situados no fim de um bloco, após o ordenamento ziguezague, caso existam;

- *Total de Trailing Ones*: corresponde ao total de *Trailing Ones* dentro de um bloco (limitado sempre no máximo a 3, mesmo que por ventura haja mais ±1 no fim do bloco), caso existam;

- *Total de Zeros*: corresponde ao total de coeficientes com valor zero que ocorrem antes do último coeficiente não-zero depois do ordenamento ziguezague;

- Run Befores: corresponde ao total de sequências de zeros antes de cada coeficiente com valor não-zero dentro de um bloco;

- Zeros Left: corresponde ao total de zeros entre um coeficiente não-zero até outro coeficiente não-zero;

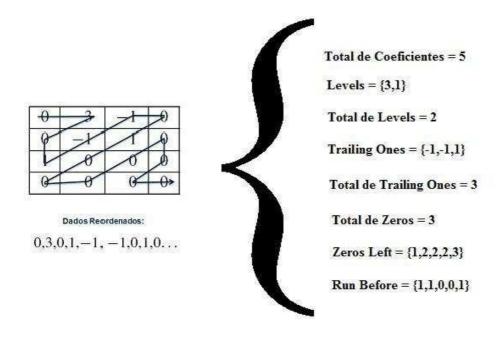

Considerando ainda o exemplo da figura 3.2, as estatísticas para o bloco são as apresentadas na figura 3.3. No caso dos valores de *Run Before* e *Zeros Left*, uma maior explicação será encontrada na seqüência.

No exemplo citado, cada coeficiente não-zero recebeu uma numeração entre 0 até 4, como pode ser visto na figura 3.4. Considerando primeiramente a estatística de *Zero Left*, para cada coeficiente não-zero, começando na ordem reversa pelo coeficiente de número 4, pode-se notar que dela até o começo dos dados existem três coeficientes cujo valor é zero. Passando agora para o coeficiente 3, vê-se que dele até o fim há agora apenas dois coeficientes cujo valor é zero, assim como para os coeficientes 2 e 1. Já o coeficiente 0 possui apenas um outro coeficiente com valor zero antes dele. Assim sendo, o vetor de valores de *Zero Left* assume a seqüência: 3,2,2,2,1 que é o que foi apresentado na figura 3.3, porém já em ordem reversa.

Figura 3.3: Estatísticas do bloco 4x4.

No caso dos *Run Befores*, usando a mesma numeração usada para os coeficientes não-zero do exemplo, começando no coeficiente 4, observa-se que entre ele e o próximo coeficiente, em ordem reversa (ou seja, o coeficiente 3) há apenas um coeficiente com valor zero. No caso do coeficiente 3 até o coeficiente 2, e do coeficiente 2 até o coeficiente 1, entre cada um deles não existe nenhum elemento com valor zero. Já entre o coeficiente 1 até o coeficiente 0, há um dado com valor zero e, finalmente, do coeficiente 0 até o começo dos dados existe, também, um coeficiente com o valor zero. Assim sendo, o vetor de *Run Before* assume os valores, respectivamente, do elemento 4 até o 0: 1,0,0,1,1, que é a seqüência de valores já apresentada na figura 3.3, mas já em ordem reversa.

O próximo passo no algoritmo consiste em codificar cada uma dessas estatísticas para os chamados elementos sintáticos do CAVLC, que serão apresentados a seguir.

$$0, 3, 0, 1, -1, -1, 0, 1, 0, \dots$$

Figura 3.4: Coeficientes não-zero numerados para estatísticas de *Run Before* e *Zeros Left*.

#### 3.1.3 Elementos Sintáticos

Os denominados elementos sintáticos do algoritmo CAVLC são a forma de codificar as estatísticas anteriormente levantadas e assim compactar o código anteriormente usado para cada uma de uma nova forma, considerando a probabilidade de cada coeficiente de ocorrer, além do contexto a nível de bloco e macrobloco que ele está inserido.

## 3.1.3.1 Coeff Token

Esse elemento sintático codifica as estatísticas de Total de Coeficientes e Total de *Trailing Ones* dentro de um único *string* de bits. Faz uso de uma dentre 6 possíveis *Look-Up Tables* (sendo duas delas usadas apenas para casos especiais de blocos Chroma DC) para a escolha do código e do tamanho do *Coeff Token*, de acordo com a variável *nC*.

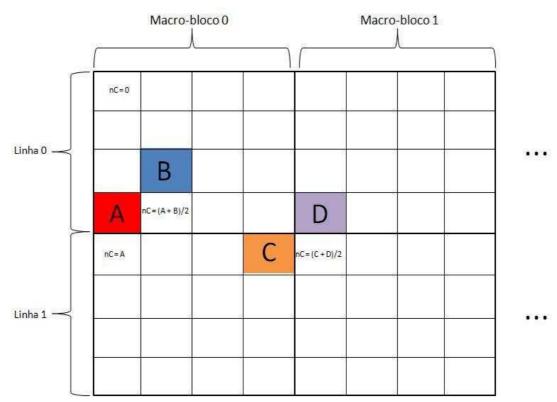

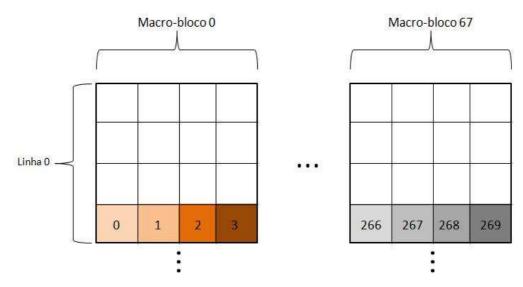

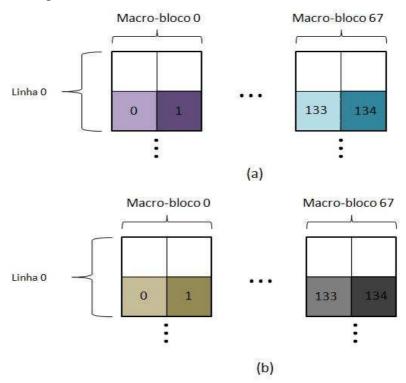

A variável nC é um valor que depende da vizinhança do bloco atualmente codificado. Em termos gerais, ele corresponde à média arredondada para cima do valor de Total de Coeficientes do vizinho imediatamente superior e do vizinho imediatamente à esquerda do atual bloco sendo codificado. No caso que um deles não exista, o valor de nC recebe o valor do Total de Coeficientes do bloco vizinho disponível. Caso nenhum dos dois exista, o valor de nC do bloco atual é 0. A figura 3.5 ilustra uma série de macroblocos com seus respectivos blocos e o cálculo de nC para alguns dele de acordo com sua vizinhança.

Figura 3.5: Cálculo de *nC* para alguns blocos dentro de macroblocos.

Para o exemplo dado na figura 3.3, considerando que se está em um bloco com nC com valor zero, o código para *Coeff Token* do exemplo seria '0000100', pois corresponde ao valor na LUT associada ao nC igual a 0 onde, usando os valores de Total de Coeficientes e Total de *Trailing Ones* como índice, encontra-se o código com o tamanho acima mostrado.

## 3.1.3.2 Trailing Ones Sign Flag

O próximo elemento sintático a ser codificado são os valores ±1 encontrados no bloco. A lógica de codificação é muito simples: sempre que o *Trailing One* tiver o valor +1, ele recebe como código um bit com valor 0; sempre que o *Trailing One* tiver o valor

-1, ele recebe como código um bit com valor 1. Esses elementos são codificados em ordem reversa, começando pelos de mais alta freqüência.

No exemplo que está sendo apresentado, apesar de ter-se quatro amostras com o valor  $\pm 1$  no final da seqüência de dados (desconsiderando os coeficientes com valor 0), apenas no máximo três desses coeficientes podem ser codificados como casos especiais (*Trailing Ones Sign Flag*).

É importante frisar que os *Trailing Ones* ocorrem apenas se eles forem os últimos valores e que eles têm que possuir necessariamente os valores ±1. Caso, por exemplo, ocorra uma seqüência de coeficientes no fim de um bloco cujos valores são, respectivamente, nessa ordem -1, -1, 3, 1, apenas o último valor ('1') será considerado um *Trailing One*, visto que o penúltimo elemento ('3'), faz com que a seqüência dos possíveis *Trailing Ones* anteriores não se confirme.

Um último detalhe que é importante citar é que essa codificação especial é feita considerando que geralmente os últimos elementos não-zero de um bloco tendem a ser valores muito pequenos, geralmente ±1, devido aos passos anteriores à codificação de entropia (Transformada e Quantização). Assim sendo, o CAVLC tira vantagem dessa característica dos blocos, atribuindo códigos pequenos (1 bit) para os *Trailing Ones* (RICHARDSON, 2003).

#### 3.1.3.3 Level

Os coeficientes não-zero restantes e que não foram classificadas como *Trailing Ones* são, então, classificadas como *Levels*. A lógica de codificação de *Levels* se baseia numa lógica aritmética que será apresentada no próximo capítulo de forma detalhada.

O tamanho e o valor de cada *Level* dependem diretamente do valor anterior codificado, pois existem 6 faixas de valores de *Level* que fazem com que um limiar seja alcançado e um código maior seja gerado para os coeficientes de mais baixa freqüência (que tendem a ter valores maiores). Esses valores também serão mostrados no próximo capítulo de uma forma mais explicada.

Para o exemplo, tem-se para o primeiro *Level* ('1') o código '1'. Esse valor faz com que o limiar para o próximo *Level* seja ultrapassado, fazendo com que o código do próximo elemento seja maior. Assim, o próximo *Level* ('3') entra em um novo valor de limiar e seu código é '0010'.

#### 3.1.3.4 Total Zeros