## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

#### MARCELO SCHIAVON PORTO

### Desenvolvimento Algorítmico e Arquitetural para a Estimação de Movimento na Compressão de Vídeo de Alta Definição

Tese apresentada como requisito parcial para a obtenção do grau de Doutor em Ciência da Computação

Prof. Dr. Sergio Bampi Orientador

Prof. Dr. Luciano Volcan Agostini (UFPel) Co-orientador

### CIP - CATALOGAÇÃO NA PUBLICAÇÃO

Porto, Marcelo Schiavon

Desenvolvimento Algorítmico e Arquitetural para a Estimação de Movimento na Compressão de Vídeo de Alta Definição [manuscrito] / Marcelo Schiavon Porto. – 2012.

166 f.:il.

Orientador: Sergio Bampi; Co-orientador: Luciano Volcan Agostini.

Tese (Doutorado) — Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação. Porto Alegre, BR — RS, 2012.

1. Estimação de movimento 2. Desenvolvimento algorítmico, 3. Desenvolvimento arquitetural 4. Vídeos de alta definição. I. Bampi, Sergio. II. Agostini, Luciano Volcan. III. Título.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos Alexandre Netto

Vice-Reitor: Prof. Rui Vicente Oppermann

Pró-Reitor de Pós-Graduação: Prof. Aldo Bolten Lucion Diretor do Instituto de Informática: Prof. Luís da Cunha Lamb

Coordenador do PPGC: Prof. Álvaro Freitas Moreira

Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

#### **AGRADECIMENTOS**

Muitas pessoas foram importantes para mim durante todo este período de doutorado, e merecem ser lembradas nestes agradecimentos. Agradeço aos meus pais Roberto Porto e Ivone Porto pela criação que me deram e pelos valores que me ensinaram ao longo da vida. Muito obrigado pelo apoio dado ao longo de toda a minha formação acadêmica, e que não foi diferente durante este doutorado.

Gostaria de agradecer também a minha tia Maria Helena Schiavon, que sempre me apoiou em todas as etapas da minha vida e é como uma segunda mãe pra mim.

Um agradecimento especial a minha namorada e companheira Júlia Islabão, que esteve ao meu lado durante estes quatro anos de doutorado, enfrentando os momentos difíceis e a distância durante boa parte deste período. Muito obrigado por estar ao meu lado, te amo muito.

Gostaria de agradecer ao grande professor Sergio Bampi, meu orientador. Muito obrigado por todas as oportunidades que me destes e pelos conhecimentos que compartilhastes comigo durante estes últimos seis anos, desde o mestrado. Muito obrigado pela confiança que depositastes em mim quando me escolheste como teu aluno de doutorado, esta foi uma oportunidade única na minha carreira e espero ter correspondido as suas expectativas.

Ao Luciano Agostini, meu grande amigo e co-orientador desta tese, não tenho palavras para expressar todo o meu agradecimento. Não tenho dúvidas de que sem o apoio do Luciano, este trabalho não teria sido possível. Foi inspirado pelo Luciano que escolhi seguir carreira acadêmica, e foi através dele que conheci o professor Bampi e o professor Susin, que foram meus orientadores durante o mestrado. O Luciano não é excelente apenas como professor e orientador, mas também é um exemplo como pessoa, sempre disposto ajudar e sempre trabalhando por todos ao seu redor. Comigo, tem sido assim desde 2003, quando ele começou as atividades no GACI, e eu ingressei como bolsista IC no grupo. Espero que possamos continuar trabalhando juntos por muito tempo ainda, agora como colegas de profissão, e que eu possa retribuir de alguma forma por tudo que fizeste por mim, muito obrigado.

Gostaria de agradecer aos meus queridos colegas do grupo de pesquisa da UFRGS, o "lab 215", com quem convivi durante este período. Agradecimentos especiais aos colegas Cláudio Diniz, Bruno Zatt, Vagner Rosa, Roger Porto, Fábio Ramos, Dieison Deprá, André Martins, Débora Matos, Franco Valdez e Cristiano Thiele. Muito obrigado a todos pelo apoio, discuções técnicas, revisões de artigos, conversas na hora do cafesinho e churrascos do grupo. Este grupo é muito forte, e foi um prazer ter participado e contribuído com ele durante este período.

Tenho que agradecer também ao grupo de Arquiteturas e Circuitos Integrados da UFPel, o GACI, o qual tenho o prazer de participar desde sua criação, e que tenho participado mais ativamente desde que retornei a Pelotas para assumir como professor na UFPel. Gostaria de agradecer ao Diego Noble, Daniel Palomino e Felipe Sapaio, que estavam no GACI quando retornei a Pelotas, e que hoje estão no mestrado da UFRGS. Tenho que agradecer em especial aos bolsistas de IC Pargles D'all Oglio, Cássio Cristani e Gustavo Sanchez, que trabalharam comigo durante os dois últimos anos deste doutorado. O apoio deles foi fundamental para a realização deste trabalho, e mais uma vez tenho que agradecer ao Luciano, que disponibilizou os seus orientados e toda a infraestrutura do GACI para que eu pudesse trabalhar.

Enfim, gostaria de agradecer a todos os amigos, colegas e funcionários da UFRGS e UFPel que de uma forma ou de outra contribuíram para o desenvolviemnto deste trabalho, quatro anos se passaram desde o início deste doutorado e com certeza não consegui agradecer nominalmente a todos.

# **SUMÁRIO**

| LISTA DE ABREVIATURAS E SIGLAS                                                                                          | 7              |

|-------------------------------------------------------------------------------------------------------------------------|----------------|

| LISTA DE FIGURAS                                                                                                        | 11             |

| LISTA DE TABELAS                                                                                                        | 15             |

| RESUMO                                                                                                                  |                |

|                                                                                                                         |                |

| ABSTRACT                                                                                                                |                |

| 1 INTRODUÇÃO                                                                                                            | 21             |

| 2 CONCEITOS DE COMPRESSÃO DE VÍDEO DIGIT                                                                                | AL 25          |

| 2.1 Conceitos Básicos de Vídeo Digital                                                                                  | 25             |

| 2.2 Compressão com Perdas e sem Perdas                                                                                  | 26             |

| 2.3 Espaço de Cores                                                                                                     |                |

| <ul> <li>2.4 Subamostragem de Cores</li> <li>2.5 Redundância de Informação em Vídeos Digitais</li> </ul>                |                |

| 2.6 Avaliação de Qualidade em Vídeos Digitais                                                                           |                |

| 3 A ESTIMAÇÃO DE MOVIMENTO                                                                                              |                |

| 3.1 Modelo de Codificador de Vídeos Digitais                                                                            | 37             |

| 3.2 Ferramentas de Codificação da EM em Padrões Atuais                                                                  | 39             |

| 3.3 Algoritmos de Busca na EM                                                                                           |                |

| 3.3.1 Full Search (FS)                                                                                                  |                |

| 3.3.3 Three Step Search (TSS)                                                                                           |                |

| 3.3.4 One at a Time Search (OTS)                                                                                        |                |

| 3.4 Estado da Arte em Algoritmos de Busca para a EM                                                                     |                |

| 3.5 Estado da Arte em Arquiteturas para a EM                                                                            |                |

| 4 A ESTIMAÇÃO DE MOVIMENTO EM VÍDEOS DE 55                                                                              | ALTA DEFINIÇAO |

|                                                                                                                         | 70             |

| <ul> <li>4.1 Análise dos Mínimos Locais</li> <li>4.2 Análise do Uso de Vários Tamanhos de Bloco no H.264/AVC</li> </ul> | 59             |

| 4.3 Avaliação da EM com Tamanhos de Bloco Maiores                                                                       |                |

| 4.4 Avaliação do Uso de Subamostragem de Pixel                                                                          |                |

| 5 ALGORITMOS DESENVOLVIDOS                                                                                              | 75             |

| 5.1 Os Algoritmos SDS-DIC e QSDS-DIC                                                                                    | 75             |

| 5.2 O Algoritmo MPDS                                                                                                    |                |

| 5.3 O Algoritmo DMPDS                                                                                                   |                |

| 5.4 Os Algoritmos Aleatórios                                                                                            |                |

| 5.4.2 Algoritmo Iterative Random Search (IRS)                                                                           |                |

| 5.4.3 Algoritmo Multiple Iterative Random Search (MIRS)                                                                 | 92             |

| 5.4.4 Algoritmo Random Diamond Search (RDS)                                                                             |                |

| 5.4.5 Exploração do Valor de <i>N</i> e do Tamanho da Área de Pesqui                                                    | sa94           |

| 5.4.6           | Resultados para os Algoritmos Aleatórios                                  | 101    |

|-----------------|---------------------------------------------------------------------------|--------|

| 5.5 Ava         | liação dos Algoritmos Desenvolvidos para Vídeos Maiores que HD 1080p      | 108    |

| 5.6 Disc        | cussão e Comparações Sobre o Desenvolvimento Algorítmico                  | 110    |

|                 | UITETURAS DE HARDWARE DESENVOLVIDAS                                       |        |

| 6.1 Arg         | uiteturas dos algoritmos SDS-DIC e QSDS-DIC                               | 117    |

| 6.1.1           | Resultados de Síntese da Arquitetura do SDS-DIC                           | 122    |

| 6.1.2           | Arquitetura do algoritmo QSDS-DIC                                         | 122    |

| 6.1.3           | Resultados de Síntese da Arquitetura do QSDS-DIC                          | 123    |

| 6.2 Arq         | uiteturas do SDS-DIC e QSDS-DIC com Somadores Compressores                | 124    |

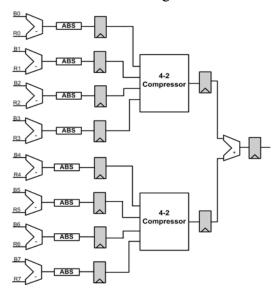

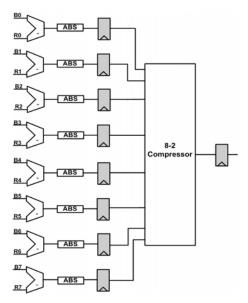

| 6.2.1           | Arquitetura da UP 4-2 e UP 8-2                                            |        |

| 6.2.2           | Resultados de Síntese com o uso de Somadores Compressores                 | 126    |

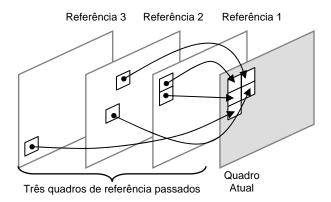

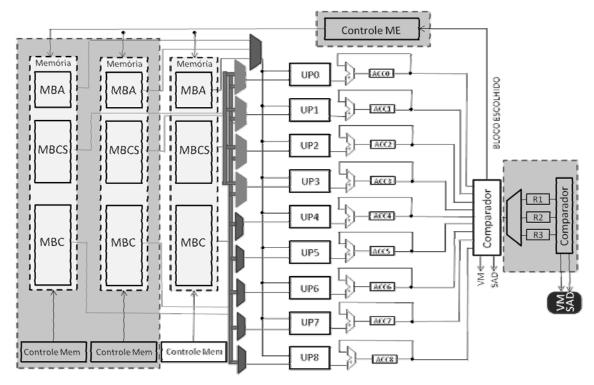

| 6.3 Arq         | uitetura do SDS-DIC para Múltiplos Quadros de Referência                  | 127    |

| 6.3.1           | Resultados de Síntese da Arquitetura do MRSDS-DIC                         | 128    |

| 6.4 Arg         | uitetura Dedicada para o Algoritmo MPDS                                   | 129    |

| 6.4.1           | Resultados de Síntese da Arquitetura do MPDS                              | 133    |

| 6.4.2           |                                                                           |        |

| 6.5 Arq         | uitetura Dedicada para o Algoritmo Hardware Oriented - Multiple Iterative | Random |

| Search (HO-M    | IRS)                                                                      |        |

| 6.5.1           | Resultados de Síntese da Arquitetura do HO-MIRS                           | 140    |

| 6.6 Ava         | liação e Comparações dos Resultados do Desenvolvimento Arquitetural       |        |

| 6.6.1           | Resultados Comparativos para as Arquiteturas Desenvolvidas                |        |

| 6.6.2           | Resultados Comparativos com Trabalhos Relacionados                        | 145    |

| 7 CON           | CLUSÕES                                                                   | 149    |

| REFERÊ          | NCIAS                                                                     | 153    |

|                 | CE A - RESULTADOS COMPLETOS DA AVALIAÇÃO DOS                              |        |

| ALGORIIM        | OS DE EM DESENVOLVIDOS                                                    | 159    |

|                 | CE B – PUBLICAÇÕES ORIGINAIS OBTIDAS COM OS                               |        |

| <b>RESULTAD</b> | OS APRESENTADOS NESTA TESE                                                | 165    |

#### LISTA DE ABREVIATURAS E SIGLAS

ABEM All Binary Motion Estimation

ACC Acumulador

ATME Adaptive True Motion Estimation

ASIC Application-specific Integrated Circuit

BC Bloco Candidato

BCC Bloco Candidato Calculado

BE Bloco Escolhido

BMPDS Best Multi-Point Diamond Search

BRAM Block RAM

BBGDS Block-Based Gradient Descent Search

Cb *Chrominance blue*

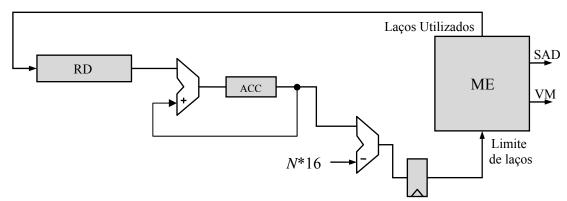

CDL Controle Dinâmico de Laços

CIF Common Intermediate Format

CLB Configurable Logic Block

Cr Chrominance red

DCS Dual Cross Search

DGDS Directional Gradient Descent Search

DIC Dynamic Iteration Control

D<sub>M</sub> Desvio Médio

DMPDS Dynamic Multi-Point Diamond Search

DS Diamond Search

DVD Digital Versatile Disk

DVSS Dynamically Variable Step Search

EDTV Enhanced-Definition Television

EM Estimação de Movimento

FDGDS Fast Directional Gradient Descent Search

FPGA Field Programmable Gate Array

FS Full Search

HD High definition

HDTV High Definition Digital Television

HO-MIRS Hardware Oriented - Multiple Iterative Random Search

MRSDS Multiple Reference Sub-sampled Diamond Search

HS Hexagon Search

HSI Hue, Saturation, Intensity

IEC International Electrotechnical Commission

IRS Iterative Random Search

ISO International Organization for Standardization

ITU-T International Telecommunication Union - Telecommunication

LDSP Large Diamond Search Pattern

LFSR Linear Feedback Shift Register

LUT Look up Table

MAE Minimum Absolute Error

MBA Memória do Bloco Atual

MBC Memória de Bloco Candidato

MBCS Memória de Bloco Candidato do SDSP

MC Motion Compensation

ME Motion Estimation

MIRS Multiple Iterative Random Search

ML Memória Local

MMEA Multi-resolution ME Algorithm)

MPDS Multi-Point Diamond Search

MPEG Moving Picture Experts Group

MSE Minimum Square Error

NSS N Step Search

VM Vetor de Movimento

OTS One at a Time Search

PMVFAST Predictive Motion Vector Field Adaptive Search Technique

PRR Percentual de Redução do Resíduo

PSNR Peak-to-Signal Noise Ratio

QCIF Quarter Common Intermediate Format

QSDS Quarter Sub-sampled Diamond Search

QFHD Quad Full High Definition

RAM Random Access Memory

RAR Roshal ARchive

RD Registrador de deslocamento

RDS Random Diamond Search

RGB Red, Green, Blue

RSP Random Search Plus

SAD Sum of Absolute Differences

SDS Sub-sampled Diamond Search

SDSP Small Diamond Search Pattern

SDTV Standart Definition Television

T Transformada

TSMC Taiwan Semiconductor Manufacturing Company

TSS Three Step Search

UFRGS Universidade Federal do Rio Grande do Sul

UMD Universal Media Disc

UMH Uneven Multi Hexagon

Own Oneven Muin Hexago

UA Unidade Aleatória

UP Unidade de ProcessamentoVGA Video Graphics Adapter

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrated Circuit

VMPDS Variable Multi-Point Diamond Search

VQEG Video Quality Experts Group

WQXGA Wide Quad eXtended Graphics Array

Y Luminance

YCbCr Luminance, Chrominance Blue, Chrominance Red

## LISTA DE FIGURAS

| Figura 2.1: Sequência de quadros e blocos em um vídeo digital                                   | 25    |

|-------------------------------------------------------------------------------------------------|-------|

| Figura 2.2: Formatos de subamostragem de crominância (RICHARDSON, 2002)                         | 28    |

| Figura 2.3: Imagem Original                                                                     | 30    |

| Figura 2.4: Imagem modificada com fundo embaçado, PSNR 26,8dB                                   | 31    |

| Figura 2.5: Imagem modificada com a parte da frente do caminhão embaçada, PSNR                  |       |

| 28,4dB                                                                                          | 31    |

| Figura 3.1: Quadro 1                                                                            | . 34  |

| Figura 3.2: Quadro 2                                                                            | . 34  |

| Figura 3.3: Resíduo sem estimação de movimento                                                  |       |

| Figura 3.4: Resíduo após a estimação e compensação de movimento                                 | 35    |

| Figura 3.5: Elementos presentes no processo de estimação de movimento (PORTO,                   |       |

| 2008d)                                                                                          |       |

| Figura 3.6: Modelo genérico de codificador de vídeo (AGOSTINI, 2007)                            |       |

| Figura 3.7: Algoritmo de Busca Completa (FS)                                                    |       |

| Figura 3.8: Large Diamond (LDSP) (L) e Small Diamond (SDSP) (S) (PORTO, 200                     |       |

| Figura 3.9: Aplicação do LDSP (a) por aresta e (b) por vértice (PORTO, 2008)                    |       |

| Figura 3.10: Algoritmo Three Step Search (PORTO, 2008)                                          |       |

| Figura 3.11: Algoritmo One at a Time Search                                                     |       |

| Figura 4.1: Pequena região em destaque em parte de uma imagem HD 1080p                          |       |

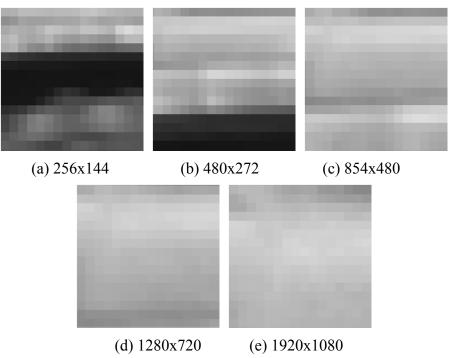

| Figura 4.2: Bloco 16x16 pixels da mesma região da imagem em diferentes resoluçõe                |       |

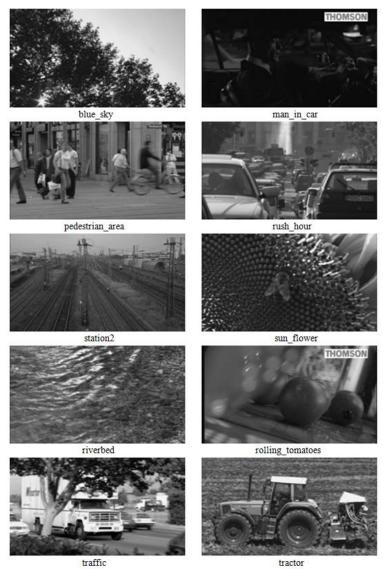

| Figura 4.3: Primeiro quadro das sequências de teste HD 1080p utilizadas                         |       |

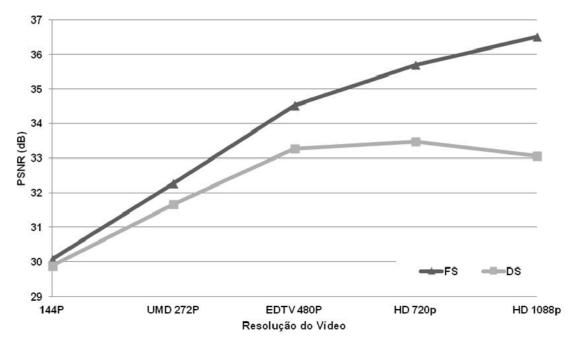

| Figura 4.4: PSNR médio para o algoritmo FS e DS em diferentes resoluções                        |       |

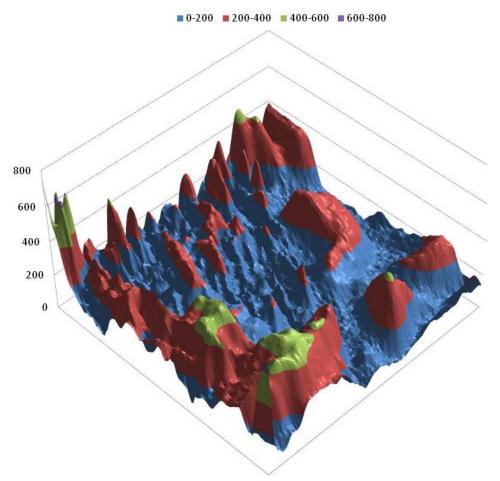

| Figura 4.5: Resultados de SAD para uma área de busca de 128x128 pixels e blocos de              |       |

| 16x16 pixels (visualização 3D)                                                                  |       |

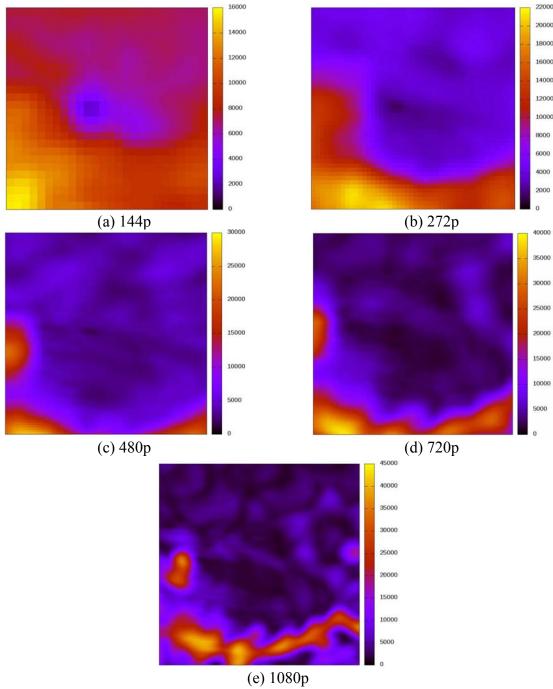

| Figura 4.6: Mapas de SAD para o vídeo sun_flower em diferentes resoluções                       | 61    |

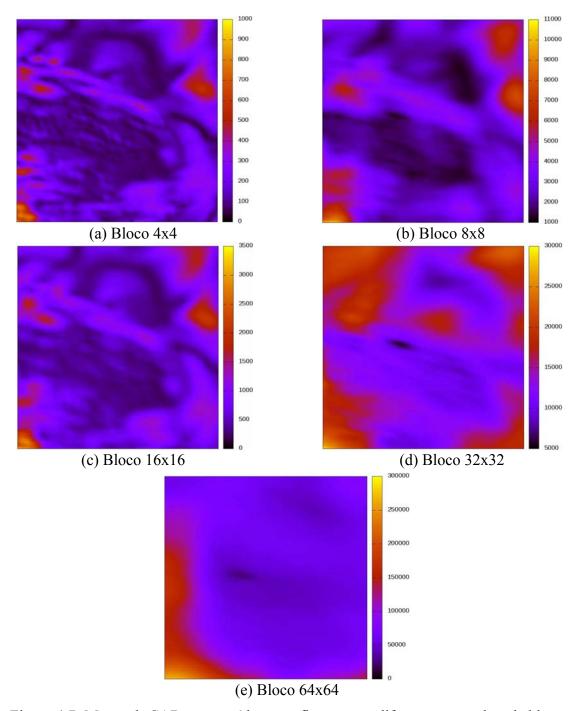

| Figura 4.7: Mapas de SAD para o vídeo sun_flower com diferentes                                 |       |

| tamanhos de bloco                                                                               | . 63  |

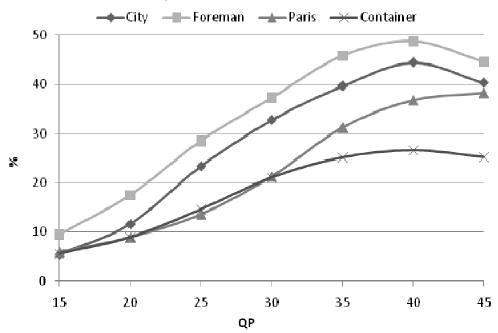

| Figura 4.9: Percentual do bitstream dedicado aos vetores de movimento no H.264/A'               |       |

| (ITU-T, 2011)                                                                                   |       |

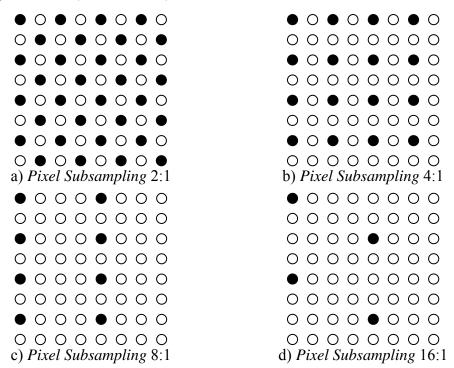

| Figura 4.10: Subamostragem de pixel (PS - Pixel Subsampling) em diferentes níveis               | . 69  |

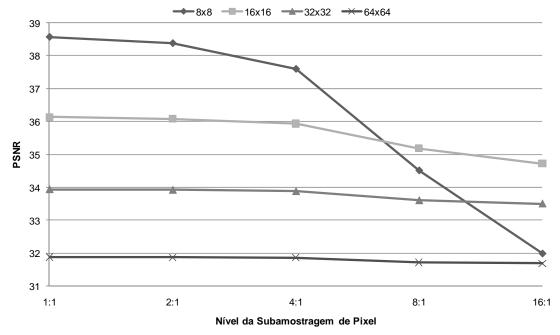

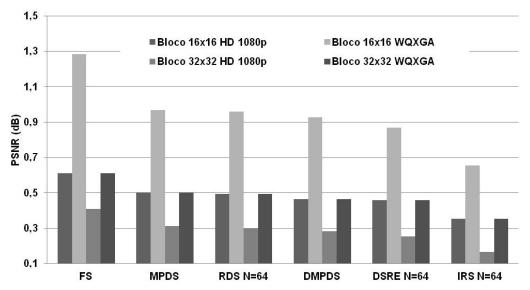

| Figura 4.11: Variação do PSNR médio para o algoritmo FS com o aumento da subamostragem de pixel | 70    |

| buountobuugoni de piroi                                                                         | . , 0 |

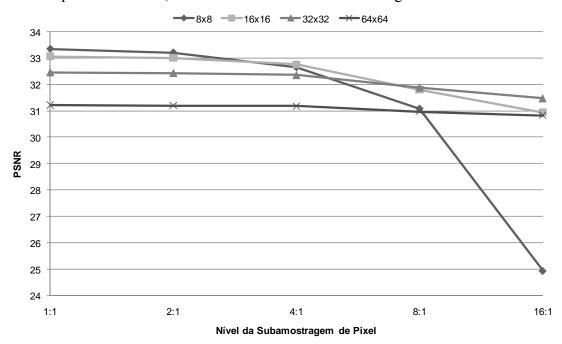

| Figura 4.12: Variação do PSNR médio para o algoritmo DS com o aumento da                                                                                    |       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| subamostragem de pixel                                                                                                                                      | 71    |

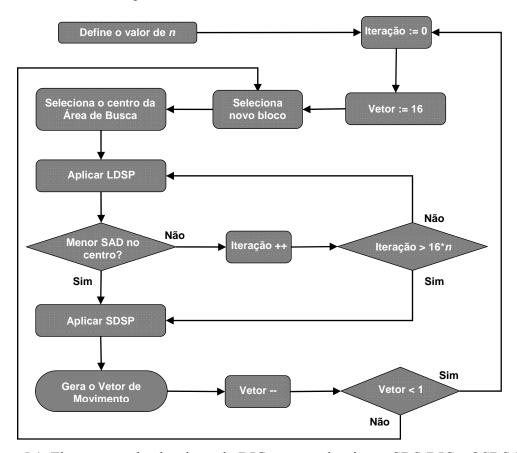

| Figura 5.1: Fluxograma do algoritmo do DIC para os algoritmos<br>SDS-DIC e QSDS-DIC                                                                         | 76    |

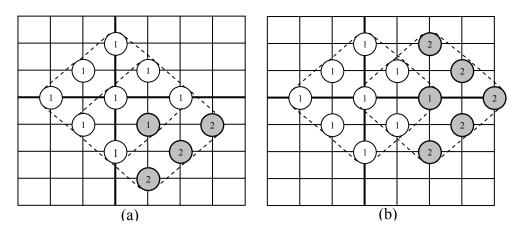

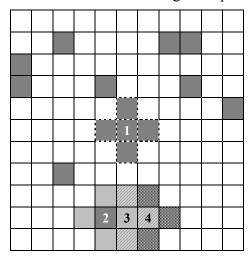

| Figura 5.2: Núcleos de busca do algoritmo MPDS                                                                                                              | 78    |

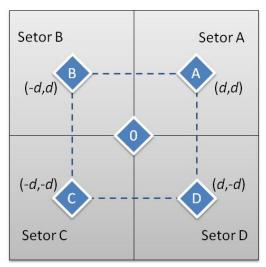

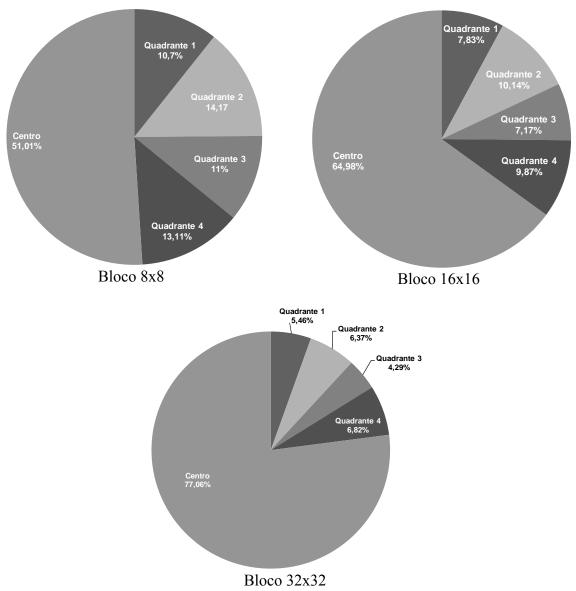

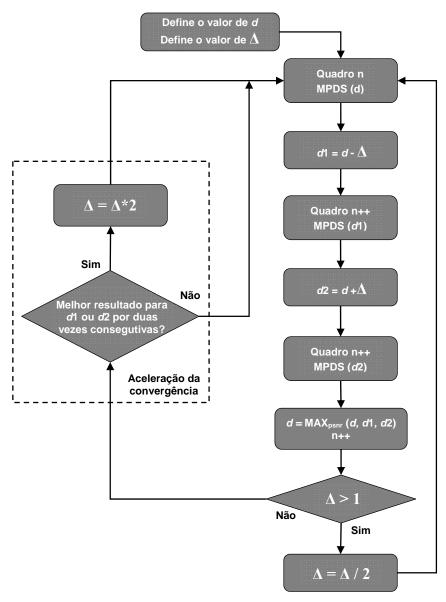

| Figura 5.3: Fluxograma do algoritmo MPDS                                                                                                                    | 79    |

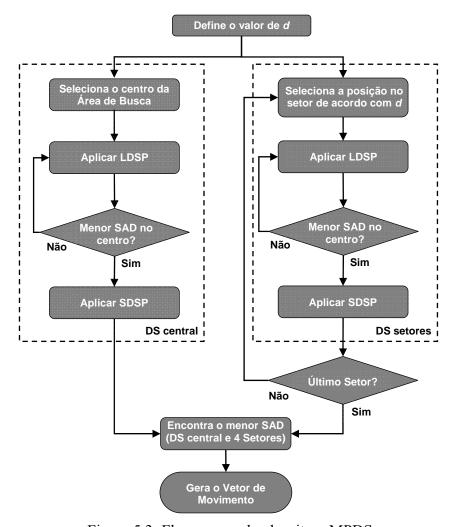

| Figura 5.4: Variação do parâmetro d para o algoritmo MPDS com blocos 8x8                                                                                    | 79    |

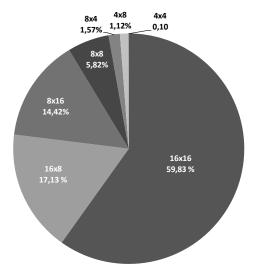

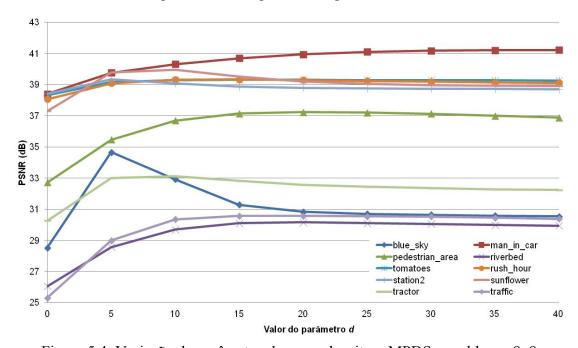

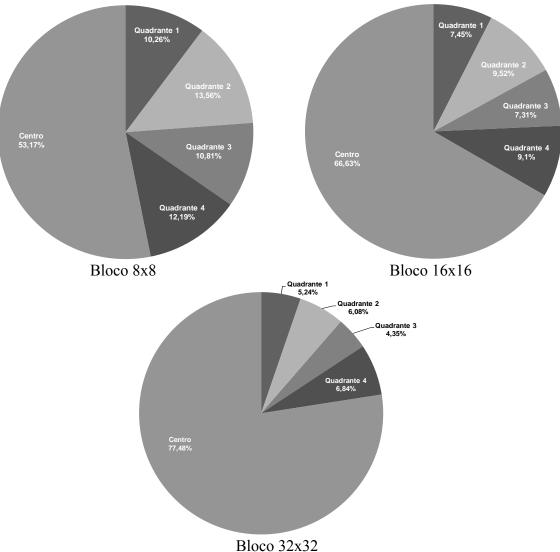

| Figura 5.5: Percentual de escolha em cada setor do algoritmo MPDS                                                                                           | 82    |

| Figura 5.6: Controle dinâmico do parâmetro d no algoritmo DMPDS                                                                                             | 84    |

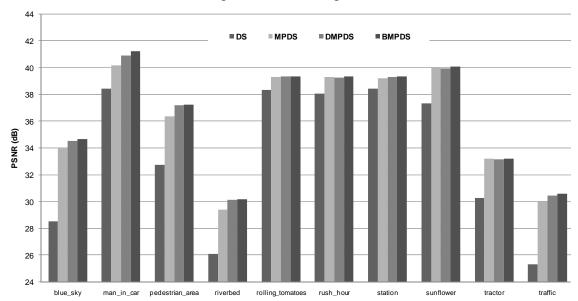

| Figura 5.7: Curvas de ganho PSNR dos algoritmos DMPDS, MPDS, BMPDS e DS com blocos 8x8                                                                      | 85    |

| Figura 5.8: Percentual de escolha em cada setor do algoritmo DMPDS                                                                                          | 86    |

| Figura 5.9: Fluxograma do algoritmo RSP                                                                                                                     | 88    |

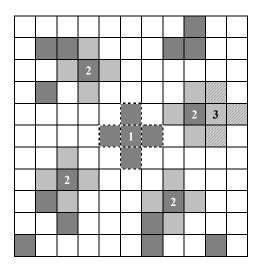

| Figura 5.10: Exemplo de busca do algoritmo RSP para N = 10                                                                                                  | 89    |

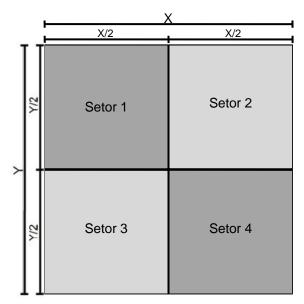

| Figura 5.11: Divisão da área de busca em setores                                                                                                            | 90    |

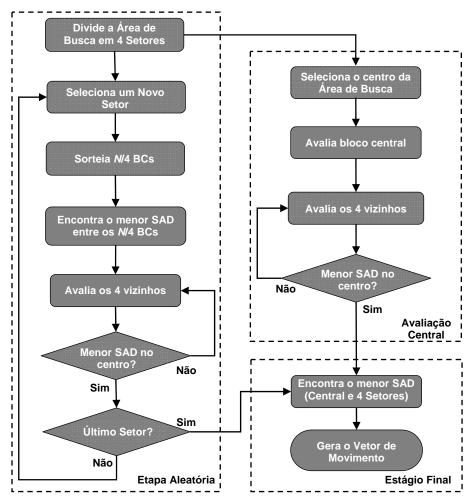

| Figura 5.12: Fluxograma do algoritmo IRS                                                                                                                    | 91    |

| Figura 5.13 – Exemplo de busca do algoritmo IRS                                                                                                             | 92    |

| Figura 5.14: Fluxograma do algoritmo MIRS                                                                                                                   | 93    |

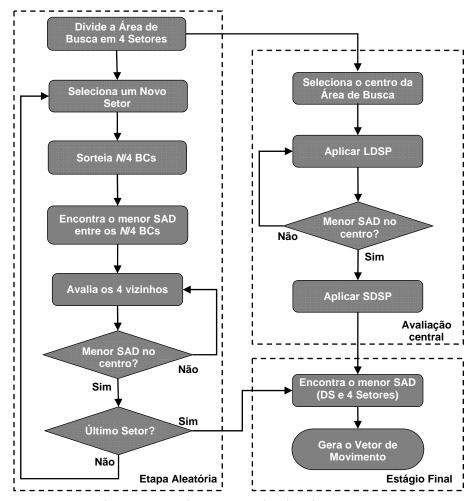

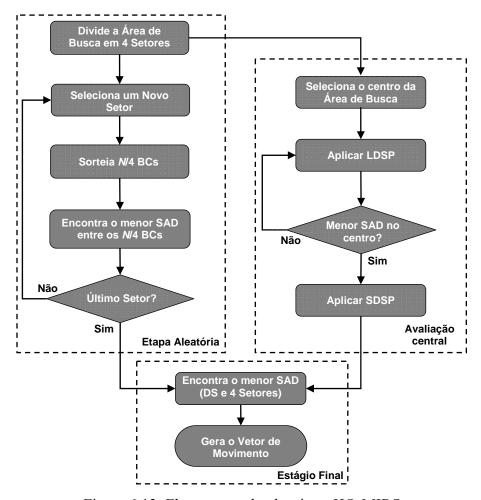

| Figura 5.15: Fluxograma do algoritmo RDS                                                                                                                    | 94    |

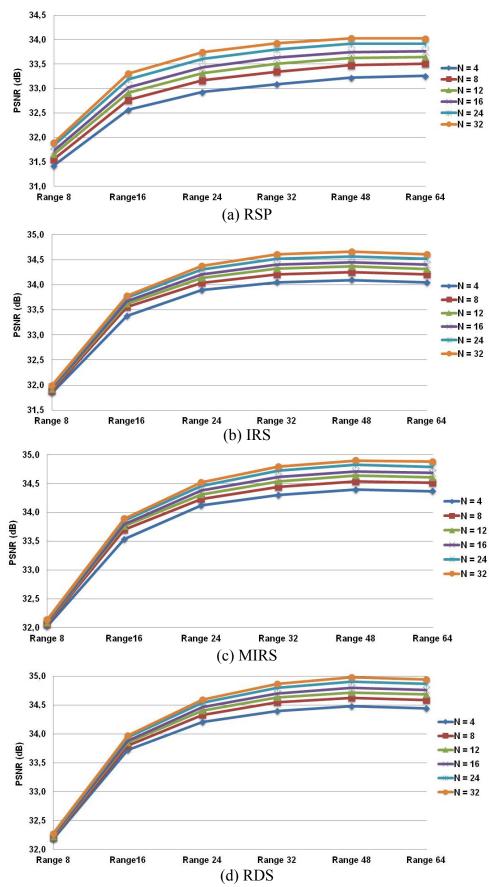

| Figura 5.16: Avaliação de qualidade para a variação do valor de N e tamanho da área de busca para os algoritmos RSP(a), IRS(b), MIRS(c) e RDS(d)            | 96    |

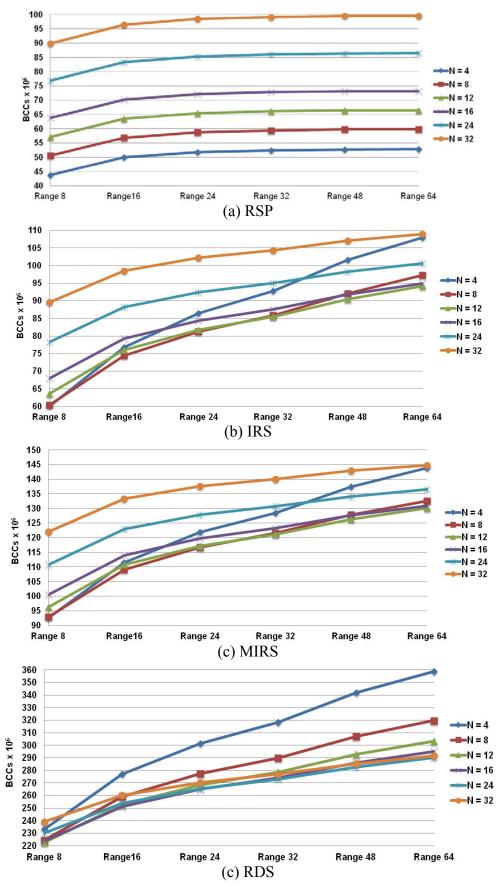

| Figura 5.17: Avaliação de custo computacional para a variação do valor de N e tamanho da área de busca para os algoritmos RSP(a), IRS(b), MIRS(c) e RDS(d). | 98    |

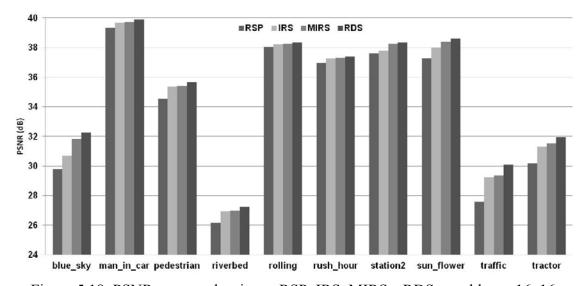

| Figura 5.18: PSNR para os algoritmos RSP, IRS, MIRS e RDS com blocos 16x16                                                                                  | . 102 |

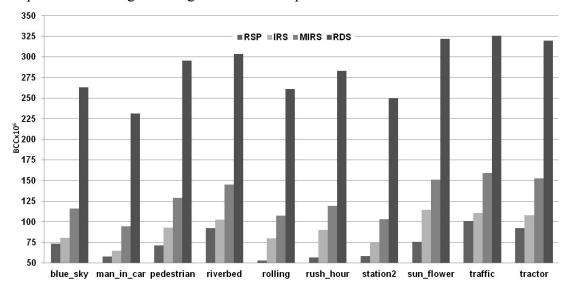

| Figura 5.19: Número de BCCs para os algoritmos RSP, IRS, MIRS e RDS com blocos 16x16                                                                        | . 104 |

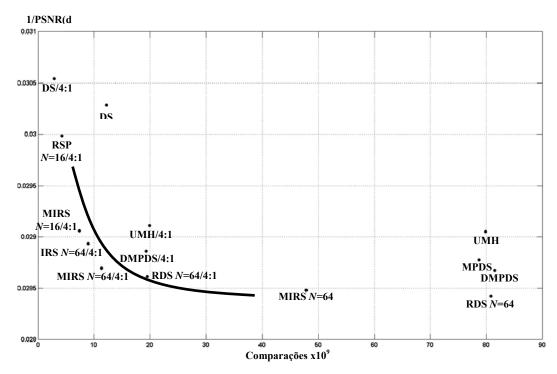

| Figura 5.21: Relação 1/PSNR versus o número de comparações para blocos 16x16                                                                                | 112   |

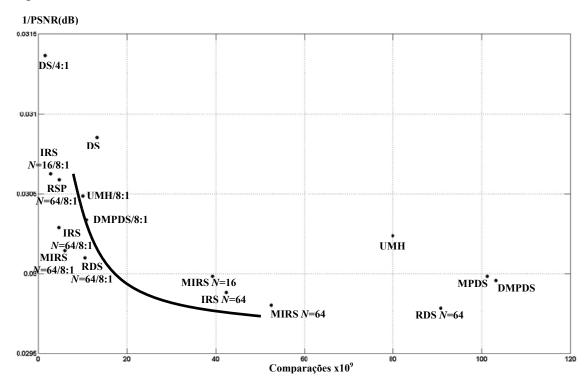

| Figura 5.22: Relação 1/PSNR versus o número de comparações                                                                                                  |       |

| para blocos 32x32                                                                                                                                           | . 114 |

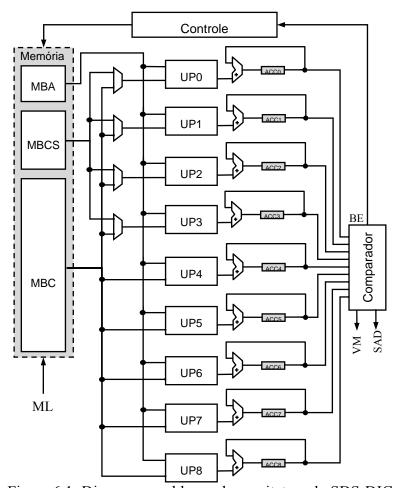

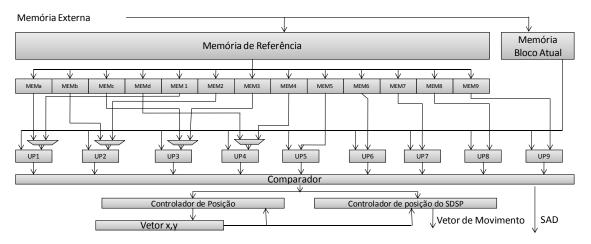

| Figura 6.1: Diagrama em blocos da arquitetura do SDS-DIC                                                                                                    | . 118 |

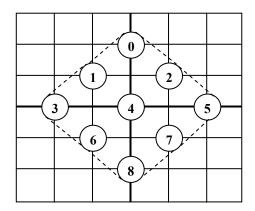

| Figura 6.2: LDSP com os blocos candidatos numerados                                                                                                         | . 119 |

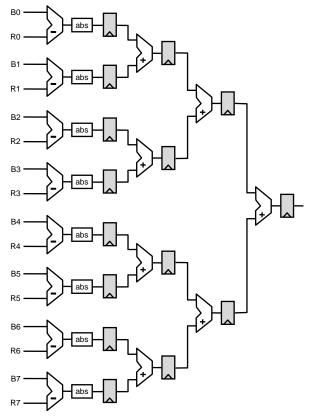

| Figura 6.3: Arquitetura da UP utilizada na arquitetura do SDS-DIC                                                                                           | . 119 |

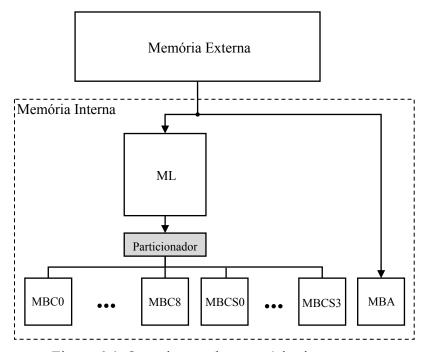

| Figura 6.4: Organização das memórias internas                                                                                                               | . 120 |

| Figura 6.5: Estrutura do controle dinâmico de laços (DIC)                                                                                                   | 121   |

| Figura 6.6: Arquitetura da UP 4-2                                                                                                                           | 125   |

| Figura 6.7: Arquitetura da UP 8-2                                                                                                                           | 125   |

| Figura 6.8: Estimação de movimento com três quadros (passados) de referência                                                                                | . 127 |

| Figura 6.9: Diagrama em blocos da arquitetura do MRSDS-DIC                                                                                                  | . 128 |

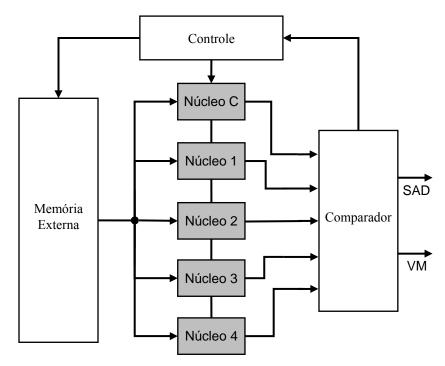

| Figura 6.10: Diagrama em blocos da arquitetura do algoritmo DS                                                                                              | 130   |

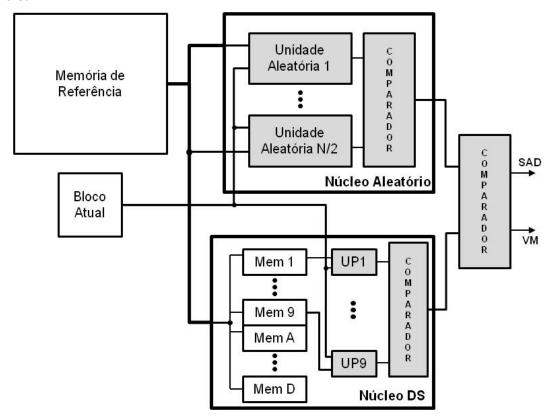

| Figura 6.11: Arquitetura do algoritmo MPDS                                                                                                                  | . 132 |

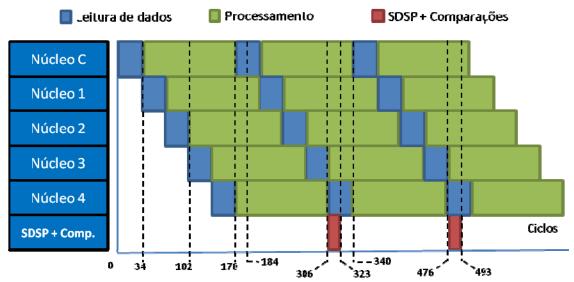

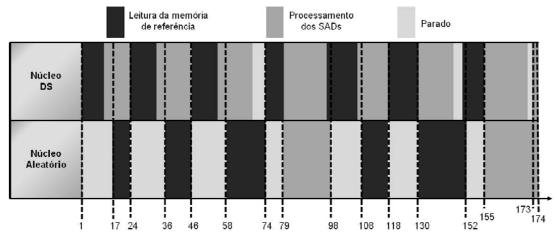

| Figura 6.12: Diagrama de ciclos da arquitetura do MPDS                                                                                                      |       |

| Figura 6.13: Fluxograma do algoritmo HO-MIRS                                                                                                                | . 137 |

| Figura 6.14: Diagrama de blocos da arquitetura do algoritmo HO-MIRS                                     | 138 |

|---------------------------------------------------------------------------------------------------------|-----|

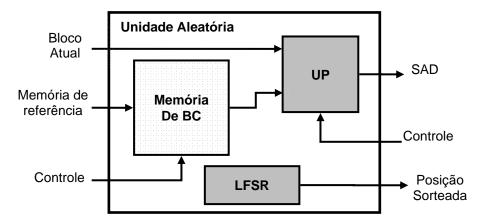

| Figura 6.15: Diagrama de blocos da arquitetura da Unidade Aleatória                                     | 139 |

| Figura 6.16: Diagrama de ciclos para a arquitetura do algoritmo HO-MIRS                                 | 140 |

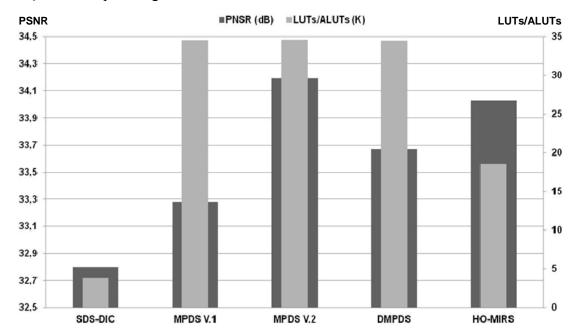

| Figura 6.17: Número de LUTs/ALUTs das arquiteturas desenvolvidas e respectivos resultados de qualidade  | 143 |

| Figura 6.18: Resultados de qualidade e número de gates utilizados pelas arquiteturas desenvolvidas      | 145 |

| Figura A.1: Resultados de PSNR e número de comparações para os algoritmos da avaliados com blocos 8x8   |     |

| Figura A.2: Resultados de PSNR e número de comparações para os algoritmos da avaliados com blocos 16x16 |     |

| Figura A.3: Resultados de PSNR e número de comparações para os algoritmos da avaliados com blocos 32x32 |     |

## LISTA DE TABELAS

| Tabela 4.1: Resultados médios de PSNR e BCCs para os algoritmos FS e DS em        |     |

|-----------------------------------------------------------------------------------|-----|

| diferentes resoluções                                                             | 59  |

| Tabela 4.2: Percentuais de escolhas de cada tamanho de bloco do                   |     |

| padrão H.264/AVC                                                                  | 64  |

| Tabela 4.3: Resultados para a EM com FS e DS para diferentes                      |     |

| tamanhos de bloco                                                                 | 66  |

| Tabela 4.4: Número médio de iterações do algoritmo DS com diferentes níveis de    |     |

| subamostragem                                                                     | 71  |

| Tabela 4.5: Resultados para a EM com o algoritmo DS para diferentes               |     |

| tamanhos de bloco e diferentes níveis de subamostragem                            | 72  |

| Tabela 5.1: Resultados para os algoritmos SDS e QSDS com restrição                |     |

| fixa iterações e com DIC                                                          | 77  |

| Tabela 5.2: Resultados médios de PSNR (dB) do algoritmo MPDS, com a               |     |

| variação do parâmetro d, em diferentes tamanhos de bloco                          | 80  |

| Tabela 5.3: Melhor valor de d para o algoritmo MPDS em diferentes                 |     |

| tamanhos de bloco                                                                 | 81  |

| Tabela 5.4: Resultados de qualidade e custo computacional do algoritmo MPDS       |     |

| Tabela 5.5: Valores ótimos de d para o algoritmo MPDS em cada sequência           | 83  |

| Tabela 5.6: Resultados de qualidade e custo computacional do algoritmo DMPDS      | 86  |

| Tabela 5.7: Resultados de qualidade e custo computacional para o algoritmo        |     |

| RSP com a variação do valor de N para a área de busca de [-48, +48]               | 99  |

| Tabela 5.8: Resultados de qualidade e custo computacional para                    |     |

| os algoritmos IRS e MIRS com a variação do valor de N para a área de busca de [-4 |     |

| +48]                                                                              | 100 |

| Tabela 5.9: Resultados de qualidade e custo computacional para o algoritmo        |     |

| RDS com a variação do valor de N para a área de busca de [-48, +48]               | 101 |

| Tabela 5.10: Resultados médios e de desvio padrão (DP) de PSNR para a             |     |

| etapa aleatória                                                                   | 102 |

| Tabela 5.11: Resultados de qualidade e custo computacional para os algoritmos     |     |

| aleatórios em diferentes tamanhos de bloco                                        | 105 |

| Tabela 5.12: Resultados de qualidade e custo computacional para os algoritmos     |     |

| aleatórios com subamostragem de pixel                                             | 107 |

| Tabela 5.13: Resultados comparativos de PSNR para os algoritmos                   |     |

| em vídeos WQXGA para blocos 16x16                                                 | 108 |

| Tabela 5.14: Resultados comparativos de PSNR para os algoritmos                   |     |

| em vídeos WQXGA para blocos 32x32                                                 | 109 |

| Tabela 5.15: Ganho dos algoritmos (dB) sobre o DS em HD 1080p                     |     |

| e WQXGA para blocos 16x16 e 32x32                                                 | 109 |

| Tabela 5.16: Resultados comparativos de qualidade e custo computacional para os   |     |

|-----------------------------------------------------------------------------------|-----|

| algoritmos de EM com tamanho de bloco 16x16                                       | 111 |

| Tabela 5.17: Resultados comparativos de qualidade e custo computacional para os   |     |

| algoritmos de EM com tamanho de bloco 32x32                                       | 113 |

| Tabela 5.18: Resultados comparativos de qualidade e custo computacional           |     |

| em relação ao algoritmo ATME                                                      | 115 |

| Tabela 6.1: Resultados de síntese para a arquitetura do SDS-DIC                   | 122 |

| Tabela 6.2: Resultados de síntese para a arquitetura do QSDS-DIC                  | 123 |

| Tabela 6.3: Resultados de síntese das arquiteturas do SDS-DIC e QSDS-DIC com      |     |

|                                                                                   | 126 |

| Tabela 6.4: Resultados de síntese da arquitetura do MRSDS-DIC                     | 128 |

| Tabela 6.5: Resultados de qualidade e custo computacional para os algoritmos DS e |     |

| MPDS com restrição de iterações                                                   | 129 |

| Tabela 6.6: Resultados de síntese da arquitetura do MPDS para FPGA                | 134 |

| Tabela 6.7: Resultados de síntese da arquitetura do MPDS para TSMC 90nm           | 135 |

| Tabela 6.8: Resultados de síntese da arquitetura do algoritmo DMPDS               | 135 |

| Tabela 6.9: Resultados médios de qualidade e custo computacional para             |     |

| os algoritmos MIRS e HO-MIRS                                                      | 137 |

| Tabela 6.10: Resultados de síntese da arquitetura do HO-MIRS para FPGA e ASIC.    | 141 |

| Tabela 6.11: Resultados comparativos das arquiteturas desenvolvidas em FPGA       | 142 |

| Tabela 6.12: Resultados comparativos das arquiteturas desenvolvidas em ASIC       | 144 |

| Tabela 6.13: Resultados comparativos das arquiteturas desenvolvidas               | 146 |

| Tabela A.1: Resultados comparativos de qualidade e custo computacional para os    |     |

| algoritmos de EM com tamanho de bloco 8x8                                         | 161 |

| Tabela A.2: Resultados comparativos de qualidade e custo computacional para os    |     |

| algoritmos de EM com tamanho de bloco 16x16                                       | 162 |

| Tabela A.3: Resultados comparativos de qualidade e custo computacional para os    |     |

| algoritmos de EM com tamanho de bloco 32x32                                       | 163 |

| Tabela A.4: Resultados comparativos de qualidade entre os algoritmos de EM        |     |

| desenvolvidos e o ATME                                                            | 164 |

| Tabela A.5: Resultados comparativos de número de comparações entre os             |     |

| algoritmos de EM desenvolvidos e o ATME                                           | 164 |

#### **RESUMO**

A compressão de vídeo é um tema extremamente relevante no cenário atual, principalmente devido ao crescimento significativo da utilização de vídeos digitais. Sem a compressão, é praticamente impossível enviar ou armazenar vídeos digitais devido à sua grande quantidade de informações, inviabilizando aplicações como televisão digital de alta definição, vídeo conferência, vídeo chamada para celulares etc. O problema vem se tornando maior com o crescimento de aplicações de vídeos de alta definição, onde a quantidade de informação é consideravelmente maior. Diversos padrões de compressão de vídeo foram desenvolvidos nos últimos anos, todos eles podem gerar grandes taxas de compressão. Os padrões de compressão de vídeo atuais obtêm a maior parte dos seus ganhos de compressão explorando a redundância temporal, através da estimação de movimento. No entanto, os algoritmos de estimação de movimento utilizados atualmente não consideram as variações nas características dos vídeos de alta definição.

Neste trabalho uma avaliação da estimação de movimento em vídeos de alta definição é apresentada, demonstrando que algoritmos rápidos conhecidos, e largamente utilizados pela comunidade científica, não apresentam os mesmos resultados de qualidade com o aumento da resolução dos vídeos. Isto demonstra a importância do desenvolvimento de novos algoritmos focados em vídeos de altíssima definição, superiores à HD 1080p.

Esta tese apresenta o desenvolvimento de novos algoritmos rápidos de estimação de movimento, focados na codificação de vídeos de alta definição. Os algoritmos desenvolvidos nesta tese apresentam características que os tornam menos suscetíveis à escolha de mínimos locais, resultando em ganhos significativos de qualidade em relação aos algoritmos rápidos convencionais, quando aplicados a vídeos de alta definição. Além disso, este trabalho também visa o desenvolvimento de arquiteturas de hardware dedicadas para estes novos algoritmos, igualmente dedicadas a vídeos de alta definição. O desenvolvimento arquitetural é extremamente relevante, principalmente para aplicações de tempo real a 30 quadros por segundo, e também para a utilização em dispositivos móveis, onde requisitos de desempenho e potência são críticos.

Todos os algoritmos desenvolvidos foram avaliados para um conjunto de 10 sequências de teste HD 1080p, e seus resultados de qualidade e custo computacional foram avaliados e comparados com algoritmos conhecidos da literatura. As arquiteturas de hardware dedicadas, desenvolvidas para os novos algoritmos, foram descritas em VHDL e sintetizadas para FPGAs e ASIC, em *standard cells* nas tecnologias 0,18μm e 90nm. Os algoritmos desenvolvidos apresentam ganhos de qualidade para vídeos de alta definição em relação a algoritmos rápidos convencionais, e as arquiteturas desenvolvidas possuem altas taxas de processamento com baixo consumo de recursos de hardware e de potência.

**Palavras-Chave:** Estimação de movimento, Desenvolvimento algorítmico, Desenvolvimento de arquiteturas de hardware, Vídeos de alta definição.

### Algorithmic and Architectural Development for Motion Estimation on High Definition Video Compression

#### **ABSTRACT**

Video compression is an extremely relevant theme in today's scenario, mainly due to the significant growth in digital video applications. Without compression, it is almost impossible to send or store digital videos, due to the large amount of data that they require, making applications such as high definition digital television, video conferences, mobiles video calls, and others unviable. This demand is increasing since there is a strong growth in high definition video applications, where the amount of information is considerably larger. Many video coding standards were developed in the last few years, all of them can achieve excellent compression rates. A significant part of the compression gains in the current video coding standards are obtained through the exploration of the temporal redundancies by means of the motion estimation process. However, the current motion estimation algorithms do not consider the inherent variations that appear in high and ultra-high definition videos.

In this work an evaluation of the motion estimation in high definition videos is presented. This evaluation shows that some well know fast algorithms, that are widely used by the scientific community, do not keep the same quality results when applied to high resolution videos. It demonstrates the relevance of new fast algorithms that are focused on high definition videos.

This thesis presents the development of new fast motion estimation algorithms focused in high definition video encoding. The algorithms developed in this thesis show some characteristics that make them more resilient to avoid local minima, when applied to high definition videos. Moreover, this work also aims at the development of dedicated hardware architectures for these new algorithms, focused on high definition videos. The architectural development is extremely relevant, mainly for real time applications at 30 frames per second, and also for mobile applications, where performance and power are critical issues.

All developed algorithms were assessed using 10 HD 1080p test video sequences, and the results for quality and computational cost were evaluated and compared against known algorithms from the literature. The dedicated hardware architectures, developed for the new algorithms, were described in VHDL and synthesized for FPGA and ASIC. The ASIC implementation used 0.18µm and 90nm CMOS *standard cells* technology. The developed algorithms present quality gains in comparison to regular fast algorithms for high definition videos, and the developed architectures presents high processing rate with low hardware resources cost and power consumption.

**Keywords:** Motion estimation, Algorithmic development, Architectural hardware development, High definition videos.

## 1 INTRODUÇÃO

A compressão de vídeos digitais é um tema de extrema importância na atualidade, principalmente devido à grande quantidade de informações contidas em vídeos digitais sem compressão. Tarefas como armazenamento ou transmissão, são praticamente impossíveis se forem considerados vídeos digitais sem compressão. Isto fez com que diversos padrões de compressão de vídeo fossem desenvolvidos, para reduzir significativamente a quantidade de dados presentes nos vídeos digitais. Esta compressão significativa na quantidade de dados possibilitou a utilização de vídeo digital em diversos dispositivos como celulares, DVD *players*, televisão digital de alta definição (HDTV), entre outros. No entanto, este problema vem se tornando maior com o constante aumento das resoluções dos vídeos digitais. Atualmente, até mesmo dispositivos móveis, como celulares e pequenas câmeras digitais, podem trabalhar com vídeos de alta definição.

Os padrões de compressão de vídeo são formados por um conjunto de algoritmos e técnicas que tentam reduzir o número de dados necessários para representar um vídeo. Dentro dos compressores de vídeo digital atuais, como o MPEG-4 (ISO/IEC, 1999) e H.264 (ITU-T, 2005), por exemplo, existem diversas etapas nas quais as informações que compõem o vídeo são submetidas, dentre elas as principais são: estimação de movimento (EM), compensação de movimento, transformadas, quantização e codificação de entropia (BHASKARAN, 1999). Dentre as etapas dos compressores atuais, a mais complexa, e que resulta no maior impacto sobre a taxa de compressão, é a estimação de movimento. A EM é responsável por encontrar uma correlação entre quadros, mapeando a redundância temporal entre os quadros vizinhos de uma cena. O processo de estimação é extremamente complexo, o que torna indispensáveis o uso de arquiteturas de hardware dedicadas para a codificação de vídeos de alta definição em tempo real.

A grande complexidade do processo de estimação fez com que diversos algoritmos rápidos fossem desenvolvidos. Os algoritmos rápidos possuem heurísticas que aceleram o processo de estimação. Em geral, estas heurísticas repetem um determinado padrão de busca até que uma dada condição de parada seja atingida. No entanto, a característica gulosa destas heurísticas faz com que elas sejam extremamente suscetíveis à escolha de mínimos locais. Toda vez que uma iteração obtém um resultado inferior ao obtido na última iteração, o algoritmo encerra sua busca, desconsiderando a possibilidade de encontrar um resultado melhor após algumas iterações. O número de mínimos locais em uma área de busca cresce significativamente com o aumento da resolução dos vídeos, logo, esta característica deve ser considerada para a estimação de movimento em vídeos de alta definição.

Existem muitos artigos científicos publicados na literatura que apresentam algoritmos rápidos de EM, bem como soluções arquiteturais para estes algoritmos. No entanto, a grande maioria dos artigos apresentam seus dados de avaliação para vídeos de baixa resolução. Em geral, os algoritmos rápidos de EM podem gerar resultados de

qualidade similares aos obtidos pelo algoritmo ótimo, quando aplicados a vídeos de baixa resolução. Estes algoritmos, quando aplicados a vídeos de alta definição, tendem a apresentar perdas significativas de qualidade em relação ao algoritmo ótimo, o que diminui a relevância destes algoritmos neste contexto.

Esta tese visa o desenvolvimento de algoritmos rápidos e arquiteturas dedicadas para a estimação de movimento com foco em vídeos de alta definição. Um dos focos deste trabalho é o desenvolvimento de novos algoritmos para a EM, voltados para a codificação de vídeos de alta definição. Estes algoritmos devem apresentar características que os tornem mais resistentes à escolha de mínimos locais, aproximando os resultados de qualidade aos obtidos pelo algoritmo ótimo, no entanto, mantendo uma redução significativa no custo computacional. Este trabalho também foca no desenvolvimento de arquiteturas de hardware dedicadas para os novos algoritmos. Estas arquiteturas tem foco em desempenho para a codificação de vídeos de alta definição (mínimo HD 1080p) em tempo real, a 30 quadros por segundo. Esta é uma área importante, principalmente para aplicações em tempo real para dispositivos móveis, onde os requisitos de taxa de processamento e consumo de energia são críticos.

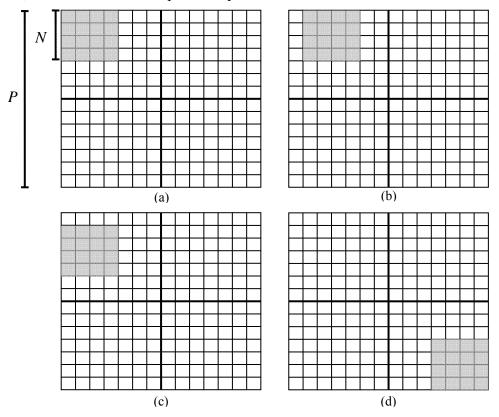

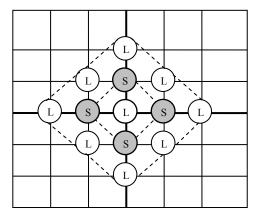

Os algoritmos rápidos de EM que foram desenvolvidos podem ser classificados em duas classes: Multiponto e Aleatória. Ambas apresentam características que visam à redução da incidência da escolha de mínimos locais na estimação de movimento em vídeos de alta definição. A classe de algoritmos multiponto utiliza a estratégia de dividir a busca em diferentes pontos da área de busca. Nesta classe de algoritmos, foram desenvolvidos os algoritmos Multi-Point Diamond Search (MPDS) e Dinamic Multi-Point Diamond Search DMPDS. Os algoritmos MPDS e DMPDS utilizam cinco núcleos de busca, um aplicado a região central da área de busca e outros quatro divididos entre os quatro setores. A distância dos núcleos de busca dos setores, em relação ao centro, é dada por um parâmetro d, que possui um valo fixo para o algoritmo MPDS e dinâmico para o algoritmo DMPDS. Os algoritmos da segunda classe (Aleatória) utilizam a aleatoriedade no processo de busca como estratégia para diminuir a incidência da escolha de mínimos locais. Todos os algoritmos aleatórios desenvolvidos possuem uma etapa em comum, o sorteio e a avaliação de N blocos candidatos aleatórios dentro da área de pesquisa. Além da etapa de exploração aleatória, cada algoritmo apresenta uma forma diferente de exploração da região central da área de busca e, também, diferentes abordagens de refinamento final que é aplicado sobre os resultados obtidos com a etapa aleatória.

Dez sequências de teste HD 1080p foram utilizadas para a avaliação dos algoritmos desenvolvidos. Os resultados de qualidade e custo computacional foram avaliados e comparados a outros algoritmos da literatura. Os resultados destas avaliações mostraram que os algoritmos desenvolvidos apresentam ganhos de qualidade significativos em relação a outros algoritmos rápidos conhecidos. Desta forma, foi possível reduzir as perdas em relação ao resultado ótimo e, ainda assim, manter ganhos significativos em redução do custo computacional. Os algoritmos desenvolvidos também foram avaliados para sequências de teste WQXGA (2560x1600 pixels) e os resultados demonstram que a eficiência dos algoritmos desenvolvidos se mantém e que os ganhos obtidos sobre algoritmos rápidos convencionais são ainda maiores dos que os obtidos em HD 1080p.

As arquiteturas de hardware dedicadas para os novos algoritmos de EM também são apresentadas. As arquiteturas foram desenvolvidas com foco em alto desempenho, sendo o requisito mínimo o processamento de 30 quadros HD 1080p por segundo. As arquiteturas foram descritas em VHDL e sintetizadas para FPGAs e *standard cells*. As

arquiteturas desenvolvidas apresentam baixa frequência de operação e baixa utilização de recursos de hardware em relação a trabalhos relacionados. Estas características também garantiram os baixos resultados de consumo de energia para a síntese ASIC. Estes resultados foram obtidos devido à eficiência dos algoritmos e das arquiteturas desenvolvidas.

O capítulo 2 deste trabalho apresenta alguns conceitos básicos da codificação de vídeo digital. Estes conceitos serão importantes para a compreensão do restante do texto. No capítulo 3 serão apresentados alguns conceitos sobre a estimação de movimento, discutindo o papel da EM no contexto da codificação de vídeo. Alguns algoritmos clássicos de EM serão apresentados, bem como uma revisão bibliográfica sobre o estado da arte em termos de algoritmos e arquiteturas dedicadas à EM. O capítulo 4 apresenta um estudo mais aprofundado sobre a EM em vídeos de alta definição. Neste estudo, o algoritmo DS (Diamond Search) é comparado com o algoritmo de busca completa (FS - Full Search) com a aplicação em vídeos de diferentes resoluções. Um estudo sobre os mínimos locais também é apresentado, bem como a avaliação do uso de diferentes tamanhos de bloco e níveis de subamostragem de pixel na EM em vídeos de alta definição. O capítulo 5 apresenta os resultados do desenvolvimento algorítmico. Os algoritmos desenvolvidos são descritos e os resultados das avaliações e comparações com outros algoritmos são apresentados. No capítulo 6 são apresentados os resultados do desenvolvimento arquitetural para a EM. As arquiteturas desenvolvidas para os novos algoritmos são descritas, bem como os resultados de síntese para FPGAs e standard cells na tecnologia TSMC 0,18um e 90nm. Este capítulo também apresenta as comparações destes resultados com trabalhos relacionados. Por fim, o capítulo sete apresenta as conclusões e trabalhos futuros apontados por esta tese.

### 2 CONCEITOS DE COMPRESSÃO DE VÍDEO DIGITAL

Neste capítulo serão apresentados alguns conceitos básicos de vídeos e compressão de vídeos digitais, que serão importantes para a compreensão dos demais capítulos apresentados nesta tese.

#### 2.1 Conceitos Básicos de Vídeo Digital

Um vídeo digital é formado por uma sequência de imagens independentes, captadas com um intervalo de tempo determinado. Em geral, para que se obtenha sensação de movimento contínuo (tempo real) é necessária à captação de 24 a 30 imagens (quadros) por segundo (GONZALEZ, 2003). Os quadros são formados por pontos (pixels). Pontos pertencentes ao mesmo quadro e espacialmente vizinhos são chamados de pontos vizinhos. Imagens, também chamadas de quadros (em inglês *frames*), pertencentes à mesma cena e temporalmente próximas, são chamadas de imagens vizinhas. Pontos e imagens vizinhas são geralmente muito similares e esta é uma característica importante de imagens e vídeos digitais. Esta similaridade resulta em grande redundância de informações na sua representação. A redundância em vídeos digitais surge de diferentes formas e todos os codificadores de vídeo atuais consideram as diferentes formas de redundância para aumentar a sua eficiência de compressão.

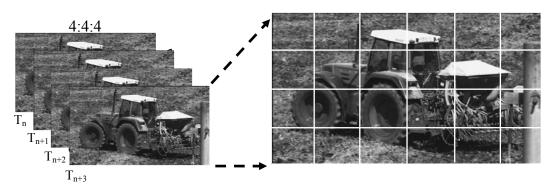

Todo vídeo digital pode ser dividido em uma sequência de quadros. Os codificadores de vídeo ainda dividem, em geral, os quadros em blocos. Estes blocos podem ter tamanhos variados, mas comumente são utilizados tamanhos de 4x4, 8x8 ou 16x16 pixels. A Figura 2.1 ilustra uma sequência de quadros temporalmente vizinhos de um vídeo digital, destacando a divisão de um quadro em blocos de pixels.

Figura 2.1: Sequência de quadros e blocos em um vídeo digital

Uma cena visual natural é contínua no tempo e no espaço, sendo que a representação digital de uma cena visual envolve amostragem espacial e temporal. A amostragem espacial é realizada, normalmente, como uma matriz retangular na imagem do vídeo. Quanto maior esta matriz (resolução), melhor será a definição (qualidade) da imagem, visto que mais pixels serão usados para a representação. A qualidade da imagem é influenciada pela quantidade de pixels. Quanto mais espaçados são os pixels,

menor a resolução da imagem amostrada, assim como quanto mais próximos são os pixels, maior é a resolução da imagem amostrada e, consequentemente, melhor será o resultado visual da imagem.

A amostragem temporal é realizada como uma série de quadros, estáticos, amostrados a certos intervalos de tempo, conforme ilustrado na Figura 2.1. Quanto maior for a taxa de amostragem, melhor será a percepção de movimento no vídeo. Um vídeo captado e exibido a 30 quadros por segundo transmite a sensação de movimento contínuo (tempo real), no entanto, ao assistir este vídeo em câmera lenta (*slow motion*), através da redução da velocidade de exibição (maior tempo entre quadros), alguns movimentos mais rápidos podem ficar prejudicados. Alguns efeitos indesejados como borrões ou *motion blur* podem se tornar perceptíveis. Estes efeitos podem ser evitados com o aumento da taxa de amostragem temporal, por exemplo, para 120 quadros por segundo. Algumas câmeras podem captar centenas de quadros por segundo (FASTEC, 2011) tornando, assim, possível a percepção de movimentos que nunca haviam sido captados por câmeras de vídeos convencionais (cinema, televisão, etc..) que amostram imagens em taxas na ordem de dezenas de quadros por segundo.

Vídeo digital é a representação de uma cena de vídeo amostrada de forma digital. Cada amostra temporal-espacial, chamada elemento de figura (*picture element* ou pixel) é representada como um número, ou um conjunto de números, que representa as componentes de luminância ou cor da amostra, de acordo com o espaço de cor utilizado. Para se obter uma imagem amostrada bidimensionalmente, a câmera foca uma projeção bidimensional da cena de vídeo em um sensor.

#### 2.2 Compressão com Perdas e sem Perdas

Os codificadores de vídeo podem ser classificados entre os que fazem a compressão sem perdas (*lossless*) e os que geram perdas durante o processo de compressão (*lossy*) (RICHARDSON, 2002).

Na compressão sem perdas, os codificadores utilizam apenas técnicas de compressão que não eliminem informações. Isto garante que o arquivo resultante do processo de descompressão é idêntico ao arquivo original. Este tipo de compressão pode ser muito eficiente para diferentes tipos de dados, principalmente para os que apresentam grande quantidade de redundância estatística. Um exemplo de compressão sem perdas muito utilizado é o compressor de arquivos ZIP (SALOMON, 2008). Estes algoritmos reestruturam o arquivo, atribuindo códigos menores para símbolos com maior ocorrência e códigos maiores para símbolos de menor ocorrência. Isto reduz o tamanho do arquivo sem perda de informação. No entanto, imagens e vídeos digitais possuem uma distribuição de probabilidade muito próxima entre os símbolos (neste contexto os valores dos pixels). Compressores de imagens sem perdas eficientes como o JPEG-LS (RICHARDSON, 2003), por exemplo, atingem apenas taxas de compressão da ordem de 3 a 4 vezes.

A compressão com perdas é a mais utilizada para a codificação de imagens e vídeos digitais. Além da relativa ineficiência dos compressores sem perdas neste contexto, o volume de dados a ser processado, armazenado ou transmitido, principalmente em vídeos, é muito elevado e requer taxas de compressão elevadas. Os compressores de vídeo atuais estão baseados no princípio de remover informações de baixa relevância visual (RICHARDSON, 2003). Desta forma, é possível alcançar elevadas taxas de compressão com uma pequena redução na qualidade visual, sendo que muitas vezes esta

perda em qualidade é imperceptível ao sistema visual humano. Compressores de vídeo atuais, como o MPEG-2 e o H.264/AVC podem atingir taxas de compressão entre 24:1 e 50:1, com a qualidade visual muito próxima a do vídeo original (GHANBARI, 2003).

#### 2.3 Espaço de Cores

A representação digital de um vídeo colorido está associada à interpretação das cores pelo sistema visual humano. Existem muitas formas de representar as cores de forma digital. Um sistema para representar cores é chamado de espaço de cores e a definição do espaço de cor a ser utilizado para representar um vídeo é essencial para a eficiência da codificação deste vídeo. São vários os espaços de cores usados para representar imagens digitais, tais como: RGB, HSI e YCbCr (SHI, 1999). O espaço de cores RGB é um dos mais comuns, tendo em vista que é este o espaço de cores utilizado nos monitores coloridos. O RGB representa, em três matrizes distintas, as três cores primárias captadas pelo sistema visual humano: vermelho, verde e azul. A grande maioria das cores perceptíveis pelo olho humano podem ser derivadas a partir de combinações destas três cores primárias. Cada um dos canais R, G e B representa a intensidade de sua respectiva cor e a informação de intensidade luminosa, ou luminância, está distribuída entre os três canais.

No espaço de cores YCbCr, as três componentes utilizadas são: luminância (Y), que define a intensidade luminosa ou o luminância; crominância azul (Cb); e crominância vermelha (Cr) (MIANO, 1999), mas todas as cores representadas pelo espaço RGB são possíveis de serem representadas também no espaço YCbCr. Os componentes R, G e B do espaço de cores RGB possuem um elevado grau de correlação, isto torna difícil o processamento de cada uma das informações de cor de forma independente. Este é o principal fator que faz com que os padrões de compressão de vídeo utilizem espaços de cores do tipo luminância e crominância, como o YCbCr (RICHARDSON, 2002). Outra vantagem do espaço de cor YCbCr sobre o espaço RGB é que, no espaço YCbCr, a informação de cor está completamente separada da informação de luminância. Deste modo, estas informações podem ser tratadas de forma diferenciada pelos compressores de imagens estáticas e vídeos. O canal de luminância (Y) possui apenas as informações de luminância, os canais de crominância azul e vermelha (Cb e Cr) possuem as informações de cor azul e vermelha, respectivamente.

#### 2.4 Subamostragem de Cores

O sistema visual humano possui menor resolução para informações de cor contidas nas imagens (GONZALEZ, 2003). Logo, os padrões de compressão de imagens estáticas e vídeos podem explorar esta característica humana para aumentar a eficiência de codificação através da redução da taxa de amostragem dos componentes de crominância, em relação aos componentes de luminância (RICHARDSON, 2002). Esta operação é chamada de subamostragem de cores e é realizada sob o espaço de cores YCbCr nos padrões de compressão de vídeos atuais.

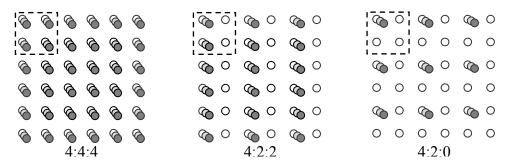

Existem várias formas de relacionar os componentes de crominância com o componente de luminância para realizar a subamostragem. Os formatos mais comuns são o 4:4:4, o 4:2:2 e o 4:2:0. No formato 4:4:4, para cada quatro amostras de luminância (Y), existem quatro amostras de crominância azul (Cb) e quatro amostras de crominância vermelha (Cr). Desta forma, não existe subamostragem de cor e não existirá nenhuma perda de qualidade no vídeo. No formato 4:2:2, para cada quatro amostras de Y, apenas duas amostras de crominância Cb e duas amostras de

crominância Cr são representadas. Com isso, 50% das informações de cor serão descartadas, reduzindo em 25% o tamanho total do vídeo, antes mesmo de qualquer etapa de compressão. O formato 4:2:0, considera que para cada quatro amostras de luminância Y, apenas uma amostra de crominância Cb e uma de Cr são representadas. A Figura 2.2 apresenta estes três formatos de subamostragem de cores.

Figura 2.2: Formatos de subamostragem de crominância (RICHARDSON, 2002)

A subamostragem de cor aumenta significativamente a eficiência da compressão, uma vez que parte da informação da imagem é simplesmente descartada, sem causar impacto visual perceptível. Considerando o formato 4:2:0 como exemplo, apenas 25% das informações de crominância serão consideradas, um quarto das amostras presentes no componente de luminância. Assim, um vídeo YCbCr no formato 4:2:0 irá utilizar exatamente a metade das amostras necessárias para um vídeo RGB ou YCbCr no formato 4:4:4. Isso implica em uma redução de 50% no volume de informações que representam o vídeo, considerando apenas a subamostragem de cores, antes da aplicação de qualquer técnica de compressão de vídeo.

#### 2.5 Redundância de Informação em Vídeos Digitais

A compressão de vídeo é baseada na eliminação de dados redundantes. Um dado é considerado redundante quando seu valor não representa uma nova informação relevante para a representação da imagem. Basicamente, existem três tipos diferentes de redundâncias exploradas na compressão de vídeos: redundância espacial, redundância temporal e redundância entrópica.

A redundância espacial, também chamada de redundância intraframe (GHANBARI, 2003), é resultado da correlação existente entre os pixels vizinhos do mesmo quadro. Pixels vizinhos tendem a possuir valores semelhantes e, por consequência, com elevado grau de redundância de informação, gerando pouco acréscimo de informação visual a cada novo ponto em relação aos seus vizinhos. As características do sistema visual humano fazem com que alguns tipos de informações que podem estar presentes na imagem não sejam captadas. Além disso, algumas informações da imagem, como o luminância, por exemplo, são mais importantes para o sistema visual humano do que outras, como as cores. Para explorar este tipo de redundância, parte da informação original da imagem é eliminada de forma irreversível pelo codificador. Existem três tipos principais de processos utilizados para este fim. O primeiro, chamado de subamostragem, que já foi explicado. O segundo, conhecido por quantização, normalmente é aplicado no domínio das frequências e pode eliminar ou atenuar as frequências de menor relevância para o sistema visual humano. Por isso, este tipo de processo de codificação é chamado de codificação com perdas. É importante destacar que a eliminação destas informações contribui para que o codificador atinja elevadas taxas de compressão, com pequeno impacto na qualidade visual da imagem que, eventualmente, pode mesmo ser nulo. O terceiro método de compressão amplamente utilizado nos codificadores de vídeo atuais, para reduzir a redundância espacial, é a codificação intra-quadro.

A redundância temporal, também chamada de redundância inter-quadros ou interframe (GHANBARI, 2003), é causada pela correlação existente entre quadros vizinhos. Na verdade, a redundância temporal poderia ser classificada como apenas mais uma dimensão da redundância espacial, como faz (GONZALEZ, 2003). Muitos blocos de *pixels* simplesmente não mudam de valor de um quadro para outro em um vídeo, como por exemplo, em um fundo que não foi alterado de um quadro para outro. Outros pixels apresentam uma pequena variação de valores causada, por exemplo, por uma variação de iluminação. Também é possível que o bloco de pixels simplesmente tenha se deslocado de um quadro para o outro, como por exemplo, em um movimento de um objeto em uma cena. Estes fatores resultam em um pequeno acréscimo de informação visual de cada imagem com relação às imagens vizinhas. Todos os padrões de codificação de vídeo atuais visam eliminar ou diminuir a redundância temporal. A exploração eficiente da redundância temporal conduz a elevadas taxas de compressão e é fundamental para o sucesso dos codificadores.

A redundância entrópica está relacionada com a forma de representação computacional dos símbolos codificados e não se relaciona diretamente ao conteúdo da imagem. A entropia é uma medida da quantidade média de informação transmitida por símbolo do vídeo (SHI, 1999). A quantidade de informação nova transmitida por um símbolo diminui na medida em que a probabilidade de ocorrência deste símbolo aumenta. Então, os codificadores que exploram a redundância entrópica têm por objetivo transmitir o máximo de informação possível por símbolo codificado e, deste modo, representar mais informações com um número menor de símbolos. A codificação de entropia, como é chamada, utiliza diferentes técnicas e algoritmos de compressão sem perdas para atingir este objetivo.

#### 2.6 Avaliação de Qualidade em Vídeos Digitais

A avaliação de qualidade em vídeos digitais é um problema muito complexo. Existem diversas métricas objetivas para a avaliação de qualidade e a maioria delas utiliza equações matemáticas aplicadas aos valores dos pixels, antes e depois da compressão, para definir a qualidade do processo. No entanto, nenhuma das métricas existentes considera de maneira eficiente as questões subjetivas que um observador humano consegue perceber.

O critério de avaliação de qualidade objetivo mais utilizado é o PSNR (*Peak Signal-to-Noise Ratio*) (GHANBARI, 2003), apresentado na equação (1). O valor de *MAX* corresponde ao valor máximo que pode ser assumido por uma amostra e normalmente este valor é igual a 255, que é o valor máximo para amostras de oito bits. *MSE* é a sigla para *Mean Squared Error*, que calcula o erro médio quadrático dos pixels de um quadro, conforme a equação (2). As variáveis *R* e *O* são os quadros original e reconstruído (após a compressão e descompressão), respectivamente. As variáveis *m* e *n* representam as dimensões do quadro. O PSNR pode ser calculado para um quadro ou apenas para um bloco deste quadro. Seus resultados podem ser acumulados para a geração do PSNR de um quadro completo ou de um vídeo. Os valores de PSNR são medidos em decibéis (dB), sendo que para quadros idênticos, que resultam em um valor de MSE = 0, o valor do PSNR será indefinido. Em geral, é possível afirmar que altos valores de PSNR indicam uma qualidade relativamente alta da imagem e baixos valores

de PSNR indicam uma qualidade relativamente baixa na imagem (RICHARDSON, 2002).

$$PSNR_{dB} = 20 \cdot \log_{10} \left( \frac{MAX}{\sqrt{MSE}} \right) \tag{1}$$

$$MSE = \frac{1}{mn} \sum_{i=0}^{m-1} \sum_{i=0}^{n-1} (R_{i,j} - O_{i,j})^2$$

(2)

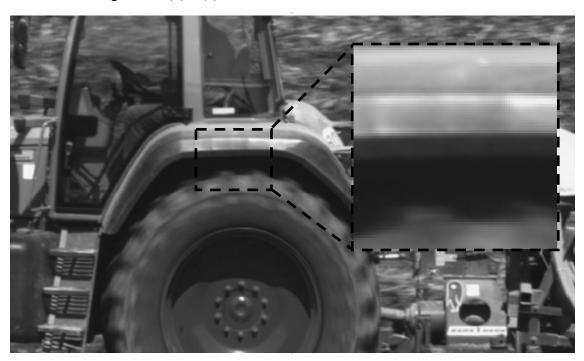

Mesmo o PSNR sendo a métrica de qualidade objetiva mais aceita pela comunidade científica, esta métrica não consegue identificar critérios subjetivos presentes em imagens e vídeos digitais. Um exemplo disto pode ser observado nas Figuras 2.3, 2.4 e 2.5. A Figura 2.3 apresenta a imagem original e as Figuras 2.3 e 2,4, apresentam uma versão modificada da imagem original. Na Figura 2.4, o fundo da imagem está embaçado e esta imagem possui um PSNR de 26,8dB. A Figura 2.4 apresenta uma versão da imagem original com a parte frontal do caminhão embaçada e esta imagem possui um PSNR de 28,4dB. Claramente, a Figura 2.5 possui uma qualidade visual inferior, no entanto, o PSNR dela é superior ao da Figura 2.4. Isto ocorre porque o PSNR considera o cálculo do MSE entre os pixels para definir o seu valor de qualidade. Na Figura 2.5, a região da parte frontal do caminhão possui uma grande diferença em relação à imagem original (Figura 2.3), no entanto, os demais pixels do quadro possuem uma diferença nula. Já a Figura 2.4, possui uma grande variação nos pixels do fundo da imagem e isto faz com que, na média, o MSE da Figura 2.5 seja menor do que o obtido pela Figura 2.4, mesmo que visualmente o resultado seja inferior. Observadores humanos darão uma importância maior à região frontal do caminhão, em detrimento à região do fundo da imagem. Este tipo de questão subjetiva pode não ser captada pelas métricas objetivas de qualidade como o PSNR.

Figura 2.3: Imagem Original

Figura 2.4: Imagem modificada com fundo embaçado, PSNR 26,8dB

Figura 2.5: Imagem modificada com a parte da frente do caminhão embaçada, PSNR  $$28,\!4\text{dB}$$

### 3 A ESTIMAÇÃO DE MOVIMENTO

As taxas de amostragem dos vídeos digitais variam entre 24 a 30 quadros por segundo, para garantir o efeito de movimento contínuo. Esta taxa tem crescido nos últimos anos, visando a melhoria da captação dos movimentos e a possibilidade de análise dos movimentos em câmera lenta (slow motion). Algumas câmeras atuais podem captar centenas de quadros por segundo (FASTEC, 2011). Neste contexto, ao analisar as imagens de um trecho de um vídeo digital, é possível perceber que as imagens vizinhas são muito similares. As diferenças são geradas, em sua maioria, por movimentos da câmera ou de objetos pertencentes à cena, exceto quando existem cortes de cena com troca de contexto visual. Esta característica dos vídeos digitais produz uma grande redundância temporal e ao comparar dois quadros vizinhos, é possível obter uma enorme quantidade de informações repetidas (redundantes), causadas por regiões da cena que não são alteradas em quadros subsequentes.

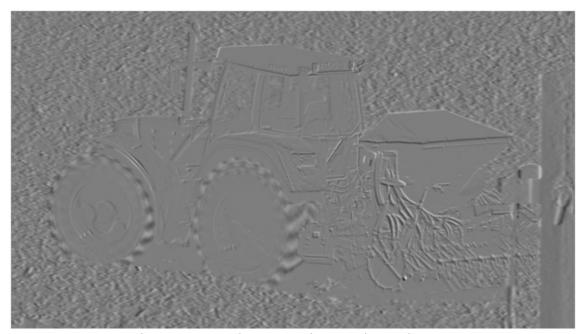

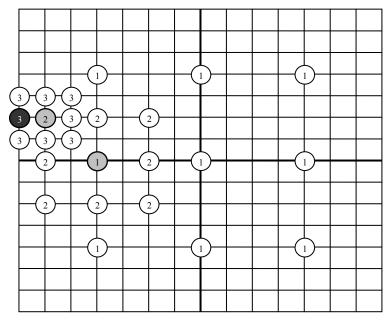

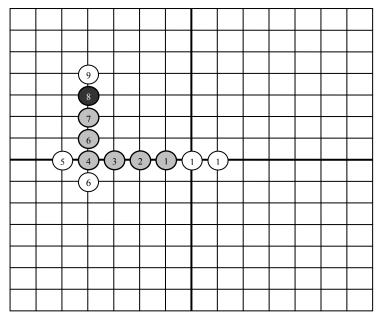

Para explicar melhor a importância da estimação de movimento na compressão de vídeos digitais, as Figuras 3.1 e 3.2 serão analisadas. Estas figuras representam, respectivamente, dois quadros temporalmente vizinhos de uma sequência de vídeo. É possível observar que as diferenças entre os quadros das Figuras 3.1 e 3.2 são praticamente imperceptíveis visualmente. Grande parte da imagem permanece estática e não sofre alterações de um quadro para outro. A Figura 3.3 foi gerada a partir da diferença (pixel a pixel) entre os quadros das Figuras 3.1 e 3.2 (codificação diferencial), ilustrando as diferenças existentes entre os dois quadros. Nas regiões onde a imagem não se altera, o valor dos pixels também não se altera, o que resulta em um resíduo (resultado da diferença entre duas imagens) de valor zero. Para as regiões que sofrem algum tipo de alteração, a diferença entre os pixels dos dois quadros resulta em um valor não nulo. Estas diferenças aparecem na Figura 3.3 como regiões claras, para diferenças positivas, e regiões escuras, para diferenças negativas. A imagem é ajustada para exibição somando-se o valor médio de um pixel a todos os pixels da imagem, para que os pixels iguais a zero tenham uma tonalidade de cinza médio. É possível observar que as diferenças ocorrem em toda a região de fundo, devido ao movimento da câmera. Além disso, existe movimentação de deslocamento do trator e também de partes móveis, como as rodas do trator. Estas diferenças são bastante significativas, sendo que nos pontos brancos, ou pretos, existem diferenças iguais, ou muito próximas, ao valor máximo.

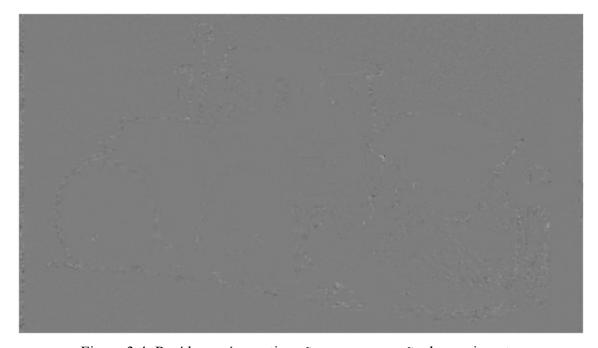

Os resíduos gerados pela codificação diferencial podem ser drasticamente reduzidos com a estimação de movimento (EM). A Figura 3.4 ilustra a imagem resultante dos resíduos gerados entre os quadros das Figuras 3.1 e 3.2 após o processo de estimação de movimento. É possível perceber uma diminuição significativa na quantidade de ruído da imagem, na comparação com a imagem da Figura 3.3. Isto se deve ao processo de identificação de blocos similares realizado pela estimação de

movimento. Ao remontar o quadro, utilizando as informações da estimação de movimento, é possível reduzir as diferenças causadas pelos movimentos de um quadro para outro, reduzindo, assim o resíduo.

Figura 3.1: Quadro 1

Figura 3.2: Quadro 2

Figura 3.3: Resíduo sem estimação de movimento

Figura 3.4: Resíduo após a estimação e compensação de movimento

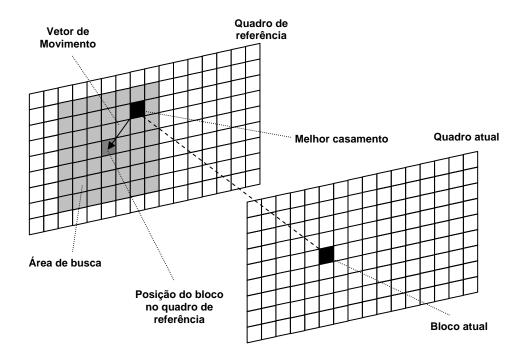

A estimação de movimento visa identificar e reduzir a redundância temporal entre imagens vizinhas de uma cena. Para isso, a EM mapeia as informações redundantes através de vetores de movimento. Os vetores de movimento são vetores de duas dimensões, no formato (x, y), que indicam o deslocamento espacial de um bloco em um quadro, em relação a um quadro de referência. Desta forma, a EM realiza um casamento de padrões de um quadro em relação a outro, que não necessariamente indica a existência de movimento em uma determinada região.

O processo de estimação de movimento para um quadro (quadro atual) começa com a definição do quadro de referência. Mais de um quadro de referência pode ser usado no processo, como será melhor explicado nas próximas sessões do texto. Para cada bloco do quadro atual, será gerado um vetor de movimento, que corresponderá ao deslocamento deste bloco em relação ao quadro de referência. Os blocos do quadro atual serão comparados com os blocos do quadro de referência, para isso, algum critério de similaridade deverá ser utilizado, como o MSE (já explicado no capítulo anterior) ou a soma de diferenças absolutas (SAD – *Sum of Absolute Differences*), por exemplo (KUHN, 1999). O bloco que obtiver a menor diferença, de acordo com o critério similaridade adotado, será o escolhido para representar o bloco do quadro atual.

O SAD consiste na soma das diferenças absolutas entre as amostras do bloco atual e dos blocos do quadro de referência. Este critério é um dos mais utilizados, principalmente para o desenvolvimento em hardware, devido à sua simplicidade. A equação (3) define o cálculo do SAD, onde R são as amostras do bloco de referência e O são as amostras do bloco do quadro de referência.

$$SAD = \sum_{i=0}^{m-1} \sum_{j=0}^{n-1} \left| R_{i,j} - O_{i,j} \right|$$

(3)

O SAD pode ser desenvolvido em hardware utilizando apenas somas e subtrações, pois não exige nenhuma operação de divisão ou exponenciação, como o MSE. Mesmo sendo mais simples, o SAD oferece bons resultados para o processo de EM. A Figura 3.5 ilustra os elementos presentes no processo de estimação de movimento. A EM pode utilizar todo o quadro de referência como área de busca, para encontrar o bloco mais similar ao bloco do quadro atual. No entanto, geralmente, uma área de busca (menor que o quadro) é determinada no quadro de referência para cada bloco do quadro atual. Esta estratégia é utilizada para reduzir a complexidade computacional da estimação de movimento. Esta área deve abranger uma região ao redor da posição original do bloco, pois a possibilidade de encontrar blocos similares, próximos à posição original, é elevada (KUO, 2009), (LAI, 2010). Cada bloco da área de busca é chamado de bloco candidato, pois qualquer um deles pode ser escolhido no processo de estimação.

Para definir a escolha do bloco candidato é necessária a utilização de um algoritmo de busca. O algoritmo de busca determina a maneira como a busca será realizada dentro da área de busca. Existem diversos algoritmos de busca publicados na literatura, cada um deles com características distintas. A escolha do algoritmo de busca tem grande influência na qualidade dos vetores de movimento gerados. Neste texto, a qualidade dos vetores de movimento será medida pelo valor do resíduo gerado pelo bloco candidato escolhido. Alguns algoritmos têm compromisso apenas com a qualidade dos vetores, sem considerar a complexidade computacional necessária para a sua implementação. Outros algoritmos têm compromisso com a baixa complexidade, em detrimento da qualidade dos vetores gerados. Em geral, algoritmos com maior complexidade computacional resultam em melhores resultados de qualidade dos vetores de movimento gerados. No entanto, algoritmos de busca atuais visam aliar baixo custo em complexidade com alto desempenho em termos de qualidade dos vetores de movimento. Na seção 3.3 alguns exemplos de algoritmos de busca para a EM serão explicados mais detalhadamente.

Figura 3.5: Elementos presentes no processo de estimação de movimento (PORTO, 2008d)

A estimação de movimento dos padrões de compressão de vídeos atuais trabalha sobre as informações de luminância do vídeo. As informações de crominância não são consideradas na EM. Os vetores são definidos para a luminância e a crominância reusa estes vetores. Esta estratégia é utilizada, pois as informações de crominância são menos relevantes para a composição do vídeo. Alguns algoritmos preveem também o uso da EM em informações de crominância (ZHIHANG, 1994), (ADIKARI, 2006), mas tais algoritmos não são foco deste trabalho. Na EM, um vetor de movimento é gerado para cada bloco de luminância do quadro atual. O processo de EM implica em uma grande complexidade computacional, no entanto, pode gerar uma redução significativa da quantidade de informação necessária para formar o vídeo, quando um bom casamento (bloco muito semelhante) é encontrado. Todas as informações contidas em um bloco (4x4 ou 8x8 ou 16x6 pixels, etc...) são substituídas por um vetor de duas dimensões, acompanhado de uma informação de resíduo. O resíduo é a diferença pixel a pixel do bloco do quadro atual e o bloco escolhido do quadro de referência. Um bom algoritmo de EM pode gerar resíduos de baixa amplitude, com valores tendendo a zero. O resíduo ainda pode ser muito comprimido através de outras técnicas de compressão, presentes nos codificadores de vídeo. O processo completo de compressão de vídeo em um codificador atual será apresentado no próximo capítulo deste texto.

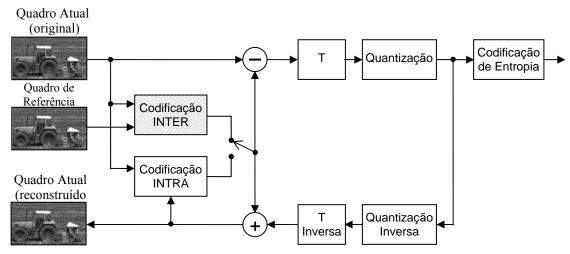

# 3.1 Modelo de Codificador de Vídeos Digitais

A Figura 3.6 apresenta o diagrama em blocos de um codificador de vídeo genérico (AGOSTINI, 2007). Este modelo de codificador está de acordo com a grande maioria dos padrões de compressão de vídeo atuais. Os principais blocos que compõem o codificador são: Codificação inter-quadros, codificação intra-quadro, transformadas (T), quantização e codificação de entropia. Cada um destes blocos trabalha para reduzir um

determinado tipo de redundância existente nos vídeos digitais, sejam elas espaciais, temporais ou entrópicas.

Figura 3.6: Modelo genérico de codificador de vídeo (AGOSTINI, 2007)

A EM está situada dentro do processo da codificação inter-quadros (*interframe*) e é responsável por identificar a redundância temporal entre os quadros vizinhos de uma cena. Esta é a etapa que apresenta a maior complexidade computacional de todo o codificador (PURI, 2004), no entanto, é na EM que se obtêm a maior parte dos ganhos em termos de taxa de compressão. Os vetores de movimento gerados pela EM são utilizados pela etapa de compensação de movimento – CM (*motion compensation*), que também está presente no bloco de codificação inter-quadros. A CM é responsável por remontar os quadros a partir dos vetores de movimento gerados pela EM e montar o quadro reconstruído.

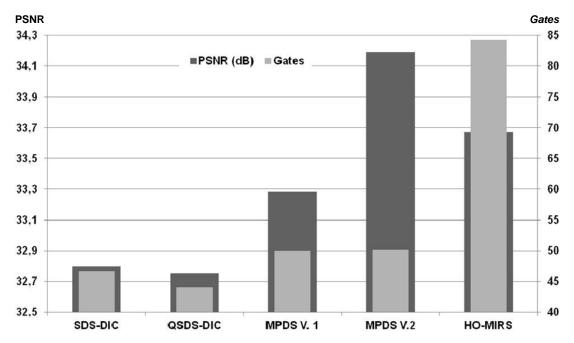

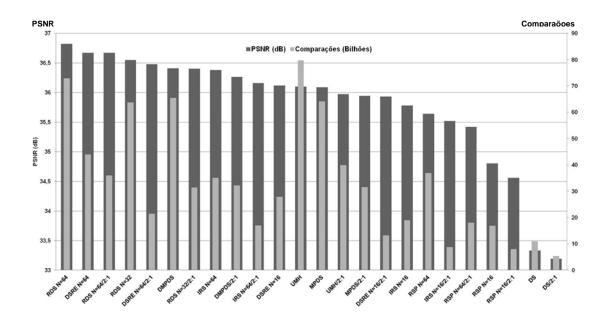

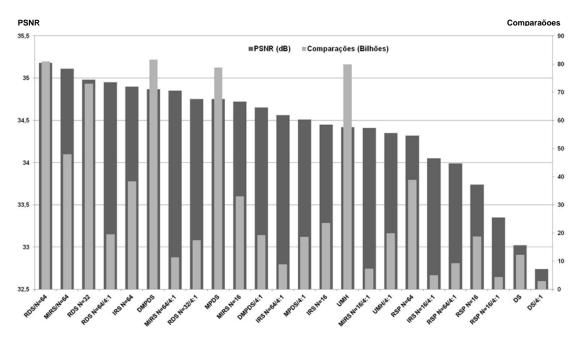

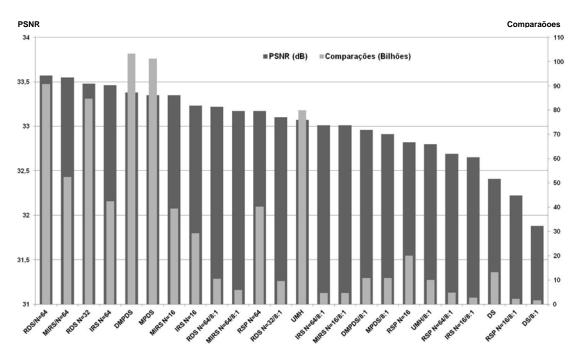

O bloco de codificação intra-quadro (*intraframe*) é um dos responsáveis por reduzir as redundâncias espaciais. Diferentemente da EM, a codificação intra-quadro utiliza apenas as informação do quadro atual para realizar a predição. Vários algoritmos podem ser utilizados para este fim, como por exemplo, os algoritmos utilizados em compressão de imagens estáticas (SALOMON, 2006).