# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

# ÉRIKA FERNANDES COTA

# Reuse-based Test Planning for Core-based Systems-on-chip

Thesis presented in partial fulfillment of the requirements for the degree of Doctor of Computer Science

Prof. Dr. Marcelo Lubaszewski Advisor

# CIP - CATALOGAÇÃO NA PUBLICAÇÃO

## Cota. Érika Fernandes

Reuse-based Test Planning for Core-based Systems-on-chip / Érika Fernandes Cota. – Porto Alegre: Programa de Pós-Graduação em Computação, 2003.

166 f.: il.

Thesis (Ph.D.) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação, Porto Alegre, BR–RS, 2003. Advisor: Marcelo Lubaszewski.

1. SoC testing. 2. Testing of embedded cores. 3. Design for test. 4. Design space exploration. 5. Network-on-chip. I. Lubaszewski, Marcelo. II. Título.

## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitora: Profa. Wrana Maria Panizzi

Pró-Reitor de Ensino: Prof. José Carlos Ferraz Hennemann Pró-Reitora Adjunta de Pós-Graduação: Profa. Jocélia Grazia

Diretor do Instituto de Informática: Prof. Philippe Olivier Alexandre Navaux

Coordenador do PPGC: Prof. Carlos Alberto Heuser

Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

# **ACKNOWLEDGMENTS**

I am beholden to my advisor, Dr. Marcelo Lubaszewski, for his encouraging discussions, unconditional support, and trust during all these years. I also want to express my gratitude to Dr. Luigi Carro for his questioning and passionate attitude and inspiring suggestions, remembering me what research is all about. It has been a pleasure to collaborate with Dr. Altamiro Susin, who reminds me how important it is to let the apparently improbable ideas grow.

From the test research community, I am indebted to the numerous researches whom I had the opportunity to work with: Dr. Alex Orailoglu from the Reliable Systems Synthesis Laboratory of UCSD, for the technical discussions and for showing me other aspects of the research; Erik Jan Marinissen, from Philips, for his friendship and encouragement. It has been a pleasure to collaborate with Dr. Michel Renovell, Dr. Florence Azaïs, Dr. Bruno Rouzeyre, Dr. Yves Bertrand, among others from the LIRMM Laboratory. I have enjoyed to collaborate in different projects with Dr. Raoul Velazco and Dr. Salvador Mir, from TIMA Laboratory.

From home, I am immensely grateful to my "Little Trem", Luigi, for his infinite patience (considering his explosive mood...) and unrestricted support; I cannot say enough thanks to my parents, José Cota and Maristella, for all their history and effort that brought me up to this point; thanks to my parents-in-law, Cesare and Esther, for their affection and help during this time.

It has been a pleasure to share the office with my colleagues of Ph.D. and M.Sc.: Márcio Kreutz, César Zeferino, Margrit Krug, Júlio Mattos, Lisane de Brisolara, Marcelo Negreiros, Adão Júnior, José Güntzel, and Marcelo Johann. I am grateful for their support and friendship. I am also grateful to Fernanda Lima and Zingara, who became dear friends in the last (tough) years.

Thanks are due to the Informatics Institute staff: Luis Otávio and his team: Margareth, Jorge, Júnior, Leandro, and Elgio, for the infra-structure; Bia and the library team: Ida, Henrique, and Adriana; Eliane, Sr. Astro, and the security people; Silvana and the administrative team: Lourdes, Jorge, Schneider, Elisiane, Angela, Claudia, and Alex, also for the infra-structure;

I also want to thank some students that have worked with me in the last few years, and that helped generating some of the results presented in this thesis: Lisane de Brisolara, Cristiano Lazzari, Leandro Cassol, Eduardo Back, Rodrigo Boccasius, Renato Hentschk, and Guilherme Schneider.

I want to express my gratitude to the members of the jury of my thesis proposal, Erik Jan Marinissen, Dr. Raoul Velazco, Dr. Altamiro Susin, and Dr. Ingrid Jansch Porto, for their comments during the definition of this thesis. Finally, I want to thank the members of the final jury, Dr. Antônio Otávio Fernandes, Dr. Marius Strum, and Dr. Altamiro

Susin, for their participation and evaluation.

I acknowledge the work of CNPq and CAPES for the scholarships during this Ph.D and the "sandwich" internship at San Diego, respectively. Finally, I am once again grateful to the brazilian taxpayers (more than never, the real ones) that financed this work.

# **CONTENTS**

| LIST                                                | OF ABBREVIATIONS AND ACRONYMS                                                                                                                          | 9                                      |

|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| LIST                                                | OF FIGURES                                                                                                                                             | 11                                     |

| LIST                                                | OF TABLES                                                                                                                                              | 13                                     |

| ABS                                                 | TRACT                                                                                                                                                  | 15                                     |

| RES                                                 | имо                                                                                                                                                    | 17                                     |

| 1 II                                                | NTRODUCTION                                                                                                                                            | 19                                     |

| 2 S<br>2.1<br>2.2<br>2.3<br>2.3.1<br>2.3.2<br>2.3.3 | Reuse-based SoC Design  NoC-based SoC Design  Test Challenges in SoC Design  Core Test Requirements  Interconnection Requirements  System Requirements | 23<br>23<br>25<br>28<br>28<br>30<br>30 |

| 3 R<br>3.1                                          | RELATED WORKS AND MOTIVATIONS                                                                                                                          | 33<br>33                               |

| 3.2<br>3.3                                          | Test Scheduling Definition                                                                                                                             | 40<br>42                               |

| 3.4.1<br>3.4.2                                      | Test Standard Initiatives                                                                                                                              | 43<br>43<br>45                         |

| 3.4.3<br>3.5                                        | ITC'02 SoC Test Benchmarks                                                                                                                             | 45<br>46                               |

|                                                     | TEST PLANNING AND DESIGN SPACE EXPLORATION IN CORE-                                                                                                    | 49                                     |

| 4.1                                                 | TAM Definition and System Cost Factors                                                                                                                 | 50                                     |

| 4.1.1                                               | Direct External Access                                                                                                                                 | 51                                     |

| 4.1.2                                               | Reuse of Functional Connections                                                                                                                        | 52                                     |

| 4.1.3                                               | Use of Serial Bypass                                                                                                                                   | 53                                     |

| 4.1.4                                               | Use of Transparency Functions                                                                                                                          | 53                                     |

| 4.1.5                                               | Parallel Bypass                                                                                                                                        | 54                                     |

| 4.2                                                 | Problem Statement                                                                                                                                      | 55                                     |

| 4.3        | <b>Solution Modeling</b>                                              |

|------------|-----------------------------------------------------------------------|

| 4.3.1      | Initial Approach                                                      |

| 4.3.2      | Final Approach                                                        |

| 4.4        | The Proposed Heuristic                                                |

| 4.5        | Heuristic Complexity                                                  |

| 4.6        | <b>Experimental Setup</b>                                             |

| 4.6.1      | ITC'02 SoC Test Benchmarks                                            |

| 4.7        | Experimental Results                                                  |

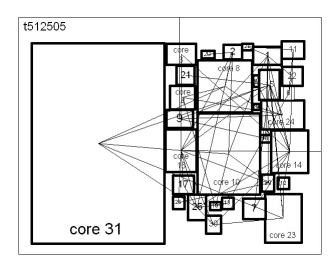

| 4.7.1      | Benchmarks d695, g1023, f2126, q12710, and t512505 66                 |

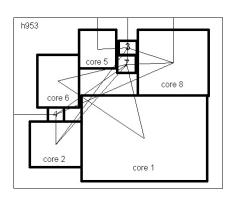

| 4.7.2      | Benchmark h953                                                        |

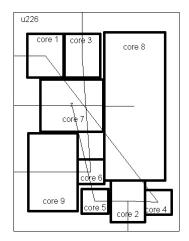

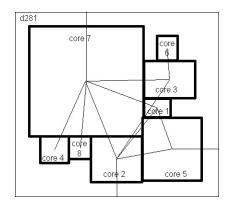

| 4.7.3      | Benchmarks u226 and d281                                              |

| 4.7.4      | Benchmarks p22810, p34392, p93791, and a586710 80                     |

| 4.8        | System Characteristics and Benchmark format                           |

| 5 N        | OC-BASED TESTING OF CORE-BASED SYSTEMS-ON-CHIP 93                     |

| 5.1        | Using the NoC During Test                                             |

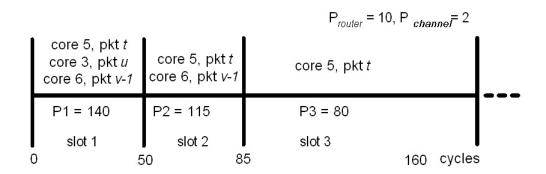

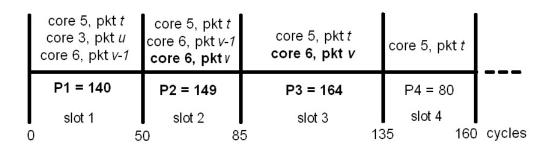

| 5.1.1      | Exploiting pipeline within the NoC                                    |

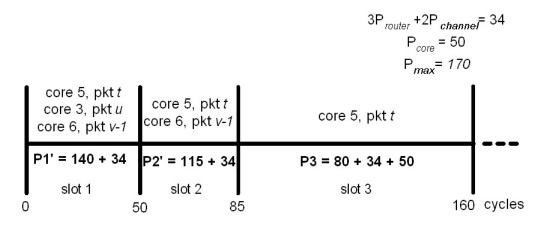

| 5.1.2      | Power Consumption Calculation                                         |

| 5.1.3      | Power-Aware Test Scheduling                                           |

| 5.1.4      | Example                                                               |

| 5.2        | Complexity Analysis                                                   |

| 5.3        | Experimental Results                                                  |

| 5.3.1      | Benchmarks d695, g1023, f2126, q12710, and t512505 108                |

| 5.3.2      | Benchmark h953                                                        |

| 5.3.3      | Benchmarks u226 and d281                                              |

| 5.3.4      | Benchmarks p22810, p34392, p93791, and a586710                        |

| <b>5.4</b> | System Configurations and Resulting Test Time                         |

| 5.4.1      | Placement of the Cores in the Network                                 |

| 5.4.2      | Number of Interfaces with the Tester                                  |

| 5.4.3      | Network Power Profile                                                 |

| 6 D        | <b>ISCUSSION</b>                                                      |

| 6.1        | Reuse-based versus NoC-based Test Planning                            |

| 6.2        | Reuse-based versus Bus-based Test Planning                            |

| 6.3        | Limitations of the Proposed Methods                                   |

|            | •                                                                     |

| 7 FI       | <b>NAL REMARKS</b>                                                    |

| REFE       | RENCES                                                                |

| APPE       | ENDIX A PLANEJAMENTO DE TESTE BASEADO EM REUSO PARA SISTEMAS EM SIL{I |

| APPE       | ENDIX B CD-ROM DESCRIPTION                                            |

# LIST OF ABBREVIATIONS AND ACRONYMS

API Application Programming Interface

ATE Automatic Test Equipment

BIST Built-In Self Test

CAD Computer-Aided Design

CTL Core Test Language

CUT Circuit under test

DFT Design for test

HDL Hardware Description Language

IP Intellectual Property

ITRS International Technology Roadmap for Semiconductors

NoC Network-on-chip

P1500 SECT P1500 Standard for Embedded Core Test

RTL Register Transfer Level

RTOS Real Time Operating System

SIA Semiconductor Industry Association

SoB System-on-board

SoC System-on-chip

TAM Test Access Mechanism

TAP Test Access Port

STIL Standard Test Interface Language

UDL User defined logic

VSIA Virtual Socket Interface Alliance

# LIST OF FIGURES

| Figure 2.1:  | Core types (KUCUKCAKAR, 1998)                                                | 24 |

|--------------|------------------------------------------------------------------------------|----|

| Figure 2.2:  | Example of SoC with super-cores and UDL (ZORIAN, 1997)                       | 25 |

| Figure 2.3:  | Some NoC topologies                                                          | 27 |

| Figure 2.4:  | Differences between SoB and SoC testing (MARINISSEN; ZORIAN, 1999)           | 29 |

| Figure 3.1:  | Conceptual architecture for the SoC testing (ZORIAN; MARINIS-SEN; DEY, 1998) | 34 |

| Figure 3.2:  | Relationship between TAM width and test costs                                | 35 |

| Figure 3.3:  | Test Bus Architectures (AERTS; MARINISSEN, 1998)                             | 37 |

| Figure 3.4:  | Test Rail Achitecture (MARINISSEN et al., 1998)                              | 38 |

| Figure 3.5:  | Flexible-width test bus architecture (IYENGAR; CHAKRABARTY;                  |    |

| _            | MARINISSEN, 2002a)                                                           | 38 |

| Figure 3.6:  | P1500 wrapper structure (MARINISSEN et al., 2002)                            | 44 |

| Figure 4.1:  | Core interface                                                               | 50 |

| Figure 4.2:  | Global TAM for a CUT                                                         | 51 |

| Figure 4.3:  | Direct external access TAM                                                   | 52 |

| Figure 4.4:  | Access via functional connections                                            | 52 |

| Figure 4.5:  | Access via serial bypass                                                     | 53 |

| Figure 4.6:  | Access via transparent core                                                  | 54 |

| Figure 4.7:  | Access via Parallel Bypass                                                   | 54 |

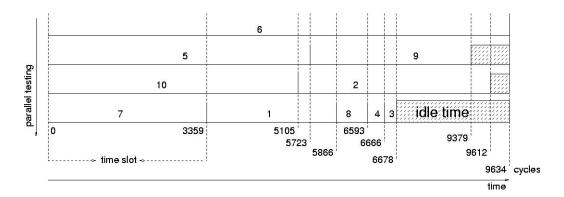

| Figure 4.8:  | Test schedule for minimum test time                                          | 58 |

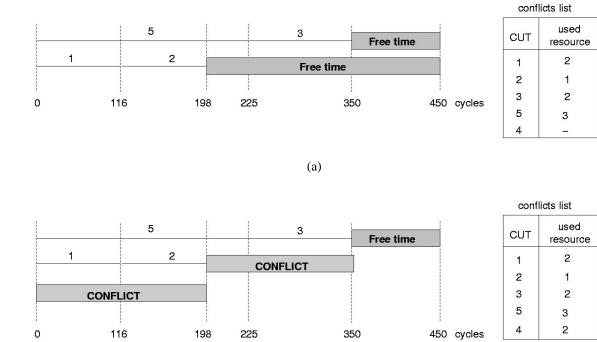

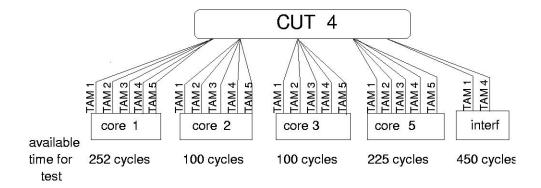

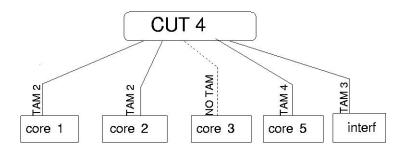

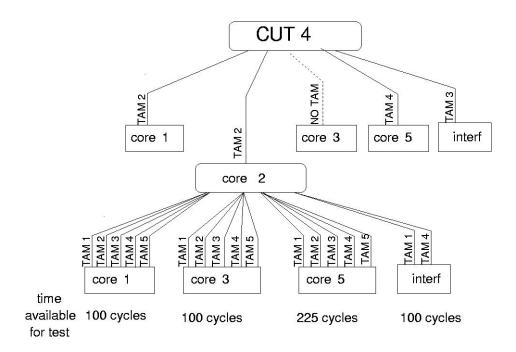

| Figure 4.9:  | Schedule Construction                                                        | 59 |

| Figure 4.10: | Tree Construction                                                            | 60 |

| Figure 4.11: | Pseudo-code of proposed model                                                | 62 |

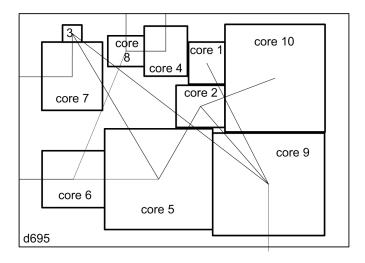

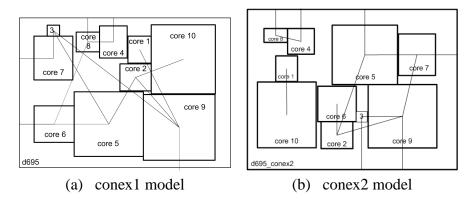

| Figure 4.12: | Floorplanning of benchmark d695                                              | 67 |

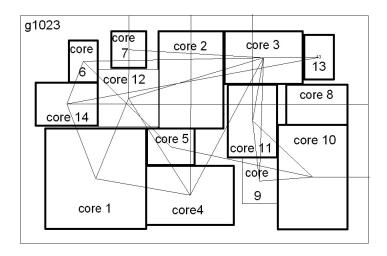

| Figure 4.13: | Floorplanning of benchmark g1023                                             | 69 |

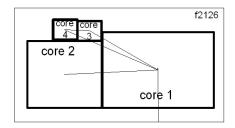

| Figure 4.14: | Floorplanning of benchmark f2126                                             | 71 |

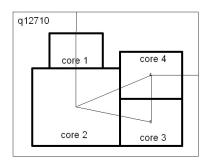

| Figure 4.15: | Floorplanning of benchmark q12710                                            | 72 |

|              | Floorplanning of benchmark t512505                                           | 73 |

| Figure 4.17: | Floorplanning of benchmark h953                                              | 75 |

|              | Floorplanning of benchmark u226                                              | 77 |

| Figure 4.19: | Floorplanning of benchmark d281                                              | 79 |

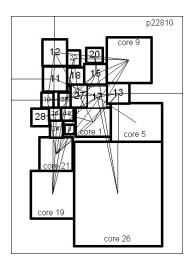

| Figure 4.20: | Floorplanning of benchmark p22810                                            | 82 |

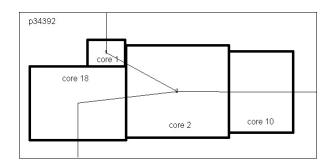

| -            | Floorplanning of benchmark p34392                                            | 83 |

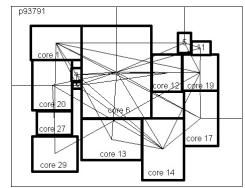

|              | Floorplanning of benchmark p93791                                            | 85 |

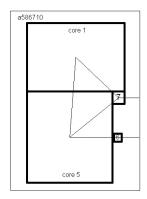

| Figure 4.23: | Floorplanning of benchmark a586710                                           | 85 |

| Figure 4.24: | Two configurations for system d695                                         | 88 |

|--------------|----------------------------------------------------------------------------|----|

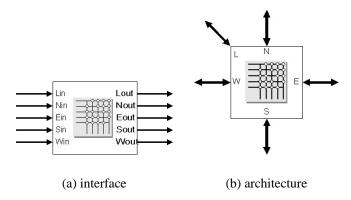

| Figure 5.1:  | Basic structure of the SOCIN router (ZEFERINO; SUSIN, 2003)                | 94 |

| Figure 5.2:  | SOCIN topologies                                                           | 94 |

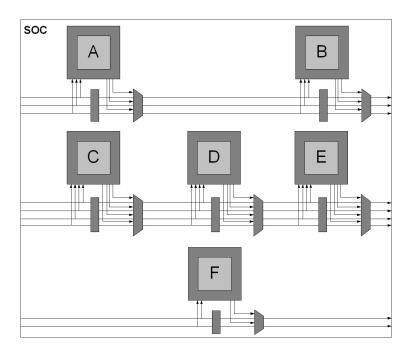

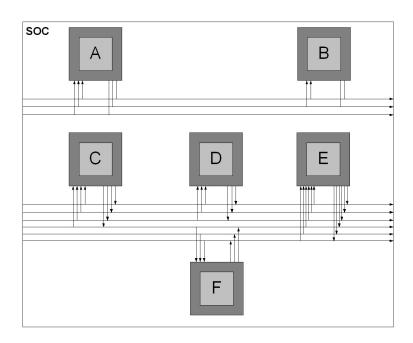

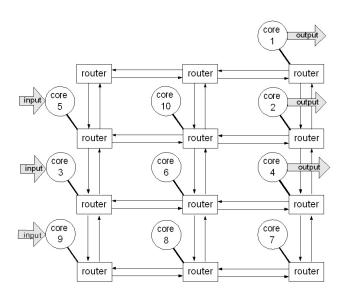

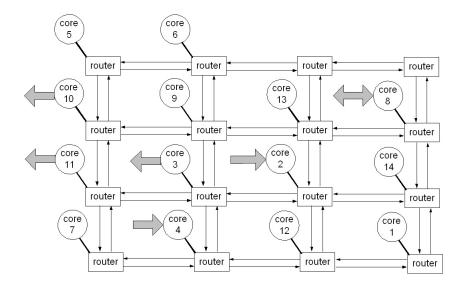

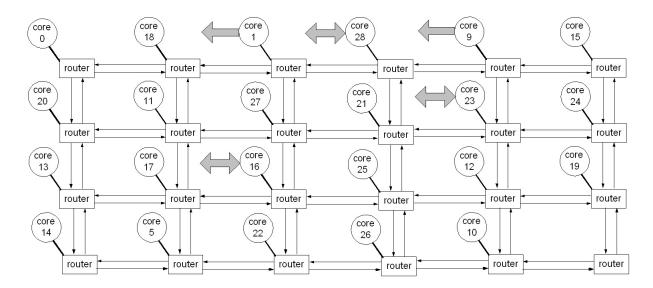

| Figure 5.3:  | System d695 implemented in a 4x3 grid SOCIN NoC                            | 95 |

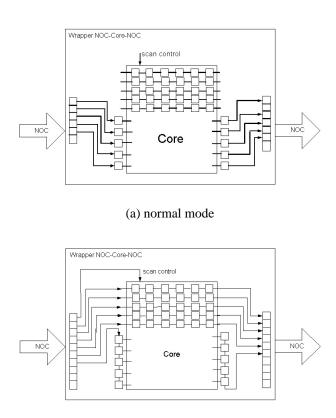

| Figure 5.4:  | Wrapper configurations                                                     | 97 |

| Figure 5.5:  | Pseudo-code of the adapted list-scheduling algorithm                       | 03 |

| Figure 5.6:  | Scheduling process considering power constraints                           | 05 |

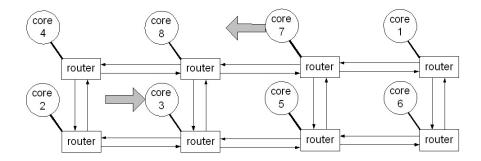

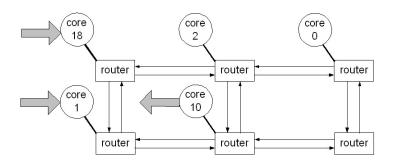

| Figure 5.7:  | System g1023 implemented in a 4x4 NoC                                      | 09 |

| Figure 5.8:  | System f2126 implemented in a 2x2 NoC                                      | 11 |

| Figure 5.9:  | System q12710 implemented in a 2x2 NoC                                     | 11 |

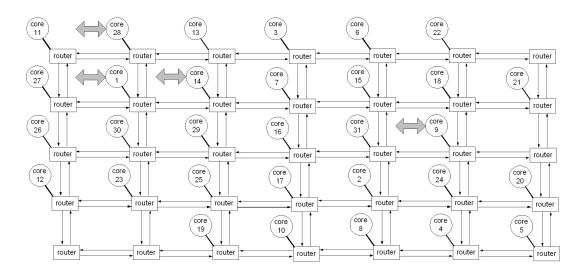

| Figure 5.10: | System t512505 implemented in a 5x7 NoC                                    | 15 |

| Figure 5.11: | System h953 implemented in a 2x4 NoC                                       | 16 |

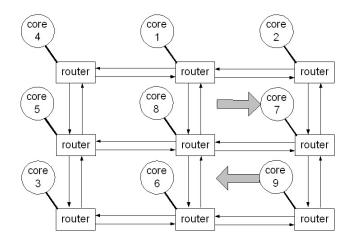

| Figure 5.12: | System u226 implemented in a 3x3 NoC                                       | 17 |

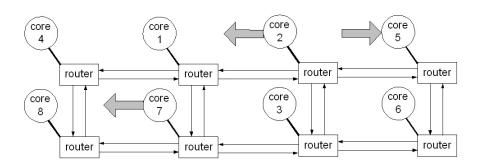

| Figure 5.13: | System d281 implemented in a 2x4 NoC                                       | 18 |

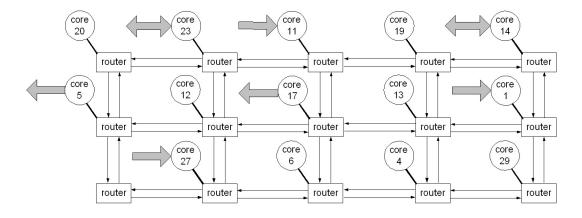

| Figure 5.14: | System p22810 implemented in a 4x6 NoC                                     | 21 |

| Figure 5.15: | System p34392 implemented in a 2x3 NoC                                     | 21 |

| Figure 5.16: | System p93791 implemented in a 3x5 NoC                                     | 22 |

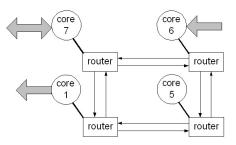

| Figure 5.17: | System a586710 implemented in a 2x2 NoC                                    | 24 |

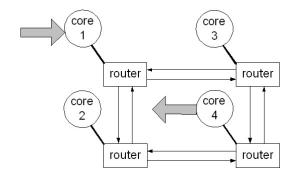

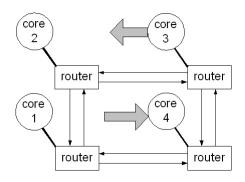

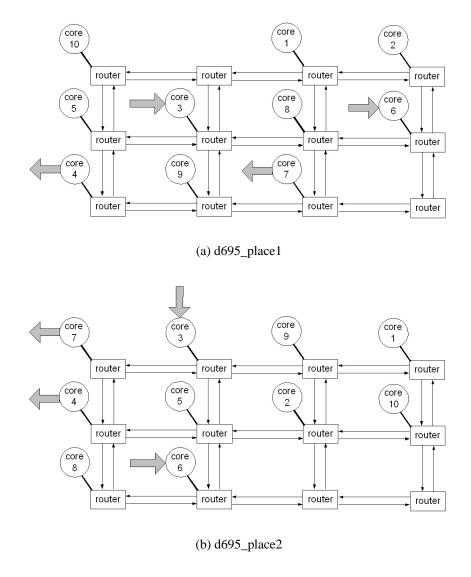

| Figure 5.18: | Different placements for system d695 in a 3x4 network                      | 28 |

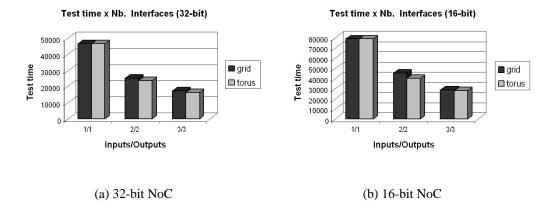

| Figure 5.19: | d695 test time variation with the number of interfaces with the tester . 1 | 28 |

# **LIST OF TABLES**

| Table 4.1:  | Some Characteristics of the ITC'02 Benchmarks (MARINISSEN; IYENGAR; CHAKRABARTY, 2002) |

|-------------|----------------------------------------------------------------------------------------|

| Table 4.2:  | Test requirements of benchmark d695                                                    |

| Table 4.3:  | Test results for benchmark d695                                                        |

| Table 4.4:  | Test requirements of benchmark g1023                                                   |

| Table 4.5:  | Test results for benchmark g1023                                                       |

| Table 4.6:  | Test requirements of benchmark f2126                                                   |

| Table 4.7:  | Test results for benchmark f2126                                                       |

| Table 4.8:  | Test requirements of benchmark q12710                                                  |

| Table 4.9:  | Test results for benchmark q12710                                                      |

| Table 4.10: | Test requirements of benchmark t512505                                                 |

| Table 4.11: | Test results for benchmark t512505                                                     |

| Table 4.12: | Test requirements of benchmark h953                                                    |

| Table 4.13: | Test results for benchmark h953                                                        |

| Table 4.14: | Test requirements of benchmark u226                                                    |

| Table 4.15: | Test results for benchmark u226                                                        |

| Table 4.16: | Test requirements of benchmark d281                                                    |

| Table 4.17: | Test results for benchmark d281                                                        |

| Table 4.18: | Test requirements of benchmark p22810                                                  |

| Table 4.19: | Test results for benchmark p22810                                                      |

| Table 4.20: | Test requirements of benchmark p34392                                                  |

| Table 4.21: | Test results for benchmark p34392                                                      |

| Table 4.22: | Test requirements of benchmark p93791                                                  |

| Table 4.23: | Test results for benchmark p93791                                                      |

| Table 4.24: | Test requirements of benchmark a586710 87                                              |

| Table 4.25: | Test results for benchmark a586710                                                     |

| Table 4.26: | New test planning results for d695                                                     |

| Table 4.27: | New test planning results for p22810                                                   |

| Table 4.28: | New test planning results for p93791                                                   |

| Table 4.29: | New test planning results for u226                                                     |

| Table 5.1:  | Test packets for system d695                                                           |

| Table 5.2:  | Test results for benchmark d695                                                        |

| Table 5.3:  | Test packets for system g1023                                                          |

| Table 5.4:  | Test results for benchmark g1023                                                       |

| Table 5.5:  | Test packets for system f2126                                                          |

| Table 5.6:  | Test results for benchmark f2126                                                       |

| Table 5.7:  | Test packets for system q12710                                        |

|-------------|-----------------------------------------------------------------------|

| Table 5.8:  | Test results for benchmark q12710                                     |

| Table 5.9:  | Test packets for system t512505                                       |

| Table 5.10: | Test results for benchmark t512505                                    |

| Table 5.11: | Test packets for system h953                                          |

| Table 5.12: | Test results for benchmark h953                                       |

| Table 5.13: | Test packets for system u226                                          |

| Table 5.14: | Test results for benchmark u226                                       |

| Table 5.15: | Test packets for system d281                                          |

| Table 5.16: | Test results for benchmark d281                                       |

| Table 5.17: | Test packets for system p22810                                        |

| Table 5.18: | Test results for benchmark p22810                                     |

| Table 5.19: | Test packets for system p34392                                        |

| Table 5.20: | Test results for benchmark p34392                                     |

| Table 5.21: | Test packets for system p93791                                        |

| Table 5.22: | Test results for benchmark p93791                                     |

| Table 5.23: | Test packets for system a586710                                       |

| Table 5.24: | d695 test time for different placements in the network                |

| Table 5.25: | Test time of t512505 for different interface configurations 129       |

| Table 5.26: | Test times for d695: cores consumption >> routers consumption 130     |

| Table 5.27: | Test times for g1023: cores consumption >> routers consumption 130    |

| Table 5.28: | Test times for p22810: cores consumption >> routers consumption . 131 |

| Table 5.29: | Test times for d695: cores consumption≈routers consumption 132        |

| Table 5.30: | Test times for g1023: cores consumption≈routers consumption 132       |

| Table 5.31: | Test times for p22810: cores consumption≈routers consumption 132      |

| Table 5.32: | Test times for p93791: 5 inputs and 4 outputs                         |

| Table 6.1:  | Comparative results between proposed approaches                       |

| Table 6.2:  | Comparative results with bus-based methods for $W = 32 \dots 139$     |

# **ABSTRACT**

Electronic applications are currently developed under the reuse-based paradigm. This design methodology presents several advantages for the reduction of the design complexity, but brings new challenges for the test of the final circuit. The access to embedded cores, the integration of several test methods, and the optimization of the several cost factors are just a few of the several problems that need to be tackled during test planning. Within this context, this thesis proposes two test planning approaches that aim at reducing the test costs of a core-based system by means of hardware reuse and integration of the test planning into the design flow.

The first approach considers systems whose cores are connected directly or through a functional bus. The test planning method consists of a comprehensive model that includes the definition of a multi-mode access mechanism inside the chip and a search algorithm for the exploration of the design space. The access mechanism model considers the reuse of functional connections as well as partial test buses, cores transparency, and other bypass modes. The test schedule is defined in conjunction with the access mechanism so that good trade-offs among the costs of pins, area, and test time can be sought. Furthermore, system power constraints are also considered. This expansion of concerns makes it possible an efficient, yet fine-grained search, in the huge design space of a reuse-based environment. Experimental results clearly show the variety of trade-offs that can be explored using the proposed model, and its effectiveness on optimizing the system test plan.

Networks-on-chip are likely to become the main communication platform of systems-on-chip. Thus, the second approach presented in this work proposes the reuse of the on-chip network for the test of the cores embedded into the systems that use this communication platform. A power-aware test scheduling algorithm aiming at exploiting the network characteristics to minimize the system test time is presented. The reuse strategy is evaluated considering a number of system configurations, such as different positions of the cores in the network, power consumption constraints and number of interfaces with the tester. Experimental results show that the parallelization capability of the network can be exploited to reduce the system test time, whereas area and pin overhead are strongly minimized.

In this manuscript, the main problems of the test of core-based systems are firstly identified and the current solutions are discussed. The problems being tackled by this thesis are then listed and the test planning approaches are detailed. Both test planning techniques are validated for the recently released ITC'02 SoC Test Benchmarks, and further compared to other test planning methods of the literature. This comparison confirms the efficiency of the proposed methods.

**Keywords:** SoC testing, testing of embedded cores, design for test, design space exploration, network-on-chip.

## Planejamento de Teste para Sistemas de Hardware Integrados Baseados em Componentes Virtuais

## **RESUMO**

O projeto de sistemas eletrônicos atuais segue o paradigma do reuso de componentes de hardware. Este paradigma reduz a complexidade do projeto de um *chip*, mas cria novos desafios para o projetista do sistema em relação ao teste do produto final. O acesso aos núcleos profundamente embutidos no sistema, a integração dos diversos métodos de teste e a otimização dos diversos fatores de custo do sistema são alguns dos problemas que precisam ser resolvidos durante o planejamento do teste de produção do novo circuito. Neste contexto, esta tese propõe duas abordagens para o planejamento de teste de sistemas integrados. As abordagens propostas têm como principal objetivo a redução dos custos de teste através do reuso dos recursos de hardware disponíveis no sistema e da integração do planejamento de teste no fluxo de projeto do circuito.

A primeira abordagem considera os sistemas cujos componentes se comunicam através de conexões dedicadas ou barramentos funcionais. O método proposto consiste na definição de um mecanismo de acesso aos componentes do circuito e de um algoritmo para exploração do espaço de projeto. O mecanismo de acesso prevê o reuso das conexões funcionais, o uso de barramentos de teste locais, núcleos transparentes e outros modos de passagem do sinal de teste. O algoritmo de escalonamento de teste é definido juntamente com o mecanismo de acesso, de forma que diferentes combinações de custos sejam exploradas. Além disso, restrições de consumo de potência do sistema podem ser consideradas durante o escalonamento dos testes. Os resultados experimentais apresentados para este método mostram claramente a variedade de soluções que podem ser exploradas e a eficiência desta abordagem na otimização do teste de um sistema complexo.

A segunda abordagem de planejamento de teste propõe o reuso de redes em-chip como mecanismo de acesso aos componentes dos sistemas construídos sobre esta plataforma de comunicação. Um algoritmo de escalonamento de teste que considera as restrições de potência da aplicação é apresentado e a estratégia de teste é avaliada para diferentes configurações do sistema. Os resultados experimentais mostram que a capacidade de paralelização da rede em-chip pode ser explorada para reduzir o tempo de teste do sistema, enquanto os custos de área e pinos de teste são drasticamente minimizados.

Neste manuscrito, os principais problemas relacionados ao teste dos sistemas integrados baseados em componentes virtuais são identificados e as soluções já apresentadas na literatura são discutidas. Em seguida, os problemas tratados por este traballho são listados e as abordagens propostas são detalhadas. Ambas as técnicas são validadas através dos sistemas disponíveis no *ITC'02 SoC Test Benchmarks*. As técnicas propostas são ainda comparadas com outras abordagens de teste apresentadas recentemente. Esta comparação confirma a eficácia dos métodos desenvolvidos nesta tese.

**Palavras-chave:** teste de sistemas integrados, teste de núcleos de hardware embarcados, projeto visando o teste, exploração do espaço de projeto, redes de interconexão em-chip.

## 1 INTRODUCTION

With the increasing complexity of current integrated circuits, testing has become one of the most expensive and time-consuming tasks of the circuit design. The density of current systems-on-chip (SoCs) and the paradigm of core-based design have posed important difficulties for the test of the resulting chip, which are mainly related to the information requirements for the definition of the system test plan. For the new systems, important information must flow from the core providers to the system integrators and finally to the test engineers, who are not necessarily part of the same department or company. Today, the cost of testing a SoC is estimated to be as high as 50% of the total cost of the chip (ZO-RIAN; DEY; RODGERS, 2000) and the reduction of this cost is crucial for the electronic market.

One of the most important problems for the test of a SoC is the access to the embedded cores during test. The increase in the number of metal layers and number of transistors in the same silicon area lead to an increase in the complexity of the electronic systems, which present now a large number of logic blocks deeply embedded into the chip. Such blocks require some type of electronic access during test, since they can not be directly accessed from the system interface. Moreover, such access mechanism is intimately related to the resulting testing costs of the system. For example, a single access mechanism that is shared among all embedded cores reduces the costs in terms of area overhead for the system, but leads to a large test time, since all cores must be tested serially. On the other hand, an exclusive access mechanism for each core results in a very reduced test time, but at a possibly unacceptable cost in terms of area overhead and pin count or, even, power consumption. Therefore, a great deal of effort has been spent in the last few years for the development of cost-effective test techniques for core-based SoCs, all of them aiming at the reduction of the test cost and complexity.

Despite the large number of SoC test approaches proposed in the last few years, one can observe two interesting aspects of such solutions: very few of them reuse the system resources during test, and very few of them consider the integration of the test planning task in the early steps of the SoC design flow. Considering the first aspect, only the first works in SoC testing considered the reuse of system connections and logic for the transmission of test data between an external tester and the embedded cores. The majority of the SoC test solutions nowadays is based on the efficient insertion of test buses. The main reason for this change seems to be the *ad hoc* characteristic of the initial works. In many cases, they assume the modification of the core logic to transmit the test data, which is usually not possible because of the intellectual property (IP) protection of the third part blocks. When the cores are not modified, specific bypass structures around the cores are required. Such structures were not standardized and required an extra effort from the system designer to be implemented. As for the second aspect, because of the complexity

of current systems, the test planning task can no longer be left for the latest stages of the design or the turnaround time of the product can be too high. Usually, the system synthesis already presents a number of problems for the system integrator (BERGAMASCHI et al., 2001): the lack of design tools capable of dealing with the variety of core formats, the lack of a single interface standard to communicate all cores in the system, IP protection issues, the size and complexity of the system, and so on. For most of the test solutions proposed in the literature, the test planning can be defined in parallel with the system design. However, they usually do not consider the system characteristics for the test definition. Only the cores requirements in terms of pins and number of test vectors are considered. Thus, each solution devised by the test plan must be verified by the system integrator separately. On the other hand, the system integrator is not always a test specialist nor is the test engineer a design expert. Moreover, there is a number of other requirements for the system synthesis that must be taken care of. Therefore, test planning tools capable of helping both, test engineers and system integrators to make design decisions at the early stages of the system design are of extreme importance to assure an effective test plan for a SoC. Such tools must take into consideration the system characteristics, such as cores floorplanning, functional connections, an so on, in addition to the cores test requirements. This way, the best trade-off among all costs involved in the system synthesis (chip area, power consumption, pin count, test time, design time, among others) can be found.

In this thesis, two test planning approaches focused on the reuse of the system resources during test and on the design space exploration are proposed. The test planning methods are defined according to the connection model of the SoC and aim at helping the system integrator and the test engineer to evaluate the impact of the test solution on the global system cost, for a number of possible configurations of a SoC.

In the first approach, a SoC with a core-to-core connection model is assumed and the test planning tool is based on two main aspects: 1) it considers a mixed set of access mechanisms that includes the insertion of partial test buses, the reuse of functional connections, the use of available transparency modes of the cores, and other bypass modes available through the wrapper or the core configuration; 2) both the test schedule and the global test access mechanisms are defined together, and not as independent tasks as in other approaches. This aspect allows the exploration of the design space, so that good compromises among the various trade-offs being sought in the system synthesis can be found. The main contribution of this method is the use of several types of access mechanisms and the consideration of different optimization factors (area, pins, test time, and power consumption) during the global test access and test schedule definition. This expansion of concerns is combined with an efficient, yet fine-grained search, in the huge design space of the reuse-based environment.

In the second approach, a system implemented over a communication platform called network-on-chip (NoC) is assumed. For those systems, the communication among the cores is implemented through a switching network that is integrated into the chip. This network already provides a real and efficient access to each block embedded into the circuit. Thus, instead of inserting new buses into the system with the sole purpose of test access, the reuse of the available communication platform during test is proposed and a test scheduling algorithm is developed. This is the first work that systematize the test of cores embedded into a NoC-based system.

The two test planning approaches are explained and formalized, and the prototype tools that implement the proposed methods are presented. Furthermore, the methods are validated using the ITC'02 SoC Test Benchmarks (MARINISSEN; IYENGAR; CHAKRABARTY,

2002), a set of SoC examples provided by both, industry and academia, to ease the comparison among the several SoC test solutions available in the literature. One will observe in the experimental results presented in this dissertation that the proposed reuse-based SoC test techniques are indeed capable of devising a good test plan for the system not only in terms of test cost reduction, but also for the integration of the test planning into the initial steps of the system design.

The sequel of this dissertation is divided as follows: Chapter 2 presents a brief introduction to the terms and current trends of SoC design, such as the core-based paradigm and the new communication model based on networks-on-chip. That chapter also details the main challenges for the test of core-based systems-on-chip. Chapter 3 gives an overview of the several SoC test solutions presented in the last few years, and explains the main motivations for this work. Chapters 4 and 5 explain, respectively, the two reuse-based test planning approaches proposed in this thesis, including the experimental results for the ITC'02 benchmarks. Chapter 6 compares the two approaches to each other, discusses their integration at the system design flow, and compares the proposed methods to other techniques. Chapter 7 concludes this manuscript with some final remarks and future work.

# 2 SOC DESIGN TRENDS AND TEST CHALLENGES

This work tackles some problems related to the test of complex circuits, usually called core-based systems. Such systems present a design cycle that is quite different from the traditional ASICs. As a consequence, the testing requirements of the core-based systems are also very distinct.

In this chapter, some concepts of the core-based designed are reviewed in Section 2.1 while Section 2.2 discusses the design of core-based systems using interconnection networks. Then, the main problems related to the test of core-based systems are listed in Section 2.3.

# 2.1 Reuse-based SoC Design

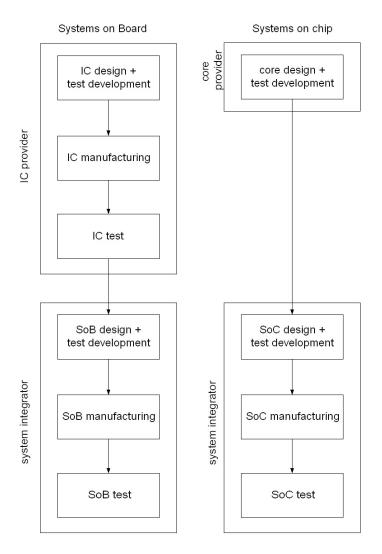

The design and manufacturing of integrated circuits is currently based on the integration of a number of pre-designed intellectual property (IP) blocks, or cores, in a single chip. Although the reuse has always been present in the design of electronic circuits, this practice has been extended and formalized in the last decade, becoming the new design paradigm of the electronic industry. The reuse of previously designed functional blocks is now the key for the design of high performance circuits with large gate counts in a short time (KUCUKCAKAR, 1998). Such a design practice is known as core-based or IP-based design, or simply as System-on-Chip (SoC) design. The main difference between a SoC and a traditional System-on-Board (SoB), which is also based on previously designed parts, is that in the former, all cores are synthesized together in a single chip, whereas in the latter each functional block is synthesized and manufactured separately, and then mounted in a discrete board. Furthermore, the reusable blocks of the SoC are also known as *virtual components*, since they are delivered as a description of a logic rather than a manufactured IC, and this constitutes another important difference between traditional design methods and core-based systems.

In the early days of SoCs, components were not really designed for reuse. However, gradually, component design evolved to include more parameterization and standard interfaces (BERGAMASCHI; COHN, 2002). Current available cores include microprocessors, memories, network interfaces, cryptography circuits, analog interfaces, among others (CMP, 2003). The more IP providers are present in the market, the more functionalities become available, and the more are the advantages of the core reuse. As a consequence, new technologies are incorporated in the products while the design time is reduced.

Embedded systems are a typical application where the core-based design is extensively applied. Cell phones, portable medical equipments, robots, and automotive controllers, are some examples of such systems. The successful design of such complex

single-chip applications requires expertise in a number of technology areas such as signal processing, encryption, and analog and RF designs. These technologies are increasingly hard to find in a single design house (GUPTA; ZORIAN, 1997). Moreover, high performance, reduced power consumption and short time-to-market are common requirements for those applications. Therefore, it is interesting to have all (or most) functional blocks (A/D converters, microprocessors, memories, mixed-signal blocks, and so on) already available. In this business model, the specialists in a specific design model (analog or RF, for example) are the core providers, and the application designer can focus on the system aspects only.

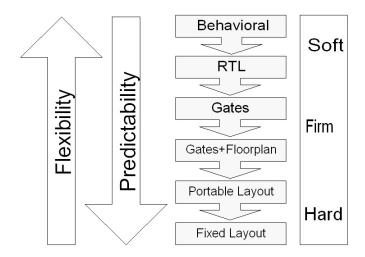

IP components are usually available in three forms (GUPTA; ZORIAN, 1997; KU-CUKCAKAR, 1998): hard, firm, and soft cores.

- Hard cores are provided as black boxes, usually in layout form and with encrypted simulation model. Due to their high performance and/or design complexity, these cores need to be provided as an optimized layout in a given technology. Examples of hard cores are microprocessors, memories, PLLs, and UARTs (CMP, 2003)

- **Firm cores** are provided as a synthesized netlist, that is, after logic synthesis and technology mapping, but without layout information. Those cores are described in a hardware description language (HDL), which can be simulated and changed if necessary. However, the user does not need to re-synthesize the block. ASICs and FPGAs are some examples of firm cores available in the market.

- **Soft cores** are given as register-transfer level (RTL) HDLs, and the user is responsible for its synthesis and layout. However, the soft cores providers usually supply synthesis and layout scripts, as well as timing assertions to make it easier the integration of those parts into the rest of the system. Some examples of soft cores are DSP blocks, Ethernet controllers, micro-controllers, and DMA controllers (CMP, 2003).

Figure 2.1: Core types (KUCUKCAKAR, 1998)

Figure 2.1 shows the relationship between the core model and its description language. The figure also shows the trade-offs in terms of flexibility and predictability of each type of core (KUCUKCAKAR, 1998). Having a completely rigid and validated layout with definite timing, the hard cores have rapid integration at the expense of flexibility. They

can further create place and route problems due to their rigidity. Technology-mapped gate-level netlists constitute a core style with less predictability than layouts, but allow significant flexibility during place and route. When technology-mapped gates (or logic) and predetermined floorplanning are used, the resulting firm cores are both flexible and more predictable. Properly written RTL sources can be synthesized into most technologies, but the freedom to change timing, area or power is not as great as in the case of behavioral models that can be synthesized via behavioral synthesis (KUCUKCAKAR, 1998).

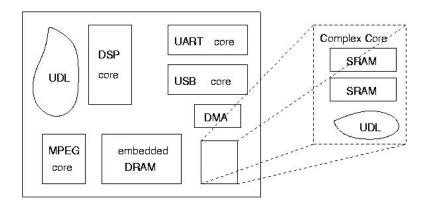

Figure 2.2 shows an example of a core-based system, where one of the cores is a supercore, that is, it embeds other cores. Notice the presence of a User Defined Logic (UDL) that adds some functionality to the system and is designed by the system integrator.

Figure 2.2: Example of SoC with super-cores and UDL (ZORIAN, 1997)

Although the design cycle of a complex system has improved with the advent of the core-based design paradigm, this is still an error-prone, labor-intensive and time-consuming task (BERGAMASCHI et al., 2001). Hence, design methods for SoCs are still an important research subject and a number of design aspects are being considered, such as the expansion of the reuse to a set of blocks and the communication issues. Moreover, the test of such systems became an important problem.

According to Zorian *et.al.* (ZORIAN; DEY; RODGERS, 2000), the effort to generate tests has been growing geometrically along with the product complexity. In the year 2000, the capital costs for testing, based on the 1997 SIA technology roadmap for semiconductors (SIA, 1997), was about 50% of the overall IC cost (ZORIAN; DEY; RODGERS, 2000). This cost showed signs of reduction according to the 1999 ITRS roadmap (SIA, 1999), due to the research and industrial efforts towards the development of cost-effective test solutions for SoCs. However, the costs related to the test of current SoCs are still an important part of the total manufacturing cost of the system-chips, and one can still see a considerable effort for its reduction. The main challenges of the SoC testing are described in Section 2.3, and solutions tackling some of these challenges are described in Chapter 3.

# 2.2 NoC-based SoC Design

Advances in the SoC design methods and tools aim at reducing the design complexity by automating some integration and synthesis steps, such as the co-simulation and co-synthesis of distinct cores descriptions. Recently, the concept of **design platforms** has been introduced to define a common set of architectural blocks over which the system is

built. The platform makes the reuse easier, since the main part of a family of applications is implemented once, but used several times. Thus, for each new application, only a small variation on the design is actually implemented.

A platform is a common base of hardware and software components that can be reused for the design of a number of distinct systems (SANGIOVANNI-VINCENTELLI; MARTIN, 2001; KEUTZER et al., 2000). The hardware base can be composed by a micro-architecture almost fixed with one or more microprocessors and other peripheral components connected through a communication structure. For example, the common architectures typically include a CPU and memories communicating over a fast bus and peripherals communicating through a slow bus (BERGAMASCHI; COHN, 2002). As for the software, the base components can be, for example, a real-time operating system (RTOS) accessible through Application Programming Interface (API) routines. These common components are standardized in such a way that they do not need to be validated for each new project, to accelerate the design time. On the other hand, the platform must offer parameterization and configuration capabilities to be easily reusable.

In terms of communication capabilities of a SoC, future systems will probably require communication templates with several dozens of Gbits/s of bandwidth (cell phones, network applications, etc). Buses can not always fulfill the performance requirements of such systems without posing new problems to power consumption and design reuse. Thus, recent works (GUERRIER; GREINER, 2000; BENINI; MICHELI, 2002; DALLY; TOWLES, 2001) have proposed the use of a pre-defined platform to implement the communication among the several cores in a chip. Such a platform is implemented as an integrated switching network, called Network-on-Chip (NoC), and meets some of the key requirements of future systems: reusability, scalable bandwidth, and low power consumption.

A study presented in (ZEFERINO et al., 2002) shows that NoCs have better communication performance than buses for a number as low as eight cores, if intensive communication, e.g. each core exchanging messages with another one, is required. For lighter workloads (fewer messages with reduced size), the performance of a central bus will be better than the NoC in systems with up to sixteen cores. Therefore, it is clear that NoCs can potentially become the preferred SoC interconnection approach in the near future.

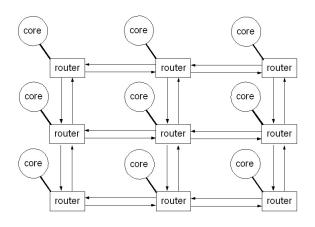

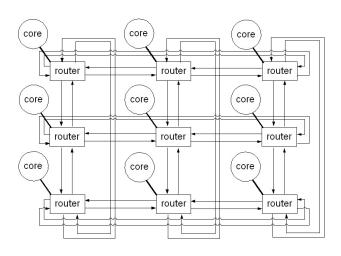

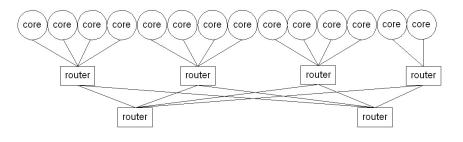

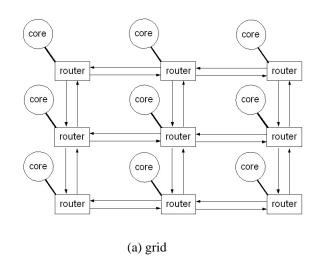

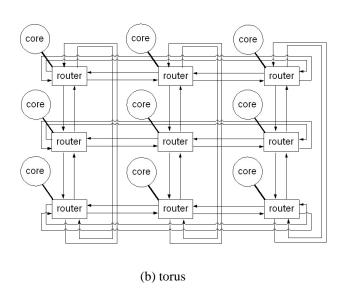

Networks-on-Chip are based on the interconnection networks largely used in parallel computers. NoCs can be defined as a structured set of routers and point-to-point channels interconnecting the processing cores of a SoC in order to support communication among them. Such a structure can be described as a graph with routers on the nodes and channels on the arcs, and it is named topology. Some examples of topologies include grid, torus, hypercube, ring, multi-stage and fat-tree (DUATO; YALAMANCHILI; NI, 1997). In current NoCs, the preferred topologies are the ones with planar structures, because they are easier to be implemented with current technologies (BABB et al., 1999). Figure 2.3 shows three examples of NoC topologies: grid (Figure 2.3(a)), torus (Figure 2.3(b)), and fat-tree (Figure 2.3(c)).

NoCs typically use the message-passing communication model, and the processing cores attached to the network communicate by sending and receiving request and response messages. A message forwards from a sender to a receiver by requesting and reserving resources of the network in order to establish a route between the sender and the receiver. To be routed by the network, a message is composed by a header, a payload and a trailer. The header and the trailer frame the packet and the payload carries the data being transferred. The header also carries the information needed to establish the path

(a) grid

(b) torus

(c) fat-tree

Figure 2.3: Some NoC topologies

between the sender and the receiver, and the trailer can be either an additional word in the message or a bit in the last word of the payload. Depending on the network implementation, messages can be split into smaller structures named packets, which have the same format of a message and are individually routed. Packet-based networks present a better resource utilization, because packets are shorter and reserve a smaller number of channels during their transfer. Besides its topology, a NoC can be described by the approaches used to implement the mechanisms for flow-control, routing, arbitration, switching and buffering, as follows. The flow control deals with data traffic on the channels and inside the routers. Routing is the mechanism that defines the path a message takes from a sender to a receiver. The arbitration establishes priority rules when two or more messages request the same resource. Switching is the mechanism that takes an incoming message of a router and puts it in an output port of the router. Finally, buffering is the strategy used to store messages when a requested output channel is busy. Current cores usually need to use wrappers to adapt their interfaces and protocols to the ones of the target NoC. Such wrappers pack and unpack data exchanged by the processing cores which.

Some implementations of such integrated networks can be found in (KARIM; NGUYEN; DEY, 2002), (FORSELL, 2002), and (ZEFERINO, 2003), for example.

# 2.3 Test Challenges in SoC Design

Figure 2.4, extracted from (MARINISSEN; ZORIAN, 1999), shows the main differences between the test of a system-on-board and a system-on-chip. In the SoB test, each integrated circuit (IC) mounted in the board is totally designed, manufactured and tested before becoming part of a more complex system. In a core-based SoC, on the other hand, all cores are tested together, after the whole system is synthesized and manufactured(ZORIAN, 1997). Although each core is assumed to be functionally correct, its behavior after manufacturing and in conjunction with other cores is not known a priori (GUPTA; ZORIAN, 1997).

Another key difference between the SoB and the SoC testing is the access to the cores periphery during test (ZORIAN; MARINISSEN; DEY, 1998). In a SoB, probes can normally be used to access each IC. Alternatively, boundary-scan chains are used to serially control and observe each block. As the number of ICs in the board is relatively small, the time required to scan-in and scan-out the test data is usually acceptable. In a SoC, probes can not be used to access the cores that are deeply embedded into the chip. Moreover, the use of boundary-scan to access internal blocks may be too costly in terms of time, as the number of cores in the system increases every day.

Furthermore, one of the main challenges of the SoC testing is the integration and coordination of the test and diagnose techniques of all cores that compose the circuit (ZO-RIAN, 1997). Whereas the test of a SoB consists basically on the test of the interconnections among ICs, in the SoC the system testing comprises not only the interconnection test, but also the verification of each core and the user defined logic as well.

One can divide the test requirements of the SoC in three levels (ZORIAN, 1998): core requirements, interconnection requirements, and system requirements.

## 2.3.1 Core Test Requirements

## • Definition of the core test approach

The definition of a test strategy for a core depends on the knowledge of the logic implemented by that block. Therefore, this task is usually performed by the core

Figure 2.4: Differences between SoB and SoC testing (MARINISSEN; ZORIAN, 1999)

provider, which also assures the protection of the intellectual property associated to the reusable block. However, the core test strategy also depends on the target technology of the final system, the system test resources and the required fault coverage, but these parameters are not known by the core provider a priori. Thus, in general, the core provider supplies a basic set of test vectors and DFT strategies (scan chains, BIST controllers) for the core, to test for the most common technology faults. For open source soft cores, the system integrator has access to the core description. In this case, the integrator can make some modifications in the core logic, although this may require additional design time. When the core can not be modified by the integrator and more DFT structures or test patterns are required, an additional agreement between the core designer and the core user is necessary. In both cases, the communication between the two parts (core provider and core user) is the key for the successful testing of the block. The transmission of the core test strategy (test patterns, expected responses, control signals, etc) must be clear and unambiguous. On the other hand, if the system integrator needs other test schemes implemented in the core, he/she must specify very clearly which modifications must be implemented. Thus, although there are numerous test techniques for all types of logics (microprocessors, analog filters, DSP-based logics, among others) that can

be reused for the test of a core, the problem at this level is the information flow from the core provider to the core user and vice-versa.

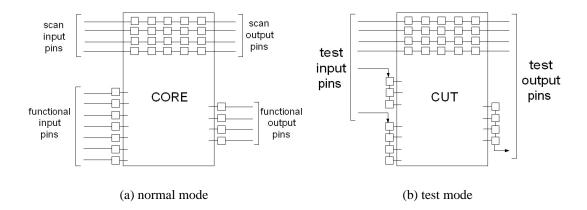

## Access to the core periphery during test

During test, other pins, in addition to the functional interfaces of the core must be accessed (scan-in and scan-out interfaces, control pins, testing clock, etc). As many cores are deeply embedded into the chip and the number of pins at system level is usually much smaller than the number of pins of a core, the transmission of the test data between an external tester and the embedded module is an important issue. Moreover, the definition of the access mechanism for each core impacts all other system test costs, such as test time, and area overhead. Therefore, the definition of such mechanism must be carefully considered.

#### • Core isolation

During the test of a core, it is usually necessary to put this block in a test mode, so that the test pins become ready to receive and send data. Additionally, it may be necessary to isolate this block from the rest of the system so that other blocks are not damaged or can be tested in parallel. Therefore, the inclusion of an extra logic around the core to provide the several operation modes of this module is usually required. This logic can be either part of the core and be delivered along with the block itself, or be implemented by the system integrator, according to the core and system requirements (ZORIAN, 1997, 1998).

#### 2.3.2 Interconnection Requirements

The test of the interconnections, in the second level, presents a single requirement: the possibility of precisely controlling and observing each connection. This test is, nevertheless, of extreme importance for the system characterization, since it can determine the actual performance achieved by the system. Furthermore, as the number of connections may be high, it has an important impact on the system test time. This test must be defined by the system integrator. In general, the interconnection test relies on the existence of some mechanism around the core (a boundary register, for example) that allows the load and capture of the interconnection signals.

#### 2.3.3 System Requirements

#### • Test of the UDL

Some authors consider the interconnections as part of the user defined logic. However, this logic can also implement some other functions, such as the data conversion between two cores. In the first case, the UDL testing is treated as the interconnection testing. In the second case, the UDL can be viewed as another core in the system, but that can be modified by the system integrator. Thus, the test of this logic can be defined as the test of an additional soft core.

## • Test scheduling definition

The test scheduling defines the order of testing of each part of the system: cores, interconnections and UDL. The scheduling depends basically on the set of test resources available and shared among cores, and on the system power constraints.

#### • Test controller

The test controller is the module that runs the test program, sending the correct control and test signals to each part under test in the system. This controller can be an automatic test equipment, outside the chip, or can be implemented inside the chip.

## • Test integration

The combination of the access mechanism of each core in such a way that all cores are properly tested without deeply affecting the system performance, cost and design time is the most important system test requirement. Actually, this system-level requirement is the combination of all requirements previously defined, and represents the complexity of the SoC testing faced by the system integrator. For example, the system integrator has to verify that the access mechanisms defined for the cores can be implemented and synthesized with the system logic, without compromising the application performance and the chip cost. Moreover, the integrator has to define a test scheduling of minimum time while still meeting the application power constraints. In fact, the test integration is very similar to the system integration, and one can certainly agree that there are several possible test solutions, considering different access mechanisms, different cores versions (BISTed and non-BISTed, for instance), and different synthesis possibilities, that meet all test requirements. Therefore, the design space considering the test is quite large. Moreover, because of this complexity, the system integrator must consider the possible test solutions as early as possible in the design flow.

According to the system design model, the test requirements can be more or less modified. For example, the flexibility of the soft cores can be used to facilitate the combination of the cores test requirements and the system constraints. Bus-based functional connections are probably faster to test, if the connections are centralized. NoC-based designs, on the other hand, may have more connections to be tested, but the communication protocol and the possibility of reuse of the communication platform may accelerate the test definition.

In Chapter 3, a summary of the solutions that have been presented in the last few years, in response to some of the defined test requirements, is presented. Then, these solutions will be discussed and the motivation and intended contributions of this work will be further detailed.

# 3 RELATED WORKS AND MOTIVATIONS

A great deal of effort has been expended in the last few years, towards the development of suitable solutions for the test of core-based systems. Responding to the several test requirements listed in Chapter 2, one can group the techniques presented so far in four categories: test access mechanism definition, test scheduling methods, test planing approaches, and standardization initiatives. The techniques in the first group tackle the problem of defining an access mechanism to the cores periphery during test. Such solutions can either be based on the reuse of system functional connections, cores logic or on the insertion of a test bus. In the second group, the minimization of the test time is addressed, usually based on an access mechanism previously defined. In the third group one will find the techniques that take into account a number of system or test aspects. Finally, the fourth group comprises the initiatives for the standardization of the interface between the cores and the system during test, and the definition of a set of SoC test benchmarks. In the sequel, some representative works of these four groups will be discussed and the remaining test requirements, still not tackled by the available solutions, will be listed.

## 3.1 Test Access Mechanism Definition

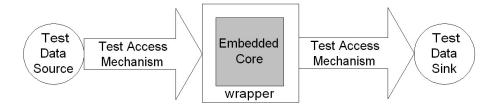

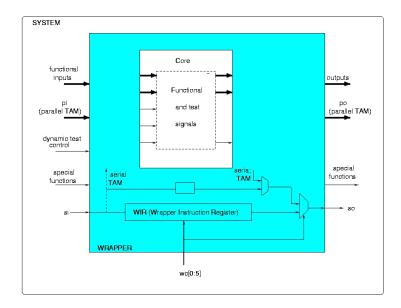

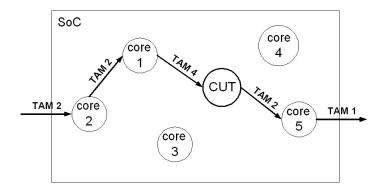

Zorian *et al.* (ZORIAN; MARINISSEN; DEY, 1998) introduced the generic conceptual test access architecture for embedded cores as well as a nomenclature for its elements that has been used in the literature. The conceptual architecture, shown in Figure 3.1, is composed of four basic elements:

- a test *stimuli* source for the real-time test pattern generation;

- a test sink for the reception and evaluation of the test responses;

- a Test Access Mechanism (TAM) for the transportation of the test data from the test source to the core and from the core to the test sink;

- a core wrapper, for the connection of the core terminals to the TAM terminals, providing the mechanisms for isolation and integration of the core to the system during test.

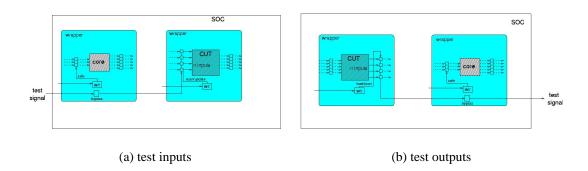

These four elements can be implemented in several ways, according to the core requirements and system constraints. However, the wrapper structure must allow the core to operate in at least three modes: normal, internal test, and external or interconnection test. Additionally, the wrapper must also implement some type of bypass mode to isolate the core from the system when other cores are being tested.

The test sources and sinks can be implemented in a number of ways:

Figure 3.1: Conceptual architecture for the SoC testing (ZORIAN; MARINISSEN; DEY, 1998)

- off-chip, using an external test equipment;

- on-chip, through BIST structures;

- as a combination of both (for example, when a core is tested by a combination of deterministic and pseudo-random vectors).

In addition, the source and the sink do not need to be of the same type, that is, one can have an on-chip test source and an off-chip test sink, or vice-versa. As one will see in the several test approaches presented in the following, the choice for one implementation of a test source, sink or access mechanism depends on the type of cores embedded into the system, on the test requirements of such cores, and on a number of system constraints, such as area, test time, time-to-market, and so on. For example, on-chip sources and sinks usually present a better fault coverage than their off-chip version, but may increase the system area, leading to yield reduction. On the other hand, off-chip sources and sinks usually require more elaborated access mechanisms and may increase the system test time.

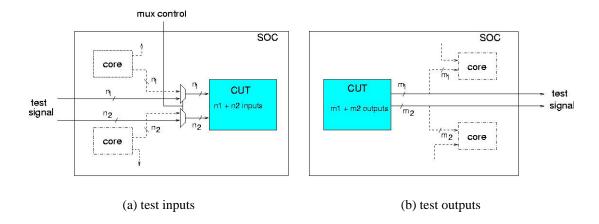

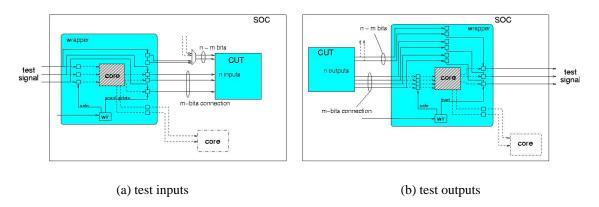

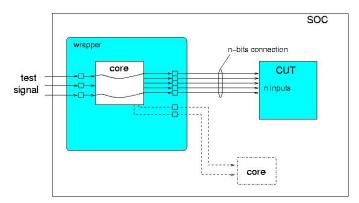

The test wrapper is a thin shell around the core that connects the TAM(s) to the core (MARINISSEN; KAPUR; ZORIAN, 2000). The wrapper provides the switching between normal functional access and test access via the TAM. Well designed wrappers provide test access for both core-internal testing as well as core-external testing. Furthermore, wrappers may provide width adaptation in case of a mismatch between core I/O width and TAM width (MARINISSEN; KAPUR; ZORIAN, 2000).

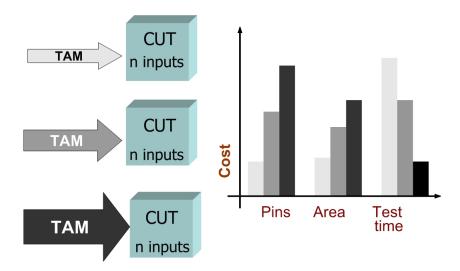

The test access mechanism communicates the core under test to the pattern sources and the test sinks. Although the same mechanism can be used for the transport of the test data in both directions, this is not mandatory and a number of TAM combinations can co-exist for the same core (ZORIAN; MARINISSEN; DEY, 1998). The design of a TAM always searches the best trade-off between the transport capacity of the mechanism and its application cost. The capacity of data transportation is limited by the capacity of the source and sink, and by the system area that can be used by the TAM, which is usually measured as the TAM bitwidth. Figure 3.2 shows the relationship between the TAM bitwidth and the test costs in terms of area and pin overhead, and the core test time.

Zorian *et al.* (ZORIAN; MARINISSEN; DEY, 1998) list the following options for the TAM definition:

- the reuse of functional buses and interconnections of the system;

- the use of specific test access inserted into the system;

- the reuse of the cores or other logic blocks for the test access path, either using the cores functionality (called transparent modes) or some type of bypass mechanism;

Figure 3.2: Relationship between TAM width and test costs

- the use of an independent access for each core or the TAM sharing among cores;

- The transportation of only the test data by the TAM or the inclusion of some control functions in the access mechanism itself.

In the following, the most important approaches for TAM definition presented so far are described. These approaches range from adaptations of traditional test techniques, such as the 1149.1 Standard (IEEE Standards Board, 1990), to the development of hierarchical and scalable methods for test access. As for the performance of the test solution, the proposed approaches create the TAM mainly considering testing time issues.

(WHETSEL, 1997), (BHATTACHARYA, 1998), (LEE; HUANG, 2000), (HU; YIBE, 2001), (LI et al., 2002a), (OAKLAND, 2000), and (LI et al., 2002b) propose test access mechanisms based on the IEEE 1149.1 boundary-scan standard, also known as JTAG standard (IEEE Standards Board, 1990). The assumption of these approaches is that many cores being used today were ASICs in the past, and the boundary-scan is already implemented for those modules. Moreover, as the JTAG mechanism requires only five extra pins at system-level, the test cost is drastically reduced. However, the inclusion of a TAP (Test Access Port) controller into a core makes the integration of such a core into a SoC (LOUSBERG, 2002) more difficult, since an extra level of controlling is required for each TAPed module. The main disadvantage of the JTAG-based methods is, nevertheless, the possibly excessive testing time caused by the reduced TAM bandwidth provided by the system-level TAP.

Other authors tackle the access problem by reusing available system resources, such as cores and functional interconnections.

Ghosh *et al.* propose a method in which test access to embedded cores is based on transparent paths through other cores and design modules (GHOSH; JHA; DEY, 1997). In the proposed method, every core should not only come with a set of pre-computed tests, but also with a set of transparent paths, capable of transporting test data through the core. If these paths are originally not available, the core provider should add design-for-test hardware to the core in order to create test access paths to other cores. Some methods for the synthesis of transparent cores are proposed in (CHAKRABARTY; MUKHERJEE; A., 2001), (MAKRIS; ORAILOGLU, 1998), and (YONEDA; FUJIWARA, 2002). However, the transparent-based access method does not seem to address the issue of time-to-market

and in many cases yields an excessive number of access paths. In (GHOSH; DEY; JHA, 1998), this problem is considered and different transparent paths are available in different versions of each core, each version with a distinct area overhead so that only one version of the core is chosen as the system area is optimized. However, if the transparent modes are defined previously to the system integration, one can not assure that all required paths will be available or a huge number of core versions is still required, and the time-to-market issue can still be a problem. On the other hand, to define the transparent modes during the system integration, soft cores are assumed, and the access to the core description is required, which is not always the case in current SoCs. Chiusano *et al.* propose in (CHIUSANO; PRINETTO; WUNDERLICH, 2000) the use of arithmetic cores to generate test patterns for subsequent cores. In this case, the core does not implement a transparent mode, but its original logic is used as a pseudo-random test pattern generator.

Nourani and Papachristou propose in (NOURANI; PAPACHRISTOU, 1998a,b) and in (NOURANI; PAPACHRISTOU, 1999) the definition of the test access architecture by taking advantage of the connections already present in the system. A *bypass* mode is introduced for each core input port to its output port through which the test data can be transferred. The system is modeled as a directed weighted graph in which the core accessibility is solved as a shortest path problem. This model has been improved and presented in (NOURANI; PAPACHRISTOU, 2000), where other structures in the system, such as buses and tri-state ports, are also considered for the test path definition. The problem of TAM definition and test time minimization is formulated and solved as an ILP problem.

The reuse of the microprocessor that is usually present in the system is proposed in a number of works (PAPACHRISTOU; MARTIN; NOURANI, 1999), (HWANG; ABRAHAM, 2001), (LAHIRI; RAGHUNATHAN; DEY, 2002), (CHEN; BAI; DEY, 2002). The basic assumption of those methods is that the microprocessor is connected to a large number (if not all) embedded cores through a functional bus or a hierarchy of buses. If this is not the case, additional hardware is inserted to make it possible the access and control of the core under test by the microprocessor. However, as there is a single or a small number of test processors being used, only one or a few cores are tested at a time. Therefore, this type of solution is usually effective for small systems where the microprocessor of the application is connected to most embedded cores. For those systems, the test time is affordable, as well as the area overhead caused by the access mechanism. On the other hand, if deterministic patterns are used, an external memory may still be required and the reduced pin count at the system interface may be a problem. If internal memories are also reused, in addition to the microprocessor reuse, they may be not large enough for the storage of all test patterns, and a mechanism for the memory reload is required.

Finally, a third line of solutions defends the insertion of additional buses in the system, called test buses, as the access mechanism. Despite the fact that the dedicated wiring increases the area costs of the SoC, the scalability and the possibility of modeling the problem with a limited number of variables, makes this TAM a very interesting and the most explored test architecture.

Varma and Bhatia describe a test access mechanism for embedded cores, named VisibleCores (VARMA; BHATIA, 1998). Their approach is based on two dedicated on-chip variable-width buses, one for transporting test control signals, and one for transporting test data signals. Embedded cores can be either connected or disconnected from the test buses. Test access from chip pins to embedded cores and vice versa is achieved by connecting the core-under-test to the test data bus, and disconnecting all other cores. A disadvantage

Figure 3.3: Test Bus Architectures (AERTS; MARINISSEN, 1998)

of this method is that only one core at a time can be connected to the test bus, while some tests involve multiple cores.

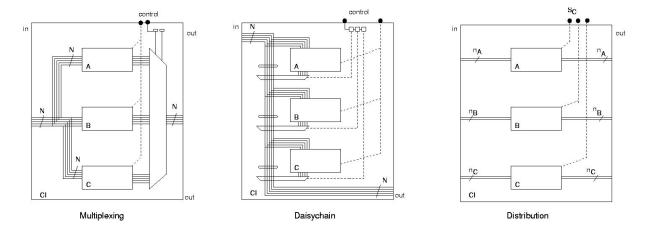

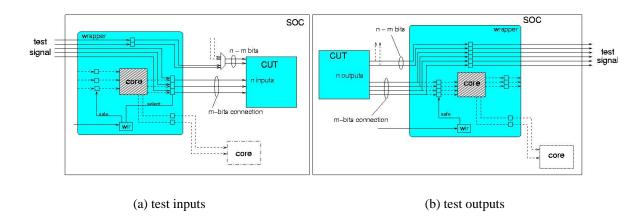

Three basic types of scalable TAMs have been described in (AERTS; MARINISSEN, 1998) and are exemplified in Figure 3.3: (a) the Multiplexing architecture, (b) the Daisychain architecture, and (c) the Distribution architecture.

In the Multiplexing and Daisychain architectures, all cores have access to the total available TAM width, while in the Distribution architecture, the total available TAM width is distributed over the cores. Note that the multiplexer in the Multiplexing Architecture is conceptual, and hence could also be implemented by means of tri-state buffers with appropriate control signals. In the Multiplexing architecture, only one core wrapper can be accessed at a time. Consequently, in this architecture the cores must be serially tested. An even more serious drawback of this architecture is that testing the circuitry and wiring in between cores is difficult; interconnect test requires simultaneous access to multiple wrappers. The other two basic architectures do not have these restrictions; they allow for both serial as well as parallel test schedules, and also support interconnect testing.

The TestRail architecture proposed in (MARINISSEN et al., 1998) and shown in Figure 3.4 is a combination of the Daisychain and Distribution architectures. A single TestRail is basically the same as what is described by the Daisychain architecture: scantestable cores connected to the same TestRail can be tested simultaneously, as well as sequentially. A TestRail architecture allows for multiple TestRails on one SoC, which operate independently, as in the Distribution architecture. The TestRail architecture supports serial and parallel test schedules, as well as hybrid combinations of those.

In most test access architectures, the cores assigned to a TAM are connected to all wires of that TAM. Such architectures are referred to in (IYENGAR; CHAKRABARTY; MARINISSEN, 2002a) as fixed-width TAMs. The flexible-width TAMs, on the other hand, refer to the core-TAM assignments where the granularity of TAM wires are considered, instead of considering the entire TAM bundle as one inseparable entity. Figure 3.5 shows an example of a flexible-width Test Bus architecture.

In (CHAKRABARTY, 2000a), Chakrabarty proves that many problems related to the definition of bus-based TAMs are NP-hard. Additionally, he uses the Integer Linear Programming (ILP) heuristic to model and solve the test bus assignment problem. In this problem, for a given number of test pins at the system interface divided into a given number of test buses, the best width for each test bus and the best assignment of test buses to

Figure 3.4: Test Rail Achitecture (MARINISSEN et al., 1998)

Figure 3.5: Flexible-width test bus architecture (IYENGAR; CHAKRABARTY; MARINISSEN, 2002a)