# FEDERAL UNIVERSITY OF RIO GRANDE DO SUL INSTITUTE OF INFORMATICS

#### LEONARDO HAX DAMIANI

# Fine Carrier Synchronization Unit for a Turbo Synchronization System

Computer Engineering Graduation Work.

Prof. Dr. Alexandre Carissimi Advisor

Dipl.-Math. Uwe Wasenmüller Co-advisor

#### FEDERAL UNIVERSITY OF RIO GRANDE DO SUL

Rector: Prof. Carlos Alexandre Netto

Vice-Rector: Prof. Rui Vicente Oppermann

Dean's office Coordinator: Profa. Valquiria Link Bassani Institute of Informatics Director: Prof. Flávio Rech Wagner Computer Engineering Coordinator: Prof. Sérgio Cechin

Librarian of the Institute of Informatics: Beatriz Regina Bastos Haro

#### Acknowledgments

I would like to express my special thanks of gratitude to my advisor Prof. Dr. Alexandre Casissimi. Throughout my thesis-writing period, he provided encouragement, sound advice, good teaching and a lot of virtuous ideas.

I am thankful to Prof. Dr.-Ing. Norbert Wehn and all the researchers from the Microelectronic Systems Design Research Group from University of Kaiserslautern, specially my co-advisor Dipl. Math. Uwe Wasenmüller, for his restless guidance, inspiration and determination in carrying out this project.

The respect to the secretaries, librarians and employees in the Informatics and Engineering departments of UFRGS and TUKL must be mentioned, for helping the departments to run smoothly and for assisting me in many different ways.

I wish to thank my entire family and friends for providing a loving and comprehensive environment for me. Last, and most important, I wish to thank my parents, Vilmar Damiani and Cleonice Hax Damiani. They bore me, raised me, supported me, taught me, and loved me.

## **SUMMARY**

| LIST OF ABBREVIATIONS AND ACRONYMS                   | 6        |

|------------------------------------------------------|----------|

| LIST OF FIGURES                                      | 7        |

| LIST OF TABLES                                       | 9        |

| ABSTRACT                                             | 10       |

| RESUMO                                               | 11       |

| 1 INTRODUCTION                                       | 12       |

| 1.1 Objectives of This Work                          | 14<br>14 |

| 1.2 Structure of the work                            | 15       |

| 2 BASIC CONCEPTS                                     | 16       |

| 2.1 Modulation                                       | 17       |

| 2.2 Signal Degradation by Noise                      | 18       |

| 2.3 Channel Capacity                                 | 22       |

| 2.4 Techniques of Detection and Correction of Errors | 23       |

| 2.5 General Considerations                           | 27       |

| 3 CREONIC SIMULATION ENVIRONMENT - CSE               | 28       |

| 3.1 CSE Architecture                                 |          |

| 3.1.1 CSE Modules and Configuration                  |          |

| 3.1.2 CSE Output                                     |          |

| 3.1.3 CSE Class Structure                            | 32       |

| 3.2 Development of New Modules                       | 35       |

| 3.2.1 Create a Parameter Class for the Module        |          |

| 3.2.2<br>3.2.2 |                                                                                                  |              |

|----------------|--------------------------------------------------------------------------------------------------|--------------|

| 3.3            | General Considerations                                                                           | 38           |

| 4 IN           | MPLEMENTATION                                                                                    | 39           |

| 4.1            | Software                                                                                         | 42           |

| 4.1.           |                                                                                                  |              |

| 4.1.2          | · · · · · · · · · · · · · · · · · · ·                                                            |              |

| 4.1.3          | 3 Extensions to Statistics Module                                                                | 48           |

| 4.2            | Hardware                                                                                         | 50           |

| 4.2.           |                                                                                                  |              |

| 4.2.2          |                                                                                                  |              |

| 4.2.3          |                                                                                                  |              |

| 4.2.4          |                                                                                                  |              |

| 4.3            | General Considerations                                                                           | 58           |

| 5 V            | ALIDATION                                                                                        | 59           |

| 5.1            | Test Environment                                                                                 | 59           |

| 5.2            | Methodology                                                                                      | 59           |

| 5.3            | Fine Carrier Synchronization Software Analysis                                                   | 63           |

| 5.4            | Fine Carrier Synchronization VHDL Analysis                                                       | 67           |

| 5.5            | Software and VHDL Tests                                                                          | 70           |

| 5.6            | General Considerations                                                                           | 71           |

| 6 C            | ONCLUSION                                                                                        | 72           |

| REFE           | ERENCES                                                                                          | 74           |

| ANNI           | EX A <article carrier="" fine="" synchronization<="" td="" tg1:=""><td>UNIT</td></article>       | UNIT         |

|                | TURBO SYNCHRONIZATION SYSTEM>                                                                    |              |

| ANNI           | EX B < XILINX ISE DESIGN TOOL SYTHESIS REPORT>                                                   | 90           |

| ANNI<br>PORTAI | EX C < RESUMO TG2: UNIDADE DE SINCRONIZAÇÃO FIN<br>DORAS PARA SISTEMAS DE SINCRONIZAÇÃO TURBO >. | NA DE<br>101 |

#### LIST OF ABBREVIATIONS AND ACRONYMS

GSM Global System for Mobile

BER Bit Error Rate

FER Frame Error Rate

SNR Signal to Noise Ratio

QPSK Quadrature Phase Shift Keying

DVB-RCS Digital Video Broadcast – Return Channel via Satellite

CSE Creonic Simulation Environment

VHSIC Very High Speed Integrated Circuits

VHDL VHSIC Hardware Description Language

ASK Amplitude Shift Keying FSK Frequency Shift Keying

PSK Phase Shift Keying

BPSK Binary PSK

QAM Quadrature Amplitude Modulation

CRC Cyclic Redundancy Check

FEC Forward Error Correction

LDPC Low-Density-Parity-Check

ARQ Automatic Repeat Request

SISO Soft In Soft Out

LLR Log Likelihood Ratio

XML Extensible Markup LanguageAWGN Additive White Gaussian NoiseFPGA Field Programmable Gate Array

ASIC Application Specific Integrated Circuit

ROM read-only-memory

IP Intellectual Properties

## LIST OF FIGURES

| Figure 2.1: Different modulations applied to a digital signal BPSK                      | . 17 |

|-----------------------------------------------------------------------------------------|------|

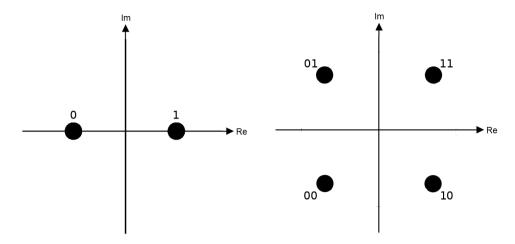

| Figure 2.2: Constellation diagram for BPSK (left) and QPSK (right) with gray coding     | g 18 |

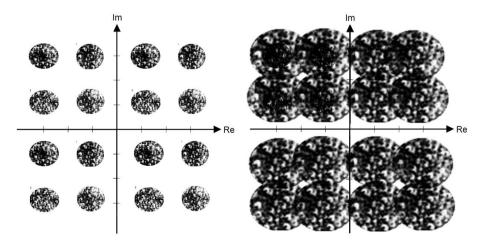

| Figure 2.3: 16-QAM with an acceptable range variation (left – high SNR) and a very      | -    |

| noisy range variation (right – low SNR)                                                 |      |

| Figure 2.4: Bit Error Rate (BER) x Channel SNR (in dB) in a QPSK communication.         |      |

| Figure 2.5: Illustration of a frequency offset (f) in a QPSK modulation                 |      |

| Figure 2.6: Illustration of phase offset (α) in a QPSK modulation                       |      |

| Figure 2.7: Illustration of a not properly sampling rate (left) and a properly sampling |      |

| rate (right) accordingly to Nyquist theorem                                             | . 23 |

| Figure 2.8: Hamming code trick to correct burst errors                                  |      |

| Figure 2.9: A generic turbo encoder                                                     |      |

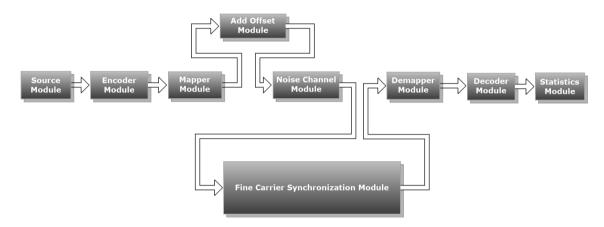

| Figure 3.1: Original simulation chain and functional modules connection available or    |      |

| CSE                                                                                     |      |

| Figure 3.2: Explanation of the <iter> tag</iter>                                        |      |

| Figure 3.3: Excerpt of the XML configuration file                                       |      |

| Figure 3.4: Excerpt of the input configuration copied to the XML output file            |      |

| Figure 3.5: Excerpt of the statistical results printed on the XML output file           |      |

| Figure 3.6: Organization of the module classes                                          |      |

| Figure 3.7: Excerpt of the Encoder_Interface file – creation and definition of the      |      |

| interfaces                                                                              | . 33 |

| Figure 3.8: Excerpt of the Encoder_Parameter file – creation and definition of the      |      |

| default parameters values                                                               | . 34 |

| Figure 3.9: Code of an empty parameter class for a LDPC decoder                         | . 35 |

| Figure 3.10: Excerpt of how to create and define default values to parameters           |      |

| Figure 3.11: Code of a new empty interface class for a LDPC decoder                     | . 37 |

| Figure 3.12: Code for a new header file for a LDPC decoder                              | . 37 |

| Figure 3.13: Code for a new cpp file for a LDPC decoder                                 |      |

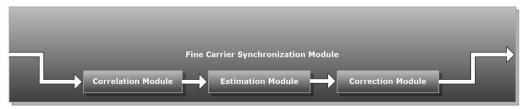

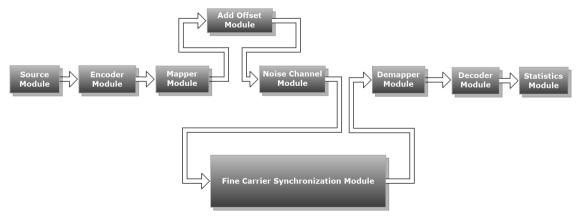

| Figure 4.1: Fine Carrier Synchronization Unit Module position regarding the original    |      |

| simulation chain                                                                        |      |

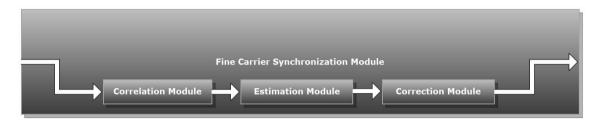

| Figure 4.2: Fine Carrier Synchronization Unit Module modularization                     | . 40 |

| Figure 4.3: Add Offset and Fine Synchronization Module positions regarding the basis    | ic   |

| simulation chain                                                                        | . 41 |

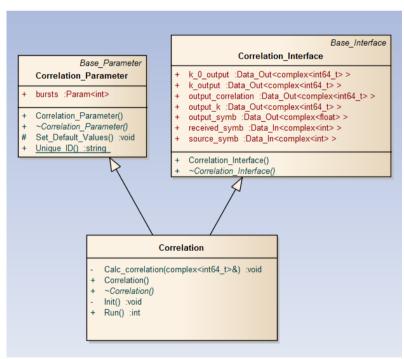

| Figure 4.4: Implementation of the calculation of the correlation values                 | . 43 |

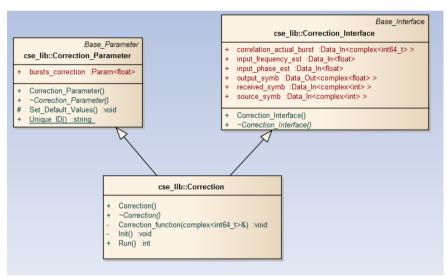

| Figure 4.5: Correlation module class diagram                                            |      |

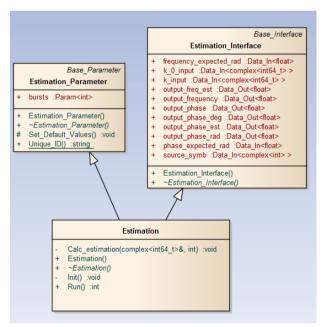

| Figure 4.6: Implementation of the estimation frequency and phase offset                 |      |

| Figure 4.7: Estimation module class diagram                                             |      |

| Figure 4.8: Correction module class diagram                                             |      |

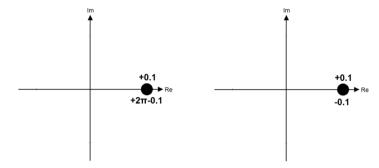

| Figure 4.9: Example of the "Wrap Around Problem" with the wrong interpretation (le      |      |

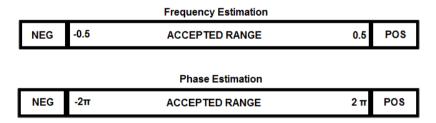

| and the right interpretation (right)                                                    |      |

| Figure 4.10: Illustration of accepted range and "out of bounds" areas regarding          |     |

|------------------------------------------------------------------------------------------|-----|

| frequency and phase estimation                                                           | 46  |

| Figure 4.11: Excerpt of the code used for the normalization of estimated values          | 47  |

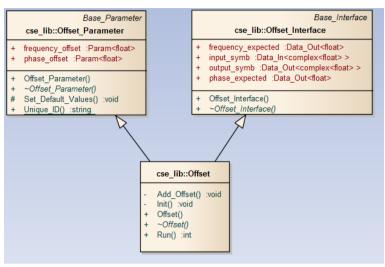

| Figure 4.12: Add Offset module class diagram                                             |     |

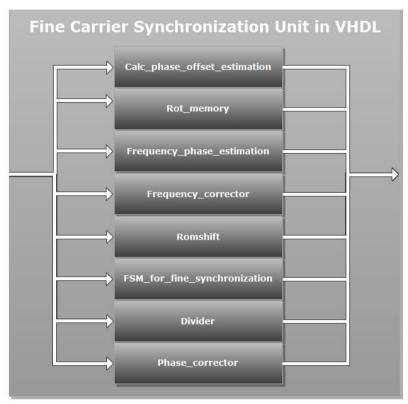

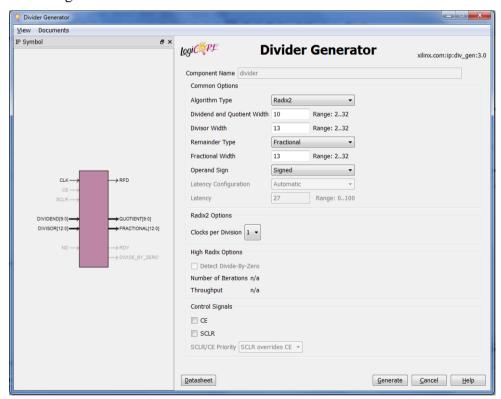

| Figure 4.13: Fine Carrier Synchronization Unit in VHDL modularization                    | 52  |

| Figure 4.14: Excerpt of the correlation calculation in VHDL                              |     |

| Figure 4.15: Excerpt of the calculation                                                  | 53  |

| Figure 4.16: GUI interface of the Xilinx tool Core Generator when creating and editin    | g   |

| the Divider module                                                                       | 54  |

| Figure 4.17: Xilinx Core Generator IP Catalog                                            | 55  |

| Figure 4.18: Excerpt of the VHDL code responsible for truncation of the correlation      | 56  |

| Figure 4.19: Excerpt of the VHDL code responsible for the adjustment of the number       | of  |

| bits between phase and frequency offset                                                  | 56  |

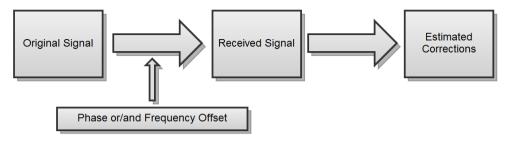

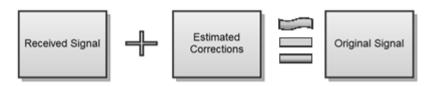

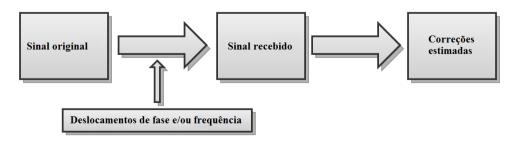

| Figure 5.1: Original signal until estimated corrections flow                             | 60  |

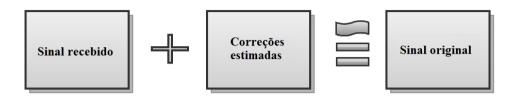

| Figure 5.2: Verification of the reliability of the estimated corrections                 |     |

| Figure 5.3: Source_bits Module instantiation and parameters definition                   |     |

| Figure 5.4: Excerpt of the code responsible for the detection of small bursts            |     |

| Figure 5.5: Add Offset Module instantiation and parameters definition                    |     |

| Figure 5.6: Channel AWGN Module instantiation and parameters definition                  | 62  |

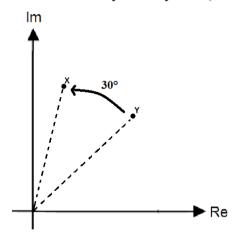

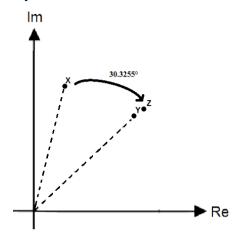

| Figure 5.7: Effect of the addition of phase offset equals 30° on the symbol              |     |

| Figure 5.8: Effect of the correction of the symbol with the estimated phase offset       |     |

| Figure 5.9: Effect of the addition of frequency offset equals 0.00446429 radians on the  | ;   |

| symbol                                                                                   | 65  |

| Figure 5.10: Effect of the correction of the symbols with the estimated frequency offset | et. |

|                                                                                          | 65  |

## LIST OF TABLES

| Table 5.1: Scenarios used to validation of the work                                      |

|------------------------------------------------------------------------------------------|

| Table 5.2: Phase offset estimation related values extracted from the XML output file. 63 |

| Table 5.3: Symbol transformation process with phase offset only (software)               |

| Table 5.4: Frequency offset estimation related values extracted from the XML output      |

| file                                                                                     |

| Table 5.5: Symbol transformation process with frequency offset only (software) 66        |

| Table 5.6: Symbol transformation process with phase and frequency offset (software) 67   |

| Table 5.7: Statistics values from the phase and frequency simulation extracted from      |

| XML output file                                                                          |

| Table 5.8: Comparison between the correlation values from the first burst                |

| Table 5.9: Average correlation value comparison                                          |

| Table 5.10: Estimated and expected phase offset (VHDL)                                   |

| Table 5.11: Symbol transformation process with phase offset only for the first symbols   |

| on the burst (VHDL)                                                                      |

| Table 5.12: Estimated and expected frequency offset (VHDL)                               |

| Table 5.13: Symbol transformation process with frequency offset only (VHDL) 69           |

| Table 5.14: Estimated and expected phase and frequency offset (VHDL) 69                  |

| Table 5.15: Symbol transformation process with phase and frequency offset (VHDL) 70      |

| Table 5.16: Analysis with the truncation threshold define as 256 symbols                 |

| Table 5.17: Estimation of phase and frequency offsets side-by-side                       |

#### **ABSTRACT**

The popularity of the wireless devices comes from several advantages related to this type of communication, i.e. mobility, easy installation and less cost for infrastructure. Hence it is vital to assure a reliable communication where errors can be autonomously fixed and information responsibly secured. The transmission over wireless channel results in frequency and phase offsets; additionally the received symbols are corrupted with noise. Therefore the estimation of the actual frequency and phase offset becomes a very critical task with high impact on communications performance; synchronization is a crucial part of each receiver in digital communication systems. In this context, throughout this work is proposed an implementation of a Fine Carrier Synchronization Unit that aims a better communication quality and lower its error rate.

**Key-words:** Wireless Communication, Synchronization, Frequency and Phase offsets.

## Unidade de Sincronização Fina de Portadoras para Sistemas de Sincronização Turbo

#### **RESUMO**

A popularidade de equipamentos sem fio decorre de uma série de vantagens relacionadas a este tipo de comunicação, i.e. mobilidade, fácil instalação e menor custo para infra-estrutura. Consequentemente é vital garantir-se uma comunicação confiável onde erros podem ser automaticamente corrigidos e a informação segura. A transmissão sobre canais sem fio resulta em deslocamentos de frequência e fase; além disso, os símbolos recebidos podem ser corrompidos com ruído. Portanto, uma estimativa dos valores de deslocamento reais de frequência e fase se torna uma tarefa fundamental com grande impacto no desempenho da comunicação. Sincronização é uma parte crucial em cada receptor em sistemas de comunicação digital. Nesse contexto, ao longo deste trabalho é proposto a implementação de uma Unidade de Sincronização Fina de Portadoras que visa melhorar a qualidade da comunicação e diminuir a taxa de erros da mesma.

**Palavras-Chave :** Comunicação sem fio, Sincronização, Deslocamentos de Frequência e Fase.

#### 1 INTRODUCTION

With the increase of mobility in our world, there is a rising necessity for communication and to have access to information, independently of the location of the individuals or information. Importance is given by the possibility that any phone call can be essential enough to save a life, close a business deal or provide hours of entertainment. Each of these examples of mobile communications proposes a challenge that can only be achieved with an efficient and reliable wireless communication.

Synchronization and channel coding/decoding are vital parts for wireless communication in every digital receiver—it decreases the errors and allows to reduce the transmission power respectively aiming for improvements in the performance [MENGALI, 1997]. With the intensification of devices using wireless data transmission technologies, it is required that there exist efficient and responsible ways to fix errors that may happen in this kind of transmission. When using wireless channel the received data will always be corrupted by some kind of noise—also timing, phase and frequency offset are introduced and somehow must be taken care of.

Receiver for wireless communication systems are in charge of the synchronization, decoding and detection [MEYR, 1997]. Detection is the ability to discern between information-bearing energy patterns and random energy patterns that distract from the information. Decoding is doing the opposite process of the encoding, in order to retrieve the original information.

In many coding systems, a decoder additionally produces soft (or side) information outputs to help another decoder identify and perhaps correct introduced errors. For example, in a Global System for Mobile (GSM) communication, an inner decoder comprising an equalizer generates a soft information output derived from path metric differences and an outer decoder comprising an error control decoder utilizes the output soft information to detect and correct introduced errors [REDL, 1995]. Soft information outputs have historically been generated by decoder in conjunction with the selection of the closest code word and its associated hard information output. Non algebraic decoders (e.g. Convolutional, Turbo) use also soft input information to increase decoding performance.

The reliability information comprising the soft information output is calculated for each individual symbol within the hard information output. The reliability of each symbol within the hard information output vector is derived without taking into consideration either the remaining symbols within that hard information output vector or any other considered code words. This is achieved by comparing the probability of the received data given a bit with a logical value of one was transmitted to the probability of the received data given a bit with a logical value of zero was transmitted.

At this moment, the Turbo codes are introduced with the purpose to improve the performance and the quality of the communication. That is only possible because a turbo code iteratively exchanges soft information, which will help the task of synchronization. Turbo codes are advanced codes which reduce bit-error-rate (BER) and frame-error-rate (FER) in comparison to other codes like convolutional codes or algebraic codes (e.g. Hamming and Reed-Solomon). Turbo Synchronization is a technique that uses the soft information to estimate the parameters needed to decrease the error rate of the communication [NOELS, 2003]. In turbo receivers, synchronization is a very challenging task – since they operate at very low signal-to-noise ratio (SNR) and therefore classical synchronizers may fail to provide reliable estimated parameters [LEHNIGK-EMDEN, 2008)]. Turbo decoders are working iteratively and after each iteration produce a soft output; it is important to note that the iterative nature of decoding allows to support synchronization.

Due to the time and purpose of this work, synchronization is the main subject. Channel decoding is left aside but it has potential to be a topic for future work. This work had as focus the frequency and phase synchronization of bursts with linear modulation, i.e. Quadrature Phase Shift Keying (QPSK) modulation. The system aims the Digital Video Broadcast – Return Channel via Satellite (DVB-RCS) standard, which is an ETSI satellite communication standard [ETSI, 2012].

Timing synchronization, sampling rate and other problems related to the communication are properly carried out before, which means that this work will focus only on the frequency and phase offset only.

It is a known fact that simulations can reduce development time and costs. A project was created at the Microelectronic Systems Design Research Group from the Technical University of Kaiserslautern, which developed the software Creonic Simulation Environment – CSE [MSDRG, 2012]. The purpose of CSE is to allow for the integration of complex simulations environments; there can be seen two distinguished models that compound CSE: the transmitter part and the receiving part. The simulation of the synchronization task for such communication systems has enormous importance on the whole project.

CSE was the starting point for the work developed. New features aiming the Fine Carrier Synchronization Unit were developed, tested and introduced into the already existing simulation environment – achieving a more powerful and wider software. Hardware implementations on Very High Speed Integrated Circuit (VHSIC) Hardware Description Language (VHDL) of these new features were also developed. Exactly the same functionality was intended in order to allow a complex and reliable comparison between both implementations. Therefore, it was possible to evaluate both – software and VHDL – according to the theory of communication systems and produce a good and complex statistical output.

#### 1.1 Objectives of This Work

This work has as purpose two main objectives:

- 1. Implementation of the Fine Carrier Synchronization module in software and its integration to the CSE, as well as the implementation of the same module in VHDL.

- 2. Analysis, comparison and evaluation of the accuracy of the implemented software and its correspondent in VHDL.

#### 1.1.1 Implementation of New Modules in Software

To achieve the first goal, the whole functionality of techniques of Synchronization for digital receivers was taken into account. Once the behavior was deeply comprehended, it became certain that a better and effective approach on the implementation of new synchronizations modules for any communications system was going to be reached. With the support of the CSE, it was possible to focus exactly on what this work proposes: the Fine Carrier Synchronization Unit. The software implementation of this unit and the integration with the CSE as a new module was aimed. An additional module for the transmitting part of the CSE (called Add Offset Module) was developed, which introduces the error of frequency and phase offset in the simulation system. This frequency and phase error will be estimated in the receiving part. The implementation of a correction module for phase and frequency offset is also necessary. To conclude, several upgrades on the Statistics Module of CSE were done in order to adapt it to the whole new set of functionalities performed by the CSE. With all the extensions of the CSE, it is possible to evaluate the statistical behavior (communication performance) of the new Fine Carrier Synchronization Unit.

#### 1.1.2 Implementation of New Modules in VHDL

The hardware implementation in VHDL can be defined exclusively based on the needs of this work; it is not – so far – part of a bigger project. Xilinx ISE Design Suite V13.2 is the used digital system design tool and VHDL is the chosen language. It is a powerful and versatile description language, with multiple mechanisms to support design hierarchy and multiple levels of abstraction. The module in VHDL was implemented aiming exactly the same functionality of the Fine Carrier Synchronization Module developed in the software. In order to achieve this goal it was necessary to make a deep analysis of how to accomplish in VHDL several functionalities easily reached in the software – and to find the perfect approach during this "translation" from software to hardware. The VHDL was simulated and synthetized with the same framework that was used to its development.

#### 1.1.3 Comparison between Software and VHDL

After the first objective of this work was successfully accomplished, the accuracy needed to be verified; it is essential that the output software and hardware are of a high excellence and properly studied. There is completely no point in developing, spending time and effort to analyze a system that does not fulfill the requirements of modern communication systems. It was also vital to re-examine new ways to improve processes and run them repeatedly - ensuring credibility, quality and functionality.

Hardware simulations and analysis are known for being extremely time-consuming. Taking into account the fact that the evaluation and the testing are extremely necessary in order to have a consistent and reasonable implementation; it was really important to

find a way to bypass this problem and prove its functionality and reliability accordingly to the desired accuracy. Therefore, the idea to improve and optimize the simulations and analysis was to have the software to support this task. The hardware and software were implemented based on the same study; consequently they both do the exact same calculations and produce the same output – designated to different platforms. This way, it was intended to have a higher number of test cases on the software than on hardware but proceed with both evaluations together – also based on comparisons and exchange of information between the two implementations.

In order to achieve a deep analysis of the developed software and hardware – regarding the originals modules included in CSE – some features will be added to the Statistics Module with the purpose of statistically analyze the Fine Carrier Synchronization Module and its functionality.

Among the objectives of this work is the implementation of such Fine Carrier Synchronization Unit in VHDL. At this point it is crucial to understand some differences between the software and the hardware implementation, for example, there is completely no use to do the VHDL implementation of the Add Offset Module, which is part of the transmit model of CSE. The "real world" is in charge of this task – adding some frequency and/or phase offset to the set of bits. By developing exactly the same unit as in the software, it is possible to assure that it will have the same functionality. Therefore, all efforts must be done on the hardware implementation of the Fine Carrier Synchronization Module. Simulations and comparisons between both, the software and the hardware implementations, was part of the usual day-to-day work while this project was under development.

#### 1.2 Structure of the work

The rest of this work is structured as follows. In chapter 2, an overview of the basic concepts needed and technical concepts involved on this work. Chapter 3 shows the whole functionality and architecture of CSE and advantages conquered by taking it as the first step into the development and implementation of the Fine Carrier Synchronization Unit. Chapter 4 deals with the software and hardware implementation of the new modules, specifically which were the adopted design options and the mathematical approach to every new module. In chapter 5, it is discussed how the validation was done, explaining the test environments, the scenarios, the methodology and the statistical evaluation of the developed software and VHDL. Chapter 6 brings the conclusion of this work. Finally, this work contains an annex A, that is the project of this work, an annex B, which is the full Xilinx ISE Design Tool Synthesis report, and an annex C, which is a summary of the thesis translated to Portuguese.

#### **2** BASIC CONCEPTS

At this point, it is important to understand how the information can be transmitted from one point to another. By varying one physical property, i.e. voltage or current, the information can be transmitted in wires. By representing the value of this voltage or current as a function of time, (t), it is possible to model the behavior of the signal and analyze it mathematically.

In the XIX century, Jean-Baptiste Joseph Fourier, a French mathematician and physicist, proved that any periodic function, g(t), with period T can be constructed by the sum of a number (possibly infinite) of sines and cosines [OPPENHEIM, 1989].

$$g(t) = a_0 + \sum_{n=1}^{\infty} \left( a_n \cos \frac{n\pi t}{T} + b_n \sin \frac{n\pi t}{T} \right)$$

(2.1)

Where  $a_n$  and  $b_n$  are the amplitude of the sine and cosine from the n harmonic terms and  $a_0$  is a constant – this decomposition is called Fourier series. From this Fourier series, the function can be reconstructed; which means that, if the period T is known and the amplitudes also given, the original function of time can be found by making the sum of the equation 2.1. A data signal with a finite duration can be treated based on the premise that it repeats the same pattern; the interval between 0 and T is equal as the one between T and 2T – and it follows this configuration towards  $\infty$ .

Communication systems can be classified into two groups depending on the range of frequencies they use to transmit information. These communication systems are classified into baseband or pass band system. Baseband transmission sends the information signal as it is without modulation (without frequency shifting) while pass band transmission shifts the signal to be transmitted in frequency to a higher frequency and then transmits it, where at the receiver the signal is shifted back to its original frequency.

There are several different ways to accomplish the transmission, each one of them has their own bandwidth (difference between the upper and lower frequency – measured in Hertz), delay, cost and ease of installation and maintenance. They can be classified into guided media (i.e. copper wire and optic fiber) or not guided media (i.e. radio waves and laser).

Unfortunately media are not perfect, therefore the received signal is not the same as the transmitted signal – this difference can lead to error. Transmission lines suffer from three major problems: attenuation, delay distortion and noise.

These errors are responsible for wrong interpretation of the information transmitted, therefore is important to be prepared to deal with errors automatically. At this point the Synchronization of the signal fits to the whole system, because it tries to estimate and correct all the negative parameters – eliminating the negative effects – before the signal is interpreted.

#### 2.1 Modulation

Computers are able to manage only binary numbers; it is possible to understand 0's and 1's, consequently it is necessary to develop some kind of alphabet or pattern to enable a proper and, many times, really complex communication with just two types of signal. The amplitude, frequency and phase of this signal can be modulated in order to transmit information. The amplitude modulation is characterized by the variation of two different amplitudes used to represent 0's and 1's. The frequency modulation, also known by frequency shift keying, are used two or more different tones. The phase modulation of the carrier is shifted systematically 0 or 180 degrees in equal periods of time. It is important to mention that this work will be restricted to digital modulation [TREES, 2001].

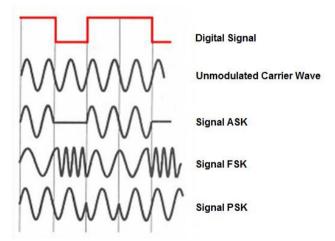

Modulation means the possibility to change one of the signal's properties (amplitude, frequency or phase) in such a way that different states are possible. Each possible state represents one symbol of the alphabet and it works with this "language" – the alphabet must be previously defined and known by both sides. Therefore, modulation means adding information on amplitude, frequency or phase. Figure 1 shows different modulations and how they can be represented and characterized to transmit a digital signal. In amplitude modulation or amplitude-shift-keying (ASK), two different amplitudes are used to represent 0 and 1. In frequency modulation or frequency-shift-keying (FSK), two – or more – different tones are used. In phase modulation or phase-shift-keying (PSK), the carrier wave is shifted 0 or 180 degrees at uniformly spaced intervals – the simplest form of PSK called Binary PSK (BPSK). The term keying is also widely used in the industry as a synonym for modulation.

Figure 2.1: Different modulations applied to a digital signal BPSK

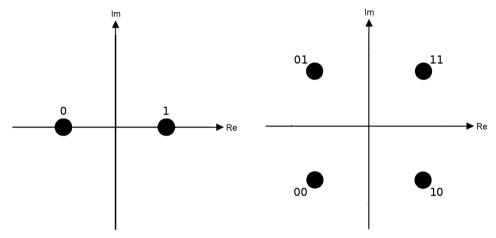

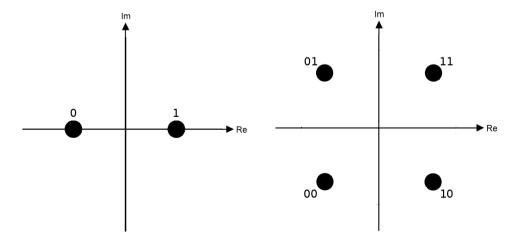

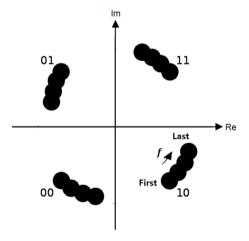

The communication can be represented in a complex plane and, for example, a Quadrature Phase Shift Keying (QPSK) has a defined alphabet with 4 symbols (00, 01, 10 and 11), equally divided on the plane. Consequently, it's natural to understand that for every  $90^{\circ}$  or  $\pi/2$ , that there will be the area where one symbol will be represented. It

is usual to refer this organization of symbols in a complex plane as a constellation diagram – Figure 2.1. There are several modulations available and in use nowadays, i.e. BPSK, QPSK, 8PSK, 16-Quadrature Amplitude Modulation (QAM), 64-QAM, etc.

Figure 2.2: Constellation diagram for BPSK (left) and QPSK (right) with gray coding

In order to explain the figure 2.2, it is important to remind that the number of symbols (constellation point) per bits respects the formula 2.2, which represents that, for example, for every 1 bit, 2 symbols can be represented and for 2 bits, 4 symbols can be represented – accordingly to equation 2.2. This means that according to the modulation scheme a symbol represents 1, 2, 4 or more bits.

The modulation would work perfectly if there were no errors, noise and degradation of signal. To understand how an error occurs, it is important to note that once something went wrong, these symbols are not going to be on the exact expected place. Due to the noise, the symbol – the "point" in figure 2.2 – shifts its position in the complex plane when compared to the original position. This shifting will not always result in wrong interpretation – it can vary certain acceptable range and it will still be considered as the right symbol.

$$Number_of_Bits = log_2 Number_of_Symbols$$

(2.2)

#### 2.2 Signal Degradation by Noise

The noise is a random fluctuation in an electrical signal, which can arise in various forms. The amount of noise present is measured by the ratio of the signal power to the noise power, called signal-to-noise ratio (SNR). The signal power is denoted by S and the noise power by N, the signal-to-noise ratio is S/N. Usually, the ratio itself is not represented; instead, the quantity  $10log_{10}S/N$  is given. These units are called decibels (dB).

Attenuation is the loss of energy as the signal propagates outward. The loss is expressed in decibels per kilometer. The quantity of energy lost depends on the frequency. To understand how the frequency affects this signal, imagine that it is not as simple wave form but as a component of a Fourier series; which each component has a different frequency and amplitude and is attenuated in a different proportion, resulting in different Fourier spectrum on the receiver's side.

To make things even worse, the several components of Fourier also have different propagation speed in the wire; this speed difference also leads to distortion of the signal received in the other end.

Another problem is the noise, which consists of an undesirable energy from other sources, not the transmitter. The thermal noise exists due to the random motion of electrons in the wire, which is inevitable. Crosstalk happens due to the inductive coupling between two wires that are close to each other. There is also the impulse noise, which happens due to spikes on the power line or other causes. For digital data, impulse noise can result in loss of one or more bits.

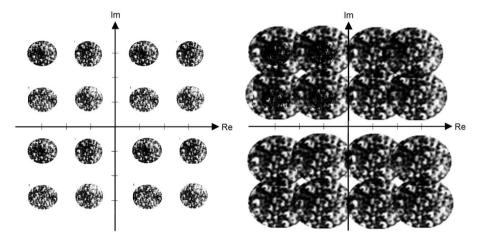

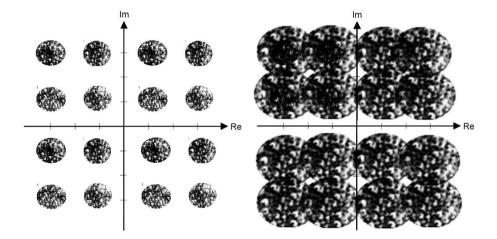

Of course a little variation on signal at the receivers side of the transmission is expected, the real problem starts when this error is bigger than the range of acceptable variation. In a very noisy environment, for matter of explanation, figure 2.3 makes it more understandable.

Figure 2.3: 16-QAM with an acceptable range variation (left – high SNR) and a very noisy range variation (right – low SNR)

Figure 2.3 comes with the purpose to illustrate and to remind that there might be different levels of noise variation; therefore, the task of classification of the received symbols may be affected or not due to the noise of the system – it is possible that some noise is harmless to the communication quality. On a high SNR environment the symbols do not have massive losses caused by noise (left part of figure 2.3); it is possible that the variation may not be enough to disturb and cause errors on the interpretation of the symbols. With a low SNR (right part of figure 2.3), the analysis and classification of the symbols can be disrupted since the range of variation of different symbols have an intersection where two different interpretations for the same coordinate is possible – which results in an error of reading the symbol. It is also important to remind that figure 2.3 does not represent an instant "picture" of the communication; it symbolizes all the possible states of the media.

SNR is going to define how bad the signal will get after going through the channel. It is directly influenced by the noise variation of the channel. Also included in the negative parameters of any synchronization are the frequency and phase offset. Figure 2.3 can be observed also by differentiating the values of SNR: left part of figure 2.3 is the representation of a high SNR value; while the right part of figure 2.3 corresponds to a low SNR value.

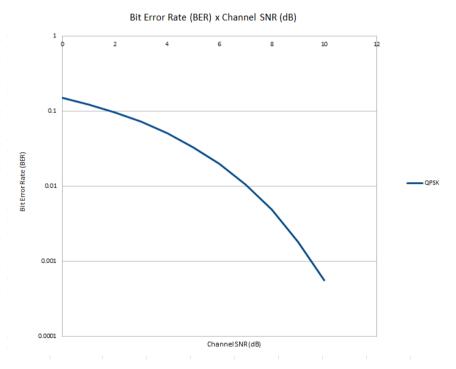

The bit error rate (BER), in a digital transmission, is the percentage of bits with errors divided by the total number of bits that have been transmitted, received or processed over a given time period. The rate is typically expressed as 10 to the negative power. For example, four erroneous bits out of 100,000 bits transmitted would be expressed as  $4 \times 10^{-5}$ , or the expression  $3 \times 10^{-6}$  would indicate that three bits were in error out of the 1,000,000 transmitted. BER is the digital equivalent of signal-to-noise ratio in an analog system.

As it can be seen in figure 2.4, the relation between BER and SNR in a simulation of a communication using QPSK shows that with the increase of the SNR, the BER will get lower (important to remind that it will never be errorless). The BER behavior of the transmitted signal is the reason for using coding techniques [TAUB, 2008].

Figure 2.4: Bit Error Rate (BER) x Channel SNR (in dB) in a QPSK communication

Frequency offset exists as the consequence from the difference between the oscillator from the transmitter (TX) and the one from the receiver (RX); the oscillators from TX and RX cannot be exactly equal. To comprehend how the frequency offset can be observed, it is primordial to understand that they do not come at the exact same moment; it is an error that increments its effect while the transmission proceeds.

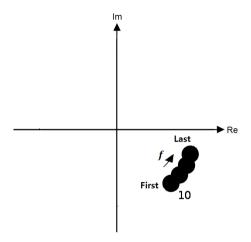

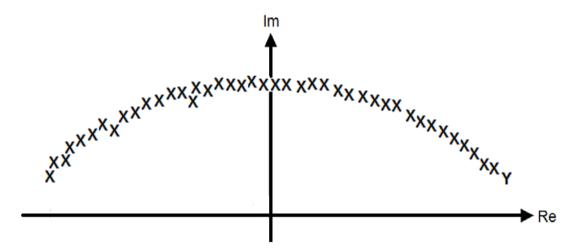

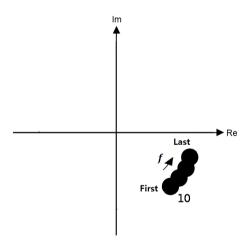

For example, figure 2.5 represents the transmission of "10101010" with a frequency offset f, which is responsible for adding a constant and incrementally error to every symbol. This is the reason why the symbols have a variation from the place identified on the figure as "first" and the "last". Every upcoming symbol will be a bit more displaced regarding the original position of the "10" on the complex plane. Due to didactic purposes, the whole bit stream is represented on a complex plane as an accumulator – if an instantaneous picture were taken of the complex plane, just one "10" symbol would be present at a moment and this would not be helpful for the comprehension of the concepts [BRACK, 2005b].

Figure 2.5: Illustration of a frequency offset (f) in a QPSK modulation

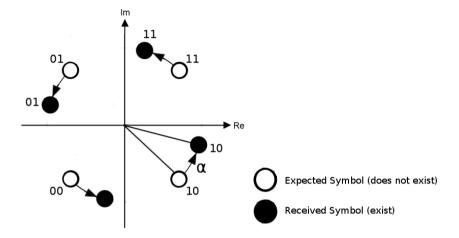

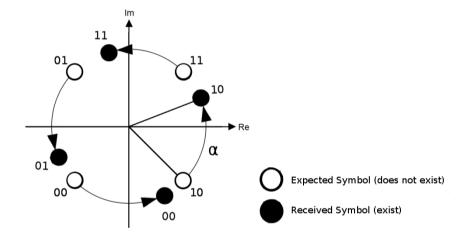

Frequency offset have a higher impact on symbols as they are more close to the end of the burst – the impact of the frequency offset will not be the same for every symbol, it is sequentially added to every new symbol [BRACK, 2005a]. On the other hand, the phase offset is the same to the whole bit stream – it acts in every symbol exactly in the same way. In figure 2.6 is explained how the phase offset works in a QPSK modulation.

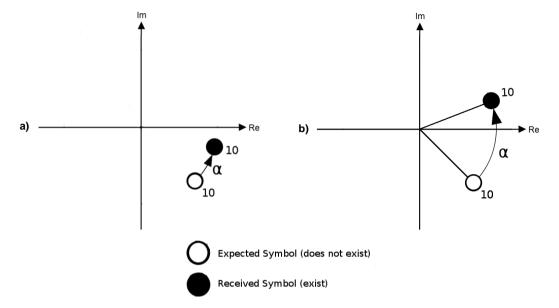

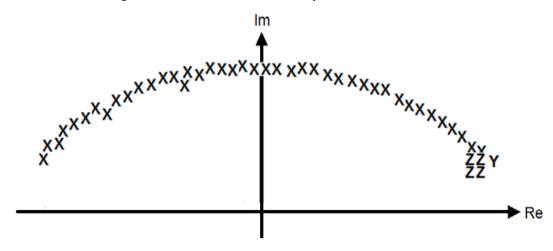

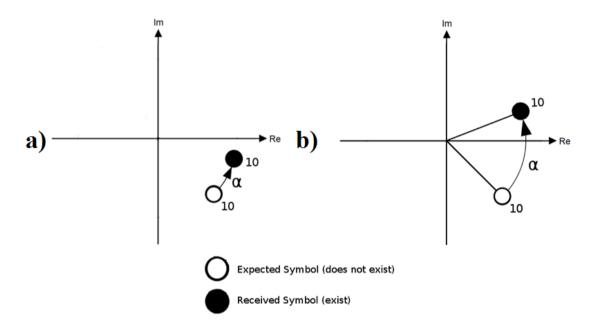

The analysis and classification of each received symbol is a receiver's task, the interpretation of the symbol is qualified in a complex plane. Figure 2.6 a) shows a QPSK transmission where a symbol "10" was transmitted with a phase offset ( $\alpha$ ) – assuming that the frequency offset is zero. The classification of this symbol does not imply any error in its interpretation; since the QPSK implies that every symbol has a 90 degrees range, it is possible to have a phase offset with no error on the interpretation of the signal. Figure 2.6 a) is important to understand that not every phase offset would result in error.

On the other hand, with figure 2.6 b) it is prominent that the phase offset introduced will result in error of the interpretation of this symbol. The symbol was located in a quadrant of the complex plane and after the addition of the phase offset it is on a different one. This means that its interpretation will result in error, which can be corrected with the right estimation of this phase offset and its future correction [VITERBI, 1983].

Figure 2.6: Illustration of phase offset ( $\alpha$ ) in a QPSK modulation

#### 2.3 Channel Capacity

Besides the errors, it is mandatory to take into account physical limitations of the media. Henry Nyquist has developed studies not just related to channel capacity but also to the sampling rate and the comprehension of both is f undamental to proceed. Channel capacity is the maximum data transfer which can occur when using the communication channel with bandwidth B – channel capacity can be defined with equation 2.3 [TANENBAUM, 2003].

Channel Capacity<sub>max</sub> =

$$2B$$

In 1924, Nyquist realized that even a perfect channel has a finite transmission capacity. He derived an equation expressing the maximum data rate for a finite bandwidth noiseless channel. In 1948, Claude Shannon carried Nyquist's work further and extended it to the case of a channel subject to random (thermodynamic) noise.

Nyquist proved that if an arbitrary signal with highest frequency component, in hertz, is  $f_{max}$  the sampling rate must be at least  $2*f_{max}$  or twice the highest analog frequency component. The sampling in an analog-to-digital converter is done by a pulse generator (clock). If the sampling rate is less then  $2*f_{max}$ , some of the highest frequency components in the analog input signal will not be correctly represented in the digitized output. When such a digital signal is converted back to analog form by a digital-to-analog converter, false frequency components appear that were not in the original analog signal. This undesirable condition is a form of distortion called aliasing. In equation 2.3, the signal consists of V discrete levels.

$$Maximum\ data\ rate = 2f_{max} \log_2 V\ bits/\sec$$

2.3

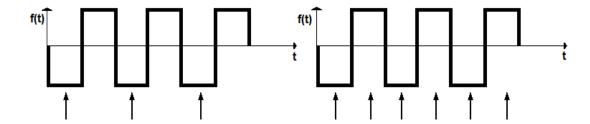

Figure 2.7 shows that a failure on the sampling rate can determine a serious mistake on the interpretation; it is the transmission of a code word 010101, by not obeying the Nyquist theorem, the interpretation will be 000 (left). By taking a correct sampling rate the right information is correctly acquired: 010101(right).

Figure 2.7: Illustration of a not properly sampling rate (left) and a properly sampling rate (right) accordingly to Nyquist theorem

Figure 2.7 represents the problem on the task of conversion of an analog-digital conversion. It is necessary to get a discrete number of samples in a continuous signal. The main problem is on the sampling/seconds rate that should be taken. A small number can result in a really poor representation of the signal. At first, the process of sampling of an analog signal can be thought that always will be losses of the information and that with the best sampling rate the losses are going to be the smaller possible; however, Shannon's theorem shows that this is not always true. Under certain conditions, the sampling of a signal can transmit precisely all the information contained in the signal. This means that the signal can be perfectly recovered from samplings without any decrease on the signal quality.

If random noise is present, the situation deteriorates quickly. Since there is always random (thermal) noise present due to the motion of the molecules in the system, this cannot be left aside. Shannon's major result is that the maximum data rate of a noisy channel whose bandwidth is  $f_{max}$ , in hertz, and whose signal-to-noise ratio is S/N, is given in equation 2.4. Shannon's result was derived from information-theory arguments and applies to any channel subject to thermal noise.

Maximum Number of bits/sec =

$$f_{max} \log_2 \left(1 + \frac{S}{N}\right)$$

2.4

#### 2.4 Techniques of Detection and Correction of Errors

Among the error detecting methods there are Parity Check Method and Cyclic Redundancy Check (CRC) Method. Parity check method is the method where one parity check bit is used along with each character code to be transmitted; as a simple example of an error-detecting code, consider a code in which a single parity bit is appended to the data. The parity bit is chosen so that the number of 1-bits in the code word or character code to be transmitted or recorded is even or odd.

For example, when 10110101 is sent in even parity by adding a bit at the end, it becomes 101101011, whereas 10110001 become 101100010 with even parity. A code with a single parity but has a distance 2, since any single-bit error produces a code word with the wrong parity, it can be used to detect single errors. Two errors cannot be detected by this scheme as the total number of 1s in the code will remain even after two bits change. As the probability of more than one error occurring is in practice very small, this scheme is commonly accepted as sufficient.

Instead of appending a parity check, which makes the total of 1-bits in the code even, one may choose to append a parity check bit which makes the number of 1-bits in

the code odd. Such parity check is known as an odd parity bit. This scheme also facilities detection of a single error in a code.

The CRC is wide spread for error detection, which codes are based upon treating bit steam as a representation of polynomials with co-efficient of zero and one only.

A k + bit frame is regarded as the co-efficient list for a polynomial with k terms, ranging from xk - 1 to x0. Such a polynomial is said to be of degrees k - 1 the high order (left most) bit is the coefficient of xk - 1, the next bit the coefficient of xk - 2, and so on. I.E. 110001 has six bits and thus represents a six-term polynomial with coefficient 1, 1, 0, 0, 0 and 1:  $x^5 + x^4 + x + 0$ .

When the polynomial code method is employed, the sender and receiver must have agreed upon a generator polynomial, G(x), in advance. Both the high-and-low-order bits of the generator must be 1. To compute the checksum for some frame with m bits, corresponding to the polynomial M(x), the frame must be longer than the generator polynomial.

The idea is to append a checksum to the end of the frame in such a way that polynomial represent by the check summed frame, it tries dividing by G(x). If there is a remainder, there has been a transmission error.

The correction of errors is more difficult than the detection. In error detection, it is just a system where it just looks to find if any error has occurred. The answer is simple yes or no. In error correction, it is demanded to know the exact number of bits that are corrupted and more importantly, their location in the message [CLARK, 1981]. The number of errors and the size of the message are important factors. Supposing the correction of one single error in an 8-bit data unit, it is necessary to consider eight possible error locations; if there were two errors in the same data unit, it is essential to consider 28 possibilities. Therefore, it is possible to imagine the receiver's difficulty in finding 10 errors in a data unit of 1000 bits.

To understand how errors can be handled, it is necessary to look closely at what an error really is. Normally, a frame consists of m data (i.e., message) bits and r redundant, or check, bits. Let the total length be n (i.e., n = m + r). An n-bit unit containing data and check bits is often referred to as an n-bit code word.

Given two code words, say, 10001001 and 10110001, it is possible to determine how many corresponding bits differ. In this case, 3 bits differ. The number of bit position in which two code words differ is called the Hamming Distance (Hamming, 1950). Its significance is that if two code words are a Hamming distance d apart, it will require d single-bit errors to convert one into the other.

In most data transmission applications, all  $2^m$  possible data messages are legal, but due to the way the check bits are computed, not all of the  $2^n$  possible codewords are used. Given the algorithm for computing the check bits, it is possible to construct a complete list of the legal codewords, and from this list find the two code words whose Hamming distance is minimum. This distance is the Hamming distance of the complete code.

The error-detecting and error-correcting properties of a code depend on its Hamming distance. To detect d errors, you need a distance d+1 code because with such a code there is no way that d single-bit errors can change a valid code word into another

valid code word. When the receiver sees an invalid code word, it can tell that a transmission error has occurred. Similarly, to correct d errors, you need a distance 2d+1 code because that way the legal code words are so far apart that even with d changes, the original code word is still closer than any other code word, so it can be uniquely determined.

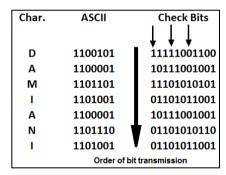

There is a trick that can be used to permit Hamming codes to correct burst errors. Sequences of k consecutive code words are arranged as a matrix, one code word per row. Normally, the data would be transmitted one column at a time, from left to right, as shown in figure 2.8. To correct burst errors, the data should be transmitted one column at a time, starting with the leftmost column. When all k bits have been sent, the second column is send, and so on. When the frame arrives at the receiver, the matrix is reconstructed, one column at a time. If a burst error of length k occurs, at most 1 bit in each of the k code words will have been affected, but the Hamming code can correct one error per code word, so the entire block can be restored. This method uses kr check bit to make blocks of km data bits immune to a single burst error of length k or less. Where r represents the number of verification bits and m the number of bits in each message.

Figure 2.8: Hamming code trick to correct burst errors

It is important to remind that several others forward error correction (FEC) codes are available now at the academic and industry field, for example Reed-Solomon (RS), Low-Density-Parity-Check (LDPC), etc [SNIFFIN, 2009].

Also important is to mention a method to recover from errors, Automatic Repeat Request (ARQ). This method is an error control for data transmission that makes use of error-detection codes, acknowledgment and/or negative acknowledgment messages, and timeouts to achieve reliable data transmission. An acknowledgment is a message sent by the receiver to indicate that it has correctly received a data. Important to keep in mind that ARQ is not a correction method (it does not correct any wrong information received) but a recovery method (it recovers the system from wrong information received).

Unusually, when the transmitter does not receive the acknowledgment before the timeout occurs (i.e., within a reasonable amount of time after sending the data frame), it retransmits the frame until it is either correctly received or the error persists beyond a predetermined number of retransmission.

ARQ is appropriate if the communication channel has varying or unknown capacity, such as is the case on the Internet. However, ARQ requires the availability of a back channel, results in possibly increased latency due to retransmissions, and requires the

maintenance of buffers and timers for retransmissions, which in the case of network congestion can put a strain on the server and overall network capacity.

Turbo codes are a development in the field of forward-error-correction channel coding. Turbo codes make use of three simple ideas: parallel concatenation of codes to allow simples decoding; interleaving to provide better weight distribution; and soft decoding to enhance decoder decisions and maximize the gain from decoder interaction [ALLES, 2007].

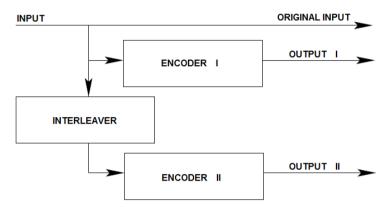

A turbo code is formed from the parallel concatenation of two codes separated by an interleaver. Interleaving is a way to arrange data in a non-contiguous way to increase performance. A generic design of a turbo code is shown in figure 2.9.

Figure 2.9: A generic turbo encoder

Although the general concept allows for free choice of the encoders and the interleaver, most designs follow the same ideas:

- The two encoders used are normally identical;

- The code is in a systematic form, i.e. the input bits also occur in the output;

- The interleaver reads the bits in a pseudo-random order.

This serves two purposes. Firstly, if the input to the second encoder is interleaved, its output is usually quite different from the output of the first encoder. This means that even if one of the output code words has low weight, the other usually does not, and there is a smaller chance of producing an output with very low weight. Higher weight is beneficial for the performance of the decoder. Secondly, since the code is a parallel concatenation of two codes, the divide-and-conquer strategy can be employed for decoding. If the input to the second decoder is scrambled, also its output will be different or "uncorrelated from the output of the first encoder. This means that the corresponding two decoders will gain more from information exchange.

In the traditional decoding approach, the demodulator makes a "hard" decision of the received symbol, and passes to the error control decoder a discrete value, either a 0 or a 1. The disadvantage of this approach is that while the value of some bits is determined with greater certainty than that of others, the decoder cannot make use of this information.

A soft-in-soft-out (SISO) decoder receives as input a "soft" (i.e. real) value of the signal. The decoder then outputs for each data an estimate expressing the probability that the transmitted data bit was equal to one. In the case of turbo codes, there are two

decoders for outputs from both encoders. Both decoders provide estimates of the same set of data bits, but in different order. If all intermediate values in the decoding process are soft values, the decoders can gain greatly from exchanging information, after appropriate reordering of values. Information exchange can be iterated a number of times to enhance performance. At each round, decoders re-evaluate their estimates, using information from the other decoder, and only in the final stage will hard decisions be made, i.e. each bit is assigned the value 1 or 0. Such decoders, although more difficult to implement, are essential in the design of turbo codes.

#### 2.5 General Considerations

By comprehending how it can be possible to transmit information over wires and wireless systems, and mainly its importance to modern communication systems; it is possible to understand why several studies on this topic must be realized - high quality systems are demanded throughout the most dynamic range of systems that depends on this kind of communication. The system must somehow certify that the way of sending information through a channel works and is efficient (modulation), the same system must be aware of interferences and it is also important to be able to work independently; detecting and correcting possible errors in an autonomous way.

As a way of increasing the quality and the utilization of time and resources when developing such systems, a simulation environment must be used. In order to enable tests, prototyping, education and the statistical analysis of such systems is mandatory. The next chapter is dedicated to explain which simulation environment was used during this work. This system – Creonic Simulation Environment – is introduced; its architecture and design options are presented and discussed, as well as advantages and disadvantages.

#### **3** CREONIC SIMULATION ENVIRONMENT - CSE

CSE was developed by the Microelectronic System Design Research Group and Dr.-Ing Timo Lehnigk-Emden and Dr.-Ing Matthias Alles – both are now former researchers from the Microelectronic System Design Research Group. CSE was one of the successful academic projects that had become a company in real world – Creonic IP Cores & System Solutions GmbH [CREONIC, 2012]. Creonic is a spin-off of the University of Kaiserslautern, founded in 2010. With broad technical knowledge and experience of business activities, the founding of Creonic was the logical consequence after successful academic projects.

The main application of the Microelectronic System Design Research Group is decoding. The purpose of CSE is to have a simulation environment for decoders – there are similar tools commercially available from Synopsys and Cadence. These commercial tools provide more features but also require money for licensing and normally the use is more complex than CSE.

The development of communication systems is a very dynamic field with respect to technical progress. In this context, Creonic collaborates closely with the Microelectronic System Design Research Group, which has an experience in the field of communication. This way it is possible to stay up-to-date regarding the state-of-the-art of science and technology – the results are the highest performance and at the same time low energy consumption.

Projects with such delicate design and development questions must be highly detail oriented. Hence, choices of design have been adopted and respected throughout the whole development of the software. For example, fixed interface and configuration procedures for functional modules, strict coding and documentation guidelines, and fully object oriented design were defined. For the documentation purposes, a documentation tool called Doxygen [DOXIGEN, 2012] was used – it generates the documentation from a set of documented source files automatically.

All the CSE project choices were done according to the goal of developing a system which can provide reduction of the development time and costs, facilitate the use, reusability and extensibility to new applications or standards.

By defining smart choices in the beginning of the project, i.e. reusability, the benefits to the project can be seen during the whole development. Reused software, which has been tried and tested in working systems, are more intend not to reveal any design and implementation fault. If software exists, there is less uncertainty in the costs of reusing that software than in the costs of development – it reduces the margin of error in project cost estimation.

CSE environment consists mainly of the library directory; which contains all the classes of the CSE, and the chains directory; containing some simulation chains, which use the library. Requirements to run the CSE are a g++ version 4.x under GNU/Linux, MS Windows or MacOS X, Microsoft Visual C++ under MS Windows and CMake – tool designed to build, test and package software.

C++ was the programming language chosen to the implementation of CSE. Which is a clever option based on the design choices made by the original developers of the software. C++ contains a good and rich standard library, compared to C, and also supports both the structured programming and object orientation [DALE, 2004].

#### 3.1 CSE Architecture

To completely comprehend the architecture of a complex simulation environment like CSE, it is necessary to come up with a specific approach in order not to miss any information or leave room for misunderstanding. On section 3.1.1 the class structure of any module and how the infrastructure provided by the system helps all the modules will be presented. On section 3.1.2 the original CSE modules are presented – they are all functional modules ready to enable the user to create new simulation chains.

#### 3.1.1 CSE Modules and Configuration

This simulation environment is extremely useful for projects related to communication systems; the simulations costs – related to configuration and connection – that once used to cost a lot of time, hours or days for the developers, now can be easily finished in a few minutes.

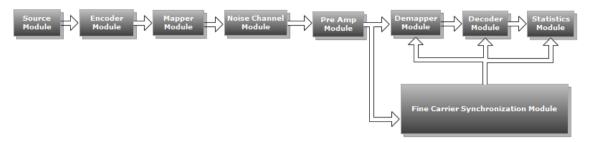

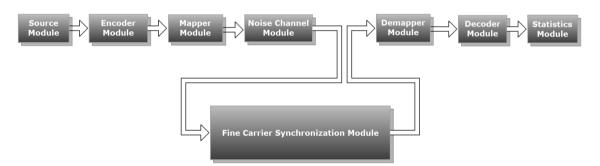

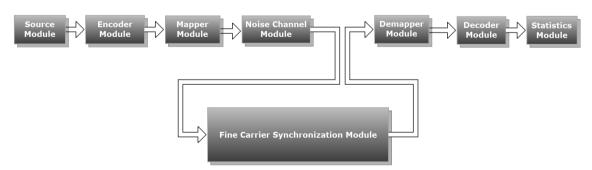

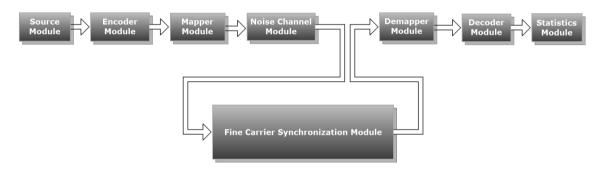

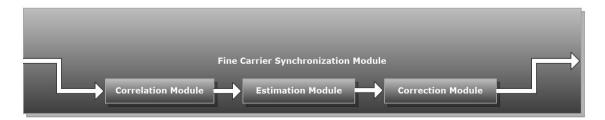

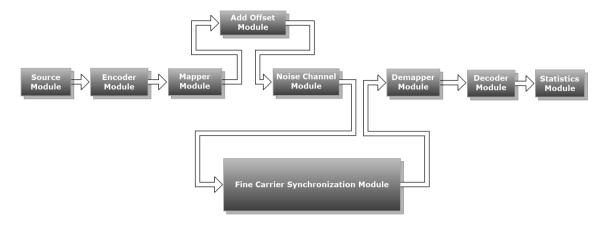

Figure 3.1: Original simulation chain and functional modules connection available on CSE

Figure 3.1 shows the simulation chain available on CSE, it represents the whole path that the bit stream will make. The source module generates random bit sequences. It is responsible for calculating one block of bits and storing them into an output buffer. The Encoder module changes the block of data bits (information bits) into a code; the code may be optimized for purposes of compressing for transmission or storage, encrypting or adding redundancies to the input code. The Mapper module is responsible for mapping bits to modulation symbols. The Noise Channel module adds to the simulation effects of real life – the impairment to communication is a linear addition of white noise with a constant spectral density and a Gaussian distribution of amplitude. The Demapper module receives the symbols from the channel and extracts the hard bits, the log likelihood ratio (LLR) values (LLR – is a statistical test used to compare the fit of two models) and the bit probabilities. The Decoder module will be in charge of the reverse operation of the encoder – changing the code into a set of signals and doing the estimation of the information bits. The Statistics module is responsible for comparing the input bits and the output bits, it takes into account the total amount of bits and how many of them are different – in other words, it is to verify how "faithful" is the output after passing through the entire simulation chain. Besides it computes this information into different statistical parameters.

The model used inside the Noise Channel Module to generate the noise is the Additive White Gaussian Noise – AWGN. Additive White Gaussian Noise (AWGN) is a white noise that is distributed according to the Gaussian distribution curve and a constant spectral noise power over the channel bandwidth. The AWGN noise affects the useful signal, which is linearly superimposed, hence the term additive. The total signal at the channel end corresponds to the addition of the amplitude of the input information signal and the amplitude of the noise signal.

All the configurations of the simulation using CSE are defined in the Extensible Markup Language (XML) configuration file, on this file it is possible – and necessary – to define all the configurations and parameters to every module instantiate. The XML file is used during runtime execution; therefore, it is not necessary to build the library if the aim is to build a simulation chain [RAY, 2001].

A typical XML configuration file starts with the main tag <cse\_chain> that contains all other tags. Each module is identified with the <instance\_name> tag, which corresponds to the <instance\_name> parameter that each module contains. By default, the instance name corresponds to the class name of the module. An optional <global> tag is also available. The purpose of this tag is to spread values to a multiple number of modules, without the need to set this value at multiple places of the XML – similar to the definition of "#define" in C++. Additional tags are dependent on the Parameter class of the module.

Up to now all the configuration works in a static environment. Therefore, the <iter> tag is introduced in the global section in order to define variables which will create a static configuration for each value. In case multiple iteration variables exist, the order of iteration variable definition is important – it turns several simulations into one with just one tag, simplifying a lot the work that has to be done. For example, in figure 3.2 by defining <num\_bits> inside the <iter> tag, it means that it will vary from 56 to 5600 with a pace of 100.

Figure 3.2: Explanation of the <iter> tag

An extra <param\_unit> tag exists for configuration of parameter units. The <unique\_id> attribute allows an automatic instantiation of the parameter unit during runtime. Parameter units allow the translation of parameters into other parameters.

Figure 3.3 shows an excerpt of the typical XML file with global parameters definition, parameters definition and the instantiation of three modules and its parameters: Mapper, Channel\_AWGN and Demapper.

```

<global>

<variable name="info bits">488</variable>

<variable name="other bits">488</variable>

<variable name="mapping">MAP QPSK</variable>

<variable name="num_bits_per_symbol">2</variable>

<variable name="noise_variance"><param param_unit="SNR" name="noise_variance"/></variable>

<variable name="es_n0">1.8:0.2:2.2

</iter>

</global>

<param_unit unique_id="Param_Unit_SNR">

<instance_name>SNR</instance_name>

<input_snr><global_variable name="es_n0"/></input_snr>

<input type>ES N0</input type>

<num info bits><global variable name="info bits"/></num info bits>

<num other bits><global variable name="other bits"/></num other bits>

<param name = "noise variance"></param>

<param name = "eb n0"></param>

<param name = "es_n0"></param>

</param unit>

<module>

<instance name>Mapper</instance name>

<mapping><global_variable name="mapping"/></mapping>

</module>

<module>

<instance name>Channel AWGN</instance name>

<noise variance><global variable name="noise variance"/></noise variance>

</module>

<module>

<instance_name>Demapper</instance_name>

<mapping><global_variable name="mapping"/></mapping>

<noise variance><global variable name="noise variance"/></noise variance>

</module>

```

Figure 3.3: Excerpt of the XML configuration file

#### 3.1.2 CSE Output

The CSE output is organized in a XML file, which brings the information of how the simulation chain was built as well as what parameters were used to perform the simulation. Besides this, it brings the statistics module output – which is the most important part at this moment. In figure 3.4 an excerpt of the simulation configuration details present on every XML output file is shown. The actual statistical output values are presented on figure 3.5, i.e., error rate bits, error rate blocks, etc.

All the data created and that goes through the simulation chain is analyzed by the statistics module at the end of the simulation – it gathers information at all moments but just analyzes in the end of the whole set of bursts since it takes into account not just one burst to get a result of what has been going on with the system. This is possible due to the fact that it is connected to both, the beginning and the end of the simulation chain.

```

<configuration>

<cse_chain>

<global>

<variable name="mapping">MAP_QPSK</variable>

</global>

<module>

<instance_name>Mapper</instance_name>

<mapping>MAP_QPSK</mapping>

</module>

<module>

<instance_name>Channel_AWGN</instance_name>

<noise_variance>0.251188643</noise_variance>

<start_seed>846546818653215</start_seed>

</module>

<module>

</cse chain>

</configuration>

```

Figure 3.4: Excerpt of the input configuration copied to the XML output file

```

<result>

<module name="Statistics_Error_Rates">

<status_out name="num_total_bits">

<value index="0">1120000</value>

</status out>

<status_out name="num_diff_bits">

<value index="0">127145</value>

</status out>

<status out name="error rate bits">

<value index="0">0.113522</value>

</status_out>

<status_out name="num_total_blocks">

<value index="0">10000</value>

</status_out>

</module >

</result>

```

Figure 3.5: Excerpt of the statistical results printed on the XML output file

#### 3.1.3 CSE Class Structure

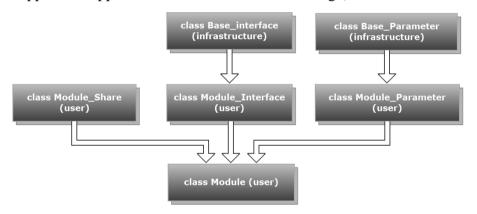

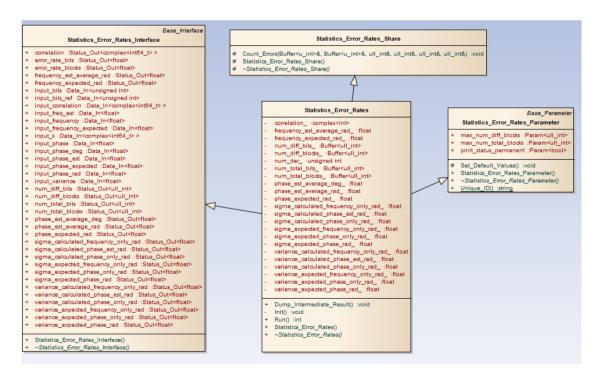

The simulation environment is composed of functional modules; they work as versatile pieces available to be organized together following the needs of the user, i.e. noise generator or channel decoder. These functional modules are connected with each other providing the possibility to create complex simulation chains. In order to have a uniform and constant development of any module, there are implementation concepts related to these functional modules that must be respected and preserved. Each module is derived from two or three classes that have to be written by the module designer:

The interface class, which defines the interface for the input and output of data to process. Furthermore, it provides status information, like number of used decoder iterations.

- The parameter class, which defines the parameters for configuration of the module functionality (e.g., chosen algorithm).

- The share class, which defines functionality that can be shared among multiple modules this class is optional.

The interface and parameter classes have to be derived from their base classes, which are provided by the CSE infrastructure. The base classes (Base\_Interface and Base\_Parameter) are parent of all interfaces and parameters, and therefore of all modules of the simulation chain. These classes provide higher level data structures, such as lists containing all the parameters or data ports of a functional module. Figure 3.6 illustrates the functional module concept (relation between classes and how they are organized) – it represents the general implementation concepts like derivation structure of functional modules. All the classes defined with the subtitle "(infrastructure)" are provided by the CSE system and offer to all the system basic facilities, services and facilities to the organization of the whole system itself, i.e., list of all input/output ports and list of all parameters of each module. All the classes with the subtitle "(user)" are the ones that the user can create (or just use if the modules are already on the original CSE, i.e., mapper, demapper, encoder, decoder, channel\_awgn).

Figure 3.6: Organization of the module classes

To a better comprehension on how the classes work together, an example will follow. A channel encoder gets bits to encode and has as output the corresponding code word. These two data interfaces are defined on the interface class of the encoder – as can be seen on figure 3.7.

```

Encoder_Interface()

{

input_bits.Register("input_bits", input_data_list_);

output_bits.Register("output_bits", output_data_list_);

}

virtual ~Encoder_Interface() {}

Data_In<unsigned int> input_bits;

Data_Out<unsigned int> output_bits;

```

Figure 3.7: Excerpt of the Encoder\_Interface file – creation and definition of the interfaces

The communication between a module and its environment is called "port" – the data type for a port is one of the two template classes available within the CSE library:

Data\_In or Data\_Out. Data\_In is the input port class of the modules, which will enable the possibility to, when instantiating it, define how are the input types and it will also be responsible to create and instantiate the buffer to connect with the input port. The data are stored in a Buffer class instance.

The interface classes can be shared easily for a group of similar modules like all encoders, because a wide range of encoders have the same data I/O. The name of the interface class is the class name of the module with the "\_interface" suffix, as "encoder interface" shown in figure 3.7.

The parameter class defines all parameters that can be changed during run-time to adapt the module functionality e.g., defining the number of symbols or defining which is the modulation to be used. A parameter is defined to be of type available in the CSE library: Param. The parameter class is usually very module specific, because the parameters have a low similarity for different modules. The name of the parameter class is the class name of the module with the "parameter" suffix. The reason to split the parameter in an extra is that all aspects like definition, default values, and automatic configuration over XML of the parameters are concentrated in a single class in one file.

The Share class contains functionality that can be shared among multiple modules. E.g., LDPC decoders can share the check node functionality or mapper and demapper use the same constellation points for a given modulation. By putting such functions into the share class, a high reuse can be achieved. In general, the parameters of the encoder, as an example, are shown in figure 3.8 – there will be always a value classified as "default", preventing the case when the user does not define what the parameter values to use are.

```

/******

* Parameters *

**********

enum LDPC_CODE {

UMIC P372 N14880 R050,

UMIC P372 N14880 R075,

UMIC P372 N14880 R080

Param<LDPC_CODE> ldpc_code;

/*******

* Default values *

********

void Set_Default_Values()

ldpc code.Init(UMIC P372 N14880 R050, "ldpc code", param list );

ldpc_code.Link_Value_String(UMIC_P372_N14880_R050, "UMIC_P372_N14880_R050");

ldpc_code.Link_Value_String(UMIC_P372_N14880_R075, "UMIC_P372_N14880_R075");

ldpc_code.Link_Value_String(UMIC_P372_N14880_R080, "UMIC_P372_N14880_R080");

```

Figure 3.8: Excerpt of the Encoder\_Parameter file – creation and definition of the default parameters values

Configuration of the functional module is a challenging task. For a standard-compliant simulation environment many modules are connected via their data interface. In order to perform the correct operation, it is mandatory to configure every single

module. Usually a standard provides a header word, defining the current operation of the circuit. This header word has to be translated into other parameters, such as modulation scheme, coding scheme, polynomials, etc.

#### 3.2 Development of New Modules

The CSE goal is to allow the user to create its own simulation environment with a rich documentation. It encourages the users to create new simulation chains and also new functional modules as well as test them inside the whole system — analyzing the results and the performance of the new changes or applications. New simulation chains can be made using the existing modules already provided by the CSE (reorganizing or/and changing parameters), creating a completely new simulation with brand new modules or using new modules with the original CSE modules.