# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

#### FELIPE RIBEIRO SCHNEIDER

# **Building Transistor-Level Networks Following the Lower Bound on the Number of Stacked Switches**

Dissertação apresentada como requisito parcial para a obtenção do grau de Mestre em Ciência da Computação

Prof. Dr. André Inácio Reis Orientador

Prof. Dr. Renato Perez Ribas Co-orientador

Porto Alegre, Março de 2007.

# CIP - CATALOGAÇÃO NA PUBLICAÇÃO

Schneider, Felipe Ribeiro

On Building Transistor-Level Networks Following the Lower Bound on the Number of Stacked Switches / Felipe Ribeiro Schneider — Porto Alegre: Programa de Pós-Graduação em Computação, 2007.

110 f.:il.

Dissertação (mestrado) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação. Porto Alegre, BR – RS, 2006. Orientador: André Inácio Reis; Coorientador: Renato Perez Ribas.

1.Logic Style. 2.Logic Synthesis. 3.Cell Libraries. I. Reis, André Inácio. II. Ribas, Renato Perez. III. On Building Transistor-Level Networks Following the Lower Bound on the Number of Stacked Switches.

## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. José Carlos Ferraz Hennemann Vice-reitor: Prof. Pedro Cezar Dutra Fonseca

Pró-Reitora Adjunta de Pós-Graduação: Profa. Valquiria Linck Bassani

Diretor do Instituto de Informática: Prof. Flávio Rech Wagner

Coordenador do PPGC: Prof. Carlos Alberto Heuser

Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

### **AGRADECIMENTOS**

Este trabalho é dedicado e em agradecimento aos meus pais, Genésio e Miraci Schneider, cuja motivação, suporte, carinho e doação em tempo integral permitiu-me concluir meus estudos com dedicação exclusiva, sem que eu tivesse que me preocupar por um único momento com a maioria das praticalidades da vida adulta enquanto estudante. Eu sempre soube que tive uma vida de privilégios proporcionada pela minha família e isso sempre me motivou a buscar nada menos que o melhor que eu tenho a oferecer como filho, amigo, estudante ou profissional.

Também dedico este trabalho aos meus mentores e amigos, Prof. André Reis e Prof. Renato Ribas, cuja dedicação se estende por vários anos, dentre e fora de classe, desde o momento que me interessei por pesquisa em microeletrônica até o princípio da minha carreira como Engenheiro.

Finalmente, gostaria de agradecer a todos os professores, colegas e amigos da UFRGS que de uma forma ou de outra contribuíram com humildade e genialidade ao meu crescimento pessoal e profissional, refletido aqui neste trabalho.

# **TABLE OF CONTENTS**

| 6               |

|-----------------|

| 7               |

| 9               |

| . 10            |

| . 11            |

| . 12            |

| . 12            |

| . 14            |

| . 14            |

| . 15            |

| . 15            |

| . 16<br>. 18    |

| . 18            |

| . 19            |

| 20              |

| . 20            |

| . 21            |

| . 23            |

| . 24            |

| . 25            |

| 27              |

| . 27            |

| . 29            |

| . 29            |

| . 30            |

| . 32            |

| . 34<br>. 34    |

| . 34<br>. 35    |

| . 36            |

| • • • • • • • • |

| 3.5.3        | Lower bound and general non-SP logic styles                                                 | 37  |

|--------------|---------------------------------------------------------------------------------------------|-----|

| 3.5.4        | Applicability and compatibility with decomposition methods                                  | 38  |

| 3.5.5        | Factorization and stacked transistors                                                       |     |

| 3.5.6        | Unawareness of lower bound in the number of stacked transistors                             | 39  |

| 3.6          | Cell Enumeration                                                                            | 40  |

| 3.6.1        | Orthogonality of Enumerations                                                               |     |

| 3.6.2        | Updating number of functions with limited stacked transistors                               |     |

| 3.6.3        | Binate Function Modeling                                                                    |     |

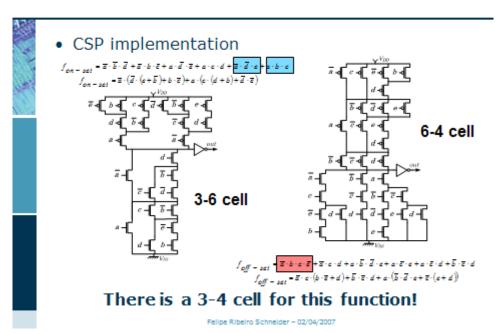

| 4 N          | CSP LOGIC STYLE                                                                             | 44  |

|              | Introduction                                                                                |     |

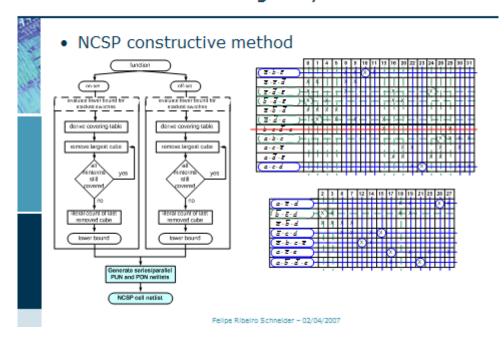

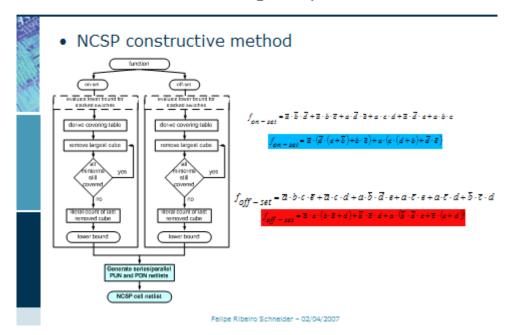

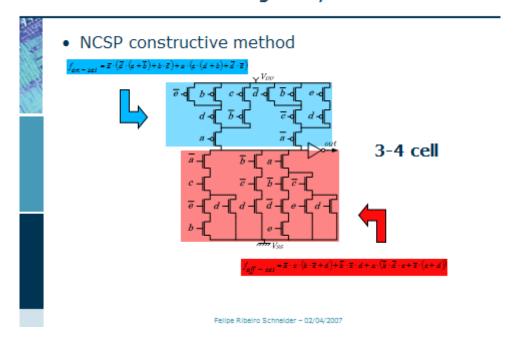

|              | Constructive method                                                                         |     |

| 4.3          | Comparison with a CSP topology                                                              | 45  |

| 4.4          | Comparing with a PTL topology                                                               | 45  |

| 4.5          | Algorithm for generating NCSP topologies                                                    | 46  |

| 4.6          | Other Lower-Bound-Based Style                                                               | 56  |

| 5 RI         | ESULTS                                                                                      | 57  |

| 5.1          | Introduction                                                                                | 57  |

| <b>5.2</b> ] | Electrical Characterization                                                                 | 57  |

| 5.2.1        | 'Black-Box' cell comparison                                                                 | 57  |

| 5.2.1.1      |                                                                                             |     |

| 5.2.1.2      |                                                                                             |     |

| 5.2.2        | Unate Cell Comparison                                                                       |     |

| 5.2.3        | Mapped Circuits Comparison                                                                  |     |

| 5.3          | Logical Effort                                                                              | 65  |

| 6 C          | ONCLUSIONS                                                                                  | 68  |

| REFE         | RENCES                                                                                      | 70  |

| ΔΡΡΕ         | ENDIX A: PRESENTATION SLIDES                                                                | 77  |

|              |                                                                                             |     |

|              | ENDIX B: CONSTRUINDO REDES DE TRANSISTORES DE<br>RDO COM O NÚMERO MÍNIMO DE CHAVES EM SÉRIE | 103 |

# LIST OF ABBREVIATIONS AND ACRONYMS

ASIC Application-specific Integrated Circuit

BBL Branch-based Logic

BDD Binary Decision Diagram

CAD Computer-aided Design

CMOS Complementary MOS (Standard CMOS)

CPL Complementary PTL

CSP Complementary SP

DSM Deep Submicron

FPGA Field-programmable Gate-array

HDL Hardware Design Language

IC Integrated Circuit

ISOP Irredundant SOP

LB Lower bound (for the number of stacked switches)

MOS Metal-oxide-semiconductor

NCSP Non-complementary SP

NRE Non-recurring Engineering

PDN Pull-down Network

PLB Programmable logic block

PTL Pass-transistor Logic

PUN Pull-up Network

RTL Register transfer-level

SoC Silicon-on-Chip

SOI Silicon on Insulator

SOP Sum-of-Products

SP Series/Parallel

VLSI Very Large Scale of Integration

# **LIST OF FIGURES**

| Figure 1.1: | Moore's Law graph showing the exponential increase in the number of transistors along the last three decades for the microprocessors family from | n  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

|             | Intel                                                                                                                                            | 13 |

| Figure 1.2: | Abstraction levels on a system design perspective.                                                                                               |    |

| Figure 1.3: | Design flow based on a standard-cell library                                                                                                     | 17 |

|             | Static CMOS gate.                                                                                                                                |    |

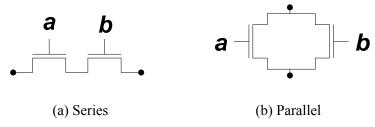

| Figure 2.2: | NMOS logic rules – series devices produces an AND, and parallel devices                                                                          |    |

|             | produces an OR                                                                                                                                   |    |

|             | Different implementations of a 2-input XOR gate                                                                                                  |    |

| Figure 2.4: | Design flow of BDD-based PTL synthesis.                                                                                                          | 24 |

| Figure 2.5: | Branch-based circuit example for the function $out = a \cdot b \cdot c + b \cdot d + e$ .                                                        | 25 |

|             | Figure 3. Flex-cell generation. Starting with (a) the original cluster of                                                                        |    |

| _           | standard cells, the mapping process (b) creates a flex cell that replaces the                                                                    |    |

|             | cluster                                                                                                                                          |    |

| Figure 3.1: | BDD and PTL implementation for function <i>c3</i> .                                                                                              | 28 |

| Figure 3.2: | Series/parallel CMOS implementations of <i>c3</i>                                                                                                | 29 |

| Figure 3.3: | PTL and CSP CMOS topologies.                                                                                                                     | 30 |

| Figure 3.4: | Two distinct PTL cells.                                                                                                                          | 32 |

|             | A small PTL example with drain inputs.                                                                                                           |    |

| Figure 3.6: | Bridge based 3-3 cell for function <i>f</i> from Example 2.                                                                                      | 38 |

| Figure 3.7: | Relationship between enumerations.                                                                                                               | 41 |

| Figure 3.8: | Transistor implementation for a 3-input XOR.                                                                                                     | 42 |

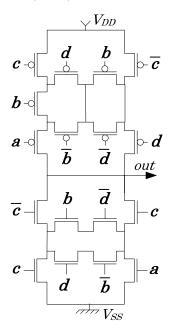

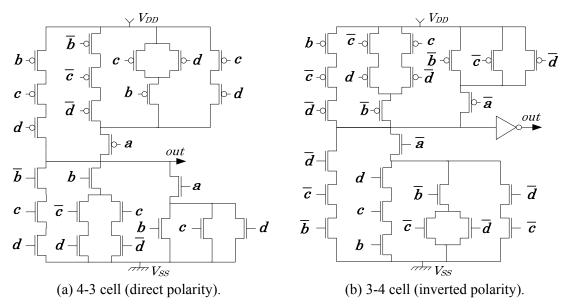

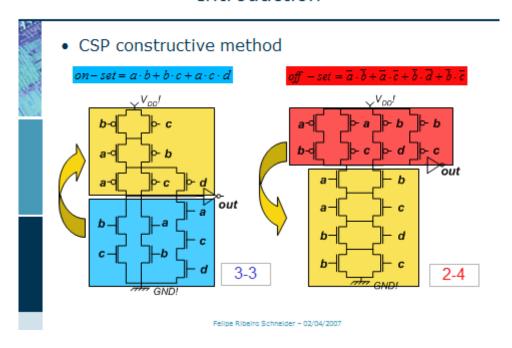

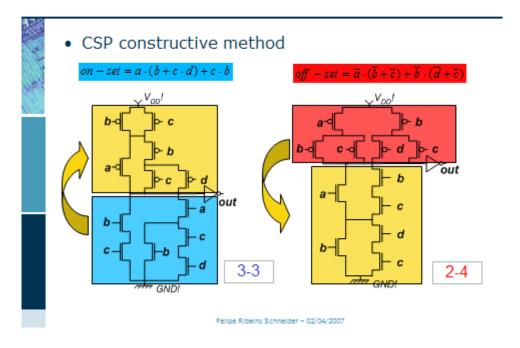

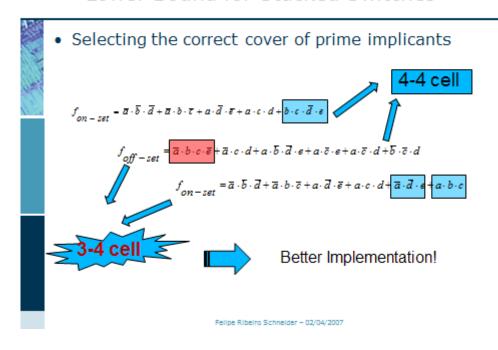

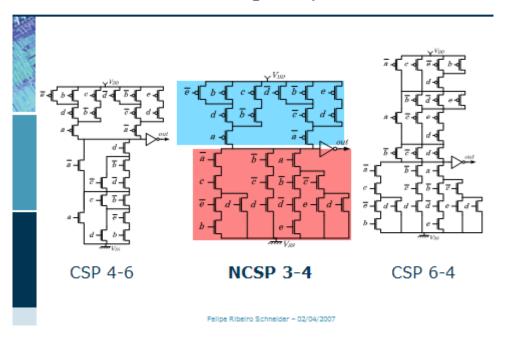

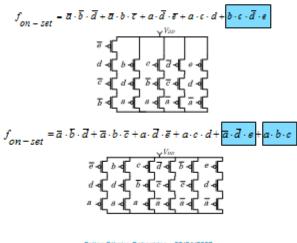

| Figure 4.1: | NCSP cells respecting the lower bounds for function f from Example 2                                                                             | 45 |

| Figure 4.2: | CSP cells not respecting the lower bounds for function f from Example 2.                                                                         | 45 |

| Figure 4.3: | 4-4 PTL cell not respecting the lower bounds for function f from example                                                                         | 2. |

|             |                                                                                                                                                  | 46 |

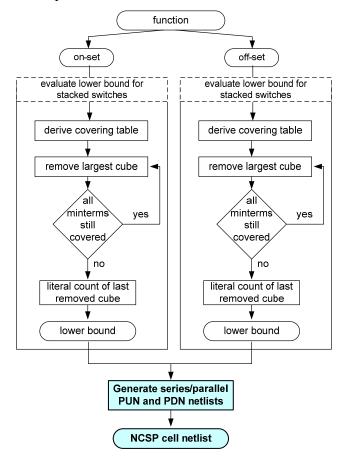

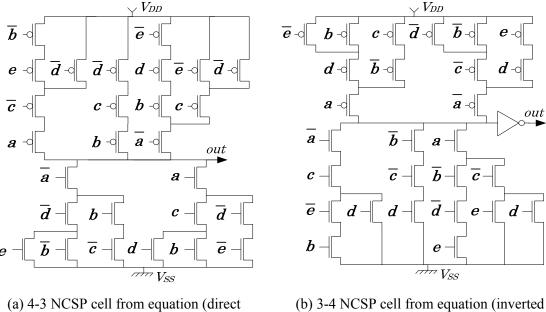

|             | NCSP logic style topology generation algorithm.                                                                                                  |    |

|             | Truth-table for the function $(0197)_{16}$ .                                                                                                     |    |

|             | Bridge-based 5-4 cell for function (0197) <sub>16</sub>                                                                                          |    |

| -           | BDD-based 4-4 PTL for function (0197) <sub>16</sub>                                                                                              |    |

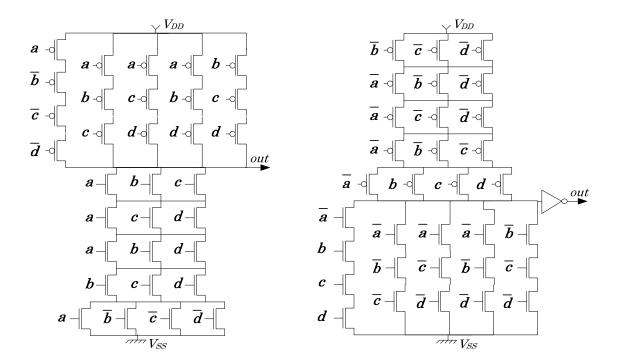

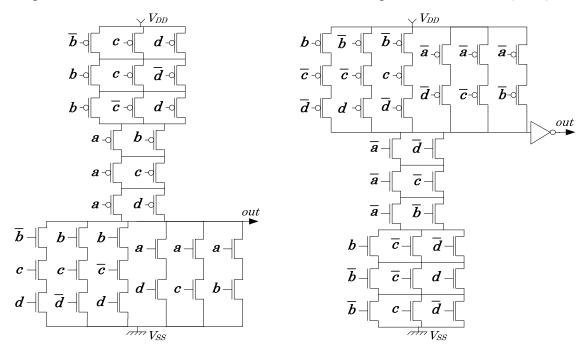

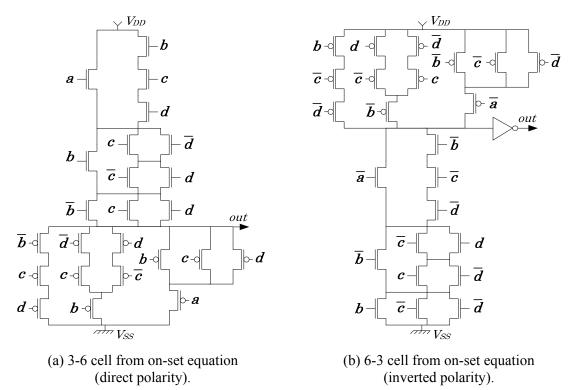

|             | CSP CMOS cells obtained from the on-set equations of function $(0197)_{16}$ .                                                                    |    |

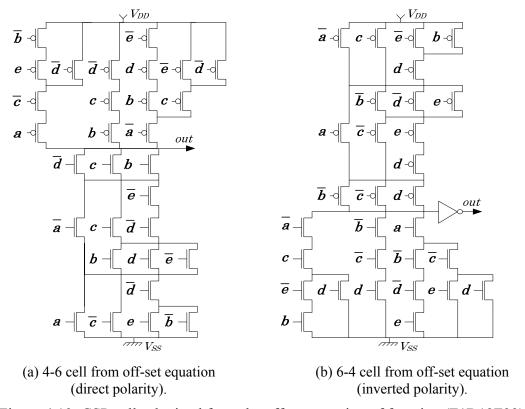

|             | CSP CMOS cells obtained from the off-set equations of function $(0197)_{16}$ .                                                                   |    |

| Figure 4.10 | D: CSP CMOS cells (factorized) for function (0197) <sub>16</sub> – on-set equation                                                               | 50 |

| Figure 4.1  | 1: CSP CMOS cells (factorized) for function (0197) <sub>16</sub> – off-set equation                                                              | 51 |

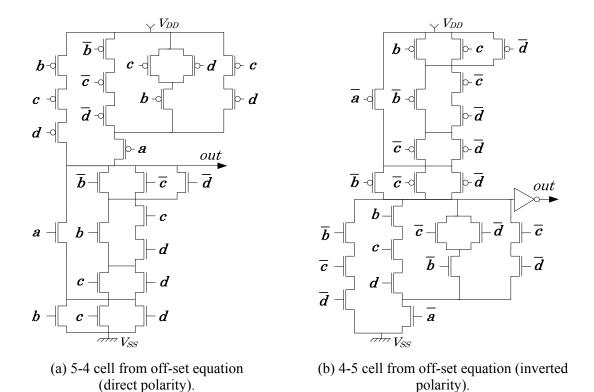

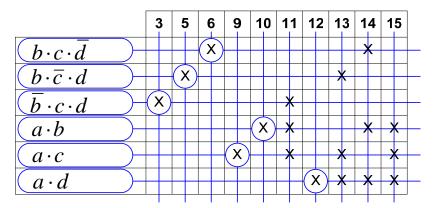

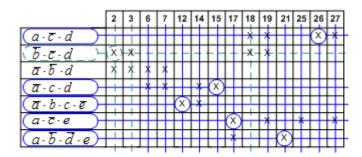

|             | 2: Covering table obtained from the on-set of function $(0197)_{16}$                                                                             |    |

|             | 3: Covering table obtained from the off-set of function $(0197)_{16}$                                                                            |    |

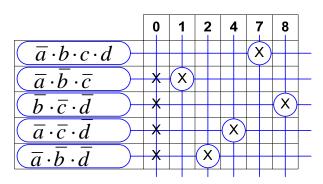

|             | 4: NCSP CMOS cells for function (0197) <sub>16</sub>                                                                                             |    |

| Figure 4.15 | 5: Truth-table for the function (F1D12F33) <sub>16</sub> .                                                                                       | 53 |

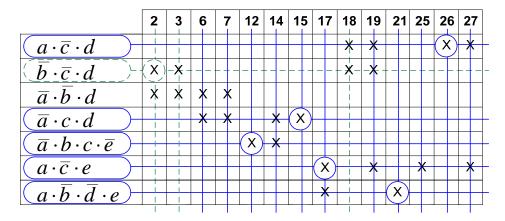

| Figure 4.16: Covering table obtained from the on-set of function (F1D12F33) <sub>16</sub> 54      |

|---------------------------------------------------------------------------------------------------|

| Figure 4.17: Covering table obtained from the off-set of function (F1D12F33) <sub>16</sub> 54     |

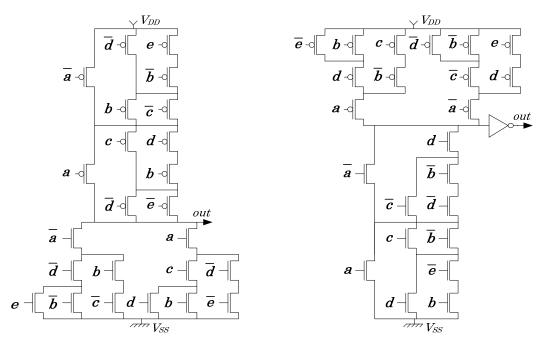

| Figure 4.18: CSP cells obtained from the on-set equation of function (F1D12F33) <sub>16</sub> 55  |

| Figure 4.19: CSP cells obtained from the off-set equation of function (F1D12F33) <sub>16</sub> 55 |

| Figure 4.20: NCSP cells for function (F1D12F33) <sub>16</sub>                                     |

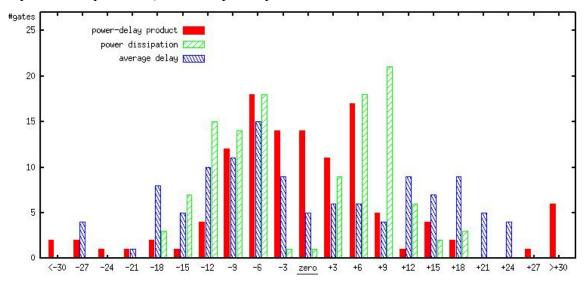

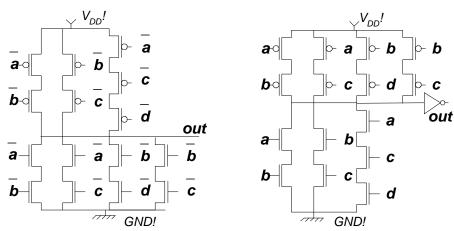

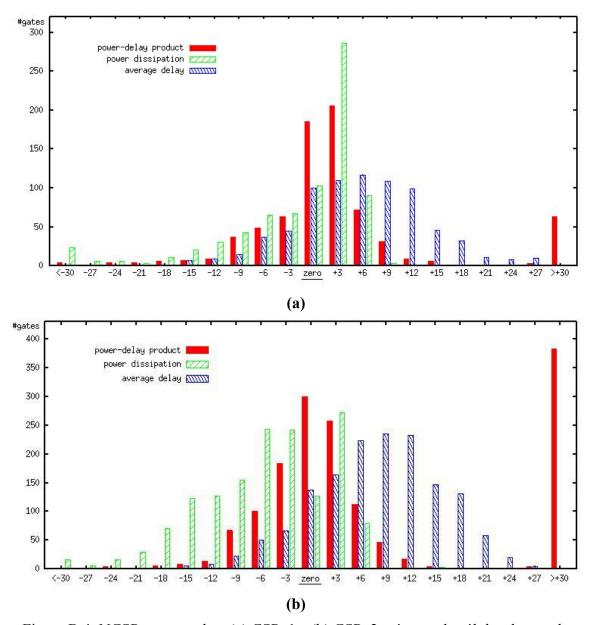

| Figure 5.1: CSP_1 (reference) and CSP_2 propagation delay comparison, number of                   |

| cells according to delay, power and PDP improvement (%)                                           |

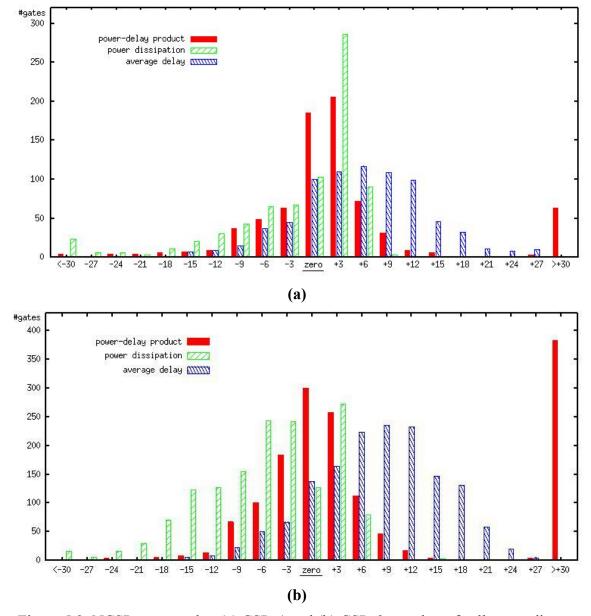

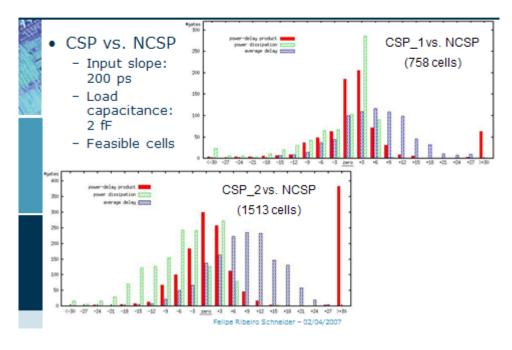

| Figure 5.2: NCSP compared to (a) CSP_1 and (b) CSP_2: number of cells according to                |

| delay, power and PDP improvement (%)                                                              |

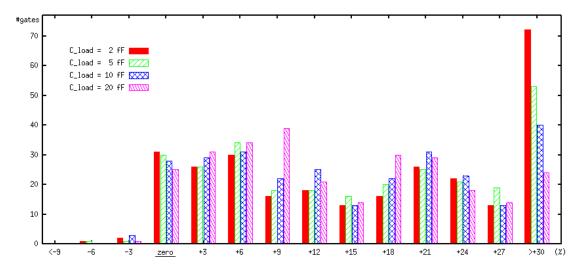

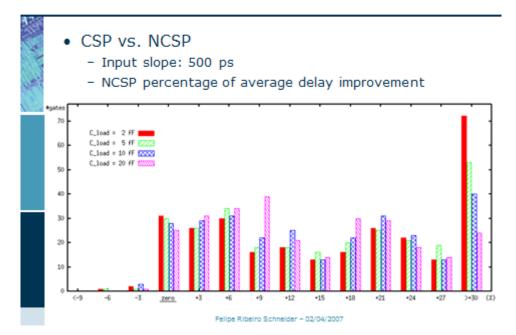

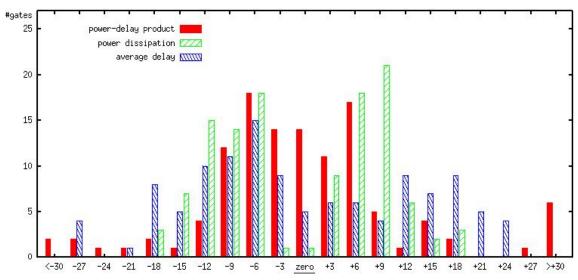

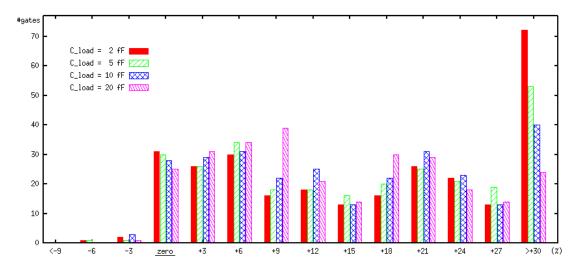

| Figure 5.3: NCSP average delay improvement (%), X-axis, versus number of 6-input                  |

| cells, Y-axis, for different output loads and input slope of 0.5ns. X-axis right                  |

| extremity means $\geq +30\%$ .                                                                    |

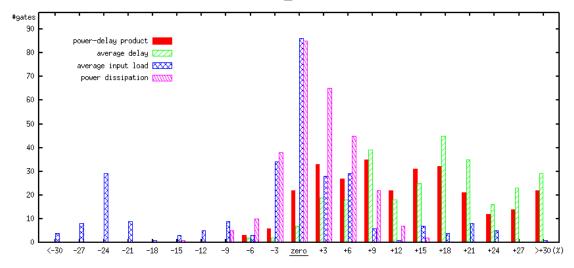

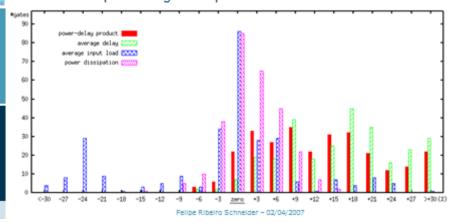

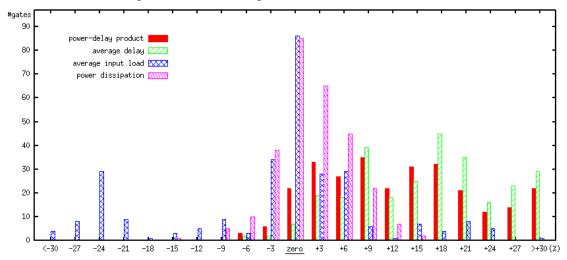

| Figure 5.4: NCSP improvement (%), X-axis, versus number of 6-inputs cells, Y-axis:                |

| power-delay product, average delay, power dissipation and average input                           |

| load. X-axis extremities mean $\geq \pm 30\%$                                                     |

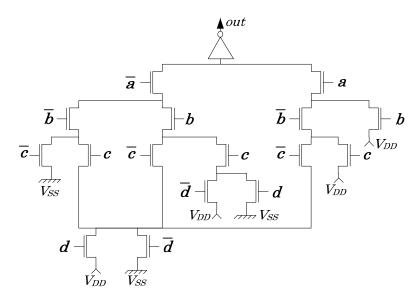

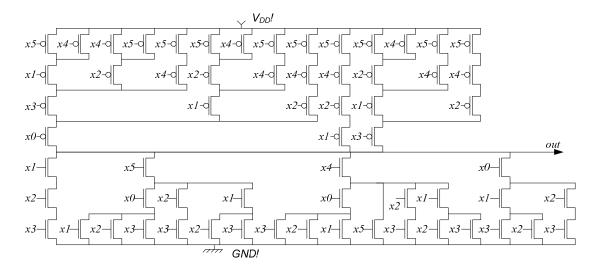

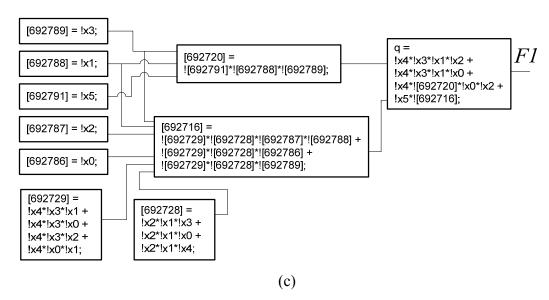

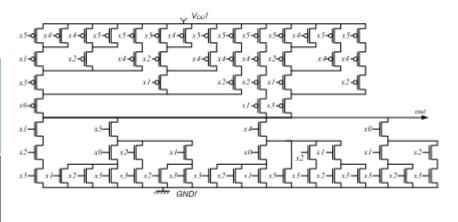

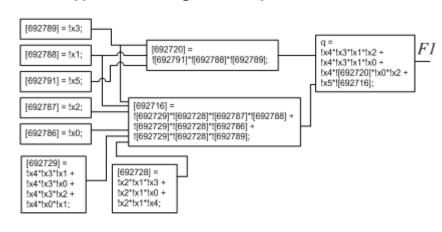

| Figure 5.4: NCSP gate implementation of function 'F1'.                                            |

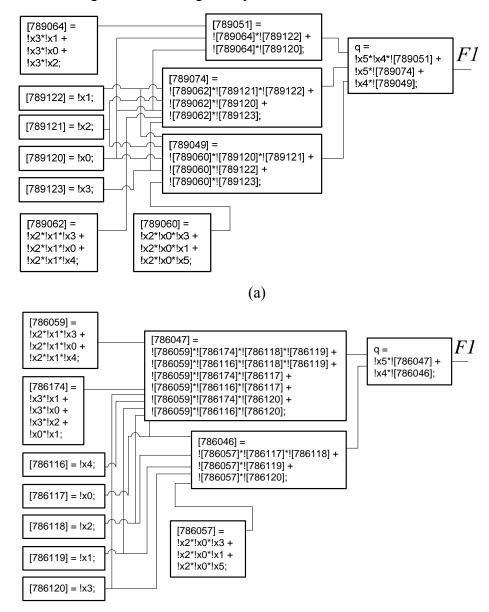

| Figure 5.5: CSP multi-stage implementation of function 'F1' targeting libraries (a) 33-           |

| 4.genlib, (b) 44-3.genlib and (c) 44-6.genlib                                                     |

# **LIST OF TABLES**

| Table 3.1: Literals in cubes associated to paths                                 | 31       |

|----------------------------------------------------------------------------------|----------|

| Table 3.2: Pull-up and pull-down paths for the PTL-based network shown in Fig.   |          |

|                                                                                  | 32       |

| Table 3.3: Pull-up and pull-down paths for the bridge-based network shown in Fi  | ig. 3.6. |

|                                                                                  | 37       |

| Table 3.4: Unawareness of the lower bound (#TR – number of transistors)          | 40       |

| Table 3.5: Number of functions with limited stacked transistors                  | 40       |

| Table 3.6: Number of functions, P- and NPN-classes until 4 inputs                | 40       |

| Table 3.7: Number of extra negative-unate P-classes with limited stacked transis |          |

| considering Theorems 2 and 5.                                                    |          |

| Table 3.8: Number of 4-input binate NPN-classes that would not be implemented    |          |

| CSP logic.                                                                       |          |

| Table 5.1: Number of negative unate functions.                                   |          |

| Table 5.2: Size of CSP multi-gate mapped circuits: #TR – number of transistors;  |          |

| number of cells.                                                                 | 63       |

| Table 5.3: Number of transistors in series for single/gate implementation of CSP | and      |

| NCSP approaches.                                                                 | 63       |

| Table 5.4: NCSP single-gate improvement (%) compared to CSP multi-gate map       |          |

| circuits.                                                                        | 63       |

| Table 5.5: Comparison of six different methods for transistor-level network gene |          |

| Table 5.5. Comparison of six different methods for transistor-rever network gene | 67       |

|                                                                                  | 07       |

# **Building Transistor-Level Networks Following** the Lower Bound on the Number of Stacked Switches

# **ABSTRACT**

Both the propagation delay and the output slope in CMOS gates are strongly related to the number of stacked PMOS and NMOS devices in the pull-up and pull-down networks, respectively. The standard CMOS logic style is usually optimized targeting one logic plane, presenting then the complemented topology in the other one. As a consequence, the minimum number of stacked transistors is not necessarily achieved. In this work, a method to find the lower bound of stacked switches (transistors) in CMOS complex gates is presented. A novel CMOS logic style, derived from such method, is then proposed and compared to conventional CMOS style through a commercial cell characterizer. Electrical characterization of sets of 3- to 6-input functions was done in order to evaluate the new method. Significant gains in propagation delay were obtained without penalty in power dissipation or area.

**Keywords:** Logic style, Logic Synthesis, Cell Libraries.

# Construindo Redes de Transistores De Acordo com o Número Mínimo de Chaves em Série

# **RESUMO**

Em portas lógicas CMOS, tanto o atraso de propagação como a curva de saída estão fortemente ligados ao número de dispositivos PMOS e NMOS conectados em série nas redes de carga e descarga, respectivamente. O estilo lógico 'standard CMOS' é, em geral, otimizado para um dos planos, apresentando então o arranjo complementar no plano oposto. Consequentemente, o número mínimo de transistores em série não é necessariamente alcançado. Neste trabalho, apresenta-se um método para encontrar o menor número de chaves (transistores) em série necessários para se implementar portas lógicas complexas CMOS. Um novo estilo lógico CMOS, derivado de tal método, é então proposto e comparado ao estilo CMOS convencional através do uso de uma ferramenta de caracterização comercial. A caracterização elétrica de conjuntos de funções de 3 a 6 entradas foi realizada para avaliar o novo método, apresentando significativos ganhos em velocidade, sem perdas em dissipação de potência ou em área.

Palavras-Chave: Estilo lógico, Logic Synthesis, Bibliotecas de Células.

### 1 INTRODUCTION

# 1.1 Digital Integrated Circuit Design

An Integrated Circuit (IC) is an electronic system consisting of a number of miniaturized passive and active electronic devices (mainly transistors, resistors, capacitors and inductors) built on a monolithic semiconductor substrate. The large majority of the current ICs are implemented in the so called Metal-Oxide-Semiconductor (MOS) technology (WESTE, 1993; RABAEY, 2003), where in most fabrication processes the semiconductor is silicon.

IC design can be divided into two broad categories: analog and digital design. Analog IC design has specializations in power IC design and radio-frequency IC design. Analog design is used in the development of operational amplifiers, linear regulators, phase-locked loops, oscillators and active filters. Analog design is more concerned with the physics of the semiconductor devices such as gain, matching, power dissipation, and resistance. Fidelity of analog signal amplification and filtering is usually critical and as a result, analog ICs use larger area active devices than digital designs and are usually less dense in circuitry. In the other hand, digital IC design is used to produce components such as microprocessors, FPGAs (Field-Programmable Gate-Arrays), memories (RAM, ROM, and flash) and digital ASICs (Application-Specific Integrated Circuits). Digital design focuses on logical correctness, maximizing circuit density, and placing circuits so that clock and timing signals are routed efficiently. This work focuses on the digital VLSI (Very Large Scale of Integration) IC design flow (MEAD, 1980; WESTE, 1993; UYEMURA, 1999; CHEN, 2000; RABAEY, 2003).

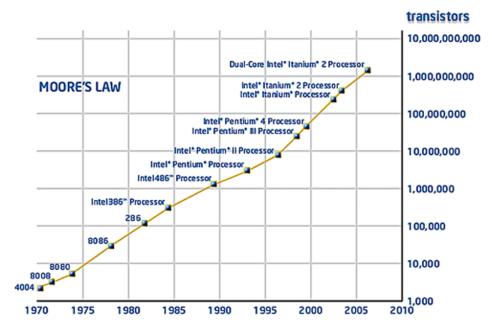

Since the advent of the technology for constructing ICs, integration density and performance of these electronic systems have gone through an astounding revolution driven by the ability of integrating in a single system more and more transistors, the devices responsible by most of the complexity of digital ICs. Indeed, the increase in the number of transistors that can be integrated in a single die has grown exponentially in the last three decades, as predicted by the so called *Moore's Law* (INTEL, 2007; MOORE, 1965). Fig. 1.1 illustrates how this increase prediction has been proved correct so far. Although it has been frequently stated that such increase might cease in a few years due to physical limitations of IC manufacturing technologies, new design methodologies and fabrication process breakthroughs have proven that such cease can be postponed (MOORE, 2003).

Figure 1.1: Moore's Law graph showing the exponential increase in the number of transistors along the last three decades for the microprocessors family from Intel (INTEL, 2007).

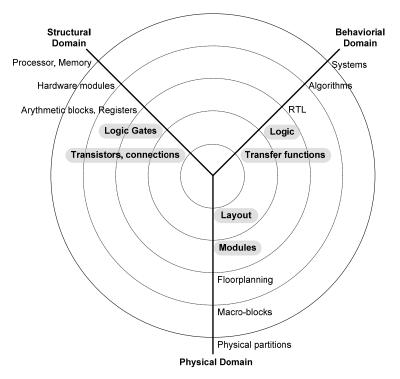

Designing ICs as complex as the ones available nowadays requires that engineers work with different levels of abstraction on a system design perspective. Fig. 2.1 shows a diagram illustrating these different levels of abstraction (GAJSKI, 1988). The highlighted abstraction levels, with special attention to *Logic Gates* in the *Structural Domain* and *Logic* in the *Behavioral Domain*, are the ones that concern the most to this work.

Figure 1.2: Abstraction levels on a system design perspective.

Among the technologies accessible today, two system design approaches play a major role in the scene of semiconductor-based integrated circuits: the FPGA-based design flow and the ASIC-based design flow. The FPGA design flow consists in configuring a set of programmable logic blocks (PLBs) built into a FPGA chip in order to achieve a desired application behavior. The ASIC design flow consists in assembling a set of basic electronic devices (i.e. transistors, resistors, capacitors, etc.) into structures called cells, which are the basic blocks in the construction of ASICs.

The choice between FPGAs and ASICs usually relies, among several factors, in the intended number of designs it is intended to be delivered to the market. The FPGA market has continuously growing as such reconfigurable chips becomes cheaper and holds more and more complex designs. However, when issues like power consumption, speed and area arise, nothing can beat the ASIC. The general rule states that for every FPGA-based design there is an ASIC that is more efficient considering area, energy and operation speed. On the other hand, ASICs are considered low-cost only for high volume designs (ZUCHOWSKI, 2002), due to the cost of dedicated masks.

This work focuses on the proposal of a new methodology for implementing, logically and structurally, the building blocks for ASICs. Therefore, next Section will focus on the most common ASIC design flows available at the present time.

# 1.2 ASIC Design Flow

As integrated circuits become more inexpensive and compact, many new types of products, such as digital cameras, digital camcorders and digital television (JURGEN 1997), are being introduced, based on digital systems. Consequently, logic design must be done under many different motivations. Since each case is different, one may have different design problems. Choosing an appropriate logic style, for example, is a very important issue when one wants to achieve certain performance requirements for a given IC design.

In this Section, let us consider two important cases of designing ICs, which leads to two contrasting logic approaches: quick design and high-performance design. Quick design of ICs is called *semi-custom design*. Recently, it has been also called *ASIC design* (CHINNERY, 2002), although the ASIC abbreviation is still used with a broader meaning. On the other hand, deliberate design for high-performance is called *full-custom design*, as this kind of design is fully customized to the high performance design space (area, speed, power and energy consumption).

In the next Subsections full-custom as well as different semi-custom approaches will be discussed.

#### 1.2.1 Full-custom

In Full-custom design one does logic and physical synthesis in order to attain the highest performance or smallest size, making use of the most advanced technologies (CHEN, 2003). It is definitely the most technology dependent design approach existent: every transistor present in every cell inside every macro-block is tweaked in order to explore all the performance advantages that a given technology can deliver.

The benefits of full-custom design in general include reduced area (and therefore recurring component cost), performance improvements and also the ability to integrate (include) analog components and other pre-designed (and thus fully verified) components such as microprocessor cores that form a System-on-Chip (SoC).

The disadvantages of full-custom can include increased manufacturing and design time, increased non-recurring engineering (NRE) costs, more complexity in the Computer-Aided Design (CAD) system and a much higher skill requirement on the part of the design team.

However for digital only designs, cell-based semi-custom design together with modern CAD systems can offer considerable performance/cost benefits with much lower risk. Automated layout tools are quick and easy to use and also can offer the possibility to manually handcraft and optimize any performance limiting aspect of the design.

### 1.2.2 Gate Array

The Gate Array design is a manufacturing method in which the diffused layers, i.e. transistors and other active devices, are predefined. Wafers containing such devices are held in stock prior to metallization, in other words, unconnected (CHEN, 2000). The physical design process then defines the interconnections of the final device. For most ASIC manufacturers, this consists of two to as many as five metal layers, each one running perpendicular to the one below it. NRE costs are much lower as photolithographic masks are required only for the metal layers, and production cycles are much shorter as metallization is a comparatively quick process. It is also important to the designer that reduced propagation delays can be achieved in ASICs when compared to the available FPGAs solutions available in the marketplace.

Metal Programmable Gate Array Design is rarely implemented by circuit designers today. It has been replaced almost entirely by field programmable devices, such as FPGAs, which can be reprogrammed several times by the user and thus offer minimal tooling charges, marginally increased piece part cost and comparable performance. Nowadays, Gate Arrays are evolving into Structured ASICs (see Subsection 1.2.3) that typically consist of a large IP (Intellectual Property) core like a processor, DSP unit, peripheral components, standard interfaces, integrated SRAM memory, and a block of reconfigurable logic. This shift is largely because ASIC devices are capable of integrating such large blocks of system functionality and SoC designs requires far more than just logic blocks.

#### 1.2.3 Structured ASIC

The basic premise of a Structured ASIC design (also referred to as Platform ASIC design) is that both manufacturing cycle time and design cycle time are reduced compared to cell-based ASICs due to pre-defined metal layers (thus reducing manufacturing time) and pre-characterization of what is on the silicon (thus reducing design cycle time). It is a relatively new design approach (PILLEGI, 2003; ZAHIRI, 2003).

In a Structured ASIC design, the logic mask-layers of a device are predefined by the ASIC vendor. Design differentiation and customization is achieved by creating custom metal layers that create custom connections between predefined lower-layer logic elements. Structured ASIC technology is seen as bridging the gap between field-

programmable gate arrays and Standard-cell ASIC designs. Because only a small number of chip layers must be custom-produced, Structured ASIC designs have much smaller NRE than standard-cell or full-custom chips, which require that a full mask set be produced for every design. This is effectively the same definition as a Gate Array.

What makes a Structured ASIC different from a gate array is that in a gate array the predefined metal layers serve to make manufacturing turn-around time faster whereas in a Structured ASIC the predefined metallization is primarily to reduce cost of the mask sets and is also used to make the design cycle time significantly shorter as well. For example, in a cell-based or gate-array project the designers often must design power, clock, and test structures themselves: these are predefined in most Structured ASICs and therefore can save time and costs for the designer, when compared to gate-array. Another important aspect about Structured/Platform ASIC is that it allows IP that is common to certain applications or industry segments to be *built-in*, like one does in FPGAs, rather than *designed-in*, as it is done in cell-based design.

#### 1.2.4 Standard-Cell

The idea behind cell-based design is to reduce the implementation effort by reusing a library of cells. The advantage of this approach is that the cells only need to be designed and verified once for a given technology, and they can be reused many times, thus amortizing the design cost. The disadvantage is that the constrained nature of the library (especially due to the limited number of cells) reduces the possibility of fine-tuning the design (RABAEY, 2003).

The Standard-cell approach standardizes the design entry-level at the logic gate (functional blocks). A library containing a wide selection of logic gates over a range of number of inputs and drive strengths is provided. Besides the basic logic functions such as inverter, AND/NAND, OR/NOR, XOR/XNOR and Flip-flops, a typical library also contains more complex functions such as AOI/OAI (AND/OR-OR/AND-INVERT), MUX, Full-adder, Comparator, Counter, Decoder and Encoder.

The layout of each cell in a specific library has a fixed height, while its width may vary, so the cell can be placed side-by-side, in such a way that their power rails and well regions properly connect to neighbor cells. Standard-cell design uses these functional blocks to achieve high gate density and good electrical performance. Standard-cell design fits between Gate Array and Full-Custom design in terms of both its NRE and recurring component cost.

The quality of a synthesized design based on standard-cells depends on three components: the synthesis tool, the place and route tools and the target cell library (SCOTT, 1994). Choosing the right cell library can have a significant impact on the characteristics of a designed circuit (VUJKOVIC, 2002; SECHEN, 2003).

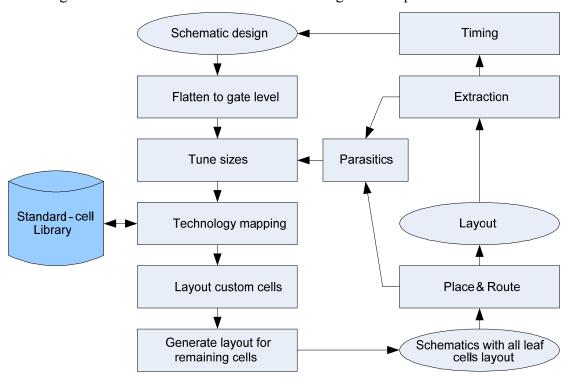

The design flow, implemented with a level of skill common in the industry, almost always produce a final device that correctly implements the original design, unless flaws are later introduced by the physical fabrication process. It is as follows:

- 1. A team of design engineers starts with a non-formal understanding of the required functions for a new ASIC, usually derived from requirement analysis.

- 2. The design team constructs a description of an ASIC to achieve these goals using a HDL (Hardware Design Language). This process is analogous to

- writing a computer program in a high-level language. This is usually called the RTL (Register transfer level) design.

- 3. A logic synthesis tool, in a process called technology mapping (SENTOVICH, 1992; REIS, 1995; JIANG, 2001; CORREIA, 2004), transforms the RTL design into a large collection of lower-level constructs called standard cells. These constructs are taken from a standard-cell library consisting of pre-characterized collections of gates. The standard cells are typically specific to the planned manufacturer of the ASIC. The resulting collection of standard cells, plus the needed electrical connections between them, is called a gate-level netlist. Standard-cells can be handcrafted or automatically generated.

- 4. The gate-level netlist is next processed by a placement tool which places the standard-cells onto a region representing the final ASIC. It attempts to find a placement of the standard-cells, subject to a variety of specified constraints.

- 5. The routing tool takes the physical placement of the standard-cells and uses the netlist to create the electrical connections between them. Since the search space is large, this process will produce a *sufficient* rather than *globally-optimal* solution. The output is a set of masks enabling a semiconductor fabrication to produce the physical ICs.

- 6. Close estimates of final delays, parasitic resistances and capacitances, and power consumptions can then be made. In the case of a digital circuit, this will then be further mapped into delay information that can be used to tune the design up.

In Fig. 1.3 an overview of the standard-cell design flow is presented.

Figure 1.3: Design flow based on a standard-cell library (CHINNERY, 2002).

#### 1.2.5 Library-free

One of the main restrictions of the standard-cell library-based designs is a limited number of cells and drive strengths available. In *library-free* (also called *library-less*) based design, as the name indicates, the library is said to be *virtual* (as it is not physically implemented before technology mapping) and may contain an unlimited number of cells (GAVRILOV, 1997; REIS, 1997; MORAES, 1999; CORREIA, 2004).

The main difference between standard-cell based technology mapping and library-free technology mapping concerns the libraries (pre-characterized and virtual, respectively) they must cope with. Library-free technology mapping implements the functions directly at the transistor-level, while guaranteeing that the final netlist of complex gates respect some topological constraints, e.g. number of transistors in series (REIS, 1998). The great number of available complex gates will improve the design space and lead to a minimization of the overall number of transistors, minimizing the design at the transistor-level.

#### 1.3 A Novel Logic Style

ASIC design based on standard cells still remains the most applied approach, even if cell generators are used to create the library (LEFEBVRE, 1997; KEUTZER, 1999; CHINNERY, 2002; SECHEN, 2003). Although different CMOS logic styles, like PTL (BUCH, 1997; SCHOLL, 2000; JIANG, 2001; AVCI, 2003) and dynamic Domino gates (THORP, 2003), have been proposed as promising choices, the conventional Complementary Series/Parallel CMOS logic style (BERKELAAR, 1988; GAVRILOV, 1997), called here as CSP, continues to be the most widely adopted in cell libraries building.

Since the worst-case delay propagation is usually related to the longest path of stacked transistors, the construction of CMOS gates with minimum transistor stack length in the pull-up network (PUN) and pull-down network (PDN) is strongly recommended. As it will be demonstrated in this work, the number of stacked transistors has a direct impact in the *logical effort* (SUTHERLAND, 1999; KABBANI, 2005; WESTE, 2006; ROSA 2007) of the cells. However, this requirement cannot be guaranteed with CSP gates. This is explained by the fact that one plane is generated from the optimized logic equation, respecting then the minimum stack transistor number, but the other one is derived by making a complementary series/parallel topology, which will not guarantee minimum length transistor stacks if the gate has too many parallel branches.

A method to define the lower bound of stacked transistors in a logic plane presented in (SCHNEIDER, 2005) has some inconsistencies that were corrected in (SCHNEIDER, 2006a), with more practical results presented in (SCHNEIDER, 2006b) and further analyzed herein. The proposal of this work is both the *lower bound* theory as well as a novel Non-Complementary Series/Parallel CMOS logic style, named NCSP, derived from the *lower bound* method. Propagation delay reduction is expected for NCSP complex gates in comparison to standard CSP ones, with no penalty in power dissipation and area overhead. Electrical characterization using a commercial library characterization tool has been carried out over several logic cells, from 3- to 6- inputs, taking into account the TSMC 0.13um CMOS technology.

# 1.4 Organization of the Dissertation

This dissertation is organized as follows. In Section 2, it is presented a background of the most common static logic styles applied by the industry nowadays. Section 3 formulates the lower bound theory for the length of transistor stacks in logic cells and provides an enumeration of feasible cells using different logic styles considering such formulation. In Section 4, the implementation of a novel logic style so called NSCP is presented. Section 5 presents the electrical characterization of NCSP gates and a comparison with the most used static logic styles nowadays. Furthermore, Section 5 presents the impact in area, presenting some cell layouts. Finally, conclusions and an analysis of the impact of this work based on its results are pointed out on Section 6.

# **2 STATIC LOGIC STYLES**

#### 2.1 Introduction

The transistor is the most basic structure found in digital circuits, where it is mostly used as a switch. These switching devices are used to form the so called logic gates, which are the building blocks of digital integrated circuits. Each logic gate is designed to behave according to a desired logic function, where the output signals of a logic gate is a function of its input signals.

The circuit of a logic gate can be built using different configurations of transistors for a given logic function. These configurations are known as *logic styles* or *logic families*. There are numerous logic styles to implement a logic gate for a given logic function. Different styles are used to perform better for different design metrics like area, speed, energy and power consumption. Depending on the application, the emphasis will be on different metrics. For example, the switching speed of digital circuits is the primary metric in a high-performance processor, while in a battery operated circuit, it is energy consumption. Recently, power dissipation also has become an important concern and considerable emphasis is placed on understanding the mechanisms of power and approaches to dealing with power. One of these mechanisms currently highlighted by the industry and the academia is the leakage current, critical in the newest Ultra DSM (Deep Submicron) technologies (ROY, 2003). In addition to those metrics, robustness to noise and reliability are also very important considerations.

Logic styles are basically classified as being dynamic or static. *Dynamic* styles (THORP, 2003), rely on temporary storage of signal values on the capacitance of high-impedance circuit nodes. The implementation approach of dynamic circuits is simpler and faster but their design and operation are more prone to failure because of the increased sensitivity to noise. The most common dynamic logic styles are Domino and its variants: Dual Domino, Multiple-Output Domino, NORA Domino and Zipper Domino (WESTE, 2006). On the other hand, *Static* styles guarantee that, under fixed input vectors, each gate output is connected to either  $V_{DD}$  or GND via a low resistance path. Also, the outputs of the gate assume at all times the value of the Boolean function implemented by the circuit, meaning the circuit does not need to be pre-charged or pre-discharged. Some of the most common static logic styles are Static CMOS, Pseudo-NMOS, DCVSL and PTL (RABAEY, 2003).

Additionally, logic styles can be also classified as single- or dual-rail circuits. Single-rail circuits have only one output while dual-rail ones have two outputs, which

very frequently are one for the direct polarity signal and one for the inverted polarity signal.

The most common logic styles used in the industry are the Complementary Series-Parallel CMOS (referred as CSP in this work) and the Pass-Transistor Logic (PTL), both static and single-rail. The logic style proposed in this work is also classified as static and single-rail. This allows its use with a design methodology flow very similar to the one applied currently to most integrated circuit designs, while it keeps the same robustness characteristic of CSP logic. In this sense the logic proposed here is superior to PTL, which may present drain inputs depending on how it is designed. Drain inputs are a design problem due to noise margin and also because the input capacitance seen at drain inputs is not constant.

In the next Sections, different logic styles available nowadays will be presented in order to allow a straightforward comparison with the logic style proposed and further explained on Chapter 4.

# 2.2 Complementary Series-Parallel CMOS

The Complementary Series-Parallel CMOS (CSP) is still nowadays the most used and well established logic style applied by the industry. The CSP style is basically an extension of the CMOS inverter to multiple inputs. The primary advantage of the CSP structure is robustness (i.e. low sensitivity to noise), good performance and low power consumption with almost no static power consumption for technologies with transistor channel length down to 130nm (WESTE, 2006).

However, newer Ultra DSM fabrication processes might considerably increase the leakage current responsible for static power consumption and in some point of time it ought to be comparable with dynamic power consumption. These increase has been dealt with more complex technologies, like SOI (Silicon-on-Insulator) and high-K dielectrics (WESTE, 2006), as well as with circuit-level modifications (ROY, 2003).

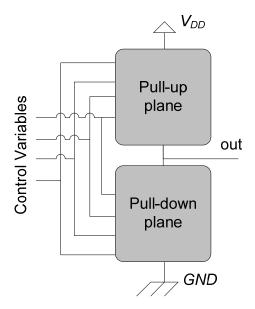

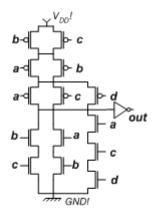

A static CMOS gate is a combination of two networks, called the *pull-up network* (PUN) and the *pull-down network* (PDN) (Fig. 2.1). The Fig. 2.1 shows a generic N-input logic gate where all the inputs are distributed to both the PUN and PDN. The function of the PUN is to provide a connection between the output and  $V_{DD}$  anytime the output of the logic gate is meant to be 1 (based on the inputs). Similarly, the function of the PDN is to connect the output to GND when the output of the logic gate is meant to be 0. The PUN and PDN networks are constructed in a mutually exclusive fashion such that *one and only one* of the networks is conducting in steady state. In this way, once the transients have settled, a path always exists between  $V_{DD}$  and the output F, realizing a high output (representing logic one), or, alternatively, between GND and F for a low output (representing logic zero). This is equivalent to stating that the output node is always a low-impedance node in steady state.

While constructing the PDN and PUN networks, the following observations should be kept in mind:

1. A transistor can be thought of as a switch controlled by its gate signal. An NMOS switch is ON when the controlling signal is high and is OFF when the controlling signal is low. A PMOS transistor acts as an inverse switch that is ON when the controlling signal is low and OFF when the controlling signal is high.

Figure 2.1: Static CMOS gate.

- 2. The PDN is constructed using NMOS devices, while PMOS transistors are used in the PUN. The primary reason for this choice is that NMOS transistors produce "strong zeros" and PMOS devices produce "strong ones" (RABAEY, 2003).

- 3. A set of construction rules can be derived to construct logic functions. NMOS devices connected in series corresponds to an NAND function (Fig. 2.2.a). With all the inputs high, the series combination conducts and the value at one end of the chain is transferred to the other end. Similarly, NMOS transistors connected in parallel represent an NOR function (Fig. 2.2.b). A conducting path exists between the output and input terminal if at least one of the inputs is high. Using similar arguments, construction rules for PMOS networks can be formulated. A series connection of PMOS conducts if both inputs are low, representing a NOR function  $(\overline{a} \cdot \overline{b} = \overline{a + b})$ , while PMOS transistors in parallel implement a NAND  $(\overline{a} + \overline{b} = \overline{a \cdot b})$ .

- 4. Using De Morgan's Theorems  $\overline{a} \cdot \overline{b} = a + b$  and  $\overline{a} + \overline{b} = \overline{a \cdot b}$ , it can be shown that the PUN and PDN networks of a complementary CMOS structure are dual networks. This means that a parallel connection of transistors in the pull-up network corresponds to a series connection of the corresponding devices in the pull-down network, and vice versa. Therefore, to construct a CMOS gate, one of the networks is implemented using combinations of series and parallel devices. The other network is obtained using duality principle by traversing the hierarchy, replacing series sub-nets with parallel sub-nets, and parallel sub-nets with series sub-nets. The complete CMOS gate is constructed by combining the PDN with the PUN.

Figure 2.2: NMOS logic rules – series devices produces an AND, and parallel devices produces an OR

# 2.3 Pass-Transistor Logic

A popular and widely-used alternative to CSP is Pass-Transistor Logic (PTL) (BUCH, 1997; HSIAO, 2000; SCHOLL, 2000; LINDGREN, 2001; ZHOU, 2001; SHELAR, 2001; SHELAR, 2002; AVCI, 2003), which attempts to reduce the number of transistors required to implement logic by allowing the primary inputs to drive gate terminals as well as source/drain terminals. This characteristic contrasts with most logic families, which only allow primary inputs to drive the gate terminals of transistors.

The switches used in PTL circuits use either NMOS pass transistors or parallel pairs of NMOS and PMOS transistors called *transmission gates*. The most known PTL variation which uses transmission gates is called CPL (Complementary Pass-Transistor Logic) (YANO, 1990). Another distinct characteristic of PTL circuits is that it can present non-series/parallel network configurations.

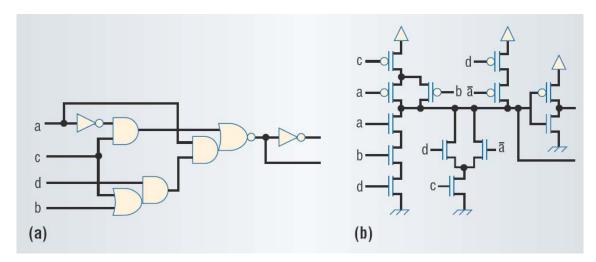

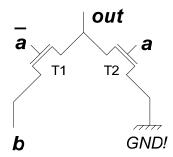

One of the promises of PTL approach is that fewer transistors are required to implement some functions, especially XOR-based gates, which include MUXes. For example, the implementation of an XOR2 gate in Figure 2.3.a requires 6 transistors (including the inverter required to invert *b*), while a complementary CMOS implementation (Fig. 2.3.b) would require 12 transistors. The reduced number of devices has the additional advantage of lower capacitance. Many authors have claimed substantial area, speed and/or power improvements for pass-transistors compared to static CMOS. However, an independent evaluation finds that for most general-purpose logic, static CMOS is superior in speed power and area (ZIMMERMANN, 1997). Mixed approaches have also been proposed, as described in ().

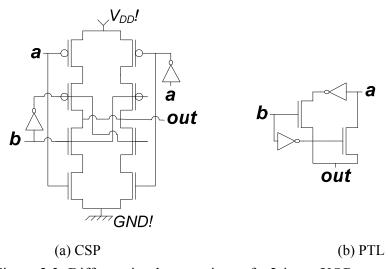

Figure 2.3: Different implementations of a 2-input XOR gate.

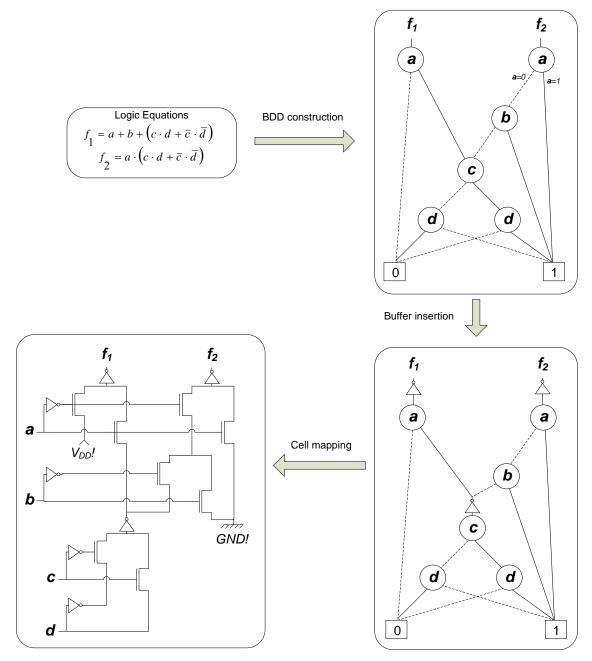

Another difference of PTL circuits it the way its logic is implemented. In logic styles like CSP, Boolean equations area translated into series/parallel arrangements. In PTL, however, the most common way of deriving circuits from logic is through the used of Binary Decision Diagrams (BBDs) (YANO, 1996). Fig. 2.4 presents the basic design flow of BDD-based PTL circuit synthesis.

Figure 2.4: Design flow of BDD-based PTL synthesis (YANO, 1996).

# 2.4 Branch-Based Logic

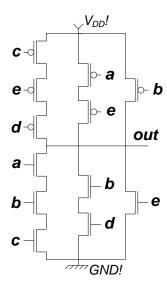

Branch-Based Logic (BBL) is a logic style that has been developed for low-power, low-voltage applications and for high-speed circuits (PIGUET, 1984; PIGUET, 1994; PIGUET, 1995; NÈVE, 2001). In this style, the transistor networks consist only of branches (i.e. a series of up to three transistors between power line and gate output).

The advantages of transistor branches are higher layout regularity (i.e. smaller diffusion capacitances) and simpler characterization (i.e. branch instead of gate modeling).

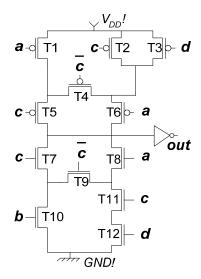

The construction of branch-based circuits is rather simple. It takes a flat (non-factorized) irredundant sum-of-products and translates each product into an and-stack (branch) in the circuit. It's done for each PUN and PDN independently, using the on-set and the off-set logic expression respectively. Fig 2.5 shows an example of a BBL circuit.

Figure 2.5: Branch-based circuit example for the function  $out = a \cdot b \cdot c + b \cdot d + e$ .

The low-power and high-speed capabilities of BBL circuits are due to its low capacitive nodes as there is no parallel connection among branches. This absence of interconnection among branches is also a positive characteristic from the layout point of view (PIGUET, 1984). However, one problem of BBL circuits is the use of too many transistors for some logic functions, as its logic expressions are flat (non-factorized) by nature.

# 2.5 Other Static Logic Styles

Several other logic styles have been proposed in order to explore different aspects of the area-speed-power design space. The choice depends on the design as well as on the tools available for the synthesis of the circuits.

An appealing approach for high-speed circuits is the BiCMOS family (ELRABAA, 1992) which uses bipolar transistors in order to achieve improved output drive capability. One of the biggest problems of this kind of logic is that the use of bipolar transistors is not very well supported for most of the fabrications processes and CAD tools available. Currently, BiCMOS is mostly used for bus drivers, I/O drivers and linear circuits like high-speed operational amplifiers (WESTE, 1993).

A couple of old yet very interesting works regarding to logic cells with minimal number of transistors are depicted in (GREA, 1958) and (NINOMIYA, 1965) which present tables with hand-crafted switch topologies for more complex logic cells.

Finally, one must cite the innovative approach developed by Zenasis Technologies (ZENASIS, 2007) so called Flex-cells (ROY, 2005). This approach was developed in

order to cope with the gap between standard-cell based design and full-custom design, where it is estimated that automated design flows deliver circuits slower by at least a factor of 6 and consume a larger area at least by a factor of 10 (Chapter 10 of CHINNERY, 2002). Flex-cell is not a logic style, indeed, but it is cited here because it is an optimization approach done at transistor-level. In summary, the Flex-cell-based optimization consists in automating the process of creating tactical cells in a design, by grouping clusters of logic gates in a single gate, as shown in Fig. 2.6. With such approach it's expected to have significant improvements in area and speed without having to handcraft such tactical cells.

Figure 2.6: Figure 3. Flex-cell generation. Starting with (a) the original cluster of standard cells, the mapping process (b) creates a flex cell that replaces the cluster (ROY, 2005).

### 3 LOWER BOUND FOR STACKED SWITCHES

#### 3.1 Introduction

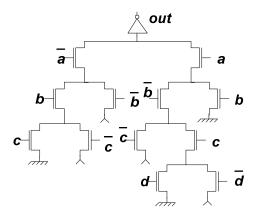

The number of stacked switches (or switches in series) inside a cell is a limiting factor to the maximum speed it may attain in CMOS technologies. Regardless of the transistor topology used to implement a switching function, there is a strong correlation between the length of its longest transistor stack and its worst-case propagation delay. This correlation is verified because the switches along this path are likely to charge or discharge a path that corresponds to the worst-case delay scenario. This loss in delay is directly related with the logical effort (SUTHERLAND, 1999; KABBANI, 2005; WESTE, 2006; ROSA 2007) of the cell, as it will be demonstrated on Chapter 5. The approach in (SHELAR, 2001) made use of this correlation described above in its algorithm for performance-driven PTL synthesis. The method presented there exploits two separate effects. First, it aims to reduce the number of serially connected gates by applying functional decomposition. Second, it reduces the number of stacked transistors (switches) inside the gates by encoding decompositions with a one-hot code and deriving cell level PTL networks partially from a BDD (Binary Decision Diagram) and partially from a one-hot multiplexer. The results reported there show significant performance gains, proving the importance of the number of stacked transistors (switches) as a parameter to the quality of cell networks, especially when performance is the design goal.

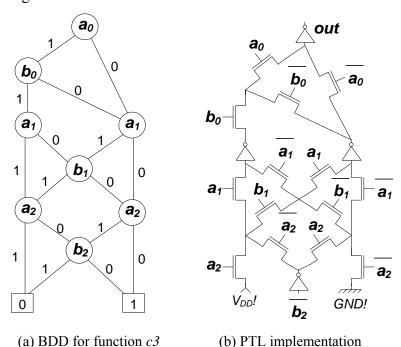

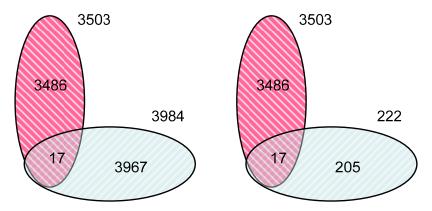

Synthesis techniques for PTL circuits have been closely related to BDD representation of logic functions, for reasons such as elimination of sneak paths and availability of efficient algorithms for the construction of BDDs (SHELAR, 2001). Indeed, the approaches in (BUCH, 1997; HSIAO, 2000; SCHOLL, 2000; LINDGREN, 2001; ZHOU, 2001; SHELAR, 2001; SHELAR, 2002; AVCI, 2003) are based on BDDs. Therefore, when discussing PTL networks in this work, it will be assumed in this work they are derived from BDDs. Despite the gains demonstrated by (SHELAR, 2001), this work will demonstrate that even the introductory example used there, the circuit *c3* (carry out for the first 3 bits of an adder), shown in Fig. 3.1, may be synthesized with a significantly smaller number of stacked transistors than originally presented. Fig. 3.1.a shows the BDD for *c3*. This BDD has a path with six arcs in series, and it would have six transistors in series if mapped as a single PTL gate. For this reason, PTL approaches will insert buffers to limit the number of transistors in series to three or four (SHELAR, 2001; ZHOU, 2001). Fig. 3.1.b shows a PTL gate for *c3*, with (inverting) buffers inserted. This way, the bottom part, below the first stage of buffers,

has four transistors in series (counting the transistors inside the buffer that generates signal B2). On the other hand, the top part of the cell has three transistors in series (counting the transistors inside the buffers). Consequently, the PTL implementation in Fig. 3.1.b may then be viewed as two independent gates connected in cascade.

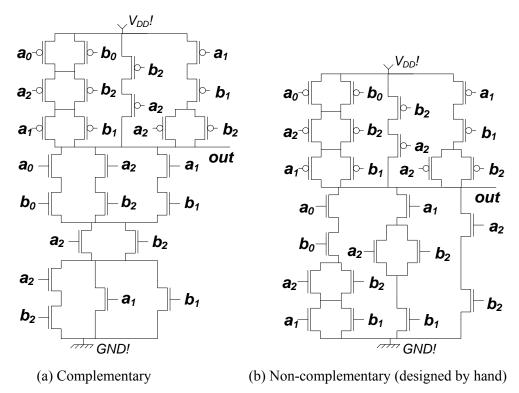

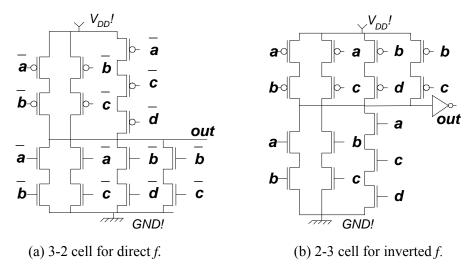

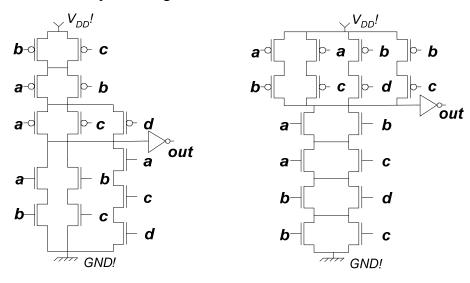

A Complementary Series/Parallel (CSP) CMOS (BERKELAAR, 1988; REIS, 1995; REIS, 1997; GAVRILOV, 1997) implementation of the circuit *c3* can be observed on Fig. 3.2.a, where there is a pull-down network with five transistors in series. This is not considered feasible from the electrical point of view as there is too much degradation of the signal in the discharge path due to increased resistance. Using CSP in this case would require the logic cell to be split into two or more stages.

However, one may notice that the *c3* function may be synthesized as a single cell where the pull-down network has at most four stacked transistors and the pull-up chain has at most three. This implementation is shown in Fig. 3.2.b, and it is 60% faster (according to SPICE simulations) than the fastest decomposed version presented in (SHELAR, 2001). Moreover, this is not a problem that is unique to the cell generation method in (SHELAR, 2001). Indeed, this seems to be true for several approaches based on PTL, as the are also examples of non-optimized pull-up and/or pull-down paths in other papers based on PTL logic (BUCH, 1997; ZHOU, 2001). Notice that although the circuit in Fig. 3.2.b is series/parallel CMOS, PUN and PDN are not topologically complementary. Therefore, this problem is not unique to the cell generation for PTL, since reducing (or controlling as a design parameter) the maximum length of transistor stacks in a circuit is important for most logic families. These observations lead us to formulate the following questions:

- 1) What is the minimum length for the PUN and PDN paths when designing a switch network for a given cell?

- 2) Is it possible to synthesize a network for the circuit in Fig. 3.2.b with shorter PUN and PDN path lengths?

Figure 3.1: BDD and PTL implementation for function c3.

Figure 3.2: Series/parallel CMOS implementations of c3.

In the next Sections it will be addressed the question of deriving exact lower bounds for the number of switches in the longest PUN and PDN stacks inside a switch network for a logic cell.

# 3.2 Basic Concepts

#### 3.2.1 Boolean space and cube size

The Boolean set B is composed of the following elements {0, 1}. A Boolean variable may assume an arbitrary value in the set B. A n-dimensional Boolean space is defined through a set composed of n Boolean variables and is noted as  $B^n = \{(a_0, a_1, ..., a_{n-1})\}/a_i$  $\in \{0, 1\}$ . The Boolean space  $B^n$  is composed of  $2^n$  distinct points. A cube of  $B^n$  is a sub-space of  $B^n$  obtained through the assignment of specific values to a subset of variables in  $B^n$ . The assignment of values to m out of the n variables in  $B^n$  will denote a cube of size  $B^{n-m}$ . A cube of unitary size is said to be a minterm. If all variables have assigned values, a single point in the Boolean space is indicated. A Boolean function is a mapping  $B^n \rightarrow B$ , such that every point in  $B^n$  is mapped to one and only one value in B. The set of variables in  $B^n$  is the domain of the function. Boolean functions may be expressed through the Boolean algebra, composed of the following operations in the B set: AND (denoted by  $\cdot$ ), OR (denoted by +) and INVERSION or NOT (denoted by a horizontal bar over the variable or function, like  $\bar{a}$ ). Consider an ordering that states that 1>0, over B. The AND of n Boolean variables is defined as the minimum value assumed by the input variables. The OR of n Boolean variables is defined as the maximum value assumed by the input variables. The INVERSION is a unary operator that returns the value in B that is different from the one assigned to the input. It is important to observe the operator precedence is NOT > AND > OR. A literal of an equation is an instance of a variable in the direct  $a_i$  or inverted  $\overline{a_i}$  form. A specific cube

of  $B^n$  may be expressed as a product of literals in the following manner: variables assigned to the value I appear as a direct literal  $a_i$ , while variables assigned to the value 0 appears as an inverted  $\overline{a_i}$  literal. For instance the cube  $a \cdot \overline{c} \cdot d$  represents the Boolean subspace where a = I, c = 0 and d = I. The subspace defined by this cube will have a size  $2^{n-3}$ , with respect to a n-dimensional Boolean space  $B^n$ . A cube C is said to be an on-set implicant cube of a given Boolean function f if all the points in the subspace defined by C are mapped to I through the function f. An implicant cube is said to be an on-set prime implicant of function f if it is not contained in a distinct implicant cube of f. Similarly, a cube f is said to be an off-set implicant cube of a given Boolean function f if all the points in the subspace defined by f are mapped to f through the function f. An implicant cube is said to be an off-set prime implicant of function f if it is not contained in a distinct implicant cube of the off-set of function f.

#### 3.2.2 Switches and logic cells

A switch controls the connection between two different points. The discussion in this paper will be restricted to two different kinds of switches, as described in the following. An *active-0* switch will connect two nodes if the control variable is equal to 0; the switch will not connect these points when the control signal is equal to 1. Similarly, an *active-1* switch will short-circuit two nodes if the control variable is equal to 1 and it will be an open circuit if the variable is 0. PMOS transistors are active-0 switches and NMOS transistors are active-1 switches.

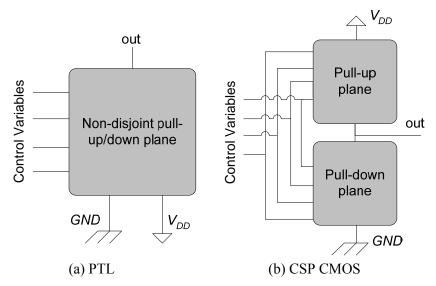

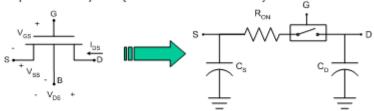

A logic cell that implements a given logic function is formed by a set of interconnected switches. These switches are controlled by the variables in the domain of the logic function. The main switch topologies used to design transistor networks for logic cells are Pass Transistor Logic (PTL) (BUCH, 1997; HSIAO, 2000; SCHOLL, 2000; LINDGREN, 2001; ZHOU, 2001; SHELAR, 2001; SHELAR, 2002; AVCI, 2003) and Complementary Series/Parallel (CSP) CMOS Logic (BERKELAAR, 1988; REIS, 1995; REIS, 1997; GAVRILOV, 1997). Fig. 3.3 illustrates these topologies. It is possible to notice that the PTL topology is composed of a single non-disjoint pull-up/down plane, while the CSP topology has two disjoint switch planes: one pull-up plane and one pull-down plane.

Figure 3.3: PTL and CSP CMOS topologies.

Independently of the topology, the output of the cell is connected to  $V_{DD}$  or GND through a path composed of serially connected switches that are active (connected) under a given input assignment. A pull-up path connects the output of the cell to the  $V_{DD}$  (logic-I) reference, through a set of serially connected switches. A pull-down path connects the output of the cell to the GND (logic-O) reference, through a set of serially connected switches. A pull-up path is associated with an on-set implicant cube, while a pull-down path is associated with an off-set implicant cube. In this work it will be referred to a cell with longest pull-up chain PU and longest pull-down PD as being a PU-PD cell. For instance, a static CMOS 2-input NAND is a 1-2 cell.

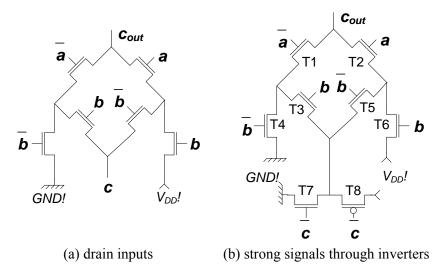

**Example 1:** Consider the PTL cells shown in Fig. 3.4, for the carry-out function of a full adder. The PTL cell in Fig. 3.4.a has the input c connected to transistor drains. However, inside an integrated circuit these signals will always be available through another cell that will generate them. In the best case, these signals will be generated through an inverter. Thus the following discussion will consider that drain signals are available through inverters. Fig. 3.4.b shows the PTL cell with the transistors corresponding to the inverters added to the transistor network. The path composed of the transistors T2-T5-T8 is a pull-up path and it is associated to the on-set implicant cube  $a \cdot \overline{b} \cdot c$ . The association between switches and literals follows the possibilities listed in Table 3.1: T2 corresponds to possibility #3, T5 corresponds to possibility #4 and T8 corresponds to possibility #2. The other pull-up paths are T1-T3-T8 and T2-T6 corresponding to the on-set implicants  $\overline{a} \cdot b \cdot c$  and  $a \cdot b$ . Similarly for the off-set, the path composed of the transistors T1-T3-T7 is a pull-down path and it is associated to the off-set implicant cube  $\bar{a} \cdot b \cdot \bar{c}$ . Again, the association between switches and literals follow the possibilities listed in Table 3.1: T1 corresponds to possibility #4, T3 corresponds to possibility #3 and T7 corresponds to possibility #4. The other pull-down paths are T1-T4 and T2-T5-T7 corresponding to the on set implicants  $\bar{a} \cdot \bar{b}$  and  $a \cdot \bar{b} \cdot \bar{c}$ . The on-set (off-set) is given by the sum of all on-set/off-set implicants corresponding to PUN/PDN paths, as given by equations (3.1)/(3.2) below. Notice that these equations are correct, but they are not prime covers. Prime covers for the on-set and off-set of this particular function would have cubes composed of at most two literals. The cell in Fig 3.4.b is a 3-3 cell, which is not the minimum transistor chain that may be achieved for this cell, as will be demonstrated later in this Chapter. Paths and associated cubes present in the switch network of Fig. 3.4.b are summarized in Table 3.2.

$$on - set = a \cdot \overline{b} \cdot c + \overline{a} \cdot b \cdot c + a \cdot b \tag{3.1}$$

$$off - set = \overline{a} \cdot b \cdot \overline{c} + \overline{a} \cdot \overline{b} + a \cdot \overline{b} \cdot \overline{c}$$

(3.2)

Table 3.1: Literals in cubes associated to paths.

| Possibility number | Switch<br>type | Literal in the switch | Literal in the cube |

|--------------------|----------------|-----------------------|---------------------|

| 1                  | Active-0       | ai                    | $\overline{ai}$     |

| 2                  | Active-0       | $\overline{ai}$       | ai                  |

| 3                  | Active-1       | ai                    | ai                  |

| 4                  | Active-1       | $\overline{ai}$       | $\overline{ai}$     |

Figure 3.4: Two distinct PTL cells.

Table 3.2: Pull-up and pull-down paths for the PTL-based network shown in Fig. 3.4.b.

| Type      | Transistors | Cube                |

|-----------|-------------|---------------------|

|           | T1-T3-T8    | $a \cdot b \cdot c$ |

| Pull-up   | T2-T5-T8    | $a \cdot b \cdot c$ |

|           | T2-T6       | $a \cdot b$         |

|           | T1-T4       | $a \cdot b$         |

| Pull-down | T1-T3-T7    | $a \cdot b \cdot c$ |

|           | T2-T5-T7    | $a \cdot b \cdot c$ |

#### 3.3 Exact Lower Bound for Stacked Switches

The lower bound for the number of stacked switches proposed hereby is based on the number of literals of the smallest cube in a prime and irredundant cover (set of prime implicants that covers a function and where each prime implicant on the set is not covered any other one in the same set). The problem with this is that if a function might have distinct prime and irredundant covers with a different number of literals in the smallest cube, then the lower bound would not be univocally defined. In the following, it is presented a proof to ensure that this condition will never happen as the size of the smallest cube in distinct prime irredundant covers of a logic function is univocally defined.

**Definition 1:** A cube with m literals will have cube size  $2^{n-m}$  in Boolean space  $B^n$ . By definition, the smallest cube is the cube with larger number of literals.

**Theorem 1:** The number m of literals in the smallest cube does not change for distinct prime implicant covers of the same logic function.

**Proof (by contradiction):** Consider two distinct prime and irredundant covers C1 and C2 of the same function f such that the smallest cubes in C1 and C2 have different sizes. Suppose that cover C1 has smallest cube(s) composed of m literals. Suppose also

that the smallest(s) cube(s) in cover C2 are composed of m-i literals, such that 0 < i < m. To turn on any prime irredundant cube in C1, it is necessary to assign at most m variables to logic-0 or logic-1 as appropriate. The reason for this is because the smallest cube in C1 is not redundant and has m literals. However, assigning at most m-i variables is sufficient to turn on any prime implicant cube in C2. Thus, the analysis of the complete set of all variable assignments containing m-i or fewer variables in  $B^n$  is sufficient to decide if the function represented by C2 evaluates to logic-1. This same analysis is not sufficient, nonetheless, to decide if the function represented by C1 evaluates to logic-1, due to the irredundant prime implicant(s) with m literals. Therefore, the functions given by covers C1 and C2 are not the same logic function, leading to a contradiction of our initial hypothesis that two distinct prime implicant covers of the same function could have smallest cubes with different sizes. QED.

**Corollary**: Theorem 1 is valid for two prime irredundant covers. Non-prime covers may have smaller non-prime cubes with more than *m* literals, where *m* is the size of the smallest cube in any prime irredundant cover. However, no cover may have only cubes greater (with a smaller number of literals) than the smallest cube in any prime irredundant cover.

**Definition 2:** A PUN path connects the output of the cell to the  $V_{DD}$  (logic-I) reference, through a set of serially connected switches.

**Theorem 2:** Given a function f, it is not possible to have a cell whose longest PUN path has fewer switches than m, being m the number of literals in the smallest cube of any prime irredundant cover C for the on-set of function f.

**Proof (by contradiction):** Recall that the smallest cube has the greater number of literals (Definition 1). By Theorem 1, all the prime irredundant covers of function f will have at least one cube with m literals, where m is the size of the smaller cube in any prime cover of f. Non-prime covers of f may have smaller cubes with more than m literals. However, covers where all the cubes have less than m literals are not possible, due to Theorem 1 and its Corollary. Consider a function f defined in f such that a prime irredundant cover f of f has f literals. Suppose now that function f has a generic switch realization where the f pull-up path has size f, such that f was a generic switch realization where the f pull-up path has size f such that f was a generic switch realization where the f pull-up path has size f such that f was a generic detail through Example 1 of Subsection 3.2.2, each of these PUN paths would be associated with an on-set implicant cube with f literals. As a consequence, every PUN path with size f was f will produce a cube with f literals where f was f was f will produce a cube with f literals where f was f literals, as f was f literals, as f was all the cubes in the realization would have a smaller number of literals f was and a greater size. QED.

**Theorem 3:** Given a function f, it is possible to produce a cell where the longest PUN path has m switches in series, being m is the number of literals in the smallest cube in a prime irredundant cover C for the on-set of function f.

**Proof (by construction):** It is possible to construct a pull-up plane for function f given a prime irredundant cover  $C = \sum P_i$  of the function, where each cube  $P_i = \prod l_i$  is a product of literals associated to the variables in the domain of the function. Every prime cube  $P_i$  contributes to the PUN with an independent path. The paths for each cube  $P_i$  are independent as they are parallel paths among each other. Each of the independent paths is composed of serially connected switches between the logic-I reference  $(V_{DD})$  and the output of the cell. The path for a given cube in the cover contains one serially connected

switch for each literal  $l_i$  in the cube, as described by Example 1 in Subsection 3.2.2. As the smallest cube has the greater number of literals, it will determine the size of the longest path. Thus this implementation will have by construction the longest PUN path with a size correspondent to the number m of literals in the smallest cube of C. Furthermore, as the path for each cube is independent, this solution has no sneak paths. QED.

**Theorem 4:** The exact lower bound in the number of stacked switches (or switches in series) in the longest PUN path of a logic function f is given by m, the number of literals in the smallest cube in any prime irredundant cover C for the on-set of function f.

**Proof:** Immediate Corollary of Theorems 2 and 3, and univocally defined as consequence of Theorem 1. QED.

**Definition 3:** A PDN path connects the output of the cell to the *GND* (logic-0) reference, through a set of serially connected switches.

**Theorem 5:** Given a function f, it is not possible to have a cell whose longest PDN path has fewer switches than m, the number of literals in the smallest cube of any prime irredundant cover C for the off-set of function f.

**Proof:** The proof is similar to that of Theorem 2. QED.

**Theorem 6:** Given a function f, it is possible to produce a cell where the longest PDN path has m switches in series, where m is the number of literals in the smallest cube in a prime irredundant cover C for the off-set of function f.

**Proof:** The proof is similar to that of Theorem 3. QED.

**Theorem 7:** The exact lower bound in the number of stacked switches in the longest PDN path of a logic function f is given by m, the number of literals in the smallest cube in any prime irredundant cover C for the off-set of function f.

**Proof:** Immediate corollary of Theorems 5 and 6, and univocally defined as consequence of Theorem 1. QED.

# 3.4 Evaluating the lower bound

At first, it may seem too time-intensive to calculate the lower bound for candidate functions, as it is necessary to calculate two prime ISOPs (Irredundant Sums-of-Products). However, as one evaluate only the PUN and PDN stacks inside cells, the evaluation process is not a critical step because it is easy to obtain prime ISOPs when the number of variables is small. For this purpose a BDD-based ISOP function (MINATO, 1996) may be used.

For the sake of simplicity, next Chapter will extract the ISOPs used to determine the lower bound for the number of transistors in PUN and PDN stacks using the well-established tabular method so called Quine-McCluskey (QUINE, 1955; MCCLUSKEY, 1956; MICHELI, 1994).

# 3.5 Consequences and Applications

This Section presents consequences and applications of the lower bounds introduced in previous Sections.

#### 3.5.1 Lower bound impact analysis

For a better understanding of the impact of the lower bound theory for stacked switch paths length, some illustrative examples are presented.

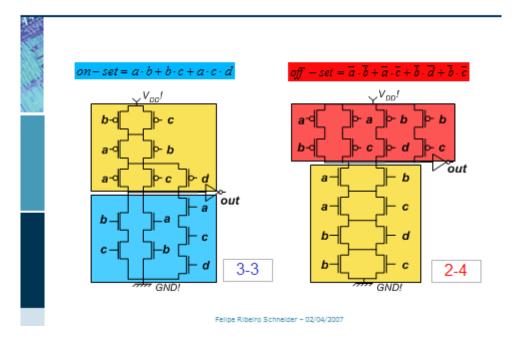

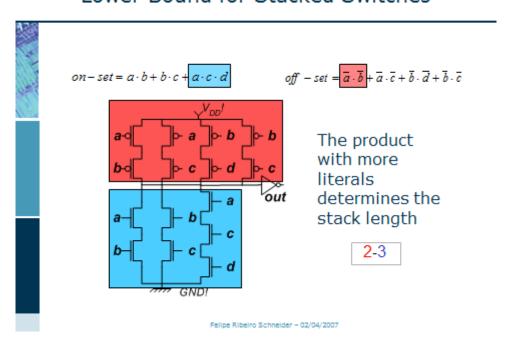

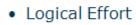

**Example 2:** Consider a function f given by equation  $f = a \cdot b + b \cdot c + a \cdot c \cdot d$ . The minimum covers for the on-set and the off-set of this function are:

$$on - set = a \cdot b + b \cdot c + a \cdot c \cdot d \tag{3.3}$$

$$off - set = \overline{a} \cdot \overline{b} + \overline{a} \cdot \overline{c} + \overline{b} \cdot \overline{d} + \overline{b} \cdot \overline{c}$$

(3.4)

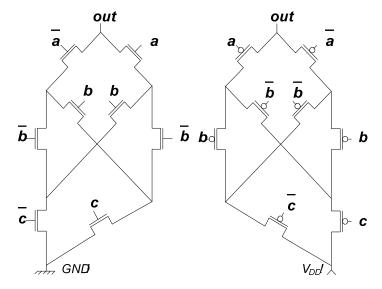

The smallest cube in the on-set is  $a \cdot c \cdot d$ , so the lower bound for the number of stacked transistors in the PUN is three. The cubes in the off-set are all the same size, and the lower bound for the number of stacked switches in the PDN is two. This way the cell corresponding to the function f is a 3-2 cell, when mapped with the constructive method proposed in the next Chapter. It could also be a 2-3 cell, if the function is inverted and an inverter is added to the cell output.

**Example 3:** Recall the function in Example 1, the carry-out of a full adder. Prime irredundant covers for the on-set and off-set are given by the following equations.

$$on - set = a \cdot b + a \cdot c + b \cdot c \tag{3.5}$$

$$off - set = \overline{a} \cdot \overline{b} + \overline{a} \cdot \overline{c} + \overline{b} \cdot \overline{c}$$

(3.6)

It is easy to see that the lower bounds for the carry-out in a full adder are two switches for both the pull-up and pull-down planes. This is consistent with the classic 2-2 cell for carry-out generation presented in the cover of the classic Weste-Eshraghian book (WESTE, 1993).

**Example 4:** What is the minimum number of transistor in series to implement the function c3? The minimum covers are given by the following equations.

$$on - set = a2 \cdot b2 + a2 \cdot a1 \cdot b1 + b2 \cdot a1 \cdot b1 + a2 \cdot a1 \cdot a0 \cdot b0 + a2 \cdot b1 \cdot a0 \cdot b0 + b2 \cdot a1 \cdot a0 \cdot b0 + b2 \cdot b1 \cdot a0 \cdot b0$$

(3.7)

$$off - set = a2 \cdot b2 + a2 \cdot a1 \cdot b1 + a2 \cdot a1 \cdot a0 + a2 \cdot a1 \cdot b0 + a2 \cdot b1 \cdot a0 + a2 \cdot b1 \cdot b0 + b2 \cdot a1 \cdot b1 + b2 \cdot a1 \cdot a0 + b2 \cdot a1 \cdot b0 + b2 \cdot b1 \cdot a0 + b2 \cdot b1 \cdot b0$$

(3.8)

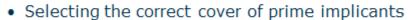

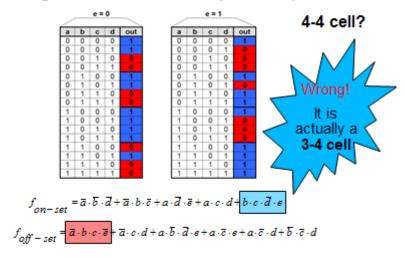

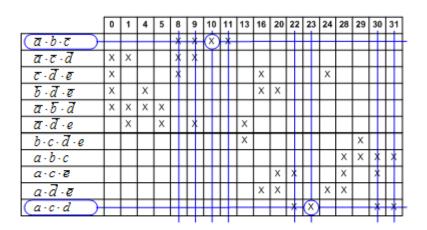

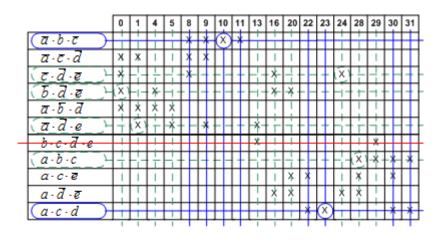

Equation (3.7) has 4 literals in the smallest cube. Equation (3.8) has 3 literals in the smallest cube. This way, the circuit presented in Fig. 2 cannot be designed with shorter transistor chains, as it is clear that minimum transistor chain version of c3 is either a 3-4 cell or a 4-3 cell, depending on polarity assignment. This is the main goal of the lower bound proposed here, to verify and ensure that performance is not being lost due to the misuse of cells with excessively long transistor stacks. The CSP implementation from equation (3.7) would be 4-7 cell, while the CSP implementation from equation (3.8) would be a 3-11 cell. The PTL cell would be a 6-6 cell.

#### 3.5.2 Lower bound and general PTL styles