### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA - PGMICRO

#### RAFAEL MENDES MALLMANN

## Arquiteturas em Hardware para o Alinhamento Local de Sequências Biológicas

Dissertação apresentada como requisito parcial para a obtenção do grau de Mestre em Microeletrônica

Prof. Dr. Gilson Wirth Orientador

## CIP - CATALOGAÇÃO NA PUBLICAÇÃO

#### Mallmann, Rafael Mendes

Arquiteturas em Hardware para o Alinhamento Local de Sequências Biológicas / Rafael Mendes Mallmann. – Porto Alegre: PGMICRO da UFRGS, 2010.

70 f.: il.

Dissertação (mestrado) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica - PGMI-CRO, Porto Alegre, BR-RS, 2010. Orientador: Gilson Wirth.

1. Smith-Waterman. 2. Distância Levenshtein. 3. Distância de edição. 4. Array sistólico. 5. Hardware dedicado. 6. Alinhamento local. 7. Programação dinâmica. 8. FPGA. 9. ASIC. 10. Comparação de genomas. I. Wirth, Gilson. II. Título.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos Alexandre Netto

Vice-Reitor: Prof. Rui Vicente Oppermann

Pró-Reitor de Pós-Graduação: Prof. Aldo Bolten Lucion Diretor do Instituto de Informática: Prof. Flávio Rech Wagner Coordenador do PGMICRO: Prof. Ricardo Augusto da Luz Reis

Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

## SUMÁRIO

| LISTA DE ABREVIATURAS E SIGLAS                                                                                                                                             | 6                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| LISTA DE FIGURAS                                                                                                                                                           | 7                               |

| LISTA DE TABELAS                                                                                                                                                           | 8                               |

| RESUMO                                                                                                                                                                     | 9                               |

| ABSTRACT                                                                                                                                                                   | 10                              |

| 1 INTRODUÇÃO                                                                                                                                                               | 11                              |

| 2.1 Material Genético                                                                                                                                                      | 14<br>14<br>15<br>16            |

| 3.1 Distância Levenshtein 3.2 Smith-Waterman 3.3 Alinhamento Múltiplo 3.4 Métodos Heurísticos                                                                              | 18<br>19<br>21<br>23<br>24      |

| 4 ARQUITETURAS ESTUDADAS                                                                                                                                                   | 26<br>26<br>27<br>27            |

| gorithn in an Extended Processor                                                                                                                                           | 28<br>28                        |

| 4.7 A Highly Parameterized and Efficient FPGA-Based Skeleton for Pairwise Biological Sequence Alignment  4.8 High Speed Implementation of Smith Weterman Algorithm for DNA | <ul><li>29</li><li>30</li></ul> |

| 4.8 High-Speed Implementation of Smith-Waterman Algorithm for DNA Sequence Scanning in VLSI                                                                                | 30<br>31                        |

| 4.10 Acceleration of Smith-Waterman Using Recursive Variable Expansion .                                                                                                   | 32                              |

| 4.11  | Arquiteturas em FPGA para Comparação de Sequencias Biologicas em    |     |

|-------|---------------------------------------------------------------------|-----|

|       | Espaço Linear                                                       | 33  |

| 4.12  | Families of FPGA-based Accelerators for Approximate String Matching | 33  |

| 4.13  | A Reconfigurable Accelerator for Smith-Waterman Algorithm           | 33  |

| 5 P   | ROJETO EM HARDWARE PARA O ALINHAMENTO LOCAL DE SEQU                 | ÊN- |

| C     | SIAS                                                                | 35  |

| 5.1   | Matriz Dinâmica                                                     | 35  |

| 5.2   | Particionamento de Sequências                                       | 38  |

| 5.3   | Protocolo de Comunicação                                            | 40  |

| 5.4   | Unidade de Processamento para a Distância Levenshtein               | 42  |

| 5.5   | Unidade de Processamento para o Smith-Waterman                      | 44  |

| 6 R   | ESULTADOS E COMPARAÇÕES                                             | 48  |

| 6.1   | Prototipando para FPGA                                              | 49  |

| 6.1.1 | Utilizando o barramento PCI Express                                 | 52  |

| 6.2   | Prototipando para ASIC                                              | 54  |

| 6.2.1 | Front End                                                           | 54  |

| 6.2.2 | Back End                                                            | 57  |

| 6.3   | Comparações                                                         | 59  |

| 7 C   | ONCLUSÕES                                                           | 65  |

| REFE  | RÊNCIAS                                                             | 67  |

## LISTA DE ABREVIATURAS E SIGLAS

API Application Programming Interface

ASIC Application-Specific Integrated Circuit

BD Base de Dados

BLAST Basic Local Alignment Search Tool

BLOSUM BLOcks of Amino Acid SUbstitution Matrix

BRAM Block Random-access memory

CUDA Compute Unified Device Architecture

CUPS Cell Updates Per Second

DDBJ Base de Dados de DNA do Japão

DMA Acesso Direto a MemóriaDNA Ácido DesoxirriboNucleico

EMBL Laboratório Europeu de Biologia Molecular

FPGA Field-Programmable Gate Array

GPU Graphics Processing Unit

HDL Hardware Description Language

LUT Look up Table

NCBI National Center for Biotechnology Information

PAM Point Accepted Mutation

PCI Peripheral Component Interconnect

PCIe Peripheral Component Interconnect Express

RAM Random-access memory

RNA Ácido Ribonucleico

SDC Synopsys Design Constraints

VHDL VHSIC hardware description language

VHSIC Very-High-speed Integrated Circuit

UP Unidade de Processamento

## LISTA DE FIGURAS

| Figura 2.1: Crescimento dos bancos de dados genético GenBank/EMBL/DDBJ                                                                           | 17       |

|--------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| (1995-2010)                                                                                                                                      |          |

| Figura 3.1: Matriz de substituição Blosum62                                                                                                      | 23       |

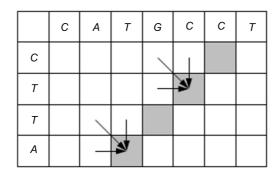

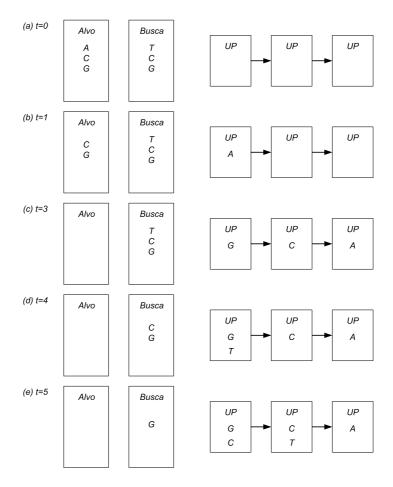

| Figura 5.1: Deslocamento do vetor <i>wavefront</i> na matriz de similaridades                                                                    | 36       |

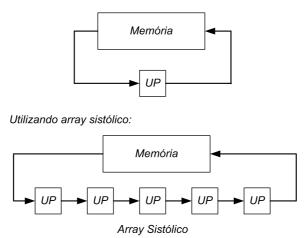

| Figura 5.2: Princípios básicos de uso do array sistólico                                                                                         | 36       |

| Figura 5.3: Exemplo de como utilizar array sistólico para algoritmos de programação dinâmica                                                     | 37       |

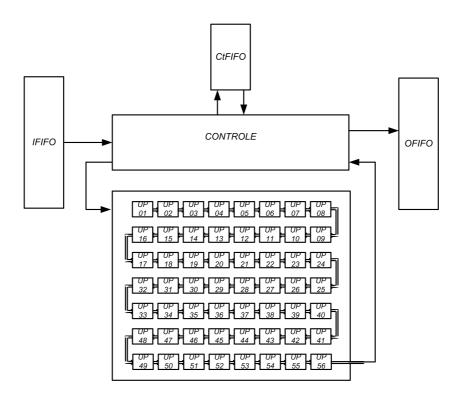

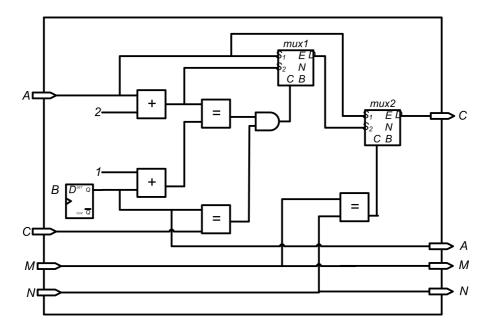

| Figura 5.4: Diagrama de blocos da arquitetura para o particionamento de sequência                                                                |          |

| Figura 5.5: Exemplo da arquitetura projetada de particionamento de sequências                                                                    |          |

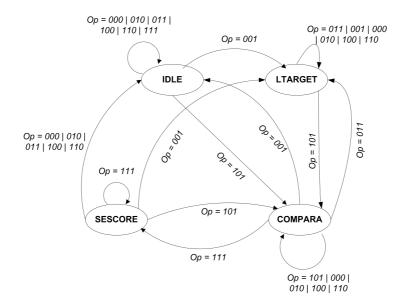

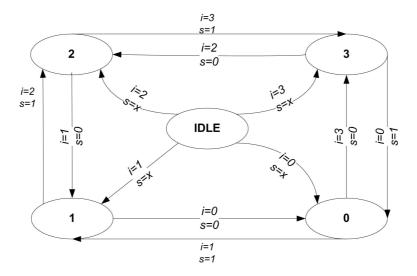

| Figura 5.6: Máquina de estados que controla a arquitetura projetada                                                                              | 41       |

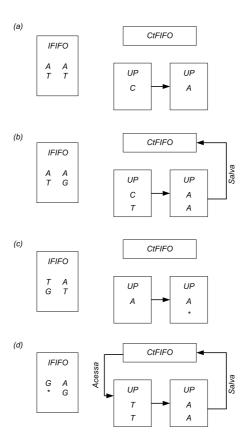

| Figura 5.7: Datapath da unidade de processamento para a distância Levenshtein                                                                    |          |

| Figura 5.8: Máquina de estados que controla o decremento e o incremento do registrador com a distância de edição                                 |          |

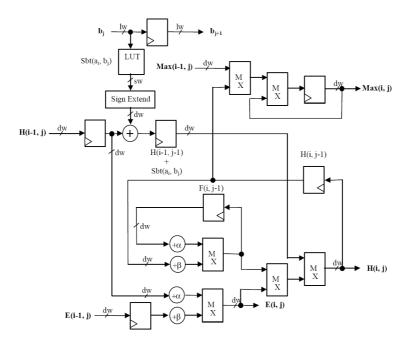

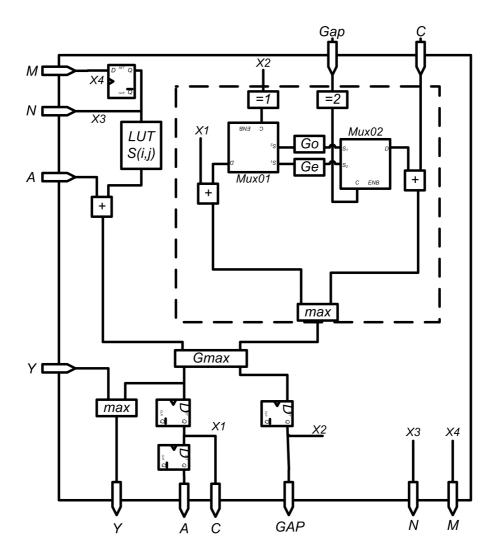

| Figura 5.9: Unidade de processamento para o Smith-Waterman que implementa diretamente as equações do algoritmo, retirado de Oliver et al. (2005a |          |

| Figura 5.10: Unidade de processamento projetada para o Smith-Waterman                                                                            |          |

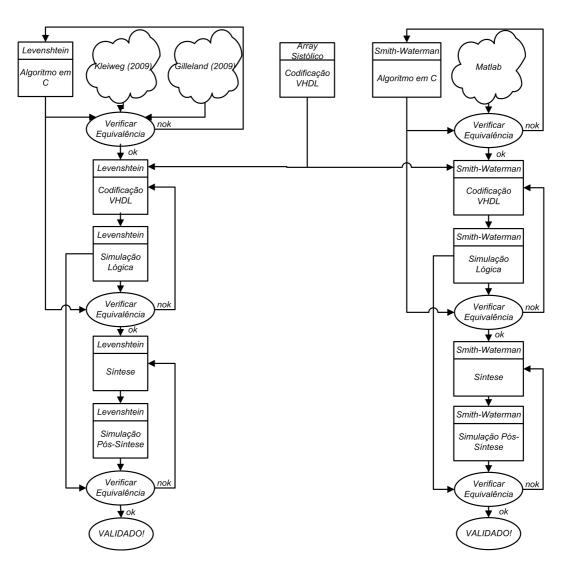

| Figura 6.1: Fluxo utilizado no projeto das arquiteturas                                                                                          | 50       |

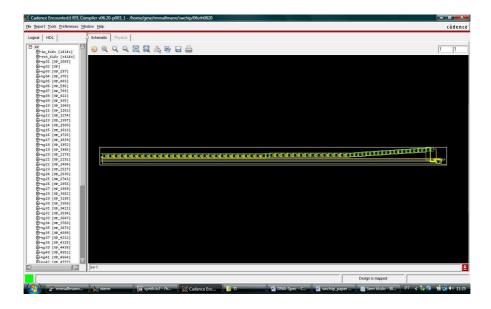

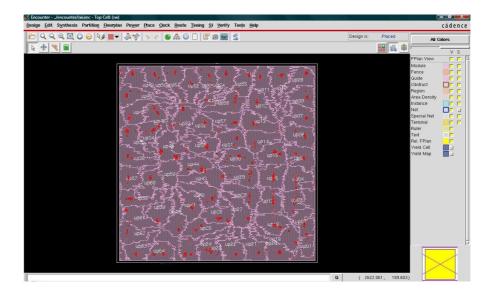

| Figura 6.2: Top-level do projeto após síntese lógica                                                                                             |          |

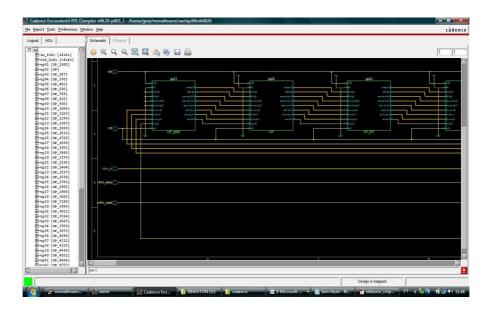

| Figura 6.3: Detalhe mostrando a conexão entre UPs após síntese lógica                                                                            |          |

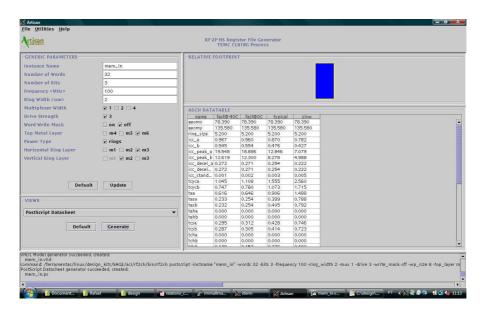

| Figura 6.4: Gerador de memória fornecido pela empresa Artisan                                                                                    |          |

| Figura 6.5: Anéis e stripes de alimentação configurados                                                                                          | 58       |

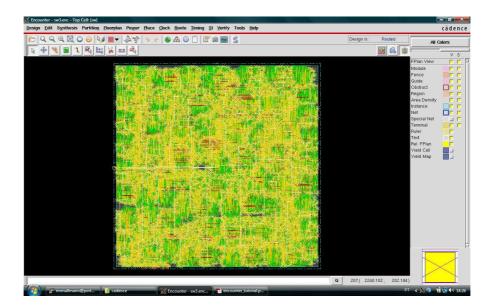

| Figura 6.6: Visão do posicionamento dos blocos projetados utilizando o Amoeba                                                                    | 58       |

| View                                                                                                                                             | 50<br>59 |

## LISTA DE TABELAS

| Tabela 2.1:                | O padrão utilizado pelo código genético                                                         | 16 |

|----------------------------|-------------------------------------------------------------------------------------------------|----|

| Tabela 3.1:<br>Tabela 3.2: | Exemplo do algoritmo distância Levenshtein                                                      |    |

| Tabela 5.1:                | Exemplo do algoritmo distância Levenshtein com otimização proposta por Lipton e Lopresti (1985) | 43 |

| Tabela 6.1:                | Dados da síntese de uma UP para o dispositivo XC5VLX330T-1                                      | 52 |

| Tabela 6.2:                | Dados da síntese dos projetos para o dispositivo XC5VLX330T-1                                   | 53 |

| Tabela 6.3:                | Desempenho do barramento PCIe usando DMA                                                        | 53 |

| Tabela 6.4:                | Relatório de área após síntese lógica                                                           | 55 |

| Tabela 6.5:                | Relatório de potência após síntese lógica                                                       | 56 |

| Tabela 6.6:                | Caminho crítico determinado após síntese lógica                                                 | 56 |

| Tabela 6.7:                | Relatório de área após síntese física                                                           | 58 |

| Tabela 6.8:                | Relatório de potência após síntese física                                                       | 58 |

| Tabela 6.9:                | Particionamento de sequências em relação ao BD Swiss-Prot                                       | 60 |

| Tabela 6.10:               | Comparação entre o desempenho da arquitetura em hardware dedi-                                  |    |

|                            | cado e o software SSearch36                                                                     | 61 |

| Tabela 6.11:               | Comparação entre as arquiteturas estudadas e arquiteturas projetadas                            |    |

|                            | para a distância Levenshtein                                                                    | 62 |

| Tabela 6.12:               | Comparação entre as arquiteturas estudadas e arquiteturas projetadas                            |    |

|                            | para o Smith-Waterman com affine gap                                                            | 63 |

|                            |                                                                                                 |    |

### **RESUMO**

Bancos de dados biológicos utilizados para comparação e alinhamento local de sequências tem crescido de forma exponencial. Isso popularizou programas que realizam buscas nesses bancos. As implementações dos algoritmos de alinhamento de sequências Smith-Waterman e distância Levenshtein demonstraram ser computacionalmente intensivas e, portanto, propícias para aceleração em hardware. Este trabalho descreve arquiteturas em hardware dedicado prototipadas para FPGA e ASIC para acelerar os algoritmos Smith-Waterman e distância Levenshtein mantendo os mesmos resultados obtidos por softwares. Descrevemos uma nova e eficiente unidade de processamento para o cálculo do Smith-Waterman utilizando *affine gap*. Também projetamos uma arquitetura que permite particionar as sequências de entrada para a distância Levenshtein em um array sistólico de tamanho fixo. Nossa implementação em FPGA para o Smith-Waterman acelera de 275 a 494 vezes o algoritmo em relação a um computador com processador de propósito geral. Ainda é 52 a 113% mais rápida em relação, segundo nosso conhecimento, as mais rápidas arquiteturas recentemente publicadas.

**Palavras-chave:** Smith-Waterman, distância Levenshtein, distância de edição, array sistólico, hardware dedicado, alinhamento local, programação dinâmica, FPGA, ASIC, comparação de genomas.

#### Hardware Architectures for Local Biological Sequence Alignment

### **ABSTRACT**

Bioinformatics databases used for sequence comparison and local sequence alignment are growing exponentially. This has popularized programs that carry out database searches. Current implementations of sequence alignment methods based on Smith-Waterman and Levenshtein distance have proven to be computationally intensive and, hence, amenable for hardware acceleration. This Msc. Thesis describes an FPGA and ASIC based hardware implementation designed to accelerate the Smith-Waterman and Levenshtein distance maintaining the same results yielded by general softwares. We describe an new efficient Smith-Waterman affine gap process element and a new architecture to partitioning and maping the Levenshtein distance into fixed size systolic arrays. Our FPGA Smith-Waterman implementation delivers 275 to 494-fold speed-up over a standard desktop computer and is also about 52 to 113% faster, to the best of our knowledge, than the fastest implementation in a most recent family of accelerators.

**Keywords:** DNA sequence scanning, Smith-Waterman, edit distanve, Levenshtein distance, dynamic programming, systolic array, FPGA, ASIC, VLSI, protein sequences, query sequence, subject sequence.

## 1 INTRODUÇÃO

A biologia molecular está repleta de perguntas fascinantes. Como as espécies se adaptam ao seu ambiente? Quais genes são responsáveis pelas principais doenças humanas? Por que é necessário produzir novas vacinas anualmente? A introdução de métodos matemáticos e a grande quantidade de dados genômicos sequenciados nos permitem responder esse tipo de questão. A disponibilidade desses dados e os algoritmos desenvolvidos para processá-los desencadearam uma revolução na biologia, muitas vezes comparada ao mesmo fenômeno ocorrido na física no início do século XX. Os efeitos dessa revolução são sentidos em muitos outros campos da ciência. Aplicações no campo da medicina, desenvolvimento de vacinas, forense, antropologia e epidemiologia prometem aumentar nossa qualidade e expectativa de vida, bem como nosso entendimento do mundo.

Pense no problema de ter que escrever o conjunto de todas as instruções necessárias para construir e operar um ser humano, e pense que essa informação deve ser acessada de forma distribuída em cada uma das trilhões de células que compõe esse corpo. A solução encontrada pela natureza para esse problema é o genoma. Calcula-se que seu tamanho completo é de 3.5 bilhões de caracteres e cada célula do corpo possui duas cópias desse conjunto de instrução (GUSFIELD, 1997).

Atualmente a tecnologia de instrumentos para sequenciar dados biológicos tem avançado drasticamente. As primeiras máquinas utilizadas no fim da década de 80 sequenciavam cerca de 4800 pares de bases por dia. Em 2010, duas importantes empresas do setor (*Illumina* e *Life Technologies*) anunciaram o lançamento de máquinas capazes de gerar, respectivamente, 25 bilhões e 100 bilhões de pares de bases em um dia (VENTER, 2010). Alguns aspectos relativos à precisão dos resultados obtidos por esses equipamentos ainda são discutidos, porém é inegável o avanço obtido em apenas 20 anos.

Todos esses dados biológicos sequenciados, atualmente, são armazenados em repositórios públicos que permitem livre acesso. Porém, com a redução dos custos dessas máquinas de sequenciamento, é relativamente comum empresas trabalharem com sequências privadas que são utilizadas para desenvolver novos fármacos e produtos de biotecnologia. Atualmente há um setor emergente denominado de medicina personalizada, que promete sequenciar um genoma humano personalizado por US\$ 6000. Desse modo, é fácil prever um mundo em alguns anos onde a informação genética será tão abundante como hoje são nossas informações financeiras.

Para Lecompte et al. (2001) o momento atual é denominado era pós-genômica, pois existe uma grande quantidade de informação biológica, onde o desafio é processar e extrair significado dessas. Dados sobre futuras doenças que o paciente possa desenvolver, ou a produção de fármacos mais eficientes que sejam elaboradas a partir das informações

de cada genoma pessoal são algumas promessas de aplicações da medicina personalizada. Mesmo hoje, a biotecnologia já utiliza muito o processamento em larga escala de dados biológicos para o desenvolvimento dos seus produtos.

É nesse contexto que nosso trabalho pretende contribuir. É conhecido pela literatura que processar dados biológicos utilizando processadores de propósito geral não é a melhor forma de lidar com esse problema em virtude da dificuldade da indústria de processadores de continuar avançando segundo a lei de Moore, segundo a qual o número de transistores em um circuito integrado dobra aproximadamente a cada dois anos. A computação híbrida, que agrega processadores de propósito geral e dedicados em um mesmo sistema, é o caminho natural para aumentar o desempenho de aplicações dedicadas (como é o caso da biologia molecular). Algumas tecnologias se apresentam como candidatas a esse modelo de computação: ASICs (Application-Specific Integrated Circuit), FPGAs (Field-Programmable Gate Array) e GPUs (Graphics Processing Unit).

Os sistemas projetados utilizando ASICs em geral são os mais rápidos e que consomem a menor potência. Porém, a principal desvantagem desse tipo de solução é em relação a flexibilidade e ao custo para pequena escala. Um sistema em ASIC, após fabricado é fixo - não permite modificação no projeto ou na configuração do algoritmo (exceto se o mesmo tenha sido projetado prevendo essa modificação). Para aplicação em biologia molecular esse tipo de solução não se apresenta como a mais adequada. Os algoritmos, em geral, permitem uma grande gama de parâmetros. Implementar em ASICs todas as configurações e modos de execução de um algoritmo em um mesmo circuito aumentaria a complexidade do projeto e reduziria o desempenho. Assim, essa solução é uma ótima candidata quando se tem um problema específico e com parâmetros bem conhecidos. Se o custo não é uma variável importante, visto que a escala para aplicações em biologia molecular ainda é pequena, essa tecnologia não deve ser desprezada, pois os melhores resultados de desempenho e potência serão encontrados nela.

Os FPGAs permitem que um algoritmo possa ser acelerado de forma semelhante ao utilizado pela tecnologia ASIC - por meio de uma arquitetura dedicada para resolução do problema em questão. Esse tipo de tecnologia utiliza uma matriz de elementos lógicos que permite que qualquer função lógica possa ser implementada nela. Uma grande vantagem dessa estrutura é que ela pode ser configurada diversas vezes, o que flexibiliza o uso e o fluxo de projeto de arquiteturas para essa tecnologia. Porém, em detrimento de permitir a reconfiguração do circuito, o desempenho global do sistema é, em geral, inferior ao encontrado em circuitos ASICs. Contudo, para a biologia molecular, se mostra uma solução bastante competitiva. É possível, por exemplo, projetar diversas arquiteturas para diferentes algoritmos (ou modos de execução de um mesmo algoritmo) e carregá-las em um único dispositivo FPGA conforme as necessidades do usuário. Ainda, analisando o desempenho por custo, o FPGA é a solução mais atraente, quando comparado à ASIC, para aplicações em biologia molecular.

Por fim, as placas gráficas denominadas GPU estão sendo bastante adotadas para a aceleração de algoritmos em diversas áreas do conhecimento - incluindo biologia molecular. Antigamente elas eram apenas utilizadas para acelerar aplicações gráficas, muito utilizadas por jogos e processamento de imagens. Porém a empresa Nvidia, uma das principais fabricantes do setor, lançou no mercado uma API (*Application Programming Interface*) denominada CUDA (*Compute Unified Device Architecture*) que permite que algoritmos desenvolvidos em diferentes linguagens possam ser paralelizados utilizando as diversas unidades de processamento da placa gráfica. Essa solução possui o mais alto

grau de flexibilidade e o menor custo. Adaptar um algoritmo para processar em uma placa gráfica usando uma API é uma tarefa bastante simples quando comparado ao projeto de circuitos dedicados que é necessário em ASIC e FPGA. Percebemos então que essa solução tem o menor tempo de projeto, o que faz que tenha o menor custo (o valor do hardware para as versões com maior desempenho se pode comparar com uma placa FPGA). Entretanto, a flexibilidade é diretamente proporcional a aceleração que esse tipo de solução alcança - em geral bastante inferior que as apresentadas por ASIC e FPGA.

Nesse trabalho nos concentramos em explorar arquiteturas em hardware dedicado utilizando a tecnologia ASIC e FPGA. Não utilizamos GPU, por essa ser uma arquitetura fixa, apenas permite que algoritmos sejam implementados nela - e não o projeto de novas arquiteturas. Trabalhamos com dois tipos de algoritmos para lidar com abordagens distintas. Para uma análise preliminar de similaridade entre duas sequências biológicas, a distância Levenshtein (também denominada distância de edição) é uma boa abordagem. A implementação em hardware é bastante eficiente, o que faz com que rapidamente seja possível analisar a proximidade entre duas sequências. Porém, em muitos casos, é necessário realizar comparações que exijam maior precisão e confiabilidade dos resultados (MCMAHON, 2008). Para esses casos, projetamos uma arquitetura que implementa o algoritmo Smith-Waterman utilizando *affine gap* e matrizes biológicas de substituição - BLOSUM (*Blocks of Amino Acid Substitution Matrix*), PAM (*Point Accepted Mutation*) etc.

Apresentamos como principais contribuições uma nova arquitetura de array sistólico, que enfatiza o uso de um protocolo de comunicação e o particionamento de sequências. Além disso, apresentamos uma nova unidade de processamento para o algoritmo Smith-Waterman com *affine gap* que reduz o número de somadores e comparadores de máximo permitindo maior frequência de operação e menor área quando comparada com outras arquiteturas. Mostramos o fluxo de prototipação desses sistemas utilizando FPGA e ASIC e analisamos o desempenho e a aceleração obtida em relação ao uso de processadores de propósito geral.

## 2 FUNDAMENTOS DE BIOLOGIA MOLECULAR E BIOIN-FORMÁTICA

A genética pode ser definida como o estudo da hereditariedade, e num sentido mais restrito, o estudo dos genes (JONES; PEVZNER, 2004). Foi iniciada com a descoberta dos "fatores de hereditariedade" por George Mendel por volta de 1860. Entrou na era molecular a partir da metade do século XX com a definição de estrutura de dupla hélice do DNA (*Ácido Desoxirribonucleico*), proposta por James Watson e Francis Crick, e com o surgimento das primeiras técnicas de sequenciamento, desenvolvidos por Sanger e Coulson em 1975 (CRISTIANINI; HAHN, 2007).

As questões mais fundamentais da biologia molecular tratam do funcionamento das células. Em organismos unicelulares e multicelulares é necessário descobrir como as células reagem em seu ambiente, como os genes afetam essas reações e como os organismos se adaptam a novos ambientes (SACCONE; PESOLE, 2003).

O objetivo desse capítulo é apresentar uma revisão das ideias básicas da biologia molecular, permitindo um conhecimento mínimo para o entendimento dos próximos capítulos. Entendemos que na biologia existem muitas exceções: todas as generalizações e regras que apresentaremos aqui estarão erradas para alguns organismos. Porém, de forma geral, os principais pontos estão corretamente expostos.

#### 2.1 Material Genético

Toda a vida no planeta depende de três tipos de molécula: DNA, RNA (Ácido Ribonucleico) e proteínas. Basicamente, o DNA representa uma grande biblioteca responsável por descrever o funcionamento da célula. Em contrapartida, o RNA é responsável por transferir pequenos pedaços dessa biblioteca para diferentes regiões da célula, onde esses pequenos volumes são utilizados para a síntese de proteínas. Essas, formam enzimas que, por meio de reações bioquímicas, enviam sinais para outras células, formando assim algumas partes do corpo (como a queratina em nossa pele) e fazem todo o trabalho da célula (JONES; PEVZNER, 2004).

O DNA foi descoberto em 1869 por Johann Friedrich Miescher quando ele isolou o núcleo de células sanguíneas brancas (leucócitos). No início do século XX já se sabia que o DNA era uma molécula composta por quatro tipos de bases: adenina (A), timina (T), guanina (G) e citosina (C). Originalmente, os biólogos descobriram um quinto tipo de base, denominada uracila (U), quimicamente semelhante a timina. A partir de 1920, o ácido nucleico foi agrupado em duas classes chamada DNA e RNA, que diferem na

composição das bases: o DNA utiliza o T e o RNA utiliza o U. Formalmente, o conjunto de todo o DNA associado a um organismo é denominado genoma.

As proteínas são formadas por cadeias de aminoácidos. Um proteína típica contém 200-300 aminoácidos, porém algumas são bem menores (20-40) e outras bem maiores (dezenas de milhares de aminoácidos). As proteínas podem ser modeladas como cadeias unidimensionais, porém não tem esse formato na célula. Elas são na realidade estruturas tridimensionais, onde o seu formato é o responsável por determinar a sua função. Existem 20 tipos de aminoácidos, o tipo e a posição nas cadeias são os responsáveis por determinar o formato da estrutura e, consequentemente, a função. O número de possibilidades de proteínas é enorme. Se assumirmos que todas as proteínas possuam tamanho máximo de 400 aminoácidos, se pode criar  $20^{400}$  diferentes tipos de proteínas. Segue abaixo, os alfabetos utilizados para representar DNA (2.1), RNA (2.2) e aminoácidos (2.3):

$$N_{DNA} = \{A, C, G, T\} \tag{2.1}$$

$$N_{RNA} = \{A, C, G, U\}$$

(2.2)

$$A = \{A, R, N, D, C, Q, E, G, H, I, L, K, M, F, P, S, T, W, Y, V\}$$

(2.3)

## 2.2 Dogma Central da Biologia Molecular

O modo mais fácil de explicar como as proteínas são feitas (ignorando muitos detalhes e condensando complicadas reações celulares) é por meio do diagrama apresentado em (2.4).

$$DNA \to RNA \to Proteina$$

(2.4)

Basicamente, o dogma central postula que "DNA produz RNA que produz proteínas" (a qual auxilia que seja produzido DNA novamente). O processo que produz proteínas a partir de DNA é dividido em duas etapas: transcrição  $(DNA \to RNA)$  e tradução  $(RNA \to Proteina)$  (SACCONE; PESOLE, 2003). É sabido que o dogma central nem sempre está correto, porém para a nossa abordagem ele é suficiente.

A máquina celular responsável por produzir proteínas é denominada ribossomo. O ribossomo utiliza uma sequência de nucleotídeos (no caso, RNA) e traduz essa cadeia de caracteres para uma nova cadeia de caracteres de aminoácidos. Para o ribossomo não trabalhar diretamente com o DNA é necessário que seja utilizado uma cópia do mesmo. Devido a razões físicas da célula é mais fácil o ribossomo traduzir aminoácidos a partir de RNA. Assim, a célula transcreve os genes codificados em DNA para RNA (denominado RNA mensageiro) e os envia para o ribossomo.

O processo de transcrição de DNA para RNA mensageiro possui correspondência um por um entre a sequência de origem (DNA) e a sequência destino (RNA). A diferença básica é o uso do nucleotídeo uracila no lugar da timina. O próximo passo é o processo de tradução de RNA para aminoácidos. Esse processo não é tão simples, tendo em vista que o alfabeto do RNA é composto por 4 símbolos e o alfabeto dos aminoácidos por 20 símbolos. Nesse caso, não é possível fazer uma correspondência um por um entre a sequência de origem e a de destino. Dessa forma, a correspondência possível é utilizar 3 nucleotídeos para representar 1 aminoácido permitindo uma faixa de representação de 64 aminoácidos  $(4^3)$ .

Assim, todos os organismos na terra utilizam esse método para traduzir nucleotídeos para aminoácidos. É denominado *códon* o conjunto de 3 nucleotídeos que formam um

|   | A     | G     | С     | T     |  |

|---|-------|-------|-------|-------|--|

| A | AAA K | AGA R | ACA T | ATA I |  |

|   | AAG K | AGG R | ACG T | ATG M |  |

|   | AAC N | AGC S | ACC T | ATC I |  |

|   | AAT N | AGT S | ACT T | ATT I |  |

| G | GAA E | GGA G | GCA A | GTA V |  |

|   | GAG E | GGG G | GCG A | GTG V |  |

|   | GAC D | GGC G | GCC A | GTC V |  |

|   | GAT D | GGT G | GCT A | GTT V |  |

| С | CAA Q | CGA R | CCA P | CTA L |  |

|   | CAG Q | CGG R | CCG P | CTG L |  |

|   | CAC H | CGC R | CCC P | CTC L |  |

|   | CAT H | CGT R | CCT P | CTT L |  |

| T | TAA * | TGA * | TCA S | TTA L |  |

|   | TAG * | TGG W | TCG S | TTG L |  |

|   | TAC Y | TGC C | TCC S | TTC F |  |

|   | TAT Y | TGT C | TCT S | TTT F |  |

Tabela 2.1: O padrão utilizado pelo código genético

aminoácido. A Tabela 2.1 mostra como é feita essa tradução. É percebido que diferentes *códons* podem representar um mesmo aminoácido. O conjunto de aminoácidos formados a partir da tradução representam proteínas. Como dito anteriormente, as proteínas é que são as responsáveis por grande parte do trabalho realizado na célula - incluindo cópia de DNA, mover materiais para dentro da célula e comunicar com células vizinhas.

#### 2.3 Bancos de Dados Genéticos

O primeiro passo para qualquer análise genética é obter as sequências necessárias para o estudo. Todos os genomas sequenciados que foram objetos de publicações acadêmicas estão disponíveis na internet. As principais revistas e congressos científicos exigem que a sequência objeto do trabalho seja armazenada em alguma base de dados pública.

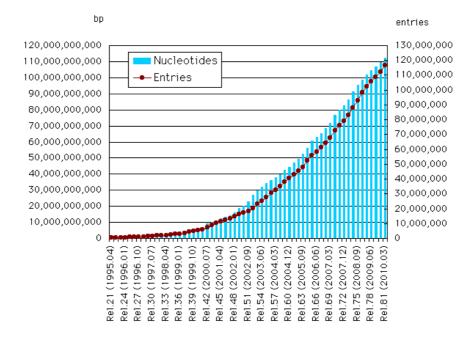

O principal agente responsável pela distribuição dessas base de dados (BD) é o consórcio formado pelos três maiores bancos de dados genéticos: a Base de Dados de DNA do Japão (DDBJ), o Laboratório Europeu de Biologia Molecular (EMBL) e o *GenBank* (financiado pelo governo dos Estados Unidos). Esses bancos são denominados bancos primários, pois são os responsáveis pelo armazenamento e distribuição de forma gratuita de todas as sequências públicas já mapeadas. O principal problema em relação à confiabilidade desses bancos consiste que as informações não são curadas, ou seja, as sequências armazenadas não são verificadas por um comitê para analisar a sua relevância. Em março de 2010, havia aproximadamente 120 bilhões de bases de nucleotídeos armazenadas nesses três bancos. A Figura 2.1 mostra o crescimento dos mesmos a partir de abril de 1995 até março de 2010. Ainda, segundo o relatório NCBI (2009) desde o seu nascimento em 1982 até abril de 2009 o número de bases tem dobrado a cada 18 meses.

Existem ainda outros bancos de dados públicos, denominados secundários, que deri-

Figura 2.1: Crescimento dos bancos de dados genético GenBank/EMBL/DDBJ (1995-2010)

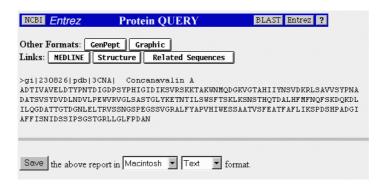

Figura 2.2: Exemplo do formato FASTA

vam dos primários. Basicamente eles se especializam em nichos e geralmente são curados. Como exemplo podemos citar o UniprotKB/Swiss-Prot, especializado em sequências de proteínas, possuindo todos os dados curados. Outro exemplo é o Prosite especializado em apontar domínios funcionais em uma proteína utilizando consensos armazenado em seu banco de dados. Por fim, o KEGG é um banco de dados secundário responsável por representações e mapas de vias metabólicas.

Existem muitos formatos utilizados para armazenar as sequências nesses bancos. Nenhum padrão foi criado, porém observa-se que praticamente todos os bancos públicos utilizam (além de seus próprios formatos) o formato FASTA. Esse é um formato muito simples e compacto para armazenar a informação biológica. A Figura 2.2 mostra um exemplo de uma sequência no formato FASTA. Observamos na primeira linha o caractere de maior (>) que simboliza o início da sequência seguido por algumas informações sobre a mesma. Logo após, a segunda linha, já inicia com a sequência propriamente dita. O caractere de fim de sequência é representado pelo fim do arquivo ou pelo início de uma nova sequência.

## 3 ALGORITMOS PARA ALINHAMENTO DE SEQUÊNCIAS

Nesse capítulo apresentamos alguns dos principais algoritmos utilizados para alinhamento de sequências biológicas. O desenvolvimento desses algoritmos foram obtidos em saltos lentos. Os principais resultados vieram com espaçamento, em geral, de uma década: distância Levenshtein na década de 60, alinhamento global Needleman-Wunsch em 70, alinhamento local Smith-Waterman em 80 e heurísticos no início dos anos 90.

Medir a similaridade entre duas sequências (DNA, RNA ou proteínas) é considerado o mais importante cálculo na genômica computacional e tem se tornado uma tarefa diária para biólogos (CRISTIANINI; HAHN, 2007). Existem diferentes tipos de alinhamentos, que serão discutidos nesse capítulo, mas o objetivo principal é determinar o quão semelhantes são as sequências envolvidas no alinhamento.

Consideramos dois tipos básicos de algoritmos de alinhamento: global e local. Podemos considerar que, se duas sequências possuem o mesmo ancestral, se espera que elas possuam muitos símbolos em comum. Assim, o alinhamento busca aproximar os símbolos das sequências analisadas. Permite-se inserir lacunas entre as duas sequências, denominadas ao longo desse trabalho de *gap*, como forma de representar resultados evolutivos de inserção ou remoção de genes - denominado *indel*. Assim em (3.1) mostramos um exemplo de alinhamento global e em (3.2) um exemplo de alinhamento local retirados de Ticona (2003).

Dadas as sequências:

$$A = \{G, A, A, G, G, A, T, T, A, G\}$$

$$B = \{G, A, T, C, G, G, A, G\}$$

Tem-se o seguinte alinhamento global:

$$G \quad A \quad A \quad G \quad G \quad A \quad T \quad T \quad A \quad G$$

$$| \quad | \quad | \quad | \quad | \quad | \quad | \quad G \quad A \quad T \quad C \quad G \quad G \quad A \quad G$$

Percebe-se que no alinhamento global é buscado o melhor alinhamento das sequên-

cias por todo o seu comprimento. Já o alinhamento local busca o melhor alinhamento em uma determinada parte da sequência. Definimos alinhamento ótimo como o alinhamento que resulta o maior escore final. O algoritmo que encontra o alinhamento global ótimo é o Needleman-Wunsch, apresentado em Wunsch (1970) e foi utilizado como inspiração para o desenvolvimento do algoritmo de alinhamento local ótimo Smith-Waterman. Esse, apresentado em Smith e Waterman (1981). No capítulo 3.2 detalhamos o funcionamento do algoritmo Smith-Waterman e apresentamos um exemplo de uso.

Existem muitas aplicações para o alinhamento de sequências. Por exemplo, partindo do princípio que é conhecida a função de uma proteína em um organismo se utiliza o alinhamento para buscar proteínas semelhantes e fazer inferências sobre o funcionamento dessas proteínas que ainda não se tem evidências experimentais. Denomina-se esse processo de predição de proteínas. Outra aplicação é a construção de árvores evolutivas (ou árvores filogenéticas) responsáveis por determinar a história evolutiva do gene, caracterizar ancestrais e caracterizar famílias gênicas e proteicas (JONES; PEVZNER, 2004). Nesse contexto, o alinhamento entre sequências é uma etapa importante no fluxo utilizado para a criação dessas árvores. Outro uso do alinhamento de sequências é na própria montagem da sequência. Uma das etapas do fluxo, exige que seja realizada a comparação entre duas sequências para fazer uma máscara e descartar parte da sequência que não é necessária.

### 3.1 Distância Levenshtein

Em 1966, Vladimir Levenshtein introduziu o conceito de distância de edição entre duas cadeias de caracteres como o valor mínimo de operações necessárias para transformar uma das cadeias na outra (JONES; PEVZNER, 2004). Utiliza-se três operações básicas para se calcular a distância de edição: inserir, apagar e substituir. Usualmente o custo de substituir um caractere em outro é fixo em 2 e o custo de apagar e inserir é a metade deste. A maneira mais comum de implementar esse algoritmo é utilizando programação dinâmica, técnica que consiste em dividir uma tarefa complexa em pequenas tarefas menores (SACCONE; PESOLE, 2003). Podemos dividir o algoritmo em duas etapas. A primeira é responsável por buscar o valor da distância de edição e a segunda pelo alinhamento das duas sequências. Em (3.3) mostramos a distância de edição entre duas cadeias de caracteres e o alinhamento. A seguir explicaremos melhor como é calculada cada etapa do algoritmo.

Dadas as sequências:

$$A = \{A, T, A, G, C\}$$

$$B = \{C, A, T, A, G\}$$

Tem-se o seguinte alinhamento:

$$A T A G C$$

$$A T A G C$$

$$C A T A G$$

Distância Levenshtein = 2:

Consideramos as duas sequências de entrada como vetores de caracteres. Assim  $A = \{a_1, a_2, a_3, a_m\}$  e  $B = \{b_1, b_2, b_3, b_n\}$ , denominados, respectivamente, de alvo e de busca. Inicia-se o cálculo da distância de edição inicializando uma matriz h(i,j) de tamanho (m+1)

| *              | * | C | A | T | A | G |

|----------------|---|---|---|---|---|---|

| *              | 0 | 1 | 2 | 3 | 4 | 5 |

| A              | 1 | 2 | 1 | 2 | 3 | 4 |

| T              | 2 | 3 | 2 | 1 | 2 | 3 |

| A              | 3 | 4 | 3 | 2 | 1 | 2 |

| $\overline{G}$ | 4 | 5 | 4 | 3 | 2 | 1 |

| C              | 5 | 4 | 5 | 4 | 3 | 2 |

Tabela 3.1: Exemplo do algoritmo distância Levenshtein

1)\*(n+1). A primeira linha e a primeira coluna da matriz é inicializada utilizando a condição inicial h(0,1)=1, h(0,2)=2 até h(0,j)=m e h(1,0)=1, h(2,0)=2 até h(1,j)=i. Observa-se que é inserido um elemento nulo em h(0,0)=0 que será fixo durante todo o cálculo, juntamente com a primeira coluna e a primeira linha da matriz. Assim, para cada elemento da matriz que não sejam os elementos fixos é calculado o valor de d conforme (3.4). Utiliza-se sempre as posições noroeste (a), norte (b) e oeste (c) de cada elemento da matriz para efetuar esse cálculo, isto é h(i-1,j-1), h(i-1,j) e h(i,j-1). O campo sub é igual a 2 e os campos ins e del iguais a 1.

Por exemplo, vamos considerar o cálculo do primeiro elemento h(1,1) da matriz mostrada na Tabela 3.1. Observamos que os valores utilizados no cálculo para o elemento noroeste é h(i-1,0)=0, para o norte é h(i-1,j)=1 e para o oeste é h(i,j-1)=1. Analisando a equação mostrada em (3.4), percebemos que o primeiro termo para esse exemplo é igual a 2 (já que o caractere de busca é diferente do caractere de alvo). Analogamente, o segundo e o terceiro termo também são iguais a 2. Assim, o mínimo entre os três termos da equação calculados será o valor final d da matriz h(i,j).

Por fim, um apontador registra de qual dos termos da matriz (noroeste, norte ou oeste) que resultou o valor mínimo e o próximo elemento da matriz é calculado. O deslocamento da matriz h(i,j) pode ser tanto na horizontal quanto na vertical. Discutimos no capítulo 5.1 o uso da técnica *wavefront* que permite paralelizar o cálculo dos elementos da matriz. O último termo da matriz, h(m,n), é o valor da distância de edição final. Para realizar o alinhamento, se percorre o caminho de cada apontador a partir do último até o primeiro termo. O caminho do alinhamento é mostrado pelos elementos achurados na Tabela 3.1.

$$d = min \begin{cases} \begin{cases} a & if (A(i) = B(j)) \\ a + sub & if (A(i) \neq B(j)) \\ b + ins \\ c + del \end{cases}$$

(3.4)

Essa técnica é bastante utilizada para buscar similaridades entre sequências biológicas. Ainda, o algoritmo Smith-Waterman que será descrito no capítulo 3.2, pode ser considerado um caso geral para a distância de edição, pois possibilita adicionar custos nas operações dependendo de sua localização utilizando as matrizes de substituição.

Existem muitas aplicações para o algoritmo Levenshtein, além de buscar similaridades entre sequências de DNA e proteínas. Grande parte das ferramentas de busca *web* utilizam a distância Levenshtein para sugerir palavras para a busca, quando acreditam que essa tenha sido digitada incorretamente. Outros usos para esse algoritmo são reco-

nhecimento automático de fala, filtros contra *spam* e ferramentas para tradução de textos (WOREK, 2002).

### 3.2 Smith-Waterman

O algoritmo Smith-Waterman foi desenvolvido por T.F. Smith e M.S Waterman, apresentado no trabalho Smith e Waterman (1981), para calcular o alinhamento ótimo entre duas sequências de caracteres. O algoritmo utiliza como entradas uma sequência denominada alvo e outra denominada busca e encontra o alinhamento ótimo entre elas. É considerada a técnica mais popular utilizada para alinhar sequências, pois permite buscar similaridades em partes da sequência - diferente do alinhamento global que busca sempre alinhar a sequência como um todo. Em relação a métodos heurísticos como o Blast (Basic Local Alignment Search Tool) e o FASTA, possui como vantagens retornar sempre o alinhamento ótimo. Em contrapartida, possui maior complexidade computacional - na ordem de O(m\*n).

Consideramos as duas sequências de entrada como vetores de caracteres. Assim  $A = \{a_1, a_2, a_3, a_m\}$  e  $B = \{b_1, b_2, b_3, b_n\}$ , denominados, respectivamente, alvo e busca. Essas sequências podem representar DNA ou RNA (alfabeto com 4 caracteres) ou proteínas (alfabeto com 20 caracteres). O algoritmo possui as condições iniciais mostradas em (3.5) e (3.6) e constrói uma matriz de similaridades h(i,j) utilizando as equações mostradas em (3.7), (3.8) e (3.9).

$$h(i,0) = e(i,0) = f(i,0) = 0 \ 0 < i < m$$

(3.5)

Na equação (3.5) observamos que são inicializadas três matrizes m\*n, onde m é o número de elementos no vetor A e n o número de elementos no vetor B. Observa-se que a primeira linha das matrizes é preenchida com 0.

$$h(0,j) = e(0,j) = f(0,j) = 0 \ 0 \le j \le n$$

(3.6)

Analogamente, a equação 3.6 inicializa a primeira coluna das três matrizes com 0.

A equação (3.7) busca calcular o escore máximo entre as duas sequências de caracteres. O primeiro termo da equação garante que a matriz somente terá valores positivos. O segundo termo soma ao elemento noroeste da posição h(i,j) o valor de uma matriz de substituição - representada por s(i,j). A matriz de substituição receberá como entrada os elementos dos vetores A e B que estão sendo comparados. Caso esses elementos sejam iguais, o resultado da matriz será um valor positivo e consideramos que houve um match. Caso sejam distintos, o resultado da matriz será um valor negativo e consideramos que houve um mismatch. Essas matrizes são utilizadas para melhorar a qualidade dos alinhamentos com base em fatores biológicos e probabilísticos (HENIKOFF; HENIKOFF, 1992). A Figura 3.1 mostra a matriz de substituição Blosum62. Observamos na figura que a matriz retorna um valor para cada possibilidade de comparação, sempre retornando positivo quando ocorre um match e negativo quando ocorre um mismatch.

$$h(i,j) = \max \begin{cases} 0 \\ h(i-1,j-1) + s(i,j) \\ e(i,j) \\ f(i,j) \end{cases} \quad 1 \le i \le n \text{ and } 1 \le j \le m$$

(3.7)

O terceiro termo da equação (3.7) é calculado na equação (3.8). Observamos que nessa equação, no primeiro termo, é o elemento norte da posição h(i,j) que é subtraído por uma penalidade denominada  $gap\ open$ . Nesse caso, se considera que houve um mismatch entre as sequências e se insere um gap em uma das sequências para melhor alinhá-la. O segundo termo calcula outra penalidade denominada  $gap\ extend$ , caso já tenha sido aberto um gap anteriormente - utiliza a matriz e(i,j) que é responsável por armazenar os gaps que foram abertos e os que foram prolongados. A equação (3.9) é análoga, porém os termos analisados estão na posição oeste de h(i,j), representam o quarto termo da equação (3.7), e utilizam a matriz de gap relacionada com esse termo, denominada f(i,j).

$$e(i,j) = \max \begin{cases} h(i-1,j) - g_o \\ e(i-1,j) - g_e \end{cases} \quad 1 \le i \le n \text{ and } 1 \le j \le m$$

(3.8)

$$f(i,j) = \max \begin{cases} h(i,j-1) - g_o \\ f(i,j-1) - g_e \end{cases} \quad 1 \le i \le n \text{ and } 1 \le j \le m$$

(3.9)

Dentre todos os termos calculados na equação (3.7) apenas o que possuir maior valor será armazenado na matriz de similaridades h(i,j). Analogamente, na equação (3.8) o que possuir maior valor será armazenado na matriz de gap e(i,j) e na equação 3.9 o que possuir maior valor será armazenado na matriz f(i,j). O maior valor da matriz h(i,j) será o escore máximo (ou o escore de similaridade) entre as duas sequências. Quanto maior esse valor mais semelhantes são as sequências.

A próxima operação a ser realizada após se obter o escore máximo é denominada *trace-back*. A mesma busca, a partir do escore máximo, o caminho de volta, ou seja, de quais elementos aquele valor se originou. Assim, se verifica qual elemento (noroeste, norte ou oeste) originou o elemento atual e se retorna para esse. Realiza-se esse procedimento até se encontrar um valor nulo. A posição das sequências nos vetores *A* e *B* que fazem parte desse caminho formam o alinhamento ótimo entre as duas sequências.

Gotoh (1982) introduziu dois conceitos distintos para análise do algoritmo Smith-Waterman. O primeiro, demonstrado nas equações (3.7), (3.8) e (3.9) é o caso geral, denominado *affine gap*, utilizado quando as penalidades de *gap open* e *gap extend* são diferentes entre si. Esse modo é considerado biologicamente mais preciso, porém observando as equações percebemos que utiliza mais recursos computacionais que no caso onde os valores de *gap open* e *gap extend* são iguais - denominado *linear gap*. Para esse caso, podemos simplificar as equações (3.7), (3.8) e (3.9) para a equação (3.10) sem mais necessitarmos de matrizes de *gap* para registrar se um *gap* foi aberto ou se foi prolongado.

$$h(i,j) = \max \begin{cases} 0 \\ h(i-1,j-1) + s(i,j) \\ h(i-1,j) + g_o \\ f(i,j-1) + g_o \end{cases} \quad 1 \le i \le n \text{ and } 1 \le j \le m$$

(3.10)

```

Arg

Gln

- 3

Glu

Gly

His

-2 -3 -4 -1 -2 -3

Leu

0 -1 -3

Lys

Met

-1 -2 -3 -1 0 -2 -3 -2 1

Phe

- 3

0 -1 0 0 0 -1 -2 -1 -1 -1 -1 -2 -2 -1

Ser

-1 -2

- 2

Thr

Trp

-3 -3 -4 -4 -2 -2 -3 -2 -2 -3

- 2

- 2

-3 -3 -1

Ala Arg Asn Asp Cys Gln Glu Gly His Ile Leu Lys Met Phe Pro Ser Thr Trp Tyr Val

```

Figura 3.1: Matriz de substituição Blosum62

| *              | * | A | T  | C  | G  | T  | G  |

|----------------|---|---|----|----|----|----|----|

| *              | 0 | 0 | 0  | 0  | 0  | 0  | 0  |

| G              | 0 | 0 | 0  | 0  | 10 | 5  | 10 |

| T              | 0 | 0 | 10 | 5  | 5  | 20 | 5  |

| C              | 0 | 0 | 5  | 20 | 15 | 15 | 15 |

| T              | 0 | 0 | 10 | 15 | 15 | 25 | 20 |

| $\overline{G}$ | 0 | 0 | 5  | 14 | 25 | 20 | 35 |

Tabela 3.2: Exemplo do algoritmo Smith-Waterman

A Tabela 3.2 mostra um exemplo de matriz de similaridades h(i,j). Para esse caso se utilizou as sequências de nucleotídeos  $A = \{A, T, C, G, T, G\}$  e  $B = \{G, T, C, T, G\}$ . Utilizamos o algoritmo com affine gap, onde o valor  $g_o = -5$  e  $g_e = -1$ . Para simplificar o exemplo criamos uma matriz de substituição para nucleotídeos onde um match retorna o valor 10 e um mismatch o valor -5. O caminho em destaque representa o trace-back.

## 3.3 Alinhamento Múltiplo

O alinhamento par a par, descrito nos capítulos 3.1 e 3.2 é geralmente o primeiro passo para determinar a função biológica das sequências. Entretanto, alinhar simultaneamente múltiplas sequências pode revelar uma grande riqueza biológica de informação e é utilizado em muitas análises avançadas em biologia (GUSFIELD, 1997). Em (3.11) podemos visualizar um exemplo com o alinhamento (global) múltiplo entre três sequências hipotéticas.

Dadas as sequências:

$$A = \{V, I, V, A, L, A, S, V, E, G, A, S\}$$

$$B = \{V, I, V, A, D, A, V, I, S\}$$

$$C = \{V, I, V, A, D, A, L, L, A, S\}$$

Tem-se o seguinte alinhamento múltiplo:

$$V \quad I \quad V \quad A \quad L \quad A \quad S \quad V \quad E \quad G \quad A \quad S$$

$$V \quad I \quad V \quad A \quad D \quad A \quad L \quad V \quad I \quad - \quad S$$

$$V \quad I \quad V \quad A \quad D \quad A \quad L \quad L \quad A \quad - \quad S$$

Um algoritmo muito usado para alinhamento múltiplo é o Clustal, atualmente denominado de ClustalW. A ideia básica do Clustal é quebrar o problema de alinhamento múltiplo em múltiplos problemas de alinhamento par a par (SACCONE; PESOLE, 2003). Na primeira etapa do algoritmo são lidas todas as sequências de entrada e agrupadas par a par cobrindo todas as possibilidades de alinhamento (excluindo os idênticos). Após os pares terem sido gerados é calculado o alinhamento global usando o algoritmo de Needleman-Wunsch para cada par. As últimas etapas do algoritmo constroem uma árvore de similaridade entre os escores calculado pelo Needleman-Wunsch de cada par e utiliza essa árvore para gerar o alinhamento global.

Alguns trabalhos, como Oliver et al. (2005b), Lin et al. (2005), tem explorado acelerar o clustal utilizando uma arquitetura dedicada em hardware que implementa o Needleman-Wunsch ou o Smith-Waterman. Esses trabalhos reportam que o alinhamento par a par usando o Needleman-Wunsch no algoritmo Clustal representa 90% do tempo de processamento. Assim, uma abordagem explorada para acelerar esse algoritmo é remover do software do ClustalW a etapa que realiza os alinhamentos par a par e calculá-los utilizando uma arquitetura dedicada.

#### 3.4 Métodos Heurísticos

Os métodos heurísticos para analisar sequências biológicas surgiram no fim da década de 80. Como o número de sequências mapeadas estava aumentando nos bancos de dados públicos, o uso de técnicas de programação dinâmica (como os algoritmos citados nos capítulos 3.1 e 3.2) tornava-se impraticável devido a complexidade na ordem de O(n\*m). A solução encontrada foi o uso de métodos heurísticos - métodos rápidos que não garantem calcular a solução ótima. O mais popular desses métodos já desenvolvidos é o Blast.

O Blast é uma família de algoritmos desenvolvidos pelo NCBI (*National Center for Biotechnology Information*), que são os mesmos administradores do *GenBank*. Assim, uma configuração típica do Blast é buscar similaridades entre uma sequência específica e um banco de dados. Usar o Smith-Waterman para esse tipo de busca utilizando bancos de dados muito grandes é impraticável. No capítulo 6.3 mostramos alguns teste desse tipo utilizando o banco de dados *Swiss-Prot* e reportamos os tempos.

Com o crescente aumento no tamanho dos bancos de dados biológicos, mesmo o algoritmo heurístico do blast tem se tornado bastante lento para algumas aplicações. Assim, algumas arquiteturas em hardware dedicado exploram a aceleração do algoritmo. Uma dessas arquiteturas, apresentadas por Park et al. (2009) sugere manter o algoritmo blast em software filtrando as entradas do algoritmo para diminuir o tamanho do banco de dados. O filtro é projetado em hardware e utiliza o algoritmo Smith-Waterman como

unidade central do sistema. Os autores relatam uma aceleração de 6 vezes na execução do Blast comparado com a versão sem o filtro.

### 4 ARQUITETURAS ESTUDADAS

Este capítulo tem o objetivo de descrever algumas arquiteturas em hardware encontradas na literatura para o cálculo do Smith-Waterman. Encontramos diferentes abordagens para o cálculo da matriz dinâmica utilizada pelo algoritmo. A maioria das arquiteturas estudadas partem da premissa de utilizar múltiplas unidades de processamento para calcular as células da matriz de similaridade. Apesar de termos estudado também as arquiteturas recentemente publicadas Lloyd e Snell (2008), Boukerche et al. (2010), para algoritmos que também calculam alinhamento de sequências buscamos analisar mais detalhadamente as que implementam o Smith-Waterman com *affine gap* e a distância Levenshtein.

Uma observação importante, que muitas vezes não é considerada nas arquiteturas apresentadas é em relação ao tipo de dados de entrada que podem ser processados. Especificadamente, o DNA possui quatro caracteres para codificar a timina, guanina, citosina e adenina (T, G, C e A). Porém, as proteínas são produzidas por 20 diferentes aminoácidos. Assim, é necessário apenas dois bits para representar os 4 caracteres que codificam o DNA e 5 bits para os aminoácidos que codificam as proteínas. O valor de saída das arquiteturas é o escore máximo encontrado e, em alguns casos, informação sobre em qual elemento da matriz de similaridade ocorreu o valor máximo (para posterior alinhamento em software).

Adota-se como unidade de medida de desempenho o CUPS (*Cell Updates Per Second*). Para calcular o CUPS se multiplica a frequência de operação pelo número de UPs (Unidades de Processamento) do circuito. Em (4.1) é mostrada a fórmula para obter o CUPS. Outros critérios adotados além do desempenho são o número de unidades de processamento em paralelo e o tamanho máximo de caracteres de uma sequência possível de ser calculado.

$$CUPS = freq_{clock} * UP (4.1)$$

## 4.1 A Run-Time Reconfigurable System for Gene-Sequence Searching

Nesse artigo Puttegowda et al. (2003) apresentam uma arquitetura para calcular a distância Levenshtein utilizando sequências de nucleotídeos. Os autores exploram a reconfiguração em tempo de execução do dispositivo FPGA para reduzir o tamanho da unidade de processamento. Assim, é mantido fixo (*hardcode*) o valor de *match* e *mismatch* e também a própria sequência de alvo. Dessa forma é possível integrar 7000 UPs em um dispositivo FPGA XC2V6000, onde uma UP ocupa 4 slices. O desempenho relatado é de

1260 GCUPS e frequência de operação de 180 MHz.

Uma característica interessante do trabalho é a divisão do array sistólico em 4 *cores* distintos de 1750 UPs. Assim, é possível comparar até 4 sequências em paralelo que possuam esse tamanho. O autor não implementa o particionamento de sequências, apenas cita poder conectar várias placas com a arquitetura proposta quando for necessário comparar sequências grandes. O sistema é implementado em uma placa com barramento PCI (*Peripheral Component Interconnect*) e acesso a memória RAM (*Random-access memory*) externa. Em Guccione e Keller (2002) é mostrada uma arquitetura bastante semelhante a esta, utilizando a ferramenta JBITS da empresa Xilinx para fazer a reconfiguração do dispositivo.

### 4.2 A Smith-Waterman Systolic Cell

Nesse artigo Yu et al. (2003) apresentam uma arquitetura que implementa a distância Levenshtein para comparar nucleotídeos. O autor utiliza um sistema com memória de entrada (8 bytes) e memória de saída (2 bytes) e 4032 unidades de processamento em um array sistólico. A frequência obtida para um FPGA XCV1000E-6 é de 202 MHz e o desempenho de 814 GCUPS. A principal contribuição dos autores nesse trabalho foi alocar uma UP em apenas 3 slices. Para isso utilizaram macros do FPGA da Xilinx que permite que os recursos dos slices sejam configurados manualmente no código HDL (Descrição em Linguagem de Hardware). Eles também compartilharam alguns recursos entre duas UPs, fazendo com que a unidade mínima da arquitetura seja duas UPs que ocupam 6 slices. Não foi utilizada reconfiguração do dispositivo em tempo de execução. Os autores não projetaram o particionamento da sequência.

## 4.3 An Efficient Digital Circuit for Implementing Sequence Alignment Algorithn in an Extended Processor

Nesse trabalho Kundeti et al. (2008) apresentam uma nova arquitetura para calcular a distância Levenshtein. O objetivo dos autores é projetar um co-processador, que possa ser embarcado a um processador de propósito geral e acessado utilizando o conjunto de instrução (com modificações) do mesmo. Os autores relatam alguns dos trabalhos que implementam a distância de edição utilizando arrays sistólicos, tais como Lipton e Lopresti (1985). Porém, consideram que esse tipo de solução possui muitas desvantagens em relação ao tamanho máximo de sequências que podem ser comparadas e também, no caso de sequências menores, o consumo de potência do array quando este é sub-utilizado. Assim, mesmo oferecendo um desempenho inferior, os autores apresentam uma arquitetura serial (com a computação baseada em um registrador de *shift* e alguns somadores) capaz de calcular um bloco de tamanho fixo (denominado t) durante cada chamada da instrução projetada para o cálculo da distância de edição. Desse modo, a complexidade do cálculo do algoritmo que em um processador de propósito geral é de O(m\*n), passa para O(m/t\*n/t).

A arquitetura foi prototipada utilizando a tecnologia ASIC (TSMC 0.13 um), em Verilog e utilizando os softwares Encounter da Cadence para síntese lógica e Synopsys VCS para verificação do *netlist* gerado. O trabalho não relata se a síntese física foi realizada e, desse modo, se conclui que os resultados apresentados são referentes às estimativas de

desempenho do Encounter após a síntese lógica. A frequência máxima de operação (com o *slack* igual a 0) é de 1 GHz utilizando 460 *gates*. Os autores compararam o desempenho dessa arquitetura com um processador de propósito geral Pentium 2.4 GHz. Para diferentes valores de *t* (*t*=8, 16, 32) o desempenho foi de, respectivamente, 3.77, 4.33 e 5.50 vezes maior. Por meio da tabela de resultados apresentada pelos autores, inferimos que no melhor caso da arquitetura é possível comparar até 15 caracteres por ciclo, resultando em um desempenho de 15 GCPUS.

Apesar dos resultados serem significativos quando comparados com uma arquitetura de propósito geral, apresenta um desempenho bastante inferior que as que utilizam array sistólico. Isso é devido ao grau de paralelismo alcançado, que nesse caso altera a complexidade do algoritmo para O(m+n-1).

### 4.4 Biological Information Signal Processor

Nesse trabalho Chow et al. (1991) relatam um dos primeiros esforços para projetar um sistema em hardware dedicado para o cálculo do Smith-Waterman. A arquitetura projetada é bastante flexível e permite que várias opções sejam configuradas pelo usuário. Assim, é possível escolher entre alinhamento local ou global, diferentes valores de *gap* e tipos de matrizes de substituição. Ainda, permite calcular o Smith-Waterman para proteínas e nucleotídeos para sequências de até 4194304 caracteres.

O projeto integra 16 unidades de processamento com precisão máxima na pontuação do escore de 16 bits. O autor projetou um ASIC utilizando tecnologia de 1 mm. As diversas opções de configuração do chip aumentaram significativamente a área da unidade de processamento e a complexidade do controle. Os autores relatam uma aceleração de 445 vezes em relação a um supercomputador Cray 2 de US\$ 20M (consideram como US\$ 50K o custo do seu sistema). A área do circuito é de 100 mm2 e a frequência de operação de 12.5 MHz. Os autores apresentam como resultado de desempenho o valor de 0.2 GCUPS.

## 4.5 SWASAD: An ASIC Design for High Speed DNA Sequence Matching

Em Han e Parameswaran (2002) é mostrado o projeto de um circuito ASIC para calcular o Smith-Waterman. Obteve-se uma frequência de 50 MHz, porém o gargalo do sistema foi considerado o barramento PCI. Assim, o projeto seria capaz de operar em uma frequência muito mais alta caso não houvesse as interconexões com esse barramento. O fluxo de projeto adotado utilizou a ferramenta Leonardo Spectrum para a síntese lógica com tecnologia AMI 0.5 um. A síntese física foi realizada utilizando a ferramenta ICStation da empresa Mentor Graphics.

O barramento interno da unidade de processamento é de 8 bits que pode ser expandido para 16 bits utilizando uma lógica de *overflow* que reduz as UPs do circuito. Sem *overflow* o escore máximo que pode ser obtido é de apenas 256. Percebemos que o escore máximo é determinado pelo tipo de pontuação aplicada. Porém, consideramos baixo o valor de 256 para um uso prático do chip. O autor não analisa o tempo gasto para tratar o *overflow*.

Os autores mostram que, ao invés de utilizar comparadores na unidade de processa-

mento (são necessários 3), o uso de subtratores é mais eficiente. Eles realizaram comparações do impacto de projetar esse dispositivo com comparadores e com subtratores e, segundo eles, os subtratores ocupam menor área e possuem menor atraso.

O SWASAD possui 64 unidades de processamento por chip. O esforço dos projetistas foi de integrar o maior número de unidades possíveis. O projeto permite diferentes pontuações para *match* e *mismatch* (mas não utiliza matrizes de substituição) e para as pontuações de *gap open* e *gap extend*. Os autores mostram como resultado o desempenho de 3.2 GCUPS. Na conclusão do artigo, os autores relatam que poderiam utilizar 1024 unidades de processamento se o projeto utilizasse uma tecnologia de 100 nm. O circuito utiliza como entradas apenas sequências de nucleotídeos.

# 4.6 Hyper Customized Processors for Bio-Sequence Database Scanning on FPGAs

Nesse artigo Oliver et al. (2005a) apresentam algumas arquiteturas para calcular o Smith-Waterman para comparação de proteínas (não é citado o uso da arquitetura para DNA/RNA). Os autores utilizam uma arquitetura básica de array sistólico e projetam duas unidades de processamentos distintas: uma para usar o Smith-Waterman com *affine gap* e outra com *linear gap*. Utilizam 16 bits para representar os dados na matriz.

Os autores demonstram preocupação com a questão do particionamento de sequências. Afirmam que, na prática, dificilmente as sequências cabem na estrutura do array sistólico. Assim, a metodologia utilizada foi quebrar a sequência em um conjunto finito de pedaços. O autores implementaram a quebra de sequências utilizando projetos distintos para cada tipo de uso do algoritmo. Os autores armazenam nas unidades de processamento apenas a coluna da matriz de substituição correspondente à sequência alvo armazenada na UP. Assim, é consumido alguns ciclos toda vez que uma sequência alvo é armazenada para carregar as matrizes de substituição em cada UP. Na quebra das sequências esses ciclos são novamente consumidos, pois com novas sequências novas matrizes de substituição devem ser carregadas.

A primeira arquitetura projetada calcula *linear gap* e permite particionar a sequência até 3 vezes. Esse projeto utilizou 252 unidades de processamento operando a 55 MHz e pode comparar sequências com tamanho máximo de 756 (com desempenho de 13.9 GCUPS). A segunda arquitetura, análoga a primeira, permite particionar a sequência em até 12 vezes e comparar sequências com tamanho máximo de 2016 caracteres (desempenho de 9.2 GCUPS).

A terceira arquitetura projetada calcula *affine gap* (o que torna a unidade de processamento mais complexa). Na primeira abordagem, permite quebrar a sequência em até 3 vezes e 168 unidades de processamento (operando a 45 MHz) podem comparar sequência com no máximo 504 caracteres (7.6 GCUPS de desempenho). A quarta arquitetura, permite quebrar em 12 vezes a sequência - 119 unidades de processamento para comparar sequências com até 1428 caracteres (5.2 GCUPS).

O dispositivo alvo foi o FPGA Virtex-2 XC2V6000 da empresa Xilinx. Não são mostrados detalhes da síntese, porém é comparado o desempenho da arquitetura com o desempenho de um Pentium IV para a mesma tarefa (é obtida uma aceleração de 170 vezes para *linear gap* e 125 para *affine gap*). O autor relata que mesmo na arquitetura

de *affine gap* a estratégia utilizada foi criar diversos projetos para os diferentes valores de *gap* (tornando esses valores constantes em cada arquitetura).

## 4.7 A Highly Parameterized and Efficient FPGA-Based Skeleton for Pairwise Biological Sequence Alignment

Nesse trabalho Benkrid et al. (2009) apresentam uma arquitetura que permite alto grau de parametrização em tempo de projeto. Isso significa que o código, desenvolvido em Handel-C, permite que diversos fatores relacionados a arquitetura possam ser facilmente configurados. Os autores defendem a ideia que o uso de linguagem de síntese de alto nível (Handel-C, System C, System Verilog etc..) diminuem o abismo que existe entre os profissionais de bioinformática e os projetistas de hardware. Assim, como diretiva de projeto os autores optaram por desenvolver o hardware como se estivem desenvolvendo software, mesmo sabendo que perderiam em desempenho. O resultado é uma arquitetura que permite ser implementada em qualquer dispositivo FPGA e (segundo autor) ASIC.

Entre os parâmetros que podem ser alterados em tempo de projeto destacamos o tipo de sequência (proteína, RNA ou DNA), o tipo de penalidade (affine ou linear gap), o tamanho máximo da sequência comparada e o tipo de algoritmo (Smith-Waterman ou Needleman-Wunsch). A ideia é ter um banco de dados com diversas dessas configurações sintetizadas e carregar no dispositivo FPGA o projeto que melhor se adeque com a necessidade do usuário.

Os autores também destacam a importância do particionamento de sequências no array sistólico. Os autores apresentam uma arquitetura que utiliza uma FIFO (*First In First Out*) na saída da última unidade de processamento, conforme a apresentada em Moldovan e Fortes (1986). Porém nenhum detalhe sobre essa implementação é apresentada, nem em relação ao tamanho máximo de sequências que é possível comparar.

Por fim, os autores apresentam resultados da implementação da arquitetura em uma placa Alpha Data com FPGA Virtex-2 XC2VP100-6. Utilizaram a matriz de substituição Blosum50 e compararam 288 sequências de proteína com tamanho médio de 288 caracteres. O número de unidades de processamento desse experimento foi de 135 (operando a 40 MHz) e o cálculo foi finalizada em 88 ms com um tempo inicial de configuração do dispositivo de 244 us.

Os autores ainda apresentam o resultado de desempenho de diversas configurações de sua arquitetura básica. A performance em GCUPS varia de 4 a 12, o número de unidades de processamento de 100 a 250 e a frequência de 40 a 60 MHz. Basicamente as diferenças são em relação ao tipo de pontuação *affine* ou *linear gap* e número de bits para representar os dados na matriz (o melhor resultado, 252 UP com GCUPS 12.02 utiliza 10 bits). Os demais resultados utilizam 16 bits.

# 4.8 High-Speed Implementation of Smith-Waterman Algorithm for DNA Sequence Scanning in VLSI

A ideia principal do trabalho de Cheng e Parhi (2008) é diminuir o tempo de computação do array sistólico. Não é mostrado no trabalho o projeto de uma arquitetura completa, capaz de receber sequências em uma memória de entrada, compará-las e enviá-las para

uma memória de saída. Os autores se dedicaram a projetar unidades de processamento que pudessem reduzir o processamento do array sistólico. Para isso eles utilizam como premissa aumentar o *throughput* do sistema, o que significa fazer com que as unidades de processamento calculem mais de uma entrada por ciclo de *clock*. Considerando o número de entradas por unidade de processamento sendo J, os autores pretendem diminuir a complexidade do algoritmo de O(m+n-1) para O(m+(n-1/J)). Onde m é o número de caracteres da sequência alvo e n o número de caracteres da sequência de busca. Evidentemente que essa abordagem é válida somente para comparações onde a sequência de busca são bem maiores que as sequências de alvo.

No trabalho os autores mostram diagramas de blocos das unidades de processamento para calcular affine e linear gap. Projetaram também unidades de processamento recebendo 2 sequências de busca por ciclo de *clock* e 3 sequências de busca por ciclo de *clock*. Os autores utilizaram técnicas de pipeline, para não aumentar o caminho crítico da unidade de processamento e também otimizar os recursos de hardware (reduzir a área). Dessa forma os autores comparam o resultado de sua unidade de processamento com a projetada por Oliver et al. (2005a), utilizando o mesmo dispositivo Virtex II VC2V6000. Eles alcançaram a mesma frequência de operação (55 MHz), porém compararam 3 sequências de busca no mesmo instante de clock (o outro trabalho compara 1 sequência por instante de *clock*). Eles não mostram nenhum detalhe de sua arquitetura: número de unidades de processamento, número de bits para representar a matriz e tamanho máximo de sequências comparadas. Relatam, porém, na conclusão do paper que a principal desvantagem de sua arquitetura é que o aumento, em área, da unidade de processamento é maior que J vezes em relação à área da unidade de processamento de Oliver et al. (2005a). Isso demonstra que para processar 3 sequências de busca no mesmo instante de clock eles utilizam uma área de unidade de processamento mais de 3 vezes maior que a utilizada por Oliver et al. (2005a). Percebemos, com isso, que a principal contribuição apresentada por essa arquitetura é quando se compara sequências alvo pequenas e fixas com um banco de dados de seguências grandes.

## 4.9 Differential Scoring for Systolic Sequence Alignment

Nesse trabalho Serna (2007) apresentam uma arquitetura de array sistólico que modifica o modo como as pontuações de *match* e *gap* são realizadas. Os autores afirmam que o tamanho em bits utilizado para representar a matriz de similaridade e o valor de escore máximo estão diretamente relacionados com a complexidade do array sistólico. Assim, é mostrado uma nova maneira de se calcular as penalidades do algoritmo Smith-Watreman. Os autores utilizam o conceito de *affine gap* e *linear gap* porém modificam a forma como é realizada a pontuação usando para isso o conceito de agrupar a pontuação de células vizinhas. Dessa forma, eles exemplificma que para alinhar sequências de tamanho (10<sup>6</sup>), com penalidades menores que 4 bits são necessários 22 bits para representar os escores na matriz de similaridades. Porém, utilizando a técnica apresentada por eles são necessários 4 bits - o que representa uma redução de 82%. Isso reduz bastante todo o sistema, tamanho de memória, unidades de processamento e frequência de operação.

A principal desvantagem da arquitetura apresentada é não calcular o algoritmo Smith-Waterman em sua concepção original, conforme detalhado em Smith e Waterman (1981), e amplamente utilizado por biólogos. Dessa forma, mesmo com a significativa redução do hardware, é difícil comparar essa arquitetura com as demais por não calcular o mesmo

algoritmo (e sim uma variação do mesmo). Os autores relataram que prototiparam o circuito utilizando o dispositivo FPGA Spartan-3 XC3S200 da empresa Xilinx e obtiveram frequência de 100 Mhz. Porém não é relatado mais nenhum detalhe do protótipo - tamanho máximo de sequências, número de unidades de processamento.

## 4.10 Acceleration of Smith-Waterman Using Recursive Variable Expansion

Nesse artigo não é apresentada nenhuma implementação, porém uma nova abordagem em hardware para aumentar o desempenho do algoritmo Smith-Waterman. A ideia principal desse trabalho Nawaz et al. (2008) é reduzir o tempo de computação do array sistólico - semelhante ao de Cheng e Parhi (2008). Porém ao invés de utilizar *pipeline* na unidade de processamento os autores optaram por utilizar uma técnica denominada de *recursive variable expansion*. Basicamente, transformam as 3 equações básicas do algoritmo Smith-Waterman em 8 equações para que possa haver um maior paralelismo no array sistólico. Utilizando essa técnica, demonstraram que 2 unidades de processamento vizinhas podem receber 2 sequências de busca para serem comparadas. Como as dependências foram removidas, o vetor *wavefront* se desloca em blocos de *2X2* nas unidades de processamento, com exceção das bordas onde é realizado um tratamento especial.

Assim, consideraram em seu estudo que a unidade de processamento serial necessita de 4 ciclos de clock para finalizar seu cálculo (eles identificaram quatro operações dependentes dentro da unidade de processamento, e as dividiram de forma que cada operação seja executada em um ciclo). Eles definem o tempo de computação geral do sistema de array sistólico serial como 4(m+(n-1)). Utilizando esse método, o tempo é reduzido para 5(m/2 + ((n/2)-1))). Evidentemente que o custo dessa arquitetura, como no trabalho apresentado por Cheng e Parhi (2008) recai no tamanho da unidade de processamento. Como dito no início desse capítulo, os autores apresentam nesse trabalho apenas a ideia de otimização de hardware (sem nenhuma implementação).

Podemos fazer uma estimativa do aumento na área que essa arquitetura pode ocasionar comparando a sua unidade de processamento com uma unidade de processamento serial típica. A primeira, conforme dados do trabalho, utiliza 14 somadores, 17 comparadores e 4 LUTs (*Look up Table*) para armazenar as matrizes de substituição. Uma unidade de processamento típica do Smith-Waterman possui (no mínimo) 3 somadores e 3 comparadores e as 4 LUTs com a matriz de substituição. Assim, percebemos que o deslocamento do vetor *wavefront* em blocos 2X2 vai gerar um aumento na área de cada unidade de processamento em mais de 4 vezes. Esse tipo de solução é ideal para utilizar em sequências pequenas prototipadas em famílias de FPGA que possuam grande capacidade. Nesse caso não faria sentido muitas unidades de processamento em paralelo (visto as sequências serem pequenas) e haveria uma grande quantidade de área disponível no dispositivo para ser utilizada.

## 4.11 Arquiteturas em FPGA para Comparação de Sequências Biológicas em Espaço Linear

Corrêa (2008) apresenta em sua tese de doutorado uma arquitetura genérica de array sistólico com o intuito de implementar UPs para os algoritmo Smith-Waterman e o DI-ALIGN. O projeto é todo desenvolvido utilizando SystemC, transformado para Verilog utilizando a ferramenta Forte e sintetizado para FPGA Virtex 2 XC2VP70.

A arquitetura apresentada utiliza um protocolo de comunicação para carregar as sequências de DNA nas diversas UPs e, após o processamento, obter o maior escore e a localização. Para o Smith-Waterman foram projetadas duas arquiteturas utilizando 20 e 100 UPs com a versão de *linear gap* do algoritmo. A frequência obtida foi de 174,7 MHz (100 UPs) e 180 MHz (20 UPs). O autor utiliza como comparação uma implementação em software do algoritmo executada em um processador de propósito geral. A aceleração obtida é de 246,9 vezes.

# **4.12** Families of FPGA-based Accelerators for Approximate String Matching

Nesse trabalho Court e Herbordt (2007) apresentam um *framework* capaz de gerar diversas arquiteturas otimizadas para os algoritmos de alinhamento local (Smith-Waterman) e global (Needleman-Wunsch). A premissa dos autores para o desenvolvimento dessa ferramenta é que, em geral, as arquiteturas previamente desenvolvidas permitem a aceleração em determinada condição específica do algoritmo. Eles defendem que uma arquitetura em hardware suficientemente genérica acarretaria muitos atrasos e não possibilitaria a aceleração que uma arquitetura específica permite. Assim, eles apresentam uma família de arquiteturas que podem ser facilmente geradas utilizando as especificidades dos algoritmos.

Os autores mapearam 3 blocos básicos que são os responsáveis por definir a forma de uso dos algoritmos Smith-Waterman e Needleman-Wunsch. O primeiro denominaram *CharRule*, que busca definir o tipo de dados que serão processados (nucleotídeos ou aminoácidos) e o tipo de matriz de substituição que será utilizado. O segundo componente, *MatchCell*, visa fornecer informações sobre as fórmulas que implementam o algoritmo. O último elemento é denominado *Sequencer* e permite configurar como será a saída do algoritmo (apenas o escore ou se será necessário o *traceback*).

Os autores não revelam se utilizaram *affine* ou *linear gap* para implementar o Smith-Waterman. Utilizando proteínas como entrada e matriz de substituição os autores alocaram 138 UPs em um dispositivo FPGA XC2VP70. A frequência alcançada é de 39 MHz com desempenho de 5,4 GCUPS. Relatam também uma aceleração em relação ao algoritmo executado em software de 186 vezes.

## 4.13 A Reconfigurable Accelerator for Smith-Waterman Algorithm