# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

#### PAULO FRANCISCO BUTZEN

# **Aging Aware Design Techniques and CMOS Gate Degradation Estimative**

Thesis presented in partial fulfillment of the requirements for the degree of Doctor in Microelectronics

Prof. Dr. Renato Perez Ribas Advisor

Prof. Dr. André Inácio Reis Co-advisor

Porto Alegre, October 2012.

# CIP - CATALOGAÇÃO NA PUBLICAÇÃO

Butzen, Paulo Francisco

Aging Aware Design Techniques and CMOS Gate Degradation Estimative [manuscrito] / Paulo Francisco Butzen. – 2012.

79 f.:il.

Orientador: Renato Perez Ribas; Co-orientador: André Inácio Reis.

Tese (doutorado) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica. Porto Alegre, BR – RS, 2012.

1. Projeto de circuitos integrados digitais. 2. Portas Lógicas 3. Efeitos de Envelhecimento. I. Ribas, Renato Perez. II. Reis, André Inácio. III. Título.

#### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos Alexandre Netto

Vice-Reitor: Prof. Rui Vicente Oppermann

Pró-Reitor de Pós-Graduação: Prof. Aldo Bolten Lucion Diretor do Instituto de Informática: Prof. Luis da Cunha Lamb

Coordenador do PGMICRO: Prof. Ricardo Reis

Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

#### ACKNOWLEDGMENT

Firstly I would like to thank God for the wonderful life that I have and for keeping up my courage and enthusiasm every day.

I would like to express my gratitude to my family, especially to thank my mom, Gloria, and my dad, Otavio, and my sister, Paula, for their patience, encouragement and love. They were always supporting me and encouraging me with their best wishes.

I acknowledge my fiancée, Raquel, for her love, care, partnership, and support. She was always there cheering me up and stood by me through the good times and bad.

I would like to thank CNPq for financial support. And also thank all my colleagues from LOGICS Research Lab. They were always willing to help and give their best suggestions.

Finally, I would like to express my gratitude to my advisors, Renato Perez Ribas and André Inácio Reis, for their guidance, patience and example. They were always close and ready to guide me when the things seemed dark and the project seemed endless.

# TABLE OF CONTENTS

| LIS | T OI | F FIGURES                           | 6  |

|-----|------|-------------------------------------|----|

| LIS | ТОЕ  | TABLES                              | 9  |

| ABS | STRA | ACT                                 | 10 |

| RES | SUM  | O                                   | 11 |

| 1   | INTI | RODUCTION                           | 12 |

| 2   | PRE  | LIMINARIES                          | 14 |

| 2.1 | Di   | gital System Design Methodologies   | 14 |

| 2   | .1.1 | Standard Cell Design Flow           | 15 |

| 2.2 | Te   | chnology Scaling                    | 19 |

| 2   | .2.1 | Static Currents                     | 20 |

| 2   | .2.2 | Manufacturing Variability           | 21 |

| 2   | .2.3 | Radiation                           | 24 |

| 2   | .2.4 | Aging Effects                       | 26 |

| 3   | AGI  | NG EFFECTS                          | 28 |

| 3.1 | Но   | ot Carrier Injection                | 28 |

| 3   | .1.1 | HCI Physical Mechanism              | 28 |

| 3   | .1.2 | HCI Long Term Analytical Model      | 30 |

| 3.2 | Ne   | gative Bias Temperature Instability | 31 |

| 3   | .2.1 | NBTI Physical Mechanism             | 31 |

| 3   | .2.2 | NBTI Long Term Analytical Model     | 33 |

| 3.3 | Ti   | me Dependent Dielectric Breakdown   | 35 |

| 3   | .3.1 | TDDB Physical Mechanism             | 35 |

| 3   | .3.2 | TDDB Long Term Analytical Model     | 36 |

| 3.4 | In   | teraction Between Mechanisms        | 38 |

| 4   | MOT  | TIVATION AND THESIS CONTRIBUTIONS   | 40 |

| 4.1 | Н    | CI Aware Solutions                  | 40 |

| 4.2 | NI   | BTI Aware Solutions                 | 42 |

| 4.3 | TDDB Aware Solutions                        | 44 |

|-----|---------------------------------------------|----|

| 4.4 | Interaction                                 | 46 |

| 4.5 | Contributions to the State-of-the-Art       | 47 |

| 5 I | DEFINING AGING COSTS                        | 48 |

| 5.1 | HCI Aging Cost                              | 50 |

| 5.2 | NBTI Aging Cost                             | 51 |

| 5.3 | TDDB Aging Cost                             | 52 |

| 5.4 | Aging Cost Validation                       | 53 |

| 6 I | DESIGN FOR RELIABILITY                      | 60 |

| 6.1 | Transistor Arrangement Restructuring        | 60 |

| 6.2 | Design More Reliable Circuits               | 63 |

| 6.2 | 2.1 Pin Reordering in Symmetrical Functions | 63 |

| 6.2 | 2.2 Complex Logic Functions Design Analysis | 65 |

| 6.2 | 2.3 Secondary Effects                       | 68 |

| 7 ( | CONCLUSIONS                                 | 70 |

| 7.1 | Summary of Contributions                    | 70 |

| 7.2 | Future Works                                | 71 |

| REF | FERÊNCIAS                                   |    |

## LIST OF ABBREVIATIONS

ASIC Application-Specific Integrated Circuits

CLA Carry Look Ahead

CMOS Complementary Metal Oxide Semiconductor

FPGA Field-Programmable Gate-Arrays

HCI Hot Carrier Injection

HDB Hard Breakdown IC Integrated Circuit

MOS Metal Oxide Semiconductor

MOSFET Metal Oxide Semiconductor Field Effect Transistor

MTCMOS Multi Threshold Complementary Metal Oxide Semiconductor

NBTI Negative Bias Temperature Instability

NMOS N-type Metal Oxide Semiconductor

PBD Progressive Breakdown

PLD Programmable Logic Devices

PMOS P-type Metal Oxide Semiconductor

PTM Predictive Technology Model

RTL Register Transfer Level

SBD Soft Breakdown

SEE Single Event Effects

SET Single Event Transient

SEU Single Event Upset

TDDB Time Dependent Dielectric Breakdown

TDI Total Dose Ionization

TSP Transistor Stress Probability

TSwP Transistor Switching Probability

VLSI Very Large Scale Integration

# LIST OF FIGURES

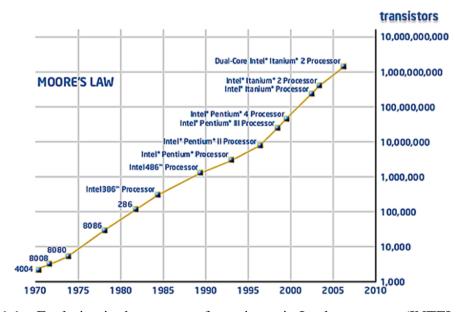

| Figure 1.1 – Evolution in the amount of transistors in Intel processors                                                                                                                           | . 12 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

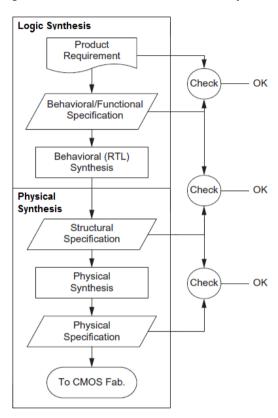

| Figure 2.1 – Standard cell design flow.                                                                                                                                                           | . 16 |

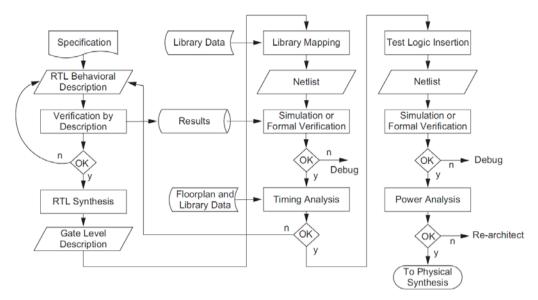

| Figure 2.2 – Logic synthesis flow.                                                                                                                                                                | . 17 |

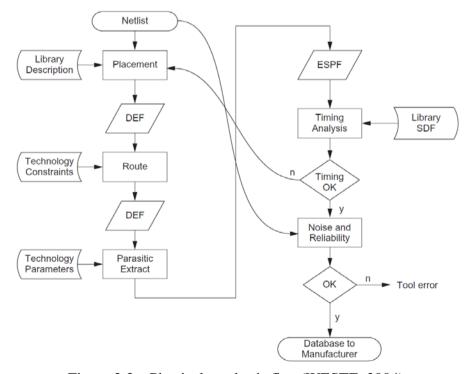

| Figure 2.3 – Physical synthesis flow.                                                                                                                                                             | . 17 |

| Figure 2.4 – Two versions of a CLA unit (OUT = $!(G2 + P2 \cdot (G1 + P1 \cdot (G0 + P0 \cdot G0))))$                                                                                             | 1.0  |

| C0))))                                                                                                                                                                                            |      |

| Figure 2.5 – Active (dynamic) and static power consumption in Intel processors                                                                                                                    |      |

| Figure 2.6 – Major static currents in MOS transistor.                                                                                                                                             |      |

| Figure 2.7 – Circuits exploring MTCMOS technique                                                                                                                                                  |      |

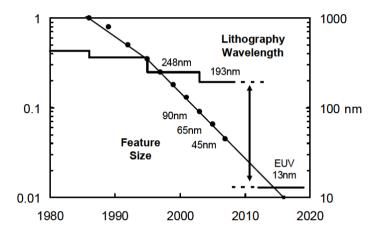

| Figure 2.8 – Wavelength versus technology node                                                                                                                                                    | . 22 |

| Figure 2.9 – Frequency and static power variations of microprocessors in a wafer                                                                                                                  | . 23 |

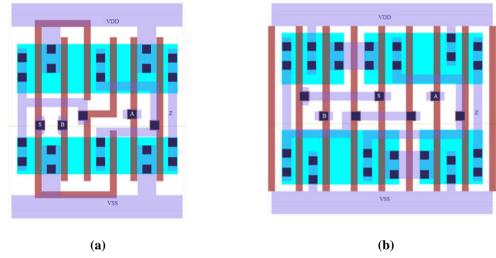

| Figure 2.10 -Gate layout considering conventional (a) and restrictive (b) design rules                                                                                                            | 3.23 |

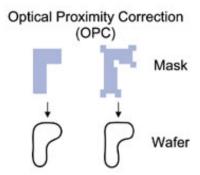

| Figure 2.11 – Original and post processed OPC layout and printed shapes                                                                                                                           | . 24 |

| Figure 2.12 – Incidence of an energy particle in MOS transistor                                                                                                                                   | . 25 |

| Figure 2.13 – TMR architecture.                                                                                                                                                                   | . 25 |

| Figure 2.14 – Traps and conductive path in gate oxide due to TDDB effect                                                                                                                          | . 27 |

| Figure 2.15 – Stress and recovery behavior of NBTI                                                                                                                                                | . 27 |

| Figure 2.16 – Carriers injection into the oxide due to HCI.                                                                                                                                       | . 27 |

| Figure 3.1 – Illustration of hot-carrier generation in NMOS transistor, and the lateral electric field in the channel                                                                             |      |

| Figure 3.2 – Transistor stress probability (TSP) for two stacked PMOS transistor of a NOR gate: (a) top transistor (connected to power supply); (b) bottom transistor (connected to output node). |      |

| Figure 3.3 – V <sub>th</sub> degradation of two stacked PMOS transistor of NOR gate according long-term model presented in Equation (3.6) and the TSP values illustrated in Figure 3.2.           |      |

| Figure 3.4 – Transient change of gate current showing SBD, PBD and HBD                                                                                                                            | . 36 |

| Figure 3.5 – Power law TDDB equivalent circuit model                                                                                                                                              | . 37 |

| Figure 3.6 – Comparative analysis between models described by Equation (3.8) and Equation (3.9).                                                                                                  |      |

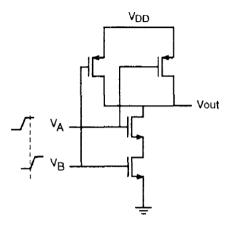

| Figure 4.1 – Example of input signal scheduling in a 2-input NAND gate to reduce H degradation.                                                                                                   | ICI  |

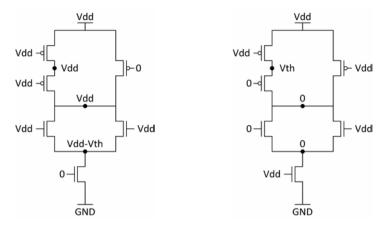

| Figure 4.2 – HCI aware design by adding self-bootsrapping transistor.                                                                                                                             |      |

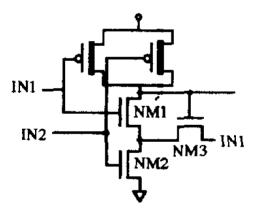

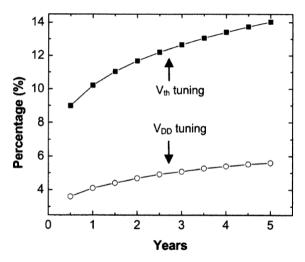

| Figure 4.3 – V <sub>dd</sub> and V <sub>th</sub> adjustment to compensate the NBTI degradation in cirspeed.               |                |

|---------------------------------------------------------------------------------------------------------------------------|----------------|

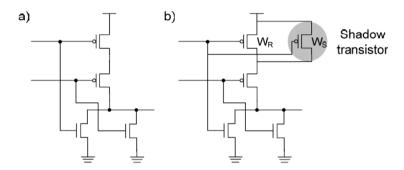

| Figure 4.4 – NOR gate: (a) conventional schematic, and (b) with a shadow (red transistor for the upper PMOS.              | lundant)       |

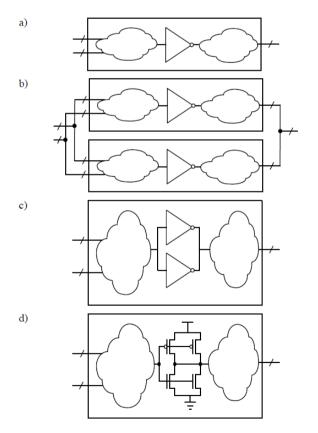

| Figure 4.5 – Duplication strategies: (a) original approach, (b) block duplication duplication, (d) transistor duplication | , , , <u>C</u> |

| Figure 5.1 – Signal probabilities procedure                                                                               | 49             |

| Figure 5.2 – Switching signal probability procedure.                                                                      | 49             |

| Figure 5.3 – Procedure to determine the HCI aging cost                                                                    | 51             |

| Figure 5.4 – Procedure to determine the NBTI aging cost                                                                   | 52             |

| Figure 5.5 – Possible bias conditions in transistor arrangement.                                                          | 53             |

| Figure 5.6 – Procedure to determine the TDDB aging cost                                                                   | 53             |

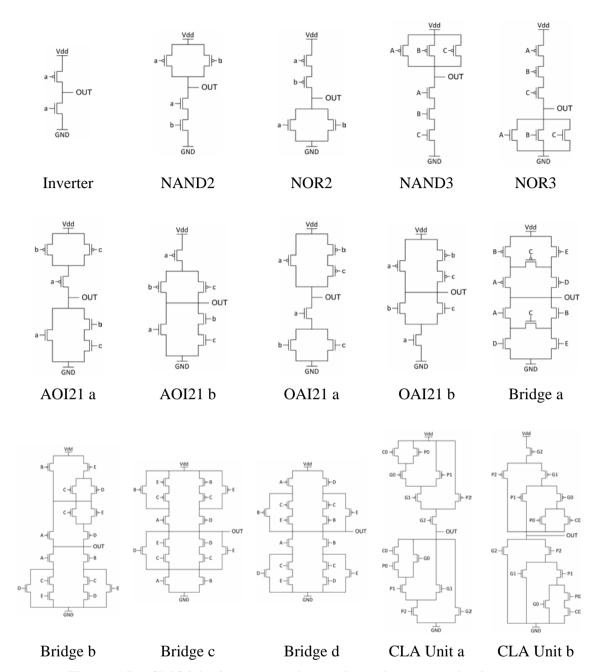

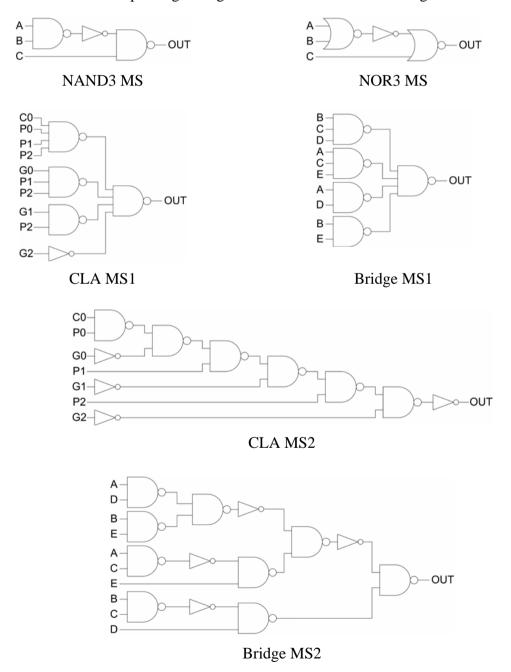

| Figure 5.7 – CMOS logic gates used to evaluate the proposed aging cost                                                    | 55             |

| Figure 6.1 – Multiple stage design solution.                                                                              |                |

|                                                                                                                           |                |

# LIST OF TABLES

| Table 2.1 – Comparison of CMOS digital circuit design solutions                              | 15       |

|----------------------------------------------------------------------------------------------|----------|

| Table 5.1 – HCI aging cost evaluation results                                                | 56       |

| Table 5.2 – NBTI aging cost evaluation results.                                              | 57       |

| Table 5.3 – TDDB aging cost evaluation results                                               | 58       |

| Table 5.4 – Delay aging cost results                                                         | 59       |

| Table 6.1 – Degradation savings due to transistor arrangement restructuring                  | 62       |

| Table 6.2 – HCI degradation savings due to transistor arrangement restructuring              | 63       |

| Table 6.3 – NOR gate degradation when different input signals probabilities are app          |          |

| Table 6.4 – HCI degradation in NAND gate applying different input signals switchin activity. | ng       |

| Table 6.5 – Aging degradation in single and multiple stages design solutions                 | 67       |

| Table 6.6 – Rise and fall delay degradation due to NBTI in single and multiple stage         | <b>;</b> |

| gates.                                                                                       | 68       |

| Table 6.7 – Secondary effects of aging mechanism.                                            | 69       |

#### **ABSTRACT**

The increased presence of integrated circuit (IC) in the people's life has occurred for main two reasons. The first is the aggressive scaling of integrated device dimensions. This miniaturization enabled the construction of smaller, faster and lower power consumption devices. The other factor is the use of a cell based methodology in IC design. This methodology is able to provide efficient circuits in a short time. With the devices scaling, new factors that were usually ignored in micrometer technologies have become relevant in nanometer designs. Among them, it can be mentioned the static consumption, process parameters variability, manufacturability and aging effects. Some of these factors, such as static consumption and variability, are already taken into account by the standard cell design methodology. On the other hand, the degradation caused by aging effects has increased at each new technology node, as well as the importance in relation to the circuit reliability throughout its entire lifetime has also increased. This thesis explores such aging effects in the design of digital IC. The main contributions can be highlighted as the definition of a cost of aging that can be exploited by logic synthesis algorithms to produce a more reliable circuit. This cost can be also used by the analysis tools in order to obtain an estimative of the degradation that specific circuit experiences throughout their lifetime. In addition, a proposal to reorder the transistor structural arrangement of logic gates is presented in order to treat the effects of aging on initial steps in the design flow. Finally, a simplified analysis of the characteristics to be exploited at circuit level is performed exploring details of the design of complex logic gates. The aging cost results have given a good and fast prediction of logic gates degradation. The transistor arrangement restructuring approach is a good alternative to design more reliable circuits. Furthermore, the use of complex arrangements is also an excellent alternative which exploits the intrinsic robustness of series transistors association. Moreover, the discussed approaches can be easily used together with existing techniques in the literature to achieve better results.

**Keywords:** digital integrated circuit design, logic gates, CMOS technology, aging effects, modeling, reliability.

# Técnicas de Projeto Considerando Envelhecimento e Estimativa da Degradação em Portas Lógicas CMOS

#### **RESUMO**

O advento da utilização de circuitos integrados pela sociedade se deu por dois motivos. O primeiro consiste na miniaturização das dimensões dos dispositivos integrados. Essa miniaturização permitiu a construção de dispositivos menores, mais rápidos e que consomem menos frequência. O outro fator é a utilização da metodologia baseada em biblioteca de células. Esta metodologia permite o projeto de um circuito eficiente em um curto espaço de tempo. Com a redução dos dispositivos, novos fatores que eram desconsiderados no fluxo automático passaram a ter importância. Dentre eles podemos citar o consumo estático, a variabilidade, a manufaturabilidade e o envelhecimento. Alguns desses fatores, como o consumo estático e a variabilidade, já estão integrados à metodologia baseada em biblioteca de células. Os efeitos de envelhecimento tem sua degradação aumentada a cada novo processo tecnológico, assim como tem aumentado também a sua importância em relação à confiabilidade do circuito ao longo da sua vida útil. Este trabalho irá explorar estes efeitos de envelhecimento no projeto de circuitos integrados digitais. Dentre as principais contribuições pode-se destacar a definição de um custo de envelhecimento na definição de portas lógicas, que pode ser explorado pelos algoritmos de síntese lógica para obterem um circuito mais confiável. Este custo também pode ser utilizado pelas ferramentas de análise a fim de obter uma estimativa da degradação que o circuito proposto irá sofrer ao longo da sua vida útil. Além disso, é apresentada uma proposta de reordenamento estrutural do arranjo de transistores em portas lógicas, a fim de tratar os efeitos de envelhecimento nos níveis mais iniciais do fluxo. Por fim, uma análise simplificada de características a serem exploradas ao nível de circuito é discutida utilizando o auxílio do projeto de portas lógicas complexas. Os resultados apresentam uma boa e rápida estimativa da degradação das portas lógicas. A reestruturação do arranjo dos transistores tem se apresentado como uma boa alternativa ao projeto de circuitos mais confiáveis. Além disso, a utilização de arranjos mais complexos também é uma excelente alternativa que explora a robustez intrínseca da associação de transistores em série. Além disso, as alternativas propostas podem ser utilizadas em conjunto com técnicas já existentes na literatura.

**Palavras-Chave:** projeto de circuitos integrados digitais, portas lógicas, tecnologia CMOS, efeitos de envelhecimento, modelagem, confiabilidade.

#### 1 INTRODUCTION

The presence of digital integrated circuits (IC) in people's lifestyle has increased significantly during the last decades. These components can be found from computers and mobiles to embedded systems in cars and house appliances. This success is mainly due to the progress achieved by the semiconductor industry.

The semiconductor industry has been guided by the "Moore's Law". In 1965, Gordon E. Moore predicted that the numbers of transistors that could be integrated in a single die would double every 24 months (MOORE, 1965). Such behavior has been roughly confirmed until now, as illustrated in Figure 1.1 (INTEL, 2010). This increment in transistor count is resulted from the scaling down of device dimensions. In general, the scaling process improves the amount of device in the same area, increases the transistor speed and reduces the individual parasitic capacitances. However, a drawback of this scaling is the advent of several effects that were usually neglected in micrometer technologies due to their insignificant magnitude. Static currents, performance variability and device reliability are some examples of those new issues that have to be considered in nanometer IC design (RABAEY, 2003).

Figure 1.1 – Evolution in the amount of transistors in Intel processors (INTEL, 2010).

On the other hand, different design solutions can be explored to implement electronic systems. The choice of the most efficient solution involves the evaluation of the costs, capabilities and limitation of each design style based on the circuit requirements. Basically, digital circuits can be designed from three different approaches. A microprocessor can perform the computation from a functional circuit

specification, through an algorithm description (software programing). Programmable logic devices (PLDs), in turn, are usually used to implement the circuit from a register transfer level (RTL) description, which specifies the components and connections required to achieve the circuit behavior. The last approach consists in designing the entire layout of an integrated circuit. An automated flow, known as standard cell design methodology, that reuses pre-designed and pre-characterized gates, is a common strategy for fast development of the physical design of a chip (WESTE, 2004).

This thesis investigates the reliability aspect of IC designed in nanometer technologies. The consequences of emerging aging effects during the entire system lifetime are investigated. The focus is centered in the design solutions that can be applied in standard cell methodology to generate more reliable circuits. CMOS logic gates and circuit level design solutions are explored.

The rest of the text is organized as follow. The basic concepts of VLSI design solutions and a brief review of the challenges related to the technology scaling process are presented in Chapter 2. The physics mechanisms behind three aging effects and respective analytical models are discussed in Chapter 3. In Chapter 4 are discussed several solutions proposed to deal with the aging degradation. A lack of design solutions to deal with this aging degradation in the standard cell flow motivates the proposals presented in the last section of that chapter. The definition of a logic gate aging cost is presented in Chapter 5, whereas design solutions at circuit level are explored in Chapter 6. Conclusions and final remarks are presented in Chapter 7.

#### 2 PRELIMINARIES

This chapter presents the basic concepts associated to solutions explored in this thesis. The different digital system design methodologies are initially discussed. The standard cell methodology receives special attention since the most of the proposed approaches are directly applied in this scope. The new design challenges introduced by the technology scaling are presented in following. The discussion presents a brief overview of the physics and some design techniques for each design topic.

## 2.1 Digital System Design Methodologies

Due to the wide variety of potential applications and the current complexity of the circuits, the choice of the correct design solution is crucial to the success of an electronic product. This choice involves mainly the evaluation of economic cost, circuit performance and time-to-market. The main difference between the existing solutions is the integrated components associated (WESTE, 2004).

A digital system can be developed by programming a microprocessor or microcontroller. In this approach, a generic microprocessor is programmed by software for a desired application. Hardware integration that explores this type of solution has associated with it reduced design cost and development time. Since the solution involves programing in high level language, the approach presents good flexibility. However, such solution tends to have the worst performance in terms of speed and power consumption when compared to other existing methodologies. Also, the unit cost of a microprocessor can be considered elevated. This solution is ideal when the project requires short time-to-market and flexible product constrains.

Another approach is the use of programmable logic devices (PLDs). In this case, the programming is done at the hardware level system. When compared to microprocessors, this solution presents a better performance in terms of speed and power consumption at the cost of non-recurring engineering (NRE) cost and development time. A variety of PLDs are available. Each one has their own architecture and technology of configuration, impacting the performance, cost and programmability characteristics. FPGAs and CPLDs are the most powerful programmable devices. They are usually designed in modern manufacturing processes and uses static RAM and flash memories to configure routing and logic functions. Such solution is usually adopted when microprocessors does not achieve speed and power consumption requirements.

In addition to the two previous approaches, there is a third solution related to the development of application specific integrated circuits (ASICs). It is commonly used in applications that have strict time and power consumption constraints. Moreover, due to the cost associated with the customized manufacturing process, the development of

ASICs is more associated to products of high market demanding. There are two main methodologies that used in IC design: the full-custom and the standard cells.

In full-custom methodology, all geometric forms of layout that represent the devices and interconnection in the circuit are designed individually (customized). From this degree of freedom is possible to obtain almost optimal circuit in terms of area, speed and power consumption. The main drawback is the exhaustive handmade tasks, increasing significantly the final design cost. Typically, such approach is used to improve the circuit area, performance and/or power consumption in respect to the standard cells design.

A cell-based methodology, also known as standard cell methodology, is widely used in ASIC design. This approach in based on standard cell library that contains several pre-designed and pre-characterized gates as the basic block to be automatically reused in the IC design. The circuit designed using the standard cell methodology does not have the NRE costs as elevated as the circuit designed using the full-custom approach. There are two main reasons for this reduced cost. The first one is the fact that the basic block is a pre-designed logic gate instead of geometric forms of full-custom methodology. The second one is the existence of a complete automated flow that explores the cells available in a target library.

Table 2.1 summarizes the main characteristics of each solution discussed previously. The remainder of this section presents the standard cell design flow and explores the potential points of optimization.

| Design Solution |                 | Unit<br>Cost | Complexity/Cost of Implementation | Time to<br>Market | Speed     | Power Consumption | Flexibility |

|-----------------|-----------------|--------------|-----------------------------------|-------------------|-----------|-------------------|-------------|

| Microprocessor  |                 | Medium       | Low                               | Low               | Low       | High              | High        |

| PLD             |                 | Medium       | Medium                            | Low               | Medium    | Medium            | Medium      |

| IC<br>Design    | Cell-<br>Based  | Low          | High                              | High              | High      | Low               | Low         |

|                 | Full-<br>Custom | Low          | High                              | High              | Very High | Low               | Low         |

Table 2.1 – Comparison of CMOS digital circuit design solutions.

#### 2.1.1 Standard Cell Design Flow

The standard cell design flow is widely used to design integrated circuits. The main factors contributing to this great spread are:

- Automated design flow which provides a quickly development time when compared to full-custom methodology;

- The use of a cell library which consists of a set of logic gates already designed and previously characterized;

- Possibility to generate a circuit with nearly optimal results with respect to performance, area and power.

This methodology can be divided into two main stages, as illustrated in Figure 2.1. The logic synthesis generates a structural description composed by logic gates and registers from a circuit specification created from the product requirements. This step

explores the selection of logic gates from a pre-designed library to represents the best result considering the design constraints. The physical synthesis generates the circuit layout from the structural description provided by the logic synthesis. It is responsible for the circuit organization, the placement of logic gates and the signals routing. In both stages are carried out tests to check if the circuit meets the specifications generated early. If product requirements are not met, a rework is required. Considering this methodology, the circuit quality depends on three factors: the logic synthesis tool, the physical synthesis tool (place and route), and the cell library (SCOTT, 1994).

Figure 2.1 – Standard cell design flow (WESTE, 2004).

The logic synthesis process may be subdivided, as illustrated in Figure 2.2. To initial circuit specification are applied technology independent optimizations. Since these optimizations are independent of technology, they occur at the logical level and exploit primarily the concepts of factorization, reduction/rewriting graphs, trees or BDDs, and functional composition/decomposition. Next, the technology mapping step uses the logic gates of a cell library to find the best logic gates combination which meet the constraints of the circuit. In the set of logic gates defined by the technology mapping, new optimizations can be applied, now considering the target technology, in order to generate an optimized network of logic gates. During the complete flow, several verification steps are performed to guarantee the logic correctness of generated circuit and the desired performance. The resulted circuit from this phase is a set of logic gates and their interconnections that are used as starting point in physical synthesis.

Figure 2.2 – Logic synthesis flow (WESTE, 2004).

The physical synthesis stage may be subdivided as illustrated in Figure . Usually, the first step is named floorplanning and it is responsible to define the position of the high level blocks in the total circuit area. The I/O pads position, power supply and clock network is also defined in such step. The next step is responsible for positioning the gates of each high level block in the circuit area. The signal routing is performed in the following. From this stage, the layout of the circuit is complete. However, to be considered ready, the circuit needs to have their characteristics verified. As in logic synthesis, there are several verification steps that confirm if the designed circuit meets the constraints. On the contrary, any of the above steps can be executed again trying to achieve a better result.

Figure 2.3 – Physical synthesis flow(WESTE, 2004).

As the basic unit used in standard cell methodology is the logic gate, the quality of integrated circuits that are designed using this solution is directly related to the quality of the target standard cell library (SCOTT, 1994). Some aspects that have influence in the quality of a library involves the amount of logic gates, their layout and cell sizing, the sizing variety (drive strength), and the amount of logic function presented in the library. In the literature, there are authors claiming that the best library is the one with few cells (RICCI, 2007), while others support libraries with as many cells as possible (GUAM, 1996), with no consensus on this. Ideally, it is easier to obtain a gate that implement the correct logic function with the appropriate size to achieve the optimal solution for a specific portion of the circuit with a library that contain a higher the number of designed logic functions with several sizing options. However, as more cells are added to the library, more runtime is necessary to technology mapping algorithm and also more time is needed to design, verify and characterize the library.

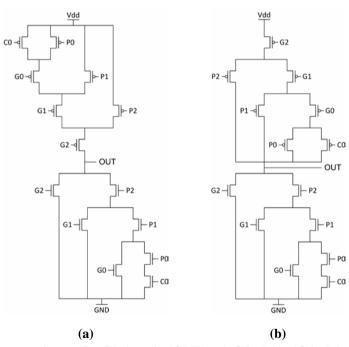

Disregarding the amount of logic gates, their layout and sizing, another point that can increase the quality of a library is the diversity of transistor arrangement that implement some logic function. Figure 2.4 illustrates two versions of the function " $OUT = !(G_2 + P_2 \cdot (G_1 + P_1 \cdot (G_0 + P_0 \cdot C_0)))$ ". This function represents the 'generate signal' in a carry lookahead adder (CLA), and will be referred as 'CLA unit' in the rest of the text. Each of these versions has different speed and power consumption characteristics and this difference can be explored by the technology mapping if both versions are presented in the cell library.

Figure 2.4 – Two versions of a CLA unit (OUT =  $!(G2+P2 \cdot (G1+P1 \cdot (G0+P0 \cdot C0))))$ ).

A variant of the cell-based methodology is the one that explores the automatic cell generation, commonly known as library-free (BERKELLAR, 1998; ABOUZEID, 1992; CORREIA, 2004; MARQUES, 2007). In this variant, it is assumed that the gates can have their layout automatically generated by a tool as they are used by the technology mapping algorithm. In this case, the library contains only the cells that the technology mapping algorithm uses to design the circuit. The main advantage of this approach is that the system is not restricted to a pre-defined amount of logic gates available. With

the possibility to automatically generate any logic gate, the technology mapping algorithm can exploit the diversity of options available to design optimized gates. Such diversity includes both different logic styles and different versions for the same style. Ideally, with the possibility of using any gate at any portion of the circuit, this variant would tend to produce better results when compared to the standard cell design flow presented previously.

One of the major obstacles for the use of library-free concept is the fact that the logic gates in this variant were not previously characterized. Without the characterization values, the technology mapping algorithms that exploit this approach usually use metrics that do not reflect the actual behavior of the logic gate (CORREIA, 2004; MARQUES, 2007). The development of more accurate metrics enables the technology mapping algorithms to reach closer results to the real circuit behavior.

Those metrics are not restricted to timing and power information. The existence of metrics to nanometer effects could also support the design of more robust circuits. The aging effect can be used as example. In traditional approaches, they are treated at post-technology mapping stages of the design flow. One reason for that is the inexistence of data that can be used by the technology mapping algorithm. When properly computed, a metric for the aging effects could be associated with the cost of the logic gate, allowing its analysis in an initial stage of the project. This early treatment can avoid possible reprocesses, lowering the total circuit design cost.

#### 2.2 Technology Scaling

The transistor dimension scaling is the main artifice used by the semiconductor industry to increase the performance of the integrated circuits. As mentioned previously, the nanometer devices have more current capability and smaller capacitances than the bigger ones. These two factors contribute to design faster circuits at each advance in technology node. Smaller capacitances also contribute to lower power consumption per operation. Moreover, smaller dimensions also allow the integration of more devices in same silicon area, reducing so the circuit cost and allowing the design of more complex circuit in the die.

The higher transistor density in nanometer circuits produces thermal issues due the higher power consumption per area (HUANG, 2004). The reduction of power supply  $(V_{dd})$  is necessary to deal with power and thermal constrains in the circuit. An inconvenient of such reduced power supply is the lower circuit noise margin and smaller robustness against radiation particles (DRESSENDORFER, 1989). Another consequence of this  $V_{dd}$  reduction is the threshold voltage  $(V_{th})$  reduction too. The  $V_{th}$ reduction is necessary to keep a good transistor current capacity. This reduced  $V_{th}$ increases significantly the transistor subthreshold current, that is one of the main contributors to the static power increasing in nanometer designs (NARENDRA, 2006). Other contributors, such as gate tunneling current and band-to-band tunneling current, have their magnitude increased due to the increment in electric fields presented in transistor structures (ROY, 2003). Although the supply voltage has been reduced, the reduction in transistor dimensions is proportionally higher than the supply voltage scaling, increasing so the electric fields. This increment in electric fields causes also degradation in transistor characteristics during the circuit lifetime. The mechanisms that cause this degradation are called aging effects, that can be also considered as a temporal variation in transistors characteristics (STATHIS, 2003). Moreover, another aspect that increases as the transistor dimension scaling is the process variation. Since the absolute value of transistor dimensions or doping profile is smaller, any variation in drawing shapes or in dopant profile has higher impact in the transistor parameters. The scenario has become even worse due to the fact that the light wavelength used in lithography process is several times larger than the smallest drawing dimension considered in the technology node (BORAK, 2003). All of those issues have become important design aspects to the performance, area and power consumption of nanoscale IC designs (ORSHANSKY, 2008). Some details related to such undesired effects are discussed in the following.

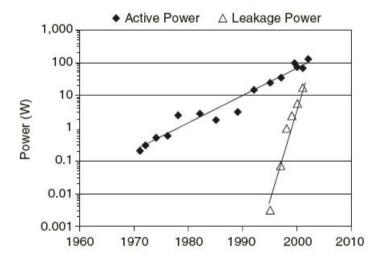

#### 2.2.1 Static Currents

In past technologies, the magnitude of static currents was low and usually neglected. However, as the devices have been being scaled to achieve higher density, performance, and lower dynamic power consumption, the static power in the nanometer regime is becoming a significant portion of total power dissipation in CMOS circuits, as depicted in Figure 2.5. These currents are responsible for power consumption when the circuit is in idle mode. The fact that several integrated circuits are embedded in portable applications and the basic requirement for this type of equipment is the reduced power consumption, the importance of treating properly static power consumption is quite obvious.

Figure 2.5 – Active (dynamic) and static power consumption in Intel processors (MOORE, 2003).

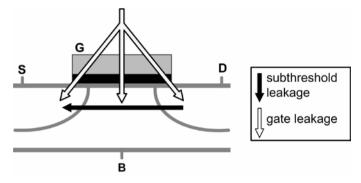

The reduction of the supply voltage is necessary to maintain, or even decrease, the dynamic power consumption (ROY, 2003; MUKHOPADHYAY, 2006; BUTZEN, 2010; CHENG, 2006; AGARWAL, 2006; ALKABANI, 2008). In order to keep the current capacity of the devices and avoid the aggravation of short channel effects, the transistor threshold voltage and the transistor gate oxide thickness ( $t_{ox}$ ) have followed the  $V_{dd}$  reduction. Due to the same reason, the dopants density has been increased. The changes in these three transistor parameters have resulted in a significant increasing in static currents for every new technology node. Figure shows the two major static currents present in nanometer MOS transistor. Besides subthreshold and gate tunneling currents, there are minor components as the current through the reverse biased pnjunctions (BTBT), the punchthrough current and the gate induced drain leakage (GIDL) (ROY, 2003).

Figure 2.6 – Major static currents in MOS transistor.

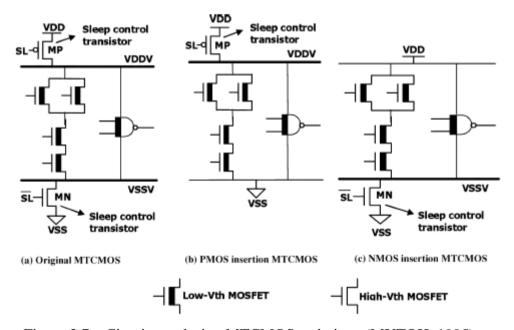

Several models and reduction techniques have been proposed and used by industry to address this undesired consumption. Regarding to the reduction techniques, at manufacturing level, the introduction of high- $\kappa$  dielectric in transistor oxide gate allows a significant reduction in the gate tunneling current (KITTI, 2009). Furthermore, new technologies have transistors with different threshold voltages. This fact is related to the exponential dependence of subthreshold current to  $V_{th}$  (KAO, 2000; WEI 1999). Additionally to the techniques that use the dual threshold transistors, the forward and reverse body biasing is also explored (NARENDRA, 2003). The use of sleep transistors to turn off parts of the circuit that are not executing a computation is also explored to reduce the static power. This technique associated to dual threshold transistors is called multi-threshold CMOS (MTCMOS) (MUTOH, 1995). Figure 2.7 illustrates the basic concepts of this approach.

Figure 2.7 – Circuits exploring MTCMOS technique (MUTOH, 1995).

#### 2.2.2 Manufacturing Variability

As the minimum dimensions are reduced, greater is the uncertainty regarding to the effective shape and the effective quantity of atoms which form the devices. Thus, the device characteristics are more sensitive to any slight variations in shape and in amount of atoms that compose it. These variations can be classified as random variations and systematic variations. The random variations are mainly related to the fabrication

process. Random dopant fluctuations (RDF) and line edge roughness (LER) are examples of random variations. The principal way to mitigate this kind of variation is centered in process calibration. There is no solution at design level to deal directly with such variations. Most works evaluate the effect and the impact in device behavior. The systematic variations are mainly related to the lithography process.

Lithography is a key process in the fabrication of integrated circuits. The light wavelength used in this process is directly linked to resolution of the layout. Figure 2.8 illustrates the wavelength used in the technological nodes from 1  $\mu$ m to 45 nm. According to Figure 2.8, it seems clear that in the processes below 180 nm the resolution of the layout patterns is penalized due to the light wavelength larger than the minimum allowed drawing shape size.

Figure 2.8 – Wavelength versus technology node (SIVAKUMAR, 2006).

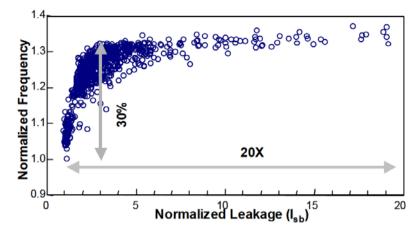

Moreover, the affected transistor characteristics can achieve different magnitudes (BORAK, 2003). Figure 2.9 shows the variations in frequency and static power consumption of identical microprocessors produced over the same wafer. While the frequency variation does not reach 40%, the variation in static power consumption is about 20 times. Moreover, environmental variations, such as in temperature and in power supply voltage contribute to add more uncertainty about the circuit behavior. There are several works that explore techniques to minimize the effect of variability in nanoscale ICs (BHUSHAN, 2006; SYLVESTER, 2008; PANG, 2009; AITKEN, 2009).

Several techniques in manufacturing and design levels are used to allow circuits at dimensions smaller than the used wavelength. At process level, two strategies have to be mentioned. The first one is the exploitation of optical concepts to allow the use of a wavelength larger than the printed shape. The second one is the strategy named immersion lithography that improves the process resolution (MACK, 2006, FRENCH 2007). At design level, the techniques are centered in layout optimization. Restrictive design rules (RDR) are being used to mitigate the systematic variations (JHAVERI, 2010). As the own name suggests, this set of design rules is more restrictive than the traditional one. Example of restrictions is the rules that allow layers in only one direction with equally spacing between them. Figure 2.10 illustrates the layout of a logic gate designed considering traditional approach and considering restrictive design rules.

Figure 2.9 – Frequency and static power variations of microprocessors in a wafer (BORAK, 2003).

Figure 2.10 – CMOS gate layout considering conventional (a) and restrictive (b) design rules (PALLISGAARD, 2012).

There are also several techniques that exploit post-layout processing. These techniques explore the drawing-printed shapes relationship to improve the final layout resolution. Such techniques are named resolution enhancement techniques (RET) (WONG, 2001). For instance, the technique called optical proximity correction (OPC) applies some distortions in original layout with the objective to achieve the expected final form. Figure 2.11 illustrates the objective and solutions presented by this technique for a simple layout. Other techniques, such as phase-shift mask and double patterning, are also used in the context of RET (JHAVERI, 2010). In addition to the approaches discussed above, the evaluation of variability robustness in different transistor arrangements can also be explored as a solution to mitigate variability (SILVA, 2009). This approach can provide important data to help the standard cell design flow, especially the mapping algorithm, in generating circuits with lower variability.

Figure 2.11 – Original and post-processed OPC layout and printed shapes (MACK, 2006).

#### 2.2.3 Radiation

Radiation effects are related to the incidence of ions and particles in the integrated circuits (DRESSENDORFER, 1989). The main transient effect caused by these particles is a momentary voltage and current value change in transistors terminals. The perturbation magnitude and duration is proportional to the energy of the incident particle and the amount of charges stored in transistor structured. According to the incident region or the perturbation propagation, a bit flip can occurs, resulting in a wrong system computation.

Each new technology generation present a scaling in transistor dimensions. This dimension scaling is directly related to the reduction in the number of atoms that make up device structure. The reduction of the supply voltage reflects in small circuit noise margins. These two factors are responsible to nanometer circuits being more vulnerable to the effects of energy particles that reach it. In other words, voltage fluctuations that were caused only by high-energy particles in micrometer processes, in nanometric circuits they are caused by particles of average power, increasing significantly the occurrence of failures due to radiation (JOHNSTON, 2000).

Figure 2.12 illustrates the incidence of an energy particle in MOS transistor. When a particle strikes an IC, it produces a large population of electron-hole pairs. Since electrons present a higher mobility than holes, electrons are collected towards higher potentials present on the IC bulk, which generates a fast current transient. If the stricken IC area is the reverse-biased depletion region of a transistor, and if this transient is large enough, the perturbation may result in the loss of the stored information (i.e., a bit flip).

The effects caused by radiation can be divided into cumulative effects, called total ionizing dose (TID), and transient effects, known as single events effects (SEEs) (LABEL, 2000). TID consists in accumulation of charges over time in nsulating layers, provoking leakage current increase and transistor transistor threshold voltage shifts. This effect causes degradation in transistor parameters. This degradation is permanent, but it usually takes a long time to cause a functional failure in the circuit. It is also being mitigated with the scaling due to the small dimensions of transistor structures (LABEL, 2000). SEEs, in turn, are also classified according to the location affected by the radiation particle.

Single event effects are generally characterized by a voltage variation at a transistor node caused by a particle impact in that device terminal. As mentioned before, the perturbation magnitude and duration are proportional to the particle energy value. In extreme cases, these events may have enough energy to cause a permanent failure (i.e.,

hard SEEs), or even cause the device destruction (i.e., destructive SEEs) (LABEL, 2000).

Figure 2.12 – Incidence of an energized particle in MOS transistor.

The radiation effects that cause transient faults (i.e., soft SEEs) are classified according to the affected location. When the node reached by a particle is a storage element and the particle has enough energy to provoke a bit flip in that element, the effect is known as single event upset (SEU). The other case is when the particle hits the combinational logic blocks. In this case, the effect is called single event transient (SET). The voltage perturbation from a SET is usually logically or electrically masked. An indirect SEU occurs when the voltage perturbation from a SET is propagated to a storage element. The computation error is characterized when occurs a bit flip in the storage unit (MASSENGILL, 2000).

As the vulnerability of circuits against radiation effects increases in new technology processes, the use of techniques that produce radiation robust circuits become more important. There are techniques at all levels of abstraction, from the algorithmic level to the process level. At process level, the use of silicon-on-insulator (SOI) can be pointed out. At physical level, several layout solutions are proposed (COLINGE, 2001). At gate level, it can be highlighted works that explore the logical and electrical masking, as well as the robustness of the network of transistors compared to the propagation of the effect of radiation (NICOLAIDIS, 1999).

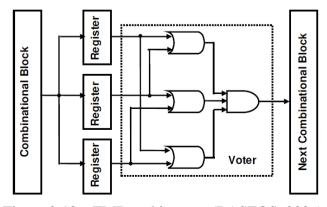

From architectural to algorithmic level, the redundancy is explored. Techniques as triple modular redundancy (TMR), time redundancy (TR), parity, error detection and correction (EDAC), can be explored (NICOLAIDIS, 1999; PETERSON, 1980). The concept is the use of redundancy to be able to detect the correct computation by comparing experimental results.

Figure 2.13 illustrates the TMR, where there are three instantiations of the same circuit and a voter that computes the correct result. All these techniques introduce significant area overhead and performance penalty.

Figure 2.13 – TMR architecture (BASTOS, 2006).

#### 2.2.4 Aging Effects

The transistor scaling is responsible for a significant improvement in circuit performance in each new technology generation. The reduced dimensions increase the electric fields across the device structures. These higher electric fields are the main responsible for the increased device characteristics degradation over time. Effects such as time dependent dielectric breakdown (TDDB), negative bias temperature instability (NBTI) and hot carrier injection (HCI) have become important parameters to be taken into account in circuits designed in nanometer technologies. Considering that the transistor dimensions continue scaling, and consequently the electric fields in transistor structure continue increasing, the importance of treating such wearout mechanisms in the new technology nodes is increasing since they may cause important losses in timing performance, increasing also power consumption and ultimately, functional errors in the system computation (WANG, 2007; VATTIKONDA, 2006; CHEN, 2003; TAKEDA, 1995; TONG, 2009; NIGAM, 2009).

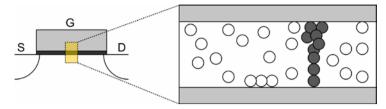

The metal-oxide-semiconductor structure that characterizes the MOS devices can be considered the most vital transistor structure (STATHIS, 2003). Ideally, the gate oxide should be a 'perfect' insulator. However, some defects are presented in the crystal structure since the oxide growth in the manufacturing process. The transistor is characterized with these defects and the effect of their existence is computed in this characterization. During the transistor operation, some new defects are created in the MOS structure, degrading the device characteristics. As the oxide is getting thinner, the electric field across it is getting more intense. The same occurs with the gate length scaling and the increment of the electric field across the channel. These higher electric fields increase the defect generation tax and increase the importance of treating these wearout mechanisms.

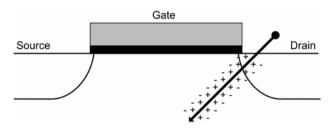

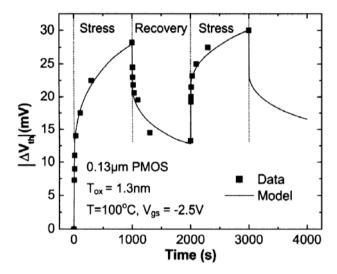

The defects created by the wearout mechanisms in the oxide structure results in penalties on timing and power performance of the circuit. The degradation caused by each aging effect involves in general more than one physical mechanism. However, each effect has its degradation behavior well defined. Also, the affected transistor characteristic is well known. TDDB and NBTI are static degradation effects, while HCI acts when the transistor is switching. TDDB effect creates traps at gate oxide when a high electric field is presented across the oxide. This traps creation compromise the isolation oxide characteristic, increasing the gate tunneling current. At extreme cases, a conductive path through the oxide can be created and the transistor operation is compromised (TONG, 2009). Figure 2.14 illustrates the defects and the conductive path created by TDDB in a gate transistor oxide. Moreover, NBTI generates traps in the interface between the gate oxide and the substrate. This effect occurs in PMOS transistor at the presence of a high electric field. It happens when the transistors are negative biased. This interface traps degrade the transistor threshold voltage, impacting the transistor maximum current capability and the circuit speed. When the electric field is not presented, some threshold voltage recovery is verified (WANG, 2007). Figure 2.15 illustrates the dynamic behavior of NBTI effect. On the other hand, as discussed before, HCI acts when the transistor is switching. Some carriers that are flowing in the channel gain enough energy and are injected into the gate oxide near to the drain terminal. Figure 2.16 illustrates this carrier injection. This degradation is also reflected in transistor threshold voltage and, consequently, in the circuit timing characteristics (TAKEDA, 1995).

Figure 2.14 – Traps and conductive path in the gate oxide due to TDDB effect.

Figure 2.15 – Stress and recovery behavior of NBTI (VATTIKONDA, 2006).

Figure 2.16 – Carriers injection into the oxide due to HCI.

The techniques that deal with the mitigation of aging effects degradation explore the interaction between both, manufacturing and design solutions. As TDDB effect has a clear transistor bias degradation, design techniques look for the transistor with higher transistor bias degradation probabilities in order to replace them by transistor with ticker gate oxide, being this kind of device available at the fabrication process. This solution can cause timing penalty whether the transistors belong to the critical paths (STATHIS, 2003). The HCI effect is related to the channel current flow. Due to the output capacitance, the transistors connected to the output node experience high HCI degradation at every switching activity. Based on that, transistors with higher switching activity are placed far from output logic gate nodes (TAKEDA, 1995). Since NBTI has stress and recovery phases, some input vector control techniques try to maximize the recovery time to mitigate the transistor threshold voltage degradation (VATTIKONDA, 2006).

The aging effects are in the center of this work. More details related to the principal characteristics of each effect and some related works presented in the literature are discussed in the following chapters.

## 3 AGING EFFECTS

The shrinking in critical transistor dimensions to nanometer ranges and the increasing substrate doping densities result in a significant increase of electric fields through the channel region and across the gate oxide of MOS transistors. These high electric fields act in several ways changing the transistor characteristics during its lifetime. The physical mechanisms of three aging effects and respective analytical models are discussed in the following sections.

## 3.1 Hot Carrier Injection

The hot carrier injection (HCI) phenomenon is been a reliability issue in MOS circuits since the 1970s. It can be considered as one of the aging effects more studied and treated in the literature. In summary, due to the lateral electric field, carriers that are travelling in the channel gain enough energy to break the energy barriers being injected into the gate oxide, breaking so an interface state. This process results in a shift in threshold voltage, in the transconductance degradation, and in decreasing of the transistor drain current drive capability. Physical details and models are briefly reviewed bellow.

#### 3.1.1 HCI Physical Mechanism

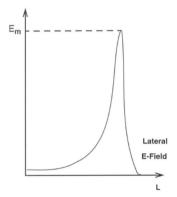

The classic theory behind the HCI effect involves the high lateral electric field in MOS transistor when the device is biased under saturation conditions. This high lateral electric field produces energetic carriers near to the transistor drain region. These carriers are called hot carriers because they have higher energy than the thermal energy of surrounding lattice. Part of this carriers produce substrate current that can lead to a latch up in CMOS structures (MATSUNAGA, 1980). However, the most important aspect for long-term reliability is those carriers that acquire sufficient energy to overcome the energetic barrier and get injected into the gate oxide, breaking an interface state (CHENG, 1985). The higher mobility of electrons makes the HCI degradation impact worse in NMOS transistors than in PMOS transistors (ROY, 2005). The carrier generation in NMOS transistor due to HCI and the intensity of the lateral electric field across the transistor channel are illustrated in Figure 3.1.

The damages caused by the carriers that are injected into the gate oxide may result in a permanently change in device characteristics, such as the drain current capability, threshold voltage and transcondutance. This oxide damage induces gradual degradation over the time and can lead to long-term circuit performance degradation and malfunctioning. As technology scaling, the supply voltage ( $V_{dd}$ ) has to be also scaled down. From the reduction in supply voltage, the HCI impact in device parameters was expected to decrease, becoming an insignificant effect. However, this behavior has not

been verified through experimental results for nanoscale technologies. In fact, the HCI degradation has not vanished for MOS operating at lower supply voltages, but remains significant and is also projected to get worse in future technology generations (KUFLUOGLU, 2007).

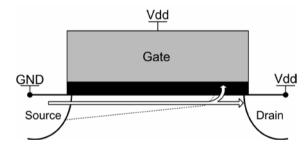

Figure 3.1 – Illustration of hot-carrier generation in NMOS transistor, and the lateral electric field in the channel (JIANG, 1998).

New theories have been introduced to explain the physical mechanisms involved in hot carrier degradation in scaling devices at low supply voltage (RAUCH. 2005). Three distinct regimes have been suggested to describe the physics involved in the transistor degradation. They representation of the lifetime degradation is proposed as function of the transistor drain current. The relations described below consider that for a fixed drain voltage  $(V_d)$ , the drain current is increased with gate voltage  $(V_g)$ , whereas the energy is lowered (GUERIN, 2007).

The first regime considers a low drain current (low  $V_g$ , high energy). In this situation, the lifetime shows to be linearly dependent to the drain current. The generated hot carriers are attracted to the interface due to the electric field with sufficient energy to break interface state.

The second degradation mode considers a medium drain current (medium  $V_g$  and energy). In this current stage, the lifetime degradation has a quadratic behavior. In this regime, the carriers are induced by impact ionization. Most of them have not enough energy to break interface bonds. However, some carriers achieve higher energy level through carrier-to-carrier interactions. In this case, these high energy carriers are able to break the bonds.

The third (and last) regime considers high drain current (high  $V_g$  and low energy). This degradation mode presents a cubic but dispersive behavior. The transition between quadratic to cubic behavior is explained by the transition from a bulk-dominated current at medium  $V_g$  to a surface-dominated current at high  $V_g$ . The carriers in this mode do not get enough energy to break a bond by a single excitation. At this regime, the carrier density close to the interface strongly increases. Considering that several carriers are required to lower the energy needed to generate an interface state, the high carrier density favors the low energy interaction between carriers and bonds.

From this last perspective, the impact of traditional channel hot carriers (CHC) and also the impact of phenomenon presented in nanometer technologies, such as cold carriers (CCC) and non-conductive hot carriers (NCHC), are considered.

#### 3.1.2 HCI Long Term Analytical Model

As mentioned previously, the HCI effect was exhaustively explored for micrometric technologies from the 1980s to the 1990s. During this time, several analytical models have been presented in the literature (TAKEDA, 1983; TAM, 1984; HU, 1985; GROESENEKEN, 1995).

One of the most accepted model, and largely used by the industry and academic community, explores the classic relation between HCI degradation and the lateral electric field presented in transistor channel. The lucky electron model (LEM) explores the field driven approach (TAM, 1984; HU, 1985). In this scope, the damage caused by HCI is related to the interface state generation ( $N_{it}$ ). This interface states are directly linked to threshold voltage degradation. The model relates the HCI degradation to the electric field at the drain ( $E_m$ ), to the drain to source current ( $I_{ds}$ ), and to the stress time (t) in a simple power law relationship, as presented in the following (GROESENEKEN, 1995):

$$\Delta N_{it} = C_1 \left[ \frac{I_{ds}}{W} \cdot \exp\left( -\frac{\Phi_{it,e}}{q \cdot \lambda_e \cdot E_m} \right) \cdot t \right]^n$$

(3.1)

where W is the channel width,  $\Phi_{it,e}$  is the critical energy for electrons create an interface state,  $\lambda_e$  is the hot-electron mean free path,  $C_1$  is a technology dependent constant, and n is widely accepted to be 0.5.

However, the LEM does not consider the importance of low energy carriers in nanometer technologies. The new energy driven theory, summarized in previous section, has been introduced to explain the carrier degradation mechanisms for nanometric devices operating at low supply voltages. The energy-driven model explores the carriers behavior at various energy levels, ranging from high-energy hot carriers to low-energy cold carriers. The model provides the device lifetime ( $\tau$ ) as presented in the following (BRAVAIX, 2009):

$$\frac{1}{\tau} = C_1 \cdot \left(\frac{I_{ds}}{W}\right)^{a_1} \cdot \left(\frac{I_{bs}}{I_{ds}}\right)^m + C_2 \cdot \left(\frac{I_{ds}}{W}\right)^{a_2} \cdot \left(\frac{I_{bs}}{I_{ds}}\right)^m + C_3 \cdot V_{ds}^{a_3/2} \cdot \left(\frac{Ids}{W}\right)^{a_3} \cdot \exp\left(\frac{-E_{emi}}{K_B \cdot T}\right)$$

(3.2)

where  $C_1$ ,  $C_2$ ,  $C_3$  are three technology parameters determined by their dominant mode, i.e., high, medium and low energy modes, respectively.  $E_{emi}$  is the activation energy. The parameters m,  $a_1$ ,  $a_2$ ,  $a_3$  are extracted from experimental data. More details can be obtained in (BRAVAIX, 2009).

The terms in Equation (3.2) correspond to the high, medium and low energy modes, described in previous section, and present excellent fit with experimental results. However, for a design point-of-view, the previous model is not practical. Although hot carrier injection is a cumulative effect in nature, the previous approaches turn too complex the analysis of dynamic degradation involved in circuit normal operation conditions. A long term cumulative model is required to obtain practical estimative of the transistor degradation over a long period of time. A simple empirical model that captures the long term  $V_{th}$  transistor degradation is expressed by (TAKEDA, 1983):

$$\Delta V_{th} = A \cdot t^n \tag{3.3}$$

where, A is a technology dependent constant related to the number of carriers generated by impact ionization, t is time, and n reflect the most severe hot carrier mechanism. This model is still valid, and it is also being used to capture transistor aging-induced variability (MAGNONE, 2011).

During digital circuit operation, the transistor is not under degradation all the time. In fact, the transistor suffers HCI degradation only when its input is switching (HUARD, 2007). Also, the more severe degradation occurs in transistors with maximum drain-to-source voltage (GUERIN, 2008). Hence, a derived close form expression for  $V_{th}$  degradation due to HCI can be given by:

$$\Delta V_{th} = A \cdot (TSwP \cdot t)^n \tag{3.4}$$

Similar to the approach proposed in (TAKEDA, 1983), the proposed solution considers a specific technology node and a given set of environmental conditions, that are important to obtain the technology dependent constants A and n. To capture the switching activity, the degradation is expressed as a function of the transistor switching probability (TSwP).

## 3.2 Negative Bias Temperature Instability

Negative bias temperature instability (NBTI) is a degradation phenomenon occurring mainly in PMOS transistor, investigated since the late 1960s. Even though the exact degradation causes are not well understood yet, it is now commonly admitted that under a constant negative gate voltage bias and elevated temperature a built up of interface traps and positive charges occur either at the oxide-substrate interface and in the oxide layer (HUARD, 2006; GRASSER, 2011). PMOS transistors are mostly affected, since these devices are negatively biased when they are conducting. NBTI effect increases the PMOS transistor threshold voltage ( $V_{th}$ ) over time, reducing the device drive current and circuit speed (PAUL, 2006).

#### 3.2.1 NBTI Physical Mechanism

There is a constant effort during last decade to advance in the comprehension of NBTI degradation. Several experiments with different characterization methodologies and stress conditions have been used to try to identify the physical mechanisms lying behind the NBTI degradation. It can be considered a consensus that NBTI degradation results from the superposition of many individual processes. Although there is no single physical mechanism that is comprehensive enough to explain all the behaviors related to the NBTI phenomenon, two solutions are the most accepted. Those solutions are

proposed considering experimental data extracted from characterization circuits (DENAIS, 2004; SHEN, 2006; KARL, 2008; KEANE, 2010).

An initial approach to deal with NBTI behavior was proposed in 1977, and consists in a hydrogen-diffusion controlled interface state creation mechanism (JEPPSON, 1977). This reaction diffusion theory has been the bulk of the literature for several years. From this theory, it is arguably believed that the increase of  $V_{th}$  due NBTI is caused by broken Si-H or Si-H<sub>2</sub> bonds. These broken bonds are induced by the electric field generated by the positive holes from the PMOS transistor channel and the voltage applied to the transistor gate. H atoms diffuse away to the oxide, creating positive interface traps, which cause the increasing in  $V_{th}$ . Each new experimental measurement reveals new details related to NBTI degradation behavior, and the reaction-diffusion theory has been reviewed and adapted (STATIS, 2005; ALAM, 2007).

However, some experiments over new technologies have suggested that the hydrogen diffusion was dispersive (KACZER, 2005; GRASSER, 2008). From this perspective, the interface traps creation is not the sole source of NBTI degradation but a second mechanism also contribute to the  $V_{th}$  increment. This second approach is based on the hole trapping/detrapping theory. This mechanism involved in  $V_{th}$  increment can be described by tunneling of channel carriers into oxide defects induced by the electric field through the gate oxide when the PMOS transistor is negative biased. The oxide defects can either pre-exist in the transistor structure or be created by electrical stress. Transistors with high- $\kappa$  dielectric have higher density of pre-existing defects. From this point-of-view, hole trapping/detrapping is becoming the dominant contributor to NBTI degradation (KACZER, 2010).

Another important characteristic involved in NBTI effect is its dynamic behavior. There are two phases of NBTI for a PMOS transistor behavior depending on its bias condition. The first phase is usually referred as "stress". In this phase occurs the device degradation. It occurs when the transistor is negative biasing, the gate voltage  $V_g = 0$  and drain-to-source voltage  $V_{gs} = -V_{dd}$ . An elevated electric field is experience through the gate oxide with this bias condition. From reaction diffusion mechanism, positive interface traps are accumulating over the stress time with H diffusing towards the gate. The hole trapping are associated to the carrier tunneling injection and trapping in gate oxide. The second phase is usually referred as "recovery". The PMOS bias condition on this phase are  $V_g = V_{dd}$ , and  $V_{gs} = V_{dd}$ . The electric field is no more present through the gate oxide, and no new interface traps are generated or carriers are tunneling. Instead, the carriers trapped in the oxide are emitted back to the substrate and the H diffuses back and recomposes the broken Si-H or Si-H<sub>2</sub> interface bonds. Figure 2.5 illustrates the NBTI dynamic behavior.

The NBTI dynamic behavior allows the decomposition of NBTI degradation in two different components. The first component is defined as permanent or universal degradation, and the other one is a non-universal or recoverable degradation (HUARD, 2006; ISLAM, 2011). The permanent degradation is associated to the interface defect generation, while the hole trapping is associated to the non-universal component. This approach is consistently explained using the reaction-diffusion theory as the universal slow mechanism and the hole trapping as the non-universal fast mechanism. From this approach, the hole trapping is at the origin of the strong recovery effect and the reaction diffusion reflect the long term degradation.

Those efforts in understanding the theory behind NBTI effect and developing models to estimate the degradation have to be supported by practical measurements in order to be effective. Those techniques usually use specialized equipment to access individual devices or explore the concept of on-chip monitors that are capable to measure some parameter which reflects the degradation (DENAIS, 2004; SHEN, 2006; KARL, 2008; KEANE, 2010). Since NBTI degradation is perceptible in long period of time (usually years), the degradation is usually accelerated by raising the power supply  $(V_{dd})$  (KIM, 2008). To correlate the accelerate measurements to real behavior is another challenge involved in this process. The sensors have also to be able to measure the static and dynamic behaviors. Furthermore, the measurements should explore a range of stress voltages, temperatures and time. The characterization methodologies are in constant investigation, and they are the most responsible to the advance in NBTI comprehension (HUARD, 2006).

#### 3.2.2 NBTI Long Term Analytical Model

NBTI degradation models are based on the physical mechanism theory previously discussed and on the experimental data findings. From a historical perspective, the dynamic behavior of NBTI degradation is the main challenge related to NBTI models. It is inherently complicated since NBTI exhibits the unique property of both stress and recovery behavior during circuit dynamic operation. The dynamic models based on the reaction diffusion theory explore the number of interface traps to obtain the  $V_{th}$  degradation (ALLAM, 2005; VATTIKONDA, 2006; ALAM, 2007). The models that explore hole trapping/detrapping theory use the holes trapped into oxide defects to estimate the  $V_{th}$  change (GRASSER, 2011). The following equation has been proposed in (ISLAM, 2011), and it is one of the models that explore both theories to obtain the  $V_{th}$  degradation ( $\Delta V_{th}$ ), as expressed by:

$$\Delta V_{th} = \Delta V_{IT} + \Delta V_{HT} + \Delta V_{OT} \tag{3.5}$$

where  $\Delta V_{IT}$ ,  $\Delta V_{HT}$ , and  $\Delta V_{OT}$  refer to the contributions to  $\Delta V_{th}$  from interface traps, preexisting oxide defects, and electrical generated oxide defects, respectively.  $\Delta V_{IT}$ ,  $\Delta V_{HT}$ , and  $\Delta V_{OT}$  basis can be obtained in (ISLAM, 2011).

The NBTI dynamic degradation models estimate accurately the  $V_{th}$  degradation from cycle to cycle. However, under regular operating conditions, the  $V_{th}$  degradation due to NBTI is perceptible in a long term, e.g. over a few years. Considering long term prediction, that is the focus of this work, it is unpractical to run cycle to cycle simulation for the estimation of transistor degradation. Hence, a derived close form expression for  $V_{th}$  degradation that considers a specific technology node and a given set of environmental conditions could be expressed by:

$$\Delta V_{th_{-}NBTI} = A.(TSP.t)^{n} \tag{3.6}$$

where A is a technology dependent constant, t is time, and n is the NBTI time exponential constant. TSP is defined as the probability of PMOS transistor in negative biasing. It is a function of the input signal probability and the position of the transistor in the arrangement (BUTZEN, 2010). A procedure to obtain the TSP from any transistor netlist is presented in Chapter 5.

The used model is derived by the one proposed in (WANG, 2007). The main difference is in the *TSP* term. (WANG, 2007) uses the input signal probability instead of TSP. The motivation to use TSP instead only input signal probability is to explore the

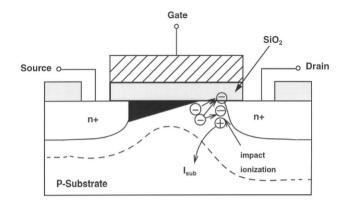

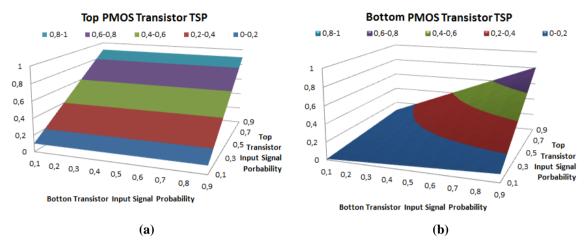

influence of the transistor position in the arrangement. The plots depicted in Figure 3.2 illustrate the *TSP* of the top and bottom transistor that are present in the pull-up stack of a NOR gate, according to input signal probabilities. The top transistor in the stack, i.e. the one connected to the power supply, has its degradation condition controlled only by its input signal. The bottom transistor has to consider the combination of both input signal probabilities (KUMAR, 2007).

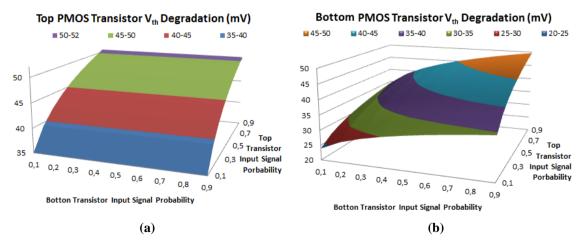

Figure 3.2 – Transistor stress probability (TSP) for two stacked PMOS transistor of a NOR gate: (a) top transistor (connected to power supply); (b) bottom transistor (connected to output node).

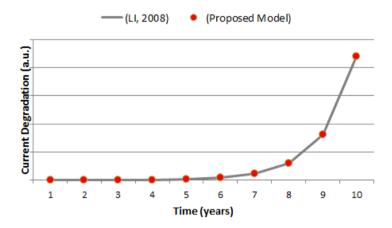

Figure 3.3 presents the  $V_{th}$  degradation results for the two stacked PMOS transistors of a NOR gate. The data illustrated in the plots consider a maximum  $V_{th}$  degradation of 50 mV, the probabilities presented in Figure 3.2 and the technology dependent parameters applying the values used in (WANG, 2007):  $A = 3.9 \times 10^{-3}$  and n = 1/6. From the plots is possible to verify the model fidelity from the experimental data reported in the literature (DENAIS, 2004; SHEN, 2006; KARL, 2008; KEANE, 2010). The importance of considering TSP instead of only input signal probabilities are also evident. If only input signal were considered, the plots might have the same behavior. However, the difference between both plots achieves 47% in the worst case.

Figure 3.3 – Vth degradation of two stacked PMOS transistor of NOR gate according to long-term model presented in Equation (3.6) and the TSP values illustrated in Figure 3.2.

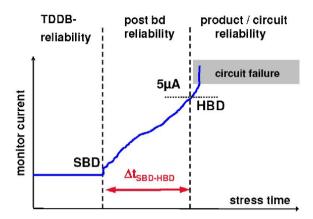

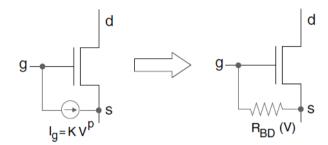

#### 3.3 Time Dependent Dielectric Breakdown

Another reliability issue in nanoscaled devices is the time dielectric dependent breakdown (TDDB). This mechanism degrades the isolation properties of gate dielectric, increasing the tunneling current across the transistor gate terminal. TDDB is an increasing concern in digital circuit design as gate dielectric thickness is scaling down and the supply voltage does not follow that aggressive scaling. The result is an increasing in the electric field through the gate oxide for every new technology node, causing a large TDDB degradation. The following sections review the physical concepts behind TDDB and present a long term analytical model that will be used in this work.

#### 3.3.1 TDDB Physical Mechanism

Although the TDDB effect has been studied for decades, many of the physical details behind TDDB are still under debate. However, there is a general consensus that the large electric field across the transistor gate oxide is the direct cause of TDDB.