# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL ESCOLA DE ENGENHARIA PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA

#### ERIK SCHÜLER

## UMA INTERFACE PARA O AUMENTO DA FAIXA DE FREQÜÊNCIAS DE OPERAÇÃO DE FPAAS

#### ERIK SCHÜLER

### UMA INTERFACE PARA O AUMENTO DA FAIXA DE FREQÜÊNCIAS DE OPERAÇÃO DE FPAAS

Dissertação de mestrado apresentada ao Programa de Pós-Graduação em Engenharia Elétrica (PPGEE), da Universidade Federal do Rio Grande do Sul (UFRGS), como parte dos requisitos para a obtenção do título de Mestre em Engenharia Elétrica.

Área de concentração: Automação e Instrumentação Eletro-Eletrônica

ORIENTADOR: Prof. Dr. Luigi Carro

Porto Alegre

(2004)

#### ERIK SCHÜLER

# UMA INTERFACE PARA O AUMENTO DA FAIXA DE FREQÜÊNCIAS DE OPERAÇÃO DE FPAAS

Esta dissertação foi julgada adequada para a obtenção do título de Mestre em Engenharia Elétrica e aprovada em sua forma final pelo Orientador e pela Banca Examinadora.

|     | Orientador:                                                            |  |  |

|-----|------------------------------------------------------------------------|--|--|

|     | Prof. Dr. Luigi Carro, UFRGS                                           |  |  |

|     | Doutor pelo Programa de pós-graduação em Ciência da                    |  |  |

|     | Computação, CPGCC, UFRGS, Brasil                                       |  |  |

|     |                                                                        |  |  |

| Ban | nca Examinadora:                                                       |  |  |

|     |                                                                        |  |  |

|     | Prof. Dr. Antonio Petraglia, COPPE - UFRJ                              |  |  |

|     | Doutor pela University of California, EUA.                             |  |  |

|     |                                                                        |  |  |

|     | Prof. Dr. Sergio Bampi, CPGC – UFRGS                                   |  |  |

|     | Doutor pela Stanford University, EUA.                                  |  |  |

|     |                                                                        |  |  |

|     | Prof. Dr. Altamiro Amadeu Susin, PPGEE - UFRGS                         |  |  |

|     | Doutor pelo Institut National Polytechnique de Grenoble, INPG, França. |  |  |

|     |                                                                        |  |  |

|     |                                                                        |  |  |

|     | Coordenador do PPGEE:                                                  |  |  |

|     | Prof. Dr. Carlos Eduardo Pereira                                       |  |  |

#### **DEDICATÓRIA**

Dedico este trabalho ao meu pai Érico, minha mãe Isolda e minha irmã Ingrid, por todas as coisas boas nestes 27 anos. A minha avó Ezelinda, por ser minha segunda mãe. A toda minha família em Porto Alegre, Rio de Janeiro e Veranópolis, que apesar da distância, sempre acreditaram em mim. A minha namorada Carolina, pelos dez anos de companhia, amor e amizade, e pelos próximos que virão.

#### **AGRADECIMENTOS**

Agradeço ao Programa de Pós-Graduação em Engenharia Elétrica da UFRGS, PPGEE, pela oportunidade de realização deste trabalho, assim como à CAPES e à CEEE pela provisão das bolsas de mestrado.

Agradeço aos professores da banca examinadora dessa dissertação por terem aceito o convite e aos professores da Graduação e Pós-Graduação do DELET por todo o conhecimento compartilhado e auxílio.

Agradeço em especial ao professor e orientador Dr. Luigi Carro pelos mais de quatro anos de orientação, ensino e amizade durante a bolsa de Iniciação Científica e o Mestrado.

Agradecimento aos colegas de Mestrado e dos laboratórios LAPROT, SIAM, LAPSI e LACOM pela ajuda na preparação deste e de vários outros trabalhos, e pelos vários momentos de descontração. Aos meus amigos de Veranópolis e Porto Alegre, obrigado pelo apoio e pelos vários anos de amizade.

Enorme agradecimento a minha namorada Carolina pela paciência e compreensão durante todos esses anos em que a distância não foi obstáculo. A sua família Alzir, Neca, Letícia e D. Ida, muito obrigado pelo acolhimento, amizade e apoio.

Acima de tudo, agradeço a minha família, que sempre me apoiou em tudo, dando incentivo e conselhos nos momentos de indecisão. Em especial ao meu pai por nunca medir esforços para me proporcionar absolutamente tudo que sempre precisei, a minha irmã pelos vários anos de companhia em todos os cantos do país, ainda mais aqui em Porto Alegre, e pelo sobrinho e afilhado Lucca. A minha mãe, que na hora que mais precisei estava lá pra me dar a mão, agradeço eternamente.

#### **RESUMO**

O crescente avanço nas mais diversas áreas da eletrônica, desde instrumentação em baixa freqüência até telecomunicações operando em freqüências muito elevadas, e a necessidade de soluções baratas em curto espaço de tempo que acompanhem a demanda de mercado, torna a procura por circuitos programáveis, tanto digitais como analógicos, um ponto comum em diversas pesquisas. Os dispositivos digitais programáveis, que têm como grande representante os *Field Programmable Gate Arrays* (FPGAs), vêm apresentando um elevado e contínuo crescimento em termos de complexidade, desempenho e número de transistores integrados, já há várias décadas. O desenvolvimento de dispositivos analógicos programáveis (*Field Programmable Analog Arrays – FPAAs*), entretanto, esbarra em dois pontos fundamentais que tornam sua evolução um tanto latente: a estreita largura de banda alcançada, conseqüência da necessidade de um grande número de chaves de programação e reconfiguração, e a elevada área consumida por componentes analógicos como resistores e capacitores, quando integrados em processos VLSI.

Este trabalho apresenta uma proposta para aumentar a faixa de freqüências das aplicações passíveis de serem utilizadas tanto em FPAAs comerciais quanto em outros FPAAs, através da utilização de uma interface de translação e seleção de sinais, mantendo características de programabilidade do FPAA em questão, sem aumentar em muito sua potência consumida.

A proposta, a simulação e a implementação da interface são apresentadas ao longo desta dissertação. Resultados de simulação e resultados práticos obtidos comprovam a eficácia da proposta.

Palavras-chaves: FPGA analógico. FPAA. FPMA. SoC. Translação de frequência. Mixer.

#### **ABSTRACT**

The increasing advance in several areas of electronics, from low frequency instrumentation to telecommunications operating in very high frequencies, and the necessity of low cost solutions in a short space of time, following the demand of the market, makes the search for digital and analog programmable circuits a common point in many researches. Digital programmable devices, which have as a great representant Field Programmable Gate Arrays (FPGAs) devices, have shown a high and continuous increase in terms of complexity, performance and number of integrated transistors for many decades. The development of analog programmable devices (Field Programmable Analog Arrays – FPAAs), however, stops in two fundamental points that make their evolution slow: the narrow bandwidth reached, consequence of the necessity of a great number of programming and configuration switches, and the huge area occupied for analog components as resistors and capacitors, when integrated in a VLSI process.

This work presents a proposal to increase the frequency range of the applications that can be used also with commercials FPAAs and others FPAAs, through the use of an interface to translate and select signals, keeping the programmability characteristics of the FPAA, without increasing so much the dissipated power.

The proposal, simulation and implementation of the interface are presented in this dissertation. The simulations and practical results obtained show the proposal efficiency.

Keywords: Analog FPGA. FPAA. FPMA. SoC. Frequency translation. Mixer.

### SUMÁRIO

| LISTA DE ILUSTRAÇÕES                                            | 9      |

|-----------------------------------------------------------------|--------|

| LISTA DE TABELAS                                                | 12     |

| LISTA DE ABREVIATURAS                                           | 13     |

| 1 INTRODUÇÃO                                                    | 15     |

| 2 O CONTEXTO DOS FPAAS                                          | 19     |

| 2.1 AMPLIFICADOR OPERACIONAL E AMPLIFICADOR DE TRANSCONDUTÂNCIA | 22     |

| 2.2 CARREGADOR DE CORRENTE                                      | 22     |

| 2.3 CAPACITOR CHAVEADO                                          |        |

| 2.4 CORRENTE CHAVEADA                                           |        |

| 2.5 OUTRAS TOPOLOGIAS                                           |        |

| 3 CARACTERIZAÇÃO DE FPAAS                                       |        |

| 3.1 AMPLIFICADOR OPERACIONAL E COMPONENTES PASSIVOS             |        |

| 3.2 CAPACITOR CHAVEADO                                          |        |

| 3.3 CARREGADOR DE CORRENTE                                      |        |

| 3.4 SOLUÇÃO MISTA                                               |        |

| 4 PROPOSTA DE INTERFACE PARA AUMENTO DA FAIXA DE FREQU          | ÜÊNCIA |

| DE OPERAÇÃO DE FPAAS                                            |        |

| 4.1 MIXERS E TRANSLAÇÃO DE FREQÜÊNCIAS                          |        |

| 4.2 ESTRUTURAS DIFERENCIAIS                                     |        |

| 4.3 MIXER PROPOSTO                                              | 47     |

| 4.3.1 Determinação da topologia do mixer                        |        |

| 4.3.2 Dimensionamento dos transistores                          |        |

| 4.3.3 Análise de utilização de NMOS versus porta de transmissão |        |

| 4.3.4 Influência das capacitâncias parasitas                    | 59     |

| 4.3.5 Reduzindo os efeitos das capacitâncias parasitas          |        |

| 4.4 FILTRO PASSA-FAIXA PROPOSTO                                 |        |

| 4.4.1 Filtro biquadrático de Tow-Thomas                         |        |

| 4.4.2 Filtro biquadrático Gm-C                                  |        |

| 5 RESULTADOS PRÁTICOS OBTIDOS COM FPAAS COMERCIAIS              | 80     |

| 5.1 FPAA LATTICE                                                | 81     |

| 5.2 FPAA ANADIGM                                                |        |

| 6 ANÁLISE DE POTÊNCIA, ÁREA E FREQÜÊNCIA                        |        |

| 6.1 ANÁLISE DA FAIXA DE FREQÜÊNCIA DE OPERAÇÃO                  |        |

| 6.2 ANÁLISE DA ÁREA OCUPADA                                     |        |

| 6.3 ANÁLISE DA POTÊNCIA DISSIPADA                               |        |

| 7 CONCLUSÃO                                                     |        |

| REFERÊNCIAS                                                     |        |

| APÊNDICE A: MODELOS AMS 0,35μ DOS TRANSISTORES                  |        |

| A1: Transistor NMOS                                             |        |

| A2: TRANSISTOR PMOS.                                            |        |

|                                                                 |        |

| APÊNDICE B: DESCRIÇÃO SPICE DOS CIRCUITOS UTILIZADOS NAS            |

|---------------------------------------------------------------------|

| SIMULAÇÕES118                                                       |

| B.1 AMPLIFICADOR OPERACIONAL SINGLE-ENDED118                        |

| B.2 CARREGADOR DE CORRENTE118                                       |

| B.3 TRANSCONDUTOR DE NAUTA119                                       |

| B.4 CHAVE TIPO PORTA DE TRANSMISSÃO119                              |

| B.5 FILTRO BIQUADRÁTICO COM OPAMP119                                |

| B.6 AMPLIFICADOR INVERSOR A CAPACITOR CHAVEADO120                   |

| B.7 FILTRO BIQUADRÁTICO COM CARREGADOR DE CORRENTE120               |

| B.8 MIXER PASSIVO COM NMOS E COM PORTA DE TRANSMISSÃO121            |

| B.9 FILTRO GM-C                                                     |

| APÊNDICE C: ARQUIVOS EM MATLAB® PARA CÁLCULOS DE                    |

| CAPACITÂNCIAS PARASITAS E ANÁLISES DOS ESPECTROS DE MIXERS123       |

| C.1 MULTIPLICADOR IDEAL                                             |

| C.2 CÁLCULO DAS CAPACITÂNCIAS PARASITAS                             |

| APÊNDICE D: ESTRUTURAS INTERNAS DOS FPAAS COMERCIAIS                |

| UTILIZADOS                                                          |

| D.1 LATTICE ISPPAC10 COMO PASSA-FAIXA127                            |

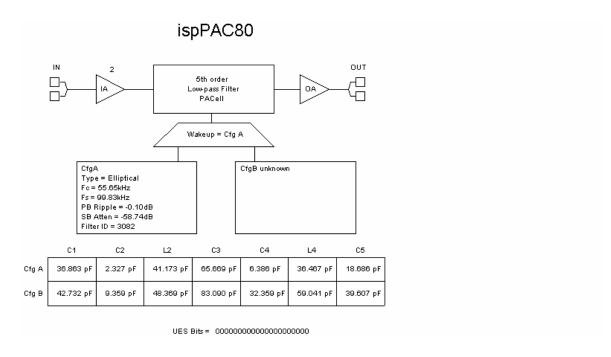

| D.2 LATTICE ISPPAC80 COMO PASSA-BAIXA                               |

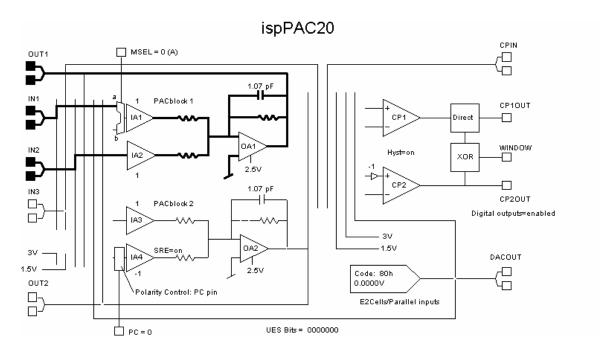

| D.3 LATTICE ISPPAC20 COMO SOMADOR128                                |

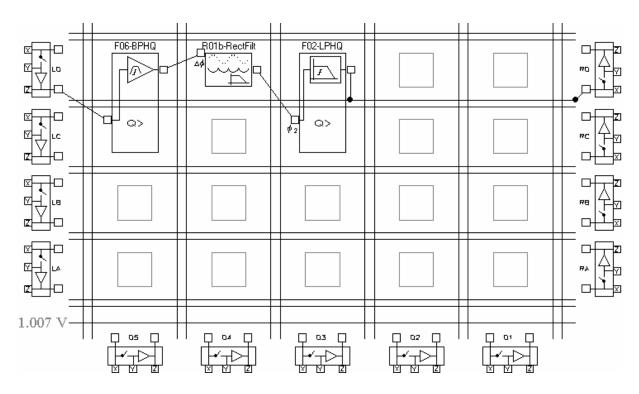

| D.4 ANADIGM AN10E40 COMO DEMODULADOR AM129                          |

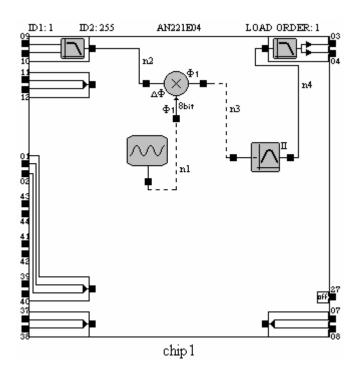

| D.5 ANADIGM AN221E04 COMO CONDICIONADOR PARA PONTE DE WHEATSTONE129 |

| APÊNDICE E: SIMULAÇÕES DOS EXPERIMENTOS PRÁTICOS131                 |

| E.1 FILTRO PASSA-FAIXA USANDO ISPPAC10131                           |

| E.2 FILTRO PASSA-BAIXA USANDO ISPPAC80                              |

| E.3 SOMADOR USANDO ISPPAC20132                                      |

| E.4 DEMODULADOR AM USANDO AN10E40                                   |

| E.5 PONTE DE WHEATSTONE USANDO AN221E04                             |

| APÊNDICE F: SIMULAÇÕES SPICE DOS CIRCUITOS UTILIZADOS135            |

| F.1 CAB IMPLEMENTANDO FILTRO PASSA-BAIXA                            |

| F.2 CAB IMPLEMENTANDO FILTRO PASSA-ALTA                             |

| F.3 CAB IMPLEMENTANDO AMPLIFICADOR-INVERSOR                         |

| F.4 CAB IMPLEMENTANDO INTEGRADOR                                    |

| F.5 CAB IMPLEMENTANDO DIFERENCIADOR                                 |

| F.6 AMPLIFICADOR OPERACIONAL SINGLE-ENDED                           |

| F.7 CARREGADOR DE CORRENTE                                          |

| F 8 TRANSCONDITION DE NAUTA                                         |

### LISTA DE ILUSTRAÇÕES

| Figura 1 | . Relação produtividade e projeto, conforme (ERNST, 2000)                                | 15  |

|----------|------------------------------------------------------------------------------------------|-----|

| Figura 2 | 2. Possível estrutura de um <i>System on Chip</i> .                                      | 16  |

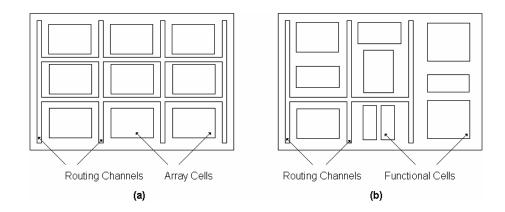

| Figura 3 | 3. Estrutura de um FPAA segundo (D'MELLO, 1998)                                          | 20  |

| Figura 4 | L. Estrutura interna para (a) rede de interconexão e (b) CAB, segundo (LEE, 1998).       | 20  |

| Figura 5 | 5. Comparação entre topologias de FPAAs, conforme (KLEIN, 1998)                          | 21  |

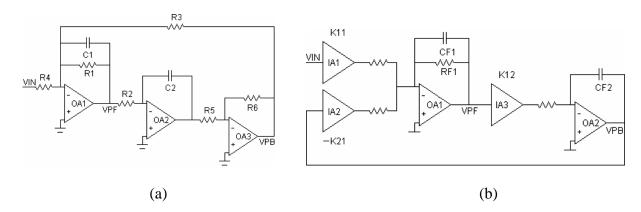

| Figura 6 | 6. (a) Filtro biquadrático com amplificador operacional e componentes passivo; (b)       |     |

|          | equivalente realizado pelo ispPAC10, conforme (LATTICE, 2000a)                           | 27  |

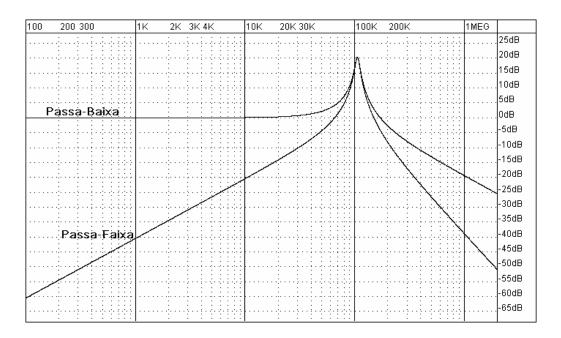

| Figura 7 | 7. Diagrama de Bode simulado para o filtro a amplificador operacional e elementos        |     |

|          | passivos apresentado na figura 6(a).                                                     | 28  |

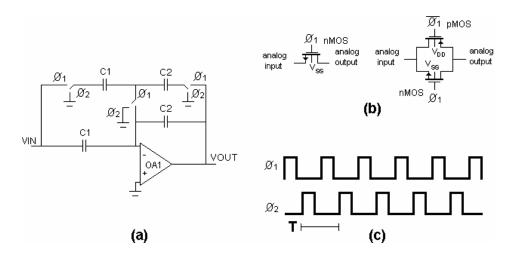

| Figura 8 | 3. (a) Amplificador inversor a capacitor chaveado conforme (ANADIGM, 2002); (b           | )   |

|          | chaves analógicas e portas de transmissão; (c) sinais de controle das chaves             | 30  |

| Figura 9 | 9. Simulação do amplificador a capacitor chaveado apresentado na figura 8(a)             | 31  |

| Figura 1 | 0.(a) Filtro de segunda ordem com carregador de corrente, conforme (PREMONT,             |     |

|          | 1998) e (b) carregador de corrente utilizado                                             | 33  |

| Figura 1 | 1. Diagrama de Bode simulado para o filtro a carregador de corrente apresentado na       | l   |

|          | figura 4.                                                                                | 34  |

| Figura 1 | 2.(a) Estrutura e (b) funcionamento do FPMA com conversor $\Sigma\Delta$                 | 36  |

| Figura 1 | 3. Proposta de interface para alocação de sinais.                                        | 38  |

| Figura 1 | 4. Proposta de translação de sinais para uma dada freqüência de operação de um           |     |

|          | FPAA qualquer.                                                                           |     |

| Figura 1 | 5. Exemplos de mixers ativos e passivos, conforme (LEUNG, 2002; RAZAVI, 1998)            | 3). |

|          | 42                                                                                       |     |

| Figura 1 | 6. Representação de um mixer com seus sinais de entrada (RF), do oscilador local         |     |

|          | (LO) e de saída (IF).                                                                    |     |

| Figura 1 | 7. Espectro da multiplicação de duas senóides e uma senóide e uma onda quadrada.         | 45  |

| -        | 8. Par diferencial bipolar, conforme (RAZAVI, 1998).                                     |     |

| _        | 9. Primeira estrutura proposta para o mixer                                              |     |

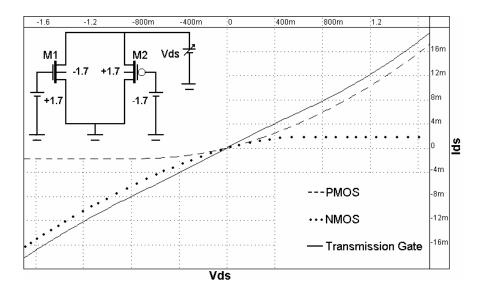

|          | 20. Simulação de curva Ids <i>versus</i> Vds para transistores NMOS e PMOS               |     |

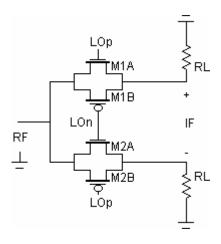

| _        | 21. Segunda estrutura proposta para o mixer                                              | 51  |

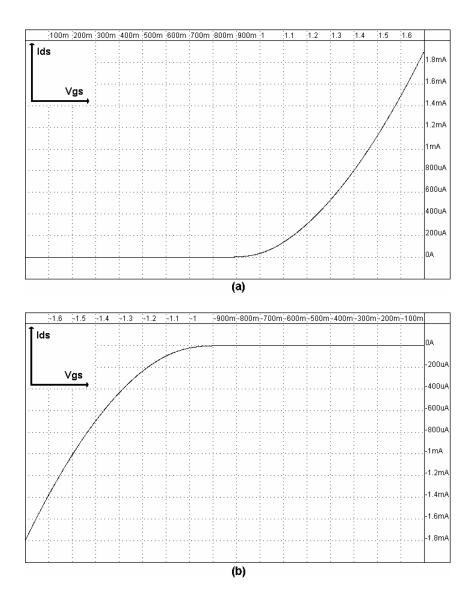

| Figura 2 | 22. Simulação de curva Vgs <i>versus</i> Ids, para obtenção da tensão de limiar (Vt) dos |     |

|          | transistores (a) NMOS e (b) PMOS.                                                        |     |

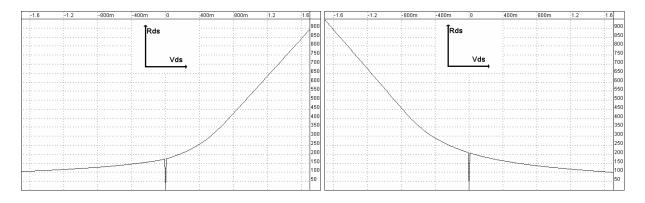

| Figura 2 | 23. Simulação da variação de Rds com a tensão Vds para (a) o NMOS e (b) PMOS             | 55  |

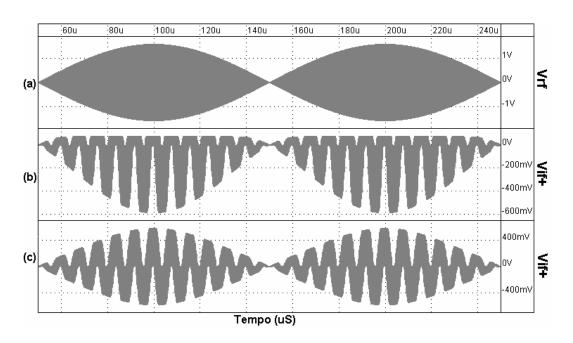

| Figura 2 | 24. Simulação para (a) sinal de entrada e sinais de saídas para mixer usando (b) dois    |     |

|          | transistores NMOS e (c) dois transmission gates                                          | 56  |

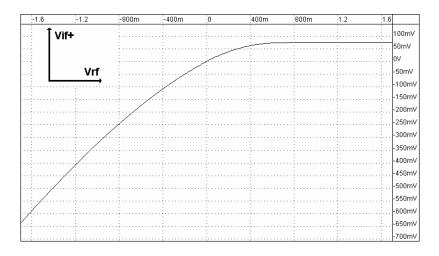

| Figura 2 | 25. Simulação da variação da tensão de entrada Vrf <i>versus</i> tensão de saída Vif+ do |     |

|          | mixer com chaves NMOS                                                                    | 58  |

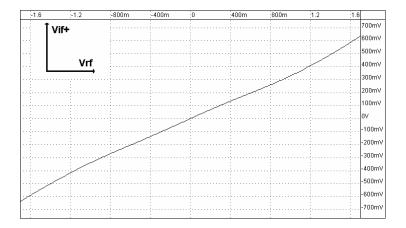

| Figura 2 | 26. Simulação da variação da tensão de entrada Vrf <i>versus</i> tensão de saída Vif+ do |     |

|          | mixer com chaves formadas por portas de transmissão                                      | 58  |

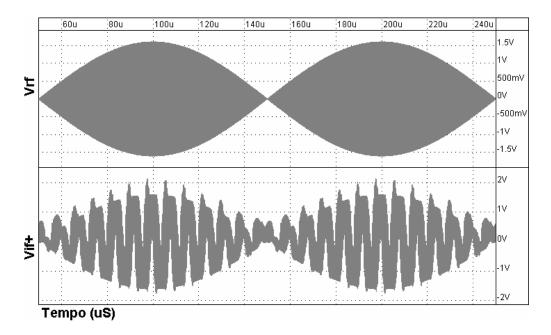

| Figura | 27 | Simulação para sinal de entrada e saída para o mixer de portas de transmissão con carga de valor elevado na saída.           |    |

|--------|----|------------------------------------------------------------------------------------------------------------------------------|----|

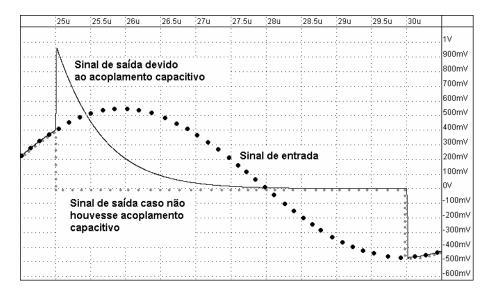

| Figura | 28 | Simulação de curvas de descarga das capacitâncias parasitas dos transistores do mixer.                                       |    |

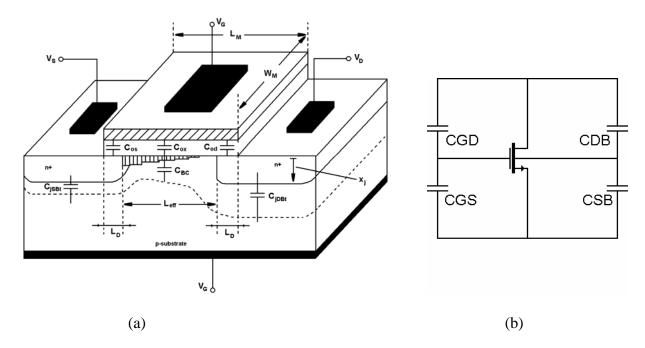

| Figura | 29 | .(a) Modelo tridimensional do transistor MOS com capacitâncias parasitas e (b) capacitâncias terminais.                      |    |

| Figura | 30 | Interface com carga de saída de valor baixo e buffer de entrada                                                              |    |

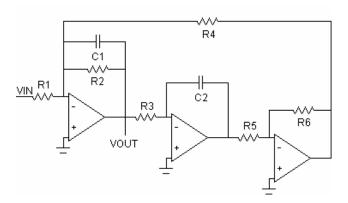

| _      |    | Filtro biquad de Tow-Thomas implementado com rede RC, conforme                                                               |    |

| C      |    | (SCHAUMANN, 2001)                                                                                                            | 67 |

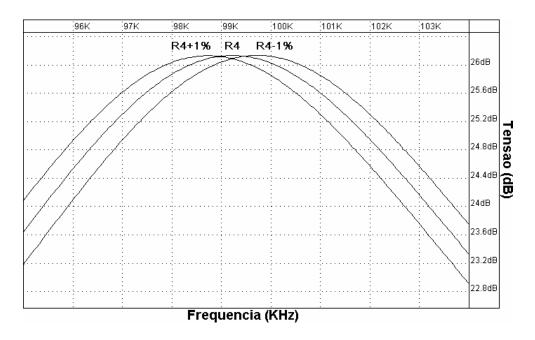

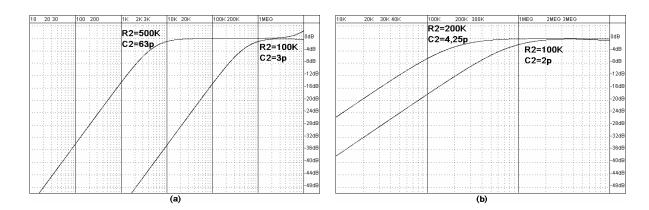

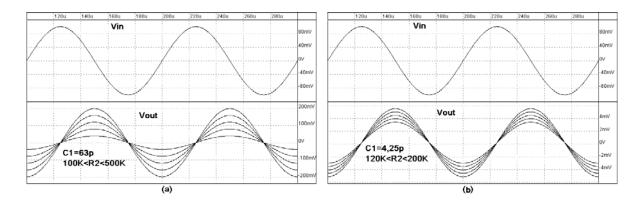

| Figura | 32 | Simulação da variação da frequência de corte com a variação de R4                                                            |    |

|        |    | Filtro biquad de Tow-Thomas implementado com MOSFET-C, conforme (SCHAUMANN, 2001)                                            |    |

| Figura | 34 | Simulação da variação da frequência de corte com a variação do offset do sinal de                                            |    |

| 8      |    | entrada                                                                                                                      |    |

| Figura | 35 | Filtro biquad de Tow-Thomas implementado com capacitor chaveado, conforme (SEDRA, 1991)                                      |    |

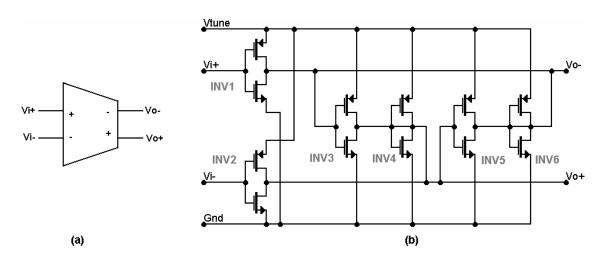

| Figura | 36 | (a) Símbolo para o transcondutor diferencial conforme (SCHAUMANN, 2001) e                                                    |    |

| C      |    | (b) transcondutor diferencial de Nauta, conforme (ANDREANI, 2002)                                                            | 75 |

| Figura | 37 | .Filtro de segunda ordem Gm-C, conforme (SCHAUMANN, 2001)                                                                    | 76 |

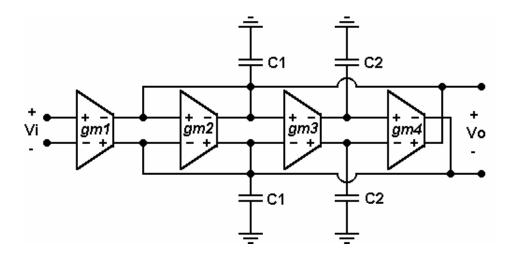

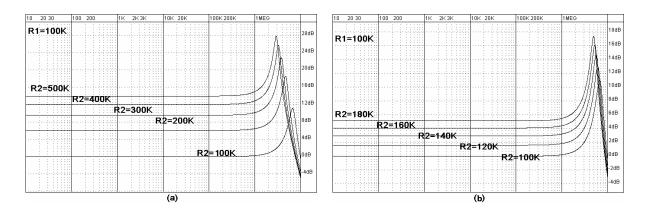

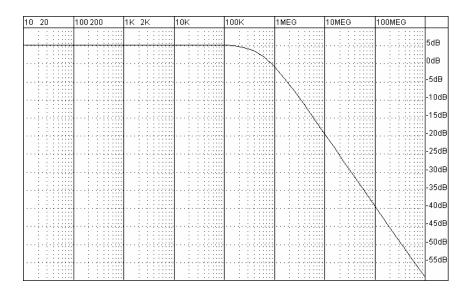

| _      |    | Simulação de (a) variação do ganho do filtro Gm-C com a variação $gm_I$ , (b)                                                |    |

| C      |    | variação do fator de qualidade com variação de $gm_2$ e (c) variação da freqüência corte com a variação de $gm_3$ e $gm_4$ . |    |

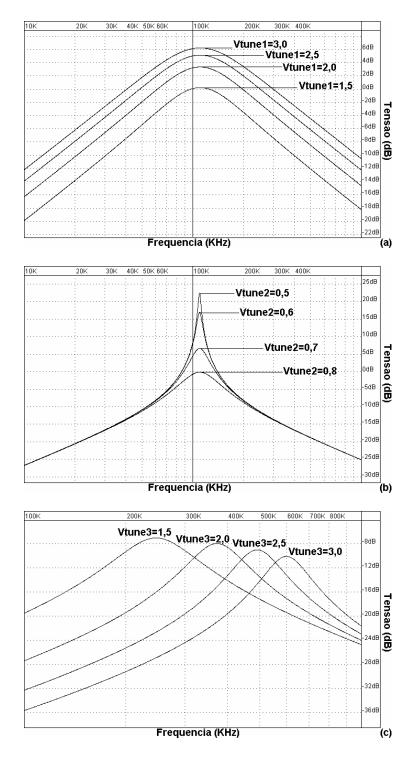

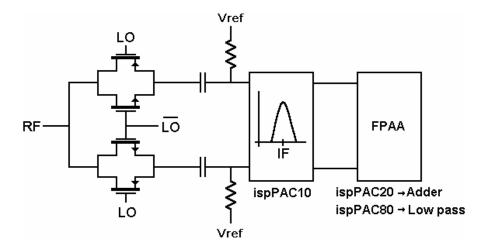

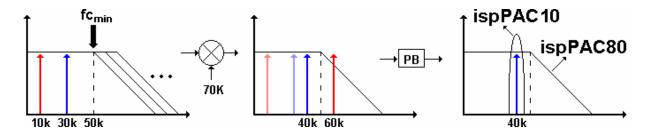

| Figura | 39 | Estrutura do mixer, filtro passa-faixa e aplicação, usando FPAAs da Lattice                                                  |    |

|        |    | Sequência para filtragem utilizando FPAA da Lattice                                                                          |    |

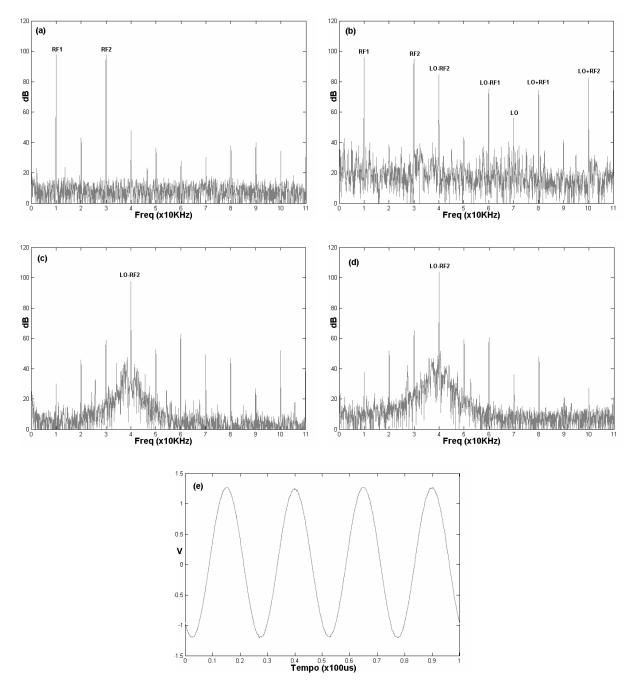

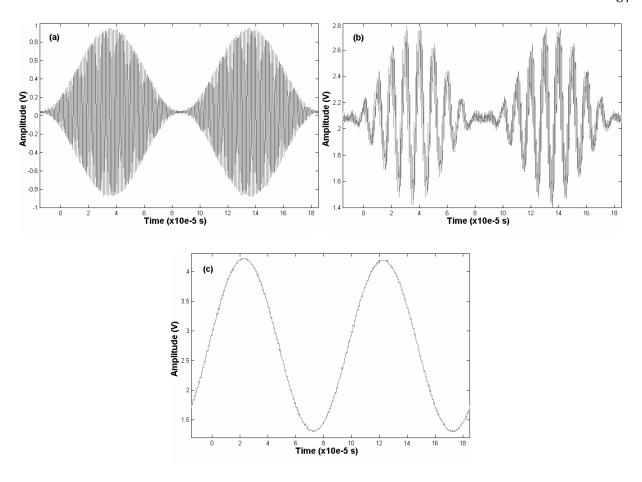

|        |    | . Medidas mostrando (a) FFT do sinal de entrada (10KHz+30KHz); (b) FFT do sin                                                |    |

| υ      |    | mixado; (c) FFT do sinal filtrado pelo passa-faixa em 40KHz; (d) FFT do sinal                                                |    |

|        |    | filtrado pelo passa-baixa em 55,65KHz e (e) sinal filtrado no domínio tempo                                                  | 83 |

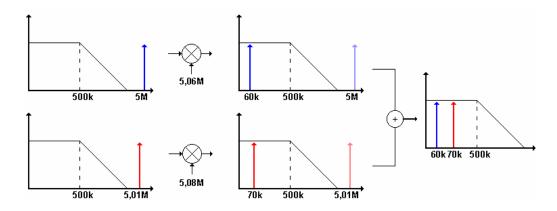

| Figura | 42 | Sequência para a soma de dois sinais em alta frequência usando o ispPAC20                                                    |    |

| _      |    | . Medidas mostrando (a) FFTs dos sinais de entrada em 5MHz e 70KHz; (b) FFT o                                                |    |

| 8      |    | sinal em 5MHz mixado para 60KHz; (c) FFT do sinal em 60KHz após o filtro                                                     |    |

|        |    | passa-faixa; (d) FFT da soma dos sinais em 60KHz e 70KHz e (e) sinal de saída i                                              | 10 |

|        |    | domínio tempo.                                                                                                               |    |

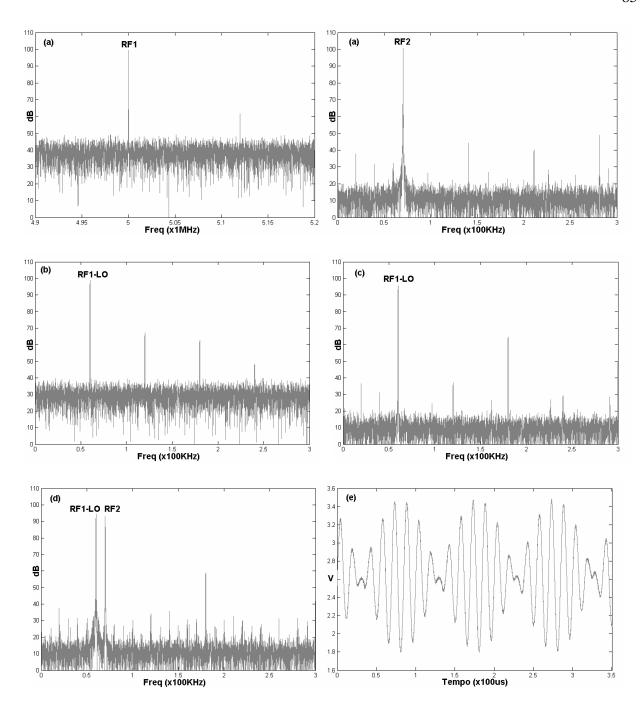

| Figura | 44 | Esquema de demodulação AM.                                                                                                   |    |

| _      |    | . Medidas mostrando (a) sinal de entrada modulado em amplitude; (b) sinal mixado                                             |    |

| υ      |    | (c) sinal de saída demodulado                                                                                                |    |

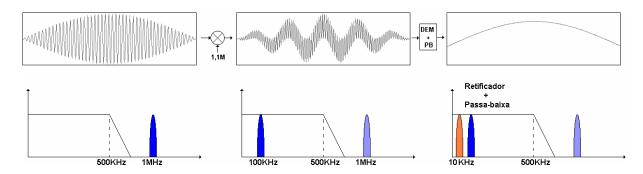

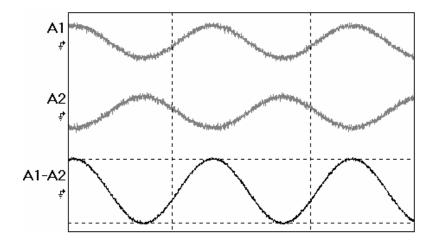

| Figura | 46 | Estrutura para leitura de sensor em uma ponte de Wheatstone.                                                                 |    |

| _      |    | Medida dos sinais diferenciais de saída do FPAA e subtração entre estes sinais                                               |    |

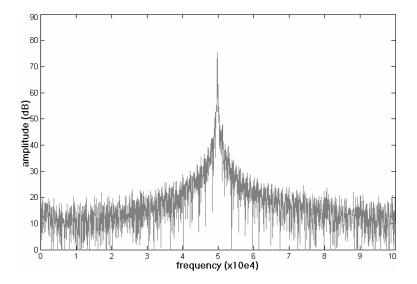

| _      |    | .Medida mostrando o espectro de frequência de uma das saídas do FPAA                                                         |    |

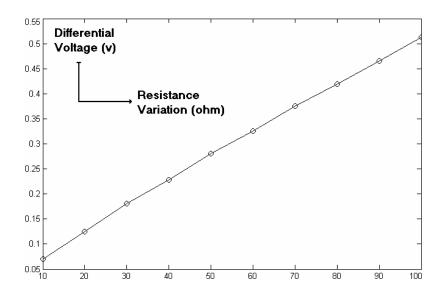

|        |    | Aquisição prática mostrando a variação da tensão diferencial de saída <i>versus</i> variação da resistência do sensor        |    |

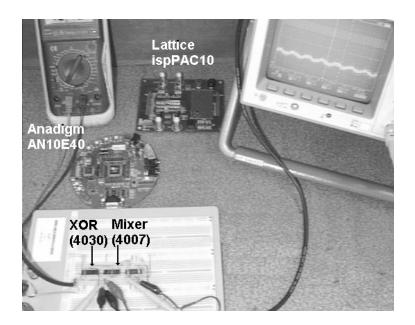

| Figura | 50 | . Montagem usada para os experimentos práticos.                                                                              | 92 |

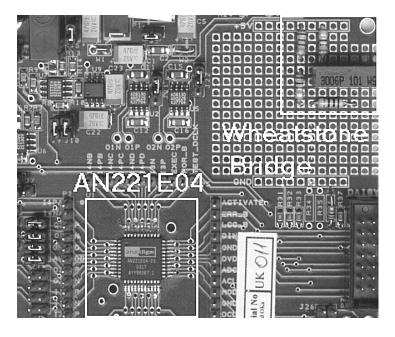

| _      |    | Montagem da ponte de Wheatstone juntamente com o AN221E04                                                                    |    |

|        |    | .Comparação entre as faixas de freqüência de operação dos FPAAs propostos                                                    |    |

| _      |    | (a) Estrutura matricial do FPAA proposto e (b) estrutura interna do CAB                                                      |    |

| _      |    | Simulação da resposta em frequência para o mixer utilizado na interface                                                      |    |

| _      |    | Filtro Tow-Thomas usando os CABs propostos                                                                                   |    |

|        |    | Estrutura interna do ispPAC10.                                                                                               |    |

|        |    | Estrutura interna do ispPAC80.                                                                                               |    |

|        |    | Estrutura interna do ispPAC20.                                                                                               |    |

|        |    | Estrutura interna do AN10E40.                                                                                                |    |

| Figura 60. Estrutura interna do AN221E04.                                              | 129    |

|----------------------------------------------------------------------------------------|--------|

| Figura 61. Simulação do Diagrama de Bode para passa-faixa usando ispPAC10              | 131    |

| Figura 62. Simulação do Diagrama de Bode para passa-baixa usando ispPAC80              | 132    |

| Figura 63. Simulação do Diagrama de Bode para somador usando ispPAC20                  | 132    |

| Figura 64. Simulação da Demodulação AM de sinal usando AN10E40                         | 133    |

| Figura 65. Simulação da Ponte de Wheatstone usando AN221E04.                           | 133    |

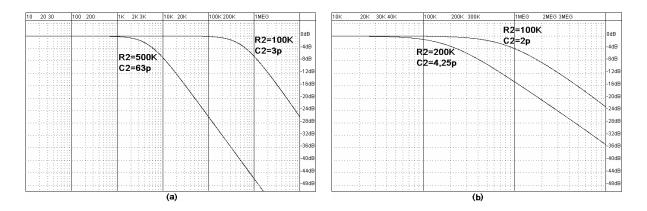

| Figura 66. Simulação do Diagrama de Bode para passa-baixa usando CABs descritos no     |        |

| apêndice B para FPAA com banda entre (a) DC-500KHz e (b) 200KHz-700K 135               | Hz.    |

| Figura 67. Simulação do Diagrama de Bode para passa-alta usando CABs descritos no      |        |

| apêndice B para FPAA com banda entre (a) DC-500KHz e (b) 200KHz-700K 135               | Hz.    |

| Figura 68. Simulação do Diagrama de Bode para amplificador usando CABs descritos no    | )      |

| apêndice B para FPAA com banda entre (a) DC-500KHz e (b) 200KHz-700K                   | Hz.    |

| 136                                                                                    |        |

| Figura 69. Simulação do integrador usando CABs descritos no apêndice B para FPAA co    | m      |

| banda entre (a) DC-500KHz e (b) 200KHz-700KHz                                          | 136    |

| Figura 70. Simulação do diferenciador usando CABs descritos no apêndice B para FPAA    | com    |

| banda entre (a) DC-500KHz e (b) 200KHz-700KHz                                          | 137    |

| Figura 71. Simulação do Diagrama de Bode do opamp utilizado nos circuitos, descrito no | )      |

| apêndice B, com uma carga de 100KΩ e 5pF                                               | 137    |

| Figura 72. Simulação do Diagrama de Bode do carregador de corrente utilizado nos circu | iitos, |

| descrito no apêndice B, com uma carga de 100KΩ e 5pF                                   | 138    |

| Figura 73. Simulação do Diagrama de Bode para o transcondutor de Nauta utilizado nos   |        |

| circuitos, descrito no apêndice B, com uma carga de 100KΩ e 5pF                        | 138    |

| , ,                                                                                    |        |

#### LISTA DE TABELAS

| Tabela 1. | Valores de C para diferentes frequências de corte do filtro da figura 2(a)     | 29   |

|-----------|--------------------------------------------------------------------------------|------|

| Tabela 2. | Valores de $C_{ox}$ e $\mu$ para o transistor P e N.                           | 55   |

| Tabela 3. | Valores de capacitâncias parasitas estimadas através das curvas de descarga do |      |

|           | circuito RC, para RF em (120+130)KHz e LO em 100KHz.                           | 61   |

| Tabela 4. | Valores de capacitâncias parasitas calculados analiticamente                   | 64   |

| Tabela 5. | Comparação entre técnicas utilizadas para realização do biquad de Tow-Thoma    | s.72 |

| Tabela 6. | Constituição dos filtros Tow-Thomas para estimativas de área, potência e       |      |

|           | impedância de entrada *                                                        | 73   |

| Tabela 7. | Valores medidos e calculados para variação da tensão e da resistência          | 90   |

| Tabela 8. | Configuração das chaves do CAB para realização de diferentes funções           | 95   |

| Tabela 9. | Valores de resistores e capacitores dos FPAAs propostos para comparação        | 96   |

| Tabela 10 | . Área ocupada pelos FPAAs propostos                                           | 98   |

| Tabela 11 | . Consumo do CAB conforme função implementada*                                 | .100 |

| Tabela 12 | . Consumo do mixer com a variação da frequência de chaveamento                 | .101 |

#### LISTA DE ABREVIATURAS

ADC: Analog to Digital Converter

AM: Amplitude Modulation

**BJT**: Bipolar Junction Transistor

CAB: Configurable Analog Block

CMOS: Complementary Metal Oxide Semiconductor

CMRR: Common Mode Rejection Rate

DAC: Digital to Analog Converter

DC: Direct Current

FFT: Fast Fourier Transformer

FM: Frequency Modulation

FPAA: Field Programmable Analog Array

FPGA: Field Programmable Gate Array

FPMA: Field Programmable Mixed-Signal Array

GIC: General Impedance Converter

HD3: Third Order Harmonic Distortion

IF: Intermediate Frequency

IIP3: Input Third Order Intercept Point

IM3: Third Order Intermodulation Product

IP: Intellectual Property

LNA: Low Noise Amplifier

LO: Local Oscillator

MEMS: Micro Electro-Mechanical System

MOS: Metal Oxide Semiconductor

MOSFET: Metal Oxide Semiconductor Field Effect Transistor

NF: Noise Figure

NMOS: N-type MOS

OIP3: Output Third Order Intercept Point

**OPAMP:** Operational Amplifier

OTA: Operational Transconductance Amplifier

PLL: Phase Locked Loop

PMOS: P-type MOS

PSRR: Power Supply Rejection Rate

RF: Radio Frequency

SAB: Single Amplifier Biquadratic

SNR: Signal to Noise Rate

SoC: System on Chip

VLSI: Very Large Scale Integrated

#### 1 INTRODUÇÃO

A rápida evolução das tecnologias em silício tem trazido benefícios exponenciais em custo, escala de integração, potência, tamanho e velocidade. Espera-se que este processo de evolução continue pelo menos mais 10 anos, aumentando dramaticamente o potencial de mercado (ITRS, 2002). Entretanto, a capacidade de penetração neste mercado irá depender da capacidade de criação e eficiência com a qual as idéias se tornam produtos reais.

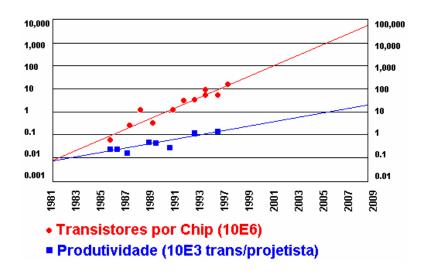

O projeto em silício não tem mantido o compasso com o desenvolvimento de tecnologias, embora gradativos melhoramentos na produtividade dos projetistas tenham ocorrido através dos anos. Este paradoxo pode ser visto na figura 1, retirada de (ERNST, 2000) onde se percebe a lacuna existente entre a capacidade de produção e a capacidade de integração de componentes em sistemas.

Figura 1. Relação produtividade e projeto, conforme (ERNST, 2000).

Recentemente, muitas formas de aumentar a velocidade do processo de projeto têm surgido, dentre as quais citam-se o re-uso de Propriedade Intelectual (do inglês *Intellectual Property – IP*) (SAVAGE, 2000), Redes em Chip (*Networks-on\_Chip – NoCs*) (BENINI, 2002) e aumento do uso de reconfigurabilidade (LEWIS, 2002; GREENBAUM, 2002).

A reconfigurabilidade, em especial, é um ponto de interesse que vem crescendo, na medida que permite, simplesmente através da alteração de uma especificação de entrada, a programação de novas funções de hardware. A reprogramação do hardware permite, por sua vez, uma redução significativa dos custos de projeto, visto que o projeto da parte reconfigurável é amortizado entre vários produtos. A mesma redução de custos que a indústria de software conseguiu no desenvolvimento de sistemas (frente àqueles baseados puramente em hardware) está sendo buscada pelos projetistas que usam hardware reconfigurável digital e analógico.

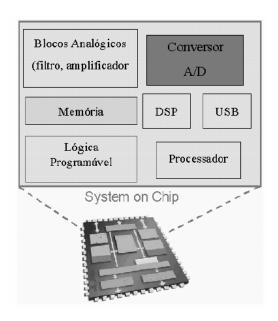

Os chamados *System on Chip* (SoC) (ERNST, 2000; GUPTA, 1997), são uma grande tendência na evolução dos sistemas eletrônicos, possibilitando a inclusão de todo um sistema em uma única pastilha de silício. Ainda, este sistema pode conter partes mecânicas servindo como sensores ou atuadores, como é o caso dos MEMS (*Micro Electro-Mechanical System*) (LATORRE, 1998). A figura 2 mostra uma possível estrutura do que poderia ser um dispositivo SoC, para o qual uma das tendências possíveis é se tornar uma estrutura completamente reconfigurável.

Figura 2. Possível estrutura de um *System on Chip*.

A reconfigurabilidade digital é garantida pelos FPGAs (*Field Programmable Gate Arrays*) (TRIMBERGER, 1994), cuja complexidade e nível de integração estão cada vez maiores, seguindo a já conhecida lei de Moore.

Entretanto, por maior que seja o processamento digital existente, sempre que for necessária a comunicação deste sistema com outros sistemas, por exemplo via RF, a aquisição de medidas físicas provenientes do meio externo (temperatura, voz, aceleração) ou qualquer outra forma que relacione grandezas analógicas, se fará necessária a existência de um bloco analógico, o qual também se deseja reconfigurável, possibilitando sua rápida e fácil adaptação a qualquer sistema analógico, tais quais são os FPGAs em relação aos sistemas digitais.

Os chamados FPAAs (*Field Programmable Analog Arrays*) (D'MELLO, 1998) vêm ao encontro desta necessidade de reconfiguração analógica, antes restrita apenas aos projetistas de sistemas digitais. Porém, a reconfigurabilidade analógica apresenta ainda algumas barreiras a serem transpostas, dentre elas, o limitado alcance de freqüências disponível nos dispositivos comerciais e mesmo acadêmicos atualmente existentes. Algumas das soluções apresentadas incorrem, ora no elevado gasto de potência dissipada devido ao processamento digital dos sinais (FABRIS, 2003a, 2003b), ora na reduzida programabilidade oferecida (PIERZCHALA, 1998a, 1998b), já que o uso de chaves para reconfiguração e programação deve ser limitado.

Uma proposta para lidar tanto com o problema das limitações em freqüência e da potência dissipada será apresentada neste trabalho, discutindo os aspectos relacionados às limitações do sistema e implementação deste. Esta dissertação está assim organizada: o capítulo II apresenta uma breve revisão bibliográfica a respeito de alguns dos principais FPAAs descritos na literatura, sejam eles desenvolvidos em âmbito acadêmico ou comercial. No capítulo III, faz-se uma caracterização de quatro tipos de FPAAs desenvolvidos, sendo que três representam 60% da totalidade dos FPAAs desenvolvidos até então. A quarta

topologia analisada é a apresentada em (FABRIS, 2003a), a partir da qual se originou a idéia apresentada neste trabalho. O capítulo IV apresenta o desenvolvimento da proposta apresentada nesta dissertação, seguido por algumas aplicações desenvolvidas, que estão apresentadas no capítulo V e que dão suporte à proposta apresentada. O capítulo VI apresenta uma análise onde se compara o gasto de potência, área ocupada e faixa de freqüência de operação entre dois FPAAs estruturalmente idênticos, porém com bandas de freqüências deslocadas entre si, mostrando que o uso da interface propicia além do aumento da faixa de frequência de operação em quase 3 décadas, também uma redução da área ocupada pelo circuito analógico (cerca de 8 vezes menor), sem incorrer em um consumo maior de potência (apenas 15% da potência total do FPAA). As conclusões são apresentadas no capítulo VII. Os apêndices A e B contém os parâmetros SPICE e as descrições SPICE, respectivamente, utilizadas no desenvolvimento deste trabalho. O apêndice C apresenta alguns arquivos Matlab® utilizados e o apêndice D contém uma descrição das estruturas internas dos FPAAs comerciais utilizados para o desenvolvimento das aplicações, cujas simulações encontram-se no apêndice E. Finalmente, o apêndice F mostra as simulações dos circuitos utilizados neste trabalho.

#### 2 O CONTEXTO DOS FPAAS

Algumas das idéias básicas sobre reconfigurabilidade foram estabelecidas durante os anos 60 e 70, mas estas não foram muito difundidas até o aperfeiçoamento dos FPGAs, onde plataformas reconfiguráveis provaram ser uma alternativa prática para sistemas digitais (RINCON, 1998). A programabilidade analógica, por sua vez, deu seus primeiros passos com o surgimento de alguns componentes programáveis tais como filtros (BURR, 1998; NATIONAL, 2001), potenciômetros digitais (ANALOG, 1997; XICOR, 2003), amplificadores de ganho programável (ANALOG, 2003; BURR, 1993), entre outros (D'MELLO, 1998).

Em outubro de 1994, a IMP Inc. (San Jose, Califórnia) lançou a arquitetura do EPAC (*Electrically Programmable Analog Circuit*) (KLEIN, 1995, 1998), que daria origem em 1999 ao ispPAC10 (LATTICE, 2000a, 2000b; OHR, 1999). A Zetex Ltd. (Oldham, Inglaterra) lançou o TRAC (*Totally Reconfigurable Analog Circuit*) (ZETEX, 1999a, 1999b; CLARKE, 1996; FLOCKTON, 1998) em novembro de 1996. Também em 1996, A. Bratt e I. MacBeth descreveram em (BRATT, 1996, 1998a, 1998b) a estrutura do que viria a ser, em julho de 2000, o primeiro circuito analógico reconfigurável (IVIE, 2002; ANADIGM, 2002) da então Anadigm Microeletronics Ltda.

A seguir serão descritas as estruturas básicas propostas para diferentes FPAAs desenvolvidos em nível acadêmico e comercial, para que se tenha uma idéia do que se dispõe atualmente em termos de reconfigurabilidade analógica. Um estudo mais detalhado a respeito do estado da arte destes dispositivos pode ser encontrado em (SCHÜLER, 2003).

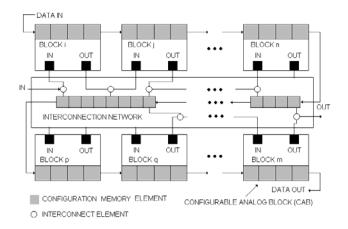

A figura 3 mostra a estrutura mais geral de um FPAA, formado por Células Analógicas Reconfiguráveis (CAB – *Configurable Analog Block*) e uma rede de interconexões.

Figura 3. Estrutura de um FPAA segundo (D'MELLO, 1998).

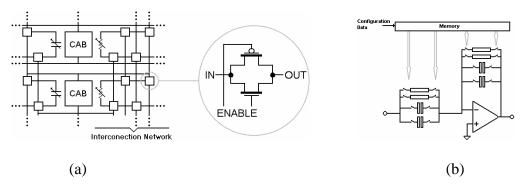

Tanto os CABs quanto a rede de interconexão possuem em suas estruturas um conjunto de chaves necessárias ou para a configuração de um CAB em diferentes funções analógicas, ou para a ligação entre diferentes CABs a fim de obter-se uma função mais complexa, como mostram as figuras 4(a) e 4(b).

Figura 4. Estrutura interna para (a) rede de interconexão e (b) CAB, segundo (LEE, 1998).

A existência destas chaves, quando operando em alta freqüência, e a necessidade de componentes passivos como resistores e capacitores de tamanhos elevados, quando operando em baixa freqüência, torna o FPAA um dispositivo altamente limitado em banda, uma vez que, em altas freqüências, as chaves introduzirão pólos parasitas, e em baixas freqüências, os componentes passivos tornarão o circuito irrealizável em processos VLSI, devido à grande área necessária.

A distribuição e funcionalidade dos CABs podem ser divididas em duas formas, como mostra a figura 5. No primeiro caso tem-se a estrutura clássica na qual, assim como nos FPGAs, existem diversos blocos reconfiguráveis idênticos. Para cada módulo é dado um certo número de funções programáveis e características, sendo que todas elas devem funcionar independentemente da maneira como as células são configuradas ou ligadas com outras células. A segunda topologia contém módulos que são otimizados para certas classes de aplicações, o que, apesar de não permitir o mesmo grau de reconfigurabilidade que a primeira estrutura, garante um projeto mais bem otimizado em relação a aspectos como freqüência, consumo e linearidade para as aplicações às quais os FPAAs foram desenvolvidos.

Figura 5. Comparação entre topologias de FPAAs, conforme (KLEIN, 1998).

Diferentes estruturas e tecnologias foram empregadas na realização de FPAAs, sempre buscando conciliar um alto grau de programabilidade com uma largura de banda relativamente grande. Pode-se dividir os FPAAs encontrados na literatura, de acordo com a forma de processamento do sinal em duas categorias: tempo contínuo e tempo discreto.

Os FPAAs operando em tempo contínuo têm como principais representantes, porém não únicos, aqueles cujos CABs são baseados em amplificadores operacionais (opamp) (ZETEX, 1999b) e/ou amplificadores de transcondutância (OTA) (LATTICE, 2000a), e aqueles cujos núcleos dos CABs são carregadores de corrente (GAUDET, 1999). Para os dois

casos, componentes passivos (resistores, capacitores, diodos) conectados em diferentes configurações por meio de chaves realizam diferentes funções analógicas. Já os FPAAs que processam o sinal em tempo discreto possuem dois representantes: os a capacitor chaveado, os quais também possuem um amplificador operacional como elemento central do CAB, e os a corrente chaveada, que não fazem uso de opamp.

#### 2.1 AMPLIFICADOR OPERACIONAL E AMPLIFICADOR DE TRANSCONDUTÂNCIA

Os FPAAs baseados em amplificadores operacionais possuem, assim como os baseados em capacitor chaveado, uma limitação em banda imposta pelo próprio opamp (SEDRA, 1991). Além disso, um opamp sozinho não realiza função alguma, a não ser a de comparador. Assim, faz-se necessária a inclusão de componentes passivos e/ou ativos (resistores, capacitores, diodos, transistores) para a realização de funções mais complexas. Logo, o mesmo problema associado à área faz-se presente nesta estrutura, além da inserção de chaves que limitará tanto a freqüência quanto a linearidade do dispositivo.

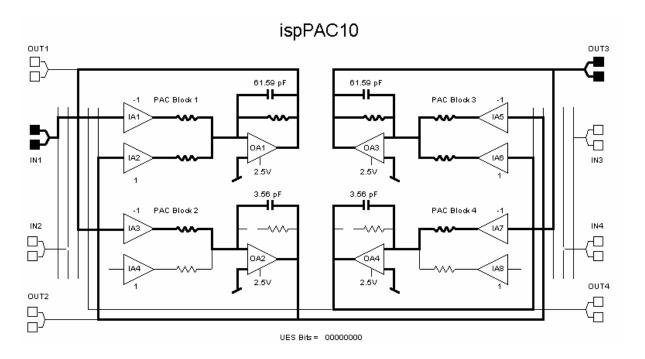

Como exemplos de FPAAs baseados em opamp apresentam-se os descritos em (LOOBY, 2000), e os dispositivos comerciais produzidos pela Lattice Semiconductor Corp. (ispPAC10/20/30/80/81 e ispPAC-POWR604/1208) e pela Zetex Ltd., denominado TRAC (*Totally Re-Configurable Analog Circuit*). Os representantes da Lattice possuem, além de amplificadores operacionais, amplificadores de transcondutância (SCHAUMANN, 2001).

#### 2.2 CARREGADOR DE CORRENTE

O uso de carregadores de corrente (*current conveyor*) no desenvolvimento de FPAAs apresenta como grande vantagem a grande largura de banda obtenível por estes dispositivos, que pode chegar facilmente a centenas de MHz (PREMONT, 1998; TOUMAZOU, 1990). Novamente, seu uso é limitado devido à necessidade da utilização de componentes passivos para a realização de alguma função analógica e de chaves associadas a estes componentes.

Além disso, o transporte de sinais de informação de corrente para diferentes pontos do circuito torna-se difícil, na medida que é necessário o uso de copiadores de correntes, o que não ocorre em circuitos usando sinais em tensão. Dentre os FPAAs com carregadores de corrente, citam-se os apresentados em (PREMONT, 1998) e (GAUDET, 1999).

#### 2.3 CAPACITOR CHAVEADO

A tecnologia de capacitor chaveado favoreceu o desenvolvimento de filtros ativos para aplicações de precisão, especialmente em baixas freqüências (SCHAUMANN, 2001). Entretanto, esta técnica depende de capacitores lineares, os quais ocupam uma grande área em sistemas integrados. Além disso, este tipo de realização de circuito tem sua operação em freqüência limitada à freqüência de Nyquist (LATHI, 1998) e, é claro, uma vez que sua utilização requer uma grande quantidade de chaves, estas também limitam sua resposta em altas freqüências. Por outro lado, estruturas baseadas em capacitor chaveado possuem um alto grau de reconfigurabilidade e programabilidade, já que, por exemplo, a freqüência de corte de um filtro qualquer pode ser alterada simplesmente através da variação da freqüência de chaveamento, ou através da mudança da relação entre dois capacitores.

Alguns dos FPAAs baseados em capacitor chaveado são descritos em (LEE, 1998; KUTUK, 1998; KLEIN, 1998; BRATT, 1998b). Este último, denominado DPAD2, originou o FPAA atualmente desenvolvido pela Anadigm, o AN10E40 (ANADIGM, 2002), a qual desenvolve também os FPAAs da família AnadigmVortex (ANADIGM, 2003), todos a capacitor chaveado.

#### 2.4 CORRENTE CHAVEADA

Uma técnica análoga ao capacitor chaveado é a de corrente chaveada. Este tipo de estrutura permite circuitos com um consumo de potência menor que os a capacitor chaveado, uma vez que utiliza corrente ao invés de tensão, permitindo a utilização de fontes de

alimentação de menor valor (TOUMAZOU, 1990). Outra vantagem é a não necessidade do uso de opamps, não havendo os problemas associados ao seu uso. Basicamente, dois problemas existem nesta topologia: há uma menor linearidade quando comparada ao capacitor chaveado, e é necessária a criação de várias cópias do sinal de corrente para alimentar múltiplos blocos com o mesmo sinal, o que não ocorre com o capacitor chaveado, que trabalha com tensão. Além disso, a largura de banda é limitada, mais uma vez, pela freqüência de Nyquist. Um FPAA baseado em corrente chaveada é apresentado em (CHANG, 1996).

#### 2.5 OUTRAS TOPOLOGIAS

Além das topologias apresentadas, outras foram utilizadas na realização de FPAAs, para a obtenção de melhores resultados em uma ou outra característica. Citam-se espelhos de corrente (ZHANG, 1996; EMBABI, 1998), CMOS operando na condição de *subthreshold* (LEE, 1991) e multiplexadores e demultiplexadores (SANTINI, 2002). Também estruturas mistas, que juntam o processamento digital e analógico de sinais, têm sido apresentadas para a realização de dispositivos reconfiguráveis, estes denominados FPMAs (*Field Programmable Mixed-Signal Array*), a exemplo de (FABRIS, 2003a, 2003b; CYPRESS, 2003; MADRENAS, 1999).

#### 3 CARACTERIZAÇÃO DE FPAAS

Os diferentes FPAAs já desenvolvidos apresentam limitações cuja natureza necessita ser caracterizada. Algumas destas limitações são, entre outras, nível de programabilidade, granularidade, linearidade, potência consumida e limites de freqüência. Quanto maior o nível de programabilidade, maior o número de funções analógicas que o FPAA pode realizar. Este fator está intimamente relacionado com a granularidade, ou seja, podem-se ter dispositivos cujas funções elementares realizadas são, por exemplo, filtros, amplificadores e retificadores, bem como podem existir FPAAs que realizem como funções básicas aplicações mais complexas como PLLs, VCOs e moduladores. A granularidade é um fator importante, na medida que se deseja aplicações cuja resposta não introduza distorções no sinal a ser processado. Para sistemas embarcados, uma das principais características que se deseja é o baixo consumo de potência, associado aos limites de freqüência de utilização, os quais desejase que sejam elevados em alta freqüência e dos menores possíveis em baixa freqüência, permitindo aplicações desde DC (pontes de instrumentação, por exemplo) até RF, utilizado em telecomunicações.

Neste capítulo serão apresentadas algumas simulações envolvendo três diferentes técnicas de implementação de FPAAs, a fim de demonstrar algumas das limitações citadas. Além disso, é também abordada a proposta apresentada em (FABRIS, 2003a, 2003b), mostrando algumas de suas características. As técnicas escolhidas para simulação dos FPAAs são capacitor chaveado, amplificador operacional e/ou amplificadores de transcondutância com elementos passivos, e carregador de corrente com elementos passivos, uma vez que estas três possibilitam a caracterização de 60% dos FPAAs acadêmicos encontrados na literatura (SCHÜLER, 2003). Além disso, as técnicas de capacitor chaveado e opamp/OTA associados a elementos passivos representam a totalidade dos dispositivos analógicos e mistos desenvolvidos comercialmente, na atualidade. Capacitores chaveados são utilizados tanto nos

FPAAs desenvolvidos pela Anadigm (AN10E40 e família AnadigmVortex) quanto nos FPMAs desenvolvidos pela Cypress (família CY8C2xxxx), enquanto que o uso de amplificador operacional ou OTA e elementos passivos representa os FPAAs fabricados pela Lattice (ispPAC10/20/30/80/81 e ispPAC-POWR604/1208) e Zetex (TRAC), além de um dos blocos do FPMA da Cypress.

Os circuitos, todos derivados de FPAAs existentes, foram simulados em tecnologia CMOS 0,35µm. As descrições SPICE dos circuitos bem como os parâmetros dos transistores utilizados encontram-se no Apêndice A e B. O software utilizado nas simulações dos FPAAs é o simulador de circuitos Smash, versão 5.2.1p1.

#### 3.1 AMPLIFICADOR OPERACIONAL E COMPONENTES PASSIVOS

A realização de funções analógicas utilizando-se amplificadores operacionais ou amplificadores de transcondutância e elementos passivos, principalmente resistores e capacitores, já é bastante conhecida e difundida. Esta técnica permite facilmente a realização de funções básicas como amplificadores, integradores e somadores, com os quais desenvolvem-se funções mais complexas como filtros, osciladores, PLL (*Phase Locked Loop*), moduladores e mesmo conversores analógico-digitais.

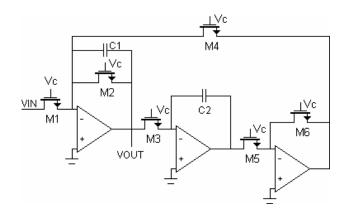

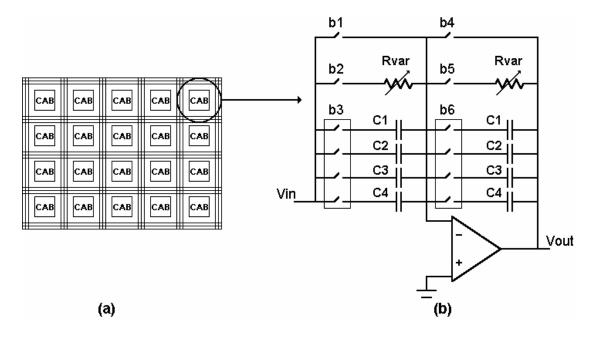

Como exemplo de uma aplicação utilizando um amplificador operacional e alguns elementos passivos, apresenta-se um filtro biquadrático semelhante ao realizado pelo ispPAC10 da Lattice o qual utiliza capacitores e OTA. O circuito está mostrado na figura 6(a), e seu equivalente realizado pelo ispPAC10 na figura 6(b).

Figura 6. (a) Filtro biquadrático com amplificador operacional e componentes passivo; (b) equivalente realizado pelo ispPAC10, conforme (LATTICE, 2000a).

As funções de transferência para as saídas passa-faixa e passa-baixa dos circuitos das figuras 6(a) e 6(b) são dadas em (1), (2), (3) e (4), respectivamente, retiradas de (LATTICE, 2000a):

$$\frac{V_{PF}}{V_{IN}} = \frac{-\frac{s}{C_1.R_4}}{s^2 + \frac{s}{C_1.R_1} + \frac{R_6}{C_1.C_2.R_2.R_3.R_5}}$$

(Passa-Faixa) (1)

$$\frac{V_{PB}}{V_{IN}} = \frac{-\frac{R_6}{C_1.C_2.R_2.R_4.R_5}}{s^2 + \frac{s}{C_1.R_1} + \frac{R_6}{C_1.C_2.R_2.R_3.R_5}}$$

(Passa-Baixa) (2)

$$\frac{V_{PF}}{V_{IN}} = \frac{-\frac{K_{11} s}{C_{F1.250k}}}{s^2 + \frac{s}{C_{F1.250k}} - \frac{K_{12}K_{21}}{(C_{F1.250k})(C_{F2.250k})}}$$

(Passa-Faixa) (3)

$$\frac{V_{PB}}{V_{IN}} = \frac{\frac{K_{11}K_{12}}{(C_{F1}.250k)(C_{F2}.250k)}}{s^2 + \frac{s}{C_{F1}.250k} - \frac{K_{12}K_{21}}{(C_{F1}.250k)(C_{F2}.250k)}}$$

(Passa-Baixa) (4)

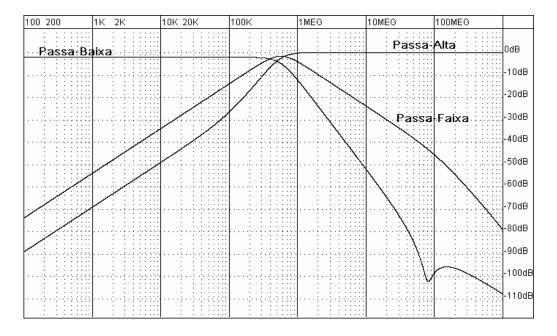

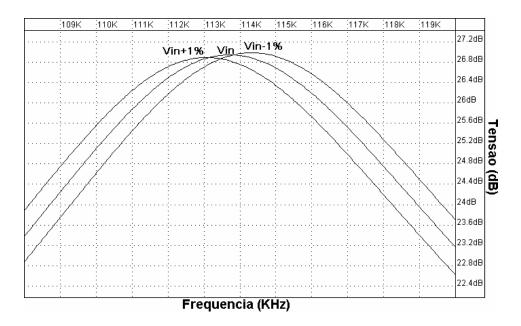

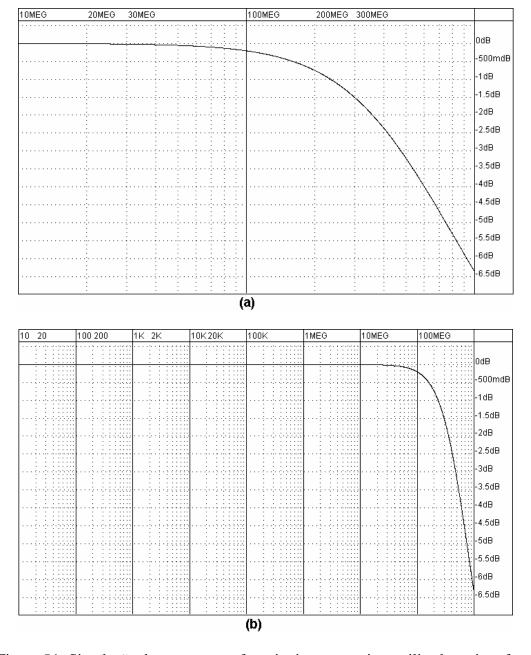

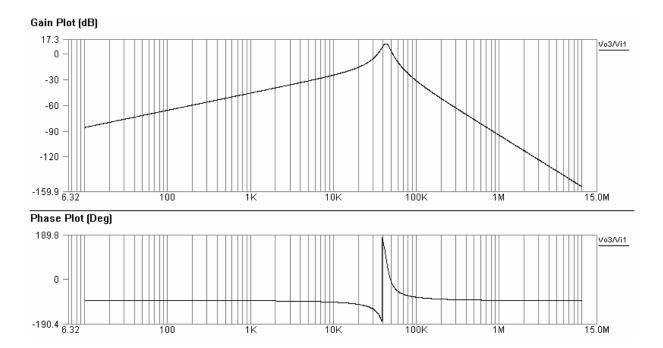

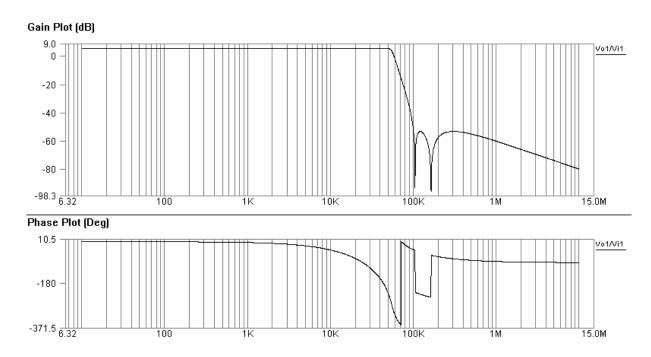

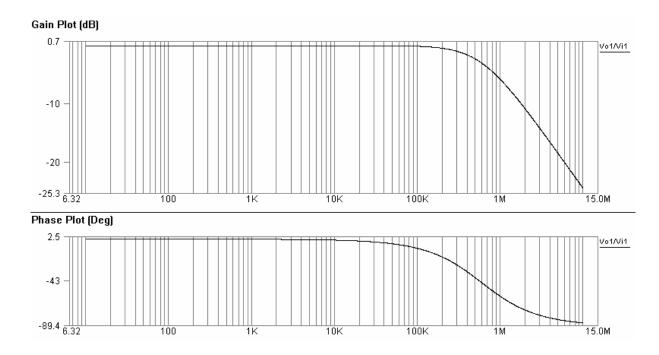

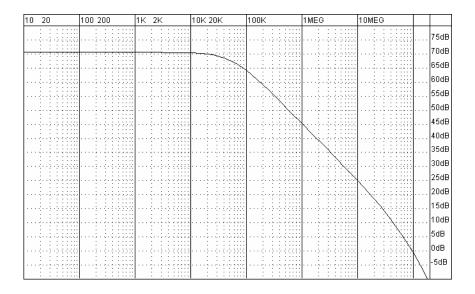

A figura 7 mostra o diagrama de Bode das saídas passa-faixa e passa-baixa do filtro apresentado.

Figura 7. Diagrama de Bode simulado para o filtro a amplificador operacional e elementos passivos apresentado na figura 6(a).

Diversos fatores envolvendo amplificadores operacionais limitam seu uso em FPAAs. Levando-se em conta apenas o amplificador operacional, dois tipos de limitações podem ocorrer: as limitações estáticas, dentre a quais citam-se tensão e corrente de *off*-set, CMRR e PSRR, e as limitações dinâmicas como largura de banda limitada, que em geral não ultrapassa algumas dezenas de MHz (produto ganho faixa), *slew rate* e *setting time*, que fazem com que o FPAA se limite a aplicações de baixa a média freqüência, além de causar distorções não lineares no sinal (SEDRA, 1991).

Além dos problemas relacionados com o amplificador operacional em si, outros problemas surgem na medida que, para a realização de funções analógicas, faz-se necessária a associação do opamp com elementos passivos tais como resistores, capacitores e diodos, o que torna a área uma limitação importante destes componentes, quando utilizados em

circuitos integrados. Para exemplificar este fato, a tabela 1 apresenta alguns valores de capacitores que seriam necessários para a implementação do filtro da figura 6(a), considerando-se C<sub>1</sub>=C<sub>2</sub>=C, para diferentes freqüências de corte deste filtro. Os valores de R são fixos em 250k ohm. Esse valor é o mesmo das resistências equivalentes dos CABs do ispPAC10 (LATTICE, 2000a). Comparativamente, é mostrada área ocupada por um amplificador operacional nesta mesma tecnologia.

Tabela 1. Valores de C para diferentes frequências de corte do filtro da figura 2(a).

| Freqüência de corte (KHz) | Valor do capacitor (pF) | Área do capacitor (μm)* |

|---------------------------|-------------------------|-------------------------|

| 0.01                      | 60000                   | 7947,19 x 7947,19       |

| 0.1                       | 6000                    | 2513,12 x 2513,12       |

| 1                         | 600                     | 794,72 x 794,72         |

| 10                        | 60                      | 251,31 x 251,31         |

| 100                       | 6                       | 79,47 x 79,47           |

| 1000                      | 0.6                     | 25,13 x 25,13           |

| Amplificador Operacional  | **0,443                 | 50,7 x 50,7             |

<sup>\*</sup> Considerando uma capacitância por área de 950 aF/µm² entre poly/poly, retirado de (MOSIS, 2004).

Pelos dados da tabela 1, a área ocupada pelos capacitores torna-se bastante elevada conforme a freqüência de corte do filtro diminui, tornando a utilização destes circuitos bastante difícil em circuitos integrados, para aplicações em baixa freqüência.

<sup>\*\*</sup> Valor do capacitor de compensação, cuja área ocupada é de 21,6µm x 21,6µm.

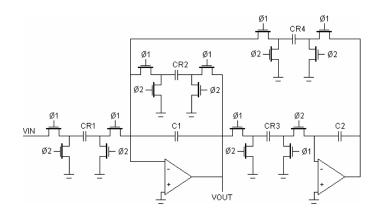

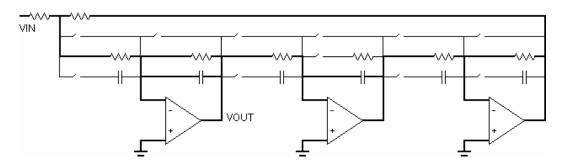

#### 3.2 CAPACITOR CHAVEADO

Para caracterização de um FPAA operando a capacitor chaveado foi utilizado o amplificador inversor representado na figura 8(a). Este amplificador possui uma estrutura semelhante ao realizado pelo AN10E40 da Anadigm através do módulo G01 (ANADIGM, 2002).

Figura 8. (a) Amplificador inversor a capacitor chaveado conforme (ANADIGM, 2002); (b) chaves analógicas e portas de transmissão; (c) sinais de controle das chaves.

Circuitos a capacitor chaveado são constituídos por capacitores, chaves analógicas ou portas de transmissão (*transmission gates*) (figura 8(b)) e amplificadores operacionais. As chaves abrem e fecham periodicamente sob controle de sinais de onda quadrada, ortogonais entre si e não sobrepostas, cada um com período *T*, de acordo com a figura 8(c) (LAKER, 1994). Este comportamento das chaves associadas aos seus respectivos capacitores torna o sistema chave-capacitor o equivalente a um resistor cujo valor é dado por:

$$\operatorname{Re} q = \frac{T}{C} \tag{5}$$

A função de transferência do amplificador da figura 8 é dada por (retirada de ANADIGM, 2002):

$$G = -\frac{C_1}{C_2} \tag{6}$$

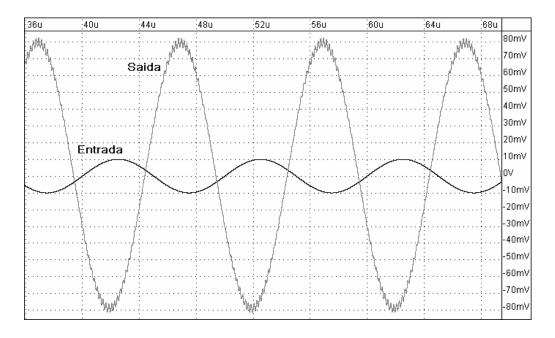

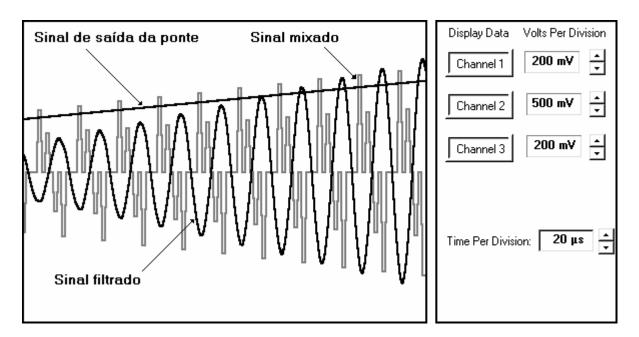

A figura 9 mostra uma simulação para o amplificador apresentado, onde se percebem claramente o efeito de chaveamento dos capacitores.

Figura 9. Simulação do amplificador a capacitor chaveado apresentado na figura 8(a).

O filtro ativo utilizando redes RC como o descrito na seção 3.1 apresenta duas propriedades que tornam sua produção em circuitos integrados monolíticos difícil: a primeira, já mencionada, é o fato de necessitar valores de capacitores elevados; a segunda é a necessidade de constantes de tempo RC com um alto grau de precisão, caso contrário as freqüências de corte fatalmente serão diferentes daquelas projetadas (SEDRA, 1991).

Em circuitos a capacitor chaveado, pode-se mostrar (SEDRA, 1991; LAKER, 1994) que a constante de tempo RC, para um integrador por exemplo, é dada pela razão entre dois capacitores multiplicada pelo período de chaveamento destes capacitores. Estes parâmetros podem ser bem controlados em circuitos integrados, sobretudo a razão entre dois capacitores, que em tecnologia MOS pode ter uma precisão de até 0.1% (SEDRA, 1991).

Além de permitir constantes de tempo de valores precisos, a fácil programabilidade é outra característica de circuitos a capacitor chaveado, uma vez que os valores da resistência equivalente podem ser variados simplesmente através do controle da freqüência de chaveamento. Assim sendo, esta técnica de implementação de circuitos apresenta-se como uma boa solução para a realização de FPAAs.

Por outro lado, a necessidade de capacitores lineares torna estes circuitos também limitados em área. Outra limitação, não menos importante, diz respeito á frequência máxima devido a três fatores, principalmente: a necessidade de chaves de programação, assim como na maioria dos FPAAs, a limitação dos amplificadores operacionais em *slew rate* e a limitação devido à frequência de chaveamento dos capacitores. Levando-se em conta a taxa de amostragem de Nyquist (LATHI, 1998), a máxima frequência de sinal que pode ser processado pelo circuito é menor que a metade da frequência de chaveamento dos capacitores.

#### 3.3 CARREGADOR DE CORRENTE

Os carregadores de corrente, ao contrário dos amplificadores operacionais, possuem uma largura de banda que pode atingir facilmente algumas centenas de MHz (TOUMAZOU, 1990), com um ganho praticamente constante. Estes dispositivos possuem, em geral, três terminais, e sua operação pode ser resumida da seguinte forma: se uma tensão é aplicada ao terminal de entrada Y, uma tensão igual aparecerá no terminal de entrada X. Similarmente, se uma corrente é forçada no terminal de entrada X, uma corrente igual irá fluir pelos terminais

Y e Z (PREMONT, 1998). Quando associados a elementos passivos, os carregadores de corrente podem realizar diversas funções analógicas, como por exemplo, integrador de corrente, amplificador de corrente, diferenciador de corrente, somadores de corrente e fontes controladas (TOUMAZOU, 1990).

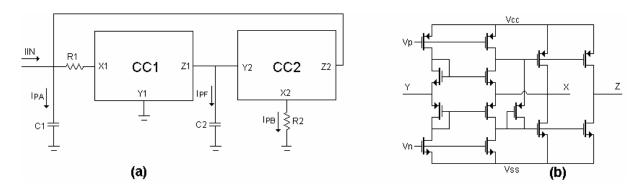

Um exemplo de aplicação de carregadores de corrente na realização de FPAAs pode ser vista na figura 10(a), onde um filtro de segunda ordem semelhante ao descrito em (PREMONT, 1998) é mostrado. A figura 10(b) mostra como é realizado o carregador de corrente.

Figura 10. (a) Filtro de segunda ordem com carregador de corrente, conforme (PREMONT, 1998) e (b) carregador de corrente utilizado.

As funções de transferência para as saídas passa-alta, passa-faixa e passa-baixa do filtro com carregador de corrente mostrado na figura 10 são dadas por (7), (8) e (9), retiradas de (PREMONT, 1998):

$$\frac{I_{PA}}{I_{IN}} = \frac{s^2}{s^2 + \frac{s}{R_1 C_1} + \frac{1}{R_1 R_2 C_1 C_2}}$$

(Passa-Alta)

$$\frac{I_{PF}}{I_{IN}} = \frac{\frac{s}{R_1 C_1}}{s^2 + \frac{s}{R_1 C_1} + \frac{1}{R_1 R_2 C_1 C_2}}$$

(Passa-Faixa) (8)

$$\frac{I_{PB}}{I_{IN}} = \frac{\frac{1}{R_1 R_2 C_1 C_2}}{s^2 + \frac{s}{R_1 C_1} + \frac{1}{R_1 R_2 C_1 C_2}}$$

(Passa-Baixa) (9)

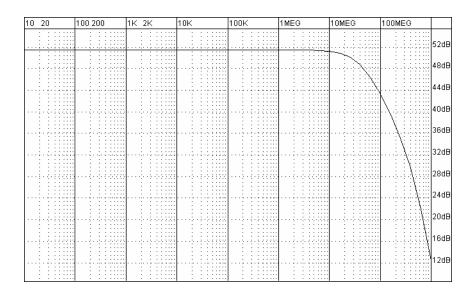

A figura 11 mostra o diagrama de Bode das saídas passa-faixa, passa-baixa e passaalta do filtro apresentado.

Figura 11. Diagrama de Bode simulado para o filtro a carregador de corrente apresentado na figura 4.

O primeiro problema que surge ao se trabalhar com carregadores de corrente é justamente o fato de se ter de fazer operações utilizando-se sinais de corrente ao invés de tensão. Com isso, em circuitos mais complexos onde há a necessidade de inserção de um mesmo sinal em diferentes pontos, faz-se necessária a inserção de mais condutores, o que não

ocorre em sistemas que trabalham com tensão, onde apenas um barramento simples distribui o mesmo sinal por vários pontos (TOUMAZOU, 1990).

Novamente, assim como para os circuitos utilizando amplificadores operacionais, é necessária a utilização de componentes passivos juntamente com os carregadores de corrente para a realização de operações analógicas. Surge então o mesmo problema de área, principalmente quando se está operando em baixas freqüências.

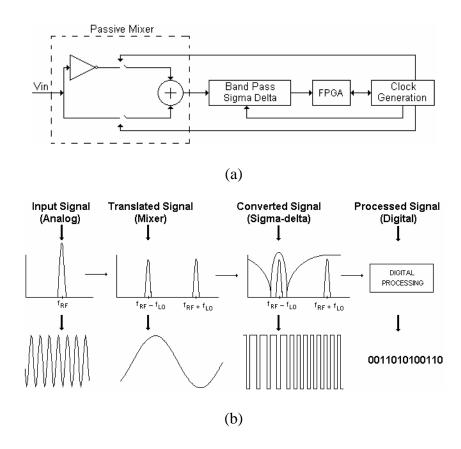

#### 3.4 SOLUÇÃO MISTA

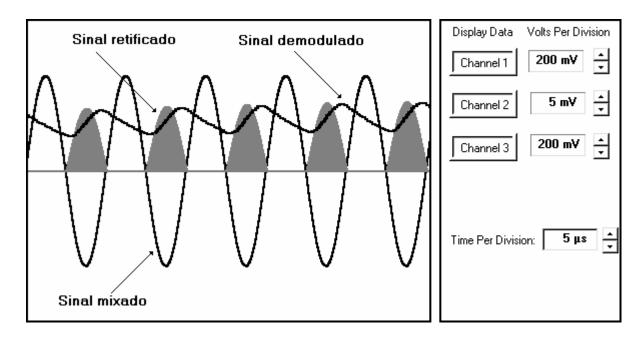

Recentemente, foi apresentado em (FABRIS, 2003a, 2003b, 2004), uma arquitetura que explora a topologia sigma-delta (CANDY, 1992; NORSWORTHY, 1997) para a conversão de sinais analógicos em digitais. O sistema, cuja estrutura e funcionamento são mostrados nas figuras 12(a) e 12(b), é constituído por um mixer passivo, responsável pela translação do sinal de entrada para uma freqüência intermediária (IF) fixa. Após, este sinal é convertido para o domínio digital através de um conversor sigma-delta passa-banda de tempo contínuo centrado em IF.

Figura 12. (a) Estrutura e (b) funcionamento do FPMA com conversor  $\Sigma\Delta$ .

O sinal é então processado por um FPGA (ou outro dispositivo de processamento digital, como um microprocessador). Este sistema, porém, apresenta como característica limitante a alta potência dissipada devido ao processamento digital realizado no sinal, uma vez que a única função da parte analógica é a translação e conversão analógico-digital do sinal a ser processado. Todo o resto do processamento, inclusive a demodulação do *bitstream* gerado pelo sigma-delta para a banda base, é feita digitalmente.

Circuitos analógicos em geral operam numa banda que vai desde DC em seu limite inferior até alguns poucos KHz no seu limite superior, ou numa banda de alguns poucos KHz no limite inferior da banda até alguns poucos MHz no limite superior da banda. Como visto anteriormente, a utilização de FPAAs fica limitada a algumas aplicações devido a este limite em sua largura de banda, imposto em baixa freqüência pela necessidade de elementos passivos de tamanho elevado. Em alta freqüência, basicamente três fatores contribuem para o

não funcionamento dos FPAAs: a existência de chaves de interconexão e programação, a necessidade da interconexão entre células distantes uma das outras, ocasionando problemas de *cross-talk* e erro de fase (PIERZCHALA, 1998a, 1998b), e a utilização de elementos centrais das células programáveis que são limitados em freqüência como, por exemplo, os amplificadores operacionais.

O desenvolvimento de FPAAs que operem em baixas freqüências pode ser contornado através da utilização, por exemplo, da técnica de capacitor chaveado, o que permite a realização de resistores de valor elevado (0.1 MΩ para um capacitor de 100p e uma freqüência de chaveamento de 100KHz (LAKER, 1994)). Para o caso da limitação em altas freqüências, a utilização de carregadores de corrente, por exemplo, pode aumentar a banda de cada CAB. Já o efeito das chaves de interconexão pode ser reduzido através da limitação das interconexões possíveis entre as células (PIERZCHALA, 1998a), o que, por outro lado, leva a uma redução da flexibilidade do FPAA, reduzindo-se o número de funções analógicas realizáveis.

Assim sendo, um FPAA que mantenha as características de alta programabilidade ao mesmo tempo em que permite o processamento de sinais tanto em freqüências baixas quanto em freqüências altas, ainda é um ponto de interesse a ser pesquisado e desenvolvido.

# 4 PROPOSTA DE INTERFACE PARA AUMENTO DA FAIXA DE FREQÜÊNCIA DE OPERAÇÃO DE FPAAS

Similarmente a (FABRIS, 2003a, 2003b, 2004), a proposta deste trabalho tem como objetivo não a mudança na estrutura do FPAA, seja na sua rede de interconexão, seja nos componentes que este usa como base para os CABs ou mesmo no tipo de processamento que ele desenvolve (tempo contínuo ou discreto). Ao contrário, o que se propõe é mudança do sinal a ser processado, permitindo a ampliação da gama de freqüências de sinais processados pelo FPAA, além de permitir o desenvolvimento destes dispositivos com o grau de programabilidade que se deseja, otimizados para trabalhar numa gama de freqüências que melhor se adapte à tecnologia e estrutura utilizadas.

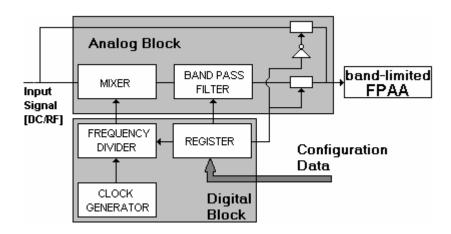

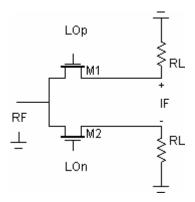

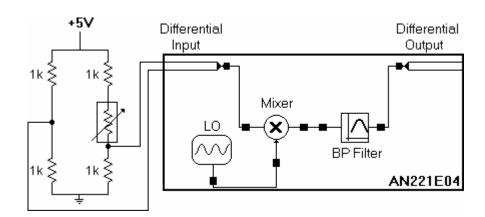

Para tanto, é proposta a utilização de uma interface constituída por dois blocos: um mixer, responsável pela translação do sinal de entrada para uma determinada freqüência e um filtro passa-faixa, o qual irá selecionar, dentre os sinais gerados na translação, aquele que irá ser processado pelo FPAA. A figura 13 mostra o diagrama em blocos da interface, e algumas das chaves de conexão necessárias a sua utilização.

Figura 13. Proposta de interface para alocação de sinais.

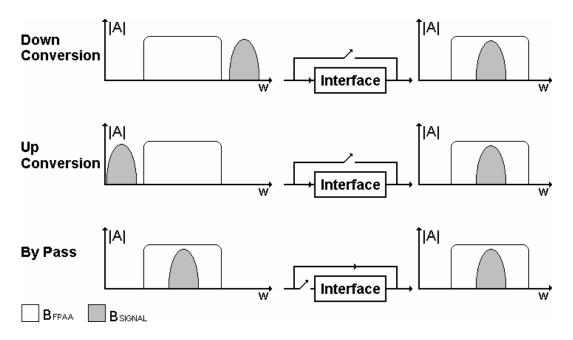

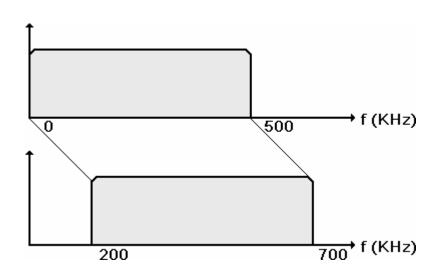

Cabe ressaltar que o que se propõe é ampliação da faixa de freqüências no qual o FPAA opera, que pode variar de baixas freqüências (instrumentação, por exemplo) a altas freqüências, a exemplo de sistemas de comunicação. A largura de banda do dispositivo ainda estará limitada devido a fatores construtivos já citados (chaves, composição dos CAB e tamanho dos componentes). Através da figura 14 pode-se entender mais claramente o que se propõe: dado um FPAA com uma determinada largura de banda B<sub>FPAA</sub> e um sinal centrado em uma freqüência qualquer, cuja largura de banda B<sub>SIGNAL</sub> seja no máximo igual a do FPAA, pode-se utilizar este FPAA para processar analogicamente este sinal, simplesmente movendo o sinal para dentro da banda do FPAA; caso a banda do sinal a ser processado já esteja centrada em uma freqüência na qual o FPAA opere, não é necessária a utilização da interface, e o sinal de entrada passa direto para o FPAA.

Figura 14. Proposta de translação de sinais para uma dada freqüência de operação de um FPAA qualquer.

Uma vez que o sinal de entrada foi movido para a freqüência de operação do FPAA e processado por este dispositivo, este sinal deve então ser recolocado para sua freqüência

original (caso seja necessário), o que pode ser feito pela mesma interface, agora na saída do FPAA.

Diferentemente de (FABRIS, 2003a), o sinal alocado em determinada freqüência é totalmente processado analogicamente através da utilização de um FPAA, reduzindo-se assim a potência dissipada no processamento digital (realizado por um FPGA, por exemplo), bem como o tempo de processamento deste sinal. Para a utilização em SoC, a redução de potência e tempo de processamento também se torna considerável, na medida que grande parte do processamento do sinal (tanto dos sinais de entrada, por exemplo de sensores, quanto de sinais de saída, por exemplo para comunicação por RF) é realizado analogicamente.

É necessário, para a realização desta interface, a determinação de algumas características que relacionam seus dois blocos principais: o mixer e o filtro passa-faixa. Ou seja, dada uma certa banda de operação de um FPAA, quais devem ser as características necessárias a esses blocos para que se tenha uma determinada resolução no sinal de saída que possibilite seu uso em uma determinada aplicação, seja em baixa ou em alta freqüência.

Antes de partir para a descrição da interface proposta e da determinação destes fatores, faz-se necessária a revisão de alguns pontos acerca da teoria envolvida no funcionamento dos mixers. Também será revista a realização de circuitos utilizando estruturas totalmente diferenciais, que é o mesmo tipo de estrutura escolhido para a realização do filtro passa-faixa, por motivos que serão analisados.

#### 4.1 MIXERS E TRANSLAÇÃO DE FREQÜÊNCIAS

Desde o surgimento dos receptores super-heteródinos (LATHI, 1998), os mixers, também conhecidos como misturadores ou conversores de frequência, têm determinado a performance total de modernos sistemas de rádio, uma vez que a grande maioria destes sistemas usa este tipo de dispositivo (MACHADO, 1996).

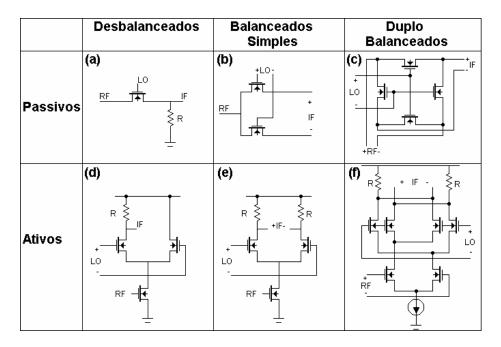

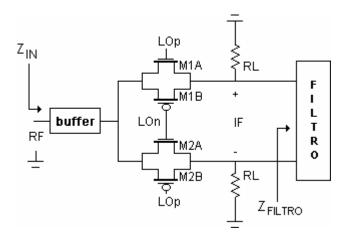

Os mixers podem ser divididos, de acordo com o ganho que dão ao sinal convertido, em dois tipos: ativos, cujo ganho de conversão é maior que um e, portanto, consomem uma certa potência quiescente, e passivos, os quais consomem apenas potência dinâmica, possuindo um ganho de conversão menor que um (perda de conversão) (LEUNG, 2002). Esses dois tipos de mixer possuem performances diferentes quanto à distorção, ruído e largura de banda. Os ativos propiciam menor ruído com maior distorção, ao passo que os passivos apresentam, em geral, maior linearidade e velocidade (RAZAVI, 1998).

Além disso, os mixers podem ser divididos, de acordo com os sinais de entrada e saída, em desbalanceados, balanceados simples e duplos balanceados (RAZAVI, 1998). Os desbalanceados (*unbalanced*) possuem uma entrada em RF e um sinal do oscilador local com entrada unipolar. Os mixers balanceados simples (*single balanced*), possuem uma entrada para RF e um sinal de LO diferencial. Já os duplos balanceados (*double balanced*) possuem tanto uma entrada RF quanto um sinal de LO diferenciais. A forma de operação dos mixers, quanto a serem balanceados ou não, irá determinar, idealmente, a existência ou não do chamado *feedthrough*, ou seja, o quão bom será o isolamento que este dispositivo irá propiciar entre suas três portas (RF, LO e IF). Um mixer desbalanceado, por exemplo, apresenta RF-IF *feedthrough*, que é a passagem do sinal de entrada RF para o sinal de saída IF. Já os balanceados simples não apresentam RF-IF *feedthrough*, mas apresentam LO-IF *feedthrough*. Finalmente, os duplos balanceados não possuem RF-IF *feedthrough*, nem LO-IF *feedthrough*, mas possuem RF-LO *feedthrough*, o que também não é desejado.

A figura 15 apresenta alguns exemplos mais conhecidos dos tipos de mixers ativos e passivos existentes.

Figura 15. Exemplos de mixers ativos e passivos, conforme (LEUNG, 2002; RAZAVI, 1998).

Para o circuito da figura 15(a), se o resistor de carga for substituído por um capacitor, tem-se o chamado mixer de amostragem (*sampling mixer*), que é também utilizado como circuito de *sample-and-hold* para uso em conversores analógico-digitais, por exemplo. O circuito da figura 15(f), é também conhecido como Célula de Gilbert.

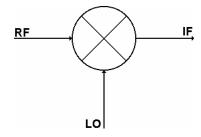

Independentemente do tipo de mixer, cuja representação está mostrada na figura 16, sua operação é similar a de um multiplicador. Um mixer converte um sinal de uma frequência (tipicamente  $\omega_{RF}$ ) para outra frequência (tipicamente  $\omega_{IF}$ ), através da multiplicação do primeiro por um outro sinal, proveniente de um oscilador local ( $\omega_{LO}$ ).

Figura 16. Representação de um mixer com seus sinais de entrada (RF), do oscilador local (LO) e de saída (IF).

É importante ressaltar que, apesar do funcionamento de um mixer poder ser explicado a partir do funcionamento de um multiplicador, existem diferenças entre esses circuitos, assim como existem diferenças entre um multiplicador e um modulador. Esses três tipos de "geradores de produtos" podem ser rapidamente diferenciados como a seguir (MACHADO, 1996).

Multiplicadores são essencialmente lineares na resposta quanto aos valores instantâneos de ambas as entradas, mas com algumas perdas em termos de ruído e largura de banda. Já os moduladores são lineares na resposta para uma das entradas, sendo a sua saída simplesmente a multiplicação desta entrada pelo sinal da outra entrada, não possuindo qualquer outro efeito sobre o sinal. Por fim, os mixers são moduladores especializados em translação de freqüência. São invariavelmente otimizados para produzir mínimo ruído e mínima distorção de intermodulação.

Tomando-se um mixer genérico como o mostrado na figura 16, e considerando um sinal senoidal de frequência  $\omega_{RF}$  na entrada RF e um sinal também senoidal gerado pelo oscilador local (LO), cuja frequência é  $\omega_{LO}$ , tem-se na saída IF do mixer o produto entre estes dois sinais, dado por:

$$S_{IF} = \operatorname{sen}(\omega_{RF}) \cdot \operatorname{sen}(\omega_{LO}) = \frac{1}{2} \left[ \cos(\omega_{RF} + \omega_{LO})t + \cos(\omega_{RF} - \omega_{LO})t \right]$$

(10)

A multiplicação entre os dois sinais (RF e LO) transformou a entrada RF em duas componentes de saída (IF), uma resultante da soma de  $\omega_{RF}$  e  $\omega_{LO}$  e outra resultante da subtração de  $\omega_{RF}$  e  $\omega_{LO}$ . Quando o sinal cuja freqüência é a resultante da soma de  $\omega_{RF}$  e  $\omega_{LO}$  é utilizado como sinal de IF, tem-se a chamada *up-conversion*; quando IF é dada pela subtração de  $\omega_{RF}$  e  $\omega_{LO}$ , tem-se uma *down-conversion*. Ainda, quando a freqüência de LO é menor que a freqüência de RF, tem-se uma conversão do tipo *low-side*; ao contrário, se a freqüência de LO é maior que a freqüência de RF, tem-se uma conversão do tipo *high-side*.

Considerando-se um mixer de chaves como o mostrado na figura 15(a), o sinal de LO passa a ser não uma senóide, mas uma onda quadrada a qual pode, por exemplo, assumir apenas os valores +1 e -1. Assim, esta forma de onda pode ser expressa por sua série de Fourier (SPIEGEL, 1992) da seguinte forma:

$$S_{LO} = \frac{4}{\pi} \left( \operatorname{sen} \omega_{LO} t - \frac{1}{3} \operatorname{sen} 3\omega_{LO} t + \frac{1}{5} \operatorname{sen} 5\omega_{LO} t - \dots \right)$$

(11)

Assim sendo, a multiplicação da senóide de entrada pelo conjunto de senóides em LO pode ser dada, já se expandindo os produtos, por:

$$S_{IF} = \frac{2}{\pi} \left[ \cos(\omega_{RF} + \omega_{LO})t + \cos(\omega_{RF} - \omega_{LO})t - \frac{1}{3}\cos(\omega_{RF} + 3\omega_{LO})t - \frac{1}{3}\cos(\omega_{RF} - 3\omega_{LO})t + \frac{1}{5}\cos(\omega_{RF} - 5\omega_{LO})t + \frac{1}{5}\cos(\omega_{RF} - 5\omega_{LO})t - \dots \right]$$

(12)

Portanto, passa-se agora a ter um conjunto de harmônicas formadas pelas somas e diferenças entre o sinal de RF e múltiplos ímpares do sinal de LO. Essas harmônicas, apesar de possuírem uma atenuação (1/3, 1/5, ...), podem colaborar para a introdução de não

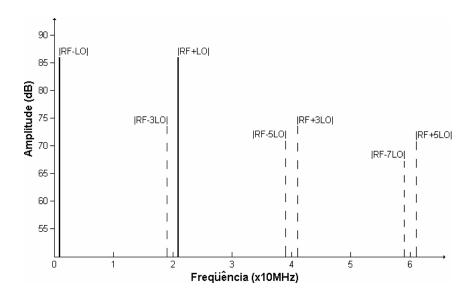

linearidades no sinal de freqüência intermediária (IF). O espectro dos dois tipos de multiplicação utilizando-se um LO senoidal e um LO com forma de onda quadrada pode ser visto na figura 17 (vide arquivos de simulação no apêndice C). Neste exemplo, a freqüência angular  $\omega_{RF}$  é  $2\pi 11 MHz$  e a freqüência angular  $\omega_{LO}$  é  $2\pi 10 MHz$ . No caso de um LO com onda quadrada, o espectro é o mesmo que aquele com LO senoidal, porém com a introdução das harmônicas indicadas por linhas tracejadas.

Figura 17. Espectro da multiplicação de duas senóides e uma senóide e uma onda quadrada.

Para a caracterização de sistemas não lineares, como é o caso dos mixers, utilizam-se alguns parâmetros específicos, dentre eles a distorção harmônica (HD<sub>3</sub>), intermodulação (HM<sub>3</sub>) e o ponto de interceptação de terceira ordem (IP<sub>3</sub>), sendo que apenas a determinação de um destes três parâmetros (em geral o ponto de interceptação de terceira ordem) é o suficiente para caracterizar um mixer, já que estes parâmetros estão relacionados entre si (LEUNG, 2002; RAZAVI, 1998; MACHADO, 1996). Outro parâmetro importante é o ruído adicionado pelo circuito, o qual pode ser caracterizado pela figura de ruído (NF).

#### 4.2 ESTRUTURAS DIFERENCIAIS

Na integração de circuitos analógicos, distúrbios de segunda ordem podem causar distorções no sinal e limitar a performance do circuito. Elementos parasitas, associados com todos circuitos integrados, provém inúmeros caminhos para que sinais indesejáveis se misturem ao sinal analógico, seja através do substrato, das fontes de alimentação ou linhas de terra. Os distúrbios originados destas fontes podem se acumular, levando a grandes perdas na relação sinal – ruído e na faixa dinâmica (LAKER, 1994).

Para reduzir estes efeitos degenerativos, estruturas diferenciais têm sido largamente utilizadas na fabricação de circuitos integrados analógicos. Dentre os três FPAAs comerciais existentes atualmente, dois deles (família AnadigmVortex e família ispPAC) possuem uma estrutura totalmente diferencial (fully differential).

Para melhorar ainda mais a resposta do circuito, é necessário que este não apenas tenha uma estrutura diferencial, mas que esta seja também balanceada, ou seja, seja realizada com caminhos de sinais invertidos e não – invertidos, num circuito totalmente simétrico.

Seja o sistema descrito em (13). Se a<sub>j</sub>=0 para j = par, então a equação (14) é satisfeita, e o sistema possui simetria ímpar, sendo, portanto, balanceado (RAZAVI, 1998).

$$y(t) = a_0 + a_1 x(t) + a_2 x(t)^2 + a_3 x(t)^3 + a_4 x(t)^4 + \dots$$

(13)

$$a_1x(t) + a_3x(t)^3 + \dots = -a_1x(t) - a_3x(t)^3 - \dots$$

(14)

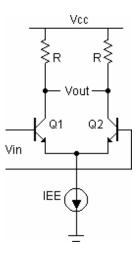

Tomando-se por exemplo o par diferencial descrito na figura 18, sua resposta pode ser dada por:

$$Vout = R.I_{EE}. \tanh\left(\frac{Vin}{2V_T}\right)$$

(15)

Sendo a função tangente hiperbólica uma função ímpar (SPIEGEL, 1992), então o circuito em questão é balanceado.

Figura 18. Par diferencial bipolar, conforme (RAZAVI, 1998).

Com uma estrutura totalmente diferencial e balanceada, todos sinais parasitas se acoplarão igualmente nos caminhos dos sinais como sinais de modo comum. A natureza diferencial destes circuitos faz com que os distúrbios de modo comum cancelem-se, reduzindo significativamente seu impacto (LAKER, 1994).

Em contrapartida, projetos totalmente diferenciais terão um custo maior, uma vez que será necessária a duplicação de muitos dos circuitos e componentes existentes.

#### 4.3 MIXER PROPOSTO

Em sistemas de rádio-recepção, os mixers são utilizados para realizar uma translação dos sinais em altas freqüências para uma freqüência mais baixa. Isso é feito para se obter uma maior seletividade, pois é mais difícil obter-se filtros de alta seletividade com uma banda

estreita (10 KHZ para voz, por exemplo) com sinais modulados em freqüências muito altas, principalmente se o filtro deve ser sintonizável. Todavia, em freqüências mais baixas, a seletividade pode ser feita muito mais facilmente (LATHI, 1998). Já para sistemas de rádiotransmissão, o objetivo dos mixers é a de elevar a freqüência da portadora, facilitando a transmissão do sinal de informação através da utilização de antenas menores e mais compactas, por exemplo, ou obtendo-se uma maior diretividade, como no caso das transmissões em microondas. Nestes sistemas, diferentes especificações de performance devem ser priorizadas baseadas na aplicação do mixer. Algumas especificações são para aplicações em receptores, cuja faixa dinâmica dos sinais de entrada é bastante larga, sendo então uma máxima linearidade em geral mais crítica do que a figura de ruído. Por outro lado, para transmissores, onde os níveis de sinal podem ser controlados, a estratégia de projeto oscila entre performance em ruído ou em distorção de intermodulação, para se obter sinais cuja faixa dinâmica seja a maior possível (LONG, 2002a). Assim, é comum ter-se um mixer específico para realização de *up-conversion* e outro específico para *down-conversion*.

Além disso, mixers utilizados em sistemas de rádio em geral são desenvolvidos para realizar a conversão de sinais dentro de uma certa banda para uma freqüência específica, como por exemplo, no sistema de radiodifusão de modulação em amplitude (AM), onde os sinais na banda compreendida entre 530KHz e 1710KHz são movidos para uma freqüência intermediária de 455KHz (LATHI, 1998).