# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

#### TATIANA GADELHA SERRA DOS SANTOS

#### Reusing Values in a Dynamic Conditional Execution Architecture

Thesis presented in partial fulfillment of the requirements for the degree of Doctor of Computer Science

Prof. Dr. Sergio Bampi Advisor

Prof. Dr. Philippe Olivier Alexandre Navaux Coadvisor

#### CIP - CATALOGING-IN-PUBLICATION

Santos, Tatiana Gadelha Serra dos

Reusing Values in a Dynamic Conditional Execution Architecture / Tatiana Gadelha Serra dos Santos. – Porto Alegre: Programa de Pós-Graduação em Computação, 2004.

115 f.: il.

Thesis (Ph.D.) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação, Porto Alegre, BR-RS, 2004. Advisor: Sergio Bampi; Coadvisor: Philippe Olivier Alexandre Navaux.

Superscalar Architecture.

Instruction Reuse.

Trace Reuse.

Multipath Execution.

Dynamic Conditional Execution.

Bampi, Sergio.

Navaux, Philippe Olivier Alexandre.

Title.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. José Carlos Ferraz Hennemann Vice-Reitor: Prof. Pedro Cezar Dutra Fonseca

Pró-Reitora Adjunta de Pós-Graduação: Prof<sup>a</sup>. Valquiria Link Bassani

Diretor do Instituto de Informática: Prof. Philippe Olivier Alexandre Navaux

Coordenador do PPGC: Prof. Carlos Alberto Heuser

Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

#### **ACKNOWLEDGMENTS**

This is certainly the best part on writing this Dissertation. The part that I have to look back and remember all good (and bad) times and people which crossed my way in the last 5 years. What can I say initially? Well... I already have tears on my eyes and I didn't even started!

It's pretty difficult to acknowledge all the people who contributed in this achievement. Hopefully, I won't forget you... But if for some reason your name is not here, please be sure that I didn't mean it. You're certainly in the bottom of my heart!

Let's start from the beginning, then. Mom and Dad. I think they are the real heroes here. They were always there for me. I owe them everything that I am and everything that I became. I thought about them all the times when I looked to my computer and said "OK, this is it! I'm giving up". Of course, I never gave up. And the simple fact of remembering how they taught me to be patient and persistent changed my mind right away. I really want them to be as proud to be my parents as I am to be their daughter. Priceless. My brother Yves, my little doctor, also deserves a big bite on this account. Even not talking to him as often as I want to, I know that there is a big, big love between us. I know that I can count on him and that he is there, ready to protect his little sister. It's really good to have him and to be sure about all this.

After my own family, but as important as they are, come Rafael and his family. He helped in every way that I can possibly remember. Even laughing at me when I was about to through my machine in the floor. He was and he is a great friend. And I'm very proud to say that I wouldn't have made it without his support. His family was also always present in my life in the past years, helping and supporting me in whatever they could. I'm really thankful for all of them.

My advisors Professor Sergio Bampi and Professor Philippe Navaux. Extraordinary people. They were always ready to listen, to help and, of course, to put me back on track when necessary. Today I can say that both of them are not just advisors, but they are friends, friends that I'll never forget. I'm not sure if I ever had the chance to tell how I admire them, but I'd like to take the time now. And I'd say: "When I grow up I want to be just like you!".

And the friends... I don't even know where to begin with. They are all awesome. They are all in my heart. And they all have to do with this work (even the ones who hate computers!).

First, my friends from UFRGS who were here in the bad mood days: Roberta (and Fabiano, Diogo and Pedro), Mônica, Rafael Bohrer, Mozart (and Chris), Ju, Patty, Nico, Pilla and Pizzol. Thank you, guys! Not only for your insights in this work, but specially to help me feel at home. Thank you for introduce me in the

coffee lovers life, thank you for all the lunches we had together, thank you for all sunny Sundays at the "Brique" and, above of all, thank you for your friendship. I will never forget you. I also won't forget my new friends and housemates, Márcia and Marta Pasin. They are really cool!

I'd like to remember my friends from UNISC as well: Rita, Rejane, Dani, Andrea and all others that made that environment such a nice place to work. And my students! All of them... They have a special place in my heart. In fact, sometimes I feel that they are my Professors. I sincerely hope that they have enjoyed our classes as much as I did.

And also the friends from the time I spent in USA and, mainly the Brazilian troupe: Nedja (and Andy, Ian and Lara), Dani (and Ewerton, Marcela and Leo), Andréia (and Joni and Luca), Maira (and Maurício and Enzo), Sérgio and Ricardo. Thanks for being my family during those years. Thank you for all parties, barbecues, trips and all the fun we had. You guys are terrific! Finally, all the old friends from Natal, especially Sadinha (and Rodrigo).

At last, I also would like to acknowledge CNPq for the scholarship, the Informatics Institute for the great support and, specially, the people from the Labtec and Corisco clusters for all their patience and time for running all my hundreds of simulations.

#### **AGRADECIMENTOS**

Essa é, sem dúvida, a melhor parte em escrever essa Tese. A parte em que eu tenho que olhar pra trás e relembrar de todos os bons (e maus) momentos e pessoas que atravessaram meu caminho nos últimos 5 anos. O que eu posso dizer inicialmente? Bem... eu já estou com os olhos mareados e nem ao menos comecei!

É bem difícil agradecer a todos que contribuiram com essa conquista. E, sinceramente, eu espero que eu não tenha esquecido você... mas se, por alguma razão, seu nome não está aqui, tenha certeza que não foi intencional. Você certamente está no fundo do meu coração!

Vamos, então, começar bem do princípio. O pai e a mãe. Eu realmente acho que eles são os verdadeiros heróis. Eles sempre estiveram aqui por mim. E eu devo pra eles tudo que sou e que me tornei. Todas as vezes que eu olhei para o computador e disse "OK, é o fim! Vou desistir", foi neles que pensei. É claro que nunca desisti. E o simples fato de lembrar como eles me ensinaram a ser paciente e persistente mudava meu pensamento. Eu realmente quero que eles tenham tanto orgulho em ser meus pais como eu tenho orgulho de ser filha deles. E isso não tem preço. Meu irmão Yves, meu Doutorzinho, também merece um grande crédito. Mesmo não conversando com ele com a freqüência que eu gostaria, eu sei que existe um grande amor entre a gente. Eu sei que posso contar com ele e ele sempre estará ali, pronto para proteger a irmãzinha. É realmente bom tê-lo e ter certeza de tudo que estou dizendo aqui.

Depois da minha própria família, mas tão importante quanto ela, vem o Rafael e a família dele. Ele me ajudou de todas as maneiras que eu posso possivelmente tentar lembrar. Mesmo nas vezes que ele ria de mim quando eu estava quase jogando minha máquina no chão. Ele foi e ele é um grande amigo. E eu tenho muito orgulho em dizer que eu não teria terminado sem o apoio dele. A família dele também sempre esteve presente na minha vida nos últimos anos, me ajudando e apoiando em tudo que eles podiam.

Meus orientadores Professores Sergio Bampi e Philippe Navaux. Pessoas extraordinárias. Eles estavam sempre prontos para ouvir, ajudar e, claro, me colocar de volta no caminho certo quando necessário. Hoje eu posso dizer que os dois não são apenas orientadores, mas amigos, amigos que eu nunca vou esquecer. Eu não tenho certeza se eu já tive chance de dizer o quanto eu os admiro, mas eu gostaria de fazê-lo agora. E diria: "Quando crescer, quero ser igualzinha a vocês!".

E os amigos... Eu nem mesmo sei por onde começar. Todos eles são fenomenais. Todos eles estão no meu coração. E todos eles tem sua parcela nesse trabalho (inclusive aqueles que odeiam computação!).

Primeiro, os amigos da UFRGS, que estavam aqui nos dias de mau humor:

Roberta (e Fabiano, Diogo e Pedro), Mônica, Rafael Bohrer, Mozart (e Chris), Ju, Patty, Nico, Pilla e Pizzol. Obrigada, galera! Não só pelas idéias nesse trabalho, mas especialmente por ajudarem a me sentir em casa. Obrigada por me introduzirem no mundo dos amantes do café, obrigada por todos os nossos almoços, obrigada por todos os domingos ensolarados no brique e, acima de tudo, obrigada pela amizade de vocês. Eu nunca vou esquecê-los. Eu também nunca vou esquecer minhas novas amigas que dividem o ap, a Márcia e a Marta Pasin. Elas são muito legais!

Eu gostaria de lembrar também dos meus amigos da UNISC: Rita, Rejane, Dani, Andrea e todos os outros que fizeram daquele ambiente um lugar tão legal de trabalhar. E os meus alunos! Todos eles... Eles têm um lugar especial no meu coração. De fato, às vezes sinto que eles são os meus professores. Eu sinceramente desejo que eles tenham curtido nossas aulas da mesma forma que eu curti.

Também aos amigos feitos enquanto morava nos EUA e, principalmente, a tropa brasileira: Nedja (e Andy, Ian e Lara), Dani (e Ewerton, Marcela e Leo), Andréia (e Joni e Luca), Maira (e Maurício e Enzo), Sérgio e Ricardo. Obrigada por serem minha família durantes aqueles anos. Obrigada por todas as festas, churrascos, passeios e toda a diversão que sempre fizemos. Vocês são realmente maravilhosos! Finalmente, todos os meus velhos amigos de Natal, especialmente a Sadinha (e o Rodrigo).

Por último, eu gostaria de agradecer ao CNPq pela bolsa de doutorado, ao Instituto de Informática pelo grande suporte e, especialmente, às pessoas dos clusters Labtec e Corisco por toda paciência e tempo para rodar as minha centenas de simulações.

## TABLE OF CONTENTS

| LIST OF ABBREVIATIONS AND ACRONYMS |                                       |    |  |  |

|------------------------------------|---------------------------------------|----|--|--|

| LIST                               | LIST OF FIGURES                       |    |  |  |

| LIST                               | LIST OF TABLES                        |    |  |  |

| ABST                               | <b>ABSTRACT</b>                       |    |  |  |

| RESU                               | <b>RESUMO</b>                         |    |  |  |

| 1 IN                               | TRODUCTION                            | 17 |  |  |

|                                    |                                       | 20 |  |  |

| 2.1                                |                                       | 24 |  |  |

| 2.2                                | <del>-</del>                          | 25 |  |  |

| 2.3                                | Summary                               | 31 |  |  |

| 3 D                                | CE - DYNAMIC CONDITIONAL EXECUTION    | 32 |  |  |

| 3.1                                | Hammock Classification                | 33 |  |  |

| 3.2                                | DCE Pipeline                          | 36 |  |  |

| 3.2.1                              | Fetch                                 | 37 |  |  |

| 3.2.2                              | Register Rename – First Stage         |    |  |  |

| 3.2.3                              | Register Rename – Second Stage        |    |  |  |

| 3.2.4                              | Dispatch                              |    |  |  |

| 3.2.5                              |                                       | 39 |  |  |

| 3.2.6                              | Execution                             | 39 |  |  |

| 3.2.7                              | Write Back                            | 39 |  |  |

| 3.2.8                              | Commit                                | 39 |  |  |

| 3.3                                | DCE Optimizations – the CIDI Approach | 40 |  |  |

| 4 D                                | CE LIMITATIONS                        | 42 |  |  |

| 4.1                                |                                       | 42 |  |  |

| 4.2                                |                                       | 43 |  |  |

| 4.2.1                              | -                                     | 43 |  |  |

| 4.2.2                              |                                       | 47 |  |  |

| 5 P                                | REVIOUS WORKS                         | 52 |  |  |

| 6.1.1<br>6.1.1<br>6.2<br>6.2.1<br>6.2.2                                                          | EUSING VALUES IN DCE       57         Instruction Reuse in DCE       58         Memory Access Reuse       59         Trace Reuse in DCE       61         Building and Storing a Trace       61         Reusing a Trace       64                                                                                                                        |

|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 S<br>7.1<br>7.2<br>7.3                                                                         | IMULATION ENVIRONMENT         67           The Extended sim-dce Simulator         67           Simulation Strategy         70           Summary         72                                                                                                                                                                                             |

| 8 S<br>8.1<br>8.1.1<br>8.1.2<br>8.1.3<br>8.2<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>8.2.5<br>8.3 | IMULATION RESULTS74Reusing Instructions as an Alternative to DCE overhead74Number of Reused Instructions74Overhead Reduction74Overall Performance75Reusing Traces as an Alternative to DCE overhead77Traces Characteristics78Overhead Reduction80Number of Cycles that an Instruction Remains in the Pipeline82Speedup84Side Effects in DCE90Summary95 |

| 9 C<br>9.1<br>9.1.1<br>9.1.2<br>9.1.3                                                            | CONCLUSIONS96Future Work100Reusing Branches100Trace Reuse Based on a Fixed Stride100Out-of-Order Commit101                                                                                                                                                                                                                                             |

| 7<br>10.1<br>10.2<br>10.3                                                                        | EUSANDO VALORES EM UMA ARQUITETURA COM EXECU-         ÃO CONDICIONAL DINÂMICA       105         Introdução       105         O Reuso de Valores na Arquitetura DCE       105         Sumário das Conclusões       110         ERENCES       111                                                                                                        |

#### LIST OF ABBREVIATIONS AND ACRONYMS

ALU Arithmetic and Logic Unit

BHB Block History Buffer

BTB Branch Target Buffer

CIDI Control Independent Data Independent

CPU Central Processing Unit

D-cache Data Cache

DCE Dynamic Contional Execution

DRAM Dynamic Random Access Memory

DTM Dynamic Trace Memoization

FP Floating Point

FU Functional Unit

I-cache Instruction Cache

IC Input Context

ILP Instruction Level Parallelism

Int Integer

IPC Instructions Per Cycle

L1 cache Level 1 L2 cache Level 2

LRB Load Reuse Buffer

LRU Least Recently Used

OC Output Context

OS Operating System

PC Program Counter

RAM Random Access Memory

RAW Read After Write

RB Reuse Buffer

ROB ReOrder Buffer

RISC Reduced Instruction Set Computer

RTM Reuse Trace Memory

SMT Simultaneous MultiThread

Sn reuse Scheme (name)

Sv reuse Scheme (value)

Sv+d reuse Scheme (value and dependence)

SRAM Static Random Access Memory

TLB Translation Lookaside Buffer

TB Trace Buffer

WAR Write After Read

WAW Write After Write

## LIST OF FIGURES

| Figure 2.1:  | Fetch stage                                                         | 20 |

|--------------|---------------------------------------------------------------------|----|

| Figure 2.2:  | Fetch width with branch occurrence                                  | 21 |

| Figure 2.3:  | Misfetch occurrence                                                 | 23 |

| Figure 2.4:  | Misprediction occurrence                                            | 23 |

| Figure 2.5:  | Sim-outorder pipeline                                               | 24 |

| Figure 2.6:  | Fetch stage stalls                                                  | 26 |

| Figure 2.7:  | Percentage of cycles wasted due to branch occurrence                | 27 |

| Figure 2.8:  | Instructions fetched per cycle                                      | 27 |

| Figure 2.9:  | Distribution of instructions in benchmarks (a) bzip2 and (b) equake | 28 |

| Figure 2.10: | Distribution of instructions in benchmarks (a) gcc and (b) mesa .   | 29 |

| Figure 2.11: | Distribution of instructions in benchmarks (a) parser and (b) vpr   | 30 |

| Figure 2.12: | Instructions Per Cycle achieved with hybrid and perfect predictions | 30 |

| Figure 3.1:  | Fetch cycle example in DCE                                          | 34 |

| Figure 3.2:  | Example of simple hammocks                                          | 35 |

| Figure 3.3:  | Example of complex hammocks                                         | 35 |

| Figure 3.4:  | DCE pipeline                                                        | 37 |

| Figure 3.5:  |                                                                     | 40 |

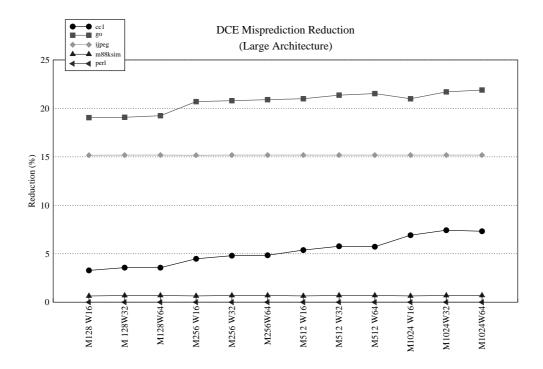

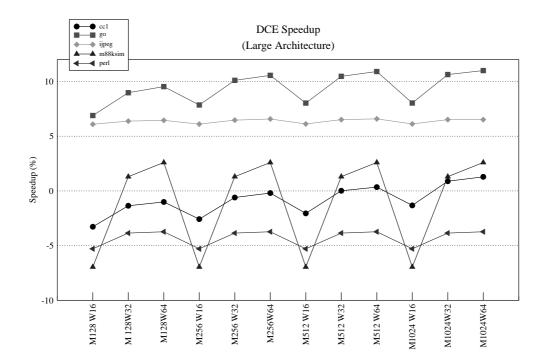

| Figure 4.1:  | DCE misprediction reduction (large architecture)                    | 45 |

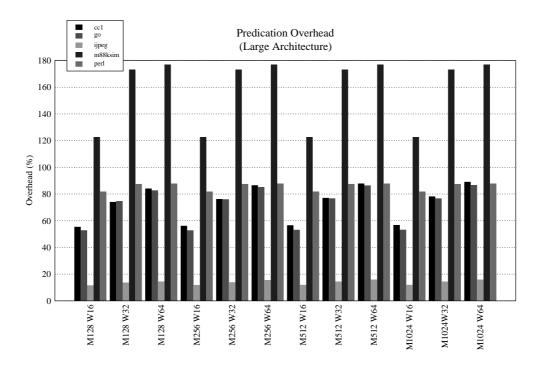

| Figure 4.2:  | DCE speedup (large architecture)                                    | 46 |

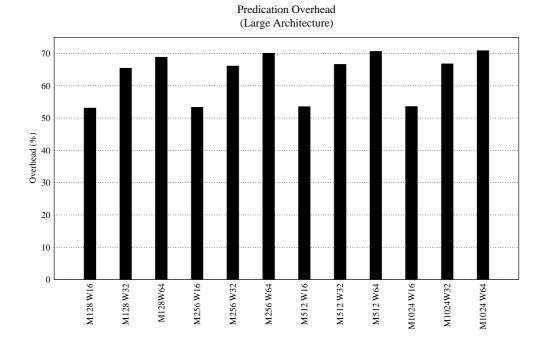

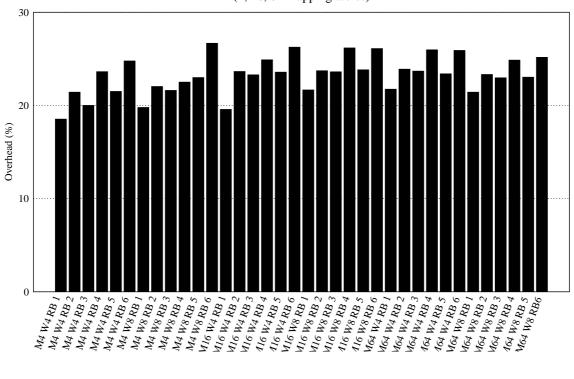

| Figure 4.3:  | Overhead produced (large architecture)                              | 46 |

| Figure 4.4:  | Harmonic mean of overhead produced in all benchmarks simula-        |    |

| 9            | ted (large architecture)                                            | 47 |

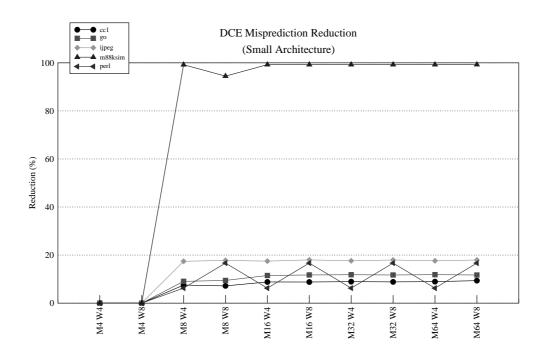

| Figure 4.5:  | DCE misprediction reduction (small architecture)                    | 48 |

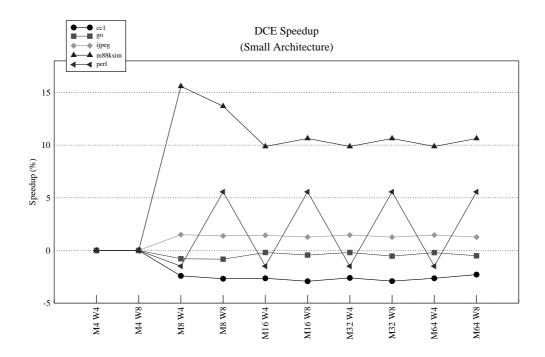

| Figure 4.6:  | DCE speedup (small architecture)                                    | 49 |

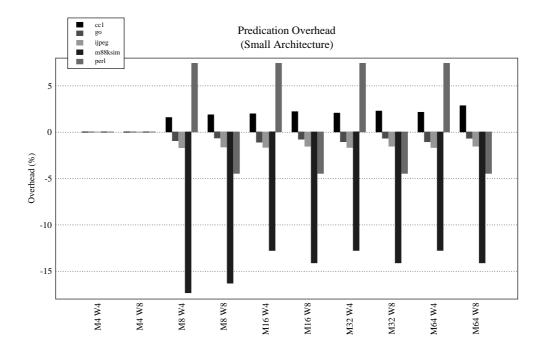

| Figure 4.7:  | Overhead produced (small architecture)                              | 49 |

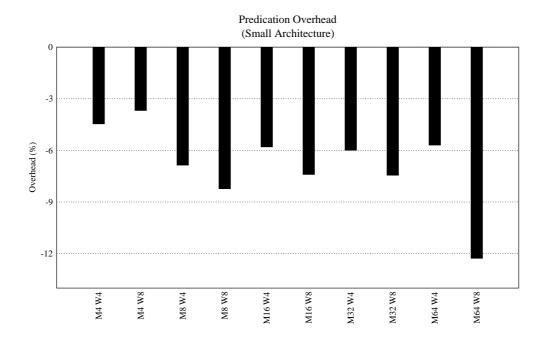

| Figure 4.8:  | Average of overhead produced (small architecture)                   | 50 |

| Figure 4.9:  | Redundant instructions introduced by DCE                            | 51 |

| Figure 6.1:  | Pipeline with an instruction reuse mechanism                        | 58 |

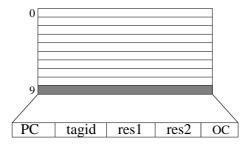

| 0            | Reuse Buffer (RB) organization                                      | 58 |

|              | Data dependent branches                                             | 59 |

| ~            | Trace example                                                       | 62 |

| 0            | Input and output context formation                                  | 62 |

| Figure 6.6:  | Building a trace                                                    | 64 |

| 0            | Trace Buffer (TB) structure                                         | 65 |

| ~            | Pendent buffer                                                      | 66 |

| Figure | 7.1:  | Simplified algorithm for trace reuse                                | 68  |

|--------|-------|---------------------------------------------------------------------|-----|

| Figure | 7.2:  | Simplified algorithm for trace construction                         | 69  |

| Figure | 7.3:  | Simplified algorithm for trace storage                              | 69  |

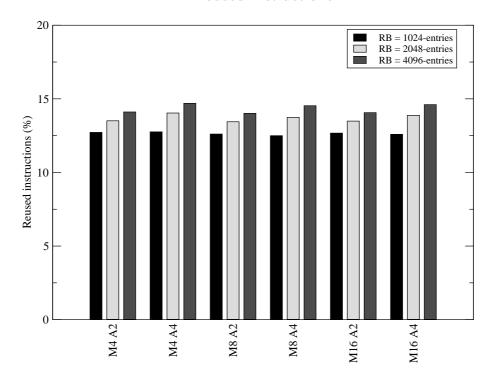

| Figure | 8.1:  | Percentage of reused instructions (8 wide architecture)             | 75  |

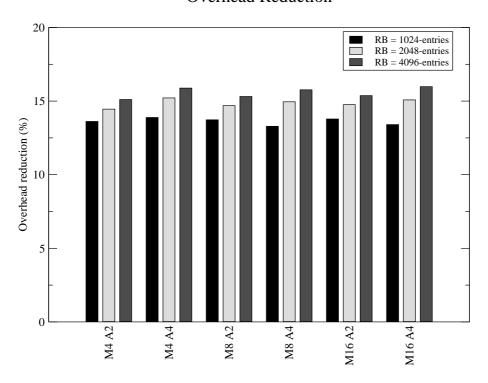

| Figure | 8.2:  | Percentage of overheard reduction                                   | 76  |

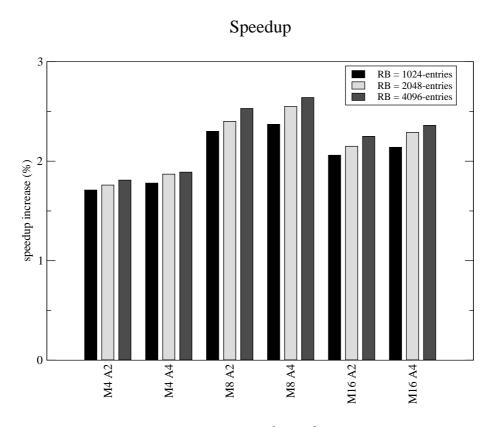

| Figure | 8.3:  | Percentage of speedup increase                                      | 76  |

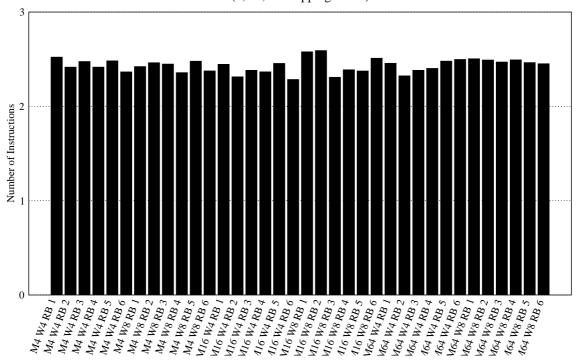

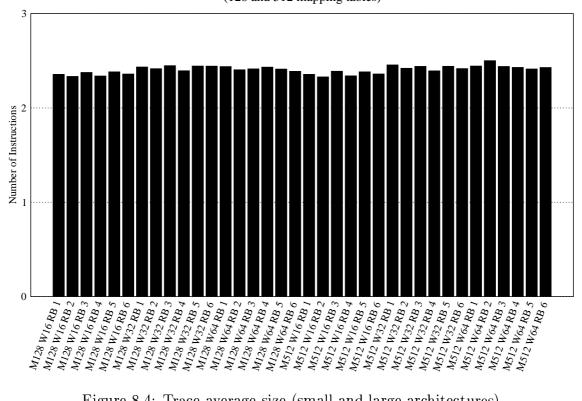

| Figure | 8.4:  | Trace average size (small and large architectures)                  | 79  |

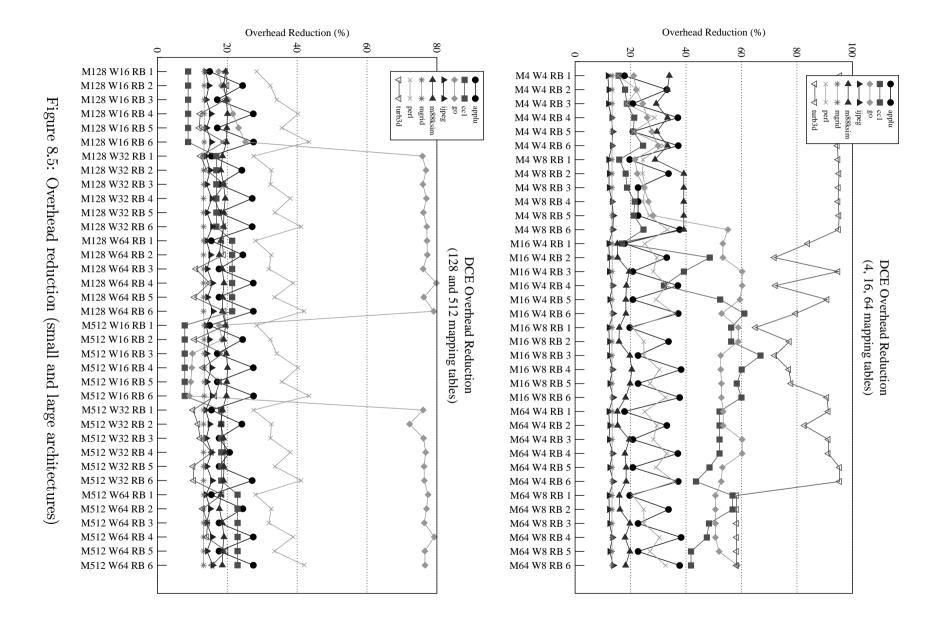

| Figure | 8.5:  | Overhead reduction (small and large architectures)                  | 81  |

| Figure | 8.6:  | Average of overhead reduction (small and large architectures)       | 83  |

| Figure | 8.7:  | Average of cycles in pipeline (small and large architectures)       | 85  |

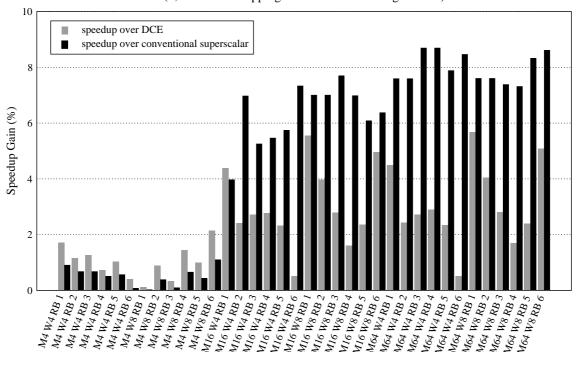

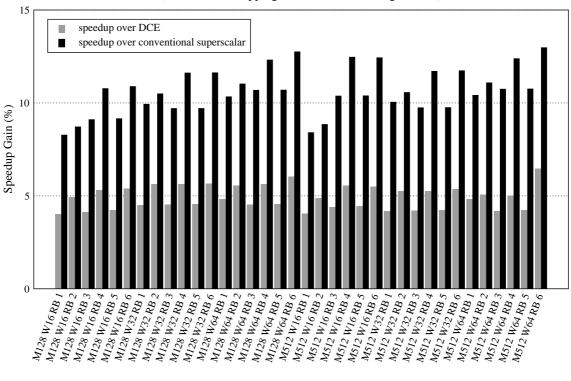

| Figure | 8.8:  | Percentage of gain in speedup (small and large architectures)       | 86  |

| Figure | 8.9:  | Percentage of gain in speedup of value reuse in DCE and in con-     |     |

|        |       | ventional superscalar architecture(small and large architectures) . | 91  |

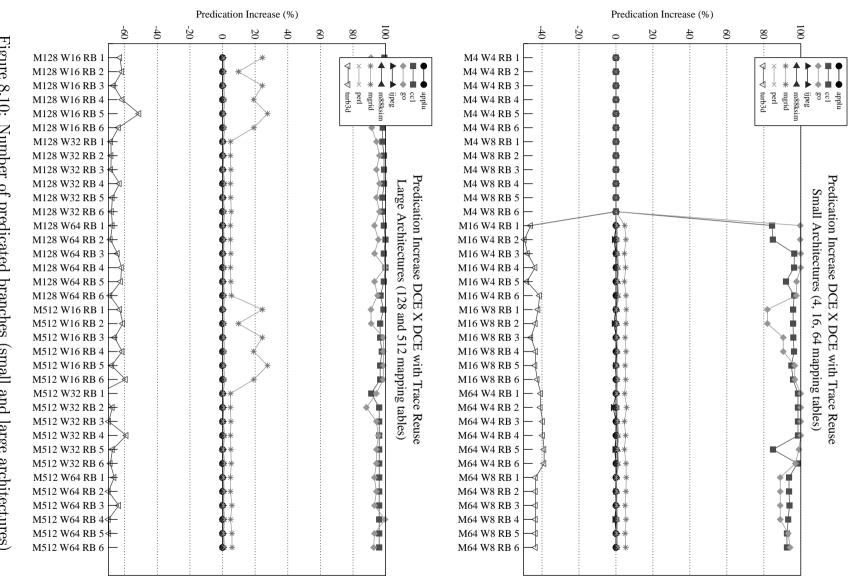

| Figure | 8.10: | Number of predicated branches (small and large architectures)       | 92  |

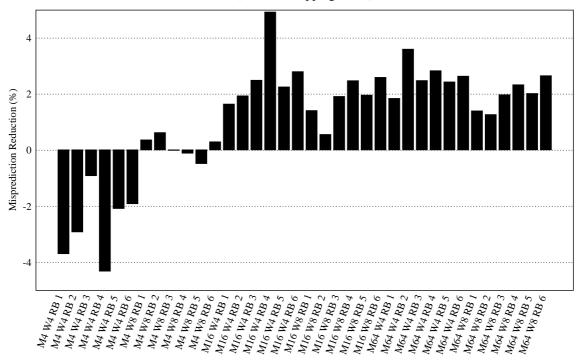

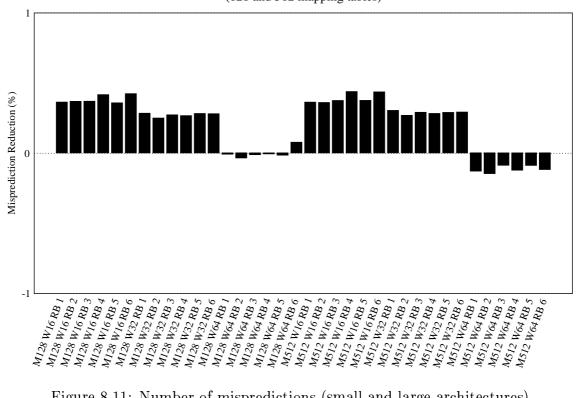

| Figure | 8.11: | Number of mispredictions (small and large architectures)            | 94  |

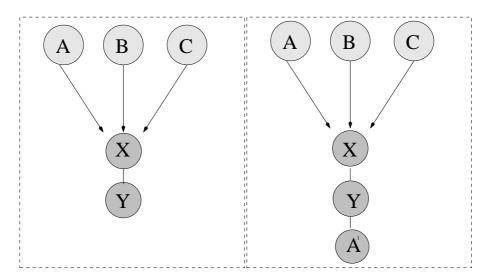

| Figure | 9.1:  | Outputs generation                                                  | 100 |

| Figure | 9.2:  | Trace not reused due to not ready operands                          | 102 |

| Figure | 9.3:  | Trace not reused with different output and input scopes 1           | 103 |

|        |       |                                                                     |     |

## LIST OF TABLES

| Table 2.1: | Configurations used in experiments                               | 25 |

|------------|------------------------------------------------------------------|----|

| Table 2.2: | Benchmarks and inputs used in the experiments                    | 25 |

| Table 2.3: | Effective fetch bandwidth                                        | 29 |

| Table 4.1: | Configurations used in original DCE experiments (large architec- |    |

|            | ture)                                                            | 43 |

| Table 4.2: | Configurations used in original DCE experiments (small architec- |    |

|            | ture)                                                            | 44 |

| Table 4.3: | Benchmarks inputs used in the simulations                        | 44 |

| Table 6.1: | Summary of pipeline modifications to support instruction reuse . | 60 |

| Table 6.2: | Summary of pipeline modifications to support trace reuse         | 66 |

| Table 7.1: | Configurations used in extended DCE experiments (first set)      | 71 |

| Table 7.2: | Configurations used in extended DCE experiments (second set) .   | 72 |

| Table 7.3: | Benchmarks inputs used in the simulations                        | 73 |

| Table 8.1: | Reuse and Trace Buffers configurations showed in results         | 78 |

| Table 8.2: | Harmonic Mean (in percentage) for the DCE speedup with trace     |    |

|            | reuse (4, 16, 64 mapping tables)                                 | 88 |

| Table 8.3: | Harmonic Mean (in percentage) for the DCE speedup with trace     |    |

|            | reuse (128 and 512 mapping tables)                               | 89 |

|            |                                                                  |    |

#### **ABSTRACT**

The Dynamic Conditional Execution (DCE) is an alternative to reduce the cost of mispredicted branches. The basic idea is to fetch all paths produced by a branch that obey certain restrictions regarding complexity and size. As a consequence, a smaller number of predictions is performed, and therefore, a lower number branches is mispredicted.

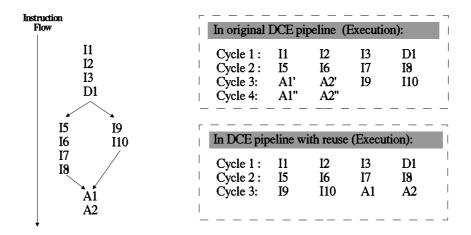

Nevertheless, as other multipath solutions, DCE requires a more complex control engine. In a DCE architecture, one may observe that several replicas of the same instruction are dispatched to the functional units, blocking resources that might be used by other instructions. Those replicas are produced after the join point of the paths and are required to guarantee the correct semantic among data dependent instructions. Moreover, DCE continues producing replicas until the branch that generated the paths is resolved. Thus, a whole section of code may be replicated, harming performance. A natural alternative to this problem is the attempt to reuse those replicated sections, namely the replicated traces.

The goal of this work is to analyze and evaluate the effectiveness of value reuse in DCE architecture. As it will be presented, the principle of reuse, in different granularities, can reduce effectively the replica problem and lead to performance improvements.

**Keywords:** Superscalar Architecture, Instruction Reuse, Trace Reuse, Multipath Execution, Dynamic Conditional Execution.

#### Reusando Valores em uma Arquitetura com Execução Condicional Dinâmica

#### **RESUMO**

A Execução Condicional Dinâmica (DCE) é uma alternativa para redução dos custos relacionados a desvios previstos incorretamente. A idéia básica é buscar todos os fluxos produzidos por um desvio que obedecem algumas restrições relativas à complexidade e tamanho. Como conseqüência, um número menor de previsões é executado, e assim, um número mais baixo de desvios é incorretamente previsto.

Contudo, tal como outras soluções multi-fluxo, o DCE requer uma estrutura de controle mais complexa. Na arquitetura DCE, é observado que várias réplicas da mesma instrução são despachadas para as unidades funcionais, bloqueando recursos que poderiam ser utilizados por outras instruções. Essas réplicas são geradas após o ponto de convergência dos diversos fluxos em execução e são necessárias para garantir a semântica correta entre instruções dependentes de dados. Além disso, o DCE continua produzindo réplicas até que o desvio que gerou os fluxos seja resolvido. Assim, uma seção completa do código pode ser replicado, reduzindo o desempenho. Uma alternativa natural para esse problema é reusar essas seções (ou traços) que são replicadas.

O objetivo desse trabalho é analisar e avaliar a efetividade do reuso de valores na arquitetura DCE. Como será apresentado, o princípio do reuso, em diferentes granularidades, pode reduzir efetivamente o problema das réplicas e levar a aumentos de desempenho.

Palavras-chave: Arquitetura Superescalar, Reuso de Instrução, Reuso de Traços, Execução de Multi-fluxos, Execução Condicional Dinâmica.

#### 1 INTRODUCTION

On the latest years, the increasing demand for performance makes computational system design more complex and sophisticated. Robust and heavy softwares require fast processors with the capability to execute hundreds of millions of operations per second. For general purpose applications, where it is difficult to specialize hardware architecture and components, the challenge is even larger and it is not an ordinary task.

In order to supply the market with these high performance requirements, hardware designers have been working over dozens of innovations every year. During the last generations, however, superscalar microprocessors are dominating the general purpose microprocessors architectures. The execution stage of those machines has the potential to execute several instructions per cycle due to the many functional units available.

The number of functional units in the execution stage may vary according to the microprocessor design, while 8 or more functional units are commonly found in commercial processors (KESSLER, 1999; HOREL; LAUTHERBACH, 1999; INTEL, 2001). Even with this potential, the effective number of instructions executed per cycle (IPC) is low. Typically, state-of-the-art microprocessors do not achieve, in average, an effective IPC equal or larger than 2 (HENNESSY; PATTERSON, 2003).

There are three major problems related to this performance bottleneck in super-scalar architectures (JOHNSON, 1991). Data dependencies, resource conflicts and control dependencies are the greatest limiters found and the effort to effectively deal with them is the most difficult challenge faced by microprocessor designers.

Data dependencies limit the parallelism extracted from the executed code because, if one or more instructions depend on previous instructions result, it is not possible to execute them in parallel. This may cause stalls in the pipeline until those instructions are executed. However, data dependencies are efficiently treated dynamically by the hardware through mechanisms such as register renaming (TOMASULO, 1967) and scoreboard (THORNTON, 1964).

Resource conflicts can be observed when two or more instructions try to use the same resource at the same time. Thus, one or more instructions may be pending until the resource is freed. In general, designers may replicate the hardware resources that most often are demanded and this normally presents an efficient result. The balance of the architecture has to be carefully reviewed and cost vs. benefit ratio and trade-offs analyzed, as more area and power are spent to have more parallel functional units. However, this is not the main bottleneck in contemporary superscalar architectures.

On the other hand, control dependencies produce a large penalty due to mispre-

dicted branches and represent one of the most significant barriers to achieve higher IPC.

There are several alternatives to reduce the problem caused by branches, but no definitive solution has been found yet. Branch prediction is the oldest and more widely used technique. Contemporary mechanisms provide very accurate predictions but indeed do not predict all branches correctly and the occurrence of a small number of mispredictions, on the order of 3% to 7% of all predicted branches, can decrease significantly the performance especially in very deep pipelines.

A misprediction is detected only after the complete execution of a branch. Thus, all instructions fetched, decoded, dispatched and executed after the mispredicted branch are squashed. This also includes control independent instructions, because the misprediction recovery mechanism usually flushes all younger instructions and restarts the fetch from the correct target.

Besides branch prediction, other mechanisms have been the target of studies, investigations and developments. Many architectures use sophisticated techniques to extract Instruction Level Parallelism (ILP) and increase performance (POSTIFF et al., 1999). Typically, this parallelism may be extracted and explored using one or more execution paths, depending on the approach adopted by the architecture.

The Dynamic Conditional Execution (DCE) is a wide-issue superscalar processor that exploits the locality of conditional branches to apply dynamic predication and multipath speculative execution. The result is a highly aggressive architecture that can reduce misprediction penalties. The general principle behind DCE is to fetch both paths of some conditional branches based on a semi-static selection mechanism. Both paths of selected branches are executed concurrently and the wrong paths are squashed selectively according to the branch result (SANTOS, 2003).

The major benefit of pursuing such approach is to reduce the number of predicted branches. As a consequence, the number of mispredictions is also reduced without requiring a special instruction set.

The problem of dynamically predicating complex branches is the introduction of a large overhead that hides the potential benefit of applying the technique. The overhead is introduced by fetching instructions from multiple paths, which will be later squashed. Moreover, DCE approach also creates multiple replicas of the same logical instruction in order to guarantee correct data dependency. This issue is detailed later on this PhD Dissertation.

Despite the overhead introduced, previous studies have shown that predicating complex branches produces a two-fold misprediction reduction with relation to predicating simple branches only (SANTOS, 2003). The speed-up obtained by predicating complex branches, however, only pays off for very wide issue machines due to the overhead.

One alternative to this problem can be found in the principle of reusing instructions. Instruction reuse, in different granularities, was a widely explored idea in previous works (GONZALEZ; TUBELLA; MOLINA, 1999; SODANI, 2000; COSTA; FRANÇA; CHAVES FILHO, 2000; WU; CHEN; FANG, 2001; COSTA, 2001; PILLA et al., 2002), but none of them were developed specifically for an architecture with dynamic predication. Most of those studies performed in conventional superscalar architectures pointed out that a large number of instructions can be reused. In DCE, this number is potentially greater due to the replicas occurrence. Thus, reducing the overhead can make resources available to issue other useful instructions.

The main goal of this work is to analyze the limits and potentials of instruction and trace reuse mechanisms to reduce overhead and ultimately lead to performance improvements in DCE architecture.

Chapter 2 addresses the impact of conditional branches on performance, while Chapter 3 depicts the DCE – Dynamic Conditional Execution architecture as an alternative to this problem. Chapter 4 presents the DCE main limitations, as a motivation for this work. Chapter 5 addresses previous works in instructions and trace reuse, while Chapter 6 presents the mechanisms to reuse values in DCE. Chapter 7 presents the simulation environment, and Chapter 8 shows the results achieved. Finally, Chapter 9 shows the conclusions, remarks and future work of this research.

## 2 CONDITIONAL BRANCHES AS PERFORMANCE LIMITER

The main function of the fetch stage is to feed the pipeline with new instructions. Apparently, this is a trivial task, but some restrictions apply to this stage, producing stalls and reducing the global performance of the architecture.

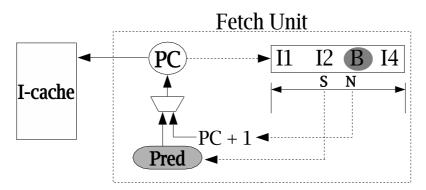

Figure 2.1 presents a scheme of the instruction fetch stage. The stage, after fetching an I-cache line, identifies whether there are branches among those instructions or not. Typically, this task is performed by analyzing the instruction opcode or by checking the branch prediction tables. If a branch is detected, the fetch stage forward that instruction to the predictor, which returns the direction to be followed by the instructions flow as well as the next probable address. When the prediction outcome is that the branch is taken, the fetch stage flushes all instructions after the branch and redirects the fetch to the correct PC. In case of not-taken prediction, the fetch stage keeps on accessing instructions sequentially.

Figure 2.1: Fetch stage

Basically, the fetch stage stalls due to four reasons: I-cache misses, branch instructions occurrence, mispredictions and instruction buffer full. Each one of these implies an additional latency or a penalty to the pipeline.

Cache miss is an old and a difficult problem to be solved. The memory hierarchy is the most common alternative to reduce this bottleneck, especially because the gap between memory and processor frequencies is widening. Cache memories have achieved some success and are essential in current high performance architecture designs. But even with 128 Kbytes or more in first level on-chip caches, misses are still a concern. Each miss has a latency that varies, typically, from 2 to 80 cycles, depending on which hierarchical level the hit occurs. Hits on L2 caches cause the order of 10–15 cycles penalty, if the L2 cache is off chip. If there is a miss in the L2

cache, a latency of 80 cycles or more may be associated to the main memory access. During all those cycles, the fetch stage is stalled and none of the pipeline stages get new instructions.

In order to reduce misses and to minimize the number of cycles wasted by the fetch stage, the lower levels of the memory hierarchy are getting larger. L1 caches of up to 128 Kbytes are already available in commercial microprocessors (KESSLER, 1999), against the usual 8 Kbytes to 16 Kbytes used in just a few years back. The increase in the L1 cache size, however, is not a good solution for the next generation of high performance processors. The cost of the large capacity increases not just the die area, but mainly the L1 access delay and the additional logic for SRAM implementation as well as an efficient addressing scheme to this large on chip memory. Keeping L1 cache access delay within 1 to 2 pipeline cycles severally limits the L1 size.

After using L1 caches with large size in previous generations, most microprocessors families are integrating one more hierarchy level on chip. The idea is to keep L1 capacity small and to improve performance through the reduction of L2 access time by means of L2 integration. Pentium 4, for example, has D-cache and I-cache with 16 Kbytes each, with L2 on chip (INTEL, 2001). The intention is to make the L2 deliver data and instructions at the same frequency of the processor, reducing the 12 cycles typical latency to a few CPU cycles only.

Even with all this effort, new mechanisms are still necessary to decrease cache miss rates and to hide the access latencies. Data and instruction prefetches appear as a low cost and good results alternative (SANTOS, 2000).

The branch occurrence may also stall the fetch stage. As mentioned before, the fetch stage detects branches as soon as the line is fetched from the I-cache. When a branch is encountered and predicted as taken, the fetch stage stalls in order to redirect the fetch. Even if the prediction is correct, the fetch width is harmed.

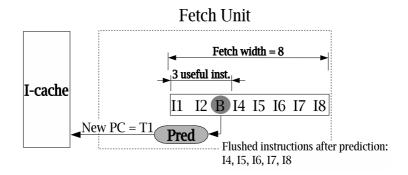

Figure 2.2 presents an example of how the instruction width is harmed due to branch occurrence.

Figure 2.2: Fetch width with branch occurrence

It is possible to observe that the fetch width, in the example showed in Figure 2.2, is reduced to only three instructions, in case of a taken branch is fetched. The remaining pipeline stages are equally affected and will perform for one cycle with only three instructions. Thus, even with a correct prediction, the performance of the architecture is limited by a single occurrence of a branch instruction.

It is also observed that the situation may be worse if the target is located at the beginning of a cache line. This problem is known as cache alignment.

The cache port allows only one line to be accessed each time. Normally, an entire line is fetched and part of it is flushed in a branch occurrence. Thus, it is not possible to fetch the target followed by its subsequent instructions and, at the same time, fetch the instructions in the next line necessary to complete the fetch width. The fetch width is harmed once again and only the instructions located in the same cache block are used. In the worst case, the fetch width is reduced to only one instruction. This can occur if the target is at the last position in the line. The so called target-word-first mechanism treats this problem in cache accesses (HENNESSY; PATTERSON, 2003), hence optimizing the access time, but not avoiding the harm to the effective fetch width.

The branch predictors are generally based in tables that store the pattern followed by each branch in previous executions. Those tables have a limited size that do not support all branches found in a program. The prediction tables and caches are similarly structured, presenting a given associativity and mapping more than one entry to the same position.

After introducing a branch predictor with several levels, the architecture is sensible to 2 different kinds of mispredictions. The first one occurs when the predictor returns a target of another branch, mapped onto the same position of the table. The second type of misprediction is worse and the penalty is even larger. This penalty applies when the branch prediction mechanism finds the right branch, but the result of the prediction is wrong. Nevertheless, even with these additional penalties when using more than one prediction table, mechanisms like this achieve good performance and they are the most widely used in current microprocessors.

In the occurrence of a miss in the addresses table, only the direction is returned by the prediction. This is yet another problem found in branch predictors. In this case, the fetch cannot be redirected properly and the subsequent instructions keep on being fetched. The penalties are also different, depending on the branch. If a branch with direct addressing causes the miss, it is possible to find the correct target after the decode stage, in the dispatch. And if the target found in the instruction is different from the sequential one, the fetch is redirected in the next cycle. On the other hand, if the branch is register dependent, its result can be just found only after execution. In this case, the penalty is larger and affects the whole pipeline. The effect is worse when the pipeline is deep (INTEL, 2001).

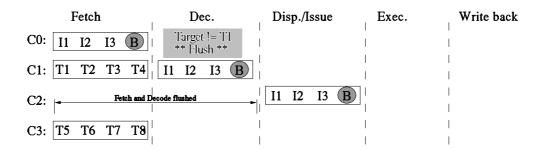

Figure 2.3 presents the penalty for the hit of a different target mapped to the same position of the fetched branch. In Figures 2.3 and 2.4 the fetch width is assumed to be equal to 4 instructions.

In this example, when a given branch is found among the fetched instructions the predictor indicates a target to be fetched in the next cycle. This target address is located in the branch table, at the same position that the right address would be, if no conflicts had happened. The branch predictor returns this address to the fetch stage. Then, the fetch stage stalls and redirects to that address. The instruction incorrectly found as target, as well as its subsequent instructions, are fetched from the cache and delivered to the decode stage. The decode stage performs normally, decoding those instructions as usual. Meanwhile, the branch hit the dispatch stage and it is possible to identify whether the predicted target is the same one found in the instruction opcode. This, however, applies only for direct branches and does not happen with register dependent branches, as mentioned before. If the two addresses are different, the dispatch sends a signal to the fetch stage. The pipeline is then

flushed, but only up to the dispatch stage. Instructions in the dispatch stage fetched ahead of the branch do not need to be squashed. In this stage, the instructions are still in order and it is possible to squash just the instructions from the misfetched path. The instructions in the dispatch, issue, execution and write back continue processing normally.

Figure 2.3: Misfetch occurrence

On the other hand, a much larger penalty applies when the direction predicted is wrong. Figure 2.4 presents the number of lost cycles due to only one misprediction in a short, five stage pipeline.

It is possible to see that, after a misprediction, the fetch is incorrectly redirected and a sequence of useless instructions is brought into the pipeline. The branch is solved only three cycles after its prediction, at the end of the execution stage. While this result is not known, the pipeline performs unnecessary operations. And even knowing the result, the fetch will be redirected again only in the write back, when the mispredicted branch reaches the top of the Re-order Buffer (RoB). As discussed before, this is necessary in order to assure that instructions fetched before the branch will not be flushed. The pipeline is then squashed and re-started in the next cycle. Additional cycles are needed to re-load all the stages again.

Figure 2.4: Misprediction occurrence

Simulations were performed in order to illustrate the issues discussed. The results are shown in the next Sections.

#### 2.1 Simulation Environment

In order to quantify the hazards described in the previous Section, simulations were ran using the SimpleScalar Tool Set (BURGER; AUSTIN, 1997). The superscalar architecture simulator, called *sim-outorder*, is very detailed and implements state-of-the-art microprocessor features, such as out-of-order execution and 3-level memory hierarchy. Also, the simulator is highly configurable, allowing the user to decide many elements like architecture width, memories capacity, number of Functional Units (UFs) and others.

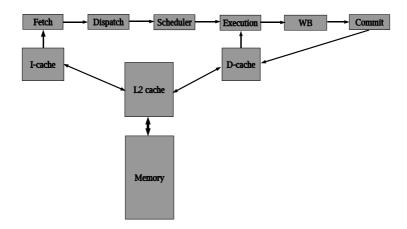

Figure 2.5 presents the *sim-outorder* pipeline. The instructions decode is performed in the second stage with the dispatch. The scheduler is responsible for the instructions issue. The stages basically work according to a conventional superscalar architecture.

Figure 2.5: Sim-outorder pipeline

Table 2.1 presents the basic configurations used in the set of experiments. The fetch, decode, dispatch and issue widths are equal to 8 instructions. The Reorder Buffer (RoB) has 128 entries, which means that a maximum of 128 instructions may be waiting to be committed. The load and store instructions are handled differently in a 64-instruction queue. Ten FUs are available (4 integer ALUs, 2 integer mult/div, 3 FP ALUs, 1 FP mult/div). Cache level 1 is splitted into I-cache and D-cache, both with 64 Kbytes, 2-way set associative. L2 cache is unified with 512 Kbytes and 4-way set associative. Hits in L1 caches, L2 cache and main memory are resolved in 1, 12 and 80 cycles, respectively. The misprediction penalty is, at least, 7 clock cycles.

A perfect branch prediction was used in a base architecture. However, a hybrid predictor was used to analyze the impact of branch occurrence and mispredictions.

The hybrid predictor (MCFARLING, 1993) combines two other predictors, the 2-level adaptative (YEH; PATT, 1991) and the bimodal (SMITH, 1981). Moreover, there is an additional table responsible to choose which kind of the predictions will take place in a given moment. In the simulations performed in this part of the work, this table was configured as a 2048-entries table. The 2-level adaptative is the global predictor, with a history register (first level) that indexes a 4096-entries table (second level). On the other hand, the bimodal mechanism has a 2048-entries table.

A subset of SPEC2000 programs was used as benchmarks for these simulations (HENNING, 2000). They are: bzip2, ggc, equake, mesa, parser, and vpr. Table 2.2

Table 2.1: Configurations used in experiments

| Parameter                                 | Configuration       |

|-------------------------------------------|---------------------|

| Fetch width                               | 8 instructions      |

| Decode width                              | 8 instructions      |

| Dispatch width                            | 8 instructions      |

| Issue width                               | 8 instructions      |

| RoB entries                               | 128 instructions    |

| Load/Store queue                          | 64 instructions     |

| Integer FUs                               | 4 FUs               |

| ${\rm Integer~Mult/Div}$                  | $2 \mathrm{\; FUs}$ |

| FP FUs                                    | 3 FUs               |

| $\mathrm{FP}\ \mathrm{Mult}/\mathrm{Div}$ | 1 FUs               |

| Memory bus width                          | 128 bytes           |

| L1 I-Cache                                | 64 Kbytes           |

| L1 D-Cache                                | 64 kbytes           |

| L2 unified cache                          | 512 Kbytes          |

| Misprediction penalty                     | 7 cycles            |

| L1 latency access                         | 1 cycle             |

| L2 latency access                         | 12 cycles           |

| Main memory latency                       | 80 cycles           |

shows the benchmarks followed by the inputs and arguments used in the simulations.

Table 2.2: Benchmarks and inputs used in the experiments

| Benchmark                                   | Inputs                                                         |

|---------------------------------------------|----------------------------------------------------------------|

| bzip2 (Int)                                 | input.source 58                                                |

| $\gcd (\mathrm{Int})$                       | -quiet -funroll-loops -fforce-mem -fcse-follow-jumps           |

|                                             | -fcse-skip-blocks -fexpensive-optimizations                    |

|                                             | -fstrength-reduce -fpeephole -fschedule-insns                  |

|                                             | -finline-functions -fschedule-insns2 -O cp-decl.i -o cp-decl.s |

| equake (FP)                                 | $ < { m ref.in} $                                              |

| mesa (FP)                                   | -frames 1000 -meshfile mesa.in -ppmfile mesa.ppm               |

| parser (Int)                                | $2.1.\mathrm{dict}$ -batch $<$ ref.in                          |

| ${ m vpr}({ m Int})$                        | ref.net ref.arch.in place.out dum.out                          |

| -nodisp -place_only -init_t 5 -exit_t 0.005 |                                                                |

|                                             | -alpha_t 0.9 412 -inner_num 2                                  |

For each configuration, 400 million instructions were simulated. The results, however, were processed after the execution of the first 100 million of instructions.

#### 2.2 The Effect of the Control Dependencies

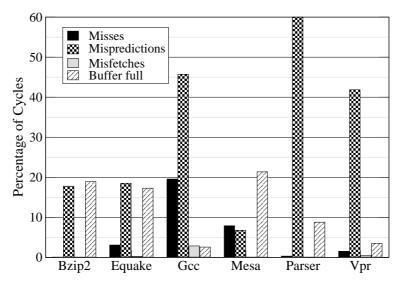

The fetch stage of the pipeline may stop due to four reasons: I-cache misses, instruction buffer full, mispredictions and misfetches.

Figure 2.6 presents the number of cycles lost due to each one of those reasons. The first bar means the number of cycles wasted by I-cache miss occurrence. The

second bar depicts the number of cycles wasted with mispredicted branches. The third bar shows the number of cycles lost due to misfetches, while the last bar means the cycles lost with instruction buffer full. These results were achieved using the hybrid predictor.

#### Reasons for Fetch Stalls

Figure 2.6: Fetch stage stalls

It is possible to see that, for this configuration, which is closer to a typical modern superscalar architecture, the main problem is relative to mispredicted branches occurrence. Also, I-cache misses are a concern, but mainly in large applications such as *qcc*.

Buffer full is the main reason for stalls in benchmarks mesa and bzip2. In fact, for benchmark mesa, mispredictions are only the third main reason for pipeline stalling. This is due to the high accuracy rate achieved by the predictor, which reduced the number of wasted cycles.

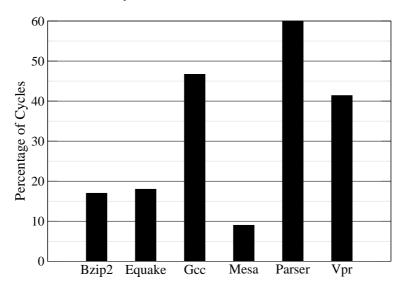

Figure 2.7 shows the number of cycles lost in case of mispredictions. The dark bar shows the percentage of cycles wasted with mispredictions. The most extreme case is the benchmark *parser*, with almost 60% of the cycles spent recovering from mispredicted branches. This means that, in this case, the architecture spent 60% of its time fetching, decoding, dispatching, issuing and executing instructions from the wrong path.

Other benchmarks, such as gcc and vpr, also achieved very negative results. And even with a high accuracy rate in the prediction, benchmarks bzip2 and equake spent, respectively, 17% and 18% of the time recovering from mispredictions.

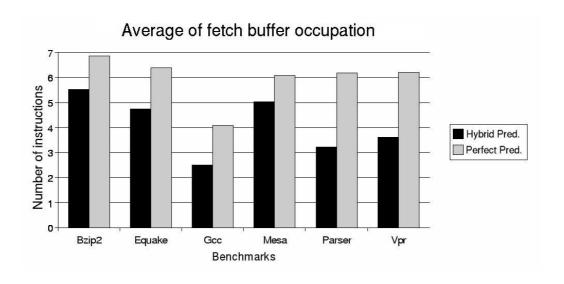

Misprediction is not the only problem caused by branches. Branch occurrence, even if correctly predicted, may harm the architecture performance. In fact, instruction alignment in the I-cache is also a significant problem and these effects can be visualized in Figure 2.8. The dark bar shows the number of instructions in the fetch buffer using the hybrid predictor, while the gray bar depicts the same number, but using perfect prediction. The hybrid predictor combines two different prediction schemes, alternating their usage according to the branch pattern (local prediction) or to the recent branch history (global prediction). This hybrid scheme is used in several state-of-the-art microprocessor and guarantees accurrate prediction rates of

#### Cycles Wasted Due to Branches

Figure 2.7: Percentage of cycles wasted due to branch occurrence

up to 98%. In the simulations performed in this work the hit rates in the prediction tables ranged between 82% and 93% for the hybrid scheme.

In average, the number of instructions delivered to the dispatch stage is lower than 5, even for perfect prediction. Ideally, both architectures have the potential to deliver 8 instructions per cycle. This means that, in average, a little over half of the fetch resources are used during execution. This number is extremely low, if compared with the number of instructions that could be fetched. As a consequence, the number of instructions executed per cycle (IPC) is going to be smaller, reducing the overall performance.

Figure 2.8: Instructions fetched per cycle

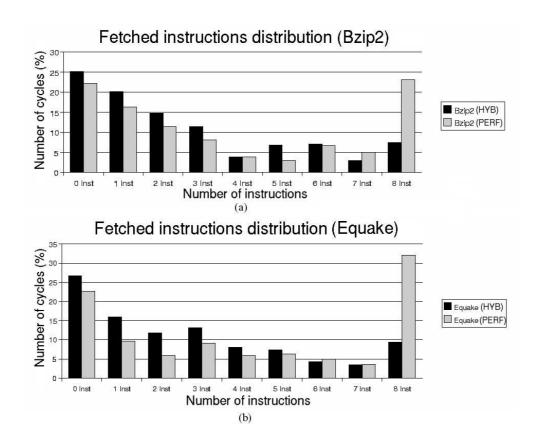

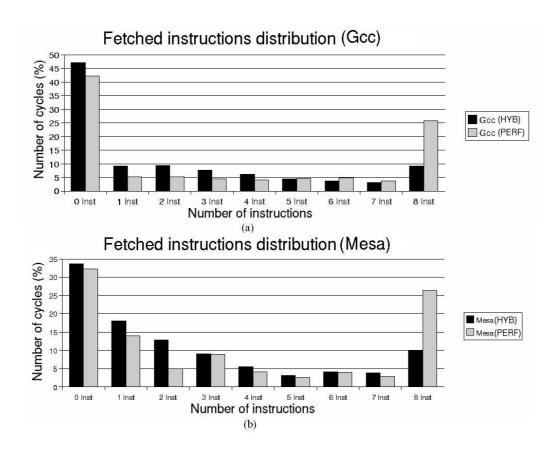

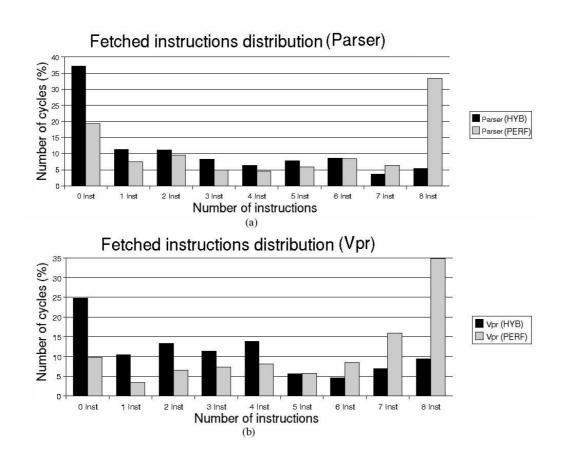

Figures 2.9, 2.10 and 2.11 depict this problem, presenting the distribution of instructions fetched during simulations in each benchmark. All horizontal axis show the number of instructions fetched, while vertical axis present the percentage of the

distribution. The dark bars show results with hybrid prediction, while the gray bars are the results with perfect prediction. In an ideal architecture, all benchmarks should be spending 100% of the time dispatching 8 instructions, the maximum number supported by the architecture.

Figure 2.9: Distribution of instructions in benchmarks (a) bzip2 and (b) equake

Unfortunately, the distribution of instructions fetched is very different from the ideal. It is possible to observe that, in all cases, there are a significant percentage of cycles in which no instructions were fetched. This situation is worse when using hybrid prediction because, in this case, the fetch stage also stalls due to mispredictions. The difference between using perfect and hybrid prediction is significant and, in some cases, such as benchmark vpr, achieves 60%. However, I-cache misses may also increase the percentage of cycles in which no instructions were fetched. This explains the high rates reached by the cases of zero or few instructions fetched per cycle.

Even using perfect prediction, the number of cycles spent fetching 8 instructions is small. The best case occurs in benchmark vpr, which could ideally fetch 8 instructions in 35% of the cycles. In benchmark bzip2, however, 8 instructions were fetched in just 23% of the cases. These rates are low because perfect prediction solves only mispredictions. Instruction alignment and I-cache misses are additional problems preventing a larger fetch bandwidth in the superscalar architecture.

During most of the time, a lower number of instructions is fetched when hybrid prediction is used. The best case was achieved by benchmark mesa, which fetched 8 instructions during 10% of the time. In general, however, for more than 40% of the cycles the architecture is fetching 1 to 4 instructions per cycle.

Figure 2.10: Distribution of instructions in benchmarks (a) gcc and (b) mesa

Table 2.3 shows the effective fetch bandwidth for each benchmark. The first column presents the benchmarks simulated. The remaining columns mean the average number of instructions fetched per cycle by the architecture with the hybrid predictor followed by the one using a perfect predictor. In all cases, the number of instructions fetched by the architecture with the perfect predictor is significantly higher. In benchmark vpr, where the larger difference was observed, the architecture with hybrid predictor fetched only 54% of the instructions usually fetched by the one with a perfect predictor.

Table 2.3: Effective fetch bandwidth

| Benchmark            | Hybrid Predictor | Perfect Predictor |

|----------------------|------------------|-------------------|

| Bzip2                | 2.60             | 3.66              |

| Equake               | 2.70             | 4.16              |

| $\operatorname{Gcc}$ | 2.18             | 3.34              |

| Mesa                 | 2.35             | 3.30              |

| Parser               | 2.44             | 4.53              |

| $\operatorname{Vpr}$ | 3.02             | 5.42              |

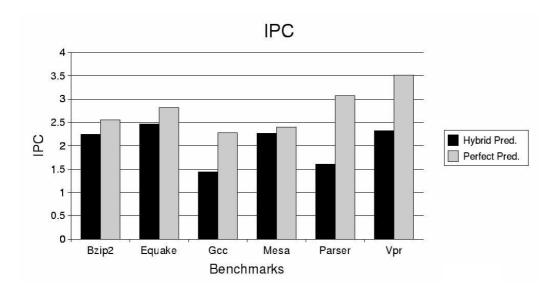

Finally, the IPC (Instructions Per Cycle) is shown in Figure 2.12. The dark bar means the performance reached by the architecture with hybrid prediction, while the gray bar shows IPC achieved by the architecture with perfect prediction. In spite of problems with alignment and misses, the architecture with perfect prediction is

Figure 2.11: Distribution of instructions in benchmarks (a) parser and (b) vpr

better in all cases. In benchmark parser the difference between both cases is close to 100%.

Figure 2.12: Instructions Per Cycle achieved with hybrid and perfect predictions

#### 2.3 Summary

The goal of this Chapter was to show how branches limit performance of modern superscalar architectures.

The simulations presented in this Chapter clearly show how the simple occurrence of branch instructions can harm superscalar architectures performance and prevent the exploitation of the Instruction Level Parallelism (ILP). The misprediction penalties are getting higher with even deeper pipelines and the occurrence of a single misprediction may cause the loss of more than 15 cycles, depending on the architecture.

Mispredictions are the main cause of fetch stalls. In some applications, such as benchmarks *parser* and *vpr*, mispredictions are responsible for almost the totality of fetch stalls. For these benchmarks and also for *gcc*, more than 40% of the cycles were lost due to branch occurrence. This, of course, causes a large loss in performance and, in some cases, there is a two-fold gain in IPC when using a perfect predictor.

In summary, branch occurrence is a real and difficult problem to be solved. Although many efforts have been made over the last 10 years, no definitive solution was found. In the following Chapters of this work a new approach to reduce this problem will be discussed. DCE, or Dynamic Conditional Execution, intends to reduce mispredictions by fetching and executing multiple paths of conditional branches.

#### 3 DCE – DYNAMIC CONDITIONAL EXECUTION

Several studies are focused in the development of new and aggressive multipath mechanisms (KELLER, 1975; NEMIROVISKY, 1990; UHT; SINDAGI, 1995; SKADRON, 1999; SANTOS; NAVAUX, 1998), which intend to improve the performance by increasing the number of executed instructions (AHUJA et al., 1998). All of them, however, need an efficient fetch stage to feed the wide execution engine.

The Dynamic Conditional Execution model is based on the concept that multiple paths may be extracted from few cache lines, in a small number of accesses, and then sent to the execution engine. In other words, multipath execution is performed conditionally and instructions are committed according to the dynamic behavior of the branches.

DCE combines dynamic predication and multipath to reduce the complexity and disruptions of the fetch. This is achieved by fetching sequentially through branches that qualify for predication.

The first step of the dynamic conditional execution is to determine whether the branch has to be predicted or predicated. Basically, a branch has to be predicated if both targets are inside a given distance and if there is no other complex instruction, such as procedure call, inside that structure (branch-then-else-join). All other cases, i.e., long structures, structures with calls, etc., are supposed to be normally predicted. The analysis of the code structures is done statically, by the compiler. Then, when the code begins the execution, the architecture will predicate all branches marked at compile time, since it is expected that resources are available to do so. During the predication state of the architecture all instructions are fetched sequentially up to the join point of the paths. After the join point, the architecture returns to behave like a conventional superscalar architecture, until the next branch marked to be predicated is reached.

In order to determine if a branch qualifies for predication, an extension of the selection mechanism proposed in (KLAUSER et al., 1998) was developed. In that selection mechanism, only simple branches qualify for predication. The model used in this work also qualifies complex branches, i.e., nested branches and other structures different from a simple non-nested *if-then-else*. The classes of complex branches allowed for predication are presented later in this Chapter.

The selection mechanism used in DCE is static and runs at compilation time, marking branches that can be predicated according to the target locality. The compiler does not change the original code, it only marks instructions valid for predication (SANTOS, 2003). At execution time, the fetch engine decides whether a selected branch will be predicated or not, based on the availability of resources.

Therefore, DCE is a combination of a static selection mechanism and hardware

support to execute branches eagerly. In DCE, selected branches are treated as regular instructions by the fetch engine and they never disrupt the fetch. As no prediction of control transfer is made at fetch time, they may not cause mispredictions.

The main difference between Klauser et al. (KLAUSER et al., 1998) and DCE (SANTOS, 2003) is that DCE dynamically predicates both simple and complex branches and it does not use conditional moves to satisfy data dependences at the join point of predicated branches.

In Klauser et al., conditional moves are inserted dynamically at the joint point to block the issue of instructions from the same data chain of the predicated paths. When the branch resolves, the conditional moves can be issued to copy the data from the correct physical register to the correct source register of the dependent instruction. Thus, the original instruction that uses the respective register becomes ready for issue only after the conditional move instruction executes.

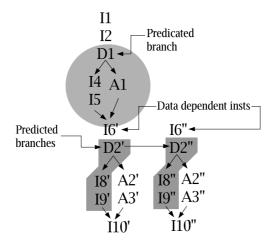

In DCE, a register renaming technique derived from Chaves et al. (CHAVES FILHO et al., 1999) generates replicas of instructions at the join point of predicated branches. Replicas are instructions that use data that is produced in one of the paths of a predicated branch. Therefore, there is one replica for each predicated path. As DCE does not use conditional moves, it does not block the issue of the dependent instructions. In DCE, the replicated instructions can be issued as soon as the appropriate physical registers are ready (i.e. the source data is available).

Resources saturation in DCE is reduced by predicating just part of the branches. The number of predicated branches is acceptable, but if all paths are fetched into the pipeline, several instructions may be replicated. This happens because both paths converge to a single join point and many instances of the same instruction may be created to assure correctness. However, only one of these instances is committed and all others are canceled as soon as the outcome of the branch is known. Those copies are pollution and they must be avoided.

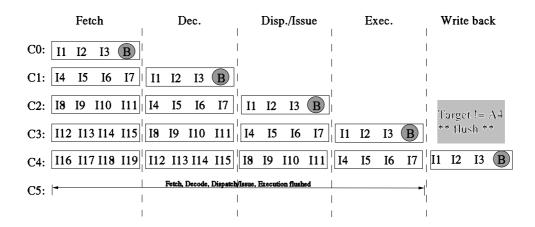

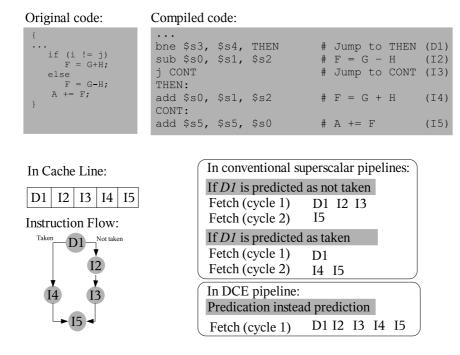

Figure 3.1 shows the example of how DCE fetch stage works. In the upper left portion of the Figure, there is a very simple example in C, while the upper right portion presents the code usually generated by the compiler for that example. The lower part of the Figure shows how this structure is fetched in a conventional architecture and in DCE. It is possible to see that, for a conventional architecture, the fetch will be always executed in two cycles, with two accesses to the same cache line. In DCE, only one access is done and all instructions are fetched at once.

After the fetch stage, the instructions are renamed according to their position in the tree dynamic path of execution. This control is extremely useful to determine which instruction comes from which path, and so which instructions have to be committed later on. The dispatch, issue and execution stages work as conventional superscalar stages, except for load and store instructions that may be predicated. The write back and commit stages are designed to identify and complete only instructions from the correct paths.

#### 3.1 Hammock Classification

As discussed before, DCE reduces the pipeline saturation by predicating only a set of branches executed by a given program. In order to identify the best set for prediction, several applications were profiled according to the branches behavior. This study, described in (SANTOS et al., 2003), pointed a significant occurrence of

Figure 3.1: Fetch cycle example in DCE

four different classes of nested structures (hammocks), besides the *Simple* class of branches predicated in the work proposed by Klauser et al. The variations of those complex hammocks are the extended model proposed in DCE, presented bellow.

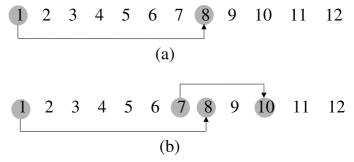

A conditional forward branch that has no nested branches may have one (if-then) or two sides (if-then-else). These branches are shown in Figure 3.2 and are called simple hammocks single sided (a) or double sided (b), respectively. This was the same subset of branches approached by (KLAUSER et al., 1998).

Conditional forward branches that have other conditional forward branches inside may be classified as follows and are illustrated in Figure 3.3:

- 1. one or more nested conditional forward branches totally contained are called pure complex hammocks (a)

- 2. one or more conditional forward hammocks whose target address coincide with the join address of the outer hammock are called *multiple join complex hammocks* (b)

- 3. one or more conditional forward branches whose target address is beyond the join address of the outer hammock are called multiple target complex hammocks (c)

- 4. one or more conditional forward branches whose target address targets the body of the taken path are called *overlap complex hammocks* (d)

Figures 3.2 and 3.3 present the six different hammock classifications. The diagrams presented are such that each number corresponds to an instruction and each arrow represents a branch to a given target, i.e. another instruction. The source of the arrow is the instruction which originated the branch (conditional or unconditional). The end of the arrow indicates the taken target instruction.

Figure 3.2: Example of simple hammocks

Figure 3.2 (a) presents the most basic hammock structure. It is a typical *if-then*, where a condition is investigated in instruction 1 and, depending on the result, the instruction flow continues sequentially or is redirected to instruction 8. Note that instruction 8 is part of any flow path started in 1, taken or not, so it is called join point. Because in this structure there are no nested branches and there is only one side (if-then), this category is called One-sided Simple.

Figure 3.3: Example of complex hammocks

Figure 3.2 (b) shows a two-sided hammock. The example corresponds to an *if-then-else*, which has a condition evaluation in instruction 1 and an unconditional branch in a later instruction, represented by instruction 7. This unconditional branch is responsible for the flow redirection demanded by the *else* command. It is possible to see that the unconditional branch is the instruction right before the target of 1, i.e. instruction 8. In this example, the join point is given at instruction 10 and the category is called *Two-sided Simple*. For instance, for a branch to fall into this category it must have the unconditional jump right before the target of the first conditional branch (branch delay slots were not considered). If this condition is not true then the branch falls off this valid category.

If a hammock has any nested hammocks it is then called *Complex*. An example of a *Complex* pattern is shown in Figure 3.3 (a). In this case, there are nested hammocks within the outer hammock. The outer hammock is an *if-then-else* similar to

the one presented earlier, where instruction 1 jumps to 8, if the condition evaluated is true. Furthermore, there is an unconditional jump in instruction 7, jumping to the join point, i.e. instruction 10. Inside this hammock, instruction 3 is a simple if-then, like the one in the first example of this Section. For this example of nested hammocks, the target of the second branch is totally contained within the most external hammock, instruction 5. When all nested branches have their targets totally contained within the boundaries of the most external branch, that branch is called Complex Pure.

Figure 3.3 (b), presents an *if-then-else* hammock with multiple join points. This means that one of the sides of the most external branch (then or else) has a nested branch whose target is the same as the first, most external branch. In the example, instruction 8 is the target of two conditional branches (instructions 1 and 3). Then, the most external branch has the same target as the most internal branch and it is called  $Complex\ with\ multiple\ joins$ . The join point of this hammock is instruction 10 as this instruction is the first instruction common to any path starting in 1. Observe though that branch 3 would have a join point at 8 if it was not a nested branch of 1. When classifying complex hammocks, the join point is considered to be the first instruction common to all paths starting from the outer hammock.

In other cases, nested branches may not have targets that are coincident with the target of the external branch. In this cases the target may be inside the else path while the branch is within the *then* path or it may be beyond the join point of the external branch, Figures 3.3 (c) and (d).

When the target of a nested branch, located within the *then* path, is actually in the else path of the most external branch, example (c), the two branches are overlapped and the category in each they are included is called *Complex overlapped*. The join point is still the common instruction to all paths, i.e. instruction 10.

Example (d) shows the nested branch 3 which has a target 12 beyond the join point of the most external branch 1. In this case, the join point is instruction 12 as it is the first instruction common to any path that starts in 1. This type of Complex branch is called Complex with multiple targets.

Other combinations of nested hammocks are also possible. The combinations showed here are the basic combinations recognized by the preprocessing compiler. The compiler initially classifies a given branch into one of the classes below. At last, it looks into the final combination, that is, a combination of one or more of the classes, and evaluates if it is still a valid combination.

A hammock may not qualify for predication due to the occurrence of any of the following: backward branches, indirect branches, unconditional jumps that are *not* related to one or more conditional branches, subroutine calls or returns and system calls.

#### 3.2 DCE Pipeline

Although DCE is considered a multipath architecture, its pipeline does not need much additional support to execute. This Section will describe each one of the stages.

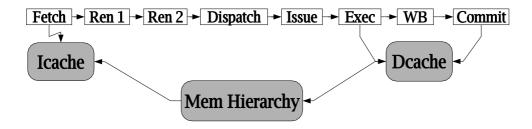

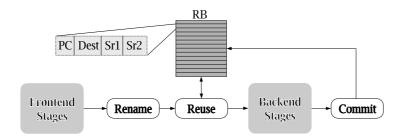

Figure 3.4 shows the basic stages in DCE pipeline. Although only eight stages are presented, several others may be introduced at simulation time in order to emulate deep pipelines. Stages  $Ren\ 1$  and  $Ren\ 2$  are responsible for register renaming. In

DCE this is done in two steps, as renaming is more complex than usual. The other stages, i.e., fetch, dispatch, issue, execute, write back and commit are similar to the ones found in regular superscalar architectures, with slight differences. Each stage is presented in the following Sections.

Figure 3.4: DCE pipeline

#### 3.2.1 Fetch

As in a common superscalar architecture, the fetch stage is responsible for bringing instructions from the I-cache. Additionally, in DCE, the fetch stage decides whether or not a qualified branch will be predicated.

This stage is implemented as a finite state machine with two states: prediction and predication. When the *fetch* stage is under prediction mode, it works exactly as a common fetch, performing the following tasks:

- Bring in a line from the memory system;

- Predict a conditional branch, if any;

- Determine the predicted address and,

- Redirect the fetch if the branch is predicted as taken.

The prediction is done by a regular branch predictor, such as a hybrid mechanism (MCFARLING, 1993). The idea, however, is to predict only part of the branches, while predicating others, as discussed previously. Thus, the processor keeps on fetching and predicting branches as usual, until a qualified branch is fetched into the pipeline.

At this point, the architecture changes its state, going to predication. In this state the fetch will determine the join point, based on the compiler information, and access the I-cache in order to bring all instructions between the branch and this address. This means that both paths of the branch will be brought into the pipeline and delivered to execution. The idea is simply to eliminate the need to predict this branch.

After the join point is fetched, the architecture automatically returns to the prediction state until a new qualified branch is brought to the pipeline.

One cans condute that no significant logic is added. In fact, the branch predictor may be even simplified, because it is performing fewer predictions.

### 3.2.2 Register Rename - First Stage

As mentioned before the scheme to rename registers was derived from a previous work, which is described in (CHAVES FILHO et al., 1999). In that work, another multipath architecture was defined and a very similar register renaming scheme implemented.

Register renaming is the most complex stage in DCE architecture and this was the main motivation to have it divided into two separate stages. This higher complexity is mainly due to the replicas generation. Initially, all replicas are created and tagged according to their position in the instruction flow. Then, after that, they are actually renamed.

Thus, this first stage was designed to tag the instructions according to the path they belong and also to produce all replicas necessary to keep correctness among different data chains. This is extremely necessary in order to allow the architecture to keep track of all paths that are executing in the pipeline. At commit stage, the architecture will retire only instructions from the correct path and they are identified by their tags (or tagids). So, each path has a single and unique tag and all instructions from that path are tagged with that same id.

Moreover, after the join point several replicas may be created, each one corresponding to a different path. After the join point all instructions are control independent, but many are data dependent still. So, all these data dependent instructions are replicated in order to maintain semantics. There is one replica for each path available, i. e., DCE will replicate five times all data dependent instructions after a branch which originated five paths, for example. Replicas will be generated until the original branch is resolved and the architecture knows the correct sequence of replicas to choose.

#### 3.2.3 Register Rename – Second Stage

The second part of the register renaming is where occurs the actual renaming. Each logical register is mapped to a physical register.

The main difference between DCE register renaming and a conventional renaming stage is that there are several mapping tables, one for each active path. This is done in order to make it easier to identify which registers are being used by which path. This is especially useful when retiring and flushing correct/incorrect paths.

As discussed earlier, as the number of mapping tables limits the maximum number of paths, it also limits the maximum number of replicas, because there will be one replica for each active path.

The register renaming itself is very similar to the original algorithm described in (TOMASULO, 1967), where logical registers are mapped (and re-mapped) to physical registers every time a given register is written.

Moreover, these tables do not store large amounts of data and they do not represent a significant implementation issue.

#### 3.2.4 Dispatch

The dispatch stage in DCE works similarly to a common dispatch stage found in any superscalar machine. It takes renamed instructions from the previous stage and moves them (in order) to the ReOrder Buffer (ROB), allocating a new entry to each instruction dispatched. After this, the instructions are ready to be issued to

the execution.

#### 3.2.5 Issue

As many others superscalar architectures instructions are issued out-of-order and the issue stage is responsible for scheduling the instructions. The idea is to issue instructions as soon as possible, depending on the availability of the operands and functional units.

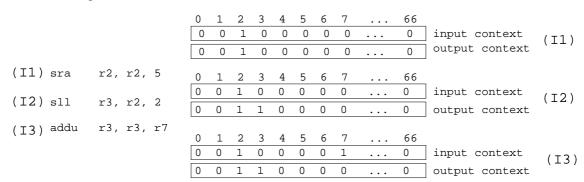

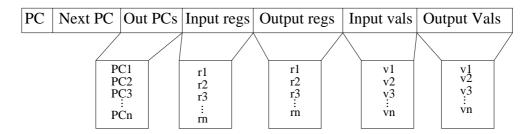

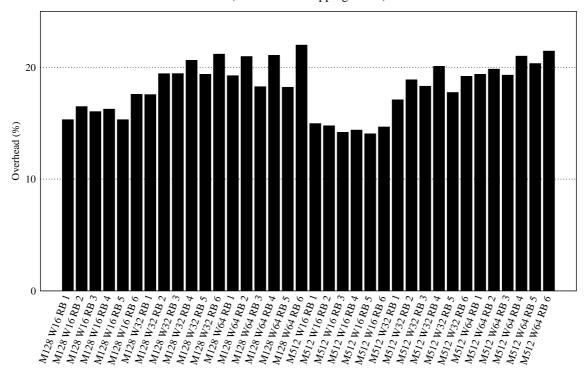

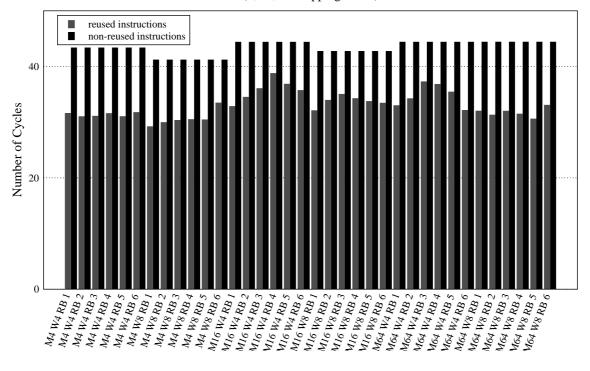

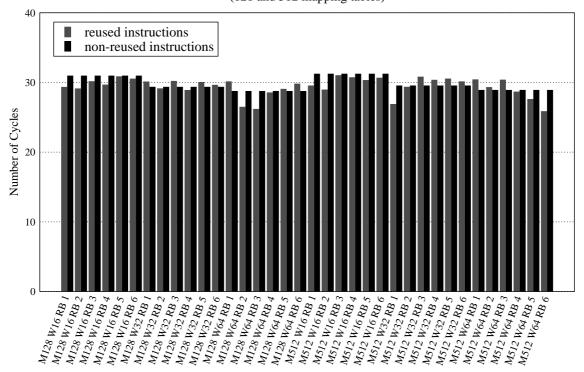

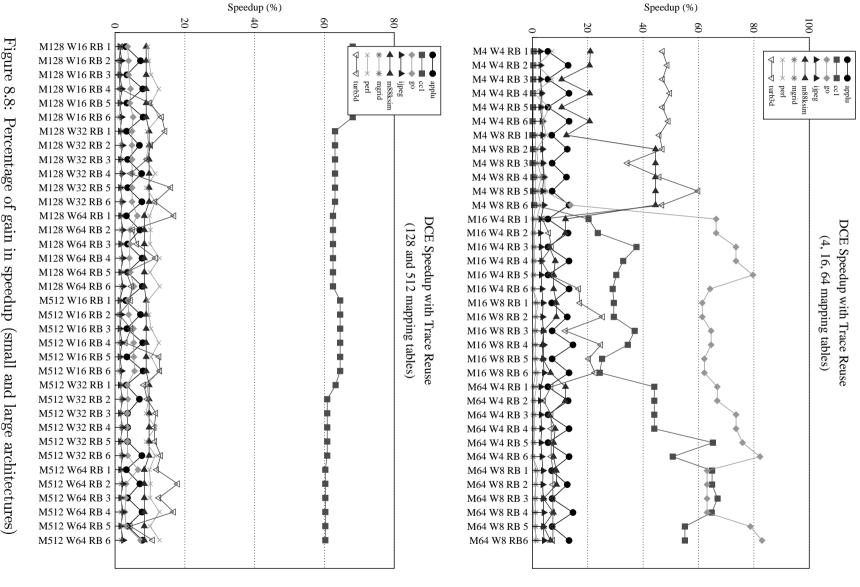

Instructions with ready operands are delivered to execution, if there are functional units available. As all WAR (Write After Read or false dependencies) and WAW (Write After Write or output dependencies) were solved by register renaming, only RAW (Read After Write) dependencies are to be observed by this stage. So, an operand is ready when there are no other pendent instructions writing on it.