# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

## FELIPE MARTIN SAMPAIO

# Energy-Efficient Memory Hierarchy for Motion and Disparity Estimation in Multiview Video Coding

Thesis presented in partial fulfillment of the requirements for the degree of Master of Computer Science

Prof. Dr. Sergio Bampi Advisor

Prof. Dr. Luciano Volcan Agostini Co-Advisor

Porto Alegre, Fevereiro de 2013.

# CIP - CATALOGAÇÃO NA PUBLICAÇÃO

Sampaio, Felipe

Energy-Efficient Memory Hierarchy for Motion and Disparity Estimation in Multiview Video Coding / Felipe Sampaio. – Porto Alegre: PPGC da UFRGS 2012.

120 f.:il.

Orientador: Sergio Bampi; Co-orientador: Luciano Agostini.

Thesis (Master) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação. Porto Alegre, BR - RS, 2013.

1. Codificação de Vídeo Multivistas. 2. Hierarquia de Memória 3. Consumo de Energia. I. Bampi, Sergio. II. Agostini, Luciano. III. Energy-Efficient Memory Hierarchy for Motion and Disparity Estimation in Multiview Video Coding.

#### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos Alexandre Netto

Vice-Reitor: Prof. Rui Vicente Oppermann

Pró-Reitor de Pós-Graduação: Prof. Vladimir Pinheiro do Nascimento

Diretor do Instituto de Informática: Prof. Luís Lamb

Coordenador do PPGC: Prof. Luigi Carro

Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

## **AGRADECIMENTOS**

Agradeço, inicialmente, aos meus pais e à minha irmã pelo apoio incondicional que me deram durante toda a minha jornada nestes dois anos de mestrado, desde a decisão pelo mestrado em outra cidade até a aceitação de nos vermos apenas aos finais de semana, quando possível. Sempre acreditaram na minha capacidade e no meu potencial. Agradeço tudo que sempre fizeram por mim! Amo vocês!

O mestrado, além do título de mestre e do meu ingresso imediato no doutorado, me proporcionou uma das maiores alegrias da minha vida: conhecer uma pessoa muito especial com quem eu estou dividindo minha vida, a minha namorada Meiri. Não existem palavras para agradecer o apoio, os conselhos e tudo que vivemos juntos (e o que vamos viver ainda). Quero te dizer que esta etapa da minha vida foi muito mais feliz porque tu, Meiri, estavas ao meu lado sempre. Te amo!

Minha vida na capital dos gaúchos é muito mais tranquila e divertida graças aos meus grandes amigos e colegas de apartamento Daniel e Diego. Com eles dividi minhas experiências, aprendi o espírito do coleguismo e cresci como pessoa e como ser humano. Obrigado pelo companheirismo! Além deles, o amigo e jornalista Mateus Kerr também merece um agradecimento especial, pelas noitadas de filosofia e de cervejas durante todo esse período. Tu és o cara, bruxo!

Mesmo morando agora em outra cidade, é impossível me esquecer daqueles com quem eu sempre posso contar para tomar aquele mate, jogar aquele futebol, ou simplesmente se 'ajuntar' numa noite de chuva para eu ganhar (com facilidade, sempre) no vídeo game. Agradeço a todos os meus amigos que estão espalhados agora pelo Brasil, mas que nunca se esquecem de te ligar pra te convidar para um churrasco.

Na UFRGS, encontrei um ambiente de trabalho ótimo, engraçado e de muita parceria. Com o tempo, mais que colegas de trabalho, eles tornaram-se amigos que serão para a vida inteira, não tenho dúvidas. Agradeço a todos os colegas que passaram pelo laboratório 215, todos foram importantes de alguma forma. De maneira especial, agradeço aos colegas: Duda, Cláudio, Daniel, Leonardo, Kléber e Cauane, pelas discussões filosóficas, churrascos e por toda a parceria.

Mesmo longe da UFPel, ainda assim continuei trabalhando com os colegas e amigos que deixei por lá. Então, um agradecimento especial a todos, principalmente para o Mateus com quem tive possibilidade de continuar trabalhando e trocando ideias.

Todo o meu trabalho e tudo que produzi nestes dois anos de mestrado só foram possíveis graças ao apoio e orientação dos professores e amigos Sergio Bampi e Luciano Agostini. Muito obrigado pelos ensinamentos e pelo apoio ao meu trabalho.

Cabe aqui um agradecimento especial ao meu orientador informal, com quem tive o prazer de trabalhar desde 2010 e que espero continuar trabalhando por muito tempo ainda. Zatt, tu és um cara fora do comum, e sabes que tens participação fundamental desde meu trabalho final da graduação até os trabalhos mais recentes. Obrigado pela parceria, por todas as conversas e pelos trabalhos intensos nesses últimos anos.

A qualidade das publicações e dos trabalhos foi possível também graças aos pesquisadores do KIT que colaboraram de maneira importante e que deram credibilidade ao meu trabalho. Obrigado ao Shafique e ao Professor Jörg Henkel pelas colaborações e trabalhos em conjunto que tivemos nos últimos anos.

Agradeço também aos órgãos de fomento brasileiros, em especial ao CNPq e à CAPES, que financiaram minhas atividades e minhas participações em conferências, onde pude divulgar minhas contribuições para a comunidade científica.

Por último, e não menos importante, eu agradeço ao Sport Club Internacional pelas alegrias e inúmeras vitórias que eu pude presenciar, agora estando fisicamente no Beira Rio, podendo cantar e te apoiar. Obrigado Campeão de Tudo!

# **SUMMARY**

| LIST (       | OF ABREVIATIONS AND ACRONYMS                               |    |

|--------------|------------------------------------------------------------|----|

| LIST (       | OF FIGURES                                                 | 9  |

|              | OF TABLES                                                  |    |

|              | RACT                                                       |    |

|              | MO                                                         |    |

| NESU         | NIO                                                        | 13 |

| 1            | INTRODUCTION                                               | 14 |

| 1.1          | Contributions of this Master Thesis                        |    |

| 1.2          | Text Organization                                          | 17 |

| 2            | MULTIVIEW VIDEO CODING BACKGROUND                          | 18 |

| _<br>2.1     | Multiview Video Encoding System                            |    |

| 2.1.1        | Multiview Scenarios and Applications                       |    |

| 2.1.2        | **                                                         |    |

| 2.1.3        |                                                            |    |

| 2.2          | Digital Video Characteristics                              |    |

| 2.3          | Basic Concepts on Video Coding                             |    |

| 2.4          | H.264/AVC Encoder for Multiview Videos                     |    |

| 2.5          | Motion and Disparity Estimation                            |    |

| 2.5.1        | Basic Concepts                                             |    |

| 2.5.2        |                                                            |    |

| 2.5.3        |                                                            |    |

| 2.6          | Intra-Frame Prediction                                     | 33 |

| 2.7          | Memory Challenges on Multiview Video Coding                |    |

| _            |                                                            |    |

| 3            | MEMORY AWARE TECHNIQUES FOR VIDEO CODING                   |    |

| 3.1          | Data Reuse Strategies                                      |    |

| 3.2          | Reference Frame Compression Techniques                     |    |

| 3.3          | Energy-Aware Memory Techniques and Architectures for ME/DE |    |

| 3.4          | Reference-Centered Schedule Motivation                     | 41 |

| 4            | PROPOSED MEMORY HIERARCHY SYSTEM                           | 44 |

| 4.1          | Memory Hierarchy System Overview                           |    |

| 4.2          | Reference-Centered Data Reuse                              |    |

| 4.3          | Statistic-Based Partial Results Compression                |    |

| 4.4          | On-chip Memory Organization                                |    |

| 4.4.1        | 1 0                                                        |    |

| 4.4.2        |                                                            |    |

| 4.5          | Intra-Based Reference Frame Compression                    |    |

| 4.5.1        | Lossless Compression                                       |    |

| 4.5.2        | •                                                          |    |

| 4.5.3        | · · · · · · · · · · · · · · · · · · ·                      |    |

| 5            | RESULTS AND DISCUSSIONS                                    | 62 |

|              |                                                            |    |

| 5.1<br>5.2   | Experimental Tests Environment                             |    |

| 5.2<br>5.2.1 | Off-chip Memory Energy Savings                             |    |

| 5.2.1        | · · · · · · · · · · · · · · · · · · ·                      |    |

|              | •                                                          |    |

| 5.3<br>5.4   | On-chip Memory Energy Savings                              |    |

| J <b>.4</b>  | Reference Frame Compressor                                 | 08 |

| 6            | CONCLUSIONS AND FUTURE WORKS                               | 73 |

|                                                            | IDIX A – MULTIVIEW VIDEO TEST SEQUENCES<br>IDIX B – STATISTIC HUFFMAN TABLES, NON-UNIFORM |                |

|------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------|

|                                                            | TIZATION LEVELS AND THRESHOLDS DEFINITION                                                 | 81             |

| <b>B.1</b>                                                 | Off-line Static Search Map for ME/DE                                                      | 81             |

| <b>B.2</b>                                                 | Static Quantization Levels and Huffman-Tables                                             | 82             |

|                                                            |                                                                                           |                |

| APPEN                                                      | IDIY C _ RESUMO EM PORTUGUÊS                                                              | 25             |

|                                                            | IDIX C – RESUMO EM PORTUGUÊS                                                              |                |

| C.1 Resu                                                   | mo                                                                                        | 85             |

|                                                            | mo                                                                                        | 85             |

| C.1 Resu<br>C.2                                            | mo                                                                                        | 85<br>86<br>87 |

| C.1 Resu<br>C.2<br>C.3                                     | mo<br>Introdução e Motivação<br>Hierarquia de Memória Proposta                            | 85<br>86<br>87 |

| C.1 Resu<br>C.2<br>C.3<br>C.3.1                            | mo                                                                                        | 85868788       |

| C.1 Resu<br>C.2<br>C.3<br>C.3.1<br>C.3.2                   | Introdução e Motivação                                                                    |                |

| C.1 Resu<br>C.2<br>C.3<br>C.3.1<br>C.3.2<br>C.3.3          | Introdução e Motivação                                                                    |                |

| C.1 Resu<br>C.2<br>C.3<br>C.3.1<br>C.3.2<br>C.3.3<br>C.3.4 | Introdução e Motivação                                                                    |                |

## LIST OF ABREVIATIONS AND ACRONYMS

3D Three-Dimensional

AGU Address Generation Unit

AVC Advanced Video Coding

BD-BR Bjontegaard Delta – Bitrate

BD-PSNR Bjontegaard Delta – Peak-to-Signal Noise Ratio

CABAC Context-Adaptive Based Arithmetic Coding

DC Disparity Compensation

DDR Double Data Rate

DE Disparity Estimation

DI Disparity Index

FBC Frame Buffer Compression

FPGA Field Programmable Logic Array

FS Full Search

GDV Global Disparity Vector

GOP Group of Pictures

HEVC High Efficiency Video Coding

ISO/IEC International Organization for Standardization/ International

**Electrotechnical Commission**

ITU International Telecommunication Unit

ITU-T ITU Telecommunication Standardization Sector

JPEG Joint Photographic Experts Group

JPEG-LS Joint Photographic Experts Group - Lossless

JM Joint Video Coding Model

JMVC Joint Multiview Video Coding Model

JVT Joint Video Team

LPDDR Low-Power Double Data Rate

MB Macroblock

MBDR Macroblock-centered Data Reuse

MC Motion Compensation

ME Motion Estimation

MMSQ-EC Min-Max Scalar Quantization / Error Compensation

MRF Multiple Reference Frames

MSE Mean Squared Error

MVC Multiview Video Coding

PDF Probability Density Function

PSNR Peak-to-Signal Noise Ratio

QP Quantization Parameter

RCDR Reference-Centered Data Reuse

RD Rate-Distortion

RDO Rate-Distortion Optimization

RFCAVLC Reference Frame Context

RGB Red, Green and Blue

SAD Sum of Absolut Differences

SATD Sum of Absolute Transformed Differences

SI Spatial Index

SRAM Static Random Access Memory

SSD Sum of Squared Differences

SW Search Window

TI Temporal Index

TH Threshold

VBS-ME Variable Block Size Motion Estimation

VLC Variable Length Coding

YCbCr Luminance, Blue Chrominance and Red Chrominance

# LIST OF FIGURES

| Figure 2.1: MVC system architecture.                                                     | 19 |

|------------------------------------------------------------------------------------------|----|

| Figure 2.2: Redundancies in multiview videos.                                            | 23 |

| Figure 2.3: Overall H.264/AVC encoder block diagram for multiview videos                 | 25 |

| Figure 2.4: Illustration of inter-frame and inter-view prediction in MVC                 | 28 |

| Figure 2.5: Motion and Disparity Estimation basic concepts                               | 29 |

| Figure 2.6: Multiple Reference Frame (MRF) example                                       |    |

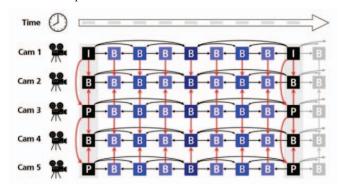

| Figure 2.7: Hierarchical prediction structures for temporal prediction                   |    |

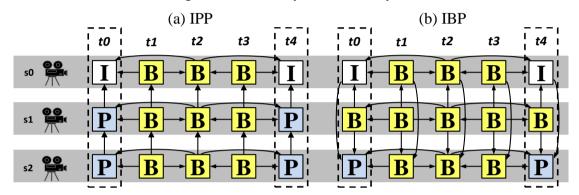

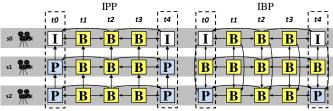

| Figure 2.8: Typical MVC Prediction Structures: (a) "IPP" and (b) "IBP"                   | 32 |

| Figure 2.9: Samples identification for the intra-frame prediction                        |    |

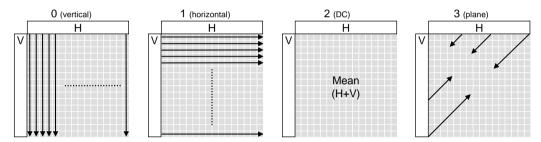

| Figure 2.10: Luminance 4x4 block intra prediction modes                                  | 33 |

| Figure 2.11: Four possible intra prediction modes for luma 16x16 blocks                  |    |

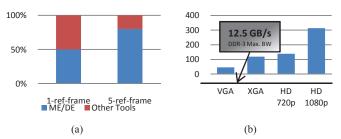

| Figure 2.12: MVC Energy Breakdown                                                        |    |

| Figure 2.13: MVC Encoder/Decoder memory bandwidth requirements                           |    |

| Figure 2.14: ME/DE off-chip memory bandwidth trend for several MVC scenarios             |    |

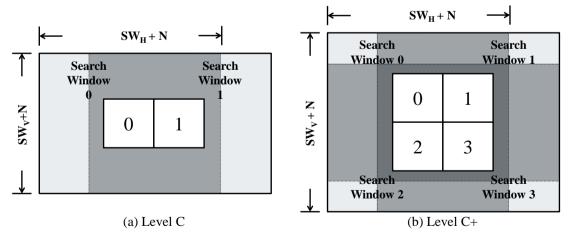

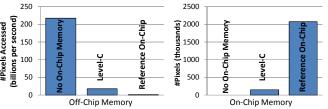

| Figure 3.1: (a) Level C and (b) Level C+ data reuse schemes.                             |    |

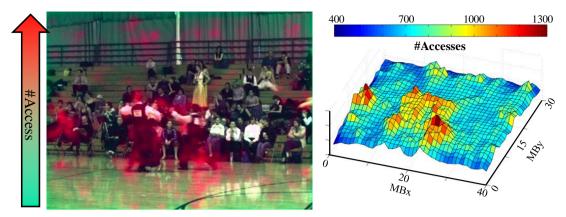

| Figure 3.2: Memory Access Analysis                                                       |    |

| Figure 3.3: MVC Prediction Structure, MB-Centered Perspective                            |    |

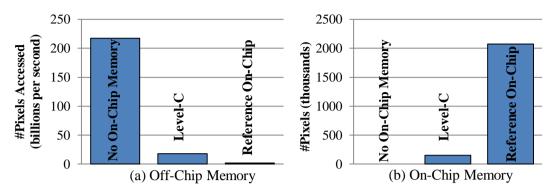

| Figure 3.4: (a) Off-chip memory bandwidth vs. (b) on-chip memory size tradeoff           |    |

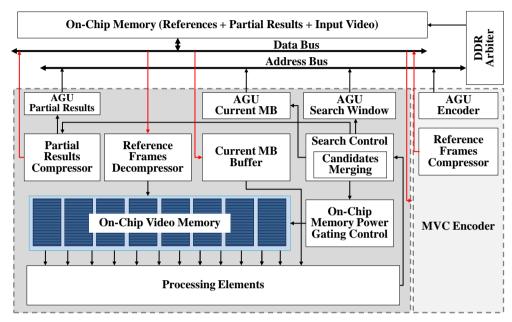

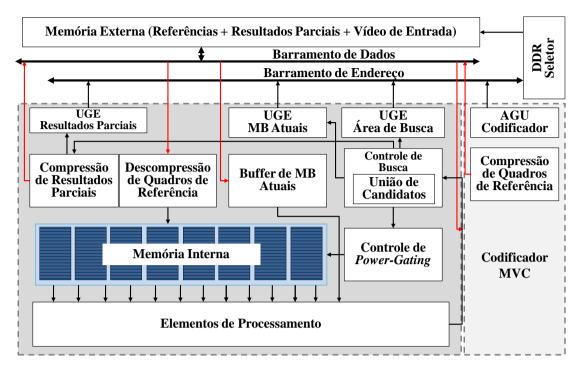

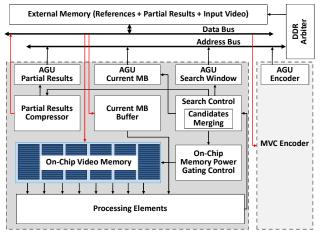

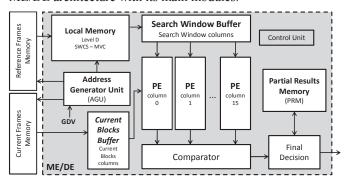

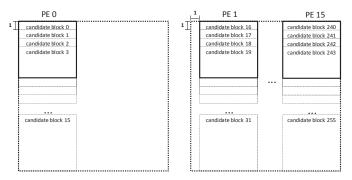

| Figure 4.1: Overall Memory Hierarchy System.                                             |    |

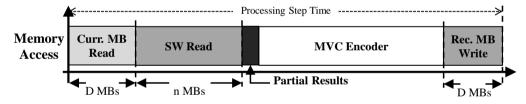

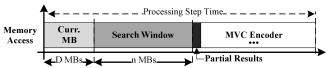

| Figure 4.2: Off-chip Memory Access Scheduling                                            |    |

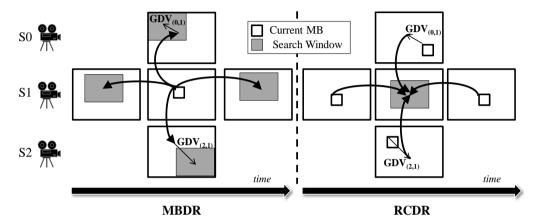

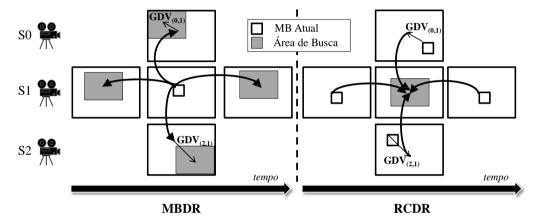

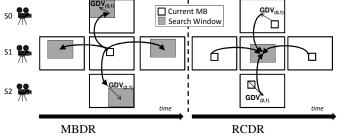

| Figure 4.3: MBDR vs. RCDR Data Reuses for ME/DE.                                         |    |

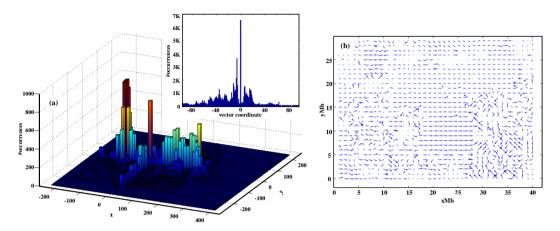

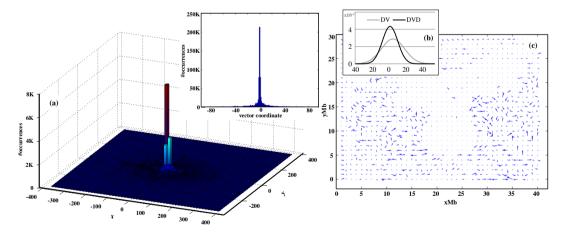

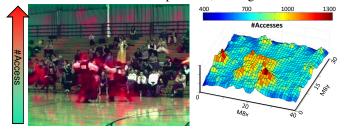

| Figure 4.4: Motion/Disparity vectors statistical properties: (a) 2D/3D histogram and (b) |    |

| vector field.                                                                            |    |

| Figure 4.5: Differential Vectors statistics: (a) 2D/3D histogram and (b) differential    |    |

| vector field                                                                             | 49 |

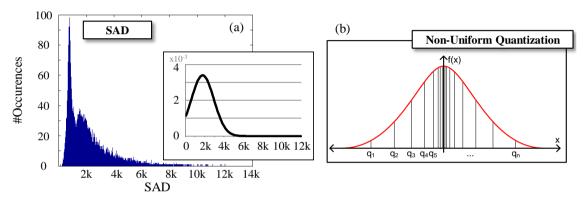

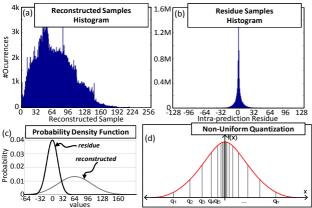

| Figure 4.6: SAD Statistics for ME/DE: (a) histogram and PDF of SAD values and (b)        |    |

| non-uniform quantization approach                                                        |    |

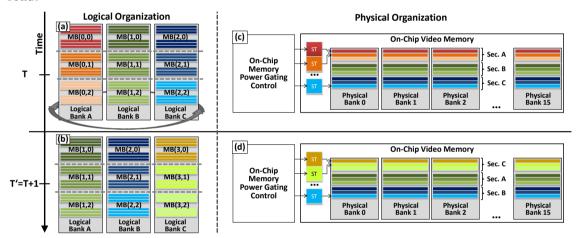

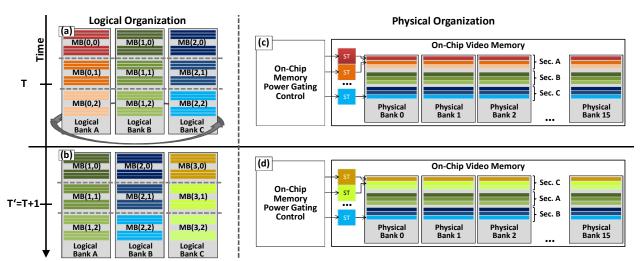

| Figure 4.7: On-Chip Video Memory: (a)(b) logical and (c)(d) physical organization        | 51 |

| Figure 4.8: Pseudo-code of the on-chip video memory power gating                         |    |

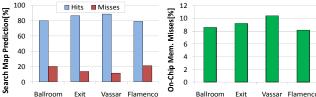

| Figure 4.9: Statistical Maps of the TZ Search algorithm for each Motion/Disparity        |    |

| Estimation and the proposed weighted-calculation.                                        | 52 |

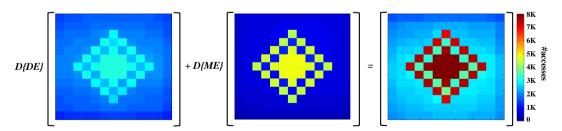

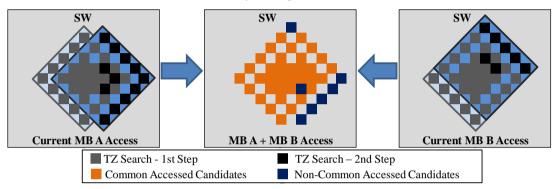

| Figure 4.10: Example: Candidate Blocks Merging                                           | 53 |

| Figure 4.11: Lossless compression algorithm for reference samples                        |    |

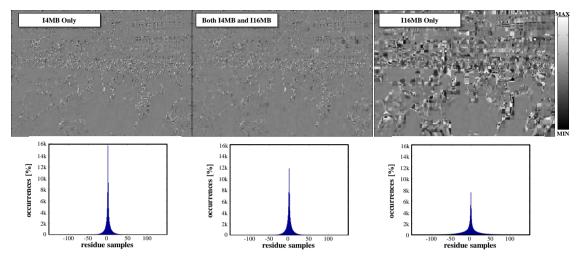

| Figure 4.12: Residue plot examples from the crowd test sequence: I4MB only, I16MB        |    |

| only and both I4MB and I16MB modes.                                                      |    |

| Figure 4.13: Lossy compression algorithm for reference samples                           |    |

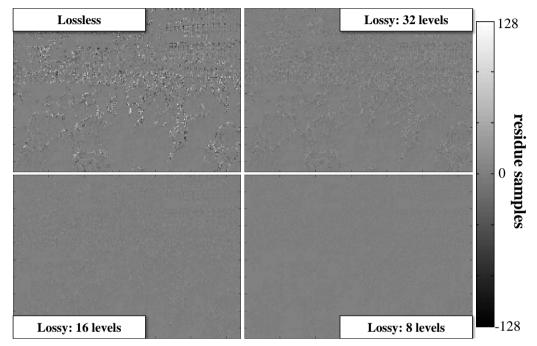

| Figure 4.14: Residue plots for lossy compression for different quantization steps:       |    |

| lossless, 32 levels, 16 levels and 8 levels.                                             | 58 |

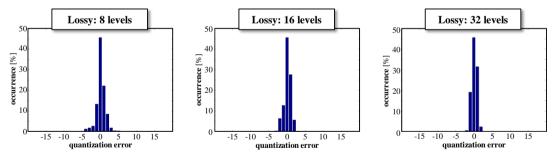

| Figure 4.15: Histogram of the quantization errors for 8, 16 and 32 levels                |    |

| Figure 4.16: Adaptive-lossy compression algorithm for reference samples                 | . 59 |

|-----------------------------------------------------------------------------------------|------|

| Figure 4.17: Thresholds definitions due to the statistical analysis of target MSE value | es.  |

|                                                                                         | . 60 |

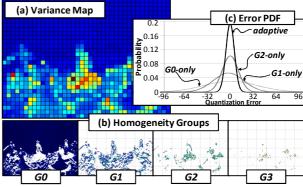

| Figure 4.18: Classification of the residual data due to the variance (homogeneity) in t |      |

| flamenco2 test sequence.                                                                |      |

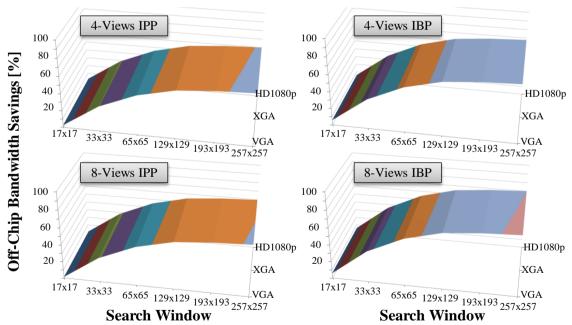

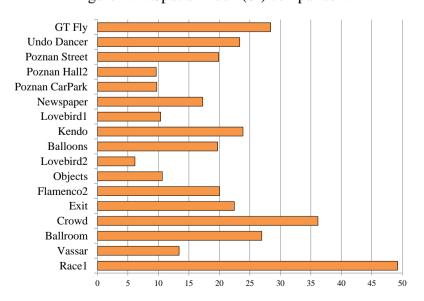

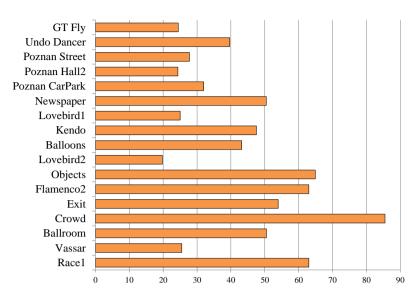

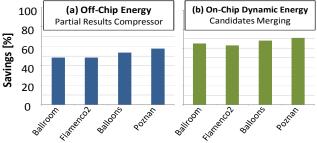

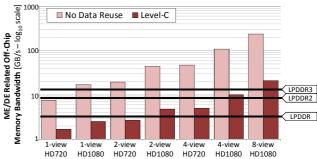

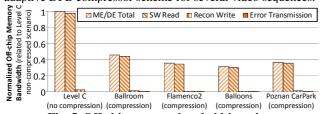

| Figure 5.1: Off-chip memory bandwidth savings (related to the MBDR approach)            | . 63 |

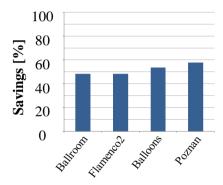

| Figure 5.2: Off-chip memory bandwidth savings due to the Partial Results Compresso      |      |

|                                                                                         |      |

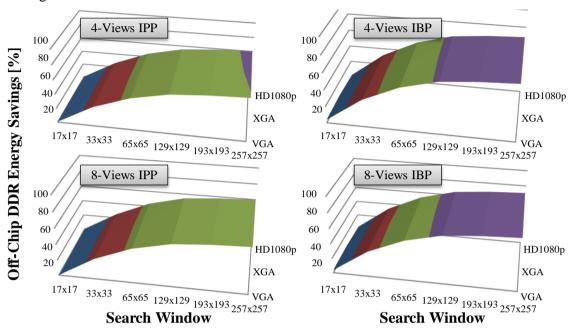

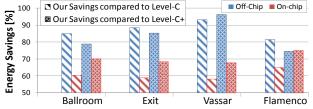

| Figure 5.3: Off-chip DDR energy savings due to RCDR strategy (over MBDR)                | . 65 |

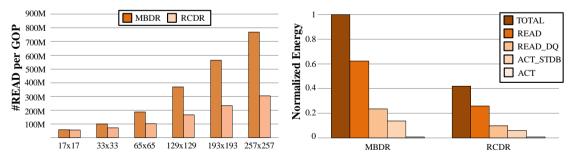

| Figure 5.4: (a) Number of DDR Read cycles (#READs) and (b) DDR energy                   |      |

| consumption profiling (RCDR vs. Level C)                                                | . 65 |

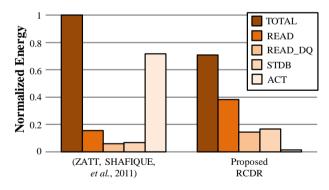

| Figure 5.5: DDR energy consumption in comparison to (ZATT, SHAFIQUE, et al.,            |      |

| 2011)                                                                                   | . 66 |

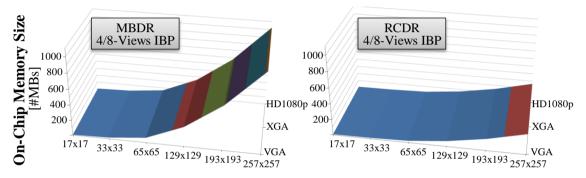

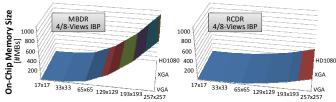

| Figure 5.6: On-chip size increasing for RCDR and MBDR                                   | . 67 |

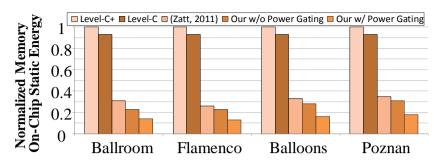

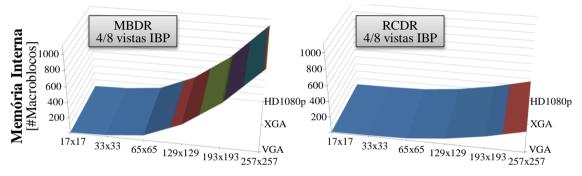

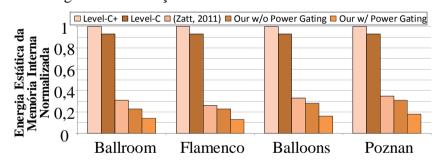

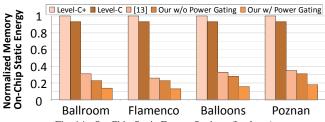

| Figure 5.7: On-chip static energy savings (leakage).                                    | . 68 |

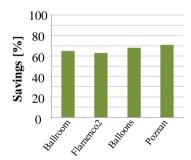

| Figure 5.8: On-chip dynamic energy savings due to candidate merging approach            |      |

| Figure 5.9: Off-chip bandwidth reduction of ME/DE reference samples due to the          |      |

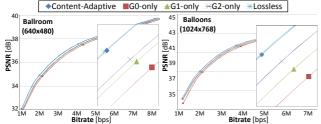

| reference frame compression                                                             | . 69 |

| Figure 5.10: PSNR of ME/DE reference samples due to the reference frame                 |      |

| compression                                                                             | . 69 |

| Figure 5.11: Off-chip memory bandwidth savings due to the proposed reference fram       | e    |

| compression                                                                             |      |

| Figure A.1: Spatial Index (SI) comparison                                               | . 79 |

| Figure A.2: Temporal Index (TI) comparison.                                             |      |

| Figure A.3: Disparity Index (DI) Comparison.                                            |      |

| Figura C.1: Diagrama em blocos da hierarquia memória                                    |      |

| Figura C.2: (a) MBDR versus (b) RCDR.                                                   |      |

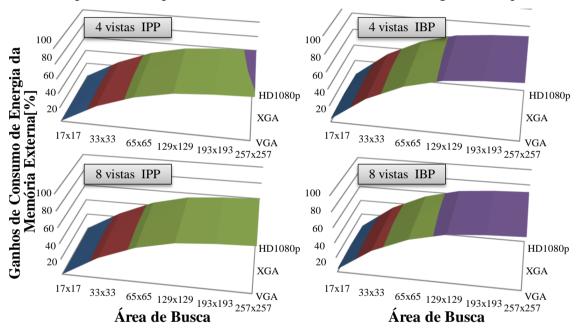

| Figura C.3: Ganhos do consumo de energia da memória externa                             |      |

| Figura C.4: Redução do tamanho da memória interna.                                      |      |

| Figura C.5: Ganhos do consumo de energia estático da memória interna                    | . 93 |

|                                                                                         |      |

# LIST OF TABLES

| Table 3.1: Data reuse techniques comparison.                                  | 38 |

|-------------------------------------------------------------------------------|----|

| Table 3.2: Reference Frames compression techniques comparison                 | 40 |

| Table 3.3: Energy-aware techniques comparison                                 | 41 |

| Table 5.1: Comparison with Reference Frame Compression Related Works          | 71 |

| Table B.1: DE off-line StatMap for the proposed power-gating control (x1000)  | 81 |

| Table B.2: ME off-line StatMap for the proposed power-gating control. (x1000) | 81 |

| Table B.3: Quantization level values: nLev=32                                 | 82 |

| Table B.4: Quantization level values: nLev=16                                 | 82 |

| Table B.5: Quantization level values: nLev=8                                  | 82 |

| Table B.6: Huffman-table probabilities for lossless compression               | 82 |

| Table B.7: Huffman-table probabilities for lossy compression (nLev=32)        | 83 |

| Table B.8: Huffman-table probabilities for lossy compression (nLev=16)        | 84 |

| Table B.9: Huffman-table probabilities for lossy compression (nLev=8)         | 84 |

| Tabela C.1: Resultados e Comparação do Compressor de Quadros de Referência    | 94 |

### **ABSTRACT**

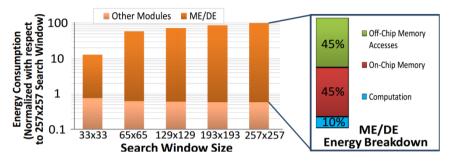

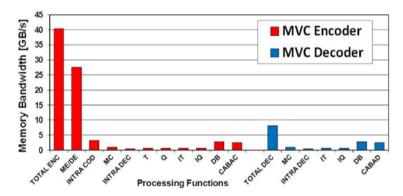

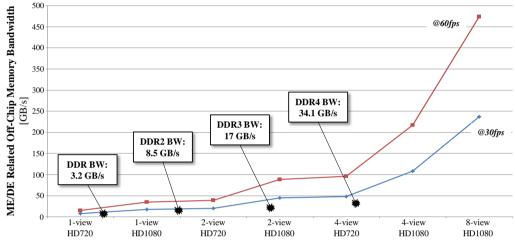

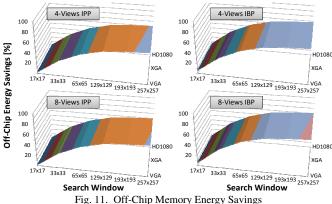

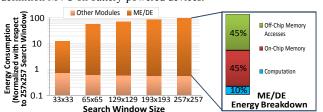

This Master Thesis proposes a memory hierarchy for the Motion and Disparity Estimation (ME/DE) centered on the encoding references, called Reference-Centered Data Reuse (RCDR), focusing on energy reduction in the Multiview Video Coding (MVC). In the MVC encoders the ME/DE represents more than 98% of the overall energy consumption. Moreover, in the overall ME/DE energy, up to 90% is related to the memory issues, and only 10% is related to effective computation. The two items to be concerned with: (1) off-chip memory communication to fetch the reference samples (45%) and (2) on-chip memory to keep stored the search window samples and to send them to the ME/DE processing core (45%). The main goal of this work is to jointly minimize the on-chip and off-chip energy consumption in order to reduce the overall energy related to the ME/DE on MVC. The memory hierarchy is composed of an onchip video memory (which stores the entire search window), an on-chip memory gating control, and a partial results compressor. A search control unit is also proposed to exploit the search behavior to achieve further energy reduction. This work also aggregates to the memory hierarchy a low-complexity reference frame compressor. The experimental results proved that the proposed system accomplished the goal of the work of jointly minimizing the on-chip and off-chip energies. The RCDR provides off-chip energy savings of up to 68% when compared to state-of-the-art, the traditional MBcentered approach. The partial results compressor is able to reduce by 52% the off-chip memory communication to handle this RCDR penalty. When compared to techniques that do not access the entire search window, the proposed RCDR also achieve the best results in off-chip energy consumption due to the regular access pattern that allows lots of DDR burst reads (30% less off-chip energy consumption). Besides, the reference frame compressor is capable to improve by 2.6x the off-chip memory communication savings, along with negligible losses on MVC encoding performance. The on-chip video memory size required for the RCDR is up to 74% smaller than the MB-centered Level C approaches. On top of that, the power-gating control is capable to save 82% of leakage energy. The dynamic energy is treated due to the candidate merging technique, with savings of more than 65%. Due to the jointly off-chip communication and on-chip storage energy savings, the proposed memory hierarchy system is able to meet the MVC constraints for the ME/DE processing.

**Keywords:** Multiview Video Coding, 3D-Video, Low-Power Design, On-Chip Video Memory, Memory Hierarch, Energy Efficient, Motion Estimation, Disparity Estimation.

### **RESUMO**

Esta dissertação de mestrado propõe uma hierarquia de memória para a Estimação de Movimento e de Disparidade (ME/DE) centrada nas referências da codificação, estratégia chamada de Reference-Centered Data Reuse (RCDR), com foco em redução de energia em codificadores de vídeo multivistas (MVC - Multiview Video Coding). Nos codificadores MVC, a ME/DE é responsável por praticamente 98% do consumo total de energia. Além disso, até 90% desta energia está relacionada com a memória do codificador: (a) acessos à memória externa para a busca das referências da ME/DE (45%) e (b) memória interna (cache) para manter armazenadas as amostras da área de busca e enviá-las para serem processadas pela ME/DE (45%). O principal objetivo deste trabalho é minimizar de maneira conjunta a energia consumida pelo módulo de ME/DE com relação às memórias externa e interna necessárias para a codificação MVC. A hierarquia de memória é composta por uma memória interna (a qual armazena a área de busca inteira), um controle dinâmico para a estratégia de power-gating da memória interna e um compressor de resultados parciais. Um controle de buscas foi proposto para explorar o comportamento da busca com o objetivo de atingir ainda mais reduções de energia. Além disso, este trabalho também agrega à hierarquia de memória um compressor de quadros de referência de baixa complexidade. A estratégia RCDR provê reduções de até 68% no consumo de energia quando comparada com estratégias estadoda-arte que são centradas no bloco atual da codificação. O compressor de resultados parciais é capaz de reduzir em 52% a comunicação com memória externa necessária para o armazenamento desses elementos. Quando comparada a técnicas de reuso de dados que não acessam toda área de busca, a estratégia RCDR também atinge os melhores resultados em consumo de energia, visto que acessos regulares a memórias externas DDR são energeticamente mais eficientes. O compressor de quadros de referência reduz ainda mais o número de acessos a memória externa (2,6 vezes menos acessos), aliando isso a perdas insignificantes na eficiência da codificação MVC. A memória interna requerida pela estratégia RCDR é até 74% menor do que estratégias centradas no bloco atual, como Level C. Além disso, o controle dinâmico para a técnica de power-gating provê reduções de até 82% na energia estática, o que é o melhor resultado entre os trabalho relacionados. A energia dinâmica é tratada pela técnica de união dos blocos candidatos, atingindo ganhos de mais de 65%. Considerando as reduções de consumo de energia atingidas pelas técnicas propostas neste trabalho, conclui-se que o sistema de hierarquia de memória proposto nesta dissertação atinge seu objetivo de atender às restrições impostas pela codificação MVC, no que se refere ao processamento do módulo de ME/DE.

**Palavras-Chave:** Codificação de Vídeos Multivistas, Vídeos 3D, Projeto de Baixa-Energia, Memória Interna, Hierarquia de Memória, Eficiência Energética, Estimação de Movimento, Estimação de Disparidade.

#### 1 INTRODUCTION

The increasing demand for immersive multimedia systems has driven the popularization of the 3D video technology that is present in a wide range of applications like teleconference, automotive infotainment, cinema and personal 3D mobile cameras or cellphones. The 3D videos are based on the multiview concept (MERKLE, SMOLIC, et al., 2007) where multiple independent cameras record the same 3D scene from different observation points (viewpoints). Each independent video is called view and the composition of multiple views is exploited by the 3D application to provide the depth perception of the objects (SMOLIC, MUELLER, et al., 2007). The multiple video streams represent a huge amount of data that must be processed and encoded before their storage or transmission.

Some case studies proved the feasibility of multiview video recorders in 3D-camcoders and 3D-mobile phones devices (SHARP, 2011) (FUJIFILM, 2010). Due to the battery-powered nature of such mobile devices, the energy consumption must be as small as possible to enable a good battery usage together with multiview video handling. This way, all the processing and encoding on the multiview videos must be as efficient as possible to meet the energy constraints.

The Multiview Video Encoding (MVC) (JVT TEAM, 2009) provides from 20% up to 50% more coding efficiency when compared to a simple H.264/AVC simulcast approach. These gains are provided due to the innovations of the MVC which exploit the inter-view correlation between frames of neighboring views. This innovative tool is called Inter-View Prediction and uses the Disparity Estimation (DE) as the main module. However, it results in significant increase in the encoding complexity and energy consumption. Along with the Motion Estimation (ME), which is the DE similar step in the Inter-Frame Prediction, the DE represents more than 90% of the MVC encoder energy consumption (ZATT, SHAFIQUE, *et al.*, 2011). For this reason, the ME/DE is the optimization target for reducing the energy consumption in the MVC encoders.

The ME/DE goal is to search for the best representation for the current block (block that is currently being processed) in one or more reference frames (already coded frames) (RICHARDSON, 2003). When the best match is found, a motion/disparity vector that indicates the position of the best match inside the reference frame is generated, so the decoder is able to reassemble the block on the other side. The search is performed within a Search Window (SW) by using a search algorithm. There are several different algorithms for this task, which can be divided into two groups: exhaustive and heuristic. The exhaustive option is the Full Search (FS) (KUHN, 1999) which analyzes all possible candidate blocks to find the best match. As alternative, the heuristic algorithms use some greedy local choices to predict the motion/disparity direction of the image block. The TZ Search is one example of a heuristic algorithm for

ME/DE that presents speed-up results of 23x when compared against the FS, with minimum quality drops (XIU-LI, SHENG-KUI e CAN-HUI, 2010). This algorithm is implemented in the MVC reference software (called JMVC).

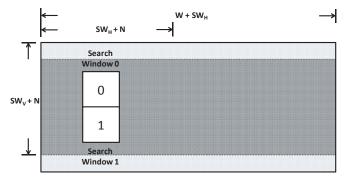

The most part of the energy consumption related to the ME/DE processing is due to the fetching of the search window samples from the off-chip memory and their corresponding on-chip storage. Both off/on-chip energies represent more than 90% of the overall ME/DE energy consumption (45% for the on-chip memory storage and 45% for the off-chip memory communication) (ZATT, SHAFIQUE, *et al.*, 2011). The search window for disparity search must typically cover a range of [-96,+96) in both directions, horizontal and vertical respectively (JVT TEAM, 2006). This amount of reference samples must be accessed for each current block in every frame, of every view on the multiview video. With the current video coding scaling demand, where (a) higher resolutions (up to 4K), (b) higher frame rates (up to 120 frames per second) and (c) a larger number of cameras (from 4 up to 8) are required, the memory requirements and its consequences to the overall MVC encoder energy demand have been increased.

During the past years, several works exploit the data locality of the ME/DE input reference samples in order to store part of them on-chip and, this way, they can be reused. Several works already proposed data reuse solutions for the non-MVC H.264/AVC, like (TUAN, CHANG e JEN, 2002) (CHEN, HUANG, et al., 2006). The MVC encoding is the target in (TSUNG, DING, et al., 2007), where more sophisticated approaches were designed by using intensive statistical analysis as the basis for their proposals. Some of these strategies were implemented as memory hierarchies of such hardware architectures to design efficient memory solutions for ME/DE (ZATT, SHAFIQUE, et al., 2011) (ZATT, SHAFIQUE, et al., 2011) (SHAFIQUE, ZATT, et al., 2012). From a different perspective, some works aim to reduce the memory overhead by compressing the data before the MVC encoder saves the reconstructed samples in the off-chip memory (for future ME/DE) (MA e SEGALL, 2011) (WANG, CHANDA, et al., 2012) (GUPTE, AMRUTUR, et al., 2011) (SONG, ZHOU, et al., 2010) (SILVEIRA, GRELLERT, et al., 2012). These works try to design efficient coding algorithms with as minimum computational effort as possible. The goal is to exchange off-chip memory bandwidth (responsible for 45% of the encoder energy) by computation overhead (around 10% of the entire energy).

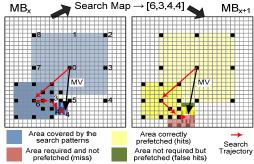

The related approaches' results do not scale in a good way with the scaling for multiview videos. As higher is the number of views as higher is the number of the required ME/DE and more reference frames are inserted to be searched. None of the related works exploit the locality of the memory accesses in the reference frame level. The adopted ME/DE data reuse strategies are centered on the current block processing order, so one reference frame must be accessed many times and at different time instants, making it harder this level of data reuse. This work proposes a different schedule for the ME/DE operations, which is based on the accessed search window that is currently present in the on-chip memory.

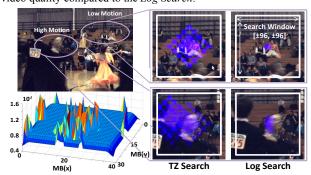

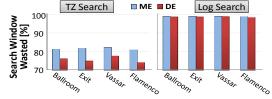

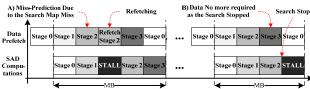

Another point is related to the wasting of energy of unprocessed samples of the search window when heuristic search algorithms are used, like the TZ Search. Considering this algorithm, on average 80% of the samples in the search window are not analyzed in the TZ Search execution and, this way, the energy to access and store these samples is wasted (ZATT, SHAFIQUE, *et al.*, 2011). Some works reduce these penalties by a predictive prefetching for the most probable samples considering the history of previous accesses for the past blocks. However, this approach implies in an

irregular off-chip memory access which complicates the control and does not match the regular burst access for the off-chip DDR memories (JEDEC, 2010). This work allies a regular pattern of access, by fetching the entire search window, and implements an on-chip memory power management to reduce the supply-voltage of the non-accessed regions of the search window to save on-chip memory energy.

Regarding the reference frame compression techniques, most of them fail to achieve good savings in the off-chip memory communication along with negligible losses in the encoder efficiency. This work aims to exploit lossless, lossy and adaptive solutions to meet with this tradeoff: high savings in the off-chip memory bandwidth and minimum losses in the MVC encoder performance.

The main challenge in this type of design is to jointly minimize the on-chip and offchip energy consumption in order to reduce the overall energy related to ME/DE on MVC.

#### 1.1 Contributions of this Master Thesis

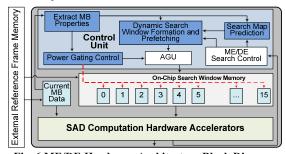

This work proposes a reference-centered memory hierarchy for ME/DE on MVC targeting low-energy consumption at both on-chip storage and off-chip memory access. The memory hierarchy is composed of an on-chip video memory, an on-chip memory power gating control, and a partial results compressor. A search control unit is also proposed to exploit the search behavior to achieve further energy reduction. This thesis also integrates to the memory hierarchy a low-complexity reference frame compressor. The goal is to improve the savings by reducing the representation of the reconstructed samples before they are saved on the off-chip memory. The contributions of this Master Thesis are summarized as follows:

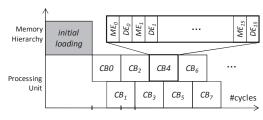

- Reference-Centered Memory Hierarchy: it employs a Reference-Centered

Data Reuse (RCDR) scheme. It makes the reference frames the center of

processing order to avoid search window retransmission and to eliminate the

need to simultaneously store on-chip multiple search window. A memory access

scheduling and an energy-efficient on-chip memory organization are proposed.

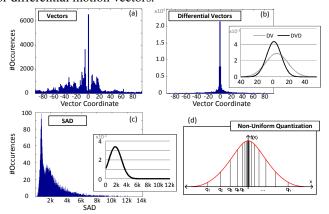

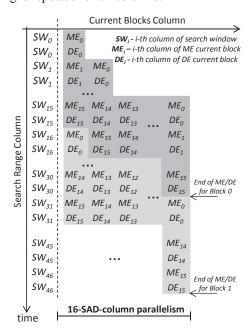

- Statistic-Based Partial Results Compressor: the RCDR strategy implies outof-order processing considering the blocks perspective, since it is not guaranteed that one block of the video will be completely processed after the ME/DE operation. This way, the partial results (motion/disparity vectors and SAD) should be stored to be used for the next ME/DE over the same block. Statistically defined non-uniform quantization and Huffman coding are employed for partial results compression.

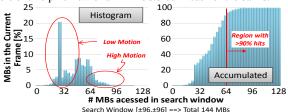

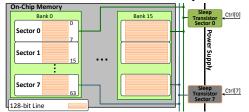

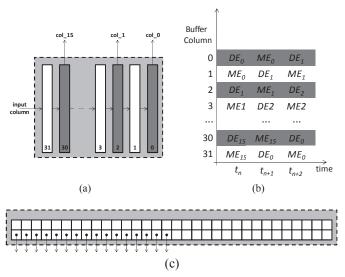

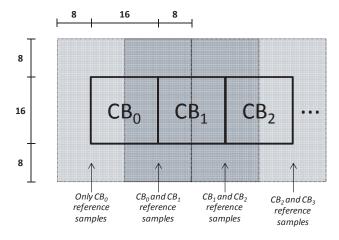

- On-chip Video Memory: the on-chip memory is organized in multiple SRAM banks featuring line-level power gating capability. At run-time, search window regions that are statistically less likely to be used are power-gated. Furthermore, the candidate blocks coding order is rearranged to minimize on-chip memory line switching and, consequently, the dynamic energy consumption.

- Low-Complexity Intra-Based Reference Frame Compressor: this compressor exploits the regular off-chip access pattern allowed by the RCDR strategy. The proposed low complexity compression algorithm is based on a simplified instance of the intra prediction defined in the H.264/AVC. The idea is use the encoder knowledge to just get the best intra mode for both I4MB and I16MB modes (RICHARDSON, 2003) that have been already processed by the MVC

encoder to code the reconstructed block before it is sent to the off-chip memory. Besides, non-linear quantization is applied in different strengths depending on the image region characteristics to reduce the losses and meet with high off-chip bandwidth reduction.

## 1.2 Text Organization

Chapter 2 presents the MVC background and points some MVC challenges related to the memory issues used as motivation for this work. Chapter 3 discusses the already proposed energy-efficient solutions for MVC encoding regarding the memory issues. Chapter 4 describes the proposed memory hierarchy system targeting energy-efficient MVC encoders. Chapter 5 presents the experimental results and comparison with the state-of-the-art works presented in the literature. Finally, Chapter 6 will conclude the work and will point some future directions for research.

## 2 MULTIVIEW VIDEO CODING BACKGROUND

During the past years, there was an intense research effort to provide even more realism for the current and the next generation multimedia applications. This effort has had as results the gradual popularization of high realism devices, like 3D television sets, which are definitely available for the common costumers for affordable prices. Other costumer devices like digital cameras, video games and cell phones already support the 3D video processing.

The digital video streams that support these 3D applications are not the usual ones taken by one single camera. Instead, the bases are videos that are captured by multiple cameras disposed at different observation points (viewpoints). Each individual video is called a *view* and the entire set of views composes the so called *multiview video*. One of the key challenges is how to transmit and store this kind of stream, since they require huge amount of bits to be represented. In this context, the Multiview Video Coding (MVC) acts in order to reduce the representation of these videos by exploiting the data redundancies (like objects that remain visible during several frames or homogeneous scene backgrounds).

This chapter initially discusses details of the overall multiview video systems, from the encoding part to the transmission systems and the final applications. Then, the multiview video characteristics are presented. The focus is to introduce the concepts of redundancies to understand how the video encoders work with the goal of exploiting them to reduce the data required for video representation. The basic concepts in multiview video coding are presented, and the main coding tools are described. Further, the Motion and Disparity Estimation, the main focus of this Master Thesis, are explained in more details. The Intra-Frame Prediction is then presented. Finally, this chapter points the main memory-related challenges in the multiview video encoders and set the contribution aimed in this work within these challenges.

# 2.1 Multiview Video Encoding System

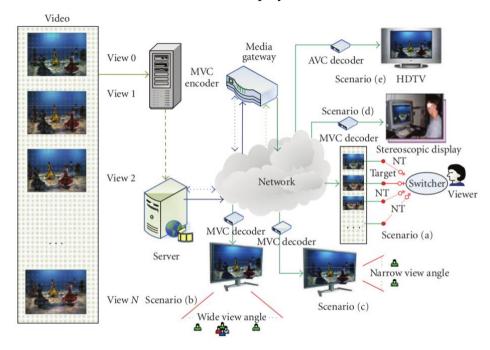

Figure 2.1 presents the end-to-end Multiview Video Coding (MVC) System for some final applications (CHEN, WANG, et al., 2009).

In this illustration, a multiview video is first captured and then encoded by a multiview video encoder (MVC encoder). A server transmits the coded bitstream(s) to different clients with different capabilities, possibly through media gateways. As the final stage, coded video is decoded and rendered with different meanings according to the application scenario and capabilities of the receiver. The scenario (a) from Figure 2.1 represents the so called free-viewpoint television, (b) is the wide view angle television, (c) corresponds to the narrow view angle television and (d) represents the 3D applications. All these scenarios combine multi video streams as input (multiview

videos). Besides, multiview videos are compliant to an ordinary singleview video decoder. This is the case of scenario (e), where only one view (called base view) is decoded and exhibited from a common 2D display.

Figure 2.1: MVC system architecture. (CHEN, WANG, et al., 2009)

The next sections initially describe the MVC final applications presented in Figure 2.1. Then, the MVC requirements and standardization are presented. Finally, details about MVC extension of H.264/AVC video coding standard are provided.

#### 2.1.1 Multiview Scenarios and Applications

The primary usage for multiview video is to support 3D video applications, where 3D depth perception of the visual scene is provided by a 3D technology display system. There is a wide range of 3D displays systems (KONRAD e HALLE, 2007) including the classic stereo system that requires special-purpose glasses to more sophisticated multiview autostereoscopic displays that do not require the use of glasses (DODGSON, 2005). The stereo systems only require two views, where the left-eye is presented to the viewers' left eye, and the right-eye view is presented to the viewers' right eye. The 3D displays and the glasses ensure that the appropriate view is viewed by the correspondent human eye. This is accomplished with either passive polarization or active shutter techniques. The multiview displays have much greater throughput restrictions relative to conventional stereo displays in order to support a given image resolution, since 3D is achieve by essentially emitting multiple complete video sample arrays in order to form view-dependent pictures. Such displays can be implemented, for instance, using conventional high-resolution displays and parallax barriers; other technologies include lenticular overlay sheets and holographic screens. Each view-dependent video can be thought of as emitting a small number of light rays in a set of discrete viewing directions (typically between eight and a few dozen for an autostereoscopic display). Generally these directions are distributed in a horizontal plane, such that parallax effects are limited to the horizontal motion of the observer (VETRO, WIEGAND e SULLIVAN, 2011).

Another goal of multiview video is to enable free-viewpoint video (SMOLIC e KAUFF, 2005). In this case, the viewer can interactively change the viewpoint and the view direction of the 3D scene. Each output view can either be one of the input views or a virtual view synthesized from a smaller set of multiview inputs and other data that assists in the view synthesis process (such as depth maps (YAN, YANG, *et al.*, 2011)). With such a system, viewers can freely navigate through the different viewpoints of the scene, within a range inside the multiple cameras. This kind of application can be implemented by using simple 2D conventional displays. However, 3D displays for free-viewpoint systems could also be considered. It is possible to see the use of this functionality in broadcast production environments, or to change the viewpoint of a sports scene in order to catch a better angle of the play. Such functionality may also be of interest of gaming, education, surveillance, and sightseeing applications. As the final step, it can imagine providing this interactively capability directly to the home viewer.

Another important application of multiview videos is to support immersive teleconference applications. Beyond the advantages provided by the 3D displays systems, it is reasonable to use this technology to enable a more realistic communication experience when motion parallax is supported. Motion parallax is caused by the change in the appearance of a scene when the viewers shift their positions, causing the revealing of occluded scene contents.

For all of the above scenarios, the storage and transmission capacity requirements are significantly increased. Consequently, there is a strong need for multiview video compression techniques. These requirements, besides the current standardization on multiview video compression are discussed as follows.

#### 2.1.2 Multiview Encoding Requirements and Standardization

The central requirement for most video coding designs is high compression efficiency. In the specific case of MVC this means a significant gain when compared to independent compression of each view. The compression efficiency of video encoders measures the tradeoff between cost (in terms of bitrate) and benefit (in terms of video quality) (SULLIVAN e WIEGAND, 1998). However, the compression efficiency is not the only criterion under consideration for the video encoder standardization. General further requirements for video encoder capabilities are also required, such as minimum resource consumption (memory, processing energy), low delay, high performance for a range of video resolutions, color sampling structures, and bit depth precisions.

Some requirements are specific related to MVC. Besides the temporal random access, it is also required the *disparity random access*. Together both ensure that any image can be accessed, decoded, and displayed by starting the decoder at a random access point and decoding a relatively small quantity of data which that image may depend. *View scalability* is also fundamental for multiview video encoders. It is related to the ability of a decoder to access a portion of the bitstream to output a subset of the encoded views (VETRO, WIEGAND e SULLIVAN, 2011). Another important requirement is the *backward compatibility*, which means that a subset of the MVC bitstream corresponding to one "base view" needs to be decodable by an ordinary (non-MVC) decoder, and the other data representing other views should be encoded in such a way that will not affect that base view decoding capability. The ability of an encoder/decoder to provide parallel processing was also required to enable practical implementation and to manage processing resources effectively. Furthermore, for ease

of implementation, it was also highly desirable for the MVC design to have as many common elements as possible with an ordinary non-MVC system.

#### 2.1.3 H.264/MVC Standard

The H.264/AVC video coding standard (JVT TEAM, 2003) was defined by a jointly group composed of experts from two important standardization companies: the ISO/IEC (International Organization for Standardization) (ISO, 2012) and the ITU-T (International Telecommunication Union - Telecommunication Sector). This new group was called JVT (Joint Video Team).

The Multiview Video Coding (JVT TEAM, 2009) was proposed in the Annex H of the H.264/AVC standard as the extension to efficiently deal with multiview videos due to the current demand on immersive multimedia applications that support this new kind of video streaming. Besides extended syntax elements, the MVC extension innovates due to the exploitation of the inter-view (also called disparity) correlations between frames of different views, by inserting the inter-view prediction. In doing so, the MVC encoders is able to achieve from 25% to 50% more compression gains compared to the simulcast approach, where the views are encoded as independent videos by non-MVC H.264/AVC encoders (MERKLE, SMOLIC, *et al.*, 2007). Moreover, quality gains of more than 3dB is also achieve. However, the computational effort inserted by the interview prediction was increased from 10 to 19 times in the MVC encoders. Besides, other design challenges emerge, like impressive memory and energy constraints.

The following sections will basis the digital video characteristics that are important for the video compressors. Then, the multiview video coding basis is explained from the generic MVC encoder description to the detailed discussion of the main focus of this work: the inter-frame and inter-view prediction.

## 2.2 Digital Video Characteristics

A digital video is a sequence of static images (called *frames*) that gives the motion sensation when exhibited in a certain rate. Typically, this frame exhibition rate should be between 24 and 30 frames per second to provide smoothly motion for the human visual system (RICHARDSON, 2003). However, nowadays the frame requirements are scaling due to the new demand for high realism. This way, elevated frame rates as 60 and 120 frames per second are already needed for state-of-the-art applications.

Each frame of the video is represented by a pixel matrix of dimensions W (width) and H (height). Each pixel stores the color and the luminosity of that position. In this sense, there are a few well-known color spaces to numerically represent one pixel. The most used color space is the RGB, which splits the pixel information in three color channels: red (R), green (G) and blue (B). The RGB color space is widely used in televisions, monitors and digital cameras. However, the RGB is not the preferred one for the video compression algorithms, since there is a compression high correlation between each color channel and, for this reason, it is not possible to apply different coding techniques to each component individually (RICHARDSON, 2003).

Instead of using RGB, the video encoders use the YCbCr color space. In this alternative space, the pixel information is divided in *luminance* (Y), *blue chrominance* (Cb) and *red chrominance* (Cr). The luminance (also referred as luma) channel represents the light intensity (grayscale) of the image. The chrominance (or chroma) components express the color tones of the pixels. In this color space there is not a high

correlation between the YCbCr components (RICHARDSON, 2003). So, they can be processed by different algorithms that are able to exploit its specific properties in order to achieve better compression rates.

This work will call each of luma and chroma components of one pixel as *sample*. Then, one pixel in the YCbCr color space will have one luma, one blue chroma and one red chroma sample associated with it.

The multiview videos are composed of several videos taken by cameras that observe the scene from different viewpoints. The multiview videos inserted another dimension on the digital video representation. Conceptually, a singleview video is a sequence of 2-dimensional matrices (using RGB or YCbCr color spaces, for example) that represents the video in the spatial and in the temporal domain. The multiview videos have one more dimension: called disparity, and it is represented by the several independent singleview streams (MERKLE, SMOLIC, *et al.*, 2007).

Multiview videos require a huge amount of bits to be represented. The video encoders aim to reduce this information by exploiting the data redundancies that are presented in the digital videos. The most important one is the temporal redundancy. This kind of correlation is related to the high similarity between two consecutive temporal frames. Since the frame rates are usually greater than 30 frames per second, there is a lot of repeated information that are presented in two neighbor frames (WIEGAND, SULLIVAN, *et al.*, 2003). The differences are generally caused by the different position of the objects in the scene, due to their motion. Even in this case, the objects generally are presented in the frame and just its position was changed. The video coding algorithms exploit this kind of redundancy by performing searches for best matches between regions of two or more neighbor frames. The goal is to identify the modulus and the direction of the motion.

Another important video characteristic is the homogeneity between neighbor pixels in the same frame. Regions like a scene background and a blue sky are examples of very homogeneous areas. This characteristic is called spatial redundancy and it is exploited in video encoders by basically try to copy the neighbor pixels to infer the other neighbor ones. The way that is performed this copy must respect the texture direction of the represented object.

Besides, some studies about the human visual system points that some characteristics the images, like high frequency regions, are not perceived by the human eye. This way, the elimination of these high frequency elements considerably increases the compression rates due to negligible losses in the perceptual quality. This kind of redundancy is classified as psycho-visual (GONZALEZ e WOODS, 2003) or as spatial (RICHARDSON, 2003), depending on the author.

The multiple views insert an additional video characteristic: the redundancies between frames from different views. In this case, the redundancy is not related to the temporal correlation, but to the multiple cameras that are observing the same scene at the same time instant, i. e., by the disparity correlation. This type of correlation is called disparity redundancy and it is generally exploited by video encoders by the same block matching process that is employed to deal with the temporal redundancies.

Figure 2.2 presents some frames of the VGA (640x480 pixels) test sequence ballroom to show examples of redundancies in a real video. The ballroom sequence is

Frame: s0t1

Frame: s1t1

Frame: s1t1

used in the standardized benchmark set used for the video coding community (JVT TEAM, 2006).

Figure 2.2: Redundancies in multiview videos.

In this whole Master Thesis, a frame will be indicated by the notation presented on Figure 2.2. For example, the frame "s1t2" indicates the frame of the view s1 captured at the time t2. Taken the frame s1t2, it can be noted regions of the image that are spatially similar, like the black dancers clothes. As already presented, this correlation among neighboring pixels in the same frame is called spatial redundancy. Furthermore, if two temporal neighboring frames are taken (s1t1 and s1t2, for example), the images are almost equals due their high temporal redundancy. The higher motions are caused by the dancers that are on the rightmost part of the frames. On the other perspective, the disparity estimation can be noted when the frames s0t1 and s1t1 are compared. In this case, the differences are not related to the motion, but to the different camera viewpoints. Also, lots of redundancies can be perceived.

## 2.3 Basic Concepts on Video Coding

As already explained in Section 2.1, the video compression is located in an extremely important role in the multiview video generation, transmission and reproduction system. This importance is increased when it is considered the scaling demand that is required for the new multimedia applications: frame resolution scaling, frame rate scaling and view number scaling. The multiview video treatment is unfeasible, at least at the current technology, if a non-compressed approach is used (MERKLE, SMOLIC, *et al.*, 2007).

The video compression (usually also called *video coding*) aims to reduce the data representation of the digital video by exploiting its existing redundancies. The main tradeoff of a video encoder is to ally high compression rates with minimal losses in visual video quality (SULLIVAN e WIEGAND, 1998). This tradeoff is commonly referred as *rate-distortion optimization* and it will be further explained.

The latest video coding standards adopt as default color space the YCbCr. This way, the digital video are composed of one luma samples matrix (Y) and two chroma samples matrices (Cb and Cr). These matrices are divided in basic unities called *blocks*, the basic coding unit of a video encoder. The coding algorithms will be applied individually for each block of the frame. The dimension of the block can vary in according with the encoder standard. The H.264/AVC standard defines a fixed-size block of 16x16 samples as the basic block size, called macroblock (MB). During the coding process, this macroblocks can be subdivided in smaller blocks (16x8, 8x16, 8x8, 8x4, 4x8 and 4x4 are allowed) (WIEGAND, SULLIVAN, *et al.*, 2003).

The first basic technique to reduce digital video representation is to discard some samples that are not important for the human eye perception. In this sense, the less important sample channels in the YCbCr color space are the chroma ones (RICHARDSON, 2003), since it was studied that the video quality perception for the human eye is more related to the luma samples resolution matrix. This way, it is possible to reduce the resolution of the chroma channels with negligible losses in quality for the human visual system. These different relations between the luma and chroma dimensions are called *color formats*.

The most common formats are 4:4:4, 4:2:2 and 4:2:0. In the 4:4:4 format, each Cb and Cr sample are related to only one luma sample. This is a non-compressed scenario where chroma and luma resolutions are the same. The 4:2:2, 4:1:1 and 4:2:0 are called *subsampled* formats, where the chroma resolution is smaller than the luma resolution.

The latest video coding standard, like H.264/AVC, the adopted correlation between luma and chroma samples is 4:2:0. It means that the blue and red chroma matrices for one frame have their dimensions subsampled to (W/2)x(H/2), while the luma resolution remains WxH. This way, this work will adopt this data format in all experimental analyses.

The basis scheme behind the latest video encoders is called *residual coding*. In this strategy, the goal is to analyze different ways to code a given block of pixels by using previously coded blocks of the video. These already coded blocks are taken as reference for the current block coding. This task is called prediction and it is the core of the residual encoders. The prediction process is responsible to search for the best way to represent the block that is being coded by using all already coded blocks as reference (in the past frames or in the same frame). As final result of the prediction step, two main elements are generated: (1) the prediction block that represents the best possible representation of the original block by using only the reference blocks and (2) the prediction mode that tells the way to use the reference pixels to generate the predicted block. The predicted block can be different when compared to the original one, so the simple discarding of these differences will result in losses in the pixel values. In order to deal with it, this difference is also generated and it is sent together with prediction mode (called residual block). In the decoder process, the predicted block is generated in an inverse way, by having the prediction mode. The original block can be remounted by adding the residual information with the predicted block.

The H.264/AVC standard (JVT TEAM, 2003), which is the adopted one for all experiments in this work, uses the residual encoding concepts. Besides, the next generation of video encoders also applies residual coding besides to new features to handle with even higher resolution videos (JCT-VC, 2012).

There are a large variety of techniques that were proposed to improve the compression rates in video encoders. In order to delimit the scope of this work, the following explanations will take as basis the techniques defined by the H.264/AVC encoder for multiview videos.

#### 2.4 H.264/AVC Encoder for Multiview Videos

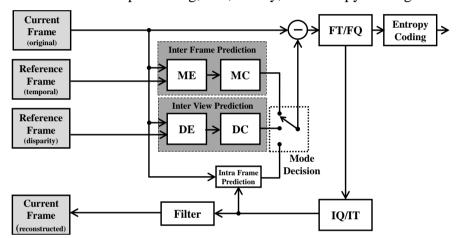

The Figure 2.3 presents the overall diagram of the H.264/AVC multiview video encoder with its main coding tools. The main modules of the encoding process are: Motion Estimation (ME) and Motion Compensation (MC), composing the Inter-Frame Prediction; the Disparity Estimation (DE) and the Disparity Compensation (DC), composing the Inter-View Prediction; the Intra-Frame Prediction; the Mode Decision; the Forward Transforms and the Forward Quantization (FT/FQ), which are responsible for the residual information processing; and, finally, the Entropy Coding.

Figure 2.3: Overall H.264/AVC encoder block diagram for multiview videos.

Inside the encoder, there are a reconstruction path, composed of the Inverse Quantization and Inverse Transforms (IQ/IT), to deal with the mismatch between encoder and decoder. This issue will be discussed further. Besides, a Deblocking Filter is also used to smooth the borders between the blocks, increasing the subjective quality of the video.

As presented in Figure 2.3, the prediction process in the H.264/AVC is divided in three different modules: (1) the Intra-Frame Prediction, (2) the Inter-Frame Prediction (ME and MC) and (3) the Inter-View Prediction (DE and DC). As already explained in the Section 2.3, the prediction process is responsible to find the prediction mode that generates the most similar predicted block to the original block.

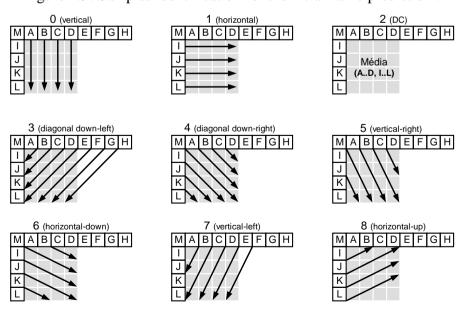

The Intra-Frame Prediction aims to exploit the spatial redundancy. Due to several predefined copy modes, the intra prediction predicts the current block by copying the already coded neighbor samples in several predefined directions. The main profile of the H.264/AVC defines the intra prediction for 16x16 and 4x4 block sizes. There are 4 possible prediction modes for the 16x16 blocks and 9 possible modes for the 4x4 modes. The intra prediction process will be further detailed in the Section 2.6.

The Inter-Frame Prediction is the task that deals with the temporal redundancy and it is composed of two main subtasks: the Motion Estimation (ME) and the Motion Compensation (MC). The goal of the ME is to effectively search for the best match between the current block in one or more already coded temporal neighbor frames

(called *reference frames*). Once the best match is found, the ME generates a *motion vector* and a *reference frame index* in order to indicate to the decoder in which reference frame the best match is and in which position it is located. The MC is the next step and it is responsible to access the reference frame memory to get the predicted block by using the ME outputs (motion vector and reference frame index). Finally, when the MC remounts the predicted block from the memory, the residual information is calculated and sent to the Forward Transforms and Forward Quantization to be properly coded.

The Inter-View Prediction is an innovation proposed by the Annex H of the H.264/AVC released in 2009 (JVT TEAM, 2009). The Inter-View Prediction is responsible to exploit the disparity correlations between neighboring frames of different views. The insertion of this coding tool increases the compression rates of multiview videos from 20% to 50%, according to the video characteristics. However, the computation effort of the overall encoder is increased in almost 19x (MERKLE, SMOLIC, et al., 2007). The steps of this prediction module are the Disparity Estimation (DE) and the Disparity Compensation (DC) and they conceptually works in a similar way to the ME/MC steps in the Inter-Frame Prediction. The difference is that the references for the DE are the already coded disparity neighboring frames, differently from the ME, which searches in temporal neighboring frames. Although the ME and DE are conceptually similar, there are important characteristics that differ one from the other, since they are working with distinct redundancies: ME exploits the temporal redundancy, i. e., the motion of the objects, and the DE acts to eliminate the disparity redundancy and it needs to catch the objects displacements due to the different camera viewpoints (MERKLE, SMOLIC, et al., 2007). These particular properties of Inter-Frame and Inter-View Predictions will be further discussed in Section 2.5.

The residual data is then processed by the Forward Transforms and Forward Quantization before they are packed in the final bitstream (coded video). These two modules compose the residual treatment path, which consists of a series of mathematical calculations that will prepare the residual blocks to be efficiently coded by the final encoding step, the Entropy Coder. First, the transforms will be applied to change the samples from the spatial domain to the frequencies domain (WIEGAND, SULLIVAN, et al., 2003). The transformed block group the frequencies in a descending order. Then, the quantization acts on the transformed block to take the lower frequencies to zero (full compression) and to attenuate the higher frequencies to lower values. The quantization strength is controlled by an external parameter, called Quantization Parameter (QP). This is the encoding step that inserts losses in the coded video, since the quantization basically performs an integer division in the transformed residual samples. This way, the encoder is not able to recover the original value. The QP is the main external parameter to control the encoder efficiency and acts in the sense to control the losses and the compression rates of the entire encoder. As higher is the QP value, higher will be the compression rates and more perceived are going to be the losses. On the other hand, lower QP values will generate minor losses and worst compression rates. The quantization output is a sparse matrix with very low values that can be very efficiently compressed by the Entropy Encoder.

The three predicted blocks (Intra-Frame, Inter-Frame and Inter-View) are then analyzed by the Mode Decision. The goal now is to decide for the best mode that minimizes the efficiency tradeoff between video quality and final bitrate. This is a very complicated task and there are a lot of things that the Mode Decision needs to considerate to take a good choice. The reference software of the MVC, the JMVC (Joint

Multiview Video Coding Model), implements the technique called Rate-Distortion Optimization (RDO) (WIEGAND, SULLIVAN, et al., 2003). The RDO is a very computation-intensive algorithm for Mode Decision that performs the full encoding process for all possible prediction modes. At the final, the RDO compares the rate-distortion costs and gets the best one. It means, in other words, that for each possible prediction mode the encoder need to execute the prediction, transforms, quantization and entropy encoding to generate its rate-distortion cost. For this reason, the RDO is extremely costly in terms of MVC encoder execution time.

The rate-distortion cost is the metric used by the RDO to choose the best prediction mode for a given block. Its mathematical definition is presented in the Equation (1), where D represents the distortion between the reconstructed block (after the quantization losses) and the original one, R is the output bitrate and  $\lambda$  is the *lagrangian* parameter which correctly weighted the tradeoff between distortion and bitrate depending on the target QP.

$$RD_{cost} = D + \lambda R \tag{1}$$

The prediction process is able to use different distortion metrics (also called similarity metrics) to measure the similarity degree between the candidate blocks and the current block. Also, these metrics are used in the RDO mode decision to calculate the distortion term (D in Equation (1)). These metrics will be detailed discussed in Section 2.5.

The mode decision accuracy directly impacts the final encoder performance in terms of quality losses and compression rates. The RDO is commonly used as superior borderline as the most efficiency and the most complex mode decision algorithm, since all possibilities are completely coded and reconstructed to get the final distortion and bitrate. For this same reason, the RDO provides the best rate-distortion results.

The criterion to define the quality of the generated video is extremely important to evaluate the encoder performance. However, there are a lot of issues that must be counted. The subjective visual analysis to determine the quality is very imprecise, since there are a lot of factors that affect the evaluation and some of them are inherently subjective. This kind of quality measurements is called *subjective metrics* (SESHADRINATHAN, SOUNDARARANJAN, *et al.*, 2010) and will not be discussed in this Master Thesis. This work adopts the *objective metrics* to evaluate the quality of the generated videos.

The objective quality is calculated by algorithms that compare the original video and the encoded video. This comparison is performed frame-by-frame by matching all pixels of the original frame with all most similar pixels of the encoded frame.

The PSNR (Peak-to-Signal Noise Ratio) is the most accepted objective quality metric by the video coding community (RICHARDSON, 2003). It is expressed in decibels (dB) and uses a logarithmic factor based on the MSE (Mean Squared Error) value of the reconstructed and original frames. The Equations (2) and (3) show the MSE and PSNR mathematical definitions, where *R* represents the reconstructed video frame and *O* is the original frame samples matrix.

$$MSE(x,y) = \sum_{i=0}^{h-1} \sum_{j=0}^{w-1} (R_{i,j} - O_{i,j})^2$$

(2)

$$PSNR = 10 \times \log_{10} \left( \frac{maxpixelvalue^2}{MSE} \right)$$

(3)

In the Equation (3), *maxpixelvalue* represents the highest representable value of a sample. Generally, most of the H.264/AVC profiles use 8-bit representation per sample. This way, the *maxpixelvalue* is adopted as 255 in this work.

## 2.5 Motion and Disparity Estimation

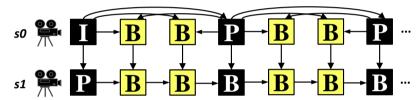

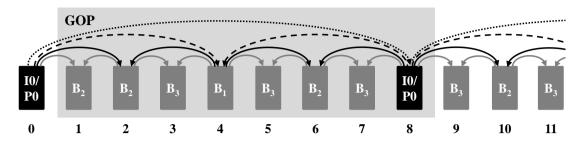

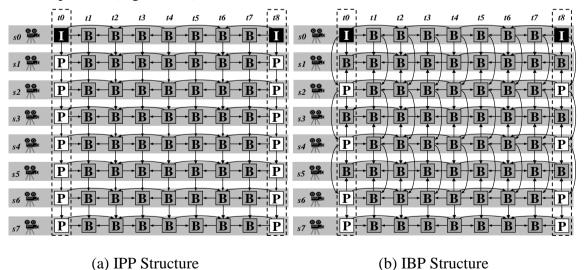

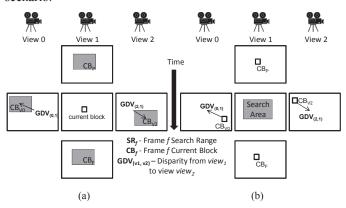

The Motion Estimation (ME) and Disparity Estimation (DE) are the main core of Inter-Frame and Inter-View Prediction steps in the MVC encoders. ME is responsible to deal with the temporal correlations of neighboring frames from the same view, while the DE perform the same task but for the disparity correlations of frames from different views. Figure 2.4 presents a simple prediction structure to introduce some concepts, where s0 and s1 represent the views, {I, P, B} are the frame types in according to the possible prediction modes for each frame (WIEGAND e SULLIVAN, 2011), and the arrows represent the temporal/disparity dependencies.

Figure 2.4: Illustration of inter-frame and inter-view prediction in MVC. (VETRO, WIEGAND e SULLIVAN, 2011)

Horizontal arrows (inside the same view) represent the ME operations. For instance, the frame s0t1 has two ME coding dependencies: frames s0t0 and s0t3. It means that these dependencies must be coded, reconstructed and stored on the reference frames memory before the frame s0t1 is started to be coded. On the other hand, the vertical arrows in Figure 2.4 represent the DE operations. For example, the frame s0t1 has both one ME dependency s0t1 and one DE dependency with the frame s1t0.

The next sections present the basic concepts involved in the ME/DE processing, along with MVC typical prediction structures that specifies the way that ME/DE are disposed for a given number of camera views.

#### 2.5.1 Basic Concepts

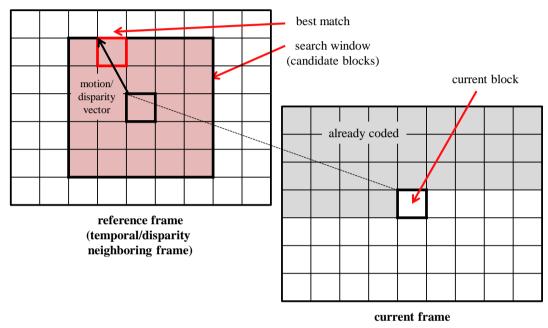

The basic concepts presented in this section are applied to both ME and DE processing flow. The conceptual difference between them is that ME exploits the temporal redundancies between neighbor frames in the same view, and DE processes frames in order to catch the camera disparity between frames of different views (generally captured in the same time instant). Figure 2.5 summarizes these concepts.

For each MB of the frame that is being processed (*current frame*), the ME/DE module is applied in according to the MVC encoder prediction structure. The goal is to find the *best match* of each block (called *current block*) of the current frame in one or more previously coded frames (called *reference frames*). The optimal best match corresponds to the block in the reference frames that provides the smallest possible rate-distortion cost in the final MVC encoding process. The optimal solution search is a very computation-intensive decision, since the entire MVC encoder process must be performed for all possible block matches in the reference frame (SULLIVAN e

WIEGAND, 1998). As a local decision, the block that minimizes the residual information (difference between the original MB and the predicted block) is always a very good candidate to be near to the optimal result (KUHN, 1999). Several low complexity metrics are used to measure the similarities between two blocks (they will be discussed on the Section 2.5.2). Using this metric, the current block is compared to blocks of the reference frame (called *candidate blocks*) and the most similar one is picked as the best match. As result, the ME/DE deliveries (1) a motion/disparity vector indicating the position of the best match and (2) a reference index that points to the specific reference frame that contains the best match (the search can be performed in more than one reference frame) (WIEGAND, SULLIVAN, *et al.*, 2003).

Figure 2.5: Motion and Disparity Estimation basic concepts.

Due to the high frame exhibition rate (30, 60 up to 120 frames per second), the best match tends to be found positions closed to the current MB. This way, the search on the entire frame blocks may represent so much effort since the best match is usually in the current MB neighborhood. This way, it is common to restrict the ME/DE search within a *search window*. Indeed, practically all ME/DE search algorithms use the search window to reduce the execution time and memory requirements (RICHARDSON, 2003). The DE has a different behavior, since the position displacement between each pair of camera is not guaranteed to be small and the best match may not be near the center of the search window. The H.264 MVC does not standardize a specific tool to deal with it, so larger search windows are required in the DE (at minimum 193x193 samples). Another standard-compliant solution is to use disparity vectors of previously MBs of the neighborhood to move the search window center to a more probable region for the best match. Moreover, several works evaluate the use of an external parameter, called Global Disparity Vector (GDV), which informs the average disparity between two view sequences (ZHEN, LIU, *et al.*, 2010).

The step after the ME/DE is the Motion and Disparity Compensation (MC/DC). In this task, the motion/disparity vector is used to access the reference frame memory to fetch the predicted block and, then, the MC/DC calculates the residual block and send it to the transforms and quantization.

The H.264/AVC standard inserted high complexity additional techniques to the ME/DE operation to improve the overall MVC encoder efficiency, like Variable Block Size (VBS-ME), quarter pixel precision and out-of-frame motion/disparity vector. These techniques will not be discussed because they are out of the scope of this work.

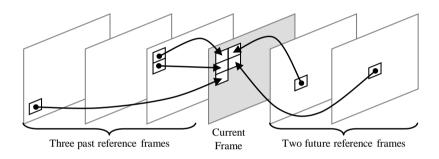

One important feature that is massively used in the MVC is the Multiple Reference Frames (MRF), where the ME/DE searches in more than one reference frame. The reference frames are organized in two lists (list 0 and list 1). Detailed description of the frame lists can be found in (WIEGAND, SULLIVAN, *et al.*, 2003). In the case of Figure 2.6, the same current frame is able to have references on five already coded reference frames (three past and two future frames, considering the exhibition order). It is massively exploited in the MVC encoders, since it is common to have past and future reference frames in the same view (processed by the ME) along with reference frames on the left and on the right camera view (encoded by the DE).

Figure 2.6: Multiple Reference Frame (MRF) example.

Another important concept is linked to the type of frames that ME/DE is able to be performed. The H.264/AVC standard classifies the frames of the multiview video in three different types (RICHARDSON, 2003).

- **I-Frame:** This type does not allow the ME/DE, since all MBs must be intra coded to not contain any encoding dependency with another frame. I-Frames are disposed in order to refresh the video dependencies to allow random access at certain points of the MVC decoding.

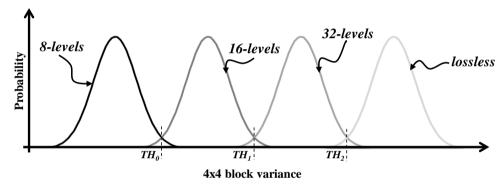

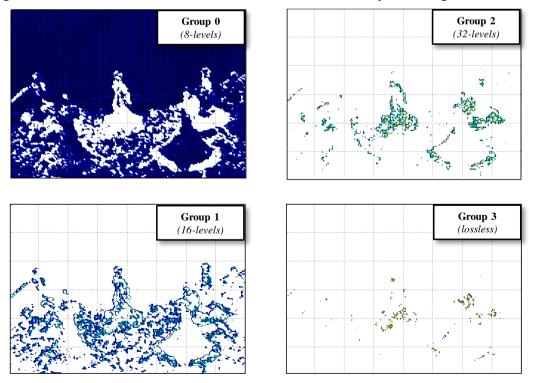

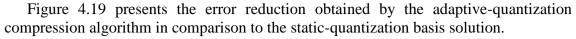

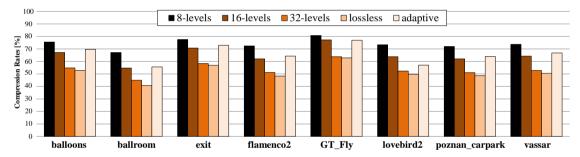

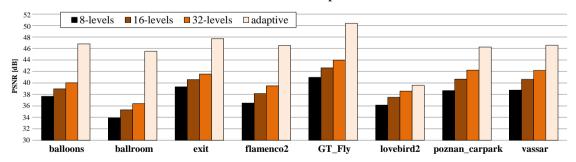

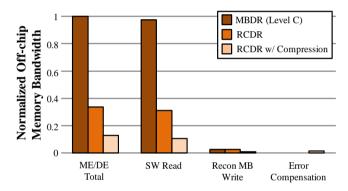

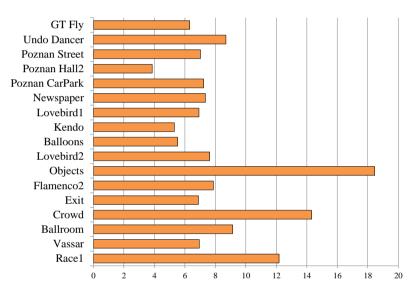

- **P-Frame**: This type allows the use at maximum one temporal/disparity reference for each MB. It means that the ME/DE is required for this type and, even searching in multiple reference frames, only one motion/disparity vector is generated for each MB or partitions/sub-partitions. Besides, the MBs of this frame type can also be intra coded.