# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA - PGMICRO

#### FÁBIO FEDRIZZI VIDOR

### Study of the Hysteretic Behavior in ZnO Nanoparticle Thin-Film Transistors

Thesis presented in partial fulfillment of requirements for the degree of Master in Microelectronics

Prof. Dr.-Ing. Gilson I. Wirth Advisor

#### CIP – CATALOGAÇÃO NA PUBLICAÇÃO

Vidor, Fábio Fedrizzi

Study of the Hysteretic Behavior in ZnO Nanoparticle Thin-Film / Fábio Fedrizzi Vidor – Porto Alegre: Programa de Pós-Graduação em Microeletrônica, 2012.

121 f.:il.

Thesis (Master) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica. Porto Alegre, BR – RS, 2012. Advisor: Gilson I. With.

1. Nanoparticles. 2. ZnO. 3. Thin-film transistors. 4. Low-cost electronics. I. Wirth, Gilson I.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos Alexandre Netto

Vice-Reitor: Prof. Rui Vicente Oppermann

Pró-Reitor de Pós-Graduação: Prof. Aldo Bolten Lucion Diretor do Instituto de Informática: Prof. Flávio Rech Wagner

Coordenador do PGMICRO: Prof. Ricardo Reis

Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

#### **ACKNOWLEDGMENT**

I extend my sincere thanks to Prof. Dr.-Ing. Gilson I. Wirth, Prof. Dr.-Ing. Ulrich Hilleringmann and M.Sc Fabian Assion for their directions and support throughout my work. Their guidance and continuous flow of ideas and critical suggestions made the elaboration of this work possible. I also thank Thiago Hanna Both for his careful reading of this work and suggestions during the research. The excellent working environment and support of LaProt from UFRGS - Federal University of Rio Grande do Sul and Group Sensorik from University Paderborn are deeply appreciated.

I would like to express my gratitude to my friends from Brazil and Germany for their friendship over the years. Furthermore, I would like to thank the Federal University of Rio Grande do Sul for the free and high quality education.

This work is dedicated to my family and my wife, Jéssica, whose love and support have been a continual inspiration.

At the end, I would like to thank CAPES for the financial support that makes this work possible.

# TABLE OF CONTENTS

| LIST OF SYMBOLS                                            | 6  |

|------------------------------------------------------------|----|

| LIST OF ABREVIATIONS AND ACRONYMS                          | 8  |

| LIST OF FIGURES                                            | 9  |

| LIST OF TABLES                                             | 13 |

| ABSTRACT                                                   | 14 |

| RESUMO                                                     | 15 |

| 1 INTRODUCTION                                             | 16 |

| 2 METAL-SEMICONDUCTOR CONTACTS (SCHOTTKY JUNCTIONS)        | 18 |

| 2.2 Energy Scales                                          | 18 |

| 2.3 Metal-Semiconductor Contact                            | 20 |

| 3 ZINC OXIDE AND GATE DIELECTRIC POLYMER                   | 25 |

| 3.1 Zinc Oxide Properties                                  | 25 |

| 3.2 Zinc Oxide Nanoparticles                               | 26 |

| 3.3 PVP Properties                                         |    |

| 4 ZINC OXIDE THIN-FILM TRANSISTOR                          | 30 |

| 4.1 Thin-Film Transistor Properties                        | 30 |

| 4.2 ZnO Thin-Film Transistor                               | 35 |

| 4.2.1 TFT in our group                                     |    |

| 4.2.2 ZnO TFT by other research groups.                    |    |

| 4.2.3 Transport of current in nanoparticulate ZnO          |    |

| 4.3 Transistor Integration Using Polymeric Gate Dielectric |    |

| 4.3.1 Wafer Preparation                                    |    |

| 4.3.3 Dielectric and Semiconductor Layer Integration       |    |

| 4.3.4 Vias                                                 |    |

| 4.3.5 Drain and Source Electrode Integration               |    |

| 4.3.6 Optical Transparency                                 |    |

| 4.3.7 Integration Difficulties                             | 62 |

| 4.4 Transistor with Silicon Dioxide as Gate Dielectric                   |  |

|--------------------------------------------------------------------------|--|

| 4.5 Transistor Characterization69                                        |  |

| 5 RESULTS AND DISCUSSIONS71                                              |  |

| 5.1 Hysteresis Studies71                                                 |  |

| 5.2 Results                                                              |  |

| 6 CONCLUSION 90                                                          |  |

| 7 FUTURE WORKS91                                                         |  |

| PUBLICATIONS BY THE AUTHOR92                                             |  |

| REFERENCES93                                                             |  |

| APPENDIX A CLEANING PROCESSES 101                                        |  |

| APPENDIX B MEASUREMENT METHODS102                                        |  |

| APPENDIX C GRAPHICS AND TABLES107                                        |  |

| APPENDIX D SUMMARY IN PORTUGUESE (RESUMO EM PORTUGUÊS DA DISSERTAÇÃO)117 |  |

#### LIST OF SYMBOLS

$C_{ins}$  Gate capacitance

E Energy

$\vec{E}$  Electric Field

$E_C$  Minimum conduction band energy

$E_F$  Fermi level

$E_{FM}$  Metal Fermi level

$E_{FS}$  Semiconductor Fermi level

$E_V$  Maximum valence band energy

$E_{VAC}$  Vacuum level

$g_m$  Transistor transconductance

$I_D$  Drain current  $I_G$  Gate current

$I_{loc}$  Local current

L Transistor length

*K<sub>B</sub>* Boltzmann's constant

q Electron charge

Sub-threshold slope voltage

T Absolute temperature

$t_{ins}$  Gate dielectric thickness

$t_{ox}$  Gate oxide thickness

$V_{DS}$ ,  $V_D$  Drain-source voltage

$V_F$  Forward voltage

$V_{GS}$ ,  $V_G$  Gate-source voltage

$V_R$  Reverse voltage

$V_T$  Threshold voltage

*x* Position

W Transistor width

$W_{\omega B}$  Metal-semiconductor barrier width

$W_F$  Metal-semiconductor barrier width under forward bias

$W_0$  Metal-semiconductor barrier width at thermal equilibrium

$W_R$  Metal-semiconductor barrier width under reverse bias

$\Delta \varphi_{BF}$  Variation of barrier height under forward bias  $\Delta \varphi_{BR}$  Variation of barrier height under reverse bias

*μ* Carrier mobility

$\mu_{FE}$  Field-effect mobility

$\chi$  Electron affinity  $\varphi$  Work function

$\varphi_B$  Barrier height from the metal to the semiconductor

$\varphi_{Bo}$  Intrinsic barrier height at thermal equilibrium  $\varphi_{Bn}$  Barrier height considering the Schottky effect

$\varphi_i$  Barrier height from the semiconductor to the metal

$\varphi_M$  Metal work function

$\varphi_S$  Semiconductor work function

#### LIST OF ABREVIATIONS AND ACRONYMS

ALD Atomic layer deposition

ATO Antimony tin oxide

FET Field effect transistor

GZO Gallium doped zinc oxide

ITO Indium tin oxide

HDMS Bis(trimethylsilyl)amine – an adhesion promoter

MISFET Metal insulator semiconductor field effect transistor

MOSFET Metal oxide semiconductor field effect transistor

MS Metal-semiconductor junction

NBTI Negative bias temperature instability

NMP N-Methyl-2-pyrrolidone

PECVD Plasma enhanced chemical vapor deposition

PEN Polyethylene Naphthalate – a polymer

PES Polyethersulfone – a polymer

PGMEA Propylene glycol monomethyl ether acetate – a solvent

PI Polyimide – a polymer

PMCF-m Poly(melamine-co-formaldehyde)-methylated – cross-linker agent

PVP Poly(4-vinylphenol) – a polymer

RF Radio Frequency

RIE Reactive ion etching

RDF Random dopant fluctuations

RTS Random telegraph signal

SEM Scanning electron microscope

TFT Thin-film transistor

UFRGS Universidade Federal do Rio Grande do Sul

## LIST OF FIGURES

| Figure 1.1: Application of transparent and flexible electronics                             |

|---------------------------------------------------------------------------------------------|

| Figure 2.1: Fermi-Dirac distribution for $T = 0$ $K$ and $T > 0$ $K$                        |

| Figure 2.2: Energy plotted as function of position, before the contact between metal and    |

| semiconductor. The work function of the metal is higher than that of the n-type             |

| semiconductor                                                                               |

| Figure 2.3: Energy-band diagram in metal on n-type semiconductor in thermal                 |

| equilibrium. qoB denotes the barrier height from the metal to the semiconductor and qoi     |

| the barrier height from the semiconductor to the metal                                      |

| Figure 2.4: Energy-band diagram in metal on n-type semiconductor under (a) forward          |

| bias and (b) reverse bias                                                                   |

| Figure 2.5: Metal-Semiconductor barrier including the Schottky effect under different       |

| bias conditions                                                                             |

| Figure 2.6: Transport process in a forward-biased Schottky barrier                          |

| Figure 2.7: Detail of the barrier width variation under different electrical bias 24        |

| Figure 3.1: ZnO's chemical structure. One unit cell is outlined for clarity                 |

| Figure 3.2: Various ZnO nanostructures                                                      |

| Figure 3.3: Chemical structures of polymeric dielectrics used in this work. (a) Pure        |

| PVP, (b) cross linker agent and (c) a cross-linked PVP chemical structure28                 |

| Figure 4.1: Simplified schematic of a TFT structure                                         |

| Figure 4.2: Schematic illustration of the central elements of TFT operation                 |

| Figure 4.3: Energy band diagram as views through the gate for (a) equilibrium, (b)          |

| depletion ( $V_{GS} < 0 V$ ), and (c) accumulation ( $V_{GS} > 0 V$ )                       |

| Figure 4.4: Band diagrams along semiconductor surface under various biases 33               |

| Figure 4.5: Four general thin-film transistor configurations, including: (a) staggered      |

| bottom-gate, (b) coplanar bottom-gate, (c) staggered top-gate and (d) coplanar top-gate.    |

|                                                                                             |

| Figure 4.6: Schematic layout of a TFT structure (gate electrode and gate dielectric         |

| layers are not shown explicitly here), in which (a) the channel layer is patterned, and (b) |

| the channel layer is unpatterned. The current is represented by arrows                      |

| Figure 4.7: Integrated TFT using oxidized doped silicon as gate structure                   |

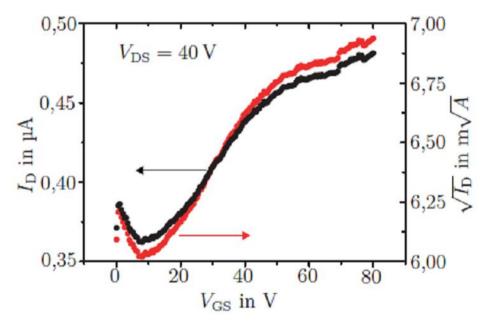

| Figure 4.8: Transfer characteristics of the silicon nanoparticle transistor with $t_{ox}$ = |

| $200 \ nm, L = 8 \ \mu m \text{ and } W = 16.000 \ \mu m.$ 36                               |

| Figure 4.9: Schematic view of a silicon single particle FET with inverted coplanar          |

| setup                                                                                       |

| Figure 4.10: Transfer curve of a Si nanoparticle FET with $L=60nm$ and $W=$                 |

| $100 \ \mu m, t_{ox} = 15 \ nm$ after thermal treatment at $300^{\circ}$ C                  |

| Figure 4.11: Characteristics of a thin film zinc oxide nanoparticle FET in inverted         |

| coplanar setup, $L=8~\mu m, W=16.000~\mu m$ and $t_{ox}=300~nm$ 39                          |

| Figure 4.12: Characteristics of a thin film zinc oxide nanoparticle FET in inverted            |

|------------------------------------------------------------------------------------------------|

| staggered setup, $L=8 \mu m$ , $W=16.000 \mu m$ and $t_{ox}=53 nm$                             |

| Figure 4.13: One particle zinc oxide FET in inverted coplanar setup, $L = 80  nm$ ,            |

| $W = 100 \ \mu m$ (metal structure), $t_{ox} = 31 \ nm$                                        |

| Figure 4.14: Characteristics of the zinc oxide nanoparticle film transistor integrated on      |

| glass, $L = 3 \mu m$ , $W = 1000 \mu m$ , $t_{ins} = 180 nm$                                   |

| Figure 4.15: (a) 3D-graph, schematic and (b) optical micrograph of the presented               |

| inverter circuit                                                                               |

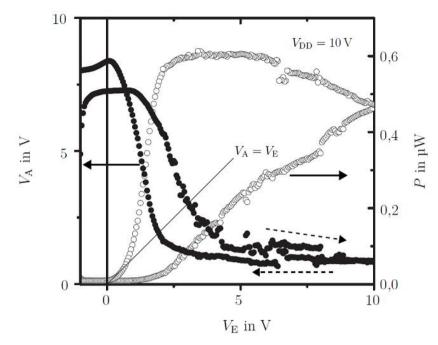

| Figure 4.16: Transfer characteristic and power consumption of the zinc oxide                   |

| nanoparticle inverter integrated on oxidized silicon substrates                                |

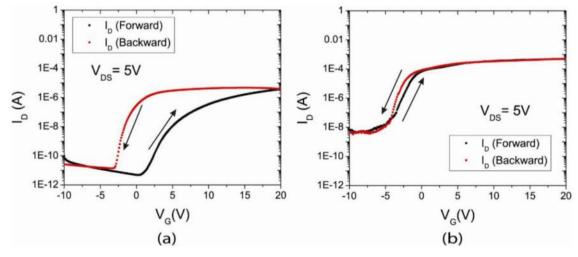

| Figure 4.17: Transfer characteristics of (a) ZnO nanoparticle TFT with Al-S/D-contact          |

| (b) ZnO nanoparticle with zinc acetate TFT and Al-S/D-contact                                  |

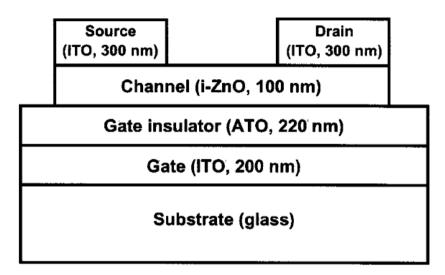

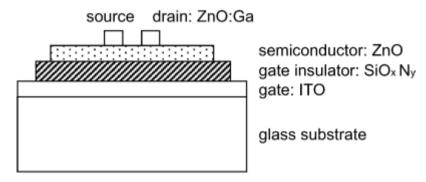

| Figure 4.18: Transparent ZnO based TFT integrated by Hoffman et al                             |

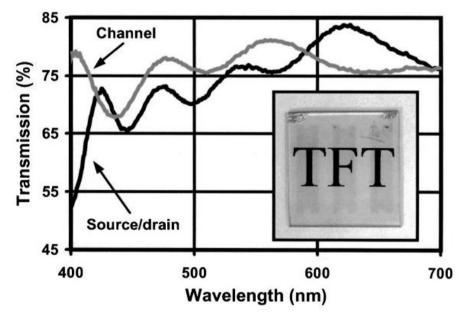

| Figure 4.19: The optical transmission spectra for the entire transparent TFT structure,        |

| including the substrate. 46                                                                    |

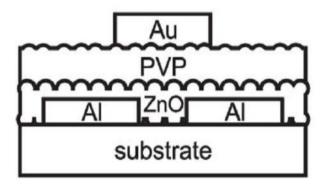

| Figure 4.20: High performance ZnO TFT integrated by Fortunato et al                            |

| Figure 4.21: Transfer characteristic and gate leakage for ZnO TFT $(W/L = 5)$ and              |

| optical transmission spectra of the entire ZnO TFT with its photograph on the corner. 47       |

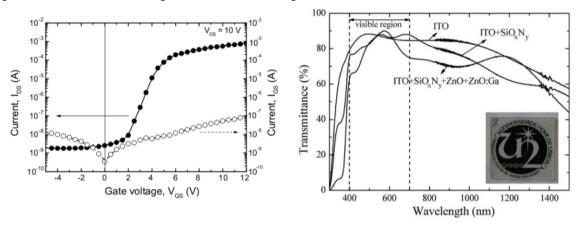

| Figure 4.22: Schematic cross-section of the ZnO nanoparticle TFT integrated by Faber           |

| et al                                                                                          |

| Figure 4.23: Transfer characteristic of a ZnO nanoparticle TFT with representative             |

| trapping mechanism                                                                             |

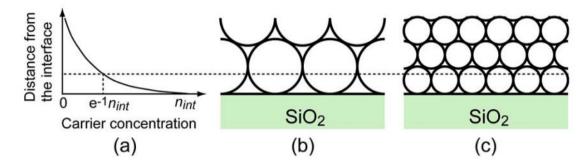

| Figure 4.24: Magnified schematics at the interface of nanoparticulate FETs, under the          |

| condition of the carrier accumulation. (a) The carrier concentration depending on the          |

| distance from the interface in FETs. N <sub>int</sub> denotes the carrier concentration at the |

| interface. (b) A rough interface with big agglomerates results in low mobility. (c) A          |

| smooth interface with small agglomerates leads to high mobility                                |

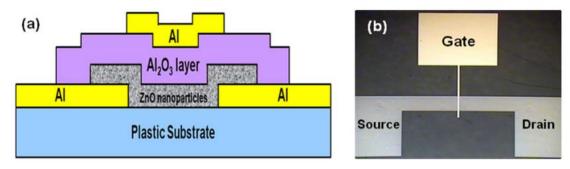

| Figure 4.25: (a) Cross-sectional schematic of a top-gate ZnO TFT and (b) an optical            |

| image of the fabricated TFT                                                                    |

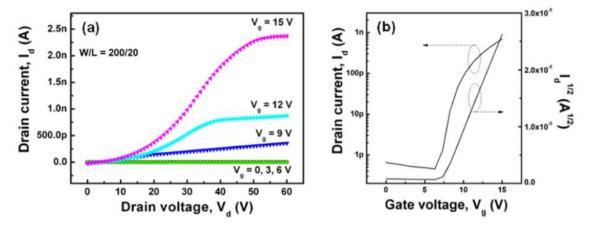

| Figure 4.26: (a) Output and (b) transfer characteristics of the fabricated TFT with a          |

| channel layer composed of solution-processed ZnO nanoparticles in the flat state 52            |

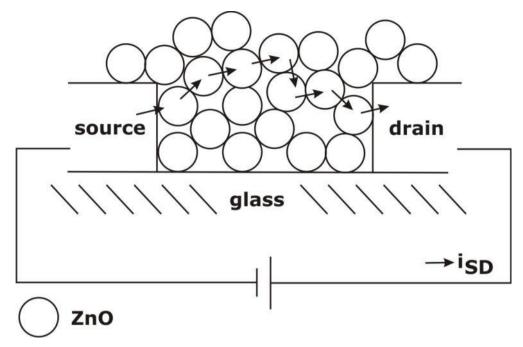

| Figure 4.27: Schematic picture of the electrode geometry used to investigate the               |

| transport in ZnO nanoparticles                                                                 |

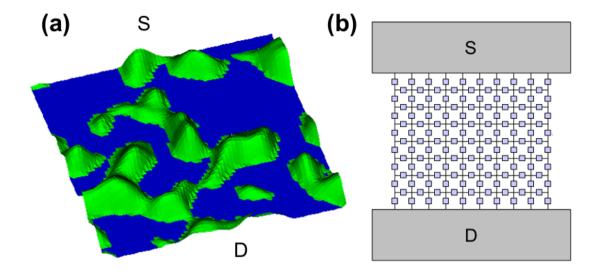

| Figure 4.28: (a) An illustration of a percolation path as result of random dopant              |

| fluctuation and (b) a resistor network representing the conduction in the transistor 54        |

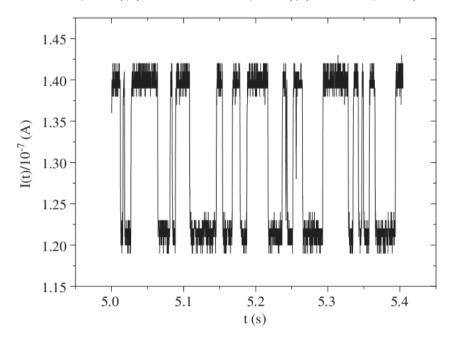

| Figure 4.29: Discrete current fluctuations correspond to capture and emission of an            |

| electron by a particular trap                                                                  |

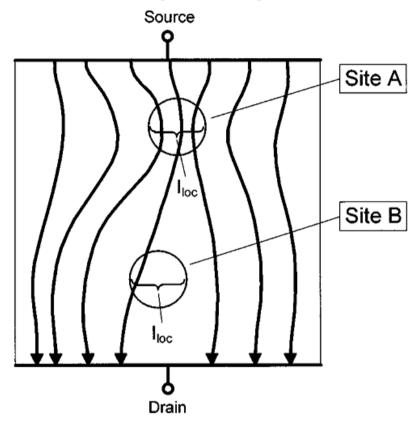

| Figure 4.30: Schematic drawing of the current flow lines in a non-uniform channel. A           |

| trap switching at location A will cause a larger RTS amplitude than the one at location        |

| B. I <sub>loc</sub> denotes local current                                                      |

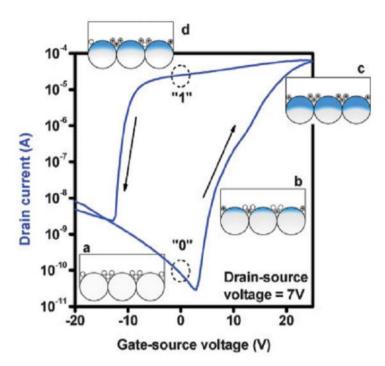

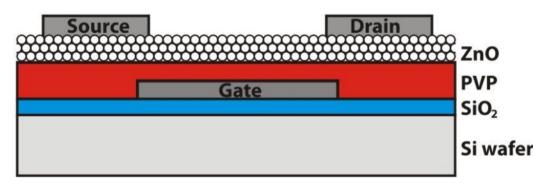

| Figure 4.31: Schematic cross-section of ZnO nanoparticle TFT with PVP as gate                  |

| dielectric                                                                                     |

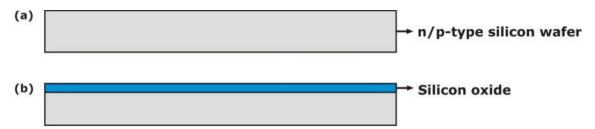

| Figure 4.32: Cross section of the wafer with silicon oxide                                     |

| Figure 4.33: Cross-section of the wafer representing the gate integration 58                   |

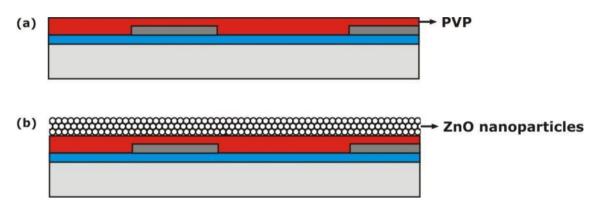

| Figure 4.34: Cross section of the wafer representing the dielectric and semiconductor          |

| layers integration                                                                             |

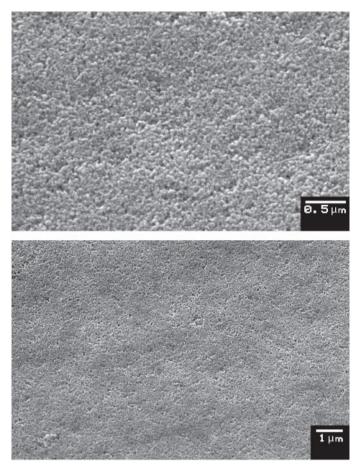

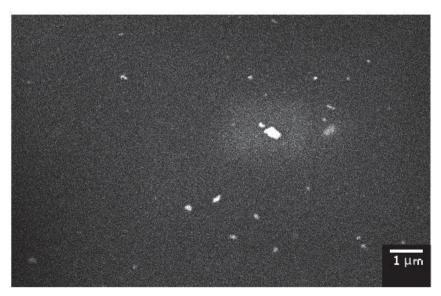

| Figure 4.35: SEM micrographs of ZnO nanoparticle layer                                         |

| Figure 4.36: Cross section of the wafer representing the vias and drain/source electrodes      |

| integration                                                                                    |

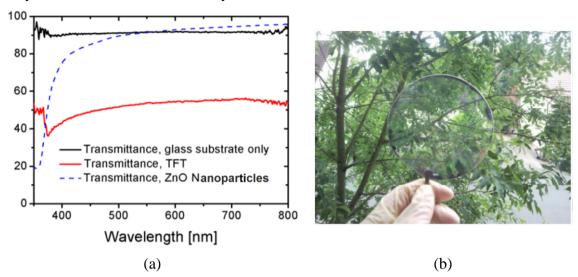

| Figure 4.37: (a) Optical transmittance of the glass substrate, TFT and Z                                                                                                 | ĽnO                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| nanoparticles, and (b) Samples on a glass substrate                                                                                                                      | . 62                                                                                                                                                                 |

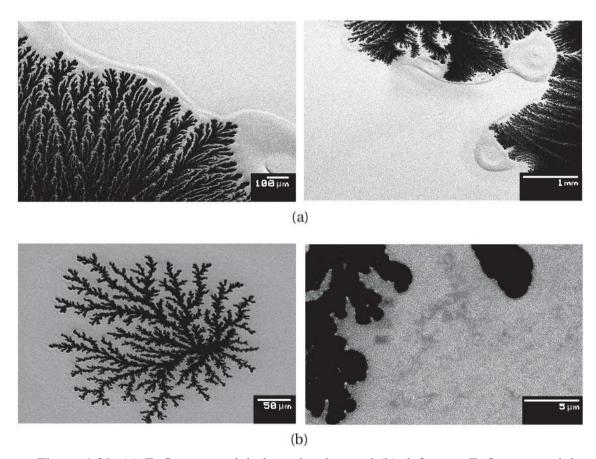

| Figure 4.38: ZnO agglomerated nanoparticles on a PVP layer (in detail)                                                                                                   |                                                                                                                                                                      |

| Figure 4.39: (a) ZnO nanoparticle layer border; and (b) defect on ZnO nanopart                                                                                           | icle                                                                                                                                                                 |

| layer (in detail)                                                                                                                                                        | . 63                                                                                                                                                                 |

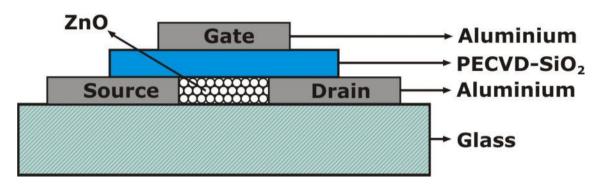

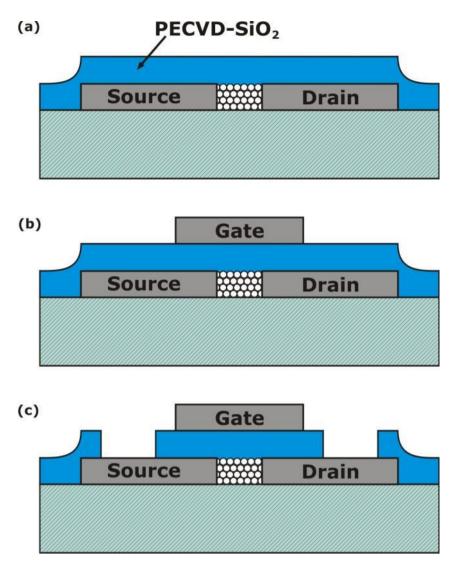

| Figure 4.40: Schematic cross-section of ZnO nanoparticle TFT with PECVD-SiO                                                                                              | 2 as                                                                                                                                                                 |

| gate dielectric                                                                                                                                                          |                                                                                                                                                                      |

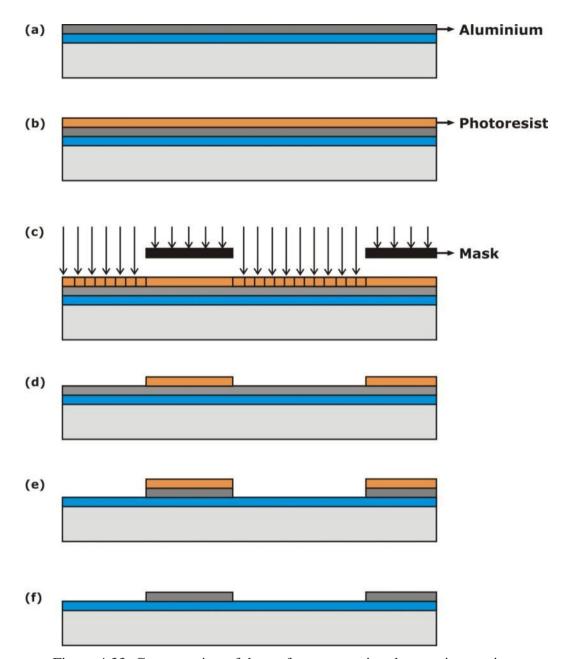

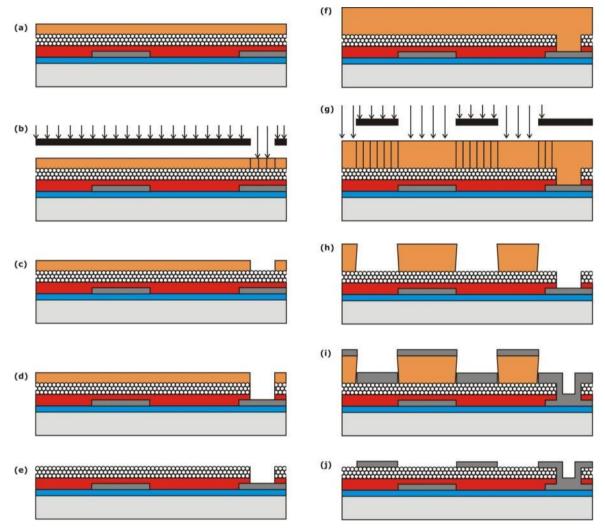

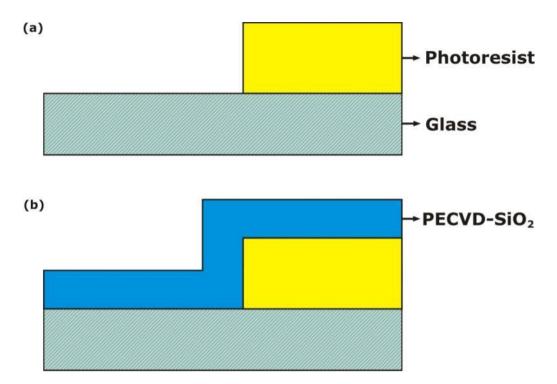

| Figure 4.41: Part of the integration process of the TFT with SiO <sub>2</sub> as gate dielectric                                                                         | . 65                                                                                                                                                                 |

| Figure 4.42: Part of the integration process of the TFT with SiO <sub>2</sub> as gate dielectric                                                                         |                                                                                                                                                                      |

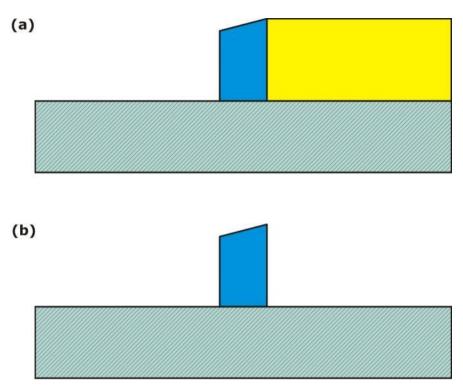

| Figure 4.43: Part of the integration process of the TFT with SiO <sub>2</sub> as gate dielectric                                                                         | . 67                                                                                                                                                                 |

| Figure 4.44: Part of the integration process of the TFT with SiO <sub>2</sub> as gate dielectric                                                                         | . 68                                                                                                                                                                 |

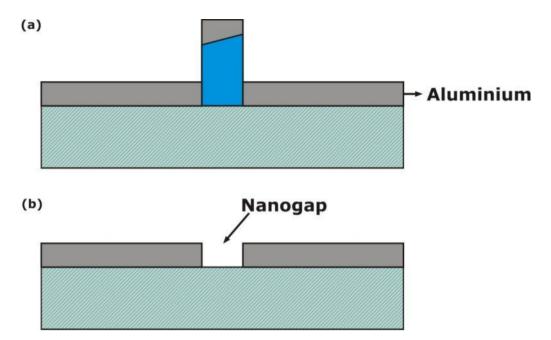

| Figure 4.45: Part of the integration process of the TFT with SiO <sub>2</sub> as gate dielectric                                                                         | . 69                                                                                                                                                                 |

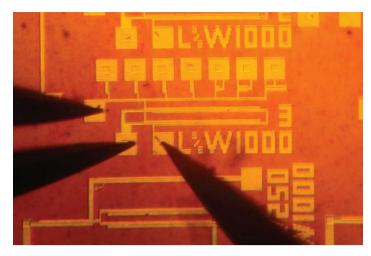

| Figure 4.46: Probes used in the characterization process (detail).                                                                                                       |                                                                                                                                                                      |

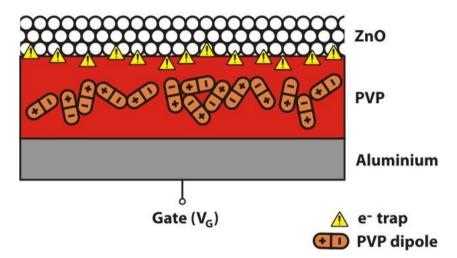

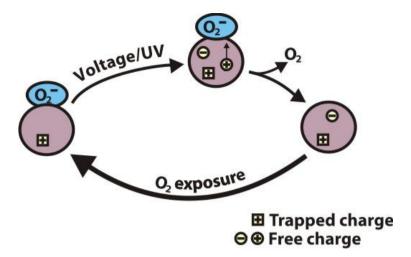

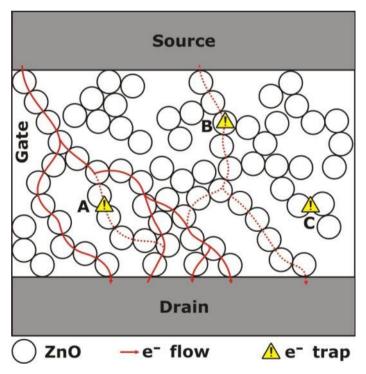

| Figure 5.1: Trap mechanism in ZnO nanoparticle TFT with PVP as gate dielectric                                                                                           |                                                                                                                                                                      |

| Figure 5.2: Oxygen trap mechanism in nanoparticulate ZnO.                                                                                                                |                                                                                                                                                                      |

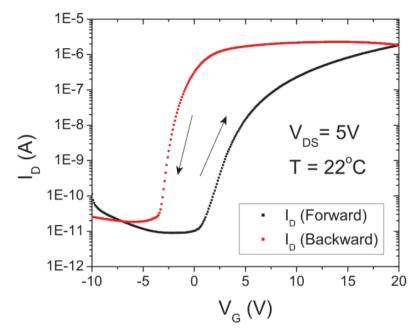

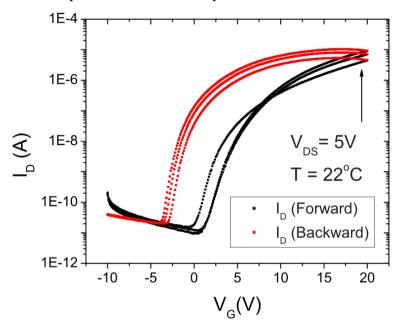

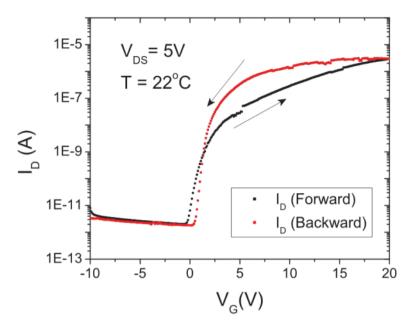

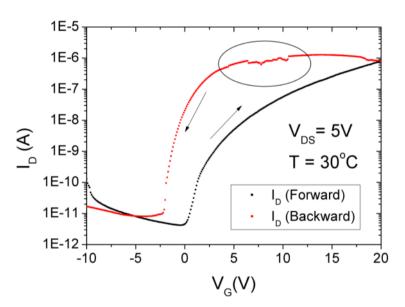

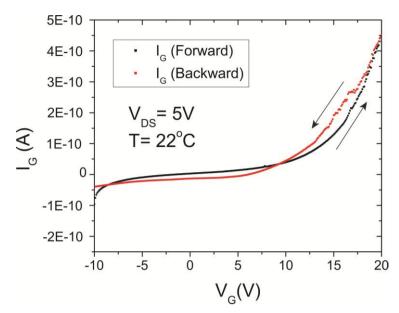

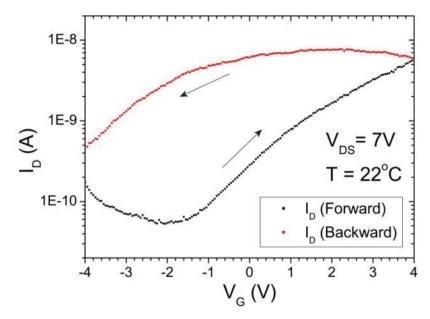

| Figure 5.3: ZnO nanoparticle TFT transfer characteristic at room temperature (M                                                                                          |                                                                                                                                                                      |

| $1000 \ \mu m$ , $L = 3/2 \ \mu m$ , Sweep Rate = $2 \ V/s$ )                                                                                                            |                                                                                                                                                                      |

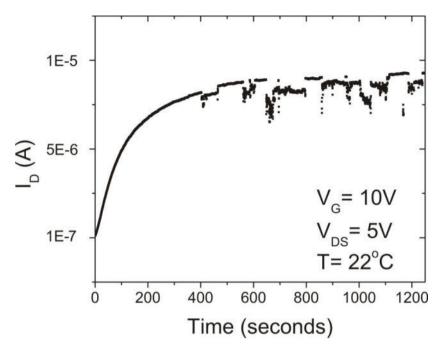

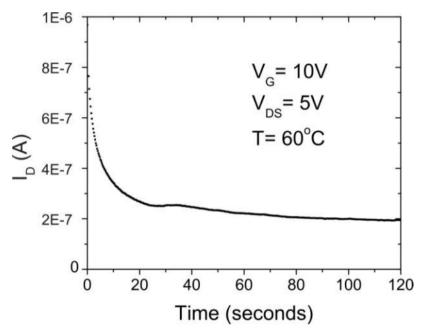

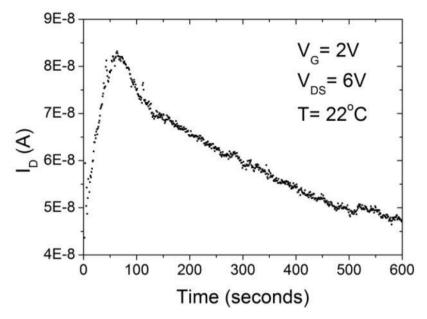

| Figure 5.4: Stress test at room temperature in a ZnO nanoparticle TFT ( $W = 1000  \mu$ )                                                                                |                                                                                                                                                                      |

| $L = 3/2 \ \mu m$ , $V_G = 10 \ V$ , $V_D = 5 \ V$ )                                                                                                                     |                                                                                                                                                                      |

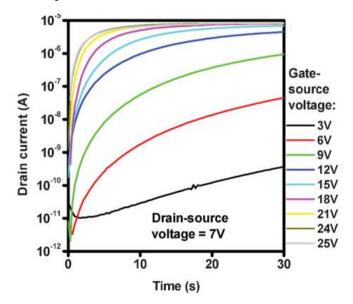

| Figure 5.5: Time-dependent response of the drain current to the application of a position $\frac{1}{2}$                                                                  |                                                                                                                                                                      |

| gate-source voltage, showing that the response is more rapid for larger gate-source                                                                                      |                                                                                                                                                                      |

| voltages                                                                                                                                                                 |                                                                                                                                                                      |

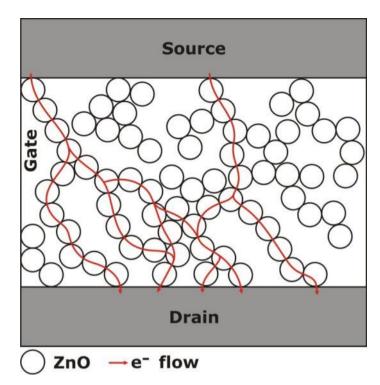

| Figure 5.6: Electron flow in a nanoparticulate ZnO film.                                                                                                                 |                                                                                                                                                                      |

| Figure 5.7: Electron flow in a nanoparticulate ZnO film under effect of active traps                                                                                     |                                                                                                                                                                      |

|                                                                                                                                                                          |                                                                                                                                                                      |

| Highre 3 X. Millitude electrical characterization on Intl hanoparticle LHT at ro                                                                                         | n                                                                                                                                                                    |

| Figure 5.8: Multiple electrical characterization on ZnO nanoparticle TFT at rotemperature $(W = 1000 \text{ mm}  I = 3/2 \text{ mm} \text{ Sweep Rate} = 2 \text{ V/s})$ |                                                                                                                                                                      |

| temperature ( $W=1000~\mu m, L=3/2~\mu m$ , Sweep Rate = $2~V/s$ )                                                                                                       | . 78                                                                                                                                                                 |

| temperature ( $W = 1000 \ \mu m$ , $L = 3/2 \ \mu m$ , Sweep Rate = $2 \ V/s$ )                                                                                          | . 78<br>vith                                                                                                                                                         |

| temperature ( $W=1000~\mu m, L=3/2~\mu m$ , Sweep Rate = $2~V/s$ )                                                                                                       | . 78<br>vith<br>. 79                                                                                                                                                 |

| temperature ( $W=1000~\mu m, L=3/2~\mu m$ , Sweep Rate = $2~V/s$ )                                                                                                       | . 78<br>with<br>. 79<br>um,                                                                                                                                          |

| temperature ( $W=1000~\mu m, L=3/2~\mu m$ , Sweep Rate = $2~V/s$ )                                                                                                       | . 78<br>with<br>. 79<br>um,<br>. 79                                                                                                                                  |

| temperature ( $W=1000~\mu m, L=3/2~\mu m$ , Sweep Rate = $2~V/s$ )                                                                                                       | . 78 with . 79 um, . 79                                                                                                                                              |

| temperature ( $W=1000~\mu m, L=3/2~\mu m$ , Sweep Rate = $2~V/s$ )                                                                                                       | . 78<br>with<br>. 79<br>um,<br>. 79<br>V =                                                                                                                           |

| temperature ( $W=1000~\mu m, L=3/2~\mu m$ , Sweep Rate = $2~V/s$ )                                                                                                       | . 78 with . 79 um, . 79 V = . 80 L =                                                                                                                                 |

| temperature ( $W=1000~\mu m, L=3/2~\mu m$ , Sweep Rate = $2~V/s$ )                                                                                                       | . 78 with . 79 um, . 79 $V = 0.80$ L = . 81                                                                                                                          |

| temperature ( $W=1000~\mu m, L=3/2~\mu m$ , Sweep Rate = $2~V/s$ )                                                                                                       | . 78<br>with<br>. 79<br>um,<br>. 79<br>V =<br>. 80<br>L =<br>. 81<br>um,                                                                                             |

| temperature ( $W=1000~\mu m, L=3/2~\mu m$ , Sweep Rate = $2~V/s$ )                                                                                                       | . 78 with . 79 um, . 79 $V = 0.80$ . 81 um, . 82                                                                                                                     |

| temperature ( $W=1000~\mu m, L=3/2~\mu m$ , Sweep Rate = $2~V/s$ )                                                                                                       | . 78 with . 79 um, . 79 \( \text{\text{\$\text{\$}}} = . 80 \) \( \text{\$\text{\$\$}} = . 81 \) \( \text{\$\text{\$}} = . 82 \) \( \text{\$\text{\$}} = . 1 \)      |

| temperature ( $W=1000~\mu m, L=3/2~\mu m$ , Sweep Rate = $2~V/s$ )                                                                                                       | . 78 with . 79 um, . 79 $V = 0.80$ . 80 $L = 0.81$ . 82 $L = 0.82$ . 82                                                                                              |

| temperature ( $W=1000~\mu m, L=3/2~\mu m$ , Sweep Rate = $2~V/s$ )                                                                                                       | . 78 with . 79 um, . 79 $V = 0.80$ . 81 um, . 82 $V = 0.82$ . 82 CFT                                                                                                 |

| temperature ( $W=1000~\mu m, L=3/2~\mu m$ , Sweep Rate = $2~V/s$ )                                                                                                       | . 78 with . 79 um, . 79 \( \text{\colored} = \text{. 80} \) L = . 81 \( \text{\colored} = \text{. 82} \) L = . 82 \( \text{CFT} \) . 83                              |

| temperature ( $W=1000~\mu m, L=3/2~\mu m$ , Sweep Rate = $2~V/s$ )                                                                                                       | . 78 with . 79 um, . 79 \( \text{\colored} = \text{. 80} \) L = . 81 \( \text{\colored} = \text{. 82} \) L = . 82 \( \text{CFT} \) . 83                              |

| temperature ( $W=1000~\mu m, L=3/2~\mu m$ , Sweep Rate = $2~V/s$ )                                                                                                       | . 78 with . 79 um, . 79 \( \text{\chi} = 80 \) \( L = \text{. 81} \) \( \text{\chi} = \text{. 82} \) \( \text{\chi} = \text{. 83} \) \( \text{\chi} = \text{. 83} \) |

| temperature ( $W=1000~\mu m, L=3/2~\mu m$ , Sweep Rate = $2~V/s$ )                                                                                                       | . 78 with . 79 um, . 79 . 80 L = . 81 um, . 82 L = . 82 TFT . 83 V = . 84                                                                                            |

| temperature ( $W=1000~\mu m$ , $L=3/2~\mu m$ , Sweep Rate = $2~V/s$ )                                                                                                    | . 78 with . 79 um, . 79 \( \text{\chi} = 80 \) L = . 81 um, . 82 L = . 82 TFT . 83 \( \text{\chi} = . 84 \) icle                                                     |

| temperature ( $W=1000~\mu m, L=3/2~\mu m$ , Sweep Rate = $2~V/s$ )                                                                                                       | . 78 with . 79 um, . 79 \( \text{\colored} = . 80 \) \( L = \text{.} 81 \) \( \text{.} 82 \) \( \text{\colored} = . 83 \) \( \text{\colored} = . 84 \) icle . 85     |

| temperature ( $W=1000~\mu m$ , $L=3/2~\mu m$ , Sweep Rate = $2~V/s$ )                                                                                                    | . 78 with . 79 $\mu$ m, . 79 $\mu$ = . 80 $\mu$ = . 81 $\mu$ m, . 82 $\mu$ = . 83 $\mu$ = . 84 $\mu$ = . 85 gate . 86                                                |

| temperature ( $W=1000~\mu m$ , $L=3/2~\mu m$ , Sweep Rate = $2~V/s$ )                                                                                                    | . 78 with . 79 $\mu$ m, . 79 $\mu$ = . 80 $\mu$ = . 81 $\mu$ m, . 82 $\mu$ = . 83 $\mu$ = . 84 $\mu$ = . 85 gate . 86                                                |

| Figure 5.20: Output characteristic of ZnO nanoparticle TFT with SiO <sub>2</sub> as gate dielectric        |

|------------------------------------------------------------------------------------------------------------|

| at room temperature ( $W = 100 \ \mu m, L = 300 \ nm$ , Sweep Rate = $2 \ V/s$ )                           |

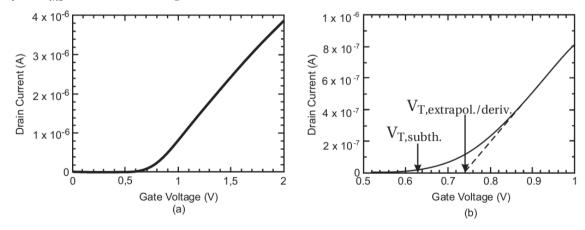

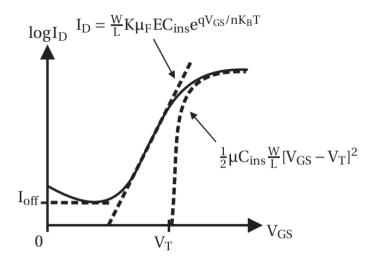

| Figure B.1: (a) $I_D - V_{GS}$ curve of a MOSFET near the threshold voltage; (b) enlarged                  |

| zoom-in of (a)                                                                                             |

| Figure B.2: Transfer characteristic of a MOSFET exhibiting an exponential dependence                       |

| below V <sub>T</sub> . As V <sub>GS</sub> is later reduced, the exponential characteristic merges with the |

| leakage current                                                                                            |

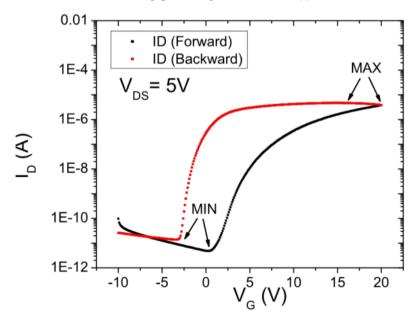

| Figure B.3: The maximum and the minimum drain current of a ZnO nanoparticle TFT                            |

| in a semi-log scale                                                                                        |

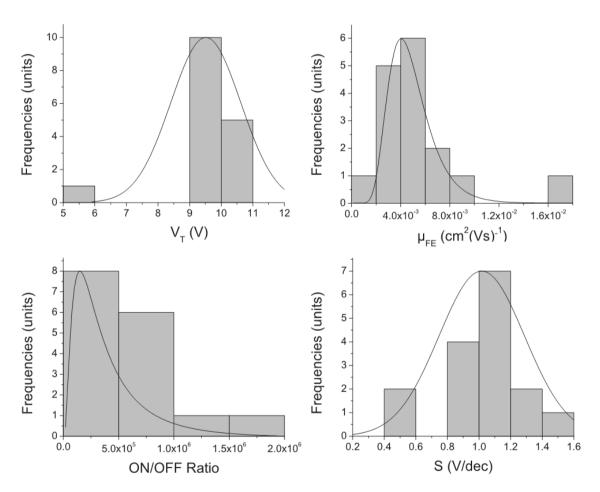

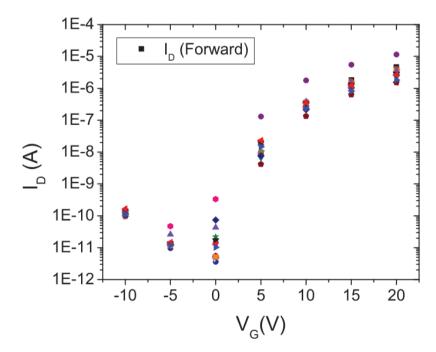

| Figure C.1: Distribution of the 'forward' characteristics of ZnO nanoparticle TFT                          |

| $(W = 1000 \ \mu m \text{ and } L = 3/2 \ \mu m).$ 107                                                     |

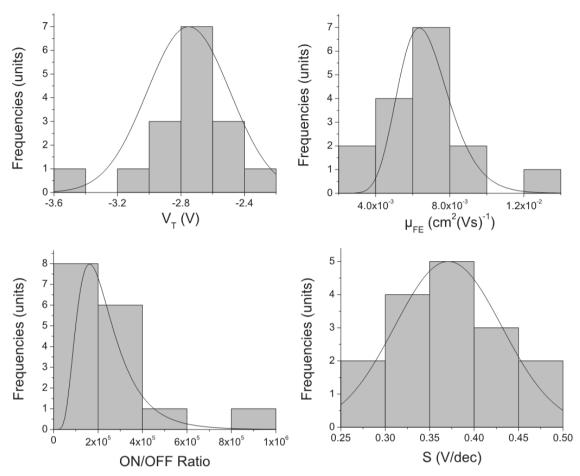

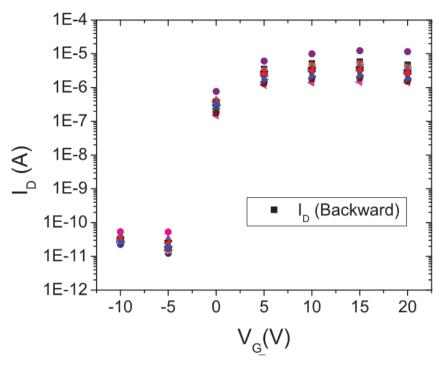

| Figure C.2: Distribution of the 'backward' characteristics of ZnO nanoparticle TFT                         |

| $(W = 1000 \ \mu m \text{ and } L = 3/2 \ \mu m).$ 108                                                     |

| Figure C.3: Current level over samples of ZnO nanoparticle TFT ( $W = 1000  \mu m$ and                     |

| $L = 3/2 \mu m$ ) while sweeping the gate voltage forwards                                                 |

| Figure C.4: Current level over samples of ZnO nanoparticle TFT ( $W = 1000  \mu m$ and                     |

| $L = 3/2 \mu m$ ) while sweeping the gate voltage backwards                                                |

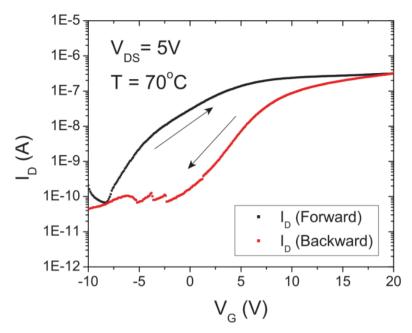

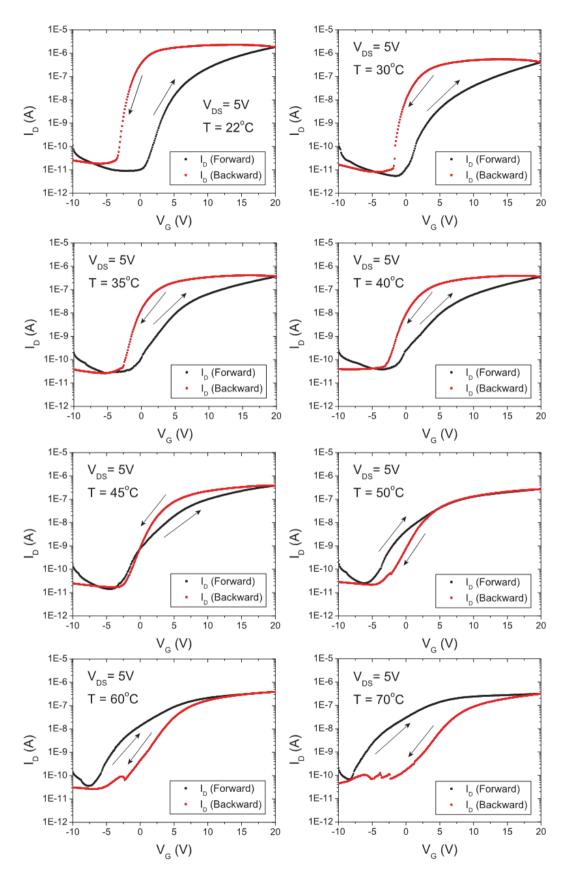

| Figure C.5: Transfer characteristics of ZnO nanoparticle TFT ( $W = 1000  \mu m$ and                       |

| $L = 3/2 \mu m$ ) with different temperatures                                                              |

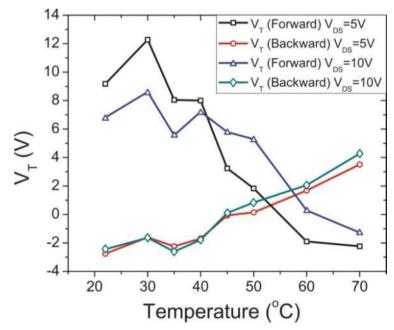

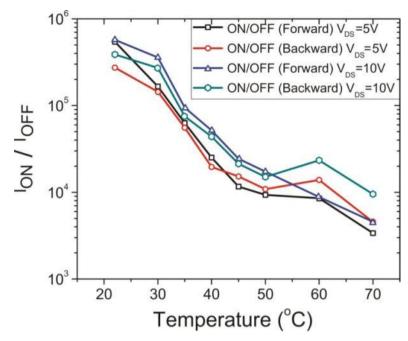

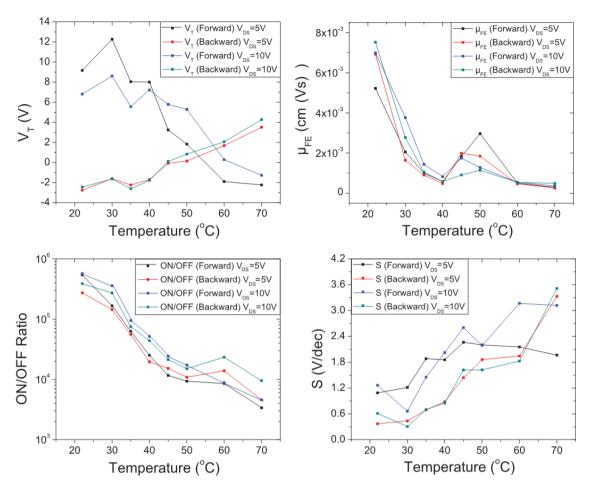

| Figure C.6: Characteristics variation under different temperatures on ZnO nanoaprticle                     |

| TFT ( $W = 1000 \ \mu m$ and $L = 3/2 \ \mu m$ )                                                           |

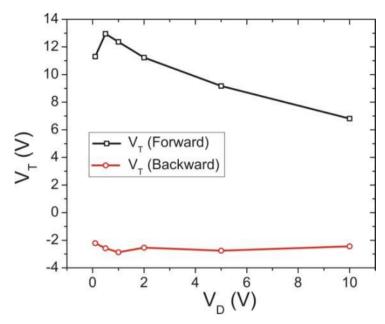

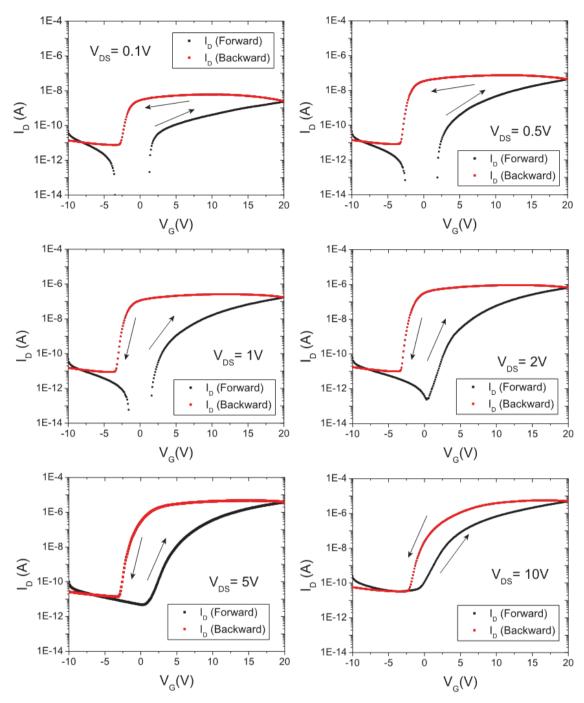

| Figure C.7: Transfer characteristics of ZnO nanoparticle TFT ( $W = 1000  \mu m$ and                       |

| $L = 3/2 \mu m$ ) applying different drain voltages                                                        |

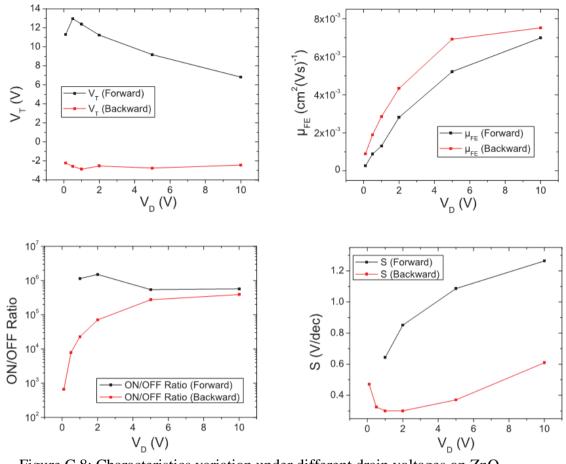

| Figure C.8: Characteristics variation under different drain voltages on ZnO nanoaprticle                   |

| TFT ( $W = 1000 \ \mu m$ and $L = 3/2 \ \mu m$ )                                                           |

|                                                                                                            |

# LIST OF TABLES

| Table 3.1: Physical properties of ZnO                                                             | . 26 |

|---------------------------------------------------------------------------------------------------|------|

| Table 4.1: PVP solution concentration.                                                            | . 59 |

| Table 4.2: ZnO solution concentration.                                                            | . 59 |

| Table 5.1: Electrical characteristics of ZnO nanoparticle TFT ( $W = 1000  \mu m$ ,               | L =  |

| $3/2 \mu m$ ) depending on the gate voltage sweeping direction                                    | . 74 |

| Table 5.2: Electrical characteristics of ZnO nanoparticle TFT with SiO <sub>2</sub> as §          | gate |

| dielectric ( $W = 100 \mu m$ and $L = 300 nm$ ) depending on the gate voltage sweep               | oing |

| direction                                                                                         | . 88 |

| Table C.1: Temperature dependency in the electrical characteristics of ZnO nanopart               | icle |

| $(W = 1000 \ \mu m \text{ and } L = 3/2 \ \mu m)$ when sweeping forward $V_G$ and $V_D = 5 \ V$   | 111  |

| Table C.2: Temperature dependency in the electrical characteristics of ZnO nanopart               | icle |

| $(W = 1000 \ \mu m \text{ and } L = 3/2 \ \mu m)$ when sweeping backward $V_G$ and $V_D = 5 \ V$  | 112  |

| Table C.3: Temperature dependency in the electrical characteristics of ZnO nanopart               | icle |

| $(W = 1000 \ \mu m \text{ and } L = 3/2 \ \mu m)$ when sweeping forward $V_G$ and $V_D = 10 \ V$  | 112  |

| Table C.4: Temperature dependency in the electrical characteristics of ZnO nanopart               | icle |

| $(W = 1000 \ \mu m \text{ and } L = 3/2 \ \mu m)$ when sweeping backward $V_G$ and $V_D = 10 \ V$ | 113  |

| Table C.5: Voltage dependency in the electrical characteristics of ZnO nanopart                   |      |

| $(W = 1000 \ \mu m \text{ and } L = 3/2 \ \mu m)$ when sweeping forward $V_G$                     |      |

| Table C.6: Voltage dependency in the electrical characteristics of ZnO nanopart                   | icle |

| $(W = 1000 \ \mu m \text{ and } L = 3/2 \ \mu m)$ when sweeping backward $V_G$                    | 116  |

#### **ABSTRACT**

During the last decades, the interest in flexible electronics has arisen. Systems that present benefits such as low cost, improved performance, transparency, reliability and better environmental credential are being extensively researched by several groups. Thin-film transistors (TFT) have good potential concerning these technologies. Therefore, zinc oxide (ZnO) based devices have been attracting researchers for its electrical, sensory and optical properties.

In this work, ZnO nanoparticles were used to integrate thin-film transistors, in which cross-linked PVP (Poly(4-vinylphenol)) and PECVD-SiO<sub>2</sub> (plasma enhanced chemical vapor deposition silicon dioxide) were used as gate dielectric layer. The complete integration process targets low cost and low temperature requirements (< 200°C). For this reason, simple process techniques as spin-coating or sidewall-etchback were used. Unfortunately, there are different reliability concerns in ZnO devices, among them aging or hysteresis. An experimental investigation of the hysteresis in the transfer characteristic is performed, and a qualitative model for the observed behavior is proposed. It was observed that the hysteresis direction is affected by temperature variation when the polymeric dielectric is used. The PVP bulk polarization, the traps in nanoparticles and at the polymeric dielectric interface, as well as the desorption of oxygen molecules in the surface of the nanoparticles, were attributed as the main cause of the hysteretic behavior.

Moreover, capture and release of charge carriers by traps at determined current paths in the transistor lead to discrete current fluctuations in stress tests, similar to random telegraph signal (RTS) reported in nanoscale MOSFET. This result supports the hypothesis of charge transport mechanism (percolation paths) in nanoparticulate ZnO.

**Keywords:** Nanoparticles, ZnO, thin-film transistors, low-cost electronics.

#### Estudo da Histerese em Transistores de Filmes Finos de Nanopartículas de Óxido de Zinco

#### **RESUMO**

Nas últimas décadas, o interesse na eletrônica flexível tem aumentado. Sistemas que apresentam benefícios, tais como: baixo custo, melhor desempenho, transparência, confiabilidade e melhores credenciais ecológicas, estão sendo extensivamente pesquisados por vários grupos. Os transistores de filmes-finos possuem potencial para alcançarem essas características. Dispositivos baseados em óxido de zinco (ZnO) tem atraído pesquisadores devido as suas propriedades elétricas, sensoriais e ópticas.

Neste trabalho, nanopartículas de ZnO foram utilizadas como semicondutor ativo e cross-linked PVP (polivinilfenol) e PECVD-SiO<sub>2</sub> (plasma enhanced chemical vapor deposition silicon dioxide) como dielétricos de porta para integrar transistores de filmesfinos. Este processo de integração tem por objetivo os pré-requisitos de baixo custo e baixa temperatura (<200°C). Por esta razão, a utilização de técnicas de integração simples, como o spin-coating ou a técnica de sidewall-etchback, foram utilizadas. Infelizmente, existem problemas relacionados à confiabilidade em dispositivos baseados em ZnO, entre eles a degradação no tempo ou a histerese. Após uma investigação experimental da histerese na característica de transferência, um modelo qualitativo para o comportamento observado é proposto. Observou-se que a direção da histerese é afetada pela variação da temperatura quando o dielétrico polimérico é usado. Baseando-se na caracterização dos transistores, a polarização do PVP, as armadilhas na superfície das nanopartículas e na interface com o dielétrico, bem como a liberação de moléculas de oxigênio da superfície das nanopartículas foram atribuídas como as principais causas da histerese.

Além disso, uma flutuação discreta da corrente é observada em testes de estresse devido à captura e liberação de portadores em determinados caminhos de corrente no transistor, semelhante a *random telegraph signal* (RTS), relatado em MOSFET nanométricos. Este resultado suporta o hipotético mecanismo de transporte de elétrons (caminhos de percolação) em filmes compostos por ZnO nanoparticulado.

Palavras-Chave: Nanopartículas, ZnO, Transistor de filmes finos, eletrônica de baixo custo.

#### 1 INTRODUCTION

Thousands of organizations have been pursuing printed, organic and flexible electronics. While some of these technologies are already mature, with substantial growth in thin-film photovoltaics market, for instance, others such as thin-film transistors, developed by hundreds of organizations, are becoming only now commercially available. The benefits of these new electronics are numerous - ranging from lower cost, improved performance, flexibility, transparency, reliability and better environmental credentials. Existing electronics and electrical products will be impacted by many newly created applications, as sensory electronic skins and transparent screens, and their extent is countless (SUN et al., 2007), (WONG et al., 2009) and (AXISA et al., 2005). Figure 1.1 presents some potential application of these new technologies, such as transparent screens and flexible electronic circuits.

Figure 1.1: Application of transparent and flexible electronics.

To integrate thin-film transistors the use of polycrystalline silicon as an active material requires expensive and complex integration processes. This is the main reason for the growing interest in solution-processed semiconducting alternatives, which are low-cost and low temperature processes. Transistors based on organic materials, particularly pentacene, are an alternative for polycrystalline silicon. However, organic semiconductors present limited channel mobility, air instability and electrical reliability issues, which generally requires further integration steps in order to overcome these issues, compromising the cost of the integration process (LEE et al., 2008) and (WONG et al., 2009).

Solutions based on inorganic materials have gained focus among researchers as a possible substitute for active semiconductors. Zinc oxide has attracted attention as a key material because of its electrical, sensory and optical properties. This material is already widely spread in society, for example, in the manufacturing of paintings, cosmetics,

pharmaceutical, plastics, batteries, electrical equipments and textiles (JAGADISH et al., 2005).

Nowadays, there are some very promising electronic devices employing ZnO as semiconductor under research. However, the techniques used require high vacuum or high temperatures (LEE et al., 2008), which are not suitable for low-cost production on flexible polymeric substrates (BUBEL et al., 2009) and (WONG et al., 2009).

Focusing on low-cost applications, a high throughput manufacturing process is needed. This is normally achieved by simple techniques such as spin coating, inkjet-printing or roll-to-roll processes. Nanoparticulate ZnO presents potential characteristics, and with recent improvements in the growth technology of ZnO nanostructures, new opportunities and applications for ZnO are emerging, i.e., flat screen and active matrix liquid crystal displays, gas, chemical and biological sensors, and UV light emitters (WONG et al., 2009), (FAN et al., 2005), (WANG et al., 2004), (MORKOÇ et al., 2009) and (JIN et al., 2008). By using nanoparticulate ZnO, it is possible to directly process the semiconductor from a liquid dispersion without the necessity of a costly or high temperature process (BUBEL et al., 2009).

Although the ZnO nanoparticles present good prospective and can be produced at low cost and high quality, some problems are observed when using nanoparticles to integrate thin-film transistors (TFT). The main concerns about the ZnO nanoparticle transistors are the hysteresis when using poly(4-vinylphenol) (PVP) (WOLFF et al., 2011-b,c), (FABER et al., 2009), (LEE et al., 2006) or SiO<sub>2</sub> (SUN et al., 2005), (ASSION et al., 2010) as gate dielectric; the low field effect mobility due to the nanoparticle interconnections (LEE et al., 2007); the roughness of the nanoparticles at the interface with the gate dielectric (OKAMURA et al., 2008), (WALTHER et al., 2010); characteristics variation depending on the bending state when integrated on flexible substrates; and the high temperature process (above 200°C), which is not adequate for some kinds of flexible substrates (LEE et al., 2007), (LEE et al., 2008), (WALTHER et al., 2010).

In this work, ZnO nanoparticles were used to integrate thin-film transistors, in which cross-linked PVP and PECVD-SiO<sub>2</sub> were used as gate dielectric layer. A comprehensive electrical characterization is carried out, focusing on the experimental investigation of the hysteresis in the transfer characteristic, and a qualitative model for the observed behavior is proposed.

This text is structured as follow. The second section discusses metal-semiconductor contacts. In the third section, zinc oxide and polymeric gate dielectric are reviewed. The ZnO TFT properties and the integration process are presented in the fourth section. In the fifth section, the results of the characterization of the transistors are reported together with a discussion of the origin of the hysteretic behavior in ZnO nanoparticle TFT. The conclusion is presented in the sixth section. The Appendix A and B present the wafer cleaning and measurement procedures, respectively. In the Appendix C, graph and tables are exposed, while in Appendix D the summary of this Master thesis in Portuguese.

# 2 METAL-SEMICONDUCTOR CONTACTS (SCHOTTKY JUNCTIONS)

Because of metal-semiconductor contacts are partly responsible for the operation of the TFT integrated in this work, they are reviewed in this section. The most relevant behavior is concisely presented. First, the metal and semiconductor energy scales are reviewed, as well as their contact under thermal equilibrium, forward and reverse bias. Second, a brief explanation on the current transport process and on Ohmic contact is presented.

#### 2.2 Energy Scales

One of the first steps to understand the contact between metals and semiconductors is regarding their representation in the energy scale and band diagram, separately. The vacuum level ( $E_{VAC}$ ) is defined as the minimum energy an electron requires in order to completely free itself from a metal or semiconductor (PIERRET, 1996). In metals, almost all states are filled in up to the Fermi level ( $E_F$ ) and empty at energies above that. In intrinsic semiconductors, however, almost all states are filled in the valence band, while the conduction band is almost empty. This is in accordance to the Fermi-Dirac distribution function (Eq. 2.1), which specifies the probability of an available state with energy E to be occupied by an electron under equilibrium conditions.

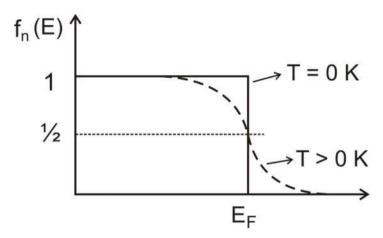

$$f_n(E) = \frac{1}{1 + e^{\frac{E - E_F}{K_B T}}}$$

(2.1)

in which,  $E_F$  is the Fermi level,  $K_B$  is the Boltzmann constant and T is the absolute temperature.

Figure 2.1 depicts the Fermi-Dirac distribution for the temperatures T = 0 K and T > 0 K. Since there are no states in the semiconductor within the forbidden gap, only energies below the valence band maximum or above the conduction band minimum are occupied (PIERRET, 1996), (COLEMAN, 2008).

Figure 2.1: Fermi-Dirac distribution for T = 0 K and T > 0 K.

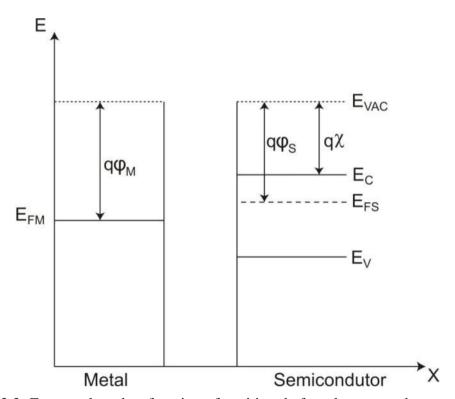

Figure 2.2 shows the energy state diagram of a metal and an n-type semiconductor; the vacuum level and work function  $(\varphi)$ , which is the energy required to free an electron at the Fermi level from the metal or semiconductor. In metals, the work function is an invariant property of a specific metal. In semiconductors, the Fermi level varies depending on the doping level. This is the main reason for the electron affinity  $(\chi)$  to be introduced, which is the difference between the vacuum level and the conduction band edge (PIERRET, 1996).

Figure 2.2: Energy plotted as function of position, before the contact between metal and semiconductor. The work function of the metal is higher than that of the n-type semiconductor.

#### 2.3 Metal-Semiconductor Contact

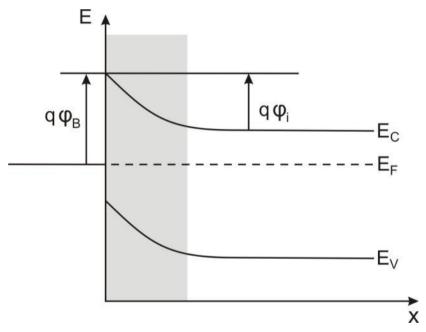

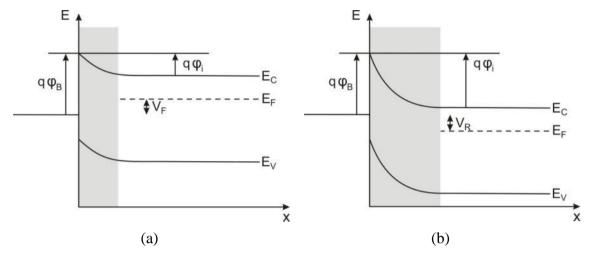

If the Fermi level in the semiconductor is higher than in the metal, for a short time after the conceptual contact formation, electrons from the semiconductor create a surface depletion region (represented in gray in Figure 2.3) and a growing barrier against the electron transfer from the semiconductor into the metal. This will continue until the transfer rate across the interface is the same in both directions, and the Fermi level is the same through the structure (PIERRET, 1996). Figure 2.3 presents the equilibrium energy for an ideal metal to n-type semiconductor contact, Figure 2.4a represents it under forward bias, and Figure 2.4b under reverse bias. A variation in the depletion region width can be observed. The barrier height  $(q\phi_B)$  from the metal to the semiconductor is not altered under different bias operation; on the other hand, the barrier from the semiconductor to the metal is sensitive to the applied bias. As explained by Sze et al. (2006), interface states also play a role on metal-semiconductor junctions, pinning the Fermi level at the interface. Therefore the barrier heights determination is not uniquely defined by metal work function and semiconductor electron affinity. Further explanation on this effect is detailed in (SZE et al., 2006).

Figure 2.3: Energy-band diagram in metal on n-type semiconductor in thermal equilibrium.  $q\phi_B$  denotes the barrier height from the metal to the semiconductor and  $q\phi_i$  the barrier height from the semiconductor to the metal.

Figure 2.4: Energy-band diagram in metal on n-type semiconductor under (a) forward bias and (b) reverse bias.

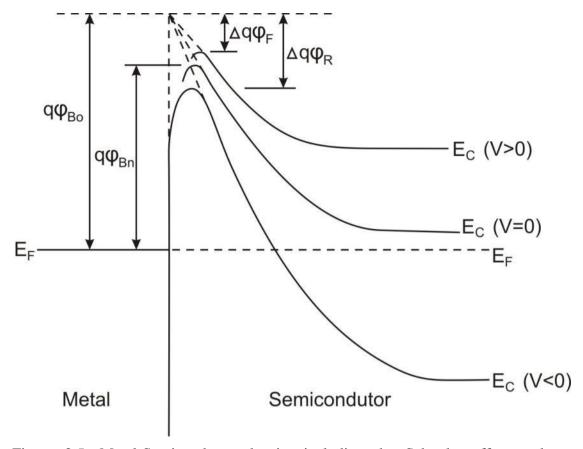

In the presence of an electric field, the barrier energy for charge carrier emission is image-force-induced lowered (SZE et al., 2006). This is called image-force lowering or Schottky effect. The barrier reduction is smaller than the barrier itself; on the other hand the barrier depends on the applied voltage as depicted in Figure 2.5. The intrinsic barrier height at thermal equilibrium is represented by  $q\phi_{Bo}$ ; when considering the Schottky effect it is reduced to  $q\phi_{Bn}$ ;  $\Delta q\phi_F$  and  $\Delta q\phi_R$  are the variation in the barrier height under forward and reverse bias operation respectively. Again, a more detailed explanation can be found in (RHODERICK et al., 1988), (SZE et al., 2006), (RIDEOUT, 1978).

Figure 2.5: Metal-Semiconductor barrier including the Schottky effect under different bias conditions. Adapted from (RIDEOUT, 1978).

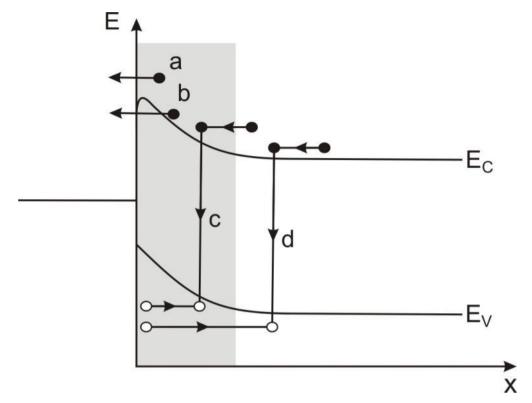

Rhoderik et al. (1988) explains that there are different transport mechanisms through the Schottky barriers. Figure 2.6 shows the carrier transport across metal-semiconductor in an n-type semiconductor under forward bias. The mechanisms are:

- a) Emission of electron from the semiconductor over the top of the barrier into the metal;

- b) Quantum-mechanical tunneling through the barrier;

- c) Recombination in the space-charge depletion region;

- d) Recombination in the neutral region ("hole injection").

Figure 2.6: Transport process in a forward-biased Schottky barrier.

Process (a) is the most important in most of the Schottky diodes and the other processes are regarded as deviations on this ideal behavior. For a p-type semiconductor, the inverse process is observed, which means that instead of holes there are electrons and instead of electrons there are holes (RHODERICK et al., 1988).

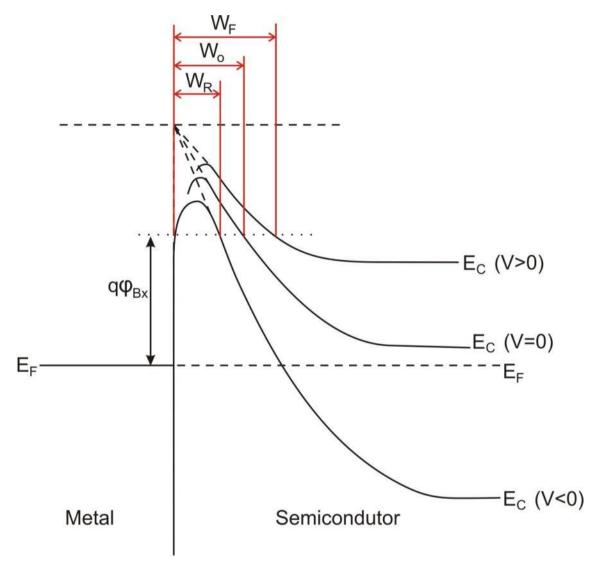

All the previous considerations about the metal-semiconductor contacts consider a rectifying behavior. However, Ohmic contacts present low impedance regardless of their biasing polarity. In other words, the barrier is present, although it is transparent to carrier transport (due to tunneling, process (b) from Figure 2.6). They are normally achieved with heavily doped semiconductors (PIERRET, 1996). Another approach to achieve Ohmic contact is applying bias to the contacts in order to shrink the barrier width, allowing the electron tunneling through the barrier (RHODERICK et al., 1988). This effect can be observed in Figure 2.7, in which the barrier width shrinks when reverse bias is applied to the junction. Additionally, this effect is partly responsible for the functioning of ZnO nanoparticle TFT (HILLERINGMANN et al., 2011).

Figure 2.7: Detail of the barrier width variation under different electrical bias.

#### 3 ZINC OXIDE AND GATE DIELECTRIC POLYMER

In this section, characteristics of the ZnO are presented, focusing mainly on its electronic and optic properties. Furthermore, the characteristics of the ZnO nanoparticles used to integrate the thin-film transistors will be presented. Also, some properties of the poly(4-vinylphenol) (PVP) used as a gate dielectric polymer are exposed.

#### 3.1 Zinc Oxide Properties

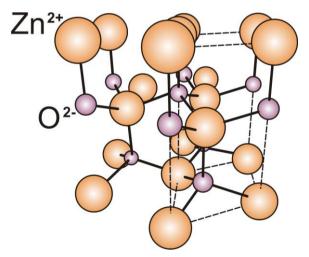

Zinc oxide is a direct, wide bandgap semiconductor material (3.37 eV), meaning it is transparent to visible light (FAN et al., 2005) and (WANG et al., 2004). This characteristic, combined to the low temperature processes required and its non-toxicity, is one of the reasons why ZnO has been gaining considerable interest for integrating transparent thin-film transistor (FAN et al., 2005) and (WANG et al., 2004). Another reason is its air-stability which can be achieved by proper fabrication or annealing. As most of the II-VI binary compound semiconductors, ZnO usually presents a hexagonal wurtzite crystal structure, as shown in Figure 3.1.

Figure 3.1: ZnO's chemical structure. One unit cell is outlined for clarity. Adapted from (JAGADISH et al., 2004)

One of the issues regarding ZnO is doping. ZnO is predicted to be an intrinsic semiconductor. On the other hand, it is found predominantly as n-type semiconductor due to the presence of a high concentration of native defects in the form of oxygen

vacancies and zinc interstitials that contribute to deep and shallow energy states, respectively (JAGADISH et al., 2004). Other authors, attribute the unintentional n-type conductivity in ZnO to hydrogen, which occurs exclusively in the positive state in ZnO; i.e., it always acts as a donor (VAN DE WALLE, 2000) and (JANOTTI et al., 2007). The obtainment of p-type ZnO has been quite difficult because of the carrier compensation by the native defects of ZnO, as explain Jagadish et al. (2004).

The Table 3.1 shows some properties of ZnO:

Table 3.1: Physical properties of ZnO.

| Property                        | Value                             |

|---------------------------------|-----------------------------------|

| Relative dielectric constant    | 8.66                              |

| Gap Energy                      | 3.37 eV, direct                   |

| Intrinsic carrier concentration | $< 10^6  \mathrm{cm}^{-3}$        |

| Electron mobility (T = 300 K)   | $200~\mathrm{cm}^2/(\mathrm{Vs})$ |

| Hole mobility (T = 300 K)       | $5 - 50 \text{ cm}^2/(\text{Vs})$ |

Source: (FAN et al., 2005)

Metal oxide semiconductor thin films are the most promising devices among solid state chemical sensors (JAGADISH et al., 2004) and ZnO based sensors are widely researched (FAN et al., 2005), (WANG et al., 2004), (QIN et al., 2011), (LIU et al., 2009) and (XU et al., 2000). Due to its excellent piezoelectric properties, it is possible to integrate sensory devices based on SAW (surface-acoustic wave) (FAN et al., 2005), (WANG et al., 2004), (JAGADISH et al., 2004), (QIN et al., 2011). In addition, ZnO is already used as an effective gas, chemical and biological sensor material, since absorbed species interact with surface complexes such as O<sup>-</sup>, O<sup>-2</sup>, H<sup>+</sup> and OH<sup>-</sup> modifying the charge distribution (WANG et al., 2004), (JAGADISH et al., 2004) (MORKOC et al., 2009), (LIU et al., 2009) and (XU et al., 2000).

#### 3.2 Zinc Oxide Nanoparticles

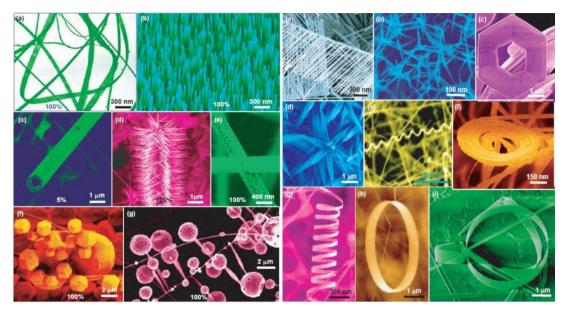

ZnO nanostructures are presented in several forms: nanobelt, aligned nanowire arrays, nanotubes, array of propellers, mesoporous, nanowires, cage and shell structures, nanosprings and spheres (JAGADISH et al., 2004), (FAN et al., 2005) and (WANG et al., 2004). Several of these nanostructures can be observed in Figure 3.2.

Figure 3.2: Various ZnO nanostructures (JAGADISH et al., 2004).

The ZnO nanoparticles used to integrate the thin-film transistors were the VP AdNano ZnO 20 DW (dispersion of VP AdNano ZnO 20 in water) distributed by Degussa AG (2006). Pure feed stocks and non-contaminating ZnO are used in the synthesis process, so the product is obtained in high purity (zinc oxide content > 99.5%). AdNano zinc oxide is a crystalline solid exhibiting the hexagonal wurtzite lattice. The smallest units of the compound, only visible using an electron microscope, are the primary particles in the range of about 15-30 nm of diameter. Based on this high degree of particle fineness, 1 gram of VP AdNano ZnO 20 can provide an active surface of 20-25 m². The primary particles are usually not isolated. They are typically bounded to each other to form aggregates. The effective particle size, which is present in dispersion, for example, is about 100 nm (DEGUSSA, 2006).

Okamura et al. (2008) states that nanoparticulate zinc oxide is regarded as one of the most promising inorganic materials for printable n-type thin-film transistor, due to the compatibility with solution, low-temperature, and high throughput processes.

#### **3.3 PVP Properties**

Poly(4-vinylphenol) is a weak acid polymer. Due to its variety of applications and simple fabrication process, many research groups have investigated its properties (VICCA et al., 2010), (BENSON et al., 2008), (JUNG et al., 2005) and (HWANG et al., 2006). Applications of the polymer include the use as gate dielectric insulator in the microelectronic field and responsive surface coating (UPPALAPATI et al., 2010).

The interesting fact about PVP for this work is the fabrication of thin films for potential application as dielectric applied via spin-coating process. However, when the dielectric is a polymer, a cross-linker agent should be applied to support the impact of solvents and bases from further process steps. The cross-linking reaction should not leave any mobile ions in the film and the cross-linker agent used in the photoresist should be avoided (VICCA et al., 2010). Moreover, the cross-linked polymer should have a very smooth surface, high electrical field strength, preferably a high dielectric

constant, high purity, and be hydrophobic while still allowing sufficient adhesion to adjacent layers, as in ZnO nanoparticles dispersion.

The cross-linked PVP is normally dissolved in propylene glycol methyl ether acetate (PGMEA) and poly(melamine-co-formaldehyde)-methylated is used as a cross-linker agent (VICCA et al., 2010), (CHOI et al., 2008) and (LIM et al., 2007). Figure 3.3 presents the chemical structures of such polymeric dielectrics, where (a) is the pure PVP, (b) is the cross-linker agent and (c) is the cross-linked PVP.

a)

$$CH_2$$

$CH_2$

$CH_2$

Figure 3.3: Chemical structures of polymeric dielectrics used in this work. (a) Pure PVP, (b) cross linker agent and (c) a cross-linked PVP chemical structure.

Lim et al. (2007) and Faber et al. (2009) report the use of PVP, especially the effect of hydroxyl (OH-) groups in the polymeric gate dielectrics, which may lead to a shift in the threshold voltage depending on the direction of the gate-source voltage sweep, corresponding to a hysteretic behavior in the transfer characteristics. The relative permittivity and the insulator thickness were obtained from (LEHDE, 2010) and their values are  $\varepsilon_r = 5.9$  and  $t_{ins} = 0.18 \ \mu m$  respectively, under the conditions used in the transistor's integration.

#### 4 ZINC OXIDE THIN-FILM TRANSISTOR

In this section, characteristics of ZnO nanoparticle based thin-film transistors (TFT) are presented, as well as the electron transport mechanism in nanoparticulate ZnO film and the transistor integration process. Furthermore, the transistor evolution in our group, a cooperation between University of Paderborn, Germany and UFRGS (Universidade Federal do Rio Grande do Sul), Brazil, and among other research groups is exposed.

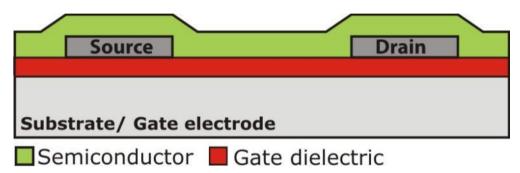

#### 4.1 Thin-Film Transistor Properties

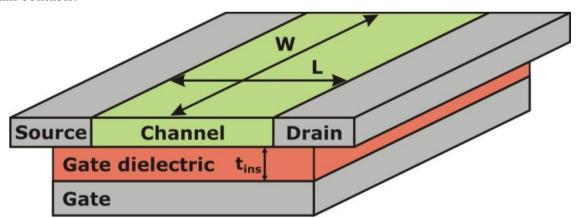

In order to understand how the TFT operates, a basic schematic representation of its structure will be used, as shown in Figure 4.1. The channel layer - a semiconductor such as amorphous/poly silicon or an organic/inorganic semiconductor - is used to transport the carriers from source to drain, normally made of metal, which creates a Schottky barriers with the semiconductor. The gate dielectric layer separates the gate electrode from the semiconductor channel. The channel width (W) and length (L) and the gate dielectric thickness ( $t_{ins}$ ) are the main TFT dimensional characteristics. As depicted in Figure 4.1, the active channel region comprises the rectangular area between source and drain contacts.

Figure 4.1: Simplified schematic of a TFT structure.

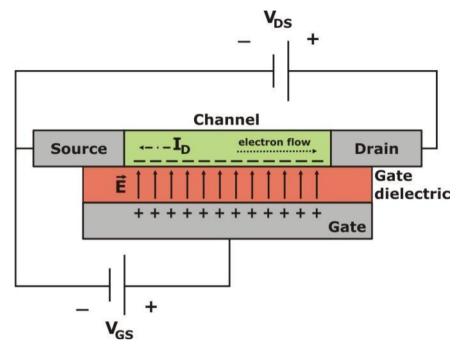

Figure 4.2 presents the key elements of the TFT operation, with electric bias and charge polarities for an n-channel device (channel current flow is mainly by electrons). The voltage applied to the gate electrode ( $V_{GS}$ ) modulates the charge density in the channel through the gate capacitance. The magnitude of the induced charge density is proportional to the applied gate voltage, which produces a corresponding variation in source-to-drain conductance. For an n-channel device, for instance, when a positive gate

voltage is applied, the electron concentration in the channel increases, while a negative voltage reduces the channel electron density.

Figure 4.2: Schematic illustration of the central elements of TFT operation.

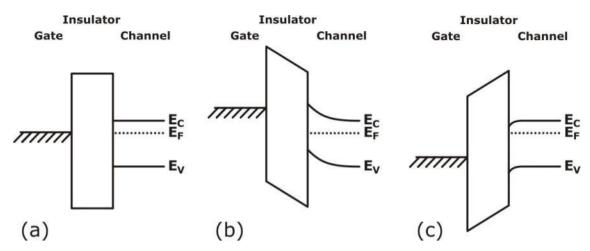

Another way to explain the formation of the channel is shown in Figure 4.3, in which ideal energy band diagram are shown, depicting the view through the gate of an n-channel accumulation-mode TFT. The device at equilibrium, i.e., with no applied electric bias, is depicted in Figure 4.3a. Negative bias repels the mobile electrons from the interface, creating a depletion region (Figure 4.3b). Comparing this bias condition to the equilibrium one, a conductance reduction is expected due to the reduced density of mobile electrons in the channel. Conversely, positive bias attracts mobile electrons forming an accumulation region near the insulator/channel interface, increasing its conductance (Figure 4.3c) (HONG et al., 2008).

A distinguishing feature of a TFT compared to a conventional MOSFET (metal-oxide-semiconductor field-effect transistor) is that the carrier transport in the channel typically occurs in an accumulation layer in a TFT, whereas, in a MOSFET, it occurs in an inversion layer (HONG et al., 2008).

Figure 4.3: Energy band diagram as views through the gate for (a) equilibrium, (b) depletion ( $V_{GS} < 0 V$ ), and (c) accumulation ( $V_{GS} > 0 V$ ).

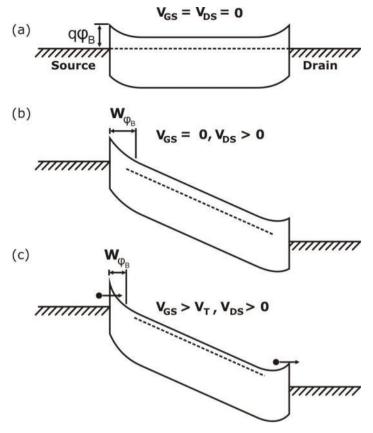

Another important element to understand TFT operation, especially for ZnO TFT integrated in this work, is the behavior of the Schottky barriers under different bias condition. In Figure 4.4a, the unbiased ZnO TFT band diagram is presented, and the presence of Schottky barriers in both metal contacts (drain and source) are observed. ZnO is an intrinsic n-type semiconductor (Section 3); however, the Fermi level exact position, represented by a dash line, is uncertain. By applying a drain voltage in the transistor, as in Figure 4.4b, the drain potential lowering is expected. However, the barrier's width is almost the same, and the electrons cannot tunnel through the barrier.

When the gate is above the threshold voltage (Figure 4.4c), the barrier width shrinks (Ohmic contacts), and the electrons tunnel through the drain and source barriers (WOLFF et al., 2010). In the bulk, the electrons "flow" due to gate voltage effect in the region near the interface of the semiconductor and the gate dielectric (channel).

Figure 4.4: Band diagrams along semiconductor surface under various biases.

Even with the above cited differences, the TFT operation is normally expressed in terms of the drain current ( $I_D$ ) as a function of the gate-to-source ( $V_{GS}$ ) and the drain-to-source ( $V_{DS}$ ) voltages. Eq. 4.1 represents the TFT operation; it is the same used to model the metal-insulator-semiconductor field-effect transistor (MISFET). Although, it may not provide quantitative agreement with the device, it represents the transistor's basic operation, as explained by Jagadish et al. (2004).

$$I_{D} = \begin{cases} 0 & ; V_{GS} \leq V_{T} \\ \frac{\mu C_{ins} W}{L} [(V_{GS} - V_{T}) V_{DS} - \frac{V_{DS}^{2}}{2}] & ; V_{DS} \leq V_{GS} - V_{T} \\ \frac{\mu C_{ins} W}{2L} [V_{GS} - V_{T}]^{2} & ; V_{DS} > V_{GS} - V_{T} \end{cases}$$

$$(4.1)$$

where,  $\mu$  is the carrier mobility,  $C_{ins}$  is the gate capacitance, W is the transistor width, L is the transistor length and  $V_T$  is the threshold voltage.

A more precise model for the TFT operation adds to the above model series resistance to the drain/source contact. Also, there is another model (3-layer model) which takes into account that, in TFT devices, the active semiconductor is a thin layer, and therefore it considers three vertical current paths (channel, bulk and interface) to represent the transistor operation. More sophisticate models such as the comprehensive depletion-mode model or the discrete trap model also describe the TFT as explained by Hong et al. (2008).

On the other hand, for the analysis in this work, the model presented through Eq. 4.1 will be used, since it represents the basic operation of the ZnO TFT and several research groups used the model for characterizing their devices or as base for other models.

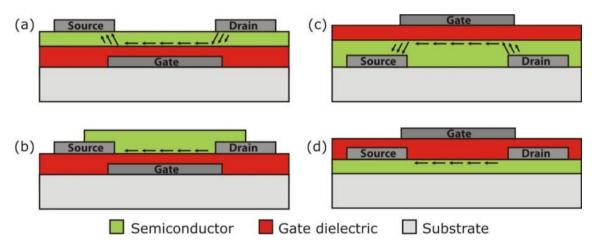

In practical terms, there are four general thin-film transistors configuration as depicted in Figure 4.5. Devices can be structured either in staggered or in coplanar configuration (HONG et al., 2008). The position of drain/source electrodes and gate dielectric in relation to the channel defines the configuration. In coplanar structures (Figure 4.5b and Figure 4.5d), the drain/source electrodes and the insulator are located in the same side of the channel, and in staggered structures (Figure 4.5a and Figure 4.5c) the drain/source electrodes and the insulator are located in opposites sides.

Other consideration when comparing the coplanar and staggered configuration is regarding the current flow in the transistor as shown in Figure 4.5 (HONG et al., 2008). In the coplanar configuration, the drain/source electrodes are in direct contact with the induced channel, enabling a direct current flow; in staggered devices, the current must flow vertically to the induced channel before flowing horizontally towards the drain. In the last configuration, due to the large contact area between drain/source and the semiconductor, a minimal contact resistance is achieved.

Additionally, the devices can be classified as either bottom-gate (Figure 4.5a and Figure 4.5b) or top-gate devices (Figure 4.5c and Figure 4.5d). A bottom-gate TFT, which has the gate electrode and dielectric underneath the channel, is normally referred as an inverted TFT.

Figure 4.5: Four general thin-film transistor configurations, including: (a) staggered bottom-gate, (b) coplanar bottom-gate, (c) staggered top-gate and (d) coplanar top-gate.

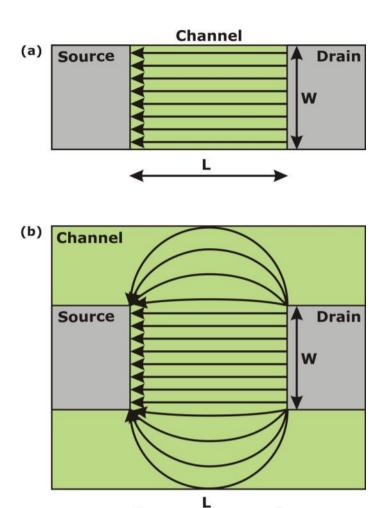

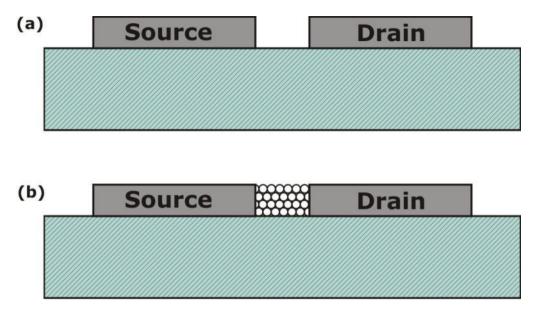

Additionally, the channel in the TFT can be either patterned or unpatterned, as shown in Figure 4.6. When the channel is patterned (Figure 4.6a) the width-to-length ratio is well defined. On the other hand when an unpatterned channel is used, peripheral current flows due to fringing electric fields outside the drawn channel. This effect can be observed in Figure 4.6b. For unpatterned channel devices, in addition to the current limited into the drain/source area, the fringing current also contributes to the total current, increasing the current when compared to the patterned channel device (JAGADISH et al., 2006).

Figure 4.6: Schematic layout of a TFT structure (gate electrode and gate dielectric layers are not shown explicitly here), in which (a) the channel layer is patterned, and (b) the channel layer is unpatterned. The current is represented by arrows.

#### 4.2 ZnO Thin-Film Transistor

In this subsection, it will be presented the evolution of the TFT in our group (a cooperation between University of Paderborn, Germany and UFRGS, Brazil), first using silicon nanoparticles and afterwards using ZnO nanoparticles. ZnO based TFT from other research groups will also be presented.

#### 4.2.1 TFT in our group

The Sensor Technology Department from Paderborn, Germany has been working since 2005 with TFT, as part of an intensive cooperation with the industrial segments for both thin-film transistors as well as so-called single-particle transistors. The aim of the research is to develop a suitable manufacturing process for electronic logic circuits on foil substrates, where transistors with proper switching behavior should be suitable for low-cost/low-performance (low power) applications (SENSORIK, 2012). In 2010 the University of Paderborn and UFRGS started a collaborative work aiming to improve

the devices and exchange knowledge in their expertise areas. The following transistor evolution with a more detailed integration process and explanation is reported in (HILLERINGMANN et al., 2011).

The group started the research using silicon nanoparticles as active semiconductor. For simplicity, thermally oxidized doped silicon wafers were used as gate structure for the first tests of the transistors, as shown in Figure 4.7, although this technique is not suitable for circuit integration.

Figure 4.7: Integrated TFT using oxidized doped silicon as gate structure. Adapted from (HILLERINGMANN et al., 2011)

The transfer characteristic of the device with  $L=8 \mu m$  and  $W=16.000 \mu m$  is shown in Figure 4.8. Even at very high gate and drain voltages the drain current is in the nanoampere range only.

Figure 4.8: Transfer characteristics of the silicon nanoparticle transistor with  $t_{ox} = 200 \text{ nm}$ ,  $L = 8 \mu m$  and  $W = 16.000 \mu m$ . (HILLERINGMANN et al., 2011)

The natural oxide on the surface of the silicon nanoparticles is the main reason for the low drain current, as this oxide acts as a potential barrier. The mean particle size of the silicon nanoparticle is around 60 nm and considering the channel length of 16  $\mu$ m,

there are at minimum 260 inter particle transitions in the channel. Considering that each transition acts as a potential barrier, the drain current is expected to be very small. The calculated field-effect mobility is about  $10^{-7} \, cm^2/Vs$  only. Thereafter this kind of device is not suitable for any application.

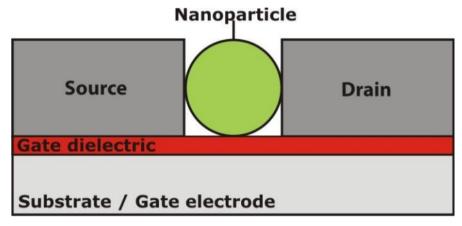

In order to reduce the number of inter particle transitions, and therefore improve the mobility, it is necessary to reduce the transistor channel length. In the best case, only one particle should act as the transistor channel. By using a nanoscaled trench into the metal and inserting the semiconductor into this trench it is possible to integrate such device, as presented in Figure 4.9.

Figure 4.9: Schematic view of a silicon single particle FET with inverted coplanar setup. Adapted from (HILLERINGMANN et al., 2011)

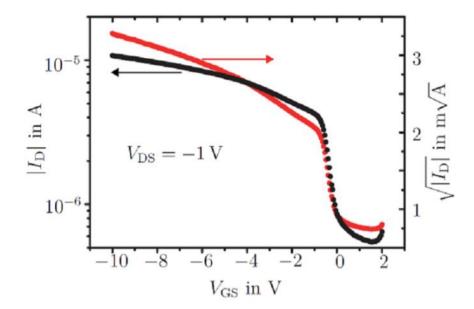

To ensure the contact between both (drain/source) contacts, the trench must fit to the particle size, in other respects no contact will be formed. The test structure of  $L=60 \, nm$  and  $W=100 \, \mu m$  were used to get at least one particle out of the spin coating process (mean particle size of 60 nm in the dispersion). Figure 4.10 depicted the transfer curve of the integrated device. The p-type FET is a depletion device with a field-effect mobility of about  $10^{-2} cm^2/Vs$ , calculated assuming a completely filled transistor width with nanoparticle. As there are only few transistors operating, this assumption overestimates the real active transistor width, which means that there is a much higher mobility in the nanoparticle.

Figure 4.10: Transfer curve of a Si nanoparticle FET with L = 60 nm and W =  $100 \mu m$ ,  $t_{ox} = 15 \text{ nm}$  after thermal treatment at  $300^{\circ}\text{C}$ . (HILLERINGMANN et al., 2011)

Since the yield of operating devices with the configuration above was very low, an inverted staggered configuration was integrated. Despite the higher yield in well operating devices, the performance improvement was not satisfactory. The silicon nanoparticles used in the above TFT are undoped; and phosphorous doping weakly influences the transistor characteristics, because the number of active dopants in a nanoparticle is very low; conversely, boron doping strongly affects the transistor because aluminium (metal used for the drain/source) and the p-type silicon built an ohmic contact. Therefore the potential barrier vanishes and the nanoparticles nearly electrically short-circuit the drain and source contacts.

Summing up, thin film transistors based in Si nanoparticles are not suitable for device integration mainly due to the natural oxide shell on the particle surface. Only by using a single particle as switch element the performance can be acceptable.

The natural oxide in the Si nanoparticles was the main reason for changing from silicon to zinc oxide nanoparticles. ZnO particles do not have any insulating shell caused by the atmosphere. An improvement in the particle interconnection was expected, since the potential barrier between neighboring particles should be lower than in silicon.

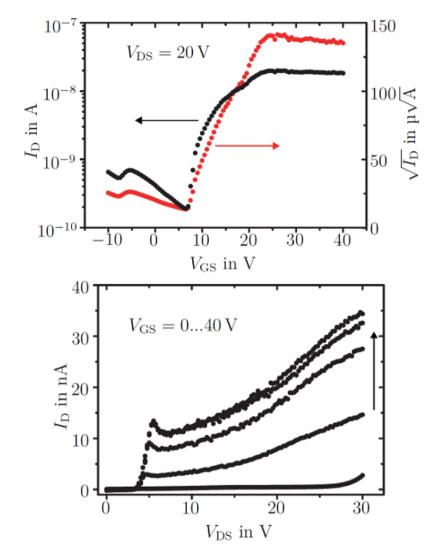

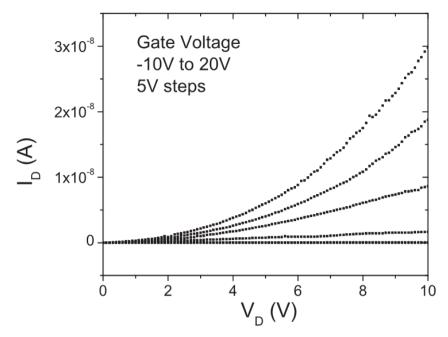

A water based dispersion of ZnO nanoparticles was used in the same template (inverted coplanar structure) as used for the Si nanoparticles based TFT. The transistor input and output curves are shown in Figure 4.11, where it is possible to observe an n-type enhancement mode FET. Field effect mobility of about  $10^{-5} cm^2/Vs$  was extracted from the transfer characteristic.

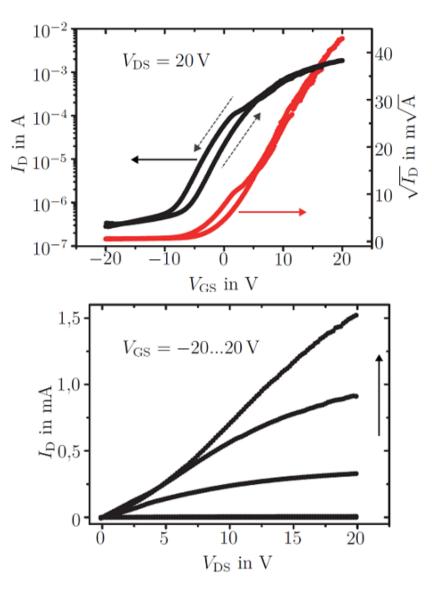

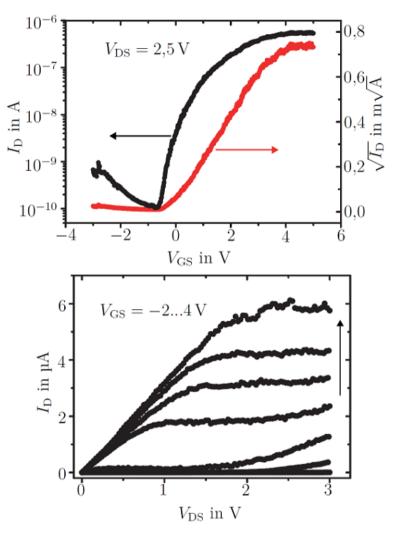

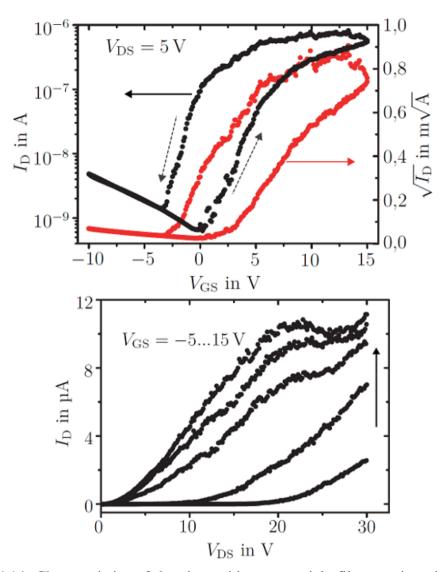

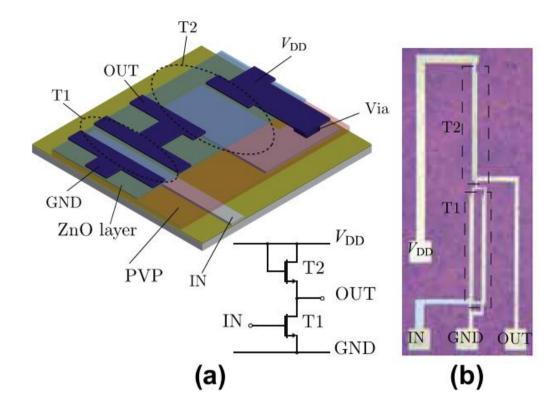

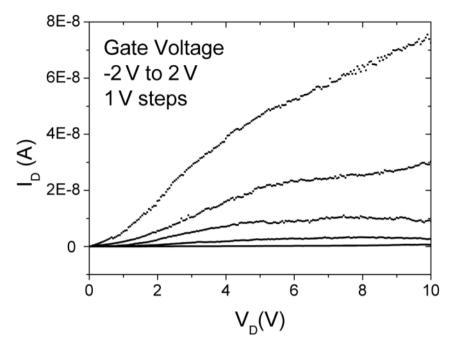

Figure 4.11: Characteristics of a thin film zinc oxide nanoparticle FET in inverted coplanar setup,  $L=8~\mu m$ ,  $W=16.000~\mu m$  and  $t_{ox}=300~nm$ . (HILLERINGMANN et al., 2011)