# Construção de um circuito de teste de uma biblioteca de células

Luís Henrique Reinicke<sup>1</sup>, Marcelo Soares Lubaszewski<sup>2</sup>

1 CEITEC S.A - Centro Nacional de Tecnologia Eletrônica Avançada S. A.

**ENG** - Engenharias

## INTRODUÇÃO

A abordagem *standard cell* é atualmente a mais utilizada para a construção de circuitos integrados digitais atualmente. Tal metodologia consiste em utilizar uma biblioteca de células elementares ou de baixa complexidade para a concepção de componentes mais elaborados. Este projeto visa construir um circuito a partir de uma metodologia eficiente proposta em [1] para testar o funcionamento das células combinacionais de uma biblioteca de células.

#### METODOLOGIA

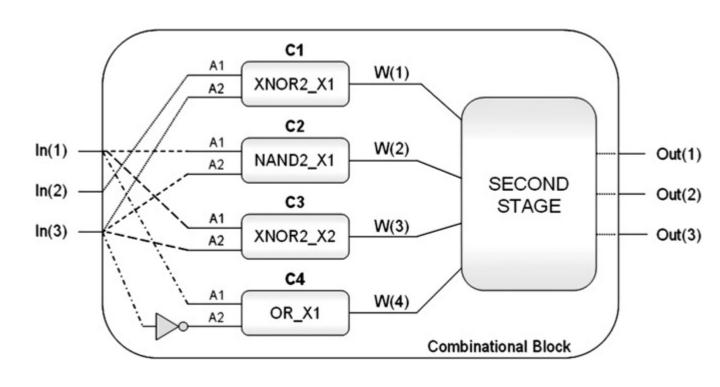

O circuito proposto possui uma parte combinacional, onde existe um número de uma estrutura que chamaremos de bloco combinaciomal. Cada bloco possui dois estágios. No primeiro estágio, estarão dispostas algumas das células da biblioteca, em paralelo, sendo alimentadas pelo sinal de entrada. No segundo estágio, existe uma lógica cujo objetivo é fazer com que a saída do bloco seja igual a entrada. Para isso, deve receber a saída do primeiro estágio(onde estão as células a ser testadas). Um exemplo de bloco combinacional pode ser visto na figura abaixo.

Figura 1. Bloco combinacional e seus dois estágios.

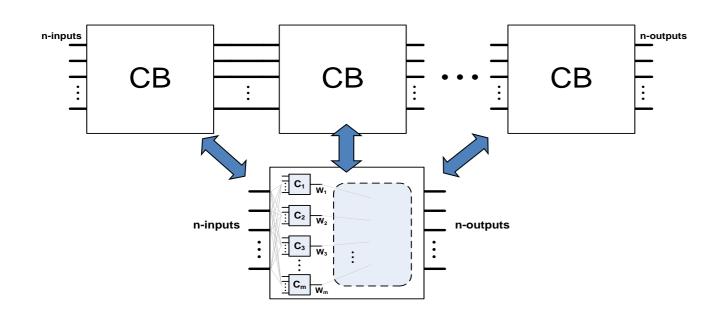

Assim, dispondo vários desses blocos em série, podemos reaproveitar os sinais de entrada e saída de cada bloco para testar o próximo bloco, pois esse sinal deve permanecer inalterado durante todo o processamento, como pode ser visto na figura abaixo.

Figura 2. Blocos combinacionais em série.

Inferimos que existe um problema com alguma(s) da(s) célula(s) da biblioteca se por ventura o sinal de saída da parte combinacional for diferentedo sinal de entrada. Esse mecanismo permite validar as células da bibliotecam para sequências específicas de bits.

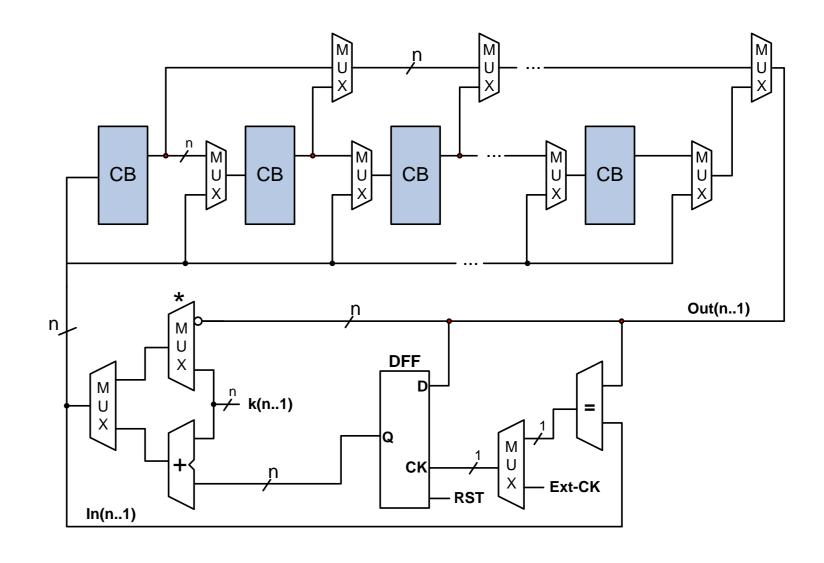

A segunda parte, de controle, consiste em um número de componentes (como um comparador para comparar entrada e saída, um conta dor para definir as sequências que irão à parte combinacional, e um número de multiplexadores e decodificadores) utilizados para alimentar a parte combinacional de acordo com a preferência do usuário e também escolher o modo de funcionamento. Pode-se ter uma ideia da disposição do circuito observando a figura abaixo.

Figura 3. Esquemático do circuito proposto.

#### RESULTADOS

Utilizando as ferramentas de síntese da *Cadence* disponibilizadas no CEITEC, foi possível realizar toda a parte de síntese lógica, restando a síntese física para que possa ser possível o envio do projeto para produção e teste. O objetivo do projeto é de realizar toda a síntese e possuir um circuito físico que possa ser testado afim de validar a metodologia proposta. Espera-se que o circuito possa ser enviado à produção no fim deste ano.

### REFERÊNCIAS

[1] R. P. Ribas, S. Bavaresco, N. Schuch, V. Callegaro, M. Lubaszewski and A. I. Reis, "Contributions to the evaluation of ensembles of combinational logic gates" Microelectronics Journal 42 (2011) 371–381