# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

# DÉBORA DA SILVA MOTTA MATOS

# Exploring Hierarchy, Adaptability and 3D in NoCs for the Next Generation of MPSoCs

Tese apresentada como requisito parcial para a obtenção do grau de Doutora em Ciência da Computação.

Advisor Prof. Dr. Altamiro Amadeu Susin

Co-advisor Prof. Dr. Luigi Carro

Porto Alegre 2014

# CIP – CATALOGAÇÃO NA PUBLICAÇÃO

Matos, Débora da Silva Motta

Exploring Hierarchy, Adaptability and 3D in NoCs for the Next Generation of MPSoCs [manuscrito] / Débora da Silva Motta Matos. – 2014.

200 f.:il.

Orientador: Altamiro Amadeu Susin; Co-orientador: Luigi Carro.

Tese (doutorado) — Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação. Porto Alegre, BR — RS, 2014.

1. Networks-on-Chip. 2. Hierarchical topology 3. Adaptability 4. Three dimensional NoCs 5. Hardware I. Susin, Altamiro Amadeu. II. Carro, Luigi. III. Exploring Hierarchy, Adaptability and 3D in NoCs for the Next Generation of MPSoCs.

# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos Alexandre Netto

Vice-Reitor: Prof. Rui Vicente Oppermann

Pró-Reitor de Pós-Graduação: Prof. Vladimir Pinheiro do Nascimento

Diretor do Instituto de Informática: Prof. Luís da Cunha Lamb

Coordenador do PPGC: Prof. Luigi Carro

Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

#### **AGRADECIMENTOS**

Inicio meus agradecimentos à pessoa mais especial em minha vida que me apoia e me incentiva todos os dias, que compreendeu os momentos em que precisamos ficar meses separados para que eu pudesse realizar colaborações com outras instituições de pesquisa que foram tão importantes para minha formação: meu amado esposo Cristiano. A ti um agradecimento especial, pela tua eterna compreensão em todos os momentos, pelo teu carinho e por aceitar e entender a minha "falta" que se tornaram uma constância na etapa final deste trabalho. Obrigada por fazer parte da minha vida!

Agradeço Àquele que está presente em todos os momentos da minha vida, guiando minhas atitudes e me dando forças: Deus.

Ao meu orientador, Prof. Altamiro Susin, que muito admiro pelo seu profissionalismo e amizade. Por sempre estar disponível quando precisei de uma orientação, de um apoio ou apenas de uma palavra amiga. Obrigada pela sua contribuição no desenvolvimento desse trabalho e por seu apoio constante ao longo de todos esses anos.

Ao meu co-orientandor, que também admiro bastante, Luigi Carro, que muito me incentivou durante esse período, me instigando a fazer sempre mais e melhor, a encontrar ideias inovadoras, a obter um diferencial e a pensar como uma cientista. Obrigada pela revisão de todos os meus trabalhos e artigos, pelas várias contribuições e incontáveis dicas. Obrigada pela compreensão e apoio em todos os momentos.

À minha mãe, Dulce, que é uma das responsáveis pela pessoa que sou e pelos valores e princípios que trago comigo, que sempre esteve disposta a me ajudar e compreender os meus momentos de ausência. Agradeço também a minha sogra, pela compreensão e por sempre se mostrar disposta a me ajudar com as demais tarefas para que me sobrasse mais tempo no desenvolvimento das minhas atividades acadêmicas.

Um forte agradecimento a minha amiga e colega Caroline Concatto, com quem realizei diversos trabalhos e publicações e que sempre esteve disposta a trocar uma ideia sobre a nossa pesquisa ou somente jogar conversa fora. Agradeço também a Anelise Kologeski pelas várias discussões de trabalho, pelo período em que dividimos apartamento em Milão e todos os lugares que descobrimos naquela época.

Agradeço também a todos os colegas do Lab215 e amigos que fiz no PPCG e PGMICRO, que ao longo desses 6 anos (mestrado e doutorado) foram muitos os que

por lá passaram, e sendo assim, abstenho-me de listar todos os nomes, pois certamente me esqueceria de alguém que, de um certo modo, participou das incontáveis conversas que tivemos, seja sobre a pesquisa, ou sobre assuntos aleatórios.

Alguns agradecimentos que foram realmente MUITO importantes para o trabalho específico da tese. Começo com o meu amigo Márcio Kreutz, que sempre esteve disponível para começarmos novas pesquisas e desenvolvermos novas ideias. Márcio, tu certamente sabes que essa tese só existe por causa da tua enorme ajuda em tantos resultados e análises que fizemos durante esse período. Obrigada pela colaboração em todos os artigos que escrevemos durante esse período. Que venham muito mais! Muito obrigada por tudo, por todas as conversas diárias. Admiro-te muito pela tua tranquilidade e otimismo, preciso aprender mais sobre isso contigo.

Outro agradecimento importante é ao Cezar Reinbrecht que também colaborou em muitas etapas desse trabalho, um trabalho que teve uma evolução bem interessante, sendo discutido e realizado passo-a-passo. Obrigada por confiar na minha pesquisa e nas minhas ideias. Agradeço ainda aos bolsistas de IC que tive durante esse período e que também colaboraram com esse trabalho: Rafael Leite, Paulo Cesar, Jonathan Martinelli e Tiago Motta. Esse último, além de meu irmão, contribuiu muito na obtenção dos últimos resultados. Agradeço-te pela tua compreensão nos últimos dois meses antes da defesa da tese.

Agradeço aos meus supervisores durante os estágios em Milão e Grenoble, Gianluca Palermos e Fabien Clermidy pelo grande aprendizado que obtive durante estas colaborações. Agradeço ainda aos demais professores do PPGC que contribuíram na minha formação: Fernanda Kastensmidt, Leila Ribeiro, Erika Cota, Sergio Bampi, dentre outros, e agradeço aos professores Cesar Zeferino, Monica Pereira e Flávio Wagner pelas importantes observações feitas sobre essa tese. Ao CNPq, agradeço por financiar meu período de estudos durante o doutorado.

Aos demais amigos e familiares que estão sempre torcendo por mim para que eu alcance meus objetivos e a todas as pessoas brilhantes que conheci desde que ingressei nesta Universidade: um muito obrigada!

# Explorando Hierarquia, Adaptabilidade e 3D em NoCs para a Próxima Geração de MPSoCs

#### **RESUMO**

A demanda por sistemas com elevado desempenho tem trazido a necessidade de aumentar o número de elementos de processamento, surgindo os chamados Sistemas em Chip Multiprocessados (MPSoCs). Além disso, com a possibilidade de redução da escala tecnológica na era submicrônica, permitindo a integração de vários dispositivos, os chips têm se tornado ainda mais complexos. No entanto, com o aumento no número de elementos de processamento, as interconexões são vistas com o principal gargalo dos sistemas-em-chip. Com isso, uma preocupação na forma como tais elementos se comunicam e estão interconectados tem sido levantada, uma vez que tais características são cruciais nos aspectos de desempenho, energia e potência, principalmente em sistemas embarcados. Essa necessidade permitiu o advento das redes-em-chip (Networks-on-Chip – NoCs) e inúmeros estudos já foram realizados para tais dispositivos. No entanto, devido ao aceleramento tecnológico atual, que traz a necessidade por sistemas ainda mais complexos, que consumam baixa energia e que permitam que as aplicações sejam constantemente atualizadas sem perder as características de desempenho, as arquiteturas de interconexão tradicionais não serão suficientes para satisfazer tais desafios. Outras alternativas de interconexão para MPSoCs precisam ser investigadas e nesse trabalho novas arquiteturas para NoCs com tais requisitos são apresentadas. As soluções propostas exploram hierarquia, adaptabilidade e interconexões em três dimensões. Esse trabalho aborda a necessidade do uso de diferentes estratégias em NoCs a fim de atingir os requisitos de desempenho e baixo consumo de potência dos atuais e futuros MPSoCs. Dessa forma, serão verificadas as diversas arquiteturas de interconexões para sistemas heterogêneos, sua escalabilidade, suas principais características e as vantagens das propostas apresentadas sobre as demais soluções.

**Palavras-Chave:** Rede-em-Chip, topologia hierárquica, crossbar, adaptabilidade, chaveamento, projetos 3D, interconexão 3D.

#### **ABSTRACT**

The demand for systems with high performance has brought the need to increase the number of cores, emerging the called Multi-Processors System-on-Chip (MPSoCs). Also, with the shrinking feature size in deep-submicron era, allowing the integration of several devices, chips have become even more complex. However, with the increase in these elements, interconnections are seen as the main bottleneck in many core systemson-chip. With this, a concern about how these devices communicate and are interconnected has been raised, since these features are crucial for the performance, energy and power consumption aspects, mainly in embedded systems. This need allows the advent of the Networks-on-Chip (NoCs) and countless studies had already been done to analyze such interconnection devices. However, due to the current technological accelerating that brings the need for even more complex systems, consuming lower energy and providing constant application updates without losing performance features, traditional interconnect architectures will not be sufficient to satisfy such challenges. Other interconnecting alternatives for MPSoCs need to be investigated and in this work, novel architectures for NoCs meeting such requirements are presented. The proposed solutions explore hierarchy, adaptability and three dimensional interconnections. This work approaches the requirements in the use of different strategies for NoCs in order to reach the performance requisites and low power consumption of the current and future MPSoCs. Hence, in this approach, several interconnection architectures for heterogeneous systems, their scalability and the main features and advantages of the proposed strategies in comparison with others will be verified.

**Keywords:** Network-on-chip, hierarchical topology, crossbar, adaptability, switching, 3D designs, 3D interconnects.

# LIST OF FIGURES

| Figure 1.1 - Trend f number of PEs for SoC Consumer Portable Design Complexity.                    |     |

|----------------------------------------------------------------------------------------------------|-----|

| Figure 1.2 - (a) Example of Clock Skew and (b) Jitter                                              |     |

| Figure 1.3 – (a) VOPD and (b) MPEG benchmarks with the communication core grap                     |     |

|                                                                                                    |     |

| Figure 1.4 - Example of cores in an MPSoC.                                                         |     |

| Figure 2.1 - Example of point-to-point interconnection.                                            | 30  |

| Figure 2.2 - (a) Example of system interconnected by Intel QuickPath and (b) its architecture.     | 38  |

| Figure 2.3 - Example of a system interconnected by a shared bus                                    |     |

|                                                                                                    |     |

| Figure 2.4 - Hierarchical AMBA bus architecture.                                                   |     |

| Figure 2.5 - IBM Cell ring bus communication architecture.                                         |     |

| Figure 2.6 – SH Mobile G1 hierarchical bus communication architecture.                             |     |

| Figure 2.7 - Example of a full bus crossbar.                                                       |     |

| Figure 2.8 - Crossbar architecture: wires, multiplexers and arbiters.                              | 43  |

| Figure 2.9 - Example of maximum wire length according to the number of PEs                         |     |

| interconnected by a crossbar                                                                       |     |

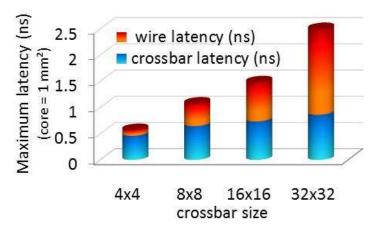

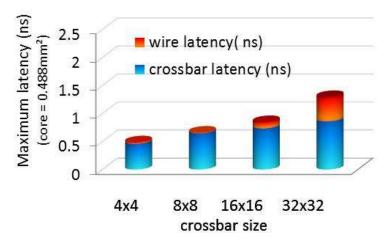

| Figure 2.10 - Maximum latency according to the crossbar size considering cores with                |     |

|                                                                                                    |     |

| Figure 2.11 - Maximum latency according to the crossbar size considering cores with                |     |

| area of 0.488mm <sup>2</sup> .                                                                     |     |

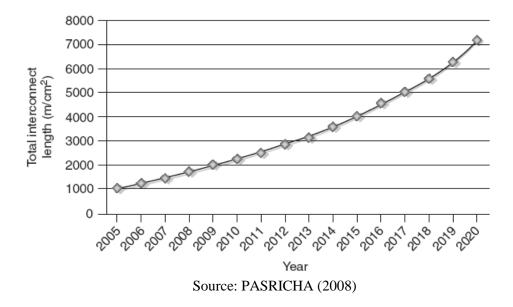

| Figure 2.12 - Trend of total interconnection length on a chip.                                     |     |

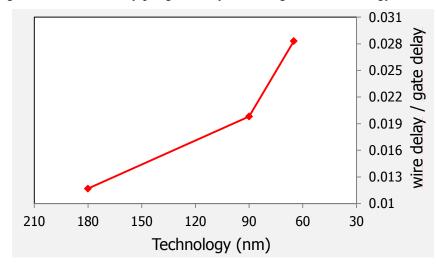

| Figure 2.13 - Wire delay per gate delay according to the technology scale                          |     |

| Source: elaborated by the author.                                                                  | 48  |

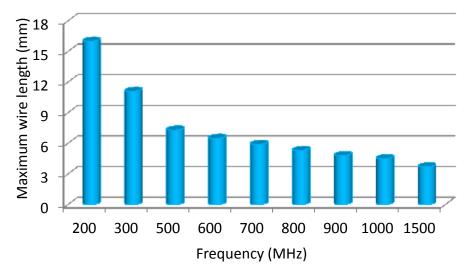

| Figure 2.14 - Maximum wire length at every frequency.                                              | 48  |

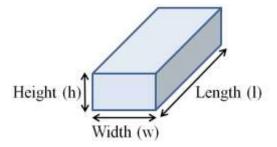

| Figure 2.15 - Wire dimensions for an integrated circuit                                            | 49  |

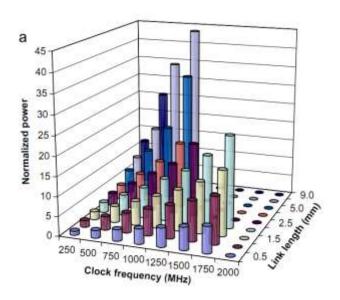

| Figure 2.16 - Power consumption at different link lengths and operating frequencies                | 49  |

| Figure 2.17 - Reasons that point out to the network-on-chip.                                       | 50  |

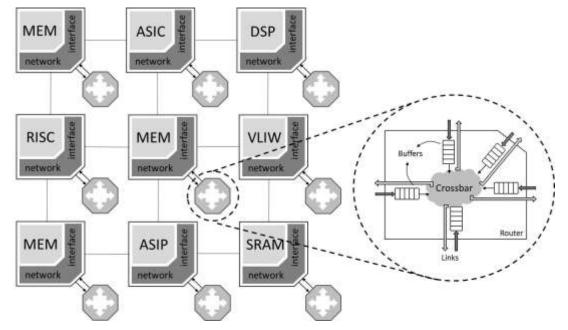

| Figure 2.18 - Example of a 3x3 NoC and the parts that constitute it                                | 52  |

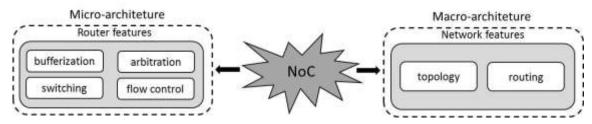

| Figure 2.19 - High-level overview of the NoC designs                                               | 53  |

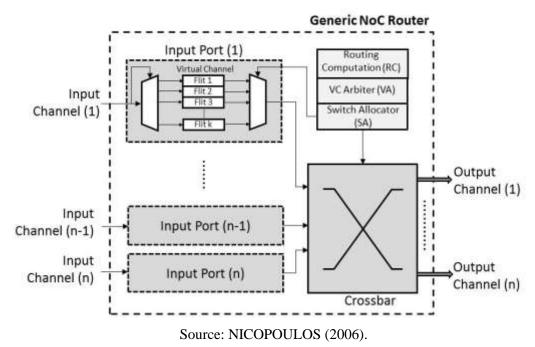

| Figure 2.20 - NoC router with virtual channel strategy                                             | 53  |

| Figure 2.21- Examples of NoC topologies: (a) 2D mesh, (b) torus, (c) fat tree, (d) ring            | ŗ,  |

| (e) hypercube.                                                                                     | 56  |

| Figure 2.22 - Example of ideal irregular topology for an application specific                      | 57  |

| Figure 2.23 - Examples of routing algorithms and their routes to send a message from               |     |

| node A to node B.                                                                                  |     |

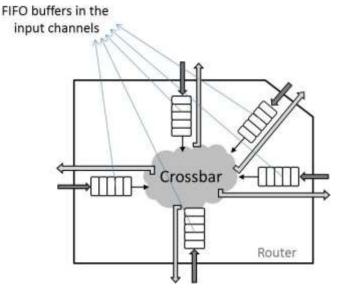

| Figure 2.24 - Example of FIFOs in the input channels of a router                                   | 62  |

| Figure 3.1 - An example of HiNoC topology.                                                         |     |

| Figure 3.2 - (a) CrossRing, (b) CrossTorus, (c) MultiCross topologies                              |     |

| Figure 3.3 - An example of HrNoC architecture.                                                     |     |

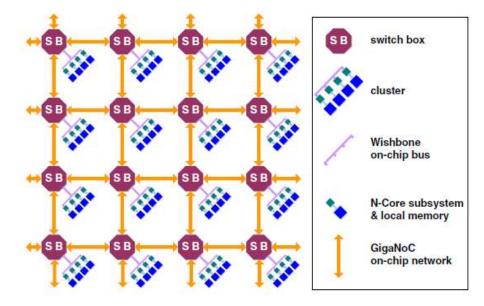

| Figure 3.4 - GigaNoC topology.                                                                     |     |

| Figure 3.5 - (a) Concentrated mesh, (b) flattened butterfly and (c) hybrid topology                |     |

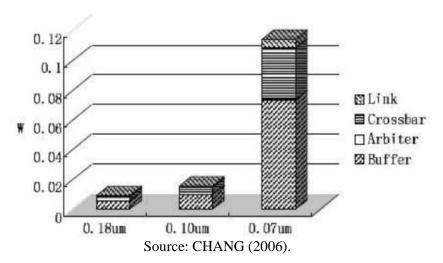

| Figure 3.6 - Power consumption of each part of the router.                                         |     |

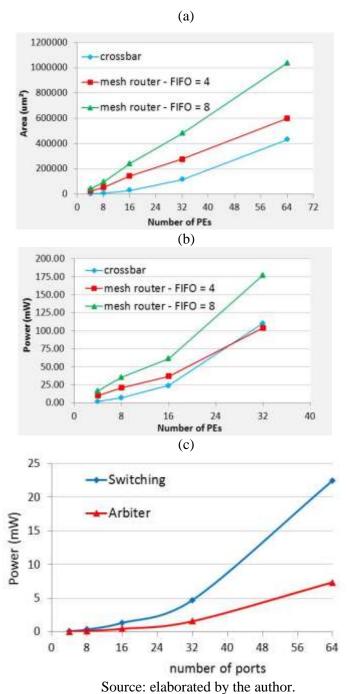

| Figure 3.7- (a) Area and (b) power consumption analyses for crossbars. (c) Power                   | , 1 |

| consumption for the parts of a crossbar.                                                           | 75  |

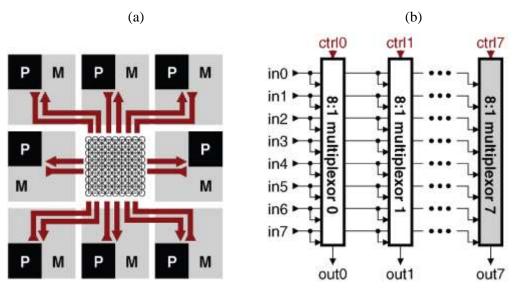

| Figure 3.8 - (a) Matrix using centralized crossbar where <i>Ps</i> denote processors and <i>Ms</i> |     |

| memories. (b) bit slices (1-bit radix-8 crossbar)                                                  |     |

| 111011101100. (0) UIL 011000 (1 UIL 1441A U 01000UAI)                                              | , 0 |

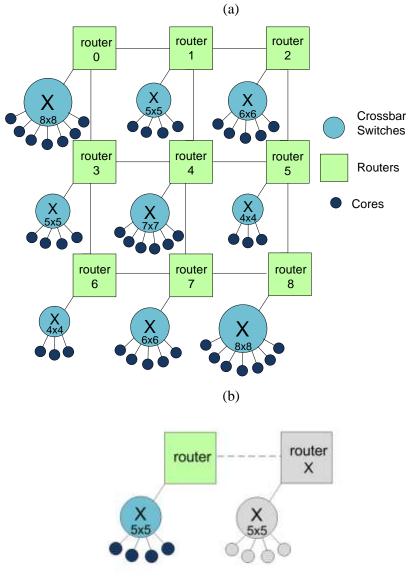

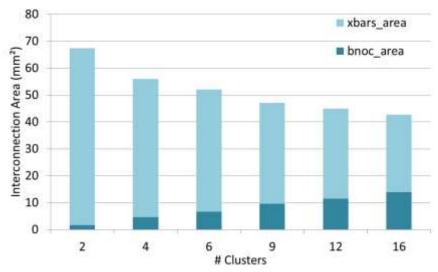

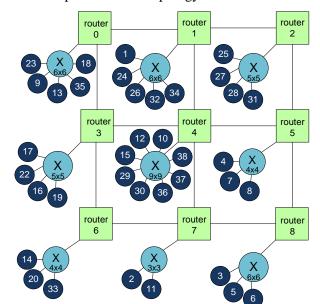

| Figure 3.9 - (a) Example of HiCIT architecture. (b) Scalability of the proposed topology                  |

|-----------------------------------------------------------------------------------------------------------|

| is reached increasing the set of router + crossbar                                                        |

| Figure 3.10 - HiCIT architecture composed of a crossbar switch on the local level and a                   |

| mesh router in the global level                                                                           |

| Figure 3.11 – State machine to control the data transfer of the crossbar switch 80                        |

| Figure 3.12 – Packet format of the HiCIT architecture. 82                                                 |

| Figure 3.13 - Two levels of HiCIT architecture and the bridges used to interconnect                       |

| them                                                                                                      |

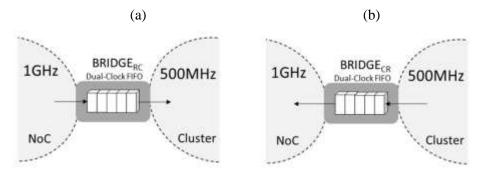

| Figure 3.14 - Example of the use of a Dual-clock FIFO for reading and writing from                        |

| NoC and cluster with different operating frequency. (a) Bridge <sub>RC</sub> , (b)Bridge <sub>CR</sub> 84 |

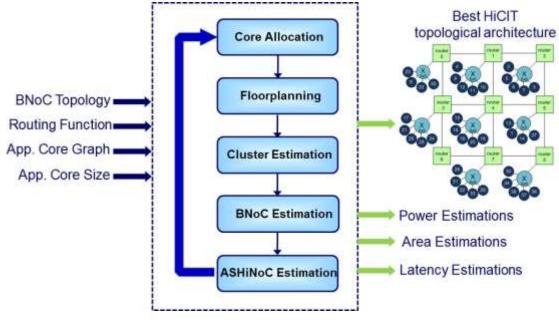

| Figure 3.15 - ASHiNoC analyzer framework                                                                  |

| Figure 3.16 - Number of crossbar 2:1 MUXES according to the number of input ports.                        |

| 90                                                                                                        |

| Figure 3.17 - Critical path for each crossbar size defined to estimate the crossbar delay.                |

| 91                                                                                                        |

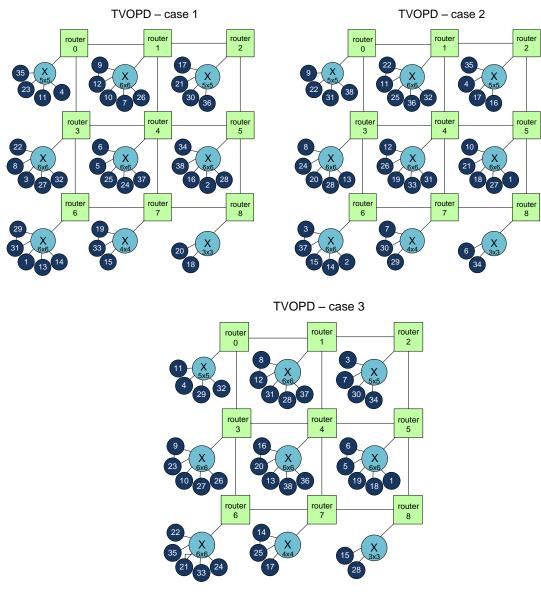

| Figure 3.18 - TVOPD core graph. 94                                                                        |

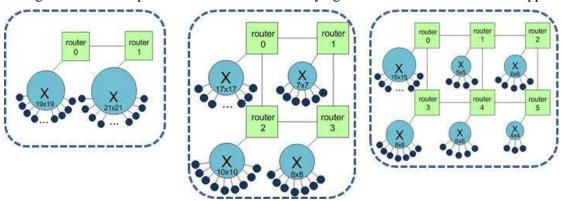

| Figure 3.19 - Example of HiCIT architectures varying the crossbar size for the same                       |

| application                                                                                               |

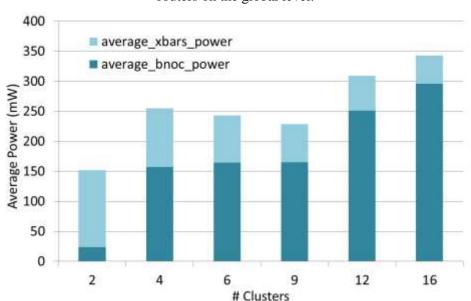

| Figure 3.20 - HiCIT interconnection average power for the best configuration, varying                     |

| the number of routers on the global level96                                                               |

| Figure 3.21- HiCIT interconnection area and for the best configuration, varying the                       |

| number of routers on the global level                                                                     |

| Figure 3.22 - HiCIT interconnection average Latency for the best configuration, varying                   |

| the number of routers on the global level                                                                 |

| Figure 3.23 - The Optimal HiCIT topology for TVOPD with 9 clusters                                        |

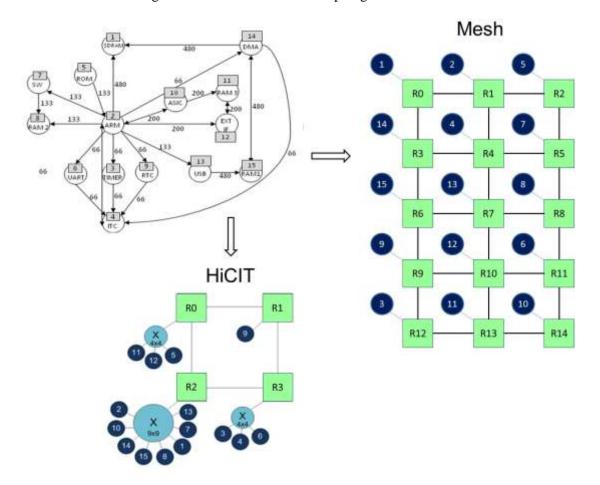

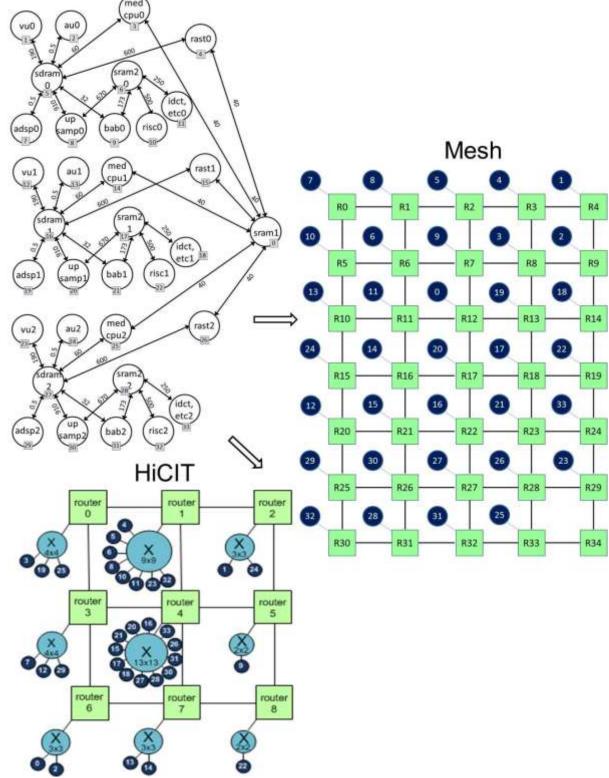

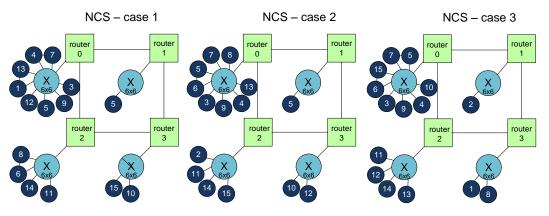

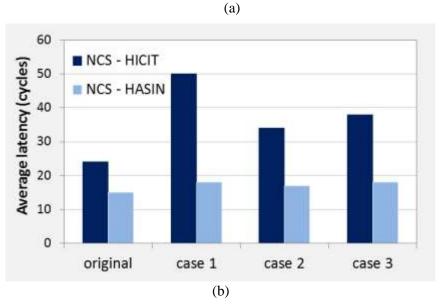

| Figure 3.24 - Mesh and HiCIT topologies for NCS benchmark                                                 |

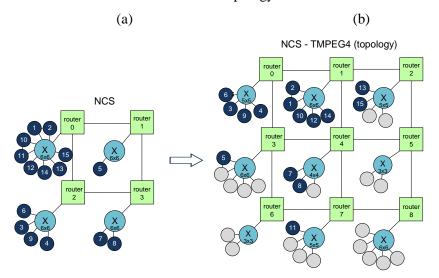

| Figure 3.25 – Mesh and HiCIT topologies for TMPEG4 benchmark                                              |

| Source: elaborated by the author. 101                                                                     |

| Figure 3.26 - Mesh topology for TVOPD benchmark                                                           |

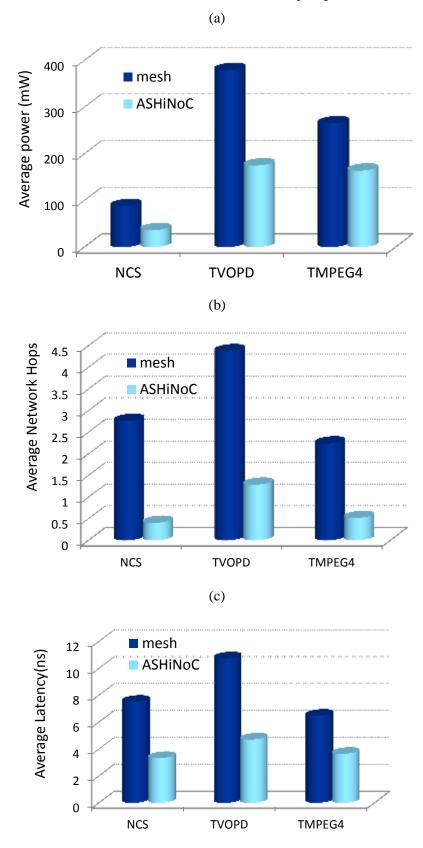

| Figure 3.27 - (a) Average power, (b) average network hops and (c) average latency for                     |

| NCS, TVOPD and TMPEG4 in the HiCIT and mesh topologies                                                    |

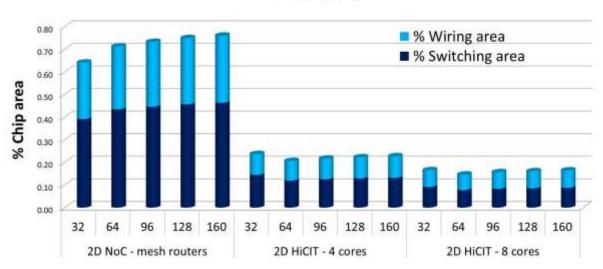

| Figure 3.28: (a) Area and (b) power consumption when the number of PEs increases.                         |

|                                                                                                           |

| Figure 3.29 - HiCIT power consumption divided in wires and cells                                          |

| Figure 3.30 - Percentage of SoC occupied by the interconnection topologies with the                       |

| total area divided in wires and cells                                                                     |

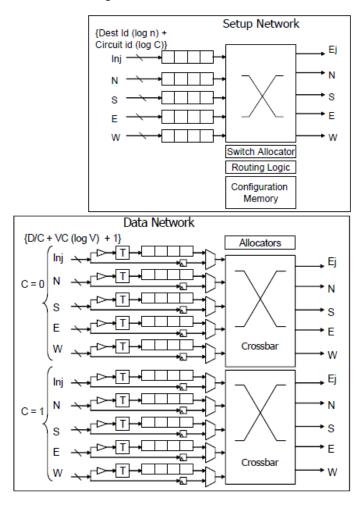

| Figure 4.1 - HCS architecture                                                                             |

| Figure 4.2 - (a) VIP architecture, (b) pipeline stages in the packet-switching mode, (c)                  |

| pipeline stages in the circuit-switching mode                                                             |

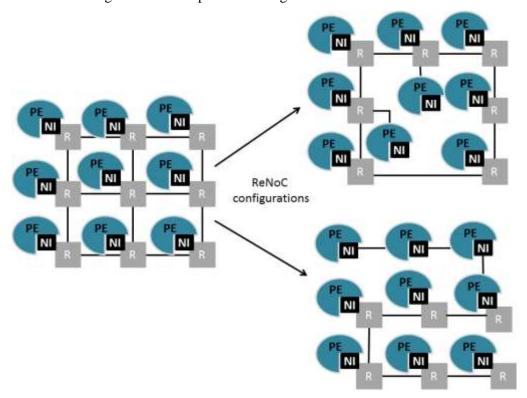

| Figure 4.3 – ReNoC architecture router with the proposed multiplexers 116                                 |

| Figure 4.4 – Two possible configurations from ReNoC architecture                                          |

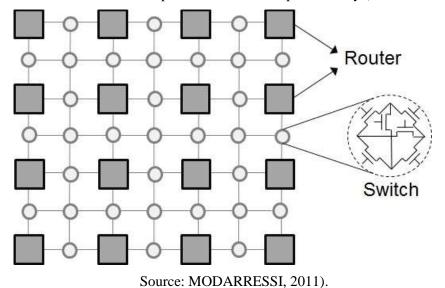

| Figure 4.5 – Use of switch box to compose the architecture presented by                                   |

| (MODARRESSI, 2011)                                                                                        |

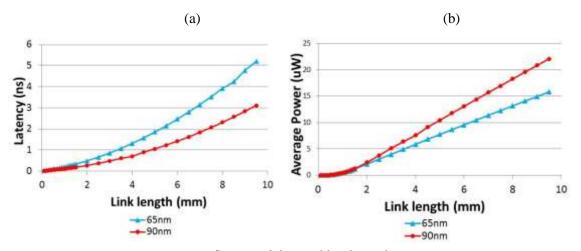

| Figure 4.6 - (a) Latency and (b) Average power consumption considering the wire                           |

| length for 65nm and 90nm                                                                                  |

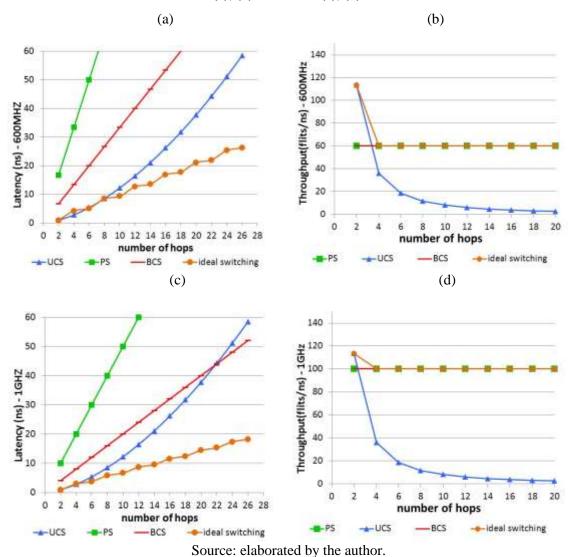

| Figure 4.7 - Latency and throughput results considering different switching possibilities                 |

| for 600MHz (a), (b) and 1GHz (c), (d)                                                                     |

| Figure 4.8 - Wire length adopted for the experiments for circuit switching mode 123                       |

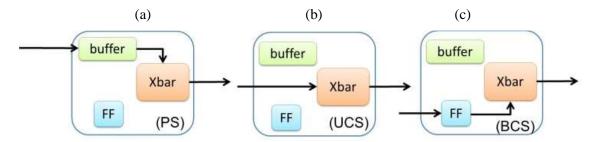

| Figure 4.9 - Three switching configuration possibilities: (a) packet switching, (b)    |     |

|----------------------------------------------------------------------------------------|-----|

| unbuffered circuit switching and (c) buffered circuit switching.                       | 123 |

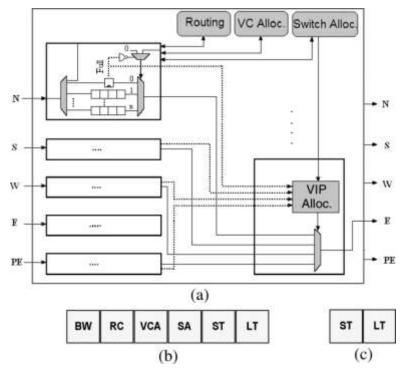

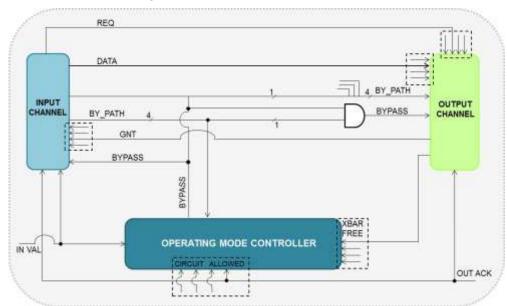

| Figure 4.10 - MINoC router architecture.                                               | 124 |

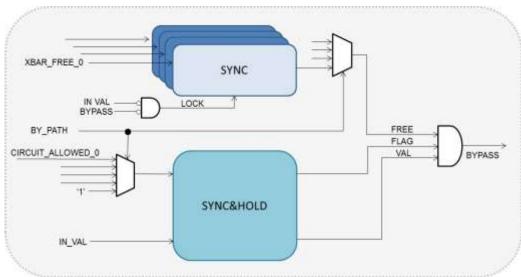

| Figure 4.11 - Operation Mode Controller Architecture                                   | 125 |

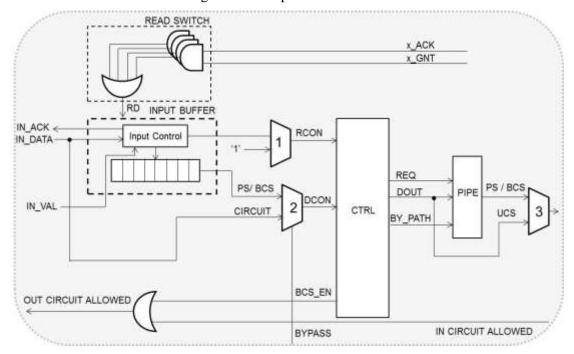

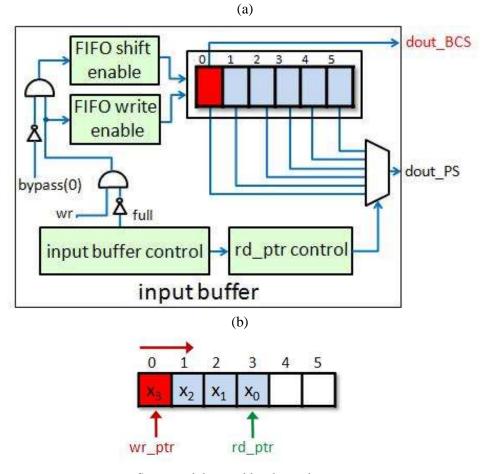

| Figure 4.12 - Input Channel architecture.                                              | 126 |

| Figure 4.13 - (a) Input buffer architecture and the (b) buffer and its pointers        | 127 |

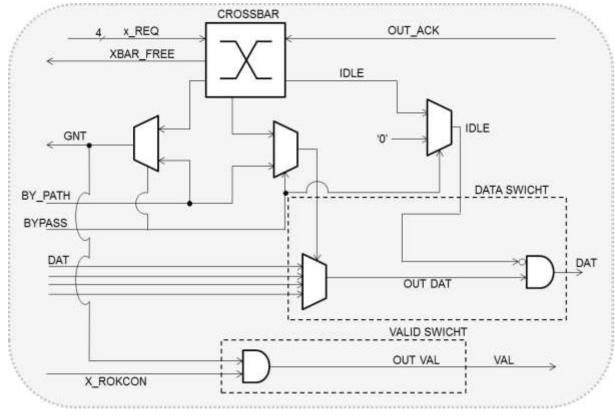

| Figure 4.14 - Output Channel architecture.                                             |     |

| Figure 4.15 - Example of MINoC configurations.                                         | 129 |

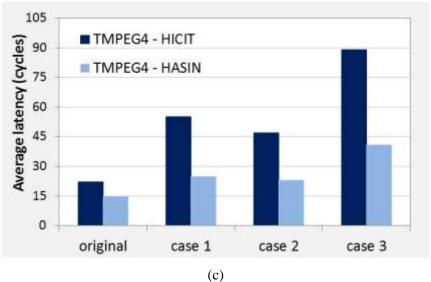

| Figure 4.16 - Average latency results for MINoC in comparison with a conventional      |     |

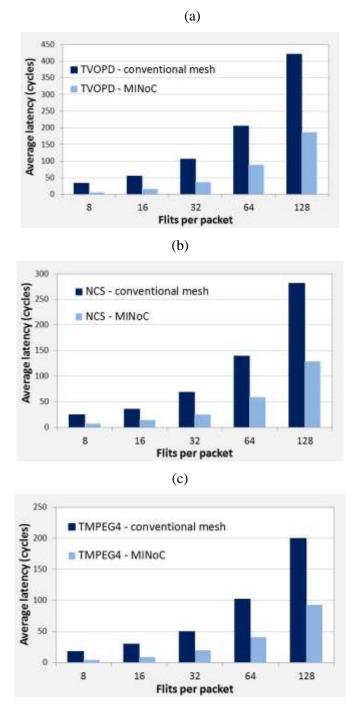

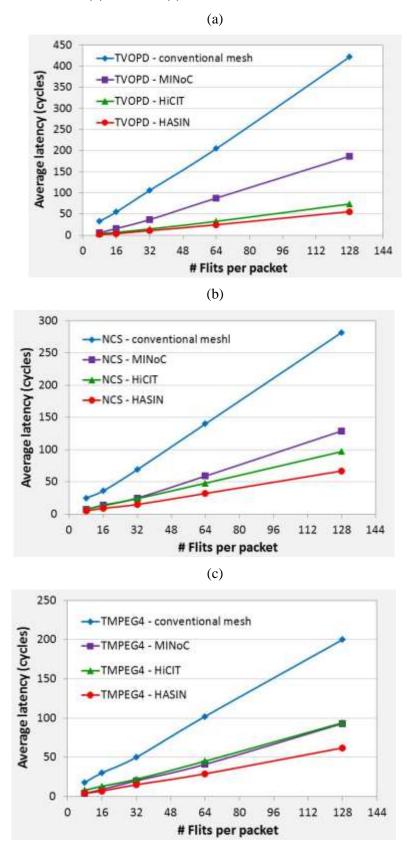

| packet switching router for (a) TVOPD, (b) NCS and (c) TMPEG4 benchmarks               | 132 |

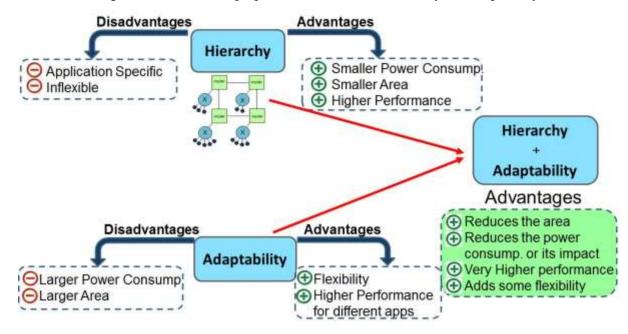

| Figure 5.1 - Ideal NoC proposal is obtained with hierarchy and adaptability            |     |

| Figure 5.2 – Mapping for HiCIT topology for TVOPD benchmark                            | 138 |

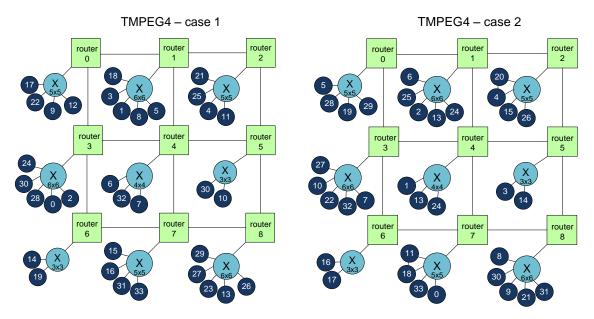

| Figure 5.3 - Mapping for HiCIT topology for TMPEG4 benchmark                           | 138 |

| Figure 5.4 – Mapping for HiCIT topology for NCS benchmark                              | 139 |

| Figure 5.5 - Average latency results for HASIN in comparison with other strategies for | or  |

| (a) TVOPD, (b) NCS and (c) TMPEG4 benchmarks.                                          | 141 |

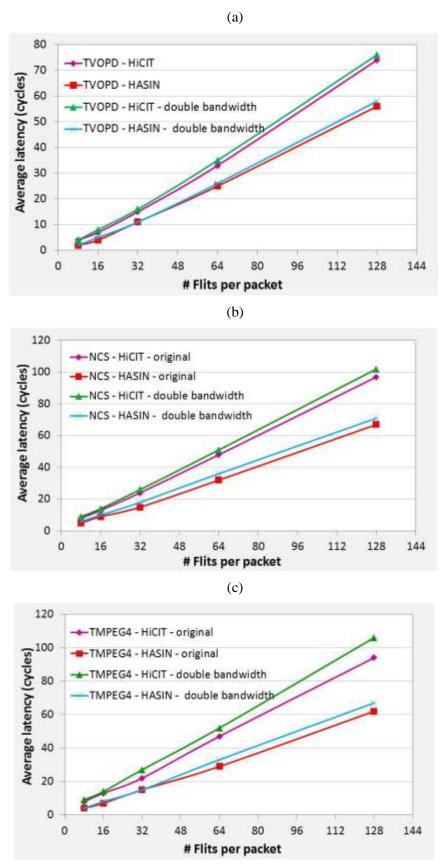

| Figure 5.6 - Average latency results for HASIN, HiCIT and MINoC when the               |     |

| bandwidths are changed for (a) TVOPD, (b) NCS and (c) TMPEG4 benchmarks                | 144 |

| Figure 5.7 - Three random mappings for HiCIT topology for TMPEG4 benchmark             | 145 |

| Figure 5.8 – Three random mappings for HiCIT topology for TVOPD benchmark              | 146 |

| Figure 5.9 - Three random mappings for HiCIT topology for NCS benchmark                | 146 |

| Figure 5.10 - Results for HiCIT and HASIN topologies for random mappings for (a)       |     |

| NCS, (b) TMPEG4 and (c) TVOPD benchmarks.                                              | 148 |

| Figure 5.11 - Core graph of D26 benchmark                                              | 150 |

| Figure 5.12 – Core graph of AV benchmark.                                              | 150 |

| Figure 5.13 – (a) original mapping and (b) the mapping adapted for D26 benchmark       |     |

| from TMPEG4 topology                                                                   |     |

| Figure 5.14 - (a) original mapping and (b) the mapping adapted for AV benchmark from   |     |

| the D26 topology.                                                                      | 151 |

| Figure 5.15 - (a) original mapping and (b) the mapping adapted for NCS benchmark       |     |

| from the TMPEG4 topology.                                                              | 151 |

| Figure 5.16 - Benchmarks mapped for topologies designed for other applications: (a)    |     |

| D26, (b) AV and (c) NCS                                                                |     |

| Figure 5.17 - (a) Power Consumption and (b) area results for different interconnection |     |

| strategies for the NCS and TVOPD benchmarks.                                           |     |

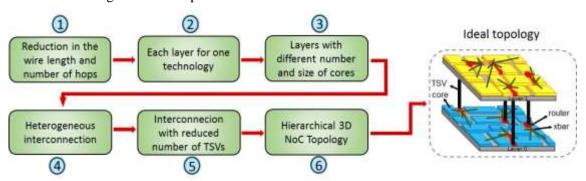

| Figure 6.1 - Six points which led the ideal interconnection solution.                  |     |

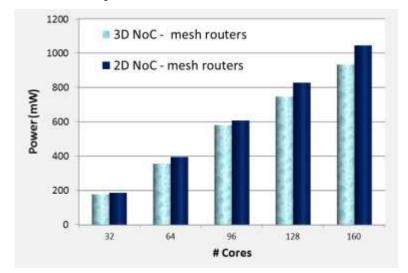

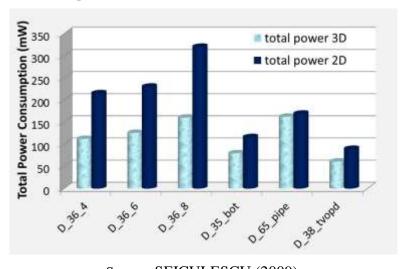

| Figure 6.3 - Comparison between 2D and 3D NoCs for different benchmarks                |     |

| Figure 6.4 - Example of specific technologies for each layer of a 3D integration       |     |

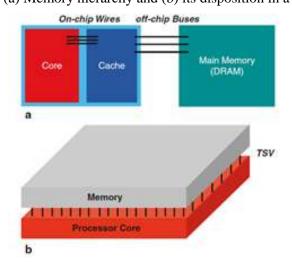

| Figure 6.5 - (a) Memory hierarchy and (b) its disposition in a 3DIC.                   |     |

| Figure 6.6 - 3D floorplan for D26 benchmark.                                           |     |

| Figure 6.7 - 3D floorplan for TVOPD benchmark.                                         |     |

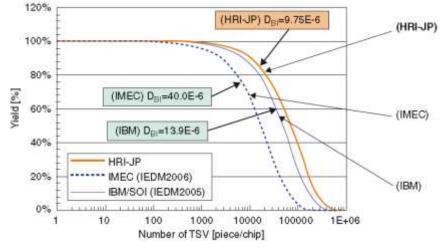

| Figure 6.8 - Number of TSVs x Yield.                                                   | 164 |

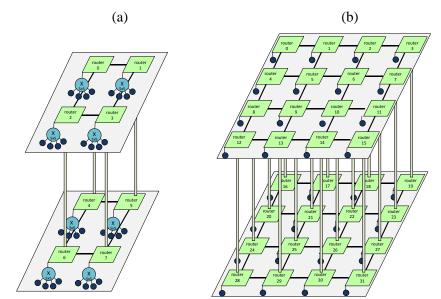

| Figure 6.9 - A comparison related to the number of pillars required for a (a)          | 1   |

| conventional 3D mesh topology and (b) the proposed hierarchical 3D topology            |     |

| Figure 6.10 - 3D-HiCIT architecture.                                                   |     |

| Figure 6.11 - 3D-HiCIT architecture.                                                   |     |

| Figure 6.12 - Example of (a) 3D-HiCIT and (b) 3D-mesh topologies for 32 PEs            |     |

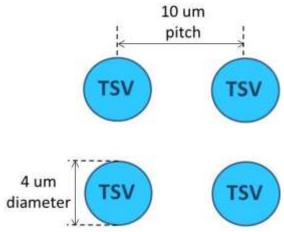

| Figure 6.13 - TSV characteristics.                                                     |     |

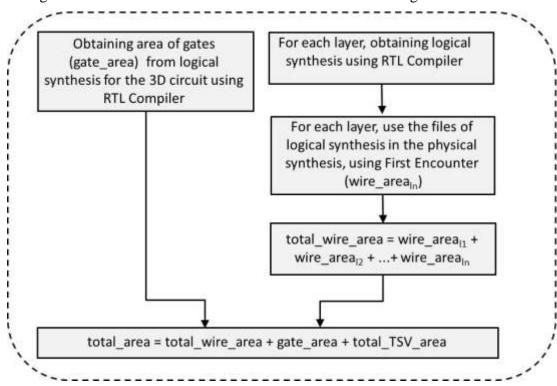

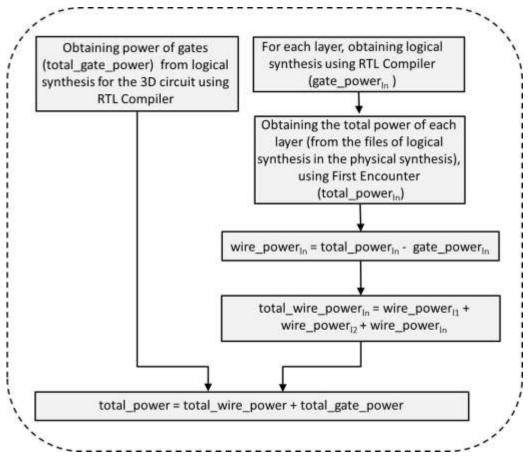

| Figure 6.15 - Flow chart to estimate the power for the 3D designs.                     | 1/0 |

|                                                                                        |     |

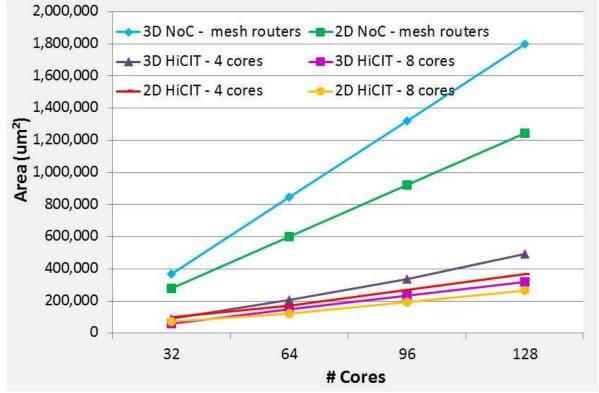

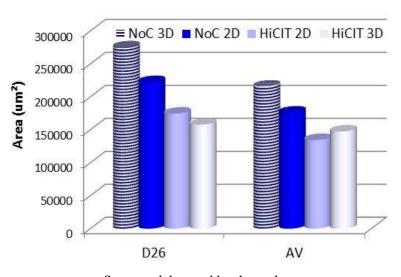

| Figure 6.16 - Area estimation comparing HiCIT and mesh topologies              | 173     |

|--------------------------------------------------------------------------------|---------|

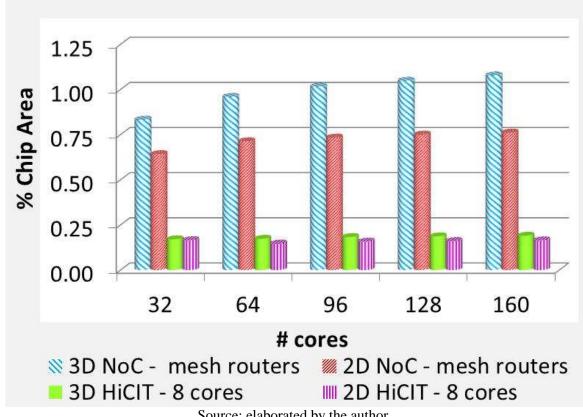

| Figure 6.17 - Percentage of chip area for each NoC topology                    | 174     |

| Figure 6.18 - Percentage of chip area for wiring, switching and TSVs           | 174     |

| Figure 6.20 - Mapping for AV benchmark for (a) 3D-mesh and (b) 3D-HiCIT        |         |

| topologies                                                                     | 176     |

| Figure 6.21 - Mapping for D26 benchmark for (a) 3D mesh and (b) 3D-HiCIT       |         |

| topologies                                                                     | 176     |

| Figure 6.22 - Area results for D26 and AV benchmarks comparing mesh and HiC    | IT      |

| topologies                                                                     | 177     |

| Figure 6.23 - Power Consumption for D26 and AV benchmarks comparing mesh       | and     |

| HiCIT topologies                                                               | 178     |

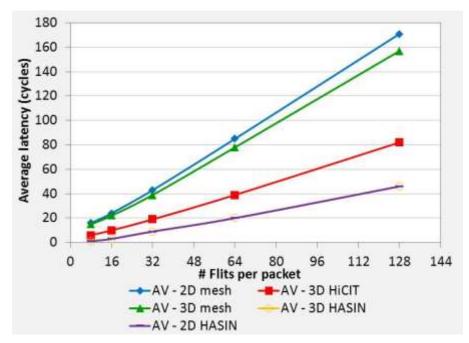

| Figure 6.24 - Average latency comparisons considering mesh and HiCIT topologic | ies for |

| D26 benchmark                                                                  | 179     |

| Figure 6.25 - Average latency comparisons considering mesh and HiCIT topologi  | es for  |

| D26 benchmark                                                                  | 179     |

| Figure 7.1 - Strategies approached in this work.                               | 183     |

# LIST OF TABLES

| Table 1.1 - Current challenges presented in section 1.1 for interconnected designs of |      |

|---------------------------------------------------------------------------------------|------|

| MPSoCs and the related solutions considered in this work                              | . 30 |

| Table 2.2 - Bus, crossbar and mesh NoC architectures                                  | . 63 |

| Table 3.1 - Resume of the hierarchical proposals found in the literature              | . 72 |

| Table 3.2 - Synthesis results for the synchronizer module considering two frequency   |      |

| possibilities                                                                         | . 84 |

| Table 3.3 - Physical information of TVOPD cores.                                      |      |

| Table 3.4 - Results for the best configuration for TVOPD benchmark                    | . 99 |

| Table 3.5 - Physical information of NCS cores.                                        |      |

| Table 3.6 - Physical information of TMPEG4 cores.                                     | 104  |

| Table 3.7 - Reduction in power, NoC hops and latency with the use of HiCIT when       |      |

| compared to a flat mesh topology.                                                     |      |

| Table 4.1- Comparison among the adaptive strategies related to the switching          | 118  |

| Table 4.2 - Synthesis results for MINoC proposal compared to a conventional router    |      |

| NCS and TVOPD benchmarks.                                                             |      |

| Table 5.1 - TVOPD benchmark core descriptions.                                        |      |

| Table 5.2 - TMPEG4 benchmark core descriptions.                                       |      |

| Table 5.3 - NCS benchmark core descriptions.                                          |      |

| Table 5.4 - AV benchmark core descriptions.                                           |      |

| Table 5.5 - D26 benchmark core descriptions.                                          |      |

| Table 5.6 - Power Consumption and Area reductions obtained for the NCS and TVOI       |      |

| applications with HASIN strategy.                                                     | 154  |

| Table 5.7 - Latency parity for HiCIT operating at 1GHz and HASIN operating at         |      |

| 500MHz.                                                                               |      |

| Table 6.1 - Topology, NoC size and number of cores defined in the experiments         |      |

| Table 6.2 - Physical information of AV cores.                                         |      |

| Table 7.1 - Solutions for each challenge and the related publications.                | 186  |

#### **ABBREVIATIONS**

2D Two Dimensional 3D Three Dimensional

3DIC Three Dimensional Integrated Circuit AHB Advanced High-performance Bus

AMBA Advanced Microcontroller Bus Architecture

APB Advanced Peripheral Bus

**ASIC** Application-Specific Integrated Circuit **ASHiNoC** Application Specific Hierarchical NoC

ΑV Audio Video

**BCS Buffered Circuit Switching**

**BIST** Built-In Self-Test **BNoC** Backbone NoC bop begin-of-packet

**CMP** Chip Multi-Processor **CPU** Central Processing Unit

CS Circuit Switching

Cu Copper

Dynamically Allocated Multi-Queue **DAMQ**

DBI Direct Bond Interconnect DPE **Data Processing Engines DSE Design Space Exploration**

end-of-packet eop

**EVC Express Virtual Channel**

PE **Processing Element**

**FCFS** First-Come, First-Served

FF Flip-Flop

**FIFO** First-In First-Out

**FPGA** Field-Programmable Gate Array

**GALS** Globally Asynchronous Locally Synchronous

**HASIN** Hierarchical Adaptive Switching Interconnection NoC **HiCIT**

Hierarchical Crossbar-based Interconnection Topology

**HCS Hybrid Circuit Switching**  IC Integrated Circuit

ID Identification Number

IEDM International Electron Device Meeting

IL Ideal Latency

IoC In-order-Core

IP Intellectual Property

ITRS International Technology Roadmap for Semiconductors

LLC Long Link Controller

LRS Least Recently Served

MINoC Multi Interconnections Network-on-Chip

MPEG Motion Picture Experts Group

MPSoC Multiprocessor SoC

MUX Multiplexers

NI Network Interface NoC Network-on-Chip

NCS Network Communication Subsystem

OoC Out-of-Order

PS Packet Switching

QoS Quality-of-Service

QPI Quick Path Interconnect

RASoC Router Architecture for System-on-Chip

RC Routing Computation

ReNoC Reconfigurable NoC

RISC Reduced Instruction Set Computer

RLC Resistance, Inductance, Capacitance

RR Round Robin

SA Switch Allocator SAF Store-and-Forward

SAFC Statically Allocated, Fully Connected

SAMQ Statically Allocated Multi-Queue

SoC System-on-Chip

SoCIN System-on-Chip Interconnection Network

TMEPG4 Triple MEPG4

TS Topology Switch

TVOPD Triple Video Objective Plane Decoder

UCS Unbuffered Circuit Switching

UFRGS Universidade Federal do Rio Grande do Sul

VA Virtual Channel Arbiter

VC Virtual Channel

VCT Virtual Cut-Through

VHDL VHSIC Hardware Description Language

VHSI Very High Speed Integrated Circuit

VIP Virtual Point-to-Point

VLIW Very Long Instruction Word

VLSI Very Large Scale Integration

WH Wormhole

Xbar Crossbar

# **TABLE OF CONTENTS**

| RESUMO                                                                                               | 25        |

|------------------------------------------------------------------------------------------------------|-----------|

| ABSTRACT                                                                                             | 27        |

| LIST OF FIGURES                                                                                      | 29        |

| LIST OF TABLES                                                                                       | 33        |

| ABBREVIATIONS                                                                                        | 35        |

| 1 INTRODUÇÃO                                                                                         | 23        |

| 1.1 Problem Description                                                                              |           |

| 1.2 Motivation and Work Context                                                                      |           |

| 1.3 Goals and Contributions                                                                          |           |

| 1.4 Organization                                                                                     | 32        |

| 2 SYSTEMS, COMMUNICATIONS AND THEIR INTERCONNECTIONS                                                 | 35        |

| 2.1 Communication Characterization                                                                   |           |

| 2.2 Before the NoCs                                                                                  |           |

| 2.2.1 Point-to-point interconnection                                                                 |           |

| 2.2.2 Buses                                                                                          |           |

| 2.3 The need for other alternatives to interconnect systems-on-chip                                  |           |

| 2.3.1 The impact of wires on the interconnections                                                    |           |

| 2.4 Networks-on-Chip: interconnection model for complex systems                                      |           |

| 2.4.1 Router                                                                                         |           |

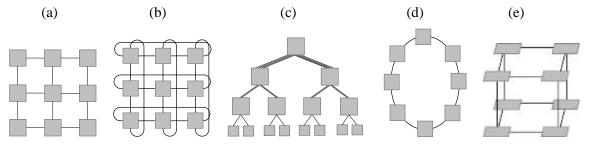

| 2.4.2 Topology                                                                                       |           |

| a) Direct Networks                                                                                   |           |

| b) Indirect Networks                                                                                 | 56        |

| c) Irregular Networks                                                                                | 56        |

| d) Hierarchical Networks                                                                             | 57        |

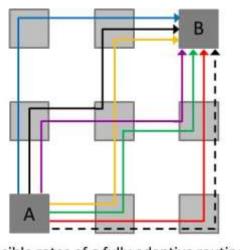

| 2.4.3 Routing                                                                                        | <b>58</b> |

| 2.4.4 Switching                                                                                      |           |

| 2.4.5 Bufferization                                                                                  |           |

| 2.4.6 Arbitration                                                                                    |           |

| 2.4.7 Flow Control                                                                                   |           |

| <ul><li>2.5 Comparison between the main interconnection devices</li><li>2.6 Considerations</li></ul> |           |

| 3 2D HIERARCHICAL NETWORKS-ON-CHIP                                                                   |           |

| 3.1 State of the art 2D hierarchical NoCs                                                            |           |

| 3.2 HiCIT topology                                                                                   |           |

| 3.2.1 Local level architecture                                                                       |           |

| 3.2.2 Global level architecture                                                                      |           |

| 3.2.3 Bridge architecture                                                                            |           |

| 3.3 ASHiNoC tool                                                                                     |           |

| 3.3.1 Problem Formulation                                                                            |           |

| 3.3.2 Overview of the application specific methodology                                               | 88        |

| 3.4 Results                                                                                          |           |

| 3.4.1 | ASHiNoC tool results                                                  | 93  |

|-------|-----------------------------------------------------------------------|-----|

| 3.4.2 | Synthesis results                                                     | 106 |

| 3.5   | Considerations                                                        | 109 |

| 4 A   | DAPTIVE NETWORKS-ON-CHIP                                              | 111 |

| 4.1   | State of the art adaptive switching NoCs                              | 112 |

| 4.2   | Switching Strategic analysis                                          |     |

| 4.3   | MINoC architecture: an adaptive NoC                                   |     |

| 4.3.1 | 1 6                                                                   |     |

| 4.3.2 | 1                                                                     |     |

| 4.3.3 | 1                                                                     |     |

| 4.3.4 | $\mathcal{E}$                                                         |     |

|       | MINoC Results                                                         |     |

| 4.4.1 |                                                                       |     |

| 4.4.2 | •                                                                     |     |

| 4.5   | Considerations                                                        | 134 |

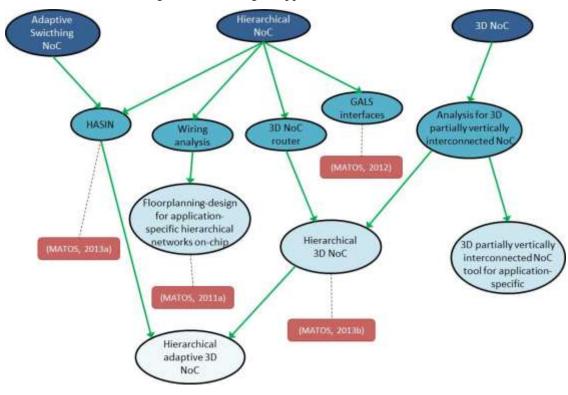

| 5 H   | IASIN – HIERARCHICAL AND ADAPTIVE NOC                                 | 135 |

| 5.1   | Experimental Results                                                  | 137 |

| 5.1.1 |                                                                       |     |

| 5.1.2 | HASIN Performance Results when the application has a double bandwidth | 142 |

| 5.1.3 | HASIN Performance Results when the application has a random mapping   | 145 |

| 5.1.4 |                                                                       |     |

| other | application                                                           |     |

| 5.1.5 | J                                                                     |     |

| 5.2   | Considerations                                                        | 155 |

| 6 T   | THREE DIMENSIONAL NETWORKS-ON-CHIP                                    | 157 |

| 6.1   | 3D NoC paradigms                                                      |     |

| 6.1.1 |                                                                       |     |

| 6.1.2 | ,                                                                     |     |

| 6.1.3 |                                                                       |     |

| 6.1.4 | $\boldsymbol{c}$                                                      |     |

|       | Interconnection with reduced number of TSVs                           |     |

|       | Hierarchical 3D NoC topology                                          |     |

|       | Proposed Hierarchical 3D NoC                                          |     |

|       | Hierarchical Architecture                                             |     |

|       | Packet Format                                                         |     |

|       | Experimental Results                                                  |     |

|       |                                                                       |     |

|       | CONCLUSION AND FUTURE WORKS                                           |     |

|       | Major contributions                                                   |     |

| 7.2   | Open issues and future directions                                     | 187 |

| REF   | ERENCES                                                               | 189 |

# 1 INTRODUÇÃO

Network-on-Chip, usually referred as NoC, has earned a space as an interconnection design due to its scalability and reusability in the multi and many core scenarios. As the number of processing elements (PEs) inside an integrated circuit has been increasing with technological advances, as well as system performance requirements, the interconnections of these systems has received a special attention. For up to a few processing elements, bus-based solutions may still be used (GUERRIER, 2000), (PANDE, 2005), (OETKEN, 2010), (SONG, 2009). However, as the number of components in these systems and their complexity scales up, the pressure on the bus system also increases. Therefore the use of bridged and multilayer buses becomes necessary, even though the protocol to control such a system gets more complex, presenting limited scalability, with variable and unpredictable performance. Moreover, at the physical level with technology scaling, while the gate delays decrease the global wire delays do not reduce in the same rate (ITRS, 2011), which will also impact the system performance. This issue surfaces in both general-purpose multicores such as Chip Multi-Processors (CMPs) and in heterogeneous application-specific Multi-Processor Systems on Chips (MPSoCs) (JERRAYA, 2005). They comprise of several components that need to be connected together in an efficient way, in order to sustain low energy consumption with enhanced performance.

Because of the aforementioned issues, over the last decade the use of Networks-on-Chip (NoCs) has been considered as an alternative to the interconnection infrastructure (TEWKSBURY, 1992), (GUERRIER, 2000), (HEMANI, 2000), (DALLY, 2001), (BENINI, 2002). The concept of switching networks originated in 1992 (TEWKSBURY, 1992), but only some years later did the use of a network-based interconnect begin to gain strength (GUERRIER, 2000). Finally the well-known NoC denomination was proposed by Hemani in 2000 (HEMANI, 2000). Therefore, SoCs (System-on-Chip) with NoCs have been a trend in the last years. Some examples of heterogeneous SoCs that use NoCs can be observed in the OMAP five platform (Texas) (TEXAS, 2013), Spear1310 and Spear1340 (ST, 2013). There are also some examples of homogeneous systems that use an NoC, such as the 48-core Intel Single-chip Cloud Computer (HELD, 2010) and the Tile64 (TILERA, 2013). This industry

movement means that old approaches such as point-to-point, crossbars, bus and others can no longer meet the communication requirements for some of the current systems.

One of the advantages of using NoCs as interconnection infrastructure is its modularity (DALLY, 2001), (PANDE, 2005), (BOLOTIN, 2004), (PASRICHA, 2008). It is a key asset in supporting scalability from the ground up, particularly in terms of performance. Physical-design-aware NoC components enable large-scale System-on-Chip designs, with more predictable (and possibly guaranteed) performance (BENINI, 2002) (NICOPOULOS, 2010). Moreover, the distributed nature of NoC infrastructures with redundancy of components can be effectively manipulated to enhance the system-level reliability (DE MICHELI, 2010).

An NoC can be described mainly by its topology, the strategies used for routing, flow control, switching, arbitration and buffering. The network topology can be represented as an arrangement of nodes and channels on a graph. The routing strategy determines how a message chooses a path through the topology, while the flow control deals with the allocation of channels and buffers of a message, as it follows the chosen path. The switching mechanism removes data from a router input channel and places it in an output channel, while the arbitration strategy is responsible for scheduling the use of channels and buffers by the messages (ZEFERINO, 2003). A switching network presents a set of switching elements with physical connections between their terminals (GUERRIER, 2000). NoCs emerged with the objective of transmitting the messages in packets, moving data from one node to another. The basic component of a NoC is the router whose function is to forward the incoming packets to one of its neighboring routers. This process is repeated in each router until the packets reach the final destination (GUERRIER, 2000).

In the next section it will be discussed the problems foreseen for the next years in terms of interconnecting designs for complex systems. Following that, the work context and the adopted solutions for each related problem are presented in section 1.2, identifying the reasons that point out the need for other alternatives of networks-on-chip. The goals and contribution of this work are described in section 1.3 and finally, the document organization is discussed in section 1.4.

#### 1.1 Problem Description

The reduction in nanoscale technology and consequently, in device sizes has led to a considerable increase in the chip density (WEERASEKERA, 2009), (PASRICHA, 2009),

(ITRS, 2011). Therefore, in association with this evolution, interconnection design for these systems is not so trivial, since the number of processing elements (PEs) in a system is continuously growing and the systems are becoming increasingly complex (NICOPOULOS, 2010), (KUMAR, 2012).

Until a few years ago, PEs were interconnected by buses, crossbars or ad-hoc interconnection structures. However, due to the limitations of these interconnection devices, new interconnection designs present other features that should be considered, such as:

- System heterogeneity;

- Requirements for high performance associated with awarded power consumption;

- Need to allow the system to be updated;

- Possibility of executing different applications considering the same interconnection device.

Then, due to all these requirements and huge design space, intelligent networks-onchip, with features applied for different scenarios, need to be applied. An NoC can have many features tuned to provide high performance with low overheads for each application. In an NoC, the link-level, as well as the router design and protocol level, can all be configured to achieve the specifications of each application. The goal can be related to the Quality-of-Service (QoS), physical constraints and/or reliability issues, and each system can have goals in specific aspects. As a result of these questions, the first NoC architectures no longer meet the requirements of the current and next MPSoC designs. Several proposed NoC architectures for NoCs with the purpose of reducing the energy consumption and increasing the system performance can be found in the literature. Nevertheless, several of these proposals present very expensive architectures, composed of virtual channels, tables and complex controls. With the addition of all such hardware resources, these NoC architectures can be prohibitive in the field of embedded systems. In this manner, the problem related to the system interconnection is not satisfactorily solved and so other alternatives need to be proposed. This work focuses exactly on proposing different techniques for varied scenarios of MPSoCs. In order to understand the future MPSoCs needs, it is important to highlight the main NoC challenges, which are as follows:

1. Large latency in the transmission of messages due to a high number of hops between the source and destination, since the trend for SoCs is a curved increase in the number of PEs (ITRS, 2011), (PASRICHA, 2009), (WEERASEKERA, 2009). Hops is the average number of switches that a

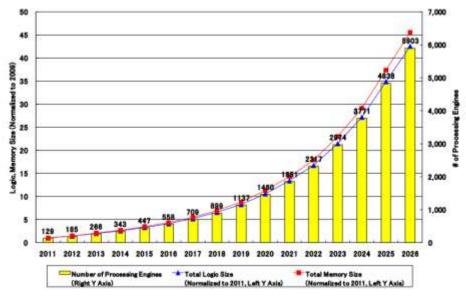

packet traverses to reach the destination node (PAVLIDIS, 2011). Figure 1.1 was extracted from International Technology Roadmap for Semiconductors (ITRS, 2011) and shows the trend in the number of Processing Engines. Processing Engines are processors customized for a specific function. A function with a large-scale, highly complicated structure which will be implemented as a set of PEs. This architecture template enables both high processing performance and low power consumption, by virtue of parallel processing and hardware realization of specific functions. The architecture does not require specific processor array architectures or symmetric processors; its essential feature is its large number of PEs embedded within the SoC to implement a set of required functions (ITRS, 2011). Thus, SoCs will potentially have a large number of PEs in order to achieve the required performance objectives.

Figure 1.1 - Trend f number of PEs for SoC Consumer Portable Design Complexity.

Source: ITRS (2011, p.7).

2. Need to obtain NoC designs with a very high performance associated with low power and energy consumption. Many proposals present an elevated increase in power consumption to reach high performance (JERGER, 2008), (MODARRESSI, 2010). However, in the embedded systems context, the power features also need to be taken into consideration (DAS, 2009), (CHOU, 2010), (ITRS, 2011).

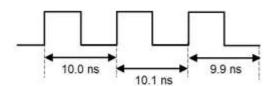

3. Very complex systems introduce long wires in the distribution of clock, causing clock skew and jitter (BEIGNÉ, 2006), (SHEIBANYRAD, 2007), (PANADES, 2007), (THONNART, 2009), (STRANO, 2011). Clock skew is defined as a spatial variation of the clock signal. The clock skew is measured by the difference between the reference point and a particular destination point. In this case, the clock signal can arrive at different points at different times (OKLOBDZIJA, 2003). Clock jitter is defined as temporal variation of the clock signal relative to the reference transition (reference edge) of the clock signal (OKLOBDZIJA, 2003). Figure 1.2 illustrates how these two situations occur.

Figure 1.2 - (a) Example of Clock Skew and (b) Jitter.

(a)

# Clock Skew: spatial variation Ref Clk End Clk Lighter

Jitter: temporal variation

(b)

Source: elaborated by the author.

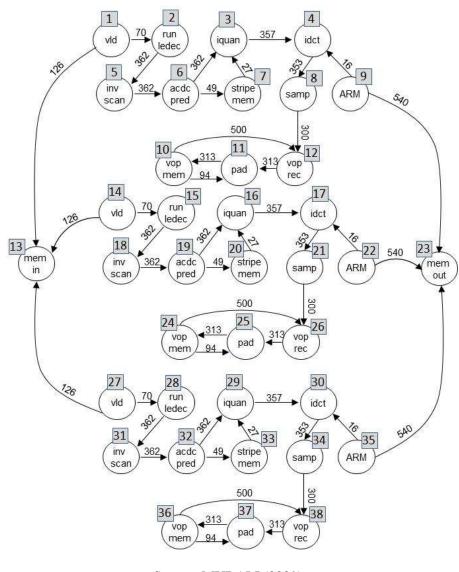

4. Need to meet different requisites and communication rates to provide the required performance at runtime, even when there are changes in the bandwidths of the cores (NICOPOULOS, 2006), (MATOS, 2011c), (BOBDA, 2005), (YING-CHERNG, 2011). In order to better understand this requirement, Figure 1.3 presents two very common benchmarks (BERTOZZI, 2005). Analyzing these figures, the bandwidth requisites of each communication can be observed. In addition, the same core used in other

applications has a different function, as, for example a RISC processor presents a specific role in each benchmark. In this manner, the same system must be able to run different applications and have its bandwidths updated according to the application being executed. In such a case, modern MPSoCs present a high complexity and they must efficiently handle some situations not foreseen in the design time.

(a) (b)

vid 70 run liquan 367 lidet

inv 362 acdc 49 stripe up arm

Figure 1.3 - (a) VOPD and (b) MPEG benchmarks with the communication core graph.

MPEG4

Source: BERTOZZI (2005).

vop

VOPD

5. Systems composed of many applications, presenting different communication needs, such as a large variation in the communicate rates due to the heterogeneity of the cores (HU, 2006), (STENSGAARD, 2008). This point is also evidenced in the figure 1.3. A common observation related to these benchmarks is the heterogeneous communication nature of SoCs, as each core only communicates with few others with a specific rate. These features can be found out from the current systems in the industry, like Tile-Gx (TILERA), OMAP5430 (TI), SPEAr1310 (ST). These systems integrate cores with different functions and requirements. The concept of Out-of-Order cores (OoCs) and In-order-Cores (IoCs) were introduced in (MANFERDELLI, 2008), where distinct communication behaviors are demanded in an MPSoC. OoCs are larger and dissipate more power than IoCs. Moreover, there is more communication among IoCs than among OoCs. Figure 1.4 exemplifies an MPSoC composed of OoCs and IoCs. An adequate NoC design must be able to manage these different requisites of an MPSoC.

DRAM DRAM loC loC Ctlr Ctlr cache cache loC cache loC cache cache cache cache PCle PCle cache cache NoC NoC loC cache cache cache cache loC loC cache cache DRAM DRAM loC loC

Figure 1.4 - Example of cores in an MPSoC.

Source: MANFERDELLI (2008).

6. Increase in the wire delay and wire power caused by the reduction of the technological scale (PARSRICHA, 2009), (WEERASEKERA, 2009), (ATIENZA, 2008). The wire does not scale with the gates due to the increment of wire resistance (HO, 2001). This characteristic will be better explained in subsection 2.3.1.

Based on the main problems related in this section, it was possible to observe the real requirements to be introduced in the proposed solution. In the next section, the strategies to solve these problems will be discussed.

# 1.2 Motivation and Work Context

When this work began, there was a lot of research related to networks-on-chip but little use in the industry. Nowadays, the use of a network-on-chip in the industry is a reality and necessity. Besides it is also possible to find specific companies designing NoCs, (ARTERIS, INOCs, SONICS, BLENDICS), confirming that old interconnection devices do not comply with the current design requirements.

This work considers several essential features for new SoC designs, focusing on what the ideal interconnection solution for these systems would be. The studies and proposals raised in this work take into account the NoC topologies, adaptabilities, switching mechanisms and the new context of design in 3 dimensions and their interconnections. From these analyses it is clear that conventional NoC solutions, as for example, a 2D mesh topology

with a simple packet switching mechanism, without any possibility of adaptability, do not meet the requirements for the future systems.

The proposal of this thesis presents combined solutions for the aforementioned challenges. Table 1.1 correlates the appropriate solution for each challenge. As can be observed from this table, it is possible to obtain an interconnection solution that meets all the raised issues with just four appropriately employed strategies.

Table 1.1 - Current challenges presented in section 1.1 for interconnected designs of MPSoCs and the related solutions considered in this work.

| Challenges                                 | Solutions                                                                                                                                   | Chapters |

|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Large systems increase the system latency  | <ul> <li>✓ Hierarchical interconnections</li> <li>✓ Adaptive strategy</li> <li>✓ 3D NoCs</li> </ul>                                         | 3, 4, 6  |

| High performance associated with low power | <ul> <li>✓ GALS</li> <li>✓ 3D NoCs</li> <li>✓ Hierarchical interconnections</li> <li>✓ Adaptive strategy + hierarchical topology</li> </ul> | 3, 5, 6  |

| 3<br>Clock skew<br>and jitter              | ✓ GALS                                                                                                                                      | 3        |

| Need to meet different system requirements | ✓ Adaptive strategy                                                                                                                         | 4, 5     |

| 5<br>Heterogeneous<br>Systems              | ✓ Hierarchical interconnections                                                                                                             | 3        |

| Increase in the wire delay and wire power  | ✓ 3D NoCs                                                                                                                                   | 6        |

The problem related to the size and complexity of the current and future systems (challenge 1) can be solved using a topology able to reduce the communication latency, like hierarchical and 3D topologies (GUERRE, 2010), (KUMAR, 2012).

As this work considers heterogeneous systems, the topology exploration is also one manner to combine high performance with low power (challenge 2 and challenge 5) (HOLLTEIN, 2006). Another ideal alternative for heterogeneous systems is to define the operating frequency according to the requirements of each part of the system. This can be provided with the use of operating frequencies defined for system isles, avoiding specifying a higher operating frequency than necessary for parts of the circuit, which would result in larger power consumption (LUDOVICI, 2011). The technique that allows the use of different operating frequency is called GALS (Globally Asynchronous Locally Synchronous). In GALS systems, the design can be partitioned in different frequency islands and the interconnection infrastructure is isolated by dual clock FIFOs at the boundary (LUDOVICI, 2011). The use of GALS is also a solution for problems related to clock skew and jitter (challenge 3), since with GALS the problems of clock distribution in the chip are reduced (BEIGNÉ, 2006). Still regarding challenge 2, the use of an adaptive strategy for NoCs is always an alternative for this problem. The adaptive NoC solutions can still be applied when the system or application has alterations or updates in their communication pattern (challenge 4) (FARUQUE, 2008), (NICOPOULOS, 2006).

An efficient solution related to the long links generated due to the large number of processing elements in a system, is the three dimensional (3D) designs. 3D designs allow shorter wires inside each chip layer and also short vertical interconnections between the layers (challenge 6) (SHEIBANYRAD, 2010).

### 1.3 Goals and Contributions

The main goal of this work is to provide a set of solutions for the next generation of heterogeneous MPSoCs, which are able to obtain high performance combined with low power consumption and small chip area. In order to accomplish this objective, a novel hierarchical topology and an intelligent adaptive switching mechanism for NoCs were developed. The hierarchical proposal is a combination of mesh topology and crossbars. These strategies were also explored in network-on-chip in three dimensional. The need for each proposed solution is linked according to the:

• system complexity;

- number and kind of cores;

- bandwidth;

- power requirements;

- need to update the application.

For example, if it is a specific application that demands high performance but would not present changes in the communication traffic, the ideal interconnection solution in terms of topology from an algorithm that takes into account the application behavior, can be specifically defined for that system. However, if the system is large and composed of heterogeneous components designed from different technologies; the solution could be the use of a hierarchical 3D NoC.

Solutions for 2D designs, such as, hierarchical topology and adaptive strategy, will be presented. The integration of these two solutions in a same NoC is investigated, analyzing the situations where advantages in this employment are obtained. Besides this, some experiments for 3D designs are also started in this work, expanding some of the 2D solutions to the 3D context. Results for different scenarios give evidence of the advantages of the proposed solutions compared to others.

The major contribution of this work is to succeed in the use of a simple topology architecture that provides small area and power consumption with high performance due to the hierarchy where the communication locality must be explored. Combined with this solution, when the initial topology needs to meet with variations in the system communication pattern, an adaptive solution allows low latency to be ensured even in intra-cluster communications. Different studies were analyzed to verify the effectiveness of this solution, such as using a specific hierarchical topology to run different heterogeneous applications and increase the bandwidths in the inter clusters. As well as this, it was proven that the proposed topology match very well with the requisites of a 3D design, as it allows the reduction of the number of vertical interconnections, which are expensive and prone to defect. Results show even more benefits in the use of the proposed topology in three dimensional.

# 1.4 Organization

This thesis is organized into 7 chapters. Before presenting the contributions, Chapter 2 provides an appropriate background of the work in this thesis. As the hierarchical proposal presents a hybrid NoC, different alternatives already used, such as buses and crossbars, are discussed as well as their advantages and disadvantages compared to current solutions. The

need and reasons that led to other interconnection solutions like the networks-on-chip are also discussed in this chapter. Following that, the main NoC features are presented.

Chapter 3 introduces the motivation and state-of-the-art hierarchical topologies. Next, the proposed hierarchical topology and its architecture are presented. An automatic tool was developed to find an optimal mapping for the specific proposed topology. From this tool, some initial results are discussed for some benchmarks.

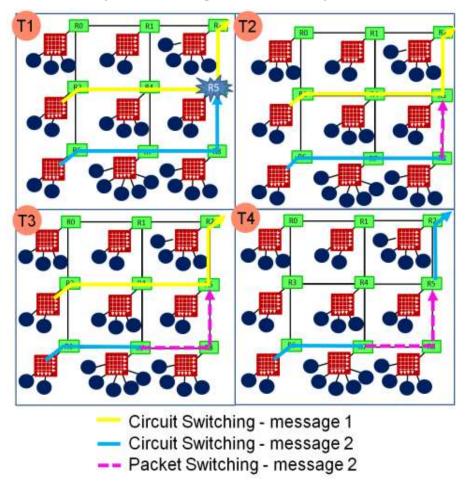

Chapter 4 presents another proposal for NoCs based on adaptability. This proposal explores switching modes for networks-on-chip. A strategy that allows using up to three switching modes was investigated. Firstly, the state-of-the-art and related works about switching adaptability in NoCs are discussed. After, the proposed adaptive NoC architecture called MINoC is presented. In the end of this chapter, performance and synthesis results are discussed.

Chapter 5 extends the integration of the two previous proposals in a same NoC. This strategy was adopted to be able to manage with possible changes in the communication rates foreseen at design time. In this manner, the high performance is ensured even when the system is updated or suffers alternations in the bandwidths of cores. Different situation were evaluated in order to prove the resilience of the proposed adaptive and hierarchical solution.

Chapter 6 presents a recent need in interconnection: network-on-chip for 3D designs. In this chapter a set of 3D design features and many factors that impact directly in an interconnection solution are raised. From these points of view, the advantages obtained when one makes use of the proposed hierarchical topology in 3D integrated circuits are perceived. Results for the previous strategies are presented and compared with other solutions.

Finally, chapter 7 provides concluding remarks on the work presented. The chapter summarizes the thesis, outlines its contributions and proposes future research directions.

#### 2 SYSTEMS, COMMUNICATIONS AND THEIR INTERCONNECTIONS

#### 2.1 Communication Characterization

Before presenting the features of the systems and their interconnection devices, it is important to define some properties of these components to later use them to compare architectures.

# Properties:

- Latency: Latency refers to how long the data/message takes from source to destination. It is indicated by the absolute time for the completion of a task (KOGEL, 2006). A latency guarantee occurs whenever a data unit crosses the communication architecture and reaches its destination within a finite amount of time (PASRICHA, 2008). It is usually measured as a time unit, for example seconds or cycles.

- **Throughput**: in general refers to the amount of information over time. This information can be defined on several levels of granularity, for example, tasks, data, bytes, bits and still in packages or flits in the NoC context (PASRISHA, 2008).

- **Bandwidth**: refers to how much data can be moved per time unit. A bandwidth guarantee concludes that a group of data units passes through a portion of the communication architecture at a certain data rate (PASRISHA, 2008).

- **Power Dissipation**: this is a measurement that denotes the energy per time. In order to better understand this measurement, one considers two situations. For example, the battery lifetime of a smartphone; it depends directly on the energy consumption; however the packaging costs depend on the heat dissipation properties which are measured by the power consumption (KOGEL, 2006).

Computational Efficiency: efficiency is derived from performance and power consumption (bits/s x W). This measurement is very relevant since it characterizes the efficiency of a given architectural element taking into account the costs of obtaining a required performance. It is easy to obtain architecture with high performance but consuming a lot of power. In this case, the efficiency will be low.

# 2.2 Before the NoCs

As this work will present and propose some hybrid interconnection devices, it is important to understand the evolution and the reasons for that. Besides, it is interesting to analyze when it is more appropriate to use one solution in place of another. Thus, following the main interconnection architectures before the introduction of NoCs will be verified.

# 2.2.1 Point-to-point interconnection

The simpler possibility to interconnect the devices of a system is point-to-point (Figure 2.1). In this case, each device is directly connected to another by a dedicated path. Although this alternative can present high performance, since the message can be sent with a minimal delay, this option is inflexible and presents limited scalability. This happens because according to the number of core increases, the physical implementation becomes more difficult due to the routing and the long wires. Analyzing the floorplan of a large system interconnected by point-to-point, long wires are required to cross the core areas.

C5 C3 C3

Figure 2.1 - Example of point-to-point interconnection.

Source: elaborated by the author.

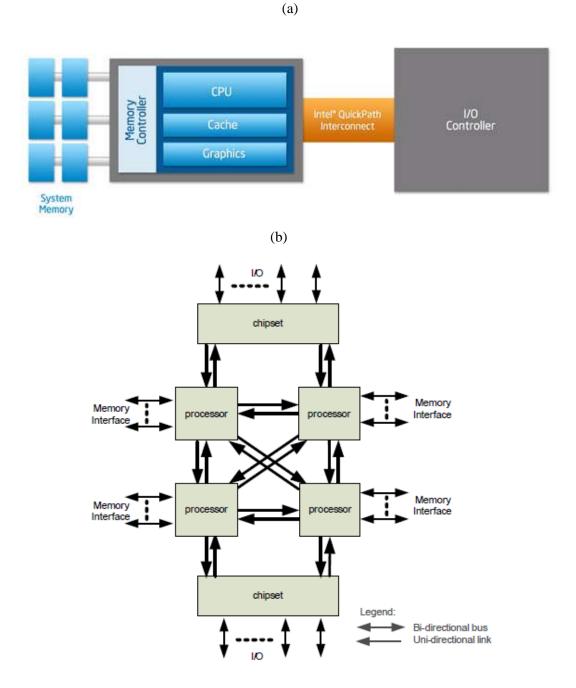

In industry, it is possible to find some examples that use point-to-point concepts. Intel proposed the QuickPath (QUICKPATH, 2008) to interconnect multicores. The differential of this device relative to other older solutions was that it presented one path to send data and another to receive. Besides this, QuickPath Interconnect (QPI) presents a path separated for memory and another for devices. One of the biggest changes compared to other alternatives

used by Intel, is the implementation of scalable, shared memory, since old devices use a single shared pool of memory connected to all the processors by a bus. With QPI, each processor has its own dedicated memory that is accessed directly through an Integrated Memory Controller. So, whenever a processor needs to access a dedicated memory of another processor, it can do through QPI where all processors are linked.

Another example of point-to-point interconnection, designed to increase the communication speed is HyperTransport at AMD (HYPERTRANSPORT, 2003). HyperTransport was designed five years before QuickPath and both present similar speeds, although these two devices are completely incompatible. The interconnection used by AMD separates data paths for input and output, enabling the processor to read and write at the same time. QuickPath also employs double data rate technology to squeeze two data transfer per clock. It has a variable bit-width between 2 and 32 bits.

With these two examples, an inverse process has occurred since these interconnection devices emerged to replace the buses used previously. In this case, this change was defined due to the high speed of the point-to-point compared to the buses. As these systems are composed of only a few cores (Figure 2.2(b)), this alternative complies with the design requirements.

Figure 2.2 - (a) Example of system interconnected by Intel QuickPath and (b) its architecture.

Source: INTEL (2008).

# 2.2.2 Buses

Buses are the most common devices for system interconnection and they have been largely used in the last decades by the industry, still being employed in many designs nowadays. In fact, depending on the system, it can be an optimal interconnection solution and

this definition is decided in function of the core communication rates, the bus architecture and the system size.

The most notable feature of a bus is its simplicity. The basic function of a shared bus is to transfer a single message at a given time. All IPs (Intellectual Properties) are interconnected in the same device and, therefore, only one IP can access the bus, while the others wait their time. However, because of the way they are shared, buses are very limited and present a control based on masters and slaves. IPs defined as masters initiate a read or write data transfer. IP slaves never can initiate a transfer; they only reply to the transfer requests. However, as many masters can request the bus simultaneously, an arbiter is necessary. The arbiter monitors the requests and considers an algorithm to choose the master with the highest priority request. A bus also requires a decoder to specify to which component the transfer corresponds. The decoder block generates the select lines that define the target slave. The transaction address is decoded and from this, it is verified which slave base address stored in the registers, it matches. Buses can be a good option for broadcasting with a few IPs, since it is simple to implement, albeit that they present some disadvantages, such as: limited performance, poor scalability, limited frequency and others.

The most simple bus topology found in many SoC architectures is the Shared Bus, as depicted in Figure 2.3. In this model, several masters and slaves are connected in the same structure. A bus arbiter examines the requests from the master interfaces and grants access according to the specified bus protocol. In this topology, the bus load is increased adding masters or slaves, limiting the bus bandwidth.

Besides the implementation simplicity, the advantage of this topology is the low area costs of few cores. The disadvantages of shared-bus architecture are large load per data bus line, long delay for data transfer, large energy consumption, and low bandwidth (MITIC, 2007). These disadvantages occur since every additional IP block connected to the bus adds to this parasitic capacitance, in turn causing increased propagation delay. As the number of IP blocks increases in a bus, the associated delay in bit transfer over the bus may grow and will eventually exceed the targeted clock period (PANDE, 2005).

Micro-controller

Digital Signal Processor

Device

Memory

Device

Figure 2.3 - Example of a system interconnected by a shared bus.

Source: elaborated by the author.

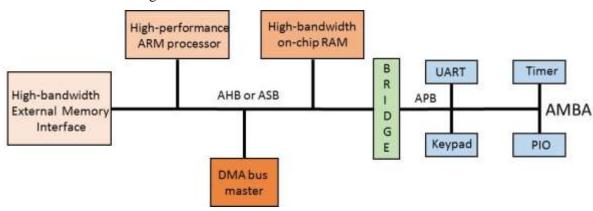

There are several bus architectures largely used in the industry, some examples are AMBA (Advanced Microcontroller Bus Architecture) Bus by ARM (AMBA, 2013), CoreConnect by IBM (IBM, 2007), Wishbone by Silicore Corporation, Avalon by Altera (SHARMA, 2012). The AMBA architecture is largely employed. The general view of the AMBA blocks is presented in Figure 2.4.

However, bus-based interconnections have performance bottlenecks as the number of cores increases (GUERRIER, 2000). Long buses (with many components) become slow due to large RC (resistive-capacitive) delays derived from each attached core (SILVANO, 2011, Chapter 1). Because of this, in order to increase the bus throughput, hierarchical buses have been considered. Hierarchical bus architecture consists of several shared buses interconnected by bridges. In this case, the bridges are responsible of interconnecting the buses, acting as a slave from one side and a master from the other. Cores are placed at the level in the hierarchy according to the required performance. However, transactions across the bridges involve additional overheads and during the transfer both buses remain inaccessible to the other components (MITIC, 2007). The increase in throughput is obtained as a result of the reduced load per bus and the possibility of having parallel transactions on different buses.

AMBA has a hierarchical bus structure and can be composed of two different bus features in each hierarchical bus. For example, AHB and ASB are used for high performance, allowing pipeline operation for multiple masters (Fig. 2.4). AHB is also used for burst transfers and split transactions. However, the APB is proposed for low power, with a simpler interface (Fig. 2.4) (AMBA, 2013). Several masters and slaves are connected to AHB and an arbiter decides which master will have data transferred. Data is transferred in bursts that involve the reading/writing of addresses and AHB is connected to APB via a bus bridge (ROYCHOUDHURY, 2003).

Figure 2.4 - Hierarchical AMBA bus architecture.

Source: AMBA (2013)

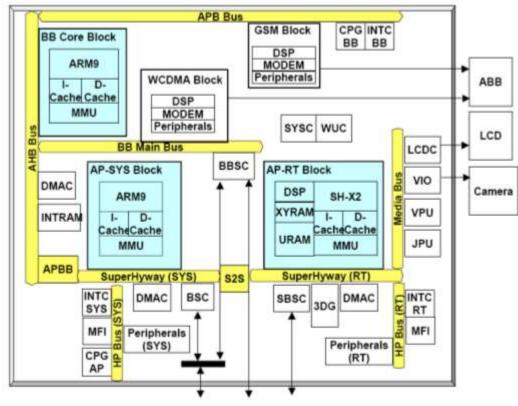

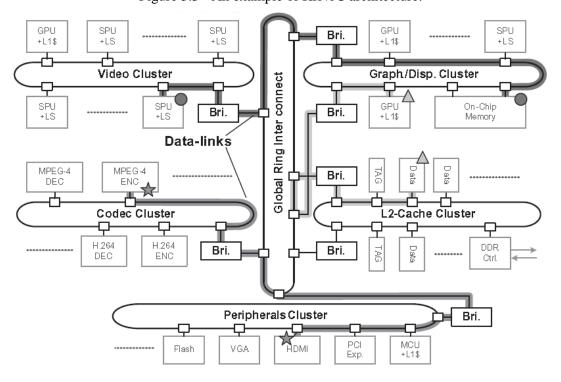

Other bus variations have been implemented by the industry in order to increase the throughput and reduce latency. Examples of this are depicted in Figures 2.5 and 2.6. In the first case, it is the IBM cell, a heterogeneous multicore processor (ROSTRUP, 2010) that uses a ring bus to interconnect the cores (PowerPC, synergistic Processing Elements and interfaces). The second figure (Figure 2.6) is the SH Mobile architecture (RENESAS, 2013) where the components are interconnected by a hierarchical bus, each with a specific bus feature.

Synergistic Processing Unit with SIMD engine SPE SPE SPE SPE Memory Flow Controllers 256 kB and DMA engines Local Store Memory on each SPE MEC LS MFC LS MFC LS MFC LS PowerPC Processor L1 High speed PPE interface for I/O L2 external I/O Interface EIB High speed Coherent XDR DRAM High speed external memory Interface Interface interface to interface other Cell processors High speed interconnect MFC LS MFC LS MFC LS MFC LS between PPE and SPEs SPE

Figure 2.5 - IBM Cell ring bus communication architecture.

Source: ROSTRUP (2010).

Figure 2.6 – SH Mobile G1 hierarchical bus communication architecture.

Source: RENESAS (2013).

The wide variety of buses presents the problem for reusable design, even though a number of companies and standard committees have attempted to standardize them (MITIC, 2007).

Although nowadays there are more efficient interconnection devices for System-on-Chips, the buses are still largely used in the industry and satisfactorily meet their system requirements, since these systems are not very complex in terms of bandwidth and number of IPs.

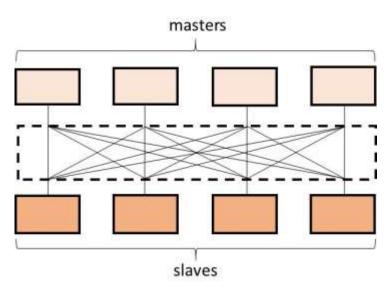

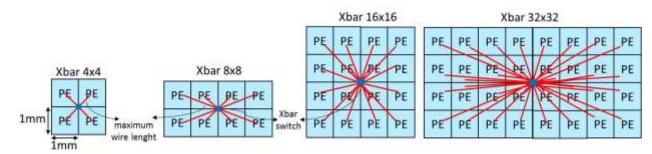

### 2.2.3 Crossbars

The crossbars appeared as an alternative to buses. Crossbars, also called bus matrix or bus crossbar (Figure 2.7), are simple components where the cores are interconnected by a switch. An arbiter is considered whenever there is competition for the same destination. In the simpler model, all cores can send messages to all others and, if the number of masters is equal to n, n transfers can be made in parallel. This possibility is the main advantage of the crossbars compared to the buses, since it allows concurrent transfers, improving the performance. Nevertheless, crossbars use more wires and logic components (one arbiter and multiplexer for each output port) which result in larger power consumption and area overheads (PASRICHA, 2008).

Figure 2.7 - Example of a full bus crossbar.

Source: elaborated by the author.

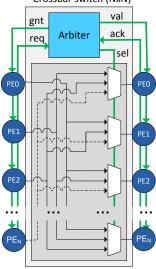

In the example of Figure 2.7, a full bus crossbar is presented. The internal crossbar architecture is presented in Figure 2.8. For each output port, one arbiter and one multiplexer are required, which can be verified. Other options considering partial bus crossbar have been proposed whenever the system does not require communication among all components. However, partial crossbars are less flexible, albeit that they reduce the number of wires. An example of commercial SoC with a full bus crossbar topology is the Niagara from SUN. This architecture connects eight SPARC processors, each one supporting up to four threads. Several efforts have shown the advantages of a full bus crossbar to significantly increase the throughput compared to the hierarchical bus strategies (PASRICHA, 2008).

Figure 2.8 - Crossbar architecture: wires, multiplexers and arbiters.

Crossbar switch (NxN)

gnt val

ack

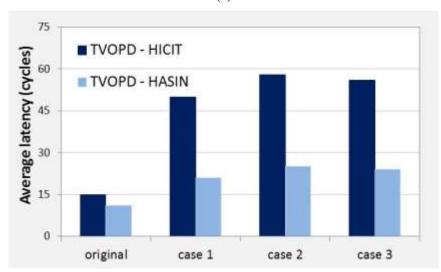

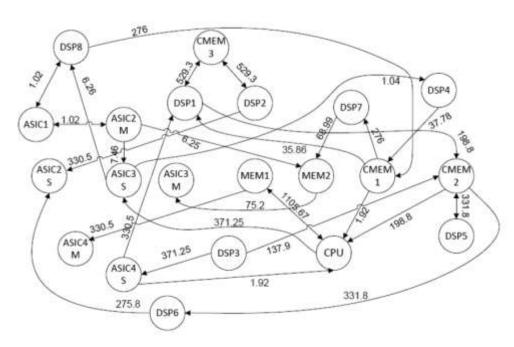

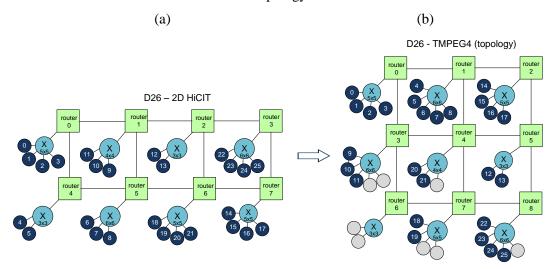

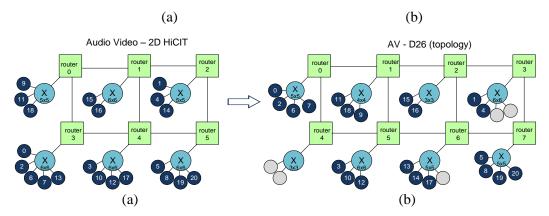

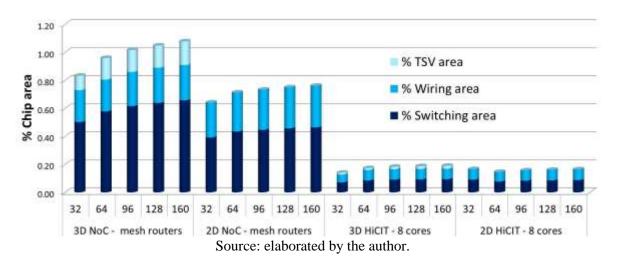

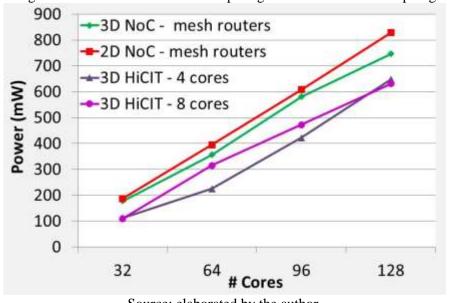

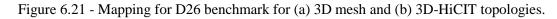

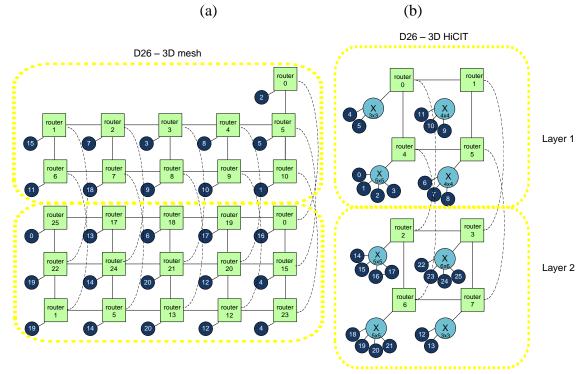

Source: elaborated by the author.